CS4952中文资料

AD9520-0_cn

图1.

应用

低抖动、低相位噪声时钟分配 SONET、10Ge、10GFC、同步以太网、 OTU2/3/4的时钟产生 和转换 前向纠错(G.710) 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟 高性能无线收发器 自动测试设备(ATE)和高性能仪器仪表 宽带基础设施

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

07213-001

SPI/I2C CONTROL PORT AND DIGITAL LOGIC

EEPROM

功能框图

CP LF

REFIN

SWITCHOVER AND MONITOR

OPTIONAL

REF1

STATUS MONITOR

PLL

VCO

REFIN

REF2

CLK

DIVIDER AND MUXES

ZERO DELAY

LVPECL/ CMOS DIV/Φ

OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 OUT9 OUT10 OUT11

12路LVPECL/24路CMOS输出时钟 发生器,集成2.8 GHz VCO

AD9520-0

特性

低相位噪声锁相环(PLL) 片内VCO调谐范围:2.53 GHz至2.95 GHz 可选外部3.3 V/5 V VCO/VCXO至2.4 GHz 1路差分或2路单端参考输入 支持最高250 MHz的CMOS、LVDS或LVPECL参考 参考输入接受16.62 MHz至33.3 MHz晶振 可选参考时钟倍频器 参考监控功能 自动/手动参考保持和参考切换模式,恢复式切换 参考间无 毛刺切换 从保持模式自动恢复 可选数字或模拟锁定检测 可选零延迟工作 12路1.6 GHz LVPECL输出分为4组 每组3路输出,共享一个带相位延迟的1至32分频器 加性输出抖动低至225 fs rms 分组输出的通道间偏斜:<16 ps 可以将每路LVPECL输出配置为2路CMOS输出(fOUT ≤ 250 MHz) 上电时所有输出自动同步 提供手动输出同步 SPI和I²C兼容型串行控制端口 64引脚LFCSP封装 非易失性EEPROM存储配置设置

SN74AC245PWLE中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-87758012A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type 5962-8775801RA ACTIVE CDIP J201TBD A42SNPB N/A for Pkg Type 5962-8775801SA ACTIVE CFP W201TBD A42N/A for Pkg Type 5962-8775801VRA ACTIVE CDIP J201TBD A42SNPB N/A for Pkg Type5962-8775801VSA ACTIVE CFP W201TBD A42N/A for Pkg Type SN74AC245DBLE OBSOLETE SSOP DB20TBD Call TI Call TISN74AC245DBR ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245DBRE4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245DW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245DWE4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245DWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245DWRE4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245N ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74AC245NE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74AC245NSR ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245NSRE4ACTIVE SO NS202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245PW ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245PWE4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC245PWLE OBSOLETE TSSOP PW20TBD Call TI Call TISN74AC245PWR ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC245PWRE4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54AC245FK ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type SNJ54AC245J ACTIVE CDIP J201TBD A42SNPB N/A for Pkg Type SNJ54AC245W ACTIVE CFP W201TBD A42N/A for Pkg Type (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.6-Dec-2006TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.6-Dec-2006TAPE AND REELINFORMATION24-Apr-2007DevicePackage Pins SiteReel Diameter (mm)Reel Width (mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74AC245DBR DB 20MLA 330168.27.5 2.51216Q1SN74AC245DWR DW 20MLA 3302410.813.0 2.71224Q1SN74AC245NSRNS 20MLA 330248.213.0 2.51224Q1SN74AC245PWRPW20MLA330166.957.11.6816Q1TAPE AND REEL BOX INFORMATIONDevice Package Pins Site Length (mm)Width (mm)Height (mm)SN74AC245DBR DB 20MLA 333.2333.228.58SN74AC245DWR DW 20MLA 333.2333.231.75SN74AC245NSR NS 20MLA 333.2333.231.75SN74AC245PWRPW20MLA333.2333.228.5824-Apr-200724-Apr-2007IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments Incorporated。

CS4922-CL资料

Preliminary Product InformationThis document contains information for a new product.Cirrus Logic reserves the right to modify this product without notice.1Copyright © Cirrus Logic, Inc. 1999(All Rights Reserved)P.O. Box 17847, Austin, Texas 78760(512) 445 7222 FAX: (512) 445 7581CS4922MPEG/G.729A Audio Decoder SystemFeaturesl DSP Optimized for Audio Decode, 24-bitFixed Point w/48-bit Accumulator l On-Chip Functional Blocks Include:-DSP with RAM and ROM Memories-CD Quality Stereo DAC with Output Filtering -Mono Output & Digital Volume Control-S/PDIF Transmitter, Bidirectional PCM Audio Port-Internal Phase Locked Loop for Clocking -Dedicated Compressed Serial Input Interfacel MPEG-1 & MPEG-2 Layers 1 & 2 With AllSample/Bit Rates and Ancillary Data Support.l MPEG-1 & MPEG-2 Packetized Audio Stream and Elementary Stream Input l G.729A Audio Decodel PCM Synthesis for Auxiliary Audiol Pin Compatibility with CS4920A and Primary Feature/Firmware Compatiblel +5 Volt Only CMOS, 44 pin PLCCDescriptionThe CS4922 is a complete audio decompression sub-system implemented in a single high integration mixed signal CMOS chip. The CS4922 has been widely used in direct broadcast system set-top boxes and proprietary embedded systems which pull compressed audio from local system memory.The CS4922 is tailored to include the necessary hard-ware and firmware to ensure proper audio/video synchronization for MPEG-2 audio decompression. In addition to audio decoding this programmable DSP solu-tion provides robust error concealment and feature implementations like ancillary data support and PCM synthesis.The CS4922 can also support the decode of other com-pression standards such as G.729A with a separate download image. The flexible architecture of the CS4922provides the ability to mix compressed audio with data from the auxiliary PCM port.ORDERING INFORMATIONCS4922-CL 44-pin PLCC CDB4922Evaluation BoardVD1VD4SCK/SCL SDA/CDOUT CDIN CS REQVA+Serial Control Port (SPI or I 2C)AUXLR AUXIN AUXOUT AUXCLK FSYNC SCLK SDATA Auxiliary Serial Audio Port Serial Audio PortRESET 90_CLK BOOT33 bit CounterDGND1DGND4DSPFLT CLKIN EXTCK ALTCLK CLKOUT PLL +Clock ManagerStereo DACAOUTM AOUTL AOUTR AES/EBU - S/PDIF TX TransmitterProgrammable IO/ PinsPIO XF1XF2XF3XF4AGND1AGND2JUL ‘99DS227PP2TABLE OF CONTENTS1CHARACTERISTICS AND SPECIFICATIONS (4)ANALOG CHARACTERISTICS (4)D/A INTERPOLATION FILTER CHARACTERISTICS (4)ABSOLUTE MAXIMUM RATINGS (5)RECOMMENDED OPERATING CONDITIONS (5)DIGITAL CHARACTERISTICS (5)SWITCHING CHARACTERISTICS - CLOCKS (6)SWITCHING CHARACTERISTICS - EXTERNAL FLAGS (6)SWITCHING CHARACTERISTICS - PROGRAMMABLE INPUT/OUTPUT (6)SWITCHING CHARACTERISTICS - BOOT INITIALIZATION (7)SWITCHING CHARACTERISTICS - CONTROL PORT (SPI MODE) (8)SWITCHING CHARACTERISTICS - CONTROL PORT (I2C MODE) (10)SWITCHING CHARACTERISTICS - SERIAL AUDIO PORT (12)SWITCHING CHARACTERISTICS - AUXILIARY DIGITAL AUDIO PORT (13)2TYPICAL CONNECTION DIAGRAM (14)3THEORY OF OPERATION (15)3.1Introduction (15)4PERIPHERALS (15)4.1Clock Manager (15)4.233-bit Counter (16)4.3Digital to Analog Converter (16)4.4Digital Audio Transmitter (17)4.5Audio Serial Input Port (17)4.6Auxiliary Digital Audio Port (17)4.7Serial Control Port (17)4.7.1I2C Mode (18)4.7.2Rise Time on SCL/SCK (20)4.7.3SPI mode (20)4.8External Flag Pins (22)5BOOT PROCEDURE (23)6POWER SUPPLY AND GROUNDING (24)7DAC FILTER RESPONSE PLOTS (26)8PIN DESCRIPTIONS (27)Power Supplies (27)Digital-to-Analog Converter (28)Serial Audio Port (28)Digital Audio Transmitter (28)Clock Manager (28)Control (29)Serial Control Port (30)Auxiliary Digital Audio Port (30)9PARAMETER DEFINITIONS (31)10PACKAGE DIMENSIONS (32)Contacting Cirrus Logic SupportFor a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: /corporate/contacts/I2C is a registered trademark of Philips Semiconductor.Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product infor-mation describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provid ed “AS IS” without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc.Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trade-marks and service marks can be found at .2LIST OF FIGURESFigure 1.Boot Timing (7)Figure 2.SPI Control Port Timing (9)Figure 3.I2C® Control Port Timing (11)Figure 4.Serial Audio Port Timing (12)Figure 5.Auxiliary Audio Port Timing (13)Figure 6.Typical Connection Diagram (14)Figure 7.CLKOUT Generation Circuit (16)Figure 8.DAC (16)Figure 9.Auxiliary Data Input Formats (17)Figure 10.Auxiliary Data Output Formats (17)Figure 11.Multi-channel Auxiliary Data Formats (18)Figure 12.Control Port Timing, I2C® Write (19)Figure 13.Serial Control Port (19)Figure 14.Control Port Timing, I2C® Read (20)Figure 15.I2C® Connection Diagram (21)Figure 16.Control Port Timing, SPI Write (21)Figure 17.Control Port Timing, SPI Read (22)Figure 18.CS4922 Suggested Layout (24)Figure 19.CS4922 Surface Mount Decoupling Layout (25)Figure 20.DAC Frequency Response (26)Figure 21.DAC Phase Response (26)Figure 22.DAC Transition Band (26)Figure 23.DAC Passband Ripple (26)341CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS (T A = 25 °C; VA+, VD+ = 5V; CLKIN = 27 MHz; Full-Scale OutputSinewave, 1.125 kHz; Word Clock = 48 kHz (PLL in use); Logic 0 = GND, Logic 1 = VD+; Measurement Bandwidth is 20 Hz to 20 kHz; Local components as shown in "Typical Connection Diagram"; SPI mode, I 2S audio data; unless otherwise specified.)Notes: 1.10 k Ω, 100pF load for each analog signal (Left, Right).30 k Ω, 100pF load for analog Mono signal.D/A INTERPOLATION FILTER CHARACTERISTICS (See Figures 20 through 23)* Refer to Parameter Definitions on page 31 of this data sheet.Specifications are subject to change without notice.Parameter*SymbolMin Typ Max Units Dynamic PerformanceDAC Resolution16--Bits DAC Differential Nonlinearity DNL--±0.9LSB Total Harmonic Distortion AOUTL, AOUTR (Note 1)AOUTM THD -0.010.020.0150.03%Instantaneous Dynamic Range AOUTL, AOUTR (Note 1)(DAC not muted, A weighted)AOUTMIDR85809085-dB Interchannel Isolation (Note 1)-85-dB Interchannel Gain Mismatch --0.2dB Frequency Response -3.0-+0.2dB Full Scale output Voltage AOUTL, AOUTR (Note 1)AOUTM2.662.7 2.883.0 3.23.3Vpp Gain Drift-100-ppm/°C Deviation from Linear Phase --5Deg Out of Band Energy (Fs/2 to 2Fs)--60-dB Analog Output Load Resistance:Capacitance:8----100k ΩpF Power SupplyPower Supply Rejection (1 kHz)-40-dB Power Supply ConsumptionVA+VD+--2010040140mA mAParameterSymbolMin Typ Max Units Passband (to -3 dB corner)(Fs is conversion freq.).0-0.476Fs Hz Passband Ripple. --±0.1dB Transition Band. 0.442Fs -0.567FsHz Stop Band.≥0.567Fs--Hz Stop Band Rejection.50--dB Stop Band Rejection with Ext. 2Fs RC filter.57--dB Group Delay. -12/Fs-s5ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0V, all voltages with respect to ground.)WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.RECOMMENDED OPERATING CONDITIONS (AGND, DGND = 0V; all voltages with respectto ground.)DIGITAL CHARACTERISTICS (T A = 25 °C; VA+, VD+ = 5V ±10%; measurements performed understatic conditions.)Notes: 2.Not Valid for pin numbers 9, 12, 13, and 30 which are configured with on-chip pull-down resistors. Notvalid for pin number 29 which is a static input signal and should be tied to either VD+ or DGND.ParameterSymbol Min Max Units DC Power Supplies:Positive Digital Positive Analog | | VA+ | - | VD+ | |VD+VA+-0.3-0.3- 6.06.00.4V V V Input Current, Any Pin Except Supplies I in -±10mA Digital Input VoltageV IND -0.3(VD+) + 0.4V Ambient Operating Temperature (power applied)T Amax -55125°C Storage TemperatureT stg-65150°CParameterSymbol Min Typ Max Units DC Power Supplies:Positive Digital Positive Analog | | VA+ | - | VD+ | |VD+VA+ 4.504.50- 5.05.0- 5.505.500.4V V V Ambient Operating TemperatureT A-70°CParameterSymbol Min Typ Max Units High-Level Input Voltage V IH TBD 2.25-V Low-Level Input VoltageV IL --0.8V High-Level Output Voltage at I o = -2.0 mA V OH VD x 0.9--V Low-Level Output Voltage at I o = 2.0 mA V OL --VD x 0.1V Input Leakage Current(Note 2)I in-- 1.0µA6SWITCHING CHARACTERISTICS - CLOCKS (T A = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 =DGND, Logic 1 = VD+, C L = 20pF)SWITCHING CHARACTERISTICS - EXTERNAL FLAGS (T A = 25 °C; VA+, VD+ = 5V;Inputs: Logic 0 = DGND, Logic 1 = VD+, C L = 20pF)Notes: 3.Assumes 2k Ω pull-up to 5V supply on XF1-XF4 pins.SWITCHING CHARACTERISTICS - PROGRAMMABLE INPUT/OUTPUT (T A = 25°C;VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C L = 20pF)ParameterSymbol MinTyp MaxUnits Master Clock Frequency CLKIN 27MHz Master Clock Duty Cycle CYCK 405060%Clock OutputCLKOUT--256 Fs MHzParameterSymbol MinTypMax Units Rise time of XF1-XF4(Note 3)t rxf 200ns Fall time of XF1-XF4t fxf100nsParameterSymbol MinTypMax Units I_O = 0Input Frequency f pio 350kHz Risetime of PIO t rpio 200ns Fall time of PIOt fpio 200ns I_O = 1Rise time of PIO t rpo 200ns Fall time of PIOt fpo200ns7SWITCHING CHARACTERISTICS - BOOT INITIALIZATION (T A = 25 °C; VA+, VD+ =5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C L = 20pF)Notes: 4.The mode of the Serial Control Port is selected by CS. CS = 1 is I 2C ® . CS = 0 is SPI mode.5.This delay is necessary after any rising edge of RESET to allow time for the part to initialize and forthe on-board PLL to stabilize.ParameterSymbol Min Max Units BOOT Setup Time to RESET Rising t bsu 350-ns RESET Rising to Boot Hold Time t bh 450-ns CS Setup Time to RESET Rising (Note 4)t cssu 200-ns RESET Rising to CS Hold Time t csh 400-ns RESET Low Timet rlow 50-µs SCK/SCL Delay Time from RESET Rising(Note 5)t rsc 2-ms SCK/SCL falling to CS rising on last byte of downloadt sfcr3-µsFigure 1. Boot Timing8SWITCHING CHARACTERISTICS - CONTROL PORT (SPI MODE) (T A = 25 °C;VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C L = 20pF)Notes: 6.Data must be held for sufficient time to bridge 300(50) ns transition time of SCK/SCL.7.CDOUT should NOT be sampled during this time period.8.REQ will only go HIGH if there is no data in SCPOUT at the rising edge of SCL/SCK during a READoperation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 k Ω. C L = 20 pF.9.If REQ went HIGH as indicated in note 7, then REQ will hold high at least until the next rising edge ofSCK/SCL. If data is in SCPOUT at this time REQ will go active LOW again. This condition should be treated as a new READ process. Address and R/W bit should be sent again.ParameterSymbolMin Max Units SPI Mode (CS = 0)SCK/SCL Clock Frequency (slow mode)(fast mode)f sck f sck --3502000kHz CS Falling to SCK/SCL Rising(slow mode)t css 20-ns Rise Time of Both CDIN and SCK/SCL Lines (slow mode)t r -50ns Fall Time of Both CDIN and SCK/SCL Lines (slow mode)(fast mode)t f t f --30050ns ns SCK/SCL Low Time (slow mode)(fast mode)t scl t scl 1100150--ns ns SCK/SCL High Time(slow mode)(fast mode)t sch t sch 1100150--ns ns Setup Time CDIN to SCK/SCL Rising (slow mode)(fast mode)t cdisu 25050--ns ns Hold Time SCK/SCL Rising to CDIN(Note 6)t cdih 50-ns Transition Time from SCK/SCL to CDOUT Valid (Note 7)t scdov -40ns Time from SCK/SCL Rising to REQ Rising (Note 7)t scrh -200ns Rise Time for REQ (Note 8)t rr -50ns Fall Time for REQ(Note 9)t rf -20ns Hold Time for REQ from SCK/SCL Rising (Note 9)t scrl 0-ns Time from SCK/SCL Falling to CS Rising t sccsh 20-ns High Time Between Active CSt csht200-nsFigure 2. SPI Control Port Timing910SWITCHING CHARACTERISTICS - CONTROL PORT (I 2C MODE) (T A = 25 °C;VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C L = 20pF)Notes:e of I 2C ® bus compatible interface requires a license from Philips.11.Data must be held for sufficient time to bridge the 300ns transition time of SCK/SCL.12.This rise time is shorter than the I 2C specifications recommend, please refer to the section on SCPcommunications for more information.13.REQ will only go HIGH if there is no data in the SCPOUT register at the rising edge of SCL/SCK duringa READ operation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 k Ω C L = 20pF.14.if REQ went HIGH as indicated in Note 13 then REQ will hold HIGH at least until the next rising edge ofSCK/SCL. If data is in the SCPOUT register at this time REQ will go active LOW again. This condition should be treated as a new READ process. The address and R/W should be sent again following a new START condition.ParameterSymbolMinMax Units I 2C ® Mode (CS=1)(Note 10)SCK/SCL Clock Frequency(slow mode)(fast mode)f scl 100400kHz Bus Free Time Between Transmissionst buf 4.7µs Start Condition Hold Time (prior to first clock pulse)t hdst 4.0µs Clock Low Time slow fast t low 4.71.2µs Clock High Timeslow fast t high 4.01.0µs SDA Setup Time to SCK/SCL Rising t sud250ns SDA Hold Time from SCK/SCL Falling (Note 11)t hdd 0µs Rise Time of Both SDA and SCK/SCL (Note 12)t r 50ns Fall Time of Both SDA and SCK/SCL t f 300ns Time from SCK/SCL Falling to CS4920 ACK t sca 40ns Time from SCK/SCL Falling to SDA Valid During READ Operationt scsdv40ns Time from SCK/SCL Rising to REQ Rising (Note 13)t scrh 200ns Hold Time for REQ from SCK/SCL Rising (Note 14)t scrl 0ns Rise Time for REQ (Note 13)t rr 50ns Fall Time for REQ(Note 14)t rf 20ns Setup Time for Stop Conditiont susp4.7µsFigure 3. I2C® Control Port TimingSWITCHING CHARACTERISTICS - SERIAL AUDIO PORT (T A = 25 °C; VA+, VD+ =5V; Inputs: Logic 0 = GND, Logic 1 = VD+; C L = 20 pF)Notes:15.The table above assumes data is output on the falling edge and latched on the rising edge. The SCLKedge is selectable in setting the EDG bit in the ASICN register. The diagram is for EDG = 1.ParameterSymbolMin Typ Max Units SCLK Frequency --12.5MHz SCLK Pulse Width Low t sckl 25--ns SCLK Pulse Width Hight sckh 25--ns SCLK rising to FSYNC edge delay (Note 15)t sfds 20--ns SCLK rising to FSYNC edge setup (Note 15)t sfs 20--ns SDATA valid to SCLK rising setup (Note 15)t sss 20--ns SCLK rising to SDATA hold time (Note 15)t ssh 20--nsRise time of SCLKt sclr --20nsFigure 4. Serial Audio Port TimingSWITCHING CHARACTERISTICS - AUXILIARY DIGITAL AUDIO PORTNotes:16.Fs determined by clock input rate and configuration of on-chip PLL.17.AUXCLK frequency selectable @ 32, 64, or 128 Fs via AUXCN register bits 1:0.ParameterSymbol Min Typ Max Units Input Sample Rate (Note 16)Fs 16-48kHz AUXCLK Period(Note 17)tsclk-1/(32Fs)1/(64Fs)1/(128Fs)-nsAUXCLK to AUXLR valid tlrun 0-25ns AUXCLK to AUXOUT data valid tdoun 0-25AUXIN data setup time to AUXCLK tdisu 50--ns AUXIN data hold time from AUXCLKtdiho3--nsFigure 5. Auxiliary Audio Port Timing2TYPICAL CONNECTION DIAGRAMFigure 6. Typical Connection Diagram3THEORY OF OPERATION3.1IntroductionThe CS4922 is a complete audio subsystem on a chip. It consists of a general-purpose Digital Signal Processor (DSP), and a number of supplementary analog and digital blocks. These supplementary blocks include a PLL clock multiplier, a serial au-dio input port, an auxiliary serial audio port, a CD quality stereo Digital-to-Analog Converter (DAC), an AES/EBU - S/PDIF compatible digital audio transmitter, and a serial control port. Figure 6 shows a typical connection diagram for the CS4922 in which a micro controller is used for loading the program code.The CS4922 is RAM based audio decoder that can be used to process compressed digital audio sig-nals. Serial audio data broadcast on networks such as cable TV, direct broadcast satellite TV, or the telephone system can be decompressed and con-verted to standard analog and digital signals. A wide variety of standard and proprietary decom-pression algorithms can be supported.CS4922 application code is available which per-forms industry standard MPEG 1 and 2, layers I and II. Application code is also available for G.729A decode.The DSP has a 24-bit fixed point data path, 5K words of program RAM, and 3K words of data RAM. The execution unit includes a 48-bit accu-mulator. The DSP can provide up to 12 MIPS. Either compressed digital audio data or PCM data can be delivered.For analog reproduction of the digital input, a ste-reo DAC using delta-sigma architecture is built-in. Switched-capacitor filters perform most of the re-construction process. Only a simple external pas-sive filter is needed to complete reconstruction.In addition to the analog output, an AES/EBU -S/PDIF compatible output is provided. This allows the designer the flexibility of transmitting the audio data in a standard digital format to an external sys-tem.To facilitate the downloading of DSP code to the CS4922, a serial control port, communicating in ei-ther I2C® or SPI format, is used. This port may also be used during run time to issue control commands to the DSP.4PERIPHERALSSix on-chip peripherals make the audio decoder ideal for decoding broadcast digital audio signals. It has a PLL clock manager, a CD quality DAC, a digital audio transmitter, a three pin serial port for audio data input, a serial bi-directional auxiliary port for digital audio data, and an SPI/I2C port for serial control information. Each peripheral has I/O mapped data, control, and status registers. Many peripherals can also generate interrupts.4.1Clock ManagerThe clock manager is primarily a clock multiplier circuit that takes a reference frequency of 27 MHz on CLKIN which is used for deriving internal clocking. At the heart of the clock manager circuit is a PLL (Phase-Locked Loop) circuit. The PLL is configured by software to produce the appropriate DSP Clock for the desired sample rate. All other in-ternal clocks required for the DAC and other pe-ripherals are derived from this root clock.The PLL’s internal VCO requires a capacitor to be connected to the FLT pin (pin 31). The typical val-ue of the FLT capacitor is 0.47 µf, which is suffi-cient for all allowable CLKIN input frequencies. It must be stressed that the best analog performance can only be achieved by placing the capacitor as close as possible to the FLT pin and that the proper layout precautions be taken to avoid noise coupling onto the FLT pin.The CLKOUT pin is a divided version of the DSP clock. A diagram of the CLKOUT generation cir-cuit is shown in Figure 7.The DSP clock is divided by a programmable di-vider and an additional divide by 2 before being output. The divider output is determined by the val-ue of the Q value which can be accessed through the application software. The divide by 2 guaran-tees a 50% duty cycle output. The Q value provides effective divides ranging from 1 to 1024, which means the frequency of CLKOUT can vary from the DSP clock frequency divided by 2 to the DSP clock frequency divided by 2048. CLKOUT can be used to synchronize external devices or generate most compressed bit rate clocks.4.233-bit CounterThe 33-bit-counter can be used to support MPEG synchronization of audio and video. This loadable counter is targeted to operate at 90 kHz. The 90kHz clock may be derived from a 27 MHz mas-ter clock provided at CLKIN (if available) or from a 90 kHz clock provided at Pin 19 90_CLK. The se-lection of the counter clock is made via the register bit DIV which is accessible through the application code. When set, the DIV bit divides the clock at CLKIN by 300 and provides the divided clock to 33-bit-counter.4.3Digital to Analog ConverterThe digital to analog converter (DAC) is a dual channel CD quality DAC. It is designed with delta sigma architecture. The baseband audio is interpo-lated to 128Fs (192Fs) before going into the modu-lator. The modulator is third order and is followed by a 1 bit DAC/switch capacitor filter stage. An ex-ternal passive filter completes the reconstruction process. The output is single ended with a drive ca-pability down to 8 kΩ. Figure 8 is a block diagram of the DAC.The interpolation filter produces images which are attenuated by at least 56 dB from .584Fs to 128Fs (192Fs). At a 48 kHz sample rate, a full scale signal at 20 kHz will produce an image at 28 kHz which is attenuated by more than 60 dB.The out-of-band quantization noise from the delta sigma modulator extends from .417Fs to 128Fs (192Fs). This noise is attenuated by the switch ca-pacitor filter and the continuous time filters. The total quantization noise and thermal noise from the analog filters integrated over the .417Fs to 128Fs (192Fs) is more than 50 dB below full scale power.Figure 7. CLKOUT Generation CircuitFigure 8. DAC4.4Digital Audio TransmitterThe transmitter encodes digital audio data accord-ing to the Sony®/Philips® Digital Interface Format (S/PDIF) or the AES/EBU interface format. The encoded data is output on the TX pin. More infor-mation on the S/PDIF and AES/EBU standards are available from Crystal’s application note library.4.5Audio Serial Input PortThe audio serial input port has a three pin interface consisting of FSYNC, SCLK, and SDATA. FSYNC is only used to frame data when the audio data is in a PCM format. Systems, such as MPEG decoders, which use the audio serial input port for compressed audio data should tie FSYNC to +5V. SCLK used to clock SDATA (serial data input) into an internal FIFO. The active edge of SCLK is de-termined by the application code running on the CS4922. Consult the documentation for each ap-plication download to determine your system re-quirements.4.6Auxiliary Digital Audio PortThe CS4922 auxiliary port provides a path for the internal DSP core to directly read and write framed PCM digital audio data. The auxiliary port is de-signed to operate in a full duplex mode that can support simultaneous PCM input and output. It is important to note that the CS4922 always masters the audio clocks on the Auxiliary Digital Audio Port.The port has the capability to support two digital audio formats. The formats are illustrated in Fig-ures 9, 10, and 11. The input and output formats are always configured to operate in the same mode. The input and output sampling rates are the same as the sample rate for the on-chip DAC. The AUX port can support 18 bit samples at 64Fs (I2S For-mat) or 20 bit samples at 128Fs (Left Justified For-mat).The CS4922 Auxiliary digital audio port physically is implemented with four device pins: AUXCLK pin 11, AUXLR pin 10, AUXIN pin 9, and AUX-OUT pin 8. AUXCLK is utilized as the primary synchronous clock. AUXOUT is the serial audio data output pin and AUXIN is the serial audio data input pin. AUXLR is an output pin used for fram-ing the auxiliary digital audio port. AUXLR cycles at the same Fs as the on-chip stereo DAC. Fs is programmed by the DSP. AUXLR and AUXOUT transition with the falling edge of AUXCLK. The rising edge of AUXCLK samples AUXIN.4.7Serial Control PortThe serial control port (SCP) can operate in I2C or SPI compatible modes. In either mode, the control port performs eight bit transfers and is always con-figured as a slave. As a slave, it cannot drive the clock signal nor initiate data transfers. The port can request to be serviced by activating the REQ pin. The port is an asynchronous interface which pro-vides interrupts and handshaking signals to allowFigure 9. Auxiliary Data Input FormatsFigure 10. Auxiliary Data Output Formatscommunication between the on-chip DSP and an off-chip device such as a micro controller. Figure 13 shows a block diagram of the port.4.7.1I2C ModeThe status of CS sets the mode of the SCP during a hardware and software reset. If CS is high during a reset the mode is I2C. Note that in most systems where I2C is the preferred control mode, CS is con-nected to the digital supply.For normal I2C operation SCL/SCK, SDA, and REQ are used. CS and CDIN are typically connect-ed to the digital supply. SCL/SCK is the serial clock input which is always driven by an external device. SDA is the serial data Input/Output signal. REQ is the active low request signal, which is driv-en low when there is valid data in the serial control port output SCPOUT register.As an I2C compatible port, data is communicated on the SDA pin and is clocked by the rising edge of SCL/SCK. The Philips I2C bus specification pro-vides details of this interface. Note the CS4922 does not meet the rise time specification of the SCL/SCK signal. For more details please refer to the section on Rise Time of SCL/SCK.Figure 12 shows the relative timing necessary for an I2C write operation for a single byte. A ‘write’is defined as the transfer of data from an I2C bus master to the CS4922 serial control port. A transfer is initiated with a start condition followed by a 7 bit address and a read/write bit (set low for a write).This address is the address assigned to the device being written to during the transfer. In the case of the CS4922, this address is stored in the SCPCN register. Immediately following power up, the CS4922's Address checking Enable (AEN) bit is set to zero. The AEN bit must be set high for the CS4922 to compare the address of the intended I2C device on the bus to its internal address. This means the CS4922 will respond to any address on the I2C bus until its address is initialized and address checking is enabled. To avoid bus conflicts the CS4922 should be held in reset (RESET active low) until the master is ready to communicate with the CS4922 and sets the address in the SCPCN. The address can only be set using the I2C bus interface, so the master should use the intended I2C address when downloading microcode to the CS4922 to avoid conflict with other devices on the bus. Once the microcode is loaded into the CS4922 the micro-code should either initialize the I2C address or pro-vide a means for the master to program the I2C address. If the CS4922 is the only device on the I2C bus, address checking is optional. However, I2C bus protocol is still required. In other words, the ad-dress bits and read/write bit are still required.If a write to the CS4922 is specified, 8 bits of data on SDA will be shifted into the input shift register as shown in Figure 13. When the shift register is full, the 8 bit data is transferred to the Serial Control Port Input (SCPIN) register on the falling edge of the 8th data bit and an acknowledge (ACK) is sent back to the master..Figure 11. Multi-channel Auxiliary Data Formats。

35RAPC4BHN2中文资料

Previous Page | Return to Index | Next Page3.5 mm SINGLE MONO AND STEREO JACKS1. 35RAPC4BV42. 35RAPC2AV3. 35RAPC2BHN24. 35RAPC4BH35. 35RAPC2BV46. 35RAPC2BH3click here to download a schematic drawing(you will need to have Adobe Acrobat installed on your system to do this)click here to download a schematic drawing(you will need to have Adobe Acrobat installed on your system to do this)click here to download a schematic drawing(you will need to have Adobe Acrobat installed on your system to do this)click here to download a schematic drawing(you will need to have Adobe Acrobat installed on your system to do this)APPLICATIONS* Multi-media workstations* Headphones/microphone sets* Interactive TV* Audio* Telecommunications* Medical* Computer* InstrumentationSWITCHCRAFT 3.5 mm JACK PART NUMBERING SYSTEMSeries MountingTypeCircuitryHousingOrientationBushingFootprintDesignation35 3.5 mm RAPCRight-Angle2A SingleClosedH (Horizontal)Board SpaceRequiredGreater ThanAboveBoard Height(RAPC)BlankThreadedBushingBlank See Note1PM PanelMount2B DoubleOpenV (Vertical)Board SpaceRequiredGreater ThanAboveBoard Height(RAPC)NNon-threadedBushing2 See Note 13B SingleOpen +SingleClosedV (Vertical)SolderTerminals ExitHousingOpposite FromBushing (PM)3 See Note 14B DoubleClosedBlank OpenFrame Jack4 See Note 15 See Note 1Notes:1. Footprints are assigned sequentially within a family of jacks.For example, all 35RAPCXXV2 jacks can use the 35RAPC4BV2 footprint independent of whether the bushing is threaded.Not all holes would be used by jacks with 2A, 2B, and 3B circuitry.35RAPCXXV3 jacks require an entirely different PC board layout than 35RAPCXXV2 jacks.Each number designates a different footprint.ORDERING INFORMATIONPart Number Description Height vs.WidthBushing35RAPC2AV mono vertical threaded3 35RAPC2AHN2mono horizontal non-threaded 35RAPC2AHN3mono horizontal non-threaded35RAPC2BHN2stereo horizontal non-threaded 35RAPC2BHN3stereo horizontal non-threaded 35RAPC3BHN2stereo horizontal non-threaded 35RAPC3BHN3stereo horizontal non-threaded 35RAPC4BHN2stereo horizontal non-threaded 35RAPC4BHN3stereo horizontal non-threaded 35RAPC2AH3mono horizontal threaded3 35RAPC2BH3stereo horizontal threaded3 35RAPC3BH3stereo horizontal threaded3 35RAPC4BH3stereo horizontal threaded3 35RAPC2AV4mono vertical threaded3 35RAPC2BV4mono vertical threaded3 35RAPC3BV4stereo vertical threaded3 35RAPC4BV4stereo vertical threaded3 35RAPC2AVN4mono vertical non-threaded 35RAPC2BVN4stereo vertical non-threaded 35RAPC3BVN4stereo vertical non-threaded 35RAPC4BVN4stereo vertical non-threaded Part numbers which include the letter "N" designate non-threaded bushings. Part numbers without the letter "N" designate threaded bushing.1. Order by part number2. Contact Switchcraft for special ordering information3. Mounting hardware included.35RAPC2AV - MONO, VERTICAL, THREADEDMATERIALSCoil Spring: Steel wire.Bushing: Nickel-plated copper alloy.Terminal: Silver-plated copper alloy.Tip Spring: Silver-plated copper alloy.Shunt Terminal: Plated copper alloy.Cover: Thermoplastic, transparent UL 94V-2.Body: Thermoplastic, UL 94V-1 black color.PERFORMANCE SPECIFICATIONSContact Resistance: 20 milliohms maximum.Insulation Resistance: 100 milliohms minimum at 250V DC.Dielectric Withstanding Voltage: 250V AC.Life: 5000 cycles, minimum.Insertion Force: 0.88 pounds - 3.5 pounds.Withdrawal Force: 0.88 pounds - 2.64 pounds.35RAPC4BHN2 - STEREO, HORIZONTAL, NON-THREADED MATERIALSCover: Thermoplastic, UL 94V-1 black color.Shunt Terminals: Silver-plated copper alloy.Ring Spring: Copper alloy.Tip Spring: Special silver plating.Ground Terminal: Plated copper alloy.Metal: Nickel-plated copper alloy.Body: Thermoplastic, UL 94V-0 black color.PERFORMANCE SPECIFICATIONSContact Resistance: 30 milliohms maximum, initial 100 milliohms maximum., after life.Insulation Resistance: 100 megohms mininimum at 500V DC.Dielectric Withstanding Voltage: 500V AC.Life: 5000 cycles, minimum.Insertion Force: 0.88 pounds - 6.6 pounds.Withdrawal Force: 0.88 pounds - 6.6 pounds.35RAPC2BHN2 - STEREO, HORIZONTAL, NON-THREADED MATERIALSCover: Thermoplastic, UL 94V-1 black color.Ring Spring: Copper alloy.Tip Spring: Silver-plated copper alloy.Ground Terminal: Silver-plated copper alloy.Metal: Copper alloy, nickel plating.Body: Thermoplastic, UL 94V-0 black color.PERFORMANCE SPECIFICATIONSContact Resistance: 30 milliohms maximum, initial 100 milliohms maximum, after life.Insulation Resistance: 100 megohms minimum at 500V DC.Dielectric Withstanding Voltage: 500V AC.Life: 5000 cycles, minimum.Insertion Force: 0.88 pounds - 6.6 pounds.Withdrawal Force: 0.88 pounds - 6.6 pounds.35RAPC2BH3 - STEREO, HORIZONTAL, THREADED MATERIALSCoil Springs: Steel wire.Tip Spring: Silver-plated copper alloy.Switchcraft元器件交易网Ring Spring: Silver-plated copper alloy.Ground Terminal: Silver-plated copper alloy.Bushing: Nickel-plated copper alloy.Cover: Thermoplastic, transparent UL 94V-2.Body: Thermoplastic, UL 94V-1 black color.PERFORMANCE SPECIFICATIONSContact Resistance: 20 milliohms maximum, initial 100 milliohms maximum, after life.Insulation Resistance: 100 megohms minimum.Dielectric Withstanding Voltage: 250V AC.Life: 5000 cycles, minimum.Insertion Force: 0.88 lbs. - 3.50 lbs.Withdrawal Force: 0.88 lbs. - 3.10 lbs.35RAPC4BH3 - STEREO, HORIZONTAL, THREADED MATERIALSCoil Springs: Steel wire.Tip Spring: Silver-plated copper alloy.Ring Spring: Silver-plated copper alloy.Contactors: Silver-plated copper alloy.Ground Terminal: Silver-plated copper alloy.Bushing: Nickel-plated copper alloy.Cover: Thermoplastic, transparent UL 94V-2.Body: Thermoplastic, UL 94V-1 black color.PERFORMANCE SPECIFICATIONSContact Resistance: 20 milliohms maximum, initial 100 milliohms maximum, after life.Insulation Resistance: 100 megohms minimum.Dielectric Withstanding Voltage: 250V AC.Life: 5000 cycles, minimum.Insertion Force: 0.88 - 3.5 pounds.Withdrawal Force: 0.88 - 3.1 pounds.35RAPC2BV4 - STEREO, VERTICAL, THREADED MATERIALSCoil Springs: Steel Wire.Ring Spring: Copper alloy strip, tin alloy plating.Ground Terminal: Copper alloy strip, tin alloy plating.Bushing: Nickel-plated copper alloy.Cover: Thermoplastic, UL 94V-0 black color.Body: Thermoplastic, UL 94V-0 black color.PERFORMANCE SPECIFICATIONS Contact Resistance: 20 milliohms maximum,Switchcraft元器件交易网initial 50 milliohms maximum, after life.Insulation Resistance: 50 megohms minimum at 500V DC.Dielectric Withstanding Voltage: 250V AC.Life: 5,000 cycles, minimum.Insertion Force: 0.88 lbs. to 3.50 lbs.Withdrawal Force: 0.88 lbs. to 3.10 lbs.35RAPC4BV4 - STEREO, VERTICAL, THREADED MATERIALSCoil Springs: Steel wire.Shunt Terminals: Copper alloy strip,tin alloy plated.Ring Spring: Copper alloy strip,tin alloy plated.Ground Terminal: Copper alloy strip,tin alloy plated.Bushing: Plated copper alloy.Cover: Thermoplastic, UL 94V-0 black color.Body: Thermoplastic, UL 94V-0 black color.PERFORMANCE SPECIFICATIONSContact Resistance: 20 milliohms maximum, initial 50 milliohms maximum, after life.Insulation Resistance: 50 milliohms minimum at 500V DC.Dielectric Withstanding Voltage: 250V AC.Life: 5000 cycles, minimum.Insertion Force: 0.88 - 3.5 pounds.Withdrawal Force: 0.88 - 3.5 pounds.Previous Page | Return to Index | Next PageTo search a category please click on the corresponding icon:| Connectors | Jacks and Plugs || Patch Panels, Patch Kits & Jackfields | Cable Assemblies and Patch Cords | Switches |Switchcraft元器件交易网All products shown are covered by Switchcraft's limited lifetime warranty.| Switchcraft home |About Us | Products | What's New | Search | Contact UsSwitchcraft元器件交易网。

CS44210资料

The CS44210 architecture uses a direct-to-digital approach that maintains digital signal integrity to the final output filter. This minimizes analog interference effects that can negatively affect system performance.

CS42324中文资料

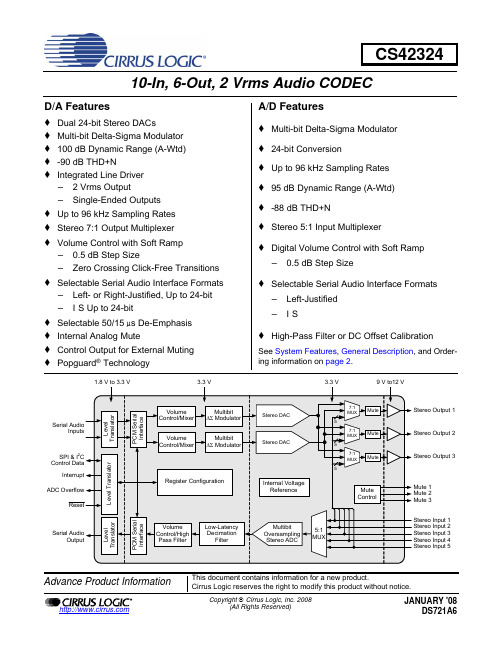

10-In, 6-Out, 2Vrms Audio CODECD/A FeaturesDual 24-bit Stereo DACs Multi-bit Delta-Sigma Modulator 100dB Dynamic Range (A-Wtd) -90dB THD+N Integrated Line Driver– 2 Vrms Output–Single-Ended OutputsUp to 96kHz Sampling Rates Stereo 7:1 Output Multiplexer Volume Control with Soft Ramp–0.5dB Step Size–Zero Crossing Click-Free Transitions Selectable Serial Audio Interface Formats –Left- or Right-Justified, Up to 24-bit –I²S Up to 24-bitSelectable 50/15 μs De-Emphasis Internal Analog MuteControl Output for External Muting Popguard ® TechnologyA/D FeaturesMulti-bit Delta-Sigma Modulator 24-bit ConversionUp to 96kHz Sampling Rates 95dB Dynamic Range (A-Wtd) -88dB THD+NStereo 5:1 Input MultiplexerDigital Volume Control with Soft Ramp–0.5dB Step SizeSelectable Serial Audio Interface Formats–Left-Justified –I²SHigh-Pass Filter or DC Offset Calibration See System Features , General Description , and Order-ing information on page 2.CS42324System FeaturesDirect Interface with 1.8 V to 3.3 V Logic LevelsSupports Asynchronous Serial Port Operation –Two Independent Clock Domains–ADC, DAC1, and DAC2 can beIndependently Assigned to the Two ClockDomains–Each Serial Port Supports Master or Slave OperationInternal Digital Loopback+3.3V Analog Power Supply+3.3V Digital Power Supply+9 V to +12 V High-Voltage Power SupplyHardware or Software Mode Configuration –Supports I²C® and SPI™ Software Interface General DescriptionThe CS42324 is a highly integrated stereo audio CODEC. The CS42324 performs stereo analog-to-digital (A/D) and up to four channels of digital-to-analog (D/A) conversion of up to 24-bit serial values at sample rates up to 96kHz.A 5:1 stereo input multiplexer is included for selecting between line-level inputs. The output of the input multi-plexer is followed by an advanced 3rd-order, multi-bit delta-sigma modulator and digital filtering/decimation. Sampled data is transmitted by the serial audio inter-face at rates from 4kHz to 96kHz, in either Slave or Master Mode.The D/A converter is based on a 5th-order multi-bit del-ta-sigma modulator with an ultra-linear low-pass filter and offers a volume control that operates with a 0.5dB step size. It incorporates selectable soft ramp and zero crossing transition functions to eliminate clicks and pops.An integrated 7:1 stereo output multiplexer on each of the three stereo 2 Vrms line-level outputs is used to se-lect any of the 5 stereo analog inputs, for analog bypass support, or the outputs of the 2 internal DACs. Each 2Vrms output can be muted with the selectable analog mute function.Standard 50/15μs de-emphasis is available for a 44.1kHz sample rate for compatibility with digital audio programs mastered using the 50/15μs pre-emphasis technique.Integrated digital level translators allow easy interfacing between the CS42324 and other devices operating over a wide range of logic levels.The CS42324 is available in a 48-pin LQFP package in Commercial (-40°C to +85°C) and Automotive (-40°C to +105°C) grades. The CDB42324 Customer Demonstra-tion board is also available for device evaluation and implementation suggestions. Please refer to “Ordering information” on page71 for complete details.TABLE OF CONTENTS1. PIN DESCRIPTIONS (8)1.1 Software Mode (8)1.2 Hardware Mode (10)1.3 Digital I/O Pin Characteristics (12)2. CHARACTERISTICS AND SPECIFICATIONS (13)RECOMMENDED OPERATING CONDITIONS (13)ABSOLUTE MAXIMUM RATINGS (13)DAC ANALOG CHARACTERISTICS - COMMERCIAL (-CQZ) (14)DAC ANALOG CHARACTERISTICS - AUTOMOTIVE (-DQZ) (15)DAC COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (16)ADC ANALOG CHARACTERISTICS - COMMERCIAL (-CQZ) (17)ADC ANALOG CHARACTERISTICS - AUTOMOTIVE (-DQZ) (18)ADC DIGITAL FILTER CHARACTERISTICS (19)ANALOG PASS-THRU CHARACTERISTICS (20)DC ELECTRICAL CHARACTERISTICS (21)DIGITAL INTERFACE CHARACTERISTICS (21)SWITCHING CHARACTERISTICS - SERIAL AUDIO (22)SWITCHING CHARACTERISTICS - SERIAL AUDIO (CONT.) (23)SWITCHING CHARACTERISTICS - SOFTWARE MODE - I²C FORMAT (24)SWITCHING CHARACTERISTICS - SOFTWARE MODE - SPI FORMAT (25)3. TYPICAL CONNECTION DIAGRAMS (26)4. APPLICATIONS (28)4.1 System Clocking (28)4.1.1 Master Clock (28)4.1.2 Synchronous / Asynchronous Mode (29)4.2 Serial Port Operation (29)4.2.1 Master Mode (30)4.2.2 Slave Mode (30)4.2.3 ADC, DAC1, and DAC2 clock selection (31)4.2.4 High-Impedance Digital Output (31)4.2.5 Digital Interface Formats (32)4.2.6 Synchronization of Multiple Devices (32)4.3 Analog-to-Digital Data Path (33)4.3.1 ADC Analog Input Multiplexer (33)4.3.2 ADC Description (33)4.3.3 High-Pass Filter and DC Offset Calibration (34)4.3.4 Digital Attenuation Control (34)4.4 Digital-to-Analog Data Path (34)4.4.1 Digital Volume Control (34)4.4.2 Mono Channel Mixer (34)4.4.3 De-Emphasis Filter (35)4.4.4 Internal Digital Loopback (35)4.4.5 DAC Description (35)4.4.6 Analog Output Multiplexer (36)4.4.7 Output Transient Control (36)4.4.8 Mute Control (37)4.5 Initialization (37)4.5.1 Determining Hardware or Software Mode (37)4.5.2 Hardware Mode Start-Up (37)4.5.3 Software Mode Start-Up (38)4.5.4 Initialization Flow Chart (39)4.6 Device Control (40)4.6.2 Software Mode - I²C Control Port (41)4.6.3 Software Mode - SPI Control Port (42)4.6.4 Memory Address Pointer (MAP) (43)4.7 Interrupts and Overflow (43)5. REGISTER QUICK REFERENCE (44)6. REGISTER DESCRIPTION (46)6.1 Device I.D. and Revision Register (Address 00h) (Read Only) (46)6.1.1 Device I.D. (Read Only) (46)6.1.2 Chip Revision (Read Only) (46)6.2 Mute Control (Address 01h) (46)6.2.1 System MCLK Source (46)6.2.2 Mute DAC2 Left-Channel (46)6.2.3 Mute DAC2 Right-Channel (47)6.2.4 Mute DAC1 Left-Channel (47)6.2.5 Mute DAC1 Right-Channel (47)6.2.6 Mute ADC Left-Channel (47)6.2.7 Mute ADC Right-Channel (47)6.3 Operational Control (Address 02h) (47)6.3.1 Global Power-Down (47)6.3.2 INT Pin High/Low Active (INT_H/L) (48)6.3.3 Freeze (48)6.3.4 Tri-State SDOUT (48)6.3.5 Tri-State Serial Port 1 (48)6.3.6 Tri-State Serial Port 2 (49)6.4 Serial Port 1 Control (Address 03h) (49)6.4.1 Serial Port 1 Master/Slave Select (49)6.4.2 Serial Port 1 Speed Mode (49)6.4.3 MCLK1 Divider (49)6.4.4 Serial Port 1 MCLK source (49)6.5 Serial Port 2 Control (Address 04h) (50)6.5.1 Serial Port 2 Master/Slave Select (50)6.5.2 Serial Port 2 Speed Mode (50)6.5.3 MCLK2 Divider (50)6.5.4 Serial Port 2 MCLK Source (50)6.6 ADC Clocking (Address 06h) (50)6.6.1 ADC MCLK Source (50)6.6.2 ADC Serial Port Source (51)6.6.3 ADC Digital Interface Format (ADC_DIF) (51)6.7 DAC1 Clocking (Address 07h) (51)6.7.1 DAC1 MCLK Source (51)6.7.2 DAC1 Serial Port Source (51)6.7.3 DAC1 Digital Interface Format (DAC1_DIF) (51)6.8 DAC2 Clocking (Address 08h) (52)6.8.1 DAC2 MCLK Source (52)6.8.2 DAC2 Serial Port Source (52)6.8.3 DAC2 Digital Interface Format (DAC2_DIF) (52)6.9 ADC Control (Address 0Ah) (52)6.9.1 ADC High-Pass Filter Freeze (52)6.9.2 ADC Soft Ramp Control (52)6.9.3 Analog Input Selection (53)6.10 DAC1 Control (Address 0Bh) (53)6.10.1 DAC1 De-Emphasis Control (53)6.10.2 DAC1 Single Volume Control (53)6.10.4 DAC1 Zero Cross Control (54)6.10.5 DAC1 Loop-Back (54)6.10.6 DAC1 Invert Signal Polarity (54)6.10.7 DAC1 Channel Mixer (54)6.11 DAC2 Control (Address 0Ch) (55)6.11.1 DAC2 De-Emphasis Control (55)6.11.2 DAC2 Single Volume Control (55)6.11.3 DAC2 Soft Ramp Control (55)6.11.4 DAC2 Zero Cross Control (55)6.11.5 DAC2 Loop-Back (56)6.11.6 DAC2 Invert Signal Polarity (56)6.11.7 DAC2 Channel Mixer (56)6.12 AOUT1 Control (Address 0Dh) (56)6.12.1 External Mute Control Pin (56)6.12.2 AOUT1 Select (56)6.13 AOUT2 Control (Address 0Eh) (57)6.13.1 External Mute Control Pin (57)6.13.2 AOUT2 Select (57)6.14 AOUT3 Control (Address 0Fh) (57)6.14.1 External Mute Control Pin (57)6.14.2 AOUT3 Select (58)6.15 ADCx Volume Control: ADCA (Address 10h) & ADCB (Address 11h) (58)6.16 DAC1x Volume Control: DAC1A (Address 12h) & DAC1B (Address 13h) (58)6.17 DAC2x Volume Control: DAC1A (Address 14h) & DAC1B (Address 15h) (59)6.18 Interrupt Mode (Address 16h) (59)6.19 Interrupt Mask (Address 17h) (59)6.19.1 DAC2 Auto Mute Left Mask (DAC2_AMUTELM) (60)6.19.2 DAC2 Auto Mute Right Mask (DAC2_AMUTERM) (60)6.19.3 DAC1 Auto Mute Left Mask (DAC1_AMUTELM) (60)6.19.4 DAC1 Auto Mute Right Mask (DAC1_AMUTELM) (60)6.19.5 Serial Port 2 Clock Error Mask (SP2_CLKERRM) (60)6.19.6 Serial Port 1 Clock Error Mask (SP1_CLKERRM) (60)6.19.7 ADC Positive Overflow Mask (ADC_OVFLPM) (61)6.19.8 ADC Negative Overflow Mask (ADC_OVFLNM) (61)6.20 Interrupt Status (Address 18h) (Read Only) (61)6.20.1 DAC2 Auto Mute Left Interrupt Status (DAC2_AMUTEL) (61)6.20.2 DAC2 Auto Mute Right Interrupt Status (DAC2_AMUTER) (61)6.20.3 DAC1 Auto Mute Left Interrupt Status (DAC1_AMUTEL) (62)6.20.4 DAC1 Auto Mute Right Interrupt Status (DAC1_AMUTEL) (62)6.20.5 Serial Port 2 Clock Error Interrupt Status (SP2_CLKERR) (62)6.20.6 Serial Port 1 Clock Error Interrupt Status (SP1_CLKERR) (62)6.20.7 ADC Positive Overflow Interrupt Bit (ADC_OVFLP) (62)6.20.8 ADC Negative Overflow Interrupt Bit (ADC_OVFLN) (63)7. GROUNDING AND POWER SUPPLY DECOUPLING (64)8. ADC FILTER PLOTS (65)9. DAC DIGITAL FILTER RESPONSE PLOTS (67)10. PARAMETER DEFINITIONS (69)11. PACKAGE DIMENSIONS (70)THERMAL CHARACTERISTICS AND SPECIFICATIONS (70)12. ORDERING INFORMATION (71)13. REVISION HISTORY (71)LIST OF FIGURESFigure 1.Equivalent Analog Output Load (16)Figure 2.Maximum Analog Output Loading (16)Figure 3.Serial Input Timing (22)Figure 4.Serial Output Timing (23)Figure 5.Software Mode Timing - I²C Format (24)Figure 6.Software Mode Timing - SPI Mode (25)Figure 7.Typical Connection Diagram - Software Mode (26)Figure 8.Typical Connection Diagram - Hardware Mode (27)Figure 9.Serial Port Topology (29)Figure 10.Master Mode Clock Generation (30)Figure 11.Converter Clocking (31)Figure 12.Tri-State Serial Port (31)Figure 13.Left-Justified up to 24-Bit Data (32)Figure 14.I²S up to 24-Bit Data (32)Figure 15.Right-Justified 16-Bit Data, Right-Justified 24-Bit Data (32)Figure 16.Analog Input Architecture (33)Figure 17.De-Emphasis Curve (35)Figure 18.Analog Output Architecture (36)Figure 19.Initialization Flow Chart (39)Figure 20.Software Mode Timing, I²C Write (41)Figure 21.Software Mode Timing, I²C Read (41)Figure 22.Software Mode Timing, SPI Mode (43)Figure 23.Single-Speed Mode Stopband Rejection (65)Figure 24.Single-Speed Mode Transition Band (65)Figure 25.Single-Speed Mode Transition Band (Detail) (65)Figure 26.Single-Speed Mode Passband Ripple (65)Figure 27.Double-Speed Mode Stopband Rejection (65)Figure 28.Double-Speed Mode Transition Band (65)Figure 29.Double-Speed Mode Transition Band (Detail) (66)Figure 30.Double-Speed Mode Passband Ripple (66)Figure 31.Single-Speed Stopband Rejection (67)Figure 32.Single-Speed Transition Band (67)Figure 33.Single-Speed Transition Band (detail) (67)Figure 34.Single-Speed Passband Ripple (67)Figure 35.Double-Speed Stopband Rejection (67)Figure 36.Double-Speed Transition Band (67)Figure 37.Double-Speed Transition Band (detail) (68)Figure 38.Double-Speed Passband Ripple (68)Figure 39.Quad-Speed Stopband Rejection (68)Figure 40.Quad-Speed Transition Band (68)Figure 41.Quad-Speed Transition Band (detail) (68)Figure 42.Quad-Speed Passband Ripple (68)LIST OF TABLESTable 1. I/O Power Rails (12)Table 2. Speed Modes (28)Table 3. Single-Speed Mode Common Clock Frequencies (28)Table 4. Double-Speed Mode Common Clock Frequencies (28)Table 5. M1 and M0 Mode Pins in Hardware Mode (29)Table 6. Slave Mode SCLK/LRCK Ratios (30)Table 7. MCLKx to LRCKx Ratios (30)Table 8. Hardware Mode Interface Format Control (32)Table 9. Hardware Mode Feature Summary (40)Table 10. Freeze-able Bits (48)1.PIN DESCRIPTIONS1.1Software ModePin Name #Pin DescriptionSDA/CDOUT1I²C Format SDA (Input/Output ) - Acts as an input/output data pin. An external pull-up resistor is required for I²C control port operation.SPI Format CDOUT (Output ) - Acts as an output only data pin.SCL/CCLK 2I²C Format, SCL (Input ) – Serial clock for the serial control port. An external pull-up resistor is required for I²C control port operation.SPI Format, CCLK (Input ) – Serial clock for the serial control port.AD0/CS 3I²C Format, AD0 (Input ) - Forms the device address input AD[0].SPI Format, CS (Input ) - Acts as the active low chip select input.AD1/CDIN 4I²C Format, AD1 (Input ) - Forms the device address input AD[1].SPI Format, CDIN (Input ) - Becomes the input data pin.INT 5Interrupt (Output ) - Indicates an interrupt condition has occurred.FILT+6FILT+ (Output ) - Full-scale reference voltage for ADC.VCMADC 7ADC Common-Mode Voltage (Output ) - Filter connections for the ADC internal quiescent refer-ence voltage.GND 8Analog Ground (Input ) - Analog ground reference.VA 9Analog Power (Input) - Positive power for the internal analog section.VBIAS 10Bias Voltage (Output ) - Positive reference voltage for the internal DAC.MUTEC111Mute Control 1 (Output ) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.SCL/CCLK G N D HS C L K 1AD0/CS AD1/CDININT SDA/CDOUT FILT+VCMADCGND VA VBIAS MUTEC1MUTEC2V A _HA O U T 1BA O U T 2AA O U T 2BA O U T 3AA O U T 3BM U T E C 3V C M B U FV C M D A CV A _HA O U T 1AS D I N 2M C L K 1L R C K 1V DG N DV LS D O U TC L K 2L R C K 2M C L K 2D I N 1MUTEC212Mute Control 2 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.MUTEC313Mute Control 3 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.VCMBUF14VCMBUF (Output) -Internally buffered VCMDACVCMDAC15DAC Common-Mode Voltage (Output)-Filter connections for the DAC internal quiescent refer-ence voltage.VA_H 1618Analog High Voltage Power (Input)-Positive power for the internal output buffer section.GNDH17Analog Ground (Input) - Ground reference for high-voltage section.AOUT1A, AOUT1B AOUT2A, AOUT2B AOUT3A, AOUT3B 19, 2021, 2223, 24DAC Analog Audio Outputs (Output) - The full-scale output level is specified in the DAC Analog Characteristics specification table.AIN5B, AIN5A AIN4B, AIN4A AIN3B, AIN3A AIN2B, AIN2A AIN1B, AIN1A 25, 2627, 2829, 3031, 3233, 34Stereo Analog Inputs 1-5 (Input)-The full-scale input level is specified in the ADC Analog Char-acteristics specification table.RST35Reset (Input) - The device enters a low-power mode when this pin is driven low. OVFL36ADC Overflow (Output) -Indicates an ADC overflow condition is present.SDIN2 SDIN13738Serial Audio Data Input (Input) - Input for two’s complement serial audio data.MCLK239Master Clock 2 (Input) - Optional asynchronous clock source for the DAC’s delta-sigma modula-tors.LRCK240Serial Port 2 Left/Right Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio input data line.SCLK241Serial Port 2 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 2. VD42Digital Power (Input) -Positive power for the internal digital section.GND43Digital Ground (Input) - Ground reference for the internal digital section.VL44Digital Interface Power (Input) -Determines the required signal level for the control and serial port interfaces as shown in “I/O Power Rails” on page12. Refer to the“Recommended Operating Conditions” on page13 for appropriate voltages.SDOUT45Serial Audio Data Output (Output) -Output for two’s complement serial audio data. SCLK146Serial Port 1 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 1.LRCK147Serial Port 1 Left/Right Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio output data line.MCLK148Master Clock 1 (Input) - Clock source for the ADC’s delta-sigma modulators. By default, this sig-nal also clocks the DAC’s delta-sigma modulators.1.2Hardware ModePin Name#Pin DescriptionM0, M11, 2Mode Selection (Input) - Determines the operational mode of the device.MDIV3MCLK Divider (Input) - Setting this pin high places a divide-by-2 circuit in the MCLK path to the core device circuitry.MUTE4MUTE (Input) -Engages the internal digital mute and activates the MUTECx pinsDIF5DIF (Input) -Sets the serial audio interface format. Setting DIF high selects I²S audio format and low selects LJ audio format.FILT+6FILT+ (Output) -Full-scale reference voltage for ADC.VCMADC7ADC Common-Mode Voltage (Output)-Filter connections for the ADC internal quiescent refer-ence voltage.GND8Analog Ground (Input)-Analog ground reference.VA9Analog Power (Input)-Positive power for the internal analog section. VBIAS10Bias Voltage (Output)-Positive reference voltage for the internal DAC.MUTEC111Mute Control 1 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.MUTEC212Mute Control 2 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.OVFLRSTAIN1AAIN1BAIN2AAIN2BAIN3AAIN3BAIN4AAIN4BAIN5AAIN5BM1MDIVMUTEDIFM0FILT+VCMADCGNDVAVBIAS MUTEC1 MUTEC2SCLK1SDIN2 MCLK1LRCK1VDGNDVLSDOUTSCLK2LRCK2MCLK2SDIN1GNDHVA_HAOUT1BAOUT2AAOUT2BAOUT3AAOUT3B MUTEC3VCMBUFVCMDACVA_HAOUT1AMUTEC313Mute Control 3 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.VCMBUF14VCMBUF (Output) -Internally buffered VCMDACVCMDAC15DAC Common-Mode Voltage (Output)- Filter connections for the DAC internal quiescent refer-ence voltage.VA_H16, 18Analog High Voltage Power (Input)-Positive power for the internal output buffer section. GNDH17Analog Ground (Input) - Ground reference for high-voltage section.AOUT1A, AOUT1B AOUT2A, AOUT2B AOUT3A, AOUT3B 19, 2021, 2223, 24DAC Analog Audio Outputs (Output) - The full-scale output level is specified in the DAC Analog Characteristics specification table.AIN5B, AIN5A AIN4B, AIN4A AIN3B, AIN3A AIN2B, AIN2A AIN1B, AIN1A 25, 2627, 2829, 3031, 3233, 34Stereo Analog Inputs 1-5 (Input)-The full-scale input level is specified in the ADC Analog Char-acteristics specification table.RST35Reset (Input) - The device enters a low-power mode when this pin is driven low. OVFL36ADC Overflow (Output) -Indicates an ADC overflow condition is present.SDIN2 SDIN13738Serial Audio Data Input (Input) - Input for two’s complement serial audio data.MCLK239Master Clock 2 (Input) - Optional asynchronous clock source for the DAC’s delta-sigma modula-tors.LRCK240Serial Port 2 Left/Right Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio input data line.SCLK241Serial Port 2 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 2. VD42Digital Power (Input) -Positive power for the internal digital section.GND43Digital Ground (Input) - Ground reference for the internal digital section.VL44Digital Interface Power (Input) -Determines the required signal level for the control and serial port interfaces as shown in “I/O Power Rails” on page12. Refer to the“Recommended Operating Conditions” on page13 for appropriate voltagesSDOUT45Serial Audio Data Output (Output) -Output for two’s complement serial audio data. SCLK146Serial Port 1 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 1.LRCK147Serial Port 1 Left Right/Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio output data line.MCLK148Master Clock 1 (Input) - Clock source for the ADC’s delta-sigma modulators. By default, this sig-nal also clocks the DAC’s delta-sigma modulators.1.3Digital I/O Pin CharacteristicsThe logic level for each input should adhere to the corresponding power rail and should not exceed the max-imum ratings.Power SupplyPinNumberPin Name I/O Driver ReceiverSoftware ModeVL 1SDACDOUTInput/OutputHi-Z/Output1.8 V - 3.3 V, Open Drain1.8 V - 3.3 V, CMOS1.8 V - 3.3 V, with Hysteresis 2SCLCCLKInput- 1.8 V - 3.3 V, with Hysteresis 3AD0CSInput- 1.8 V - 3.3 V, with Hysteresis 4AD1CDINInput- 1.8 V - 3.3 V, with Hysteresis 5INT Output 1.8 V - 3.3 V, Open Drain 1.8 V - 3.3 V, with HysteresisHardware ModeVL 1M0Input- 1.8 V - 3.3 V, with Hysteresis 2M1Input- 1.8 V - 3.3 V, with Hysteresis 3MDIV Input- 1.8 V - 3.3 V, with Hysteresis 4MUTE Input- 1.8 V - 3.3 V, with Hysteresis 5DIF Input- 1.8 V - 3.3 V, with HysteresisAll ModesVL 35RST Input- 1.8 V - 3.3 V 4740LRCK1LRCK2Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V 4641SCLK1SCLK2Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V 4839MCLK1MCLK2Input- 1.8 V - 3.3 V 3837SDIN1SDIN2Input- 1.8 V - 3.3 V 45SDOUT Output 1.8 V - 3.3 V, CMOS-36OVFL Output 1.8 V - 3.3 V, Open Drain-VA_H 111213MUTEC1MUTEC2MUTEC3Output9.0 V - 12.0 V-Table 1. I/O Power Rails2.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONSGND =GNDH =0V; All voltages with respect to ground.ABSOLUTE MAXIMUM RATINGSGND =GNDH =0 V; All voltages with respect to ground. (Note 1)Notes:1.Operation beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.2.Any pin except supplies. Transient currents of up to ±100mA on the analog input pins will not causeSCR latch-up.ParametersSymbol Min Nom Max Units DC Power Supplies:Analog Digital LogicHigh Voltage AnalogVA VD VL VA_H 3.133.131.718.55 3.33.33.39.0 3.473.473.4712.60V V V V Ambient Operating Temperature (Power Applied)Commercial(-CQZ)Automotive(-DQZ)T A-40-40--+85+105°C °CParameterSymbol Min Max Units DC Power Supplies:Analog Digital LogicHigh Voltage AnalogVA VD VL VA_H -0.3-0.3-0.3-0.3+4.50+4.50+4.50+17.0V V V V Input Current (Note 2)I in -10+10mA Analog Input Voltage V INA GND - 0.3VA_H + 0.3V Digital Input VoltageLogicV IND -0.3VL + 0.4V Ambient Operating Temperature (Power Applied)T A -55+125°C Storage TemperatureT stg-65+150°CTest Conditions (unless otherwise specified): VA = VD = VL = 3.3V, VA_H = 9V, GND =GNDH =0V; T A = 25°C; 997Hz Full-Scale Output Sine Wave. Decoupling capacitors, Filter capacitors, and Recommended output filter as shown in Figure 7 on page 26 and Figure 8 on page 27; Fs =48 kHz or 96kHz; Synchronous Mode; Measurement Bandwidth 10 Hz to 20kHz,Notes:3.One-half LSB of triangular PDF dither added to data.4.See Figures 1 and 2 on page 16. R L and C L reflect the minimum resistance and maximum capacitanceallowed in order to maintain stability in the internal op-amp. C L affects the dominant pole of the internal output amp; increasing C L beyond 100pF can cause the internal op-amp to become unstable.ParameterSymbolMin Typ Max Unit Dynamic Range(Note 3)18 to 24-Bit A-weighted unweighted 16-BitA-weighted unweighted94918885100979390----dB dB dB dB Total Harmonic Distortion + Noise(Note 3)18 to 24-Bit0 dB -20 dB-60 dB 16-Bit0 dB -20 dB -60 dB THD+N -------90-77-37-87-77-37-84-73-33-82-62-22dB dB dB dB dB dB Interchannel Isolation (1kHz)--100-dB DC AccuracyInterchannel Gain Mismatch -0.10.25dB Gain Drift -100-ppm/°C Analog OutputFull-Scale Output Voltage1.92.0 2.1V rms Max current draw from an AOUT pin I OUT-575-μA AC-Load Resistance (Note 4)R L 5--k ΩLoad Capacitance (Note 4)C L --100pF Output ImpedanceZ OUT-50-ΩTest Conditions (unless otherwise specified): VA =3.13V to 3.47V, VD =3.13V to 3.47V, VL =1.71V to 3.47V, VA_H = 8.55V to 12.60V, GND=GNDH=0V; T A = -40° C to +85° C; 997Hz Full-Scale Output Sine Wave. Decoupling capacitors, filter capacitors, and recommended output filter as shown in Figure 7 on page 26 and Fig-ure 8 on page 27; Fs=48 kHz or 96kHz; Synchronous Mode; Measurement Bandwidth 10 Hz to 20kHz,Parameter Symbol Min Typ Max Unit Dynamic Range(Note 3)18 to 24-Bit A-weightedunweighted 16-Bit A-weightedunweighted 90878380100979390----dBdBdBdBTotal Harmonic Distortion + Noise(Note 3)18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB THD+N-------90-77-37-87-77-37-80-67-27-77-67-27dBdBdBdBdBdBInterchannel Isolation(1kHz)--100-dB DC AccuracyInterchannel Gain Mismatch-0.10.25dB Gain Drift-100-ppm/°C Analog OutputFull-Scale Output Voltage 1.9 2.0 2.1V rms Max current draw from an AOUT pin I OUT-575-μA AC-Load Resistance(Note 4)R L5--kΩLoad Capacitance(Note 4)C L--100pF Output Impedance Z OUT-50-ΩDAC COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSENotes:5.Response is clock-dependent and will scale with Fs. Note that the amplitude vs. frequency plots of thisdata (Figures 31 to 42) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.6.For Single-Speed Mode, the measurement bandwidth is from StopBand to 3 Fs.For Double-Speed Mode, the measurement bandwidth is from StopBand to 3 Fs.7.De-emphasis is available only in Single-Speed Mode.Parameter (Note 5)SymbolMinTypMaxUnitSingle-Speed Mode Passband (Note 6)to -0.01dB corner to -3dB corner00--.454.499Fs FsFrequency Response (10Hz to 20kHz)-0.01-+0.01dB StopBand0.547--Fs StopBand Attenuation (Note 6)102--dB Group Delaytgd-9.4/Fs -s De-emphasis Error (Note 7) Fs = 44.1 kHz--+/-0.14dBDouble-Speed Mode Passband (Note 6)to -0.01dB corner to -3dB corner00--.43.499Fs Fs Frequency Response (10Hz to 20kHz)-0.01-+0.01dB StopBand.583--Fs StopBand Attenuation (Note 6)80--dB Group Delaytgd- 4.6/Fs-sFigure 1. Equivalent Analog Output Load Figure 2. Maximum Analog Output Loading。

CS42435_07中文资料