Laboratory_03_for_AC-DC_Converter[1]

MPLAB Code Configurator X2C Scope 库版本 2.0.0 发布说明书

Release Notes for MPLAB® Code ConfiguratorX2Cscope Library v2.0.01What is MPLAB Code Configurator X2C Scope LibraryX2CScope is a lightweight firmware-based debugging tool, and it is running on the target MCU parallelto the application. It is a runtime online debugging tool that works in RUN and DEBUGGING mode. X2CScopeis for generic use in any application and perfectly fits motor control applications.For more information, please visit https://x2cscope.github.io/2System Requirements1.MPLAB X 6.00 (or higher)2.XC16 1.50 (or higher)3.XC32 2.10 (or higher)4.MCC5.1.0 (or higher)5.MCC X2C Library v2.0.03Installing MPLAB® Code Configurator X2Cscope LibraryBasic steps for installing MPLAB® Code Configurator needs to be installed as below.To install the MPLAB® Code Configurator v5.1.0 or later Plugin1.In the MPLAB® X IDE, select Plugins from the Tools menu2.Select the Available Plugins tab3.Check the box for the MPLAB® Code Configurator v4, and click on InstallTo install and load different library version when connected to internet1.Open MPLAB® Code Configurator2.In the Versions tab under PIC24\dsPIC33\PIC32MM MCUs or X2Cscope will find the multiplelibrary version (loaded version is indicated by the green dot)3.Right Click on the required version of the library as specified in System Requirements and select Markfor load4.Click on Load Selected Libraries button to load the libraryTo install the X2Cscope Library when not connected to internet1.In the MPLAB® X IDE, select Options from the Tools menu2.Select Plugins tab3.Click on Install Library4.Add the required version(s) of the library as specified in the System Requirements.4What’s New•Migrated X2C Scope library to MCC version 5.1.0•X2C Scope library support in MCC melody.5Supported DevicesThe X2Cscope library supports the following device families.1.dsPIC33EP512GP506 (/dsPIC33EP512GP506)2.dsPIC33EV256GM106(/dsPIC33EV256GM106)3.dsPIC33EV256GM006(/dsPIC33EV256GM006)4.dsPIC33EP128GS806 (/dsPIC33EP128GS806)5.dsPIC33EP64GS506 (/dsPIC33EP64GS506)6.dsPIC33EP512GM710(/dsPIC33EP512GM710)7.dsPIC33CH128MP508 anddsPIC33CH128MP508S1(/dsPIC33CH128MP508)8.dsPIC33CK256MP508 (/dsPIC33CK256MP508)9.dsPIC33CH512MP508 anddsPIC33CH512MP508S1(https:///dsPIC33CH512MP508)10.dsPIC33CK64MP105(https:///dsPIC33CK64MP105)6 Device Support List☑ : The X2Cscope is supported for the device.7 Customer Support7.1 Microchip Web SiteMicrochip provides online support via our web site at . This web site is used to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:•Product Support – Data sheets and errata, application notes and sample programs, design resources, user’s guides and hardware support documents, latest software releases and archived software •General Technical Support – Frequently Asked Questions (FAQs), technical support requests, online discussion groups/forums (), Microchip consultant program member listing •Business of Microchip – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors, and factory representatives8.2Additional SupportUsers of Microchip products can receive assistance through several channels:•Distributor or Representative•Local Sales Office•Field Application Engineering (FAE)•Technical SupportCustomers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is available on our web site.Technical support is available through the web site at: 。

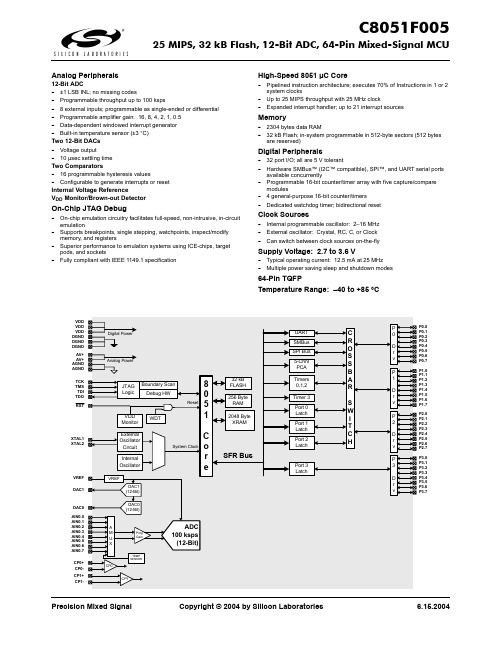

Silicon Laboratories C8051F380 1 2 3 4 5 6 7 C USB

-10 位 ADC(仅 C8051F380/1/2/3/C)•高达 500ksps•内建模拟多路复用器,单端和差分模式•VREF 来自外部引脚、内部参考或 V DD•内建温度传感器•外部转换启动输入选项-两个比较器-内部参考电压(仅 C8051F380/1/2/3/C)-掉电检测器和上电复位电路USB 功能控制器-符合 USB 规格 2.0-全速 (12Mbps) 或低速 (1.5Mbps) 运行-集成时钟恢复;全速或低速无需外部晶体-支持八个灵活的终端-1kB USB 缓冲存储器-集成收发器;无需外部电阻片上调试-片上调试电路提供全速、非侵入式的系统内调试(无需仿真器)-提供断点、单步执行、检查/修改内存和寄存器-比使用 ICE 芯片、目标仿真头和仿真插座的仿真系统有更优越的性能电源电压输入: 2.7 至 5.25V-使用片内稳压器时,支持的电压范围为 2.7~5.25V -流水线指令体系结构;70% 指令的执行时间为 1 个或2个系统时钟-高达 48 MIPS 的操作-扩展的中断处理程序内存-4352 或 2304字节 RAM-64、32 或 16kB 闪存;可在系统内编程的 512 字节扇区数字外围设备-40/25 个端口 I/O;全部能承受 5V 高灌电流-硬件增强型SPI™、两个 I2C/SMBus™ 和两个增强型UART 串口-六个通用 16 位计数器/定时器-16 位可编程计数器阵列 (PCA),有五个采集/比较模块-外部存储器接口 (EMIF)时钟源-内部振荡器:启用时钟恢复时精度为 ±0.25%。

支持所有USB 和 UART 模式-外部振荡器:晶体、RC、C 或时钟(1 或 2 引脚模式)-低频 (80kHz) 内部振荡器-在运行中可切换时钟源封装-48 引脚 TQFP (C8051F380/2/4/6)-32 引脚 LQFP (C8051F381/3/5/7/C)-5x5mm 32 引脚 QFN (C8051F381/3/5/7/C)温度范围: –40 至 +85°CC8051F380/1/2/3/4/5/6/7/CC8051F380/1/2/3/4/5/6/7/CTable of Contents1. System Overview (16)2. C8051F34x Compatibility (20)2.1. Hardware Incompatibilities (21)3. Pinout and Package Definitions (22)4. Typical Connection Diagrams (34)4.1. Power (34)4.2. USB (36)4.3. Voltage Reference (VREF) (36)5. Electrical Characteristics (37)5.1. Absolute Maximum Specifications (37)5.2. Electrical Characteristics (38)6. 10-Bit ADC (ADC0, C8051F380/1/2/3/C only) (46)6.1. Output Code Formatting (47)6.3. Modes of Operation (50)6.3.1. Starting a Conversion (50)6.3.2. Tracking Modes (51)6.3.3. Settling Time Requirements (52)6.4. Programmable Window Detector (56)6.4.1. Window Detector Example (58)6.5. ADC0 Analog Multiplexer (C8051F380/1/2/3/C only) (59)7. Voltage Reference Options (62)8. Comparator0 and Comparator1 (64)8.1. Comparator Multiplexers (71)9. Voltage Regulators (REG0 and REG1) (74)9.1. Voltage Regulator (REG0) (74)9.1.1. Regulator Mode Selection (74)9.1.2. VBUS Detection (74)9.2. Voltage Regulator (REG1) (74)10. Power Management Modes (76)10.1. Idle Mode (76)10.2. Stop Mode (77)10.3. Suspend Mode (77)11. CIP-51 Microcontroller (79)11.1. Instruction Set (80)11.1.1. Instruction and CPU Timing (80)11.2. CIP-51 Register Descriptions (85)12. Prefetch Engine (88)13. Memory Organization (89)13.1. Program Memory (91)13.2. Data Memory (91)13.3. General Purpose Registers (92)13.4. Bit Addressable Locations (92)13.5. Stack (92)C8051F380/1/2/3/4/5/6/7/C14. External Data Memory Interface and On-Chip XRAM (93)14.1. Accessing XRAM (93)14.1.1. 16-Bit MOVX Example (93)14.1.2. 8-Bit MOVX Example (93)14.2. Accessing USB FIFO Space (94)14.3. Configuring the External Memory Interface (95)14.4. Port Configuration (95)14.5. Multiplexed and Non-multiplexed Selection (98)14.5.1. Multiplexed Configuration (98)14.5.2. Non-multiplexed Configuration (98)14.6. Memory Mode Selection (100)14.6.1. Internal XRAM Only (100)14.6.2. Split Mode without Bank Select (100)14.6.3. Split Mode with Bank Select (101)14.6.4. External Only (101)14.7. Timing (102)14.7.1. Non-multiplexed Mode (104)14.7.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111 (104)14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 (105)14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110 (106)14.7.2. Multiplexed Mode (107)14.7.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011 (107)14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 (108)14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010 (109)15. Special Function Registers (111)15.1. 13.1. SFR Paging (111)16. Interrupts (118)16.1. MCU Interrupt Sources and Vectors (119)16.1.1. Interrupt Priorities (119)16.1.2. Interrupt Latency (119)16.2. Interrupt Register Descriptions (119)16.3. INT0 and INT1 External Interrupt Sources (127)17. Reset Sources (129)17.1. Power-On Reset (130)17.2. Power-Fail Reset / VDD Monitor (131)17.3. External Reset (132)17.4. Missing Clock Detector Reset (132)17.5. Comparator0 Reset (132)17.6. PCA Watchdog Timer Reset (133)17.7. Flash Error Reset (133)17.8. Software Reset (133)17.9. USB Reset (133)18. Flash Memory (135)18.1. Programming The Flash Memory (135)18.1.1. Flash Lock and Key Functions (135)C8051F380/1/2/3/4/5/6/7/C18.1.2. Flash Erase Procedure (135)18.1.3. Flash Write Procedure (136)18.2. Non-Volatile Data Storage (137)18.3. Security Options (137)19. Oscillators and Clock Selection (142)19.1. System Clock Selection (143)19.2. USB Clock Selection (143)19.3. Programmable Internal High-Frequency (H-F) Oscillator (145)19.3.1. Internal Oscillator Suspend Mode (145)19.4. Clock Multiplier (147)19.5. Programmable Internal Low-Frequency (L-F) Oscillator (148)19.5.1. Calibrating the Internal L-F Oscillator (148)19.6. External Oscillator Drive Circuit (149)19.6.1. External Crystal Mode (149)19.6.2. External RC Example (151)19.6.3. External Capacitor Example (151)20. Port Input/Output (153)20.1. Priority Crossbar Decoder (154)20.2. Port I/O Initialization (158)20.3. General Purpose Port I/O (161)21. Universal Serial Bus Controller (USB0) (172)21.1. Endpoint Addressing (172)21.2. USB Transceiver (173)21.3. USB Register Access (175)21.4. USB Clock Configuration (179)21.5. FIFO Management (181)21.5.1. FIFO Split Mode (181)21.5.2. FIFO Double Buffering (182)21.5.1. FIFO Access (182)21.6. Function Addressing (183)21.7. Function Configuration and Control (183)21.8. Interrupts (186)21.9. The Serial Interface Engine (193)21.10. Endpoint0 (193)21.10.1. Endpoint0 SETUP Transactions (193)21.10.2. Endpoint0 IN Transactions (193)21.10.3. Endpoint0 OUT Transactions (194)21.11. Configuring Endpoints1-3 (196)21.12. Controlling Endpoints1-3 IN (197)21.12.1. Endpoints1-3 IN Interrupt or Bulk Mode (197)21.12.2. Endpoints1-3 IN Isochronous Mode (198)21.13. Controlling Endpoints1-3 OUT (201)21.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode (201)21.13.2. Endpoints1-3 OUT Isochronous Mode (201)22. SMBus0 and SMBus1 (I2C Compatible) (205)C8051F380/1/2/3/4/5/6/7/C22.1. Supporting Documents (206)22.2. SMBus Configuration (206)22.3. SMBus Operation (206)22.3.1. Transmitter Vs. Receiver (207)22.3.2. Arbitration (207)22.3.3. Clock Low Extension (207)22.3.4. SCL Low Timeout (207)22.3.5. SCL High (SMBus Free) Timeout (208)22.4. Using the SMBus (208)22.4.1. SMBus Configuration Register (208)22.4.2. SMBus Timing Control Register (210)22.4.3. SMBnCN Control Register (214)22.4.3.1. Software ACK Generation (214)22.4.3.2. Hardware ACK Generation (214)22.4.4. Hardware Slave Address Recognition (217)22.4.5. Data Register (221)22.5. SMBus Transfer Modes (223)22.5.1. Write Sequence (Master) (223)22.5.2. Read Sequence (Master) (224)22.5.3. Write Sequence (Slave) (225)22.5.4. Read Sequence (Slave) (226)22.6. SMBus Status Decoding (226)23. UART0 (232)23.1. Enhanced Baud Rate Generation (233)23.2. Operational Modes (234)23.2.1. 8-Bit UART (234)23.2.2. 9-Bit UART (235)23.3. Multiprocessor Communications (236)24. UART1 (240)24.1. Baud Rate Generator (241)24.2. Data Format (242)24.3. Configuration and Operation (243)24.3.1. Data Transmission (243)24.3.2. Data Reception (243)24.3.3. Multiprocessor Communications (244)25. Enhanced Serial Peripheral Interface (SPI0) (250)25.1. Signal Descriptions (251)25.1.1. Master Out, Slave In (MOSI) (251)25.1.2. Master In, Slave Out (MISO) (251)25.1.3. Serial Clock (SCK) (251)25.1.4. Slave Select (NSS) (251)25.2. SPI0 Master Mode Operation (251)25.3. SPI0 Slave Mode Operation (253)25.4. SPI0 Interrupt Sources (254)25.5. Serial Clock Phase and Polarity (254)25.6. SPI Special Function Registers (256)26. Timers (263)26.1. Timer 0 and Timer 1 (266)26.1.1. Mode 0: 13-bit Counter/Timer (266)26.1.2. Mode 1: 16-bit Counter/Timer (267)26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload (267)26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) (268)26.2. Timer 2 (274)26.2.1. 16-bit Timer with Auto-Reload (274)26.2.2. 8-bit Timers with Auto-Reload (275)26.2.3. Timer 2 Capture Modes: USB Start-of-Frame or LFO Falling Edge (275)26.3. Timer 3 (281)26.3.1. 16-bit Timer with Auto-Reload (281)26.3.2. 8-bit Timers with Auto-Reload (282)26.3.3. Timer 3 Capture Modes: USB Start-of-Frame or LFO Falling Edge (282)26.4. Timer 4 (288)26.4.1. 16-bit Timer with Auto-Reload (288)26.4.2. 8-bit Timers with Auto-Reload (289)26.5. Timer 5 (293)26.5.1. 16-bit Timer with Auto-Reload (293)26.5.2. 8-bit Timers with Auto-Reload (294)27. Programmable Counter Array (298)27.1. PCA Counter/Timer (299)27.2. PCA0 Interrupt Sources (300)27.3. Capture/Compare Modules (301)27.3.1. Edge-triggered Capture Mode (302)27.3.2. Software Timer (Compare) Mode (303)27.3.3. High-Speed Output Mode (304)27.3.4. Frequency Output Mode (305)27.3.5. 8-bit Pulse Width Modulator Mode (306)27.3.6. 16-Bit Pulse Width Modulator Mode (307)27.4. Watchdog Timer Mode (308)27.4.1. Watchdog Timer Operation (308)27.4.2. Watchdog Timer Usage (309)27.5. Register Descriptions for PCA0 (311)28. C2 Interface (316)28.1. C2 Interface Registers (316)28.2. C2 Pin Sharing (319)Document Change List (320)Contact Information (321)List of FiguresFigure1.1. C8051F380/2/4/6 Block Diagram (18)Figure1.2. C8051F381/3/5/7/C Block Diagram (19)Figure3.1. TQFP-48 Pinout Diagram (Top View) (25)Figure3.2. TQFP-48 Package Diagram (26)Figure3.3. TQFP-48 Recommended PCB Land Pattern (27)Figure3.4. LQFP-32 Pinout Diagram (Top View) (28)Figure3.5. LQFP-32 Package Diagram (29)Figure3.6. LQFP-32 Recommended PCB Land Pattern (30)Figure3.7. QFN-32 Pinout Diagram (Top View) (31)Figure3.8. QFN-32 Package Drawing (32)Figure3.9. QFN-32 Recommended PCB Land Pattern (33)Figure4.1. Connection Diagram with Voltage Regulator Used and No USB (34)Figure4.2. Connection Diagram with Voltage Regulator Not Used and No USB (34)Figure4.3. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered) (35)Figure4.4. Connection Diagram with Voltage Regulator Used and USB Connected (Self-Powered) (35)Figure4.5. Connection Diagram for USB Pins (36)Figure4.6. Connection Diagram for Internal Voltage Reference (36)Figure6.1. ADC0 Functional Block Diagram (46)Figure6.2. Typical Temperature Sensor Transfer Function (48)Figure6.3. Temperature Sensor Error with 1-Point Calibration (49)Figure6.4. 10-Bit ADC Track and Conversion Example Timing (51)Figure6.5. ADC0 Equivalent Input Circuits (52)Figure6.6. ADC Window Compare Example: Right-Justified Data (58)Figure6.7. ADC Window Compare Example: Left-Justified Data (58)Figure7.1. Voltage Reference Functional Block Diagram (62)Figure8.1. Comparator0 Functional Block Diagram (64)Figure8.2. Comparator1 Functional Block Diagram (65)Figure8.3. Comparator Hysteresis Plot (66)Figure8.4. Comparator Input Multiplexer Block Diagram (71)Figure11.1. CIP-51 Block Diagram (79)Figure13.1. On-Chip Memory Map for 64kB Devices (C8051F380/1/4/5) (89)Figure13.2. On-Chip Memory Map for 32kB Devices (C8051F382/3/6/7) (90)Figure13.3. On-Chip Memory Map for 16kB Devices (C8051F38C) (91)Figure14.1. USB FIFO Space and XRAM Memory Map with USBFAE set to ‘1’ (94)Figure14.2. Multiplexed Configuration Example (98)Figure14.3. Non-multiplexed Configuration Example (99)Figure14.4. EMIF Operating Modes (100)Figure14.5. Non-Multiplexed 16-bit MOVX Timing (104)Figure14.6. Non-multiplexed 8-bit MOVX without Bank Select Timing (105)Figure14.7. Non-multiplexed 8-bit MOVX with Bank Select Timing (106)Figure14.8. Multiplexed 16-bit MOVX Timing (107)C8051F380/1/2/3/4/5/6/7/CFigure14.9. Multiplexed 8-bit MOVX without Bank Select Timing (108)Figure14.10. Multiplexed 8-bit MOVX with Bank Select Timing (109)Figure17.1. Reset Sources (129)Figure17.2. Power-On and VDD Monitor Reset Timing (130)Figure18.1. Flash Program Memory Map and Security Byte (137)Figure19.1. Oscillator Options (142)Figure19.2. External Crystal Example (150)Figure20.1. Port I/O Functional Block Diagram (Port 0 through Port 3) (153)Figure20.2. Port I/O Cell Block Diagram (154)Figure20.3. Peripheral Availability on Port I/O Pins (155)Figure20.4. Crossbar Priority Decoder in Example Configuration(No Pins Skipped) (156)Figure20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped) (157)Figure21.1. USB0 Block Diagram (172)Figure21.2. USB0 Register Access Scheme (175)Figure21.3. USB FIFO Allocation (181)Figure22.1. SMBus Block Diagram (205)Figure22.2. Typical SMBus Configuration (206)Figure22.3. SMBus Transaction (207)Figure22.4. Typical SMBus SCL Generation (209)Figure22.5. Typical Master Write Sequence (223)Figure22.6. Typical Master Read Sequence (224)Figure22.7. Typical Slave Write Sequence (225)Figure22.8. Typical Slave Read Sequence (226)Figure23.1. UART0 Block Diagram (232)Figure23.2. UART0 Baud Rate Logic (233)Figure23.3. UART Interconnect Diagram (234)Figure23.4. 8-Bit UART Timing Diagram (234)Figure23.5. 9-Bit UART Timing Diagram (235)Figure23.6. UART Multi-Processor Mode Interconnect Diagram (236)Figure24.1. UART1 Block Diagram (240)Figure24.2. UART1 Timing Without Parity or Extra Bit (242)Figure24.3. UART1 Timing With Parity (242)Figure24.4. UART1 Timing With Extra Bit (242)Figure24.5. Typical UART Interconnect Diagram (243)Figure24.6. UART Multi-Processor Mode Interconnect Diagram (244)Figure25.1. SPI Block Diagram (250)Figure25.2. Multiple-Master Mode Connection Diagram (252)Figure25.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram (252)Figure25.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram (253)Figure25.5. Master Mode Data/Clock Timing (255)Figure25.6. Slave Mode Data/Clock Timing (CKPHA = 0) (255)C8051F380/1/2/3/4/5/6/7/C Figure25.7. Slave Mode Data/Clock Timing (CKPHA = 1) (256)Figure25.8. SPI Master Timing (CKPHA = 0) (260)Figure25.9. SPI Master Timing (CKPHA = 1) (260)Figure25.10. SPI Slave Timing (CKPHA = 0) (261)Figure25.11. SPI Slave Timing (CKPHA = 1) (261)Figure26.1. T0 Mode 0 Block Diagram (267)Figure26.2. T0 Mode 2 Block Diagram (268)Figure26.3. T0 Mode 3 Block Diagram (269)Figure26.4. Timer 2 16-Bit Mode Block Diagram (274)Figure26.5. Timer 2 8-Bit Mode Block Diagram (275)Figure26.6. Timer2 Capture Mode (T2SPLIT = 0) (276)Figure26.7. Timer2 Capture Mode (T2SPLIT = 0) (277)Figure26.8. Timer 3 16-Bit Mode Block Diagram (281)Figure26.9. Timer 3 8-Bit Mode Block Diagram (282)Figure26.10. Timer3 Capture Mode (T3SPLIT = 0) (283)Figure26.11. Timer3 Capture Mode (T3SPLIT = 0) (284)Figure26.12. Timer 4 16-Bit Mode Block Diagram (288)Figure26.13. Timer 4 8-Bit Mode Block Diagram (289)Figure26.14. Timer 5 16-Bit Mode Block Diagram (293)Figure26.15. Timer 5 8-Bit Mode Block Diagram (294)Figure27.1. PCA Block Diagram (298)Figure27.2. PCA Counter/Timer Block Diagram (299)Figure27.3. PCA Interrupt Block Diagram (300)Figure27.4. PCA Capture Mode Diagram (302)Figure27.5. PCA Software Timer Mode Diagram (303)Figure27.6. PCA High-Speed Output Mode Diagram (304)Figure27.7. PCA Frequency Output Mode (305)Figure27.8. PCA 8-Bit PWM Mode Diagram (306)Figure27.9. PCA 16-Bit PWM Mode (307)Figure27.10. PCA Module 4 with Watchdog Timer Enabled (308)Figure28.1. Typical C2 Pin Sharing (319)List of TablesTable1.1. Product Selection Guide (17)Table2.1. C8051F38x Replacement Part Numbers (20)Table3.1. Pin Definitions for the C8051F380/1/2/3/4/5/6/7/C (22)Table3.2. TQFP-48 Package Dimensions (26)Table3.3. TQFP-48 PCB Land Pattern Dimensions (27)Table3.4. LQFP-32 Package Dimensions (29)Table3.5. LQFP-32 PCB Land Pattern Dimensions (30)Table3.6. QFN-32 Package Dimensions (32)Table3.7. QFN-32 PCB Land Pattern Dimensions (33)Table5.1. Absolute Maximum Ratings (37)Table5.2. Global Electrical Characteristics (38)Table5.3. Port I/O DC Electrical Characteristics (39)Table5.4. Reset Electrical Characteristics (39)Table5.5. Internal Voltage Regulator Electrical Characteristics (40)Table5.6. Flash Electrical Characteristics (40)Table5.7. Internal High-Frequency Oscillator Electrical Characteristics (41)Table5.8. Internal Low-Frequency Oscillator Electrical Characteristics (41)Table5.9. External Oscillator Electrical Characteristics (41)Table5.10. ADC0 Electrical Characteristics (42)Table5.11. Temperature Sensor Electrical Characteristics (43)Table5.12. Voltage Reference Electrical Characteristics (43)Table5.13. Comparator Electrical Characteristics (44)Table5.14. USB Transceiver Electrical Characteristics (45)Table11.1. CIP-51 Instruction Set Summary (81)Table14.1. AC Parameters for External Memory Interface (110)Table15.1. Special Function Register (SFR) Memory Map (112)Table15.2. Special Function Registers (113)Table16.1. Interrupt Summary (120)Table21.1. Endpoint Addressing Scheme (173)Table21.2. USB0 Controller Registers (178)Table21.3. FIFO Configurations (182)Table22.1. SMBus Clock Source Selection (209)Table22.2. Minimum SDA Setup and Hold Times (210)Table22.3. Sources for Hardware Changes to SMBnCN (217)Table22.4. Hardware Address Recognition Examples (EHACK = 1) (218)Table22.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (227)Table22.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1) (229)Table23.1. Timer Settings for Standard Baud Rates Using Internal Oscillator (238)Table24.1. Baud Rate Generator Settings for Standard Baud Rates (241)Table25.1. SPI Slave Timing Parameters (262)Table27.1. PCA Timebase Input Options (299)Table27.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules (301)Table27.3. Watchdog Timer Timeout Intervals1 (310)List of RegistersSFR Definition6.1. ADC0CF: ADC0 Configuration (53)SFR Definition6.2. ADC0H: ADC0 Data Word MSB (54)SFR Definition6.3. ADC0L: ADC0 Data Word LSB (54)SFR Definition6.4. ADC0CN: ADC0 Control (55)SFR Definition6.5. ADC0GTH: ADC0 Greater-Than Data High Byte (56)SFR Definition6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte (56)SFR Definition6.7. ADC0LTH: ADC0 Less-Than Data High Byte (57)SFR Definition6.8. ADC0LTL: ADC0 Less-Than Data Low Byte (57)SFR Definition6.9. AMX0P: AMUX0 Positive Channel Select (60)SFR Definition6.10. AMX0N: AMUX0 Negative Channel Select (61)SFR Definition7.1. REF0CN: Reference Control (63)SFR Definition8.1. CPT0CN: Comparator0 Control (67)SFR Definition8.2. CPT0MD: Comparator0 Mode Selection (68)SFR Definition8.3. CPT1CN: Comparator1 Control (69)SFR Definition8.4. CPT1MD: Comparator1 Mode Selection (70)SFR Definition8.5. CPT0MX: Comparator0 MUX Selection (72)SFR Definition8.6. CPT1MX: Comparator1 MUX Selection (73)SFR Definition9.1. REG01CN: Voltage Regulator Control (75)SFR Definition10.1. PCON: Power Control (78)SFR Definition11.1. DPL: Data Pointer Low Byte (85)SFR Definition11.2. DPH: Data Pointer High Byte (85)SFR Definition11.3. SP: Stack Pointer (86)SFR Definition11.4. ACC: Accumulator (86)SFR Definition11.5. B: B Register (86)SFR Definition11.6. PSW: Program Status Word (87)SFR Definition12.1. PFE0CN: Prefetch Engine Control (88)SFR Definition14.1. EMI0CN: External Memory Interface Control (96)SFR Definition14.2. EMI0CF: External Memory Interface Configuration (97)SFR Definition14.3. EMI0TC: External Memory TIming Control (103)SFR Definition15.1. SFRPAGE: SFR Page (111)SFR Definition16.1. IE: Interrupt Enable (121)SFR Definition16.2. IP: Interrupt Priority (122)SFR Definition16.3. EIE1: Extended Interrupt Enable 1 (123)SFR Definition16.4. EIP1: Extended Interrupt Priority 1 (124)SFR Definition16.5. EIE2: Extended Interrupt Enable 2 (125)SFR Definition16.6. EIP2: Extended Interrupt Priority 2 (126)SFR Definition16.7. IT01CF: INT0/INT1 ConfigurationO (128)SFR Definition17.1. VDM0CN: VDD Monitor Control (132)SFR Definition17.2. RSTSRC: Reset Source (134)SFR Definition18.1. PSCTL: Program Store R/W Control (139)SFR Definition18.2. FLKEY: Flash Lock and Key (140)SFR Definition18.3. FLSCL: Flash Scale (141)SFR Definition19.1. CLKSEL: Clock Select (144)C8051F380/1/2/3/4/5/6/7/CSFR Definition19.2. OSCICL: Internal H-F Oscillator Calibration (145)SFR Definition19.3. OSCICN: Internal H-F Oscillator Control (146)SFR Definition19.4. CLKMUL: Clock Multiplier Control (147)SFR Definition19.5. OSCLCN: Internal L-F Oscillator Control (148)SFR Definition19.6. OSCXCN: External Oscillator Control (152)SFR Definition20.1. XBR0: Port I/O Crossbar Register 0 (159)SFR Definition20.2. XBR1: Port I/O Crossbar Register 1 (160)SFR Definition20.3. XBR2: Port I/O Crossbar Register 2 (161)SFR Definition20.4. P0: Port 0 (162)SFR Definition20.5. P0MDIN: Port 0 Input Mode (162)SFR Definition20.6. P0MDOUT: Port 0 Output Mode (163)SFR Definition20.7. P0SKIP: Port 0 Skip (163)SFR Definition20.8. P1: Port 1 (164)SFR Definition20.9. P1MDIN: Port 1 Input Mode (164)SFR Definition20.10. P1MDOUT: Port 1 Output Mode (165)SFR Definition20.11. P1SKIP: Port 1 Skip (165)SFR Definition20.12. P2: Port 2 (166)SFR Definition20.13. P2MDIN: Port 2 Input Mode (166)SFR Definition20.14. P2MDOUT: Port 2 Output Mode (167)SFR Definition20.15. P2SKIP: Port 2 Skip (167)SFR Definition20.16. P3: Port 3 (168)SFR Definition20.17. P3MDIN: Port 3 Input Mode (168)SFR Definition20.18. P3MDOUT: Port 3 Output Mode (169)SFR Definition20.19. P3SKIP: Port 3 Skip (169)SFR Definition20.20. P4: Port 4 (170)SFR Definition20.21. P4MDIN: Port 4 Input Mode (170)SFR Definition20.22. P4MDOUT: Port 4 Output Mode (171)SFR Definition21.1. USB0XCN: USB0 Transceiver Control (174)SFR Definition21.2. USB0ADR: USB0 Indirect Address (176)SFR Definition21.3. USB0DAT: USB0 Data (177)USB Register Definition21.4. INDEX: USB0 Endpoint Index (179)USB Register Definition21.5. CLKREC: Clock Recovery Control (180)USB Register Definition21.6. FIFOn: USB0 Endpoint FIFO Access (182)USB Register Definition21.7. FADDR: USB0 Function Address (183)USB Register Definition21.8. POWER: USB0 Power (185)USB Register Definition21.9. FRAMEL: USB0 Frame Number Low (186)USB Register Definition21.10. FRAMEH: USB0 Frame Number High (186)USB Register Definition21.11. IN1INT: USB0 IN Endpoint Interrupt (187)USB Register Definition21.12. OUT1INT: USB0 OUT Endpoint Interrupt (188)USB Register Definition21.13. CMINT: USB0 Common Interrupt (189)USB Register Definition21.14. IN1IE: USB0 IN Endpoint Interrupt Enable (190)USB Register Definition21.15. OUT1IE: USB0 OUT Endpoint Interrupt Enable (191)USB Register Definition21.16. CMIE: USB0 Common Interrupt Enable (192)USB Register Definition21.17. E0CSR: USB0 Endpoint0 Control (195)USB Register Definition21.18. E0CNT: USB0 Endpoint0 Data Count (196)C8051F380/1/2/3/4/5/6/7/C USB Register Definition21.19. EENABLE: USB0 Endpoint Enable (197)USB Register Definition21.20. EINCSRL: USB0 IN Endpoint Control Low (199)USB Register Definition21.21. EINCSRH: USB0 IN Endpoint Control High (200)USB Register Definition21.22. EOUTCSRL: USB0 OUT Endpoint Control Low Byte 202 USB Register Definition21.23. EOUTCSRH: USB0 OUT Endpoint Control High Byte (203)USB Register Definition21.24. EOUTCNTL: USB0 OUT Endpoint Count Low (203)USB Register Definition21.25. EOUTCNTH: USB0 OUT Endpoint Count High (204)SFR Definition22.1. SMB0CF: SMBus Clock/Configuration (211)SFR Definition22.2. SMB1CF: SMBus Clock/Configuration (212)SFR Definition22.3. SMBTC: SMBus Timing Control (213)SFR Definition22.4. SMB0CN: SMBus Control (215)SFR Definition22.5. SMB1CN: SMBus Control (216)SFR Definition22.6. SMB0ADR: SMBus0 Slave Address (218)SFR Definition22.7. SMB0ADM: SMBus0 Slave Address Mask (219)SFR Definition22.8. SMB1ADR: SMBus1 Slave Address (219)SFR Definition22.9. SMB1ADM: SMBus1 Slave Address Mask (220)SFR Definition22.10. SMB0DAT: SMBus Data (221)SFR Definition22.11. SMB1DAT: SMBus Data (222)SFR Definition23.1. SCON0: Serial Port 0 Control (237)SFR Definition23.2. SBUF0: Serial (UART0) Port Data Buffer (238)SFR Definition24.1. SCON1: UART1 Control (245)SFR Definition24.2. SMOD1: UART1 Mode (246)SFR Definition24.3. SBUF1: UART1 Data Buffer (247)SFR Definition24.4. SBCON1: UART1 Baud Rate Generator Control (248)SFR Definition24.5. SBRLH1: UART1 Baud Rate Generator High Byte (248)SFR Definition24.6. SBRLL1: UART1 Baud Rate Generator Low Byte (249)SFR Definition25.1. SPI0CFG: SPI0 Configuration (257)SFR Definition25.2. SPI0CN: SPI0 Control (258)SFR Definition25.3. SPI0CKR: SPI0 Clock Rate (259)SFR Definition25.4. SPI0DAT: SPI0 Data (259)SFR Definition26.1. CKCON: Clock Control (264)SFR Definition26.2. CKCON1: Clock Control 1 (265)SFR Definition26.3. TCON: Timer Control (270)SFR Definition26.4. TMOD: Timer Mode (271)SFR Definition26.5. TL0: Timer 0 Low Byte (272)SFR Definition26.6. TL1: Timer 1 Low Byte (272)SFR Definition26.7. TH0: Timer 0 High Byte (273)SFR Definition26.8. TH1: Timer 1 High Byte (273)SFR Definition26.9. TMR2CN: Timer 2 Control (278)SFR Definition26.10. TMR2RLL: Timer 2 Reload Register Low Byte (279)SFR Definition26.11. TMR2RLH: Timer 2 Reload Register High Byte (279)SFR Definition26.12. TMR2L: Timer 2 Low Byte (279)SFR Definition26.13. TMR2H Timer 2 High Byte (280)SFR Definition26.14. TMR3CN: Timer 3 Control (285)C8051F380/1/2/3/4/5/6/7/CSFR Definition26.15. TMR3RLL: Timer 3 Reload Register Low Byte (286)SFR Definition26.16. TMR3RLH: Timer 3 Reload Register High Byte (286)SFR Definition26.17. TMR3L: Timer 3 Low Byte (286)SFR Definition26.18. TMR3H Timer 3 High Byte (287)SFR Definition26.19. TMR4CN: Timer 4 Control (290)SFR Definition26.20. TMR4RLL: Timer 4 Reload Register Low Byte (291)SFR Definition26.21. TMR4RLH: Timer 4 Reload Register High Byte (291)SFR Definition26.22. TMR4L: Timer 4 Low Byte (291)SFR Definition26.23. TMR4H Timer 4 High Byte (292)SFR Definition26.24. TMR5CN: Timer 5 Control (295)SFR Definition26.25. TMR5RLL: Timer 5 Reload Register Low Byte (296)SFR Definition26.26. TMR5RLH: Timer 5 Reload Register High Byte (296)SFR Definition26.27. TMR5L: Timer 5 Low Byte (296)SFR Definition26.28. TMR5H Timer 5 High Byte (297)SFR Definition27.1. PCA0CN: PCA Control (311)SFR Definition27.2. PCA0MD: PCA Mode (312)SFR Definition27.3. PCA0CPMn: PCA Capture/Compare Mode (313)SFR Definition27.4. PCA0L: PCA Counter/Timer Low Byte (314)SFR Definition27.5. PCA0H: PCA Counter/Timer High Byte (314)SFR Definition27.6. PCA0CPLn: PCA Capture Module Low Byte (315)SFR Definition27.7. PCA0CPHn: PCA Capture Module High Byte (315)C2 Register Definition28.1. C2ADD: C2 Address (316)C2 Register Definition28.2. DEVICEID: C2 Device ID (317)C2 Register Definition28.3. REVID: C2 Revision ID (317)C2 Register Definition28.4. FPCTL: C2 Flash Programming Control (318)C2 Register Definition28.5. FPDAT: C2 Flash Programming Data (318)。

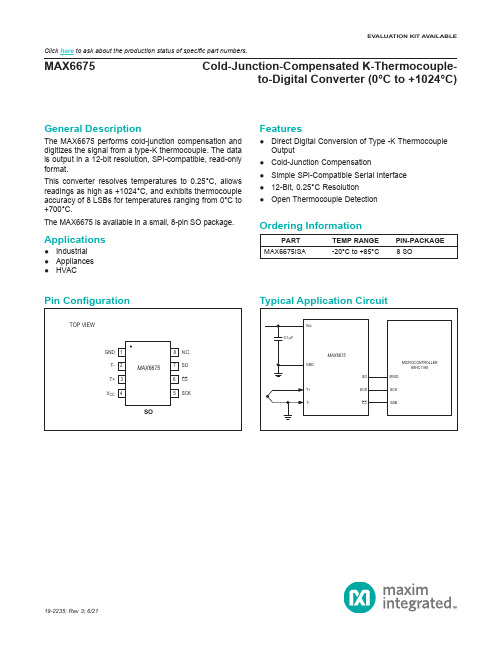

关于MAX6675的说明书

General DescriptionThe MAX6675 performs cold-junction compensation and digitizes the signal from a type-K thermocouple. The data is output in a 12-bit resolution, SPI-compatible, read-only format.This converter resolves temperatures to 0.25°C, allows readings as high as +1024°C, and exhibits thermocouple accuracy of 8 LSBs for temperatures ranging from 0°C to +700°C.The MAX6675 is available in a small, 8-pin SO package.Applications●Industrial ●Appliances ●HVACFeatures●Direct Digital Conversion of Type -K ThermocoupleOutput ●Cold-Junction Compensation●Simple SPI-Compatible Serial Interface ●12-Bit, 0.25°C Resolution ●Open Thermocouple DetectionPART TEMP RANGE PIN-PACKAGE MAX6675ISA-20°C to +85°C8 SOMAX6675Cold-Junction-Compensated K-Thermocouple-to-Digital Converter (0°C to +1024°C)19-2235; Rev 3; 6/21Ordering InformationEVALUATION KIT AVAILABLEClick here to ask about the production status of specific part numbers.Supply Voltage (V CC to GND) ............................... -0.3V to +6V SO, SCK, CS , T-, T+ to GND .....................-0.3V to V CC + 0.3V SO Current ....................................................................... 50mA ESD Protection (Human Body Model) .......................... ±2000V Continuous Power Dissipation (T A = +70°C)8-Pin SO (derate 5.88mW/°C above +70°C) ............. 471mW Operating Temperature Range ..........................-20°C to +85°CStorage Temperature Range ...........................-65°C to +150°C Junction Temperature .................................................... +150°C SO PackageVapor Phase (60s) . .....................................................+215°C Infrared (15s) ..............................................................+220°C Lead Temperature (soldering, 10s) ............................... +300°C(V CC = +3.0V to +5.5V, T A = -20°C to +85°C, unless otherwise noted. Typical values specified at +25°C.) (Note 1)PARAMETERSYMBOLCONDITIONSMINTYP MAX UNITSTemperature ErrorT THERMOCOUPLE = +700°C,T A = +25°C (Note 2)V CC = +3.3V -5+5LSBV CC = +5V -6+6T THERMOCOUPLE = 0°C to +700°C, T A = +25°C (Note 2)V CC = +3.3V -8+8V CC = +5V -9+9T THERMOCOUPLE = +700°Cto +1000°C, T A = +25°C (Note 2)V CC = +3.3V -17+17V CC = +5V-19+19Thermocouple Conversion Constant10.25µV/LSB Cold-JunctionCompensation Error T A = -20°C t o +85°C (Note 2)V CC = +3.3V -3.0+3.0°C V CC= +5V-3.0+3.0Resolution0.25°C Thermocouple Input Impedance 60k W Supply Voltage V CC 3.05.5V Supply CurrentI CC0.7 1.5mA Power-On Reset Threshold V CC rising12 2.5V Power-On Reset Hysteresis 50mV Conversion Time (Note 2)0.170.22sSERIAL INTERFACE Input Low Voltage V IL 0.3 x V CCV Input High Voltage V IH 0.7 x V CCV Input Leakage Current I LEAK V IN = GND or V CC±5µA Input CapacitanceC IN5pFto-Digital Converter (0°C to +1024°C)Electrical CharacteristicsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Absolute Maximum RatingsNote 1: All specifications are 100% tested at T A = +25°C. Specification limits over temperature (T A = T MIN to T MAX ) are guaranteedby design and characterization, not production tested.Note 2: Guaranteed by design. Not production tested.(V CC = +3.3V, T A = +25°C, unless otherwise noted.)(V CC = +3.0V to +5.5V, T A = -20°C to +85°C, unless otherwise noted. Typical values specified at +25°C.) (Note 1)PARAMETERSYMBOL CONDITIONSMIN TYPMAXUNITS Output High Voltage V OH I SOURCE = 1.6mA V CC - 0.4V Output Low Voltage V OLI SINK = 1.6mA0.4VTIMINGSerial Clock Frequency f SCL 4.3MHz SCK Pulse High Width t CH 100ns SCK Pulse Low Width t C L 100ns CSB Fall to SCK Rise t CSS C L = 10pF 100ns CSB Fall to Output Enable t DV C L = 10pF 100ns CSB Rise to Output Disable t TR C L = 10pF 100ns SCK Fall to Output Data Validt DOC L = 10pF100ns-50510-103050OUTPUT CODE ERROR vs. VOLTAGE DIFFERENTIALM A X 6675 t o c 02VOLTAGE DIFFERENTIAL (mV)O U T P U T C O D E E R R O R (L S B )1020401086420451530607590OUTPUT CODE ERROR vs. AMBIENT TEMPERATUREM A X 6675 t o c 01TEMPERATURE (°C)O U T P U T C O D E E R R O R (L S B )to-Digital Converter (0°C to +1024°C)Typical Operating CharacteristicsElectrical Characteristics (continued)Detailed DescriptionThe MAX6675 is a sophisticated thermocouple-to-digi- tal converter with a built-in 12-bit analog-to-digital con-verter (ADC). The MAX6675 also contains cold-junction compensation sensing and correction, a digital con- troller, an SPI-compatible interface, and associated control logic.The MAX6675 is designed to work in conjunction with an external microcontroller (µC) or other intelligence in ther-mostatic, process-control, or monitoring applications. Temperature ConversionThe MAX6675 includes signal-conditioning hardware to convert the thermocouple’s signal into a voltage compat-ible with the input channels of the ADC. The T+and T- inputs connect to internal circuitry that reduces the intro- duction of noise errors from the thermocouple wires. Before converting the thermoelectric voltages into equivalent temperature values, it is necessary to com-pensate for the difference between the thermocouple cold-junction side (MAX6675 ambient temperature) and a 0°C virtual reference. For a type-K thermocouple, the voltage changes by 41µV/°C, which approximates the thermocouple characteristic with the following linear equation:V OUT = (41µV / °C) x (T R - T AMB)Where:V OUT is the thermocouple output voltage (µV).T R is the temperature of the remote thermocouple junc-tion (°C).T AMB is the ambient temperature (°C).Cold-Junction CompensationThe function of the thermocouple is to sense a differ- ence in temperature between two ends of the thermo- couple wires. The thermocouple’s hot junction can be read from 0°C to +1023.75°C. The cold end (ambi-ent temperature of the board on which the MAX6675 is mounted) can only range from -20°C to +85°C. While the temperature at the cold end fluctuates, the MAX6675 continues to accurately sense the tempera- ture difference at the opposite end.The MAX6675 senses and corrects for the changes in the ambient temperature with cold-junction compen-sation. The device converts the ambient temperature reading into a voltage using a temperature-sensing diode. To make the actual thermocouple temperature measurement, the MAX6675 measures the voltage from the thermocouple’s output and from the sensing diode. The device’s internal circuitry passes the diode’s volt- age (sensing ambient temperature) and thermocouple voltage (sensing remote temperature minus ambient temperature) to the conversion function stored in the ADC to calculate the thermocouple’s hot-junction tem-perature.Optimal performance from the MAX6675 is achieved when the thermocouple cold junction and the MAX6675 are at the same temperature. Avoid placing heat-gen-erating devices or components near the MAX6675 because this may produce cold-junction-related errors. DigitizationThe ADC adds the cold-junction diode measurement with the amplified thermocouple voltage and reads out the 12-bit result onto the SO pin. A sequence of all zeros means the thermocouple reading is 0°C. A sequence of all ones means the thermocouple reading is +1023.75°C.PIN NAME FUNCTION1GND Ground2T-Alumel Lead of Type-K Thermocouple.Should be connected to ground externally. 3T+Chromel Lead of Type-K Thermocouple4V CC Positive Supply. Bypass with a 0.1µFcapacitor to GND.5SCK Serial Clock Input6CS Chip Select. Set CS low to enable the serialinterface.7SO Serial Data Output8N.C.No Connection to-Digital Converter (0°C to +1024°C)Pin DescriptionApplications InformationSerial InterfaceThe T ypical Application Circuit shows the MAX6675 interfaced with a microcontroller. In this example, the MAX6675 processes the reading from the thermocou- ple and transmits the data through a serial interface. Force CS low and apply a clock signal at SCK to read the results at SO. Forcing CS low immediately stops any conversion process. Initiate a new conversion process by forcing CS high.Force CS low to output the first bit on the SO pin. A complete serial interface read requires 16 clock cycles. Read the 16 output bits on the falling edge of the clock. The first bit, D15, is a dummy sign bit and is always zero. Bits D14–D3 contain the converted temperature in the order of MSB to LSB. Bit D2 is normally low and goes high when the thermocouple input is open. D1 is low to provide a device ID for the MAX6675 and bit D0 is three-state.Figure 1a is the serial interface protocol and Figure 1b shows the serial interface timing. Figure 2 is the SO out-put.Open ThermocoupleBit D2 is normally low and goes high if the thermocou- ple input is open. In order to allow the operation of the open thermocouple detector, T- must be grounded. Make the ground connection as close to the GND pin as possible.Noise ConsiderationsThe accuracy of the MAX6675 is susceptible to power- supply coupled noise. The effects of power-supply noise can be minimized by placing a 0.1µF ceramic bypass capacitor close to the supply pin of the device.Thermal ConsiderationsSelf-heating degrades the temperature measurement accuracy of the MAX6675 in some applications. The magnitude of the temperature errors depends on the thermal conductivity of the MAX6675 package, the mounting technique, and the effects of airflow. Use a large ground plane to improve the temperature mea- surement accuracy of the MAX6675.The accuracy of a thermocouple system can also be improved by following these precautions:●Use the largest wire possible that does not shuntheat away from the measurement area.●If small wire is required, use it only in the region ofthe measurement and use extension wire for theregion with no temperature gradient.●Avoid mechanical stress and vibration, which couldstrain the wires.●When using long thermocouple wires, use a twisted-pair extension wire.●Avoid steep temperature gradients.●Try to use the thermocouple wire well within its tem-perature rating.●Use the proper sheathing material in hostile environ-ments to protect the thermocouple wire.●Use extension wire only at low temperatures andonly in regions of small gradients.●Keep an event log and a continuous record of ther-mocouple resistance.Reducing Effects of Pick-Up NoiseThe input amplifier (A1) is a low-noise amplifier designed to enable high-precision input sensing. Keep the thermocouple and connecting wires away from elec-trical noise sources.to-Digital Converter (0°C to +1024°C)Figure 2. SO OutputFigure 1b. Serial Interface TimingFigure 1a. Serial Interface ProtocolBIT DUMMY SIGN BIT12-BITTEMPERATURE READING THERMOCOUPLEINPUTDEVICE IDSTATE Bit15141312111098765432100MSBLSBThree-stateCSSCKSOD15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0to-Digital Converter (0°C to +1024°C)PACKAGE TYPEPACKAGE CODE OUTLINE ND PATTERN NO.8 SOS8+221-004190-0096to-Digital Converter (0°C to +1024°C)Package InformationFor the latest package outline information and land patterns (footprints), go to /packages . Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.Chip InformationTRANSISTOR COUNT: 6720PROCESS: BiCMOSREVISION NUMBERREVISION DATE DESCRIPTIONPAGES CHANGED24/14Removed automotive reference136/21Updated equation in Temperature Compensation section.4Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.to-Digital Converter (0°C to +1024°C)Revision HistoryFor pricing, delivery, and ordering information, please visit Maxim Integrated’s online storefront at https:///en/storefront/storefront.html.。

FullProf 详细使用教程

New facilities concerning symmetry in FullProf

⇒ The symmetry used within FullProf is totally based in the Crystallographic Fortran 95 Modules Library (CrysFML) (Tuesday 26 ⇒ FA3-MS5, Meeting Room 11B) ⇒ These modules provide better crystallographic information to the user of the program. In particular automatic calculation of the multiplicity of each site is now performed after reading the atoms as well as the calculation of the appropriate coefficients for automatic quantitative analysis of mixture of phases. ⇒ New output files with full information of crystallographic symmetry are produced (extension: sym)

Durban, August 24, 2003

ECM-21 Software Workshop

Last minute changes in FullProf Documented in “fp2k.inf”

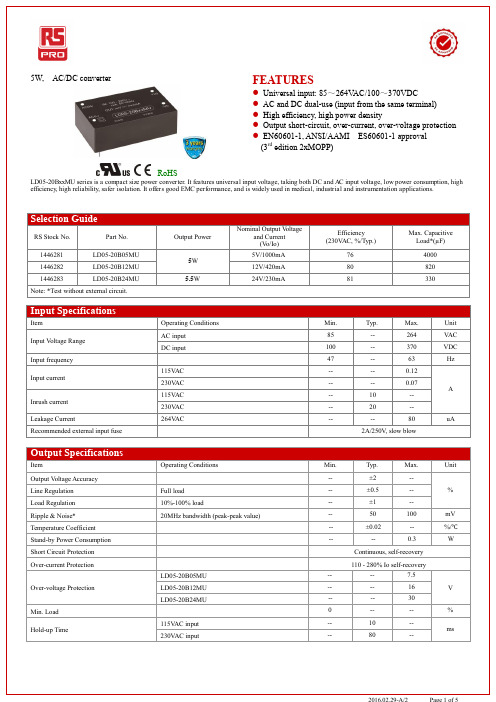

LD05-20BxxMU系列AC DC转换器用户说明书

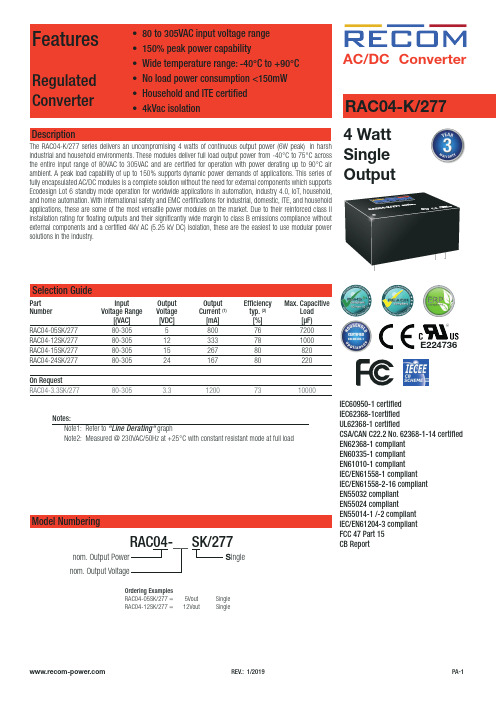

5W, AC/DC converterRoHSFEATURES● Universal input: 85~264V AC/100~370VDC● AC and DC dual-use (input from the same terminal) ● High efficiency, high power density● Output short-circuit, over-current, over-voltage protection ● EN60601-1, ANSI/AAMI ES60601-1 approval (3rd edition 2xMOPP)LD05-20BxxMU series is a compact size power converter. It features universal input voltage, taking both DC and AC input voltage, low power consumption, high efficiency, high reliability, safer isolation. It offers good EMC performance, and is widely used in medical, industrial and instrumentation applications.Selection GuideRS Stock No. Part No. Output PowerNominal Output V oltageand Current (V o/Io)Efficiency (230V AC, %/Typ.)Max. Capacitive Load*(µF)1446281 LD05-20B05MU 5W 5V/1000mA 76 4000 1446282 LD05-20B12MU 12V/420mA 80 820 1446283 LD05-20B24MU5.5W24V/230mA81330Note: *Test without external circuit.Input SpecificationsItemOperating Conditions Min. Typ. Max. Unit Input V oltage Range AC input 85 -- 264 V AC DC input 100 -- 370 VDC Input frequency 47 -- 63 HzInput current115V AC -- -- 0.12 A 230V AC -- -- 0.07 Inrush current 115V AC -- 10 -- 230V AC -- 20 -- Leakage Current264V AC ----80uA Recommended external input fuse2A/250V , slow blowOutput SpecificationsItemOperating Conditions Min. Typ. Max. UnitOutput V oltage Accuracy-- ±2 -- % Line Regulation Full load -- ±0.5 -- Load Regulation 10%-100% load-- ±1 -- Ripple & Noise* 20MHz bandwidth (peak-peak value)-- 50 100 mV Temperature Coefficient -- ±0.02 -- %/℃ Stand-by Power Consumption----0.3W Short Circuit Protection Continuous, self-recovery Over-current Protection110 - 280% Io self-recoveryOver-voltage Protection LD05-20B05MU -- -- 7.5 VLD05-20B12MU -- -- 16 LD05-20B24MU-- -- 30 Min. Load0 -- -- % Hold-up Time115V AC input -- 10 -- ms 230V AC input --80--General SpecificationsItem Operating Conditions Min. Typ. Max. Unit Isolation V oltage Input-output Test time: 1min 4000 -- -- V AC Operating Temperature -25 -- +70℃Storage Temperature -40 -- +85Max. Casing Temperature -- -- +95Storage Humidity -- -- 95 %RHWelding Temperature Wave-soldering 260±5℃; time:5~10s Manual-welding 360±10℃; time:3~5sSwitching Frequency -- -- 140 kHzPower Derating -25 ~ 0℃ 1 -- -- %/℃+55 ~ +70℃ 2 -- -- %/℃Safety Standard EN60601/UL60601Safety Certification EN60601/UL60601Safety Class CLASS IIinsulation Level Primary to Secondary2xMOPPMTBF MIL-HDBK-217F@25℃ >300,000 h Physical SpecificationsCasing Material Black flame-retardant and heat-resistant plastic (UL94-V0)Package Dimensions 53.80*28.80*19.00 mmWeight 43g (Typ.)Cooling method Free air convectionEMC SpecificationsEMI CE CISPR11/EN55011 CLASS B RE CISPR11/EN55011 CLASS BEMS ESD IEC/EN61000-4-2 Contact±6KV/Air±8KV Perf. Criteria B RS IEC/EN61000-4-3 10V/m perf. Criteria AEFTIEC/EN61000-4-4 ±2KV perf. Criteria BIEC/EN61000-4-4 ±4KV (See Fig. 2 for recommended circuit) perf. Criteria B SurgeIEC/EN61000-4-5 ±1KV perf. Criteria BIEC/EN61000-4-5 ±2KV/±4KV (See Fig. 2 for recommended circuit) perf. Criteria B CS IEC/EN61000-4-6 10 Vr.m.s perf. Criteria A PFM IEC/EN61000-4-8 10A/m perf. Criteria A V oltage dips, short interruptions andvoltage variations immunityIEC/EN61000-4-11 0%-70% perf. Criteria BProduct Characteristic Curve-25 0 55 701007075O u t p u t P o w e r P e r c e n t a g e (%)Amb ie nt T e mp e ra ture ()℃T empe rature Dera ting Curve100~264VAC 120~370VDCInp ut vo lta g e:1007010085264120100370VAC VD C240340Input Volta ge De ra ting CurveAmb ie nt te m p e ra ture :25℃Inp ut Vo lta g eO u t p u t P o w e r P e r c e n t a g e (%)Note: Input voltage should be derated based on temperature derating when it is 85~100VAC/100~120VDC;This product is suitable for use in natural air cooling environments, if in a closed environment, please contact our company’s FAE.L D05-20B05MU50 55 6065 70 75 80 85 9095 100 85V110V120V220V240V264VE f f i c i e n c y (%)Input Voltage(V)E fficiency Vs Input Voltage (F ull L oad)L D05-20B05MU5055 6065 70 75 808590 10254050657590100E f f i c i e n c y (%)Output Cur r ent Per centage(%)E fficiency Vs Output L oad(Vin=230VAC)L D05-20B24MU50 556065 70 75 80 859095 100 85V110V120V220V240V264VE f f i c i e n c y (%)Input Voltage(V)E fficiency Vs Input Voltage (F ull L oad)L D05-20B24MU5055 6065 70 75 808590 10254050657590100E f f i c i e n c y (%)Output Cur r ent Per centage(%)E fficiency Vs Output L oad(Vin=230VAC)Design Reference1. T ypical application circuitAC (L )+Vo-VoA C (L )AC (N)AC(N)C 1C 2L O ADF US E AC /DCM O VN T CFig. 1: Typical application circuitModelC1(µF) C2(µF) LD05-20B05MU 1220 LD05-20B12MU 100 LD05-20B24MU47Note:Output filtering capacitor C2 is electrolytic capacitor, it is recommended to apply electrolytic capacitor with high frequency and low resistance. For capacitance and current of capacitor please refer to manufacture’s datasheet. Capacitance withstand voltage derating should be 80% or above. C1 is ceramic capacitor, which is used to filter high-frequency noise. External input NTC is recommended to use 5D-9. External input MOV is recommended to use S14K300. External input FUSE is recommended to use 2A/250V , slow blow.2. E MC solution-recommended circuitAC DCAC (N)AC (L)LCMM OVC XC Y1C Y2FUSEAC (N)AC (L)+Vo-Vo+L1C1C2R LC a n us e MO RNS UN’s FC -L X1DNT CFig 2: EMC Recommended circuit with higher requirementsElement modelRecommended valueMOV S14K300 CX 0.1µF/275V AC L1 4.7uH/2.0A CY1 1nF/400V AC CY2 1nF /400V ACNTC 5D-9LCM 2.2mH, recommended to use MORNSUN’s FL2D -10-222FUSE 2A/250V , slow blow, necessaryFC-LX1DEMC FilterDimensions and Recommended LayoutNote:1.If the product is not operated within the required load range, the product performance cannot be guaranteed to comply with all parameters in the datasheet;2.Unless otherwise specified, parameters in this datasheet were measured under the conditions of Ta = 25℃, humidity <75% with nominal input voltage andrated output load;3.All index testing methods in this datasheet are based on our Company’s corporate stan dards;4.The performance parameters of the product models listed in this manual are as above, but some parameters of non-standard model products may exceed therequirements mentioned above. Please contact our technicians directly for specific information;5.We can provide product customization service;6.Specifications are subject to change without prior notice.。

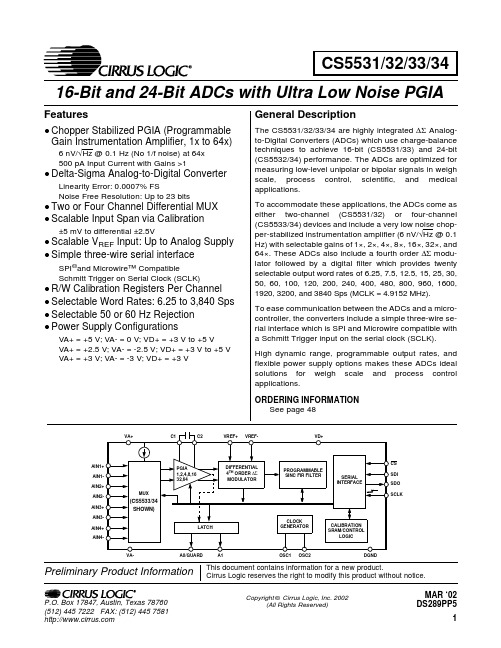

CS5532_DataSheet

Copyright ©Cirrus Logic,Inc.200278760CS5531/32/33/3416-Bit and 24-Bit ADCs with Ultra Low Noise PGIAMAR ‘02TABLE OF CONTENTS1.CHARACTERISTICS AND SPECIFICATIONS (5)ANALOG CHARACTERISTICS (5)TYPICAL RMS NOISE(NV),CS5531/32/33/34-AS (8)TYPICAL NOISE FREE RESOLUTION(BITS),CS5532/34-AS (8)TYPICAL RMS NOISE(NV),CS5532/34-BS (9)TYPICAL NOISE FREE RESOLUTION(BITS),CS5532/34-BS (9)5V DIGITAL CHARACTERISTICS (10)3V DIGITAL CHARACTERISTICS (10)DYNAMIC CHARACTERISTICS (11)ABSOLUTE MAXIMUM RATINGS (11)SWITCHING CHARACTERISTICS (12)2.GENERAL DESCRIPTION (14)2.1.Analog Input (14)2.1.1.Analog Input Span (15)2.1.2.Multiplexed Settling Limitations (15)2.1.3.Voltage Noise Density Performance (15)2.1.4.No Offset DAC (15)2.2.Overview of ADC Register Structure and Operating Modes (16)2.2.1.System Initialization (17)mand Register Quick Reference (19)mand Register Descriptions (20)2.2.4.Serial Port Interface (24)2.2.5.Reading/Writing On-Chip Registers (25)2.3.Configuration Register (25)2.3.1.Power Consumption (25)2.3.2.System Reset Sequence (25)2.3.3.Input Short (26)2.3.4.Guard Signal (26)2.3.5.Voltage Reference Select (26)2.3.6.Output Latch Pins (26)2.3.7.Offset and Gain Select (27)Contacting Cirrus Logic SupportFor a complete listing of Direct Sales,Distributor,and Sales Representative contacts,visit the Cirrus Logic web site at: /corporate/contacts/sales.cfmSPI is a registered trademark of International Business Machines Corporation.Microwire is a trademark of National Semiconductor Corporation.IMPORTANT NOTICE"Preliminary"product information describes products that are in production,but for which full characterization data is not yet available."Advance"product infor-mation describes products that are in development and subject to development changes.Cirrus Logic,Inc.and its subsidiaries("Cirrus")believe that the infor-mation contained in this document is accurate and reliable.However,the information is subject to change without notice and is provided"AS IS"without warranty of any kind(express or implied).Customers are advised to obtain the latest version of relevant information to verify,before placing orders,that information being relied on is current and complete.All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment,including those pertaining to warranty,patent infringement,and limitation of liability.No responsibility is assumed by Cirrus for the use of this information,including use of this information as the basis for manufacture or sale of any items,or for infringement of patents or other rights of third parties.This document is the property of Cirrus and by furnishing this information,Cirrus grants no license,express or implied under any patents,mask work rights,copyrights,trademarks,trade secrets or other intellectual property rights.Cirrus owns the copyrights of the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other parts of Cirrus.This consent does not extend to other copying such as copying for general distribution,advertising or promotional purposes,or for creating any work for resale.An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this ma-terial and controlled under the"Foreign Exchange and Foreign Trade Law"is to be exported or taken out of Japan.An export license and/or quota needs to be obtained from the competent authorities of the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign Trade Law and is to be exported or taken out of the PRC.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH,PERSONAL INJURY,OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE("CRITICAL APPLICATIONS").CIRRUS PRODUCTS ARE NOT DESIGNED,AUTHORIZED,OR WARRANT-ED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.Cirrus Logic,Cirrus,and the Cirrus Logic logo designs are trademarks of Cirrus Logic,Inc.All other brand and product names in this document may be trade-marks or service marks of their respective owners.2.3.8.Filter Rate Select (27)2.3.9.Configuration Register Descriptions (28)2.4.Setting up the CSRs for a Measurement (29)2.4.1.Channel-Setup Register Descriptions (30)2.5.Calibration (32)2.5.1.Calibration Registers (32)2.5.2.Gain Register (32)2.5.3.Offset Register (32)2.5.4.Performing Calibrations (33)2.5.5.Self Calibration (33)2.5.6.System Calibration (34)2.5.7.Calibration Tips (34)2.5.8.Limitations in Calibration Range (35)2.6.Performing Conversions (35)2.6.1.Single Conversion Mode (35)2.6.2.Continuous Conversion Mode (36)2.6.3.Examples of Using CSRs to Perform Conversions and Calibrations (37)ing Multiple ADCs Synchronously (38)2.8.Conversion Output Coding (38)2.8.1.Conversion Data Output Descriptions (39)2.9.Digital Filter (40)2.10.Clock Generator (41)2.11.Power Supply Arrangements (41)2.12.Getting Started (45)2.13.PCB Layout (45)3.PIN DESCRIPTIONS (46)Clock Generator (46)Control Pins and Serial Data I/O (46)Measurement and Reference Inputs (47)Power Supply Connections (47)4.SPECIFICATION DEFINITIONS (48)5.ORDERING GUIDE (48)6.PACKAGE DRAWINGS (49)LIST OF FIGURESFigure1.SDI Write Timing(Not to Scale) (13)Figure2.SDO Read Timing(Not to Scale) (13)Figure3.Multiplexer Configuration (14)Figure4.Input models for AIN+and AIN-pins (15)Figure5.Measured Voltage Noise Density (15)Figure6.CS5531/32/33/34Register Diagram (16)mand and Data Word Timing (24)Figure8.Guard Signal Shielding Scheme (26)Figure9.Input Reference Model when VRS=1 (27)Figure10.Input Reference Model when VRS=0 (27)Figure11.Self Calibration of Offset (34)Figure12.Self Calibration of Gain (34)Figure13.System Calibration of Offset (34)Figure14.System Calibration of Gain (34)Figure15.Synchronizing Multiple ADCs (38)Figure16.Digital Filter Response(Word Rate=60Sps) (40)Figure17.120Sps Filter Magnitude Plot to120Hz (40)Figure18.120Sps Filter Phase Plot to120Hz (40)Figure19.Z-Transforms of Digital Filters (40)Figure20.On-chip Oscillator Model (41)Figure21.CS5532Configured with a Single+5V Supply (42)Figure22.CS5532Configured with±2.5V Analog Supplies (43)Figure23.CS5532Configured with±3V Analog Supplies (43)Figure24.CS5532Configured for Thermocouple Measurement (44)Figure25.Bridge with Series Resistors (44)LIST OF TABLESTable1.Conversion Timing for Single Mode (36)Table2.Conversion Timing for Continuous Mode (37)mand Byte Pointer (37)Table4.Output Coding for16-bit CS5531and CS5533 (39)Table5.Output Coding for24-bit CS5532and CS5534 (39)1.CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS(VA+,VD+=5V ±5%;VREF+=5V;VA-,VREF-,DGND =0V;MCLK =4.9152MHz;OWR (Output Word Rate)=60Sps;Bipolar Mode;Gain =32)(See Notes 1and 2.)Notes: 1.Applies after system calibration at any temperature within -40°C ~+85°C.2.Specifications guaranteed by design,characterization,and/or test.LSB is 16bits for the CS5531/33andLSB is 24bits for the CS5532/34.3.This specification applies to the device only and does not include any effects by external parasiticthermocouples.The PGIA contributes 5nV of offset drift,and the modulator contributes 640/G nV of offset drift,where G is the amplifier gain setting.4.Drift over specified temperature range after calibration at power-up at 25°C.ParameterCS5531-AS/CS5533-ASUnit Min Typ Max Accuracy Linearity Error -±0.0015±0.003%FS No Missing Codes 16--Bits Bipolar Offset -±1±2LSB 16Unipolar Offset-±2±4LSB 16Offset Drift(Notes 3and 4)-640/G +5-nV/°C Bipolar Full Scale Error -±8±31ppm Unipolar Full Scale Error -±16±62ppm Full Scale Drift(Note 4)-2-ppm/°CParameterCS5532-AS/CS5534-ASCS5532-BS/CS5534-BS Unit Min Typ Max Min Typ Max Accuracy Linearity Error -±0.0015±0.003-±0.0007±0.0015%FS No Missing Codes 24--24--Bits Bipolar Offset -±16±32-±16±32LSB 24Unipolar Offset-±32±64-±32±64LSB 24Offset Drift(Notes 3and 4)-640/G +5--640/G +5-nV/°C Bipolar Full Scale Error -±8±31-±8±31ppm Unipolar Full Scale Error -±16±62-±16±62ppm Full Scale Drift(Note 4)-TBD--2-ppm/°CANALOG CHARACTERISTICS(Continued)(See Notes 1and 2.)Notes: 5.The voltage on the analog inputs is amplified by the PGIA,and becomes V CM ±Gain*(AIN+-AIN-)/2atthe differential outputs of the amplifier.In addition to the input common mode +signal requirements for the analog input pins,the differential outputs of the amplifier must remain between (VA-+0.1V)and (VA+-0.1V)to avoid saturation of the output stage.6.See the section of the data sheet which discusses input models.ParameterMinTypMaxUnitAnalog InputCommon Mode +Signal on AIN+or AIN-Bipolar/Unipolar ModeGain =1Gain =2,4,8,16,32,64(Note 5)VA-VA-+0.7--VA+VA+-1.7V V CVF Current on AIN+or AIN-Gain =1(Note 6)Gain =2,4,8,16,32,64--500500--nA pA Input Current Noise Gain =1Gain =2,4,8,16,32,64--2001--pA/√Hz pA/√Hz Input Leakage for Mux when Off (at 25°C)-10-pA Off-Channel Mux Isolation -120-dB Open Circuit Detect Current 100300-nA Common Mode Rejection dc,Gain =1dc,Gain =6450,60Hz ---90130120---dB dB dB Input Capacitance -60-pF Guard Drive Output -20-µA Voltage Reference Input Range (VREF+)-(VREF-)1 2.5(VA+)-(VA-)V CVF Current (Note 6)-500-nA Common Mode Rejection dc 50,60Hz --120120--dB dB Input Capacitance 11-22pF System Calibration Specifications Full Scale Calibration Range Bipolar/Unipolar Mode 3-110%FS Offset Calibration Range Bipolar Mode -100-100%FS Offset Calibration Range Unipolar Mode -90-90%FSANALOG CHARACTERISTICS(Continued)(See Notes 1and 2.)7.All outputs unloaded.All input CMOS levels.8.Power is specified when the instrumentation amplifier (Gain ≥2)is on.Analog supply current is reducedby approximately 1/2when the instrumentation amplifier is off (Gain =1).9.Tested with 100mV change on VA+or VA-.ParameterCS5531/32/33/34-AS CS5532/34-BS MinTypMaxMinTypMaxUnitPower SuppliesDC Power Supply Currents (Normal Mode)I A+,I A-I D+--60.581--130.5151mA mA Power ConsumptionNormal Mode (Notes 7and 8)Standby Sleep---35350045-----70450080--mW mW µW Power Supply Rejection(Note 9)dc Positive Supplies dc Negative Supply--115115----115115--dB dBTYPICAL RMS NOISE (nV),CS5531/32/33/34-AS (See notes 10,11and 12)Notes:10.Wideband noise aliased into the baseband.Referred to the input.Typical values shown for 25°C.11.For Peak-to-Peak Noise multiply by 6.6for all ranges and output rates.12.Word rates and -3dB points with FRS =0.When FRS =1,word rates and -3dB points scale by 5/6.TYPICAL NOISE FREE RESOLUTION(BITS),CS5532/34-AS (See Notes 13and 14)13.Noise Free Resolution listed is for Bipolar operation,and is calculated as LOG((Input Span)/(6.6xRMSNoise))/LOG(2)rounded to the nearest bit.For Unipolar operation,the input span is 1/2as large,so one bit is lost.The input span is calculated in the analog input span section of the data sheet.The Noise Free Resolution table is computed with a value of 1.0in the gain register.Values other than 1.0will scale the noise,and change the Noise Free Resolution accordingly.14.“Noise Free Resolution”is not the same as “Effective Resolution”.Effective Resolution is based on theRMS noise value,while Noise Free Resolution is based on a peak-to-peak noise value specified as 6.6times the RMS noise value.Effective Resolution is calculated as LOG((Input Span)/(RMS Noise))/LOG(2).Specifications are subject to change without notice.Output Word Rate (Sps)-3dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.9417171926427915515 3.882425273659111218307.7534353951841573086015.548495472118222436120316870771021673146162406211516027652710402070415048012216323039274814802950589096023022932155410602090417083401,920390344523946184036507290146003,84078013902710539010800215004300086100Output Word Rate (Sps)-3dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.941920212222222215 3.8819202121212222307.75181920212121216015.5181920202021211203117181920202020240621617171717171748012216171717171717960230151616161616161,920390151515151515153,84078013131313131313TYPICAL RMS NOISE (nV),CS5532/34-BS (See notes 15,16,17and 18)Notes:15.The -B devices provide the best noise specifications.16.Wideband noise aliased into the baseband.Referred to the input.Typical values shown for 25°C.17.For Peak-to-Peak Noise multiply by 6.6for all ranges and output rates.18.Word rates and -3dB points with FRS =0.When FRS =1,word rates and -3dB points scale by 5/6.TYPICAL NOISE FREE RESOLUTION(BITS),CS5532/34-BS (See Notes 19and 20)19.Noise Free Resolution listed is for Bipolar operation,and is calculated as LOG((Input Span)/(6.6xRMSNoise))/LOG(2)rounded to the nearest bit.For Unipolar operation,the input span is 1/2as large,so one bit is lost.The input span is calculated in the analog input span section of the data sheet.The Noise Free Resolution table is computed with a value of 1.0in the gain register.Values other than 1.0will scale the noise,and change the Noise Free Resolution accordingly.20.“Noise Free Resolution”is not the same as “Effective Resolution”.Effective Resolution is based on theRMS noise value,while Noise Free Resolution is based on a peak-to-peak noise value specified as 6.6times the RMS noise value.Effective Resolution is calculated as LOG((Input Span)/(RMS Noise))/LOG(2).Specifications are subject to change without notice.Output Word Rate (Sps)-3dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.948.59101526509915 3.88121315213770139307.751718213052991966015.524252942731402771203134364259103198392240628013626051410202050409048012211319436973014502900581096023015927452310302060411082301,920390260470912181036207230145003,84078013602690538010800215004300086000Output Word Rate (Sps)-3dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.942021222323232315 3.8820212222222222307.75192021222222226015.5192021212121211203118192021212121240621717181818181848012217171717171717960230161617171717171,920390161616161616163,840780131313131313135V DIGITAL CHARACTERISTICS (VA+,VD+=5V ±5%;VA-,DGND =0V;See Notes 2and 21.)3V DIGITAL CHARACTERISTICS (T A =25°C;VA+=5V ±5%;VD+=3.0V±10%;VA-,DGND =0V;See Notes 2and 21.)21.All measurements performed under static conditions.ParameterSymbol Min Typ Max Unit High-Level Input Voltage All Pins Except SCLKSCLK V IH 0.6VD+(VD+)-0.45--VD+VD+V Low-Level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-Level Output Voltage A0and A1,I out =-1.0mASDO,I out =-5.0mA V OH (VA+)-1.0(VD+)-1.0--V Low-Level Output Voltage A0and A1,I out =1.0mASDO,I out =5.0mAV OL --(VA-)+0.40.4V Input Leakage Current I in -±1±10µA SDO 3-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFParameterSymbol Min Typ Max Unit High-Level Input Voltage All Pins Except SCLKSCLK V IH 0.6VD+(VD+)-0.45-VD+VD+V Low-Level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-Level Output Voltage A0and A1,I out =-1.0mASDO,I out =-5.0mA V OH (VA+)-1.0(VD+)-1.0--V Low-Level Output Voltage A0and A1,I out =1.0mASDO,I out =5.0mAV OL --(VA-)+0.40.4V Input Leakage Current I in -±1±10µA SDO 3-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFDYNAMIC CHARACTERISTICS22.The ADCs use a Sinc 5filter for the 3200Sps and 3840Sps output word rate (OWR)and a Sinc 5filterfollowed by a Sinc 3filter for the other OWRs.OWR sinc5refers to the 3200Sps (FRS =1)or 3840Sps (FRS =0)word rate associated with the Sinc 5filter.23.The single conversion mode only outputs fully settled conversions.See Table 1for more details aboutsingle conversion mode timing.OWR SC is used here to designate the different conversion time associated with single conversions.24.The continuous conversion mode outputs every conversion.This means that the filter’s settling timewith a full scale step input in the continuous conversion mode is dictated by the OWR.ABSOLUTE MAXIMUM RATINGS(DGND =0V;See Note 25.)Notes:25.All voltages with respect to ground.26.VA+and VA-must satisfy {(VA+)-(VA-)}≤+6.6V.27.VD+and VA-must satisfy {(VD+)-(VA-)}≤ +7.5V.28.Applies to all pins including continuous overvoltage conditions at the analog input (AIN)pins.29.Transient current of up to 100mA will not cause SCR latch-up.Maximum input current for a power supply pin is ±50mA.30.Total power dissipation,including all input currents and output currents.WARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.ParameterSymbol Ratio Unit Modulator Sampling Ratef s MCLK/16Sps Filter Settling Time to 1/2LSB (Full Scale Step Input)Single Conversion mode (Notes 22,23,and 24)Continuous Conversion mode,OWR <3200Sps Continuous Conversion mode,OWR ≥3200Spst s t s t s1/OWR SC5/OWR sinc5+3/OWR5/OWRs s sParameterSymbolMin Typ Max Unit DC Power Supplies(Notes 26and 27)Positive Digital Positive Analog Negative Analog VD+VA+VA--0.3-0.3+0.3---+6.0+6.0-3.75V V V Input Current,Any Pin Except Supplies (Notes 28and 29)I IN --±10mA Output Current I OUT --±25mA Power Dissipation (Note 30)PDN --500mW Analog Input Voltage VREF pins AIN PinsV INR V INA (VA-)-0.3(VA-)-0.3--(VA+)+0.3(VA+)+0.3V V Digital Input VoltageV IND -0.3-(VD+)+0.3V Ambient Operating Temperature T A -40-85°C Storage T emperature T stg-65-150°CSWITCHING CHARACTERISTICS (VA+=2.5V or 5V ±5%;VA-=-2.5V±5%or 0V;VD+=3.0V±10%or 5V ±5%;DGND =0V;Levels:Logic 0=0V,Logic 1=VD+;C L =50pF;See Figures 1and 2.)Notes:31.Device parameters are specified with a 4.9152MHz clock.32.Specified using 10%and 90%points on waveform of interest.Output loaded with 50pF.33.Oscillator start-up time varies with crystal parameters.This specification does not apply when using anexternal clock source.ParameterSymbol MinTypMaxUnitMaster Clock Frequency (Note 31)External Clock or Crystal OscillatorMCLK1 4.91525MHz Master Clock Duty Cycle 40-60%Rise Times(Note 32)Any Digital Input Except SCLKSCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times(Note 32)Any Digital Input Except SCLKSCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up Time XTAL =4.9152MHz(Note 33)t ost-20-ms Serial Port Timing Serial Clock Frequency SCLK 0-2MHz Serial Clock Pulse Width High Pulse Width Lowt 1t 2250250----ns nsSDI Write TimingCS Enable to Valid Latch Clock t 350--ns Data Set-up Time prior to SCLK rising t 450--ns Data Hold Time After SCLK Rising t 5100--ns SCLK Falling Prior to CS Disable t 6100--nsSDO Read Timing CS to Data Validt 7--150ns SCLK Falling to New Data Bit t 8--150ns CS Rising to SDO Hi-Zt 9--150nsFigure1.SDI Write Timing(Not toScale)2.GENERAL DESCRIPTIONThe CS5531/32/33/34are highly integrated∆ΣAn-alog-to-Digital Converters(ADCs)which use charge-balance techniques to achieve16-bit (CS5531/33)and24-bit(CS5532/34)performance. The ADCs are optimized for measuring low-level unipolar or bipolar signals in weigh scale,process control,scientific,and medical applications.To accommodate these applications,the ADCs come as either two-channel(CS5531/32)or four-channel(CS5533/34)devices and include a very low noise chopper-stabilized programmable gain instrumentation amplifier(PGIA,6nV/√Hz@0.1 Hz)with selectable gains of1×,2×,4×,8×,16×, 32×,and64×.These ADCs also include a fourth or-der∆Σmodulator followed by a digital filter which provides twenty selectable output word rates of6.25, 7.5,12.5,15,25,30,50,60,100,120,200,240,400, 480,800,960,1600,1920,3200,and3840Samples per second(MCLK=4.9152MHz).To ease communication between the ADCs and a micro-controller,the converters include a simple three-wire serial interface which is SPI and Mi-crowire compatible with a Schmitt Trigger input on the serial clock(SCLK).2.1.Analog InputFigure3illustrates a block diagram of the CS5531/32/33/34.The front end consists of a multi-plexer,a unity gain coarse/fine charge input buffer, and a programmable gain chopper-stabilized instru-mentation amplifier.The unity gain buffer is activat-ed any time conversions are performed with a gain of one and the instrumentation amplifier is activated any time conversions are performed with gain set-tings greater than one.The unity gain buffer is designed to accommodate rail to rail input signals.The common-mode plus signal range for the unity gain buffer amplifier is VA-to VA+.Typical CVF(sampling)current for the unity gain buffer amplifier is about500nA (MCLK=4.9152MHz,see Figure4).The instrumentation amplifier is chopper-stabi-lized and operates with a chop clock frequency of MCLK/128.The CVF(sampling)current into the instrumentation amplifier is typically500pA overFigure3.Multiplexer Configuration-40°C to+85°C(MCLK=4.9152MHz).The com-mon-mode plus signal range of the instrumentation amplifier is(VA-)+0.7V to(VA+)-1.7V. Figure4illustrates the input models for the ampli-fiers.The dynamic input current for each of the pins can be determined from the models shown. Note:The C=2.5pF and C=16pF capacitors are for input current modeling only.For physicalinput capacitance see‘Input Capacitance’specification under Analog Characteristics.2.1.1.Analog Input SpanThe full scale input signal that the converter can dig-itize is a function of the gain setting and the refer-ence voltage connected between the VREF+and VREF-pins.The full scale input span of the convert-er is((VREF+)-(VREF-))/(GxA),where G is the gain of the amplifier and A is2for VRS=0,or A is 1for VRS=1.VRS is the Voltage Reference Select bit,and must be set according to the differential volt-age applied to the VREF+and VREF-pins on the part.See section2.3.5for more details.After reset,the unity gain buffer is engaged.With a 2.5V reference this would make the full scale input range default to2.5V.By activating the instrumen-tation amplifier(i.e.a gain setting other than1)and using a gain setting of32,the full scale input range can quickly be set to2.5/32or about78mV.Note that these input ranges assume the calibration regis-ters are set to their default values(i.e.Gain=1.0and Offset=0.0).2.1.2.Multiplexed Settling LimitationsThe settling performance of the CS5531/32/33/34 in multiplexed applications is affected by the sin-gle-pole low-pass filter which follows the instru-mentation amplifier(see Figure3).To achieve data sheet settling and linearity specifications,it is rec-ommended that a22nF C0G capacitor be used.Ca-pacitors as low as10nF or X7R type capacitors can also be used with some minor increase in distortion for AC signals.2.1.3.Voltage Noise Density Performance Figure5illustrates the measured voltage noise den-sity versus frequency from0.01Hz to10Hz of a CS5532-BS.The device was powered with±2.5V supplies,using120Sps OWR,the64x gain range, bipolar mode,and with the input short bit enabled.2.1.4.No Offset DACAn offset DAC was not included in the CS553X family because the high dynamic range of the con-verter eliminates the need for one.The offset regis-Figure4.Input models for AIN+and AIN-pinster can be manipulated by the user to mimic the function of a DAC if desired.2.2.Overview of ADC Register Structure and Operating ModesThe CS5531/32/33/34ADCs have an on-chip con-troller,which includes a number of user-accessible registers.The registers are used to hold offset and gain calibration results,configure the chip's operat-ing modes,hold conversion instructions,and to store conversion data words.Figure6depicts a block diagram of the on-chip controller’s internal registers.Each of the converters has32-bit registers to func-tion as offset and gain calibration registers for each channel.The converters with two channels have two offset and two gain calibration registers,the converters with four channels have four offset and four gain calibration registers.These registers hold calibration results.The contents of these registers can be read or written by the user.This allows cal-ibration data to be off-loaded into an external EE-PROM.The user can also manipulate the contents of these registers to modify the offset or the gain slope of the converter.The converters include a32-bit configuration reg-ister which is used for setting options such as the power down modes,resetting the converter,short-ing the analog inputs,and enabling diagnostic test bits like the guard signal.A group of registers,called Channel Setup Regis-ters,are used to hold pre-loaded conversion in-structions.Each channel setup register is32bits long,and holds two16-bit conversion instructions referred to as Setups.Upon power up,these regis-ters can be initialized by the system microcontrol-ler with conversion instructions.The user can then instruct the converter to perform single or multiple conversions or calibrations with the converter in the mode defined by one of these Setups.Figure6.CS5531/32/33/34Register DiagramUsing the single conversion mode,an8-bit com-mand word can be written into the serial port.The command includes pointer bits which‘point’to a 16-bit command in one of the Channel Setup Reg-isters which is to be executed.The16-bit Setups can be programmed to perform a conversion on any of the input channels of the converter.More than one of the16-bit Setups can be used for the same analog input channel.This allows the user to con-vert on the same signal with either a different con-version speed,a different gain range,or any of the other options available in the channel setup regis-ters.Alternately,the user can set up the registers to perform different conversion conditions on each of the input channels.The ADCs also include continuous conversion ca-pability.The ADCs can be instructed to continu-ously convert,referencing one16-bit command Setup.In the continuous conversions mode,the conversion data words are loaded into a shift regis-ter.The converter issues a flag on the SDO pin when a conversion cycle is completed so the user can read the register,if need be.See the section on Performing Conversions for more details.The following pages document how to initialize the converter,perform offset and gain calibrations,and how to configure the converter for the various con-version modes.Each of the bits of the configuration register and of the Channel Setup Registers is de-scribed.A list of examples follows the description section.Also the Command Register Quick Refer-ence can be used to decode all valid commands(the first8-bits into the serial port).2.2.1.System InitializationThe CS5531/32/33/34provide no power-on-reset function.To initialize the ADCs,the user must per-form a software reset by resetting the ADC’s serial port with the Serial Port Initialization sequence. This sequence resets the serial port to the command mode and is accomplished by transmitting at least 15SYNC1command bytes(0xFF hexadecimal),followed by one SYNC0command(0xFE hexa-decimal).Note that this sequence can be initiated at anytime to reinitialize the serial port.To complete the system initialization sequence,the user must also perform a system reset sequence which is as follows:Write a logic1into the RS bit of the con-figuration register.This will reset the calibration registers and other logic(but not the serial port).A valid reset will set the RV bit in the configuration register to a logic1.After writing the RS bit to a logic1,wait20microseconds,then write the RS bit back to logic0.While this involves writing an en-tire word into the configuration register,the RV bit is a read only bit,therefore a write to the configu-ration register will not overwrite the RV bit.After clearing the RS bit back to logic0,read the config-uration register to check the state of the RV bit as this indicates that a valid reset occurred.Reading the configuration register clears the RV bit back to logic0.Completing the reset cycle initializes the on-chip registers to the following states:Note:Previous datasheets stated that the RS bit would clear itself back to logic0and thereforethe user was not required to write the RS bitback to logic0.The current data sheetinstruction that requires the user to write intothe configuration register to clear the RS bithas been added to insure that the RS bit iscleared.Characterization across multiple lotsof silicon has indicated some chips do notautomatically reset the RS bit to logic0in theconfiguration register,although the resetfunction is completed.This occurs only onsmall number of chips when the VA-supply isnegative with respect to DGND.This has notcaused an operational issue for customersbecause their start-up sequence includeswriting a word(with RS=0)into theconfiguration register after performing areset.The change in the reset sequence to Configuration Register:00000000(H)Offset Registers:00000000(H)Gain Registers:01000000(H)Channel Setup Registers:00000000(H)。

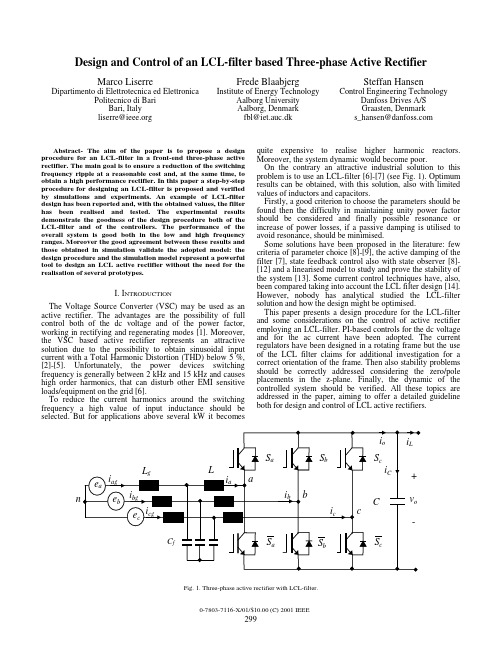

Design and Control of an LCL-filter based Three-phase Active Rectifier

I. INTRODUCTION The Voltage Source Converter (VSC) may be used as an active rectifier. The advantages are the possibility of full control both of the dc voltage and of the power factor, working in rectifying and regenerating modes [1]. Moreover, the VSC based active rectifier represents an attractive solution due to the possibility to obtain sinusoidal input current with a Total Harmonic Distortion (THD) below 5 %, [2]-[5]. Unfortunately, the power devices switching frequency is generally between 2 kHz and 15 kHz and causes high order harmonics, that can disturb other EMI sensitive loads/equipment on the grid [6]. To reduce the current harmonics around the switching frequency a high value of input inductance should be selected. But for applications above several kW it becomes

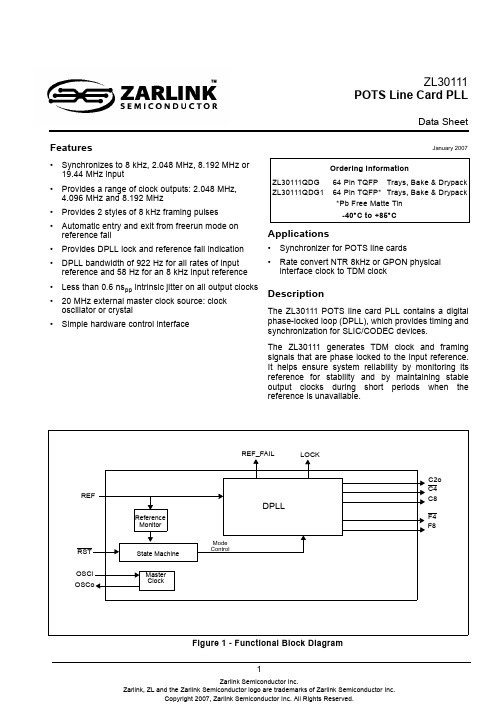

zl30111中文资料_数据手册_IC数据表