TS112N中文资料

山东省医学科学院中文核心期刊目录(447种)

86

情报学报

11-2257

1000-0135

中国科技情报学会

中国科技信息研究所

北京复兴路15号

87

软件学报

11-2560/TP

1000-9825

中国科学院(软件所)

中国计算机学会等

北京海淀区中关村南4街4号

88

山东大学学报.社科版

37-1100/C

1001-9839

中华人民共和国教育部

中华预防医学会等

天津市河东区华龙道76号

33

环境与职业医学

31-1879/R

1006-3617

上海市卫生局

上海疾病预防控制中心

上海市中兴路1105号

34

基础医学与临床

11-2652/R

1001-6325

北京市卫生局

北京生理科学会

北京东单三条5号

35

疾病控制杂志

34-1188/R

1008-6013

中华预防医学会

山东省医学科学院中文核心期刊目录(447种)

序

号

刊 名

国内统一

刊号CN

国际出版物号ISSN

主管单位

主办单位

编辑部地址

1

癌变.畸变.突变

44-1063/R

1004-616X

中国科学技术协会

中国环境诱变剂学会

广东省汕头市新陵路22号

2

安全健康和环境

37-1388/X

1672-7932

中化安全卫生技术协会

中国科学院

中科院计算技术研究所

北京中关村科学院南路6号

39

计算机应用

51-1307/TP

1001-9081

HGTG11N120CN中文资料

Data Sheet

HGTG11N120CN, HGTP11N120CN, HGT1S11N120CNS

December 2001

43A, 1200V, NPT Series N-Channel IGBT

The HGTG11N120CN, HGTP11N120CN, and HGT1S11N120CNS are Non-Punch Through (NPT) IGBT designs. They are new members of the MOS gated high voltage switching IGBT family. IGBTs combine the best features of MOSFETs and bipolar transistors. This device has the high input impedance of a MOSFET and the low onstate conduction loss of a bipolar transistor.

At TC = 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IC25 At TC = 110oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IC110 Collector Current Pulsed (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ICM Gate to Emitter Voltage Continuous. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGES Gate to Emitter Voltage Pulsed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGEM Switching Safe Operating Area at TJ = 150oC (Figure 2) . . . . . . . . . . . . . . . . . . . . . . . SSOA Power Dissipation Total at TC = 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD Power Dissipation Derating TC > 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Forward Voltage Avalanche Energy (Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . EAV Operating and Storage Junction Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . TJ, TSTG Maximum Lead Temperature for Soldering Leads at 0.063in (1.6mm) from case for 10s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TL Package Body for 10s, see Tech brief 334. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Tpkg Short Circuit Withstand Time (Note 3) at VGE = 15V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . tSC Short Circuit Withstand Time (Note 3) at VGE = 12V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . tSC

IDS112中文资料

Single OutputBlock DiagramHigh efficiency, wide input voltage range and low output noise define IDS Series of non-isolated, step-down, switching DC/DC converters.The 3.3V and 5V output devices are respectively up to 93% efficiency.All models are fully line and load regulated and maintain specified accuracy over the impressively wide input voltage ranges of 4.75 to 13.6V for 3.3V output, 6 to 16.5V for 5V output and 16 to 28V for 3.3V and 5V outputs.Output ripple and noise are typically 30mV P-P.The high efficiency of the IDS Series eliminates the need for thermally conductive potting compound. Devices are specified for full-power operation up to ambient temperatures of +70] Calculated MTBF (MIL-HDBK-217F)is more than 1.5 million hours.These simple-to-use power converters have no minimum load requirements. They draw 1mA when unloaded and a mere 100uA in the standby mode (On/Off Control turns off).3.3V models have an output voltage adjustment range from 1.8 to 3.3V and 5V models are adjustable down to 3.0V.y Standby Current 100uA onlyy Overload Protectiony Step-down Switching Regulator y Temperature Performance -25] to +70]y Low Output Noisey Remote On/Off Control y Low Costy MTBF > 1,500,000 Hours y Output Current up to 2A y Efficiency up To 93%Key Features10W, Step-Down, Single Output DC/DC ConvertersIDS100 Series8549020020005IDS122834533120020003.324( 16 ~ 28 )IDS12193278962002000512( 6 ~ 16.5 )IDS1129221143420020003.35( 4.75 ~ 13.6 )IDS101% (Typ.)mA (Typ.)mA (Typ.)mA mA VDC VDC@Max. Load @No Load @Max. Load Min.Max.EfficiencyInput CurrentOutput CurrentOutput VoltageInput VoltageModel NumberModel Selection GuideFree-Air ConvectionCooling%95---Humidity ]+125-25Storage Temperature ]+70-25AmbientOperating Temperature Unit Max.Min.Conditions ParameterEnvironmental SpecificationsExceeding the absolute maximum ratings of the unit could cause damage.These are not continuous operating ratings.mW1500---Internal Power Dissipation]235---Lead Temperature (1.5mm from case for 10 Sec.)VDC 30-0.724VDC Input ModelsVDC 25-0.712VDC Input ModelsVDC 16-0.75VDC Input ModelsInput Surge Voltage( 1000 mS )Unit Max.Min.ParameterNotes :1. Specifications typical at Ta=+25], resistive load,nominal input voltage, rated output current unless otherwise noted.2. Transient recovery time is measured to within 1%error band for a step change in output load of 50%to 100%.3. Ripple & Noise measurement bandwidth is 0-20MHz.4. These power converters require a minimum output loading to maintain specified regulation.5. Operation under no-load conditions will not damage these modules; however, they may not meet all specifications listed.6. All DC/DC converters should be externally fused at the front end for protection.7. Other input and output voltage may be available,please contact factory.8. Specifications subject to change without notice.Absolute Maximum Ratings15---1224V Input Models6---5.512V Input Models VDC 3.9---3.55V Input Models Start VoltageUnitMax.Typ.Min.Model ParameterInput SpecificationsIDS100 SeriesContinuousOutput Short Circuit%/]{0.02{0.01---Temperature Coefficient %{4{2---Transient Response Deviation uS 150100---50% Load Step Change Transient Recovery Time %------120Over LoadmV rms 15------Ripple & Noise (20MHz)mV P-P 120------Over Line, Load & Temp.Ripple & Noise (20MHz)mV P-P 5030---Ripple & Noise (20MHz)%{1.5{0.5---Io=0% to 100%Load Regulation %{0.5{0.2---Vin=Min. to Max.Line Regulation %{2.0{1.0---Output Voltage Accuracy Unit Max.Typ.Min.ConditionsParameterOutput SpecificationsK Hours------1500MIL-HDBK-217F @ 25], Ground BenignMTBFKHz ---300---Switching Frequency none Isolation Voltage UnitMax.Typ.Min.ConditionsParameterGeneral SpecificationsReferenced to Negative InputControl CommonuA-100------Control Input Current ( off )uA 50------Control Input Current ( on )uA 300100---Device Standby Input Current VDC 1.2----0.3Supply OffVDC 3.0 to 5.0VDC or Open CircuitSupply On Unit Max.Typ.Min.ConditionsParameterRemote On/Off ControlVDC5---3IDS112, IDS122VDC 3.3---1.8IDS101, IDS121Trim Down RangeUnit Max.Typ.Min.Models ParameterOutput Voltage Trim1000mA Slow - Blow Type3000mA Slow - Blow Type4000mA Slow - Blow Type24V Input Models 12V Input Models 5V Input Models Input Fuse Selection GuideIDS100 SeriesDerating Curve]Ambient TemperatureO u t p u t P o w e r (%)020406080100-255060801001109070IDS100 SeriesTest ConfigurationsPeak-to-Peak Output Noise Measurement Test Use a Cout 4.7uF ceramic capacitor.Scope measurement should be made by using a BNC socket, measurement bandwidth is 0-20 MHz. Position the load between 50 mm and 75 mm from the DC/DC Converter.Remote On/OffPositive logic remote on/off turns the module on during a logic high voltage on the remote on/off pin, and off during a logic low.Negative logic remote on/off turns the module off during a logic low and on during a logic high.To turn the power module on and off, the user must supply a switch to control the voltage between the on/off terminal and the -Vin terminal.The switch can be an open collector or equivalent.A logic low is -0.3V to 1.2V.A logic high is 3.0V to 5.0V.The maximum sink current at on/off terminal during a logic low is -100 uA.The maximum allowable leakage current of the switch at on/off terminal (3.0 to 5.0V) is 50uA.Overcurrent ProtectionTo provide protection in a fault (output overload) condition, the unit is equipped with internal current limiting circuitry and can endure current limiting for an unlimited duration. At the point of current-limit inception, the unit shifts from voltage control to current control. The unit operates normally once the output current is brought back into its specified range. Output Ripple ReductionA good quality low ESR capacitor placed as close as practicable across the load will give the best ripple and noise performance.To reduce output ripple, it is recommended to use 22uF capacitors at the output.Input Source ImpedanceThe power module should be connected to a lowac-impedance input source. Highly inductive source impedances can affect the stability of the power module.In applications where power is supplied over long lines andoutput loading is high, it may be necessary to use a capacitor at the input to ensure startup.Capacitor mounted close to the power module helps ensure stability of the unit, it is recommended to use a good quality low Equivalent Series Resistance (ESR < 1.0[ at 100 KHz) capacitor of a 100uF for the 5V input devices and a 33uF for the 12V and 24V devices.Connecting the external resistor (Radj) between the Vadj and +Vout pins decreases the output voltage to set the point as defined in the following equation:Thermal ConsiderationsMany conditions affect the thermal performance of the power module, such as orientation, airflow over the module and board spacing. To avoid exceeding the maximum temperature rating of the components inside the power module, the ambient temperature must be kept below 70°C.The derating curves are determined from measurements obtained in an experimental apparatus.IDS100 SeriesLeads are tin plated for improved solderability.235] max./10sec:Soldering temperature8.6g:Weight Trim5+Vout 4Acceleration 20G max. time 11 ms :Shock -Vin 3+Vin 210 to 55Hz acceleration 2G Remote On/Off1 5 to 10Hz amplitude 10mm pk-pk :Vibration Function Pin Physical CharacteristicsPin Connections{0.002{0.05PinX.XXX{0.005X.XX{0.13X.XX{0.01X.X{0.25。

电源管理芯片DK112中文资料

电源管理芯⽚DK112中⽂资料功能描述DK112芯⽚是专⽤⼩功率开关电源控制芯⽚,⼴泛⽤于电源适配器、LED电源、电磁炉、空调、DVD等⼩家电产品。

⼀、产品特点采⽤双芯⽚设计,⾼压开关管采⽤双极型晶体管设计,以降低产品成本;控制电路采⽤⼤规模MOS数字电路设计,并采⽤E极驱动⽅式驱动双极型晶体芯⽚,以提⾼⾼压开关管的安全耐压值。

内建⾃供电电路,不需要外部给芯⽚提供电源,有效的降低外部元件的数量及成本。

芯⽚内集成了⾼压恒流启动电路,⽆需外部加启动电阻。

内置过流保护电路,防过载保护电路,输出短路保护电路,温度保护电路及光藕失效保护电路。

内置斜坡补偿电路,保证在低电压及⼤功率输出时的电路稳定。

内置PWM振荡电路,并设有抖频功能,保证了良好的EMC特性。

内置变频功能,待机时⾃动降低⼯作频率,在满⾜欧洲绿⾊能源标准(<0.3W)同时,降低了输出电压的纹波。

内置⾼压保护,当输⼊母线电压⾼于保护电压时,芯⽚将⾃动关闭并进⾏延时重启。

内建斜坡电流驱动电路,降低了芯⽚的功耗并提⾼了电路的效率。

4KV防静电ESD测试。

⼆、功率范围输⼊电压(85~264V ac)(85~145V ac)(180~264V ac)最⼤输出功率12W18W18W三、封装与引脚定义引脚符号功能描述1Gnd接地引脚。

2Gnd接地引脚。

3Fb反馈控制端。

4Vcc供电引脚。

5678Collector输出引脚,连接芯⽚内⾼压开关管Collector端,与开关变压器相连。

四、内部电路框图五、极限参数供电电压Vcc...........................................-0.3V--9V供电电流Vcc...........................................100mA引脚电压...........................................-0.3V--Vcc+0.3V 开关管耐压...........................................-0.3V--780V 峰值电流...........................................800mA总耗散功率...........................................1000mW⼯作温度...........................................0℃--125℃储存温度...........................................-55℃--+150℃焊接温度...........................................+280℃/5S六、电⽓参数项⽬测试条件最⼩典型最⼤单位电源电压Vcc AC输⼊85V-----265V456V启动电压AC输⼊85V-----265V 4.85 5.2V关闭电压AC输⼊85V-----265V 3.64 4.2V电源电流Vcc=5V,Fb=2.2V203040mA 启动时间AC输⼊85V------500mS Collector保护电压L=1.2mH460480500V开关管耐压Ioc=1mA700------V开关管电流Vcc=5V,Fb=1.6V----3.6V600650700mA 峰值电流保护Vcc=5V,Fb=1.6V----3.6V650720800mA 振荡频率Vcc=5V,Fb=1.6V----2.8V606570KHz 变频频率Vcc=4.6V,Fb=2.8V----3.6V0.5--65KHz 抖频步进频率Vcc=4.6V,Fb=1.6V----2.8V0.81 1.2KHz 温度保护Vcc=4.6V,Fb=1.6V----3.6V120125130℃占空⽐Vcc=4.6V,Fb=1.6V----3.6V5---50%控制电压Fb AC输⼊85V-----265V 1.6--- 3.6V七、⼯作原理上电启动:当外部电源上电时,直流⾼压经开关变压器传⾄芯⽚的COLLECTOR端(5678引脚),后经内建⾼压恒流启动电路将启动电流送⾄开关管Q1的B极,通过开关管Q1的电流放⼤(约为20倍放⼤)进⼊电源管理电路经D1为Vcc外部电容C1充电,同时为Fb预提供⼀个3.6V电压(Fb引脚对地应接⼊⼀只滤波电容),当Vcc的电压逐步上升⾄5V时,振荡器起振,电路开始⼯作,控制器为Fb开启⼀个约为25uA的对地电流源,电路进⼊正常⼯作。

【研究】NS112(Incoloy 800)成分、性能、参数...

上海钢研-张工:158–O185-9914一、概述NS112是一种与Incoloy 800同系列的全奥氏体低碳的镍-铁-铬合金,该合金中的钴含量可以严格控制在0.01%以下。

NS112能耐很多腐蚀介质腐蚀。

其较高的镍含量使其在水性腐蚀条件具有很好的抗应力腐蚀开裂性能。

高铬含量使之具有更好的耐点腐蚀和缝隙腐蚀开裂性能。

该合金具有很好的耐硝酸、有机酸腐蚀性,但是在硫酸和盐酸中的耐腐蚀性有限。

除了在卤化物有可能发生点腐蚀外,在氧化性和非氧化性盐中有很好的耐腐蚀性。

在水、蒸气以及蒸汽、空气、二氧化碳的混合物中也具有很好的耐腐蚀性。

应用于硝酸冷凝器——耐硝酸腐蚀、蒸汽加热管——很好的机械性能、加热元件管——很好的机械性能等。

对于应用于高达500℃的环境,合金供货态为退火态。

NS112物理性能:密度:ρ=8.0g/cm3熔化温度范围:1350~1400℃NS112机械性能:(在20℃检测机械性能的最小值)下表中所列性质适用于NS112合金的指定规格产品软化退火(稳定化退火)后的情况。

非标准尺寸材料的特殊性能可以根据特定应用场合的要求提供。

室温机械性能(最小值)高温机械性能(最小值)NS112具有以下特性:●在高达500℃的极高温的水性介质中具有出色的抗腐蚀性●很好的抗应力腐蚀的性能●很好的加工性NS112牌号和标准:NS112化学成分:NS112ISO V型缺口冲击试验:室温平均值:轴向>=150J/cm2 径向>=100J/cm2时间-温度-敏化曲线NS112条件应力值:达到90%屈服强度的高条件应力值可应用于允许略大一点变形量的应用场合。

这些应力引起的永久应力会导致尺寸的变化,因此不推荐用于法兰和密封垫圈连接件。

NS112金相结构:NS112合金具有稳定的面心立方结构。

化学成分和恰当的热处理保证了耐腐蚀性不受敏化性的削弱。

NS112耐腐蚀性:NS112是一种通用的工程合金,在氧化和还原环境下都具有抗酸和碱金属腐蚀性能。

ASTME112中文修订版

金属平均晶粒度测定方法引言本标准规定了金属材料平均晶粒度的基本方法。

由于纯粹以晶粒几何图形为基础,与金属和合金本身无关。

因此,这些基本方法也可以用来测量非金属材料中晶粒、晶体和晶胞的平均尺寸。

如果材料的组织形貌非常接近某一个标准系列评级图,可以使用比较法。

测定平均晶粒度常用比较法,也可以用截点法和面积法。

但是,比较法不能用来测量单个晶粒。

1范围1.1 本标准规定了金属组织的平均晶粒度表示及评定的三种方法——比较法、面积法和截点法。

这些方法也适用于晶粒组织形貌与标准系列评级图相似的非金属材料。

这些方法主要适用于单相晶粒组织,但也适用于多相或多组元试样中特定类型组织的晶粒平均尺寸的测量。

1.2 本标准使用晶粒面积、晶粒直径、截线长度的单峰分布来测定式样的平均晶粒度。

这些分布近似正态分布。

本标准的测定方法不适用于双峰分布的晶粒度。

双峰分布的晶粒度参见标准E1181。

测定分布在细小晶粒基体上个别非常粗大的晶粒的方法参见E 930。

1.3本标准的测量方法仅适用平面晶粒度的测量,也就是试样截面显示出的二维晶度;不适用于试样三维晶粒,即立体晶粒尺寸的测量。

1.4 试验可采用与一系列标准晶粒度图谱进行对比的方法或者在简单模板上进行计数的方法。

利用半自动计数仪或自动图象分析仪测定晶粒尺寸的方法参见E 1382。

1.5本标准仅作为推荐性试验方法,它不能确定受检材料是否接收或适合使用的范围。

1.6 测量数值应用SI单位表示。

等同的英寸-英镑数值,如需标出,应在括号中列出近似值.1.7 本标准没有列出所有的安全事项,只是一些使用的注意事项。

本标准的使用者在使用前应掌握较合适的安全健康的操作规范和使用时限制的规章制度。

1.8 章节的顺序如下:2、参考文献2.1ASTM标准E3 金相试样的制备E7 金相学相关术语E407 金属和合金浅腐蚀的操作E562计数法计算体积分数的方法E691 通过多个实验室比较决定测试方法的精确度的方法E883 反射光显微照相指南E930 截面上最大晶粒的评估方法(ALA晶粒尺寸)E1181双峰分布的晶粒度测试方法E1382 半自动或全自动图像分析平均晶粒度方法2.2 ASTM附件2.2.1 参见附录X23术语3.1 定义-本标准采用的专业术语定义参照E73.2 本标准中特定术语的定义:3.2.1 ASTM晶粒度——G,通常定义如公式(1)N AE=2G-1 (1)N AE为100倍下每平方英寸(645.16mm2)面积内包含的晶粒个数,相当于1倍下每平方毫米面积内包含的晶粒个数乘以15.5倍。

112测量台V2.10EN版本发布说明

版本发布说明DT-SP30CN-112TEST-O-V2.10E大唐电信科技股份有限公司目录 一 版本概述 .................................................................................................................3 1.1 1.2 1.3 1.4 目的 .....................................................................................................................3 应用范围 .............................................................................................................3 版本文档清单.....................................................................................................3 约定 .....................................................................................................................3二 版本新增(扩展)功能说明 .................................................................................4 2.1 增加了指定远程局格式表的功能 ....................................................................4 三 版本兼容性说明 .....................................................................................................4 四 版本发布程序清单 .................................................................................................4 五 文档修改说明 .........................................................................................................5 六 使用注意事项 .........................................................................................................5一 版本概述1.1 目的本版本在 DT-SP30CN-112TEST-O-V2.00 版本的基础上生成,修改了原版本中存在的 问题,并增加了一些新功能以满足用户需求。

服装面料中英文对照大全

服装面料英语(一)001,里料:LINING 002,面料:FABRIC 003,平纹:TAFFETA 004,斜纹:TWILL 005,缎面:SATIN / CHARMEUSE 006,绡:LUSTRINE 007,提花:JACQUARD 008,烂花:BURNT-OUT 009,春亚纺:PONGEE 010,格子:CHECK 011,条子:STRIPE 012,双层:DOUBLE – LAYER 013,双色:TWO – TONE 014,花瑶: FAILLE 015,高士宝:KOSHIBO 016,雪纺:CHIFFON 017,乔其:GEORGETTE 018,塔丝隆:TASLON 019,弹力布:SPANDEX/ELASTIC/STREC/LYCRA 020,牛仔布:JEANET 021,牛津布:OXFORD 022,帆布:CAMBRIC 023,涤棉:P/C 024,涤捻:T/R 025,白条纺:WHITE STRIPE 026,黑条纺:BLACK STRIPE 027,空齿纺:EMPTY STRIPE 028,水洗绒/桃皮绒:PEACHSKIN 029,卡丹绒:PEACH TWILL 030,绉绒:PEACH MOSS 031,玻璃纱:ORGANDY 032,涤纶:PLOYESTER 033,锦纶:NYLON/POLYAMIDE 034,醋酸:ACETATE 035,棉; COTTON 036,人棉:RAYON 037,人丝:VISCOSE 038,仿真丝:IMITATED SILKFABRIC 039,真丝:SILK 040,氨纶:SPANDEX/ELASTIC/STREC/LYCRA 041,长丝:FILAMENT 042,短纤:SPUN 043,黑丝:BLACK YARN 044,阳离子:CATION 045,三角异形丝:TRIANGLE PROFILE 046,空气变形丝:AIR-JET TEXTURING YARN 047,超细纤维:MICRO –FIBRIC 048,全拉伸丝:FDY (FULL DRAWN YARN) 049,预取向丝:POY(PREORIENTEDYARN) 050,拉伸变形丝:DTY(DRAW TEXTURED YARN) 051,牵伸加捻丝: DT (DRWWTWIST)服装面料英语(二) 052,靛蓝青年布:Indigo chambray 053,人棉布植绒:Rayon cloth flocking054,PVC植绒:PVC flocking 055,针织布植绒:Knitting cloth flocking056,珠粒绒:Claimond veins 057,倒毛:Down pile making058,平绒:velveteen (velvet-plain) 059,仿麂皮:Micro suede060,牛仔皮植绒:Jeans flocking 061,尼丝纺:Nylon taffeta (Nylon shioze)062,尼龙塔夫泡泡纱:Nylon seersucker taffeta063,素面植绒:plain flocking 064,印花植绒:flocking(flower)065,雕印植绒:Embossingflocking 066,皮革沟底植绒:Leather imitationflocking 067,牛仔植绒雕印:Embossing jeans flocking 068,兔羊绒大衣呢:Angora cachmere overcoating 069,双面呢:double-faced woolen goods羊毛 070,立绒呢:cutvelvet 071,顺毛呢:over coating 072,粗花呢:costume tweed 073,弹力呢:lycra woolen goods 074,塔丝绒: Nylon taslon 075,塔丝绒格子:N/Taslon ripstop 076,桃皮绒:polyester peach skin 077,涤塔夫:polyester taffeta 078,春亚纺:polyester pongee079,超细麦克布:Micro fiber 080,锦棉稠(平纹):Nylon-cotton fabric (plain) 081,重平锦棉稠:Nylon-cotton-cotton fabric(double weft)082,人字锦棉纺:Nylon-cotton fabric 083,斜纹锦棉纺:Nylon-cotton fabric (twill) 084,素色天鹅绒:solid velvet 085,抽条磨毛天鹅绒:Rib fleece velvet 086,雪花天鹅绒:melangevelvet 087,轧花天鹅绒:ginning velvet088,粒粒绒布:pellet fleece velvet 089,麻棉混纺布:linen/cotton blended fabric 090,麻棉交织布:linen/cotton mixed fabric 091,素色毛巾布:solid terry 092,蚂蚁布:fleece in oneside 093,素色卫衣布:solid fleece094,鱼网布:fleece 095,彩条汗布:color-stripes single jersey 096,T/R弹力布:T/Rbengaline 097,T/C色织格子布:T/C solid check fabric098,弹力仿麂皮:Micro suede withspandex 099,T/R仿麂皮:T/R Microsuede 100,仿麂皮瑶粒绒复合布:100%polyester micro suede bounding with polar fleece 101,仿麂皮针织布复合:100% polyester bounding with knitting micro suede fabric 102,仿麂皮羊羔绒复合布:100% polyester micro suede bounding with lambfur 103,蜡光缎:cire satine 104,全消光尼丝纺:Full dull nylon taffeta 105,半消光尼丝纺:semi-dull nylon taffeta 106,亮光尼龙:Trilobal nylon 107,全消光塔丝隆:Full dull nylon taslan 108,全消光牛津布:full dull nylonoxford 109,尼龙格:Nylon rip-stop 110,塔丝隆格:Taslan rip-stop 111,哑富迪:Full dull Micro polyester pongee 112,全消光春亚纺:Full dull polyester pongee 113,春亚纺格子:polyester pongee rip-stop114,全消光涤纶桃皮绒:Full dull polyester peach 115,宽斜纹桃皮绒:Big twill polyesterpeach 116,涤锦复合桃皮绒:poly/nylonpeach 117,涤纶格子:polyester taffetarip-stop 118,涤纶蜂巢塔丝隆:polyester honey taslan119,全消光涤纶低弹牛津布:Full dull poly textured oxford 120,涤锦交织桃皮绒:Nylon/polyester inter-woven peach服装面料英语(三) 121. 棉织物:COTTON FABRIC 122. 平纹织物:PLAIN CLOTH 123. 斜纹织物:TWILL CLOTH 124. 缎纹织物:SATIN AND SATEEN CLOTH125. 纯纺织物:PURE YARN FABRIC 126. 混纺织物:BLENDED FABRIC127. 混并织物:MIXTURE 128. 交织织物:MIXED FABRIC 129. 服装用织物:DRESS FABRIC 130. 装饰用织物:FURNISHING FABRIC 131. 产业用织物:TECHNICAL FABRIC 132. 平布:PLAINCLOTH 133. 粗平布:COARSE SHEETING 134. 中平布:PLAIN CLOTH 135. 细平布:FINE PLAIN136. 粘纤平布:VISCOSE PLAIN CLOTH 137. 富纤平布:POLYNOSIC PLAIN CLOTH 138. 粘/棉平布:VISCOSE/COTTON PLAIN CLOTH 139. 粘/维平布:VISCOSE/VINYLON PLAIN CLOTH 140. 涤/棉平布:T/C PLAIN CLOTH141. 涤/粘平布:POLYESTERE/VISCOSE PLAIN CLOTH142. 棉/丙平布:COTTON/POLYPROPYLENE PLAINCLOTH143. 棉/维平布:C/V PLAIN CLOTH 144. 细纺:CAMBRIC 145. 涤/棉细纺:T/C CAMBRIC 146. 府绸:POPLIN 147. 纱府绸:POPLINETTE 148. 线府绸:THREADY POPLIN 149. 涤/棉府绸:T/C POPLIN 150. 棉/维府绸:C/V POPLIN 151. 麻纱:HAIR CORDS 152. 柳条麻纱:STRIPED HAIR CORDS153. 异经麻纱:END-AND-END HAIRCORDS 154. 提花麻纱:FIGURED HAIRCORDS 155. 罗布:LENO-LIKE CLOTH 156. 罗缎:BENGALINE, USSORES 157. 巴厘纱:VOILE 158. 麦尔纱:MULL 159. 防绒布:DOWN-PROOF FABRIC 160. 双经布:DOUBLE ENDS FABRIC 161. 双纬布:DOUBLE WEFTFABRIC 162. 蓝白花布:INDIGOPRINT 163. 纱斜纹:SINGLE DRILL 164 线斜纹:THREADY DRILL 165. 粗斜纹:COARSE DRILL 166. 细斜纹:JEAN 167. 哔叽:SERGE 168. 纱哔叽:SINGLE SERGE 169. 粘胶哔叽:VISCOSE SERGE 170. 华达呢:GABERCORD 171. 纱华达呢:SINGLE GABERCORD 172. 线华达呢:THREADY GABERCORD 173. 卡其:KHAKIDRILL 174. 单面卡其:ONE-SIDED DRILL175. 双面卡其:REVERSIBLE DRILL 176. 纱卡其:SINGLE DRILL177. 线卡其:THREADY DRILL 178. 人字卡其:POINTED DRILL179. 缎纹卡其:WHIPCORD 180. 涤/棉卡其:T/C DRILL 服装面料英语(四)181. 直贡:TWILLED SATIN 182. 纱直贡:SINGLE TWILLED SATIN183. 羽绸:SATINET 184. 线直贡:THREADY TWILLED SATIN185. 横贡:SATEEN 186. 绒布:FLANNELETTE 187. 单面绒布:IRREVERSIBLE FLANNELETTE 188. 双面绒布:BOTH-SIDE RAISED FLANNELETTE 189. 斜纹绒布:TWILLED FUSTIAN,FLANNEL TWILLS190. 厚绒布:HEAVY FLANNELETTE 191. 灯芯绒:CORDUROY192. 粗条灯芯绒:SPACIOUS WALED CORDUROY 193. 中条灯芯绒:MID-WALE CORDUROY 194. 细条灯芯绒:PINWALE CORDUROY195. 特细条灯芯绒:ULTRA-FINECORDUROY 196. 提花灯芯绒:FIGURED CORDUROY 197. 弹力灯芯绒:ELASTIC CORDUROY 198. 棉/涤灯芯绒:T/CCORDUROY 199. 仿平绒:VELVETEEN-LIKE FABRIC200. 烂花仿平绒:ETCHED-OUT VELVETEEN-LIKE FABRIC201. 平绒:VELVET AND VELVETEEN 202. 纱罗织物:LENO AND GAUZE203. 牛津布:OXFORD 204. 竹节布:SLUBBED FABRIC 205. 结子布:KNOPFABRIC 206. 提花布:FIGURED CLOTH 207. 提格布:CHECKS208. 绉布:CREPE 209. 皱纹布:CREPPELLA 210. 泡泡纱:SEERSUCKER211. 轧纹布:EMBOSSING CLOTH 212. 折绉布:WRINKLE FABRIC213. 水洗布:WASHER WRINKLE FABRIC 214. 稀密条织物:THICK AND THIN STRIPED FABRIC 215. 经条呢:WARP STRIPEED FABRIC216. 华夫格:WALF CHECKS 217. 巴拿马:PANAMA 218. 服装衬布:PADING CLOTH 219. 树脂衬布:RESIN PADDING CLOTH220. 热熔粘合衬布:HOT-MELT ADHESIVE PADDING CLOTH221. 黑炭衬:HAIR INTERLINING 222. 马尾衬:HAIR CLOTH223. 粘纤织物:SPUN RAYON FABRIC 224. 富纤织物:POLYNOSIC FABRIC225. 氨纶弹力织物:SPANDEX STRETCH FABRIC 226. 中长化纤织物:MIDFIBRE FABRIC 227. 纬长丝织物:WEFT FILAMENT MIXED FABRIC228. 纬长丝大提花仿绸织物:SILK-LIKE FABRIC JACQUARD229. 仿麂皮织物:SUEDE FABRIC 230. 仿麻布:LINEN TYPE CLOTH231. 合纤长丝仿麻布:POLYSTER LINEN TYPE FILAMENT FABRIC232. 低弹涤纶丝仿毛织物:WOOL-LIKE FABRIC WITH TRUE-RAN LOW-ELASTICYARN 233. 凉爽呢:WOOL-LIKE FABRIC 234. 雪尼儿织物:CHENILLE FABRIC 235. 柔道运动服织物:FABRIC OF JUDO WEAR236. 医药用纱布:MEDICAL GAUZE 237. 尿布:DIAPER238. 烂花布:ETCHED-OUT FABRIC239. 全包芯纱烂花布:COMPOSITE YARN ETCHED-OUT FABRIC240. 混纺纱烂花布;BLENDED YARN ETCHED-OUT FABRIC服装面料英语(五)241. 帆布:CANVAS 242. 遮盖帆布:CANVAS OF COVER 243. 橡胶帆布:RUBBER CANVAS 244. 鞋用帆布:PLIMSOLL DUCK 245. 百页布:BAIYE FABRIC 246. 滤布:FILTRATION FABRIC 247. 印花衬布:PRINTING BLANKET 248. 圆筒布:TUBULARFABRIC 249. 43-3丙纶长丝滤布:POLYPROPYLENE FILAMENT FILTRATION FABRIC250. 729-涤纶大圆筒滤布:POLYESTER TUBULAR FILTRATION FABRIC251. 318锦纶布:318 POLYAMIDE FABRIC 252. 锦纶布:601 POLYAMIDE FABRIC 253. 伞布:UMBRELLA CLOTH 254. 砂皮布:ABRASIVE CLOTH255. 玻璃纤纬织物:GLASS-FIBRE FABRIC 256. 土工模袋布:FABRICFORM257. 标准贴衬织物:STANDARD ADJACENT FABRIC 258. 家具布:UPHOLSTERYFABRIC 259. 窗帘布:WINDOW BLINDFABRIC260. 贴墙布:WALL CLOTH 261. 粘晴大提花装饰织物:R.A JACQUARD ORNAMENTALFABRIC 262. 漂白织物:BLEACHED FABRIC263. 染色织物:DYED FABRICS 264. 印花织物:PRINTED FABRIC265. 拒水整理织物:WATER REPELLENT FANISH FABRIC266. 拒油整理织物:OIL-REPELLENT FINISH FABRIC267. 阻燃整理织物:FLAME RETARDANT FINISH FABRIC268. 预缩整理织物:SHRUNK FINISH FABRIC 269. 防皱整理织物:CREASE RESISTANT FINISH FABRIC 270. 柔软电整理织物:ANTISTATIC FINISH FABRIC 271. 易去污整理织物:SOIL RELEASE FINISH FABRIC272. 减量整理织物:DEWEIGHTING FINISH FABRIC 273. 增重整理织物:WEIGHTED FINISH FABRIC 274. 液氨整理织物:LIQUID AMMONIA FINISH FABRIC 275. 电光整理织物:SCHREINER FINISH FABRIC276. 轧光整理织物:CALENDER FINISH FABRIC 277. 涂层整理织物:COATED FINISH FABRIC 278. 轧纹整理织物:GAUFFERED FINISH FABRIC279. 磨绒整理织物:SANDED FINISH FABRIC 280. 防蛀整理织物:MOTH PROOF FINISH FABRIC 281. 防毡缩整理织物:ANTIFELTING FI靛蓝青年布:Indigo chambray 人棉布植绒:Rayon cloth flocking PVC植绒:PVCflocking 针织布植绒:Knitting cloth flocking 珠粒绒:Claimond veins 倒毛:Down pilemaking 平绒:velveteen(velvet-plain) 仿麂皮:Micro suede 牛仔皮植绒:Jeans flocking 尼丝纺:Nylon taffeta (Nylon shioze) 尼龙塔夫泡泡纱:Nylon seersucker taffeta 素面植绒:plainflocking 印花植绒:flocking(flower) 雕印植绒:Embossing flocking 皮革沟底植绒:Leather imitation flocking 牛仔植绒雕印:Embossing jeans flocking 兔羊绒大衣呢:Angora cachmere overcoating 双面呢:double-faced woolen goods 羊毛立绒呢:cut velvet 顺毛呢:over coating 粗花呢:costume tweed 弹力呢:lycra woolen goods 塔丝绒: Nylon taslon 塔丝绒格子:N/Taslon ripstop 桃皮绒:polyester peach skin 涤塔夫:polyester taffeta 春亚纺:polyester pongee 超细麦克布:Micro fiber 锦棉稠(平纹):Nylon-cotton fabric (plain)重平锦棉稠:Nylon-cotton-cotton fabric(doubleweft) 人字锦棉纺:Nylon-cottonfabric 斜纹锦棉纺:Nylon-cotton fabric (twill) 素色天鹅绒:solid velvet 抽条磨毛天鹅绒:Rib fleece velvet 雪花天鹅绒:melange velvet 轧花天鹅绒:ginning velvet 粒粒绒布:pellet fleece velvet 麻棉混纺布:linen/cotton blended fabric 麻棉交织布:linen/cotton mixed fabric 素色毛巾布:solid terry 蚂蚁布:fleece in one side 素色卫衣布:solid fleece 鱼网布:fleece 彩条汗布:color-stripes single jersey T/R弹力布:T/R bengaline T/C色织格子布:T/C solid check fabric 弹力仿麂皮:Micro suede withspandex T/R仿麂皮:T/R Micro suede 仿麂皮瑶粒绒复合布:100%polyester micro suede bounding with polar fleece 仿麂皮针织布复合:100% polyester bounding with knitting micro suedefabric 仿麂皮羊羔绒复合布:100% polyester micro suede bounding with lamb fur 蜡光缎:cire satine 全消光尼丝纺:Full dull nylontaffeta 半消光尼丝纺:semi-dull nylontaffeta 亮光尼龙:Trilobal nylon 全消光塔丝隆:Full dull nylon taslan 全消光牛津布:full dull nylon oxford 尼龙格:Nylon rip-stop 塔丝隆格:Taslan rip-stop 哑富迪:Full dull Micropolyester pongee 全消光春亚纺:Full dull polyester pongee 春亚纺格子:polyester pongeerip-stop 全消光涤纶桃皮绒:Full dull polyester peach 宽斜纹桃皮绒:Big twill polyester peach 涤锦复合桃皮绒:poly/nylon peach 涤纶格子:polyester taffeta rip-stop 涤纶蜂巢塔丝隆:polyester honey taslan 全消光涤纶低弹牛津布:Full dull poly textured oxford 涤锦交织桃皮绒:Nylon/polyester inter-woven peachC Cotton 棉W Wool 羊毛M Mohair 马海毛RH、Rabbit hair 兔毛AL Alpaca 羊驼毛S Silk 真丝J Jute 黄麻L Linen 亚麻Ram Ramie 苎麻Hem Hemp 大麻T Polyester 涤纶WS Cashmere 羊绒WA Angora 安哥拉山羊毛LA Lambswool 羊羔毛TS Tussah silk 柞蚕丝YH Yark hair 牦牛毛MD Modal 莫代尔CH Camel hair 驼绒CU Cupro 铜MS Mulberry silk 桑蚕丝LY Lycra 莱卡KENDER Kender 罗布麻SILKOOL Silkool 大豆蛋白纤维CVC CVC 涤棉倒比N Nylon 锦纶R Rayon 人棉V Viscose 粘胶SP Spendex 氨纶PP Polypropylene 丙纶PV Polyvinyl 维纶A Acrylic 腈纶Tel Tencel 天丝。

ASTME112中文修订版

金属平均晶粒度测定方法引言本标准规定了金属材料平均晶粒度的基本方法。

由于纯粹以晶粒几何图形为基础,与金属和合金本身无关。

因此,这些基本方法也可以用来测量非金属材料中晶粒、晶体和晶胞的平均尺寸。

如果材料的组织形貌非常接近某一个标准系列评级图,可以使用比较法。

测定平均晶粒度常用比较法,也可以用截点法和面积法。

但是,比较法不能用来测量单个晶粒。

1范围1.1 本标准规定了金属组织的平均晶粒度表示及评定的三种方法——比较法、面积法和截点法。

这些方法也适用于晶粒组织形貌与标准系列评级图相似的非金属材料。

这些方法主要适用于单相晶粒组织,但也适用于多相或多组元试样中特定类型组织的晶粒平均尺寸的测量。

1.2 本标准使用晶粒面积、晶粒直径、截线长度的单峰分布来测定式样的平均晶粒度。

这些分布近似正态分布。

本标准的测定方法不适用于双峰分布的晶粒度。

双峰分布的晶粒度参见标准E1181。

测定分布在细小晶粒基体上个别非常粗大的晶粒的方法参见E 930。

1.3本标准的测量方法仅适用平面晶粒度的测量,也就是试样截面显示出的二维晶度;不适用于试样三维晶粒,即立体晶粒尺寸的测量。

1.4 试验可采用与一系列标准晶粒度图谱进行对比的方法或者在简单模板上进行计数的方法。

利用半自动计数仪或自动图象分析仪测定晶粒尺寸的方法参见E 1382。

1.5本标准仅作为推荐性试验方法,它不能确定受检材料是否接收或适合使用的范围。

1.6 测量数值应用S I单位表示。

等同的英寸-英镑数值,如需标出,应在括号中列出近似值.1.7 本标准没有列出所有的安全事项,只是一些使用的注意事项。

本标准的使用者在使用前应掌握较合适的安全健康的操作规范和使用时限制的规章制度。

TSL12T中文资料

GND

2

OUT

4

VDD

3

N/C

1

DESCRIPTION

Power supply ground (substrate). All voltages are referenced to GND. Output voltage. Supply voltage. No connection.

Absolute Maximum Ratings over operating free-air temperature range (unless otherwise noted)†

Functional Block Diagram

−

Voltage

+

Output

Available Options

DEVICE TSL12 TSL13

TA 0°C to 70° 0°C to 70°

PACKAGE − LEADS 4-lead Low-Profile Surface-Mount 4-lead Low-Profile Surface-Mount

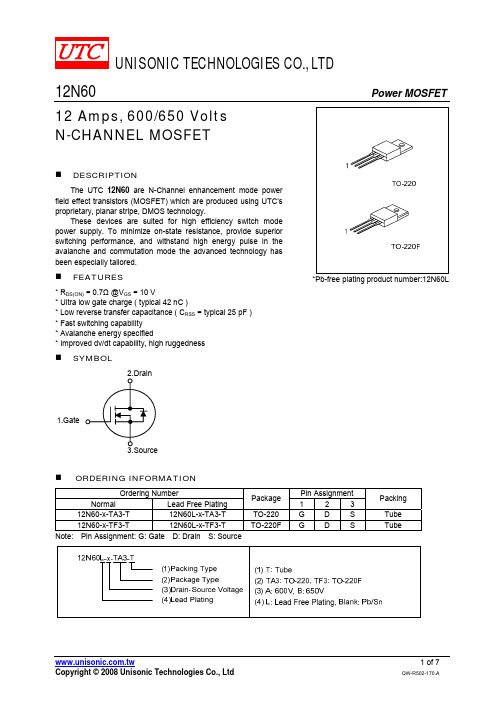

12N60中文资料

Fig. 3A Gate Charge Test Circuit

Fig. 3B Gate Charge Waveform

10V

RD tp

L VDS

BVDSS IAS

VDD

VDD D.U.T.

ID(t) tp

VDS(t) Time

Fig. 4A Unclamped Inductive Switching Test Circuit Fig. 4B Unclamped Inductive Switching Waveforms

25℃ 100

55℃

10-1 2

Notes:

1.VDS=50V 2.250μs Pulse Test

4

6

8

10

Gate-Source Voltage, VGS (V)

UNISONIC TECHNOLOGIES CO., LTD

12N60-x-TF3-T

12N60L-x-TF3-T

Note: Pin Assignment: G: Gate D: Drain S: Source

Package

TO-220 TO-220F

Pin Assignment

1

2

3

G

D

S

G

D

S

Packing

Tube Tube

Copyright © 2008 Unisonic Technologies Co., Ltd

Turn-On Rise Time Turn-Off Delay Time

tR tD(OFF)

VDD = 300V, ID = 12A, RG = 25Ω (Note 4, 5)

115 240 nsቤተ መጻሕፍቲ ባይዱ95 200 ns

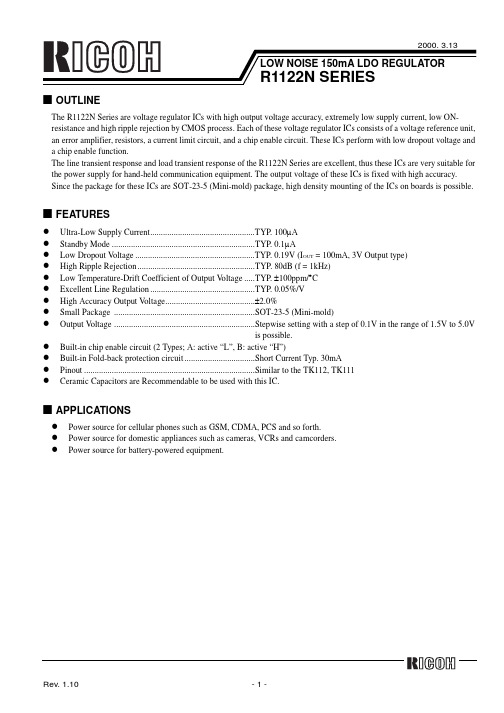

R1122N中文资料

2000. 3.13LOW NOISE 150mA LDO REGULATORR1122N SERIESn OUTLINEThe R1122N Series are voltage regulator ICs with high output voltage accuracy, extremely low supply current, low ON-resistance and high ripple rejection by CMOS process. Each of these voltage regulator ICs consists of a voltage reference unit, an error amplifier, resistors, a current limit circuit, and a chip enable circuit. These ICs perform with low dropout voltage and a chip enable function.The line transient response and load transient response of the R1122N Series are excellent, thus these ICs are very suitable for the power supply for hand-held communication equipment. The output voltage of these ICs is fixed with high accuracy. Since the package for these ICs are SOT-23-5 (Mini-mold) package, high density mounting of the ICs on boards is possible.n FEATURESl Ultra-Low Supply Current.................................................TYP. 100m Al Standby Mode...................................................................TYP. 0.1m Al Low Dropout V oltage........................................................TYP. 0.19V (I OUT = 100mA, 3V Output type)l High Ripple Rejection.......................................................TYP. 80dB (f = 1kHz)l Low Temperature-Drift Coefficient of Output V oltage.....TYP. ±100ppm/°Cl Excellent Line Regulation.................................................TYP. 0.05%/Vl High Accuracy Output V oltage..........................................±2.0%l Small Package ..................................................................SOT-23-5 (Mini-mold)l Output V oltage ..................................................................Stepwise setting with a step of 0.1V in the range of 1.5V to 5.0Vis possible.l Built-in chip enable circuit (2 Types; A: active “L”, B: active “H”)l Built-in Fold-back protection circuit.................................Short Current Typ. 30mAl Pinout................................................................................Similar to the TK112, TK111l Ceramic Capacitors are Recommendable to be used with this IC.n APPLICATIONSl Power source for cellular phones such as GSM, CDMA, PCS and so forth.l Power source for domestic appliances such as cameras, VCRs and camcorders.l Power source for battery-powered equipment.n BLOCK DIAGRAMR1122NXX1AR1122NXX1BVrefCurrent LimitV DD3124V OUTGND CE VrefCurrent LimitV DD3124V OUTGND CE n SELECTION GUIDEThe output voltage, the active type, the packing type, and the taping type for the ICs can be selected at the user's request.The selection can be made by designating the part number as shown below :R1122NXX1X-XX¬Part Number---a b cCode Contentsa Setting Output V oltage (V OUT ) :Stepwise setting with a step of 0.1V in the range of 1.5V to 5.0V is possible.b Designation of Active Type :A : active “L” type B : active “H” typecDesignation of Taping Type :Ex. TR, TL (refer to Taping Specifications; TR type is the standard direction.)n PIN CONFIGURATIONSOT-23-554NC CE(mark side)V OUT GND V DD123n PIN DESCRIPTIONPin No.Symbol Description1V OUT Output pin2GND Ground Pin3V DD Input Pin4CE or CE Chip Enable Pin5NC No Connectionn ABSOLUTE MAXIMUM RATINGSSymbol Item Rating UnitV IN Input V oltage7.0VV CE Input V oltage (CE or CE Pin)-0.3 ~ V IN+0.3VV OUT Output V oltage-0.3~ V IN+0.3VI OUT Output Current200mAP D Power Dissipation250mWTopt Operating TemperatureRange-40 ~ 85°CTstg Storage Temperature Range-55 ~ 125°Cn ELECTRICAL CHARACTERISTICSl R1122NXX1A Topt = 25°C Symbol Item Conditions MIN.TYP.MAX.UnitV OUT Output V oltage V IN = Set V OUT+1V1mA £ I OUT£ 30mAV OUT´0.98V OUT´1.02VI OUT Output Current V IN = Set V OUT+1VWhen V OUT = Set V OUT-0.1V150mAD V OUT/D I OUT Load Regulation V IN = Set V OUT+1V1mA £ I OUT£ 80mA1240mVV DIF Dropout V oltage refer to the ELECTICAL CHARACTERISTICS by OUTPUT VOLTAGEI SS Supply Current V IN = Set V OUT+1V100170m A Istandby Supply Current (Standby)V IN = V CE = Set V OUT+1V0.1 1.0m A D V OUT/D V IN Line Regulation Set V OUT+0.5V £ V IN£ 8VI OUT = 30mA0.050.20%/VRR Ripple Rejection f = 1KHz, Ripple 0.5Vp-pV IN = Set V OUT+1V80dBV IN Input V oltage 2.0 6.0VD V OUT/D T Output V oltageTemperature Coefficient I OUT = 30mA-40°C £ Topt £ 85°C±100ppm/°CIlim Short Current Limit V OUT = 0V30mA R PU CE Pull-up Resistance 2.5510M W V CEH CE Input V oltage “H” 1.5V IN V V CEL CE Input V oltage “L”00.25V en Output Noise BW = 10Hz ~ 100kHz30m Vrmsl R1122NXX1BTopt=25°CSymbolItem Conditions MIN.TYP .MAX.Unit V OUT Output V oltage V IN = Set V OUT +1V 1mA £ I OUT £ 30mA V OUT ´0.98V OUT´1.02VI OUT Output Current V IN = Set V OUT +1VWhen V OUT = Set V OUT -0.1V 150mAD V OUT /D I OUTLoad Regulation V IN = Set V OUT +1V1mA £ I OUT £ 80mA1240mVV DIF Dropout V oltage refer to the ELECTICAL CHARACTERISTICS by OUTPUT VOLTAGEI SS Supply Current V IN = Set V OUT +1V 100170m A Istandby Supply Current (Standby)V IN = Set V OUT +1VV CE = GND0.1 1.0m AD V OUT /D V INLine Regulation Set V OUT +0.5V £ V IN £ 8VI OUT = 30mA0.050.20%/VRR Ripple Rejection f = 1KHz, Ripple 0.5Vp-pV IN = Set V OUT +1V80dBV IN Input V oltage 2.0 6.0VD V OUT /D T Output V oltage Temperature Coefficient I OUT = 30mA-40°C £ Topt £ 85°C±100ppm /°C Ilim Short Current Limit V OUT = 0V 30mAR PD CE Pull-down Resistance 2.5510M W V CEH CE Input V oltage “H” 1.5V IN V V CEL CE Input V oltage “L”00.25VenOutput Noise BW = 10Hz ~ 100kHz 30m Vrmsl ELECTRICAL CHARACTERISTICS by OUTPUT VOLTAGETopt = 25°CDropout VoltageV DIF (V)Output VoltageV OUT (V)Conditions TYP.MAX.1.5 £ V OUT £ 1.60.320.551.7 £ V OUT £ 1.80.280.471.9 £ V OUT £2.30.250.352.4 £ V OUT £ 2.70.200.292.8 £ V OUT £ 5.0I OUT = 100mA 0.190.26n OPERATIONR1122XX1AR1122XX1BV DD3124V OUTGNDR2R1CE Current LimitVrefV DD3124V OUTGNDR2R1CE Current LimitVrefIn these ICs, fluctuation of Output V oltage, V OUT is detected by Feed-back Registers, R1 and R2, and the result is compared with a reference voltage by Error Amplifier, so that a constant voltage is output.A current limit circuit for protection at short mode, and a chip enable circuit are included.n TEST CIRCUITSR1121Nxx1B SeriesV DD1324V OUT I OUT INOUT GNDCE 0.1µF 2.2µFR1121Nxx1B SeriesV DD1324V OUT I SSIN OUTGNDCE0.1µF 2.2µFFig.1 Standard test Circuit Fig.2 Supply Current Test CircuitR1121Nxx1B SeriesV DD13P .G24V OUT I OUTINOUT GNDCE R1121Nxx1B SeriesV DD1324V OUT INOUTGNDI1I2CE 1µF Fig.3 Ripple Rejection, Line Transient Response TestCircuitFig.4 Load Transient Response Test Circuit2.2m F2.2m F2.2m FR1122Nxx1B SeriesR1122Nxx1B SeriesR1122Nxx1B SeriesR1122Nxx1B Seriesn TECHNICAL NOTESWhen using these ICs, consider the following points:Phase CompensationIn these ICs, phase compensation is made for securing stable operation even if the load current is varied. For this purpose, be sure to use a capacitor C OUT with good frequency characteristics and ESR (Equivalent Series Resistance).(note: When the additional ceramic capacitors are connected to the Output Pin with Output capacitor for phase compensation, the operation might be unstable. Because of this, test these ICs with as same external components as ones to be used on the PCB.)Recommended Capacitors; GRM40X5R225K6.3 (Murata)GRM40-034X5R335K6.3 (Murata)GRM40-034X5R475K6.3 (Murata)PCB LayoutMake VDD and GND line sufficient. When the impedance of these is high, it would be a cause of picking up the noise or unstable operation. Connect a capacitor with a capacitance of 2.2m F or more between VDD and GND pin as close as possible. Set external components, especially output capacitor as close as possible to the ICs and make wiring shortest.n TYPICAL APPLICATIONR1111NXX1A V OUTOUT IN V DDGNDCECap.Cap.R1111Nxx1B V OUTOUTINV DD GNDCECap.Cap.(External Components)Output Capacitor; Ceramic 2.2m F(Set Output Voltage in the range from 2.5 to 5.0V) Ceramic 4.7m F (Set Output Voltage in the range from 1.5 to 2.5V)Input Capacitor; Ceramic 2.2m FR1122Nxx1A Series R1122Nxx1BSeriesn TYPICAL CHARACTERISTICS1)Output Voltage vs. Output CurrentR11x2N151B00.20.40.60.811.21.41.61.80100200300400500Output Current Iout[mA]O u t p u t V o l t a g e V o u t [V ]VIN=2.0V VIN=2.5V VIN=3.5VR11x2N201B00.511.522.50100200300400500Output Current Iout[mA]O u t p u t V o l t a g e V o u t [V ]VIN=2.3V VIN=2.5V VIN=3.0V VIN=4.0VR11x2N301B00.511.522.533.50100200300400500Output Current Iout[mA]O u t p u t V o l t a g e V o u t [V ]VIN=3.3V VIN=3.5V VIN=4.0V VIN=5.0VR11x2N401B0123450100200300400500Output Current Iout[mA]O u t p u t V o l t a g e V o u t [V ]VIN=4.3V VIN=4.5V VIN=5.0V VIN=6.0VR11x2N501B01234560100200300400500Output Current Iout[mA]O u t p u t V o l t a g e V o u t [V ]VIN=5.3V VIN=5.5V VIN=6.0V VIN=7.0V2)Output Voltage vs. Input VoltageR11x2N151B1.0001.1001.2001.3001.4001.5001.6001234567Input Voltage V IN [V]O u t p u t V o l t a g e V O U T [V ]Iout=1mAIout=30mA Iout=50mAR11x2N201B1.5001.6001.7001.8001.9002.0002.1001234567Input Voltage V IN [V]O u t p u t V o l t a g e V O U T [V ]Iout=1mAIout=30mA Iout=50mAR11x2N301B2.5002.6002.7002.8002.9003.0003.100234567Input Voltage V IN [V]O u t p u t V o l t a g e V O U T [V ]Iout=1mAIout=30mA Iout=50mAR11x2N401B2.5003.0003.5004.0004.500234567Input Voltage V IN [V]O u t p u t V o l t a g e V O U T [V ]Iout=1mA Iout=30mA Iout=50mAR11x2N501B2.5003.0003.5004.0004.5005.0005.500234567Input Voltage V IN [V]O u t p u t V o l t a g e V O U T [V ]Iout=1mAIout=30mA Iout=50mA3) Dropout Voltage vs. Output CurrentR11x2N151B0.0000.1000.2000.3000.4000.5000.600050100150Output Current I OUT [mA]D r o p o u t V o l t a g e V D I F [V ]R11x2N201B0.0000.1000.2000.3000.4000.5000.60050100150Output Current I OUT [mA]D r o p o u t V o l t a g e V D I F [V ]R11x2N301B0.0000.1000.2000.3000.4000.5000.600050100150Output Current I OUT [mA]D r o p o u t V o l t a g e V D I F [V ]R11x2N401B0.0000.1000.2000.3000.4000.5000.60050100150Output Current I OUT [mA]D r o p o u t V o l t a g e V D I F [V ]R11x2N501B0.0000.1000.2000.3000.4000.5000.600050100150Output Current I OUT [mA]D r o p o u t V o l t a g e V D I F [V ] Topt=-40°CTopt=25°C Topt=85°CTopt=-40°CTopt=25°C Topt=85°CTopt=-40°CTopt=25°C Topt=85°CTopt=-40°CTopt=25°C Topt=85°CTopt=-40°CTopt=25°C Topt=85°C4) Output V oltage vs. TemperatureR11x2N151A/B 1.471.481.491.501.511.521.53-50-25025*******Temperature Topt O u t p u t V o l t a g e V O U T (V )R11x2N201B1.901.921.941.961.982.002.022.042.062.082.10-50-25025*******Temperature Topt O u t p u t V o l t a g e V O U T [V ]R11x2N301A/B2.942.962.983.003.023.043.06-50-25255075100Temperature Topt O u t p u t V o l t a g e V O U T (V )R11x2N401A/B3.923.943.963.984.004.024.044.064.08-50-25255075100Temperature Topt O u t p u t V o l t a g e V O U T (V )R11x2N501A/B4.904.924.944.964.985.005.025.045.065.085.10-50-25255075100Temperature Topt O u t p u t V o l t a g e V O U T (V )(°C)(°C)V IN =4.0V C IN =1m F C OUT =2.2m F I OUT =30mA(°C)(°C)V IN =5.0V C IN =1m F C OUT =2.2m F I OUT =30mA(°C)V IN =6.0V C IN =1m F C OUT =2.2m F I OUT =30mAVIN=2.5V CIN=1m FCOUT=2.2m FIOUT=30mAV IN =3.0V C IN =1m FC OUT =2.2m F I OUT =30mA5)Supply Current vs. Input VoltageR11x2N151B0204060801001201234567Input Voltage V IN [V]S u p p l y C u r r e n t I S S {u A ]R11x2N201B0204060801001201234567Input Voltage V IN [V]S u p p l y C u r r e n t I S S {u A ]R11x2N301B0204060801001201234567Input Voltage V IN [V]S u p p l y C u r r e n t I S S {u A ]R11x2N401B204060801001201234567Input Voltage V IN [V]S u p p l y C u r r e n t I S S {u A ]R11x2N501B0204060801001201234567Input Voltage V IN [V]S u p p l y C u r r e n t I S S {u A ]6)Supply Current vs. TemperatureR11x2N151A/B050100150200-50-25025*******Temperature Topt S u p p l y C u r r e n t I s s (u A )R11x2N201A/B050100150200-50-25255075100Temperature Topt S u p p l y C u r r e n t I s s (u A )R11x2N301A/B50100150200-50-25255075100Temperature Topt S u p p l y C u r r e n t I s s (u A )R11x2N401A/B050100150200-50-25255075100Temperature Topt S u p p l y C u r r e n t I s s (u A )R11x2N501A/B050100150200-50-25255075100Temperature ToptS u p p l y C u r r e n t I s s (u A )(°C)V IN =2.5V C IN =1m F C OUT =2.2m F(°C)V IN =3.0V C IN =1m F C OUT =2.2m F(°C)V IN =4.0V C IN =1m F C OUT =2.2m F(°C)V IN =5.0V C IN =1m F C OUT =2.2m F(°C)V IN =6.0V C IN =1m FC OUT =2.2m F7)Ripple Rejection vs. FrequencyR11x2N151A/B0.0010.0020.0030.0040.0050.0060.0070.0080.0090.000.1110100Frequency Freq [kHz]R i p p l e R e j e c t i o n R R [d B ]R11x2N201A/B0.0010.0020.0030.0040.0050.0060.0070.0080.0090.000.1110100Frequency Freq [kHz]R i p p l e R e j e c t i o n R R [d B ]R11x2N301A/B 0.0010.0020.0030.0040.0050.0060.0070.0080.0090.000.1110100Frequency Freq [kHz]R i p p l e R e j e c t i o n R R [d B ]R11x2N401A/B0.0010.0020.0030.0040.0050.0060.0070.0080.0090.000.1110100Frequency Freq [kHz]R i p p l e R e j e c t i o n R R [d B ]R11x2N501A/B 0.0010.0020.0030.0040.0050.0060.0070.0080.0090.000.1110100Frequency Freq [kHz]R i p p l e R e j e c t i o n R R [d B ]V IN =2.5V+0.5Vp-p C OUT =2.2m F I OUT=30mAV IN =3.0V+0.5Vp-p C OUT =2.2m F I OUT=30mAV IN =4.0V+0.5Vp-pC OUT =2.2m F I OUT=30mAV IN =5.0V+0.5Vp-p C OUT =2.2m F I OUT=30mAV IN =6.0V+0.5Vp-pC OUT =2.2m F I OUT=30mA8) Ripple Rejection vs. Input V oltage (DC bias)R11x2N301B0.0010.0020.0030.0040.0050.0060.0070.0080.0090.003.103.203.303.403.50Input Voltage V IN [V]R i p p l e R e j e c t i o n R R [d B f=400Hz f=1kHz f=10kHzR11x2N301B0.0010.0020.0030.0040.0050.0060.0070.0080.0090.003.103.203.30 3.403.50Input Voltage V IN [V]R i p p l e R e j e c t i o n R R [d B ]f=400Hz f=1kHz f=10kHzR11x2N301B0.0010.0020.0030.0040.0050.0060.0070.0080.0090.003.103.203.303.40 3.50Input Voltage V IN [V]R i p p l e R e j e c t i o n R R [d B ]f=400Hz f=1kHz f=10kHz9) Input Transient ResponseR11X2N151B Topt=25°CC OUT =Ceramic 2.2m FI OUT=1mAC OUT =Ceramic 2.2m FI OUT=10mAC OUT =Ceramic 2.2m FI OUT=50mAV IN =2.5V<-->3.5V I OUT =30mA C IN =none C OUT =2.2m F tr/tf=5m sV INV OUTR11X2N201B Topt=25°CR11X2N301B Topt=25°CR11X2N401B Topt=25°CV IN =3.0V<-->4.0V I OUT =30mA C IN =none C OUT =2.2m F tr/tf=5m sV INV OUTV OUTV INV IN =4.0V<-->5.0V I OUT =30mA C IN =none C OUT =2.2m F tr/tf=5m sV IN =5.0V<-->6.0V I OUT =30mA C IN =none C OUT =2.2m F tr/tf=5m sV INV OUTR11X2N501B Topt=25°C10) Load Transient ResponseR11X2N151B Topt=25°CR11X2N201B Topt=25°CV INV OUTV IN =6.0V<-->7.0V I OUT =30mA C IN =none C OUT =2.2m F tr/tf=5m sI OUTV OUTI OUT =50mA<-->100mA V IN =2.5V C IN =2.2m F C OUT =2.2m F tr/tf=5sI OUTV OUTI OUT =50mA<-->100mA V IN =3.0V C IN =2.2m F C OUT =2.2m F tr/tf=5m sR11X2N301B Topt=25°CR11X2N401B Topt=25°CR11X2N501B Topt=25°CI OUT =50mA<-->100mA V IN =4.0V C IN =2.2m F C OUT =2.2m F tr/tf=5m sI OUTV OUTI OUT =50mA<-->100mA V IN =5.0V C IN =2.2m F C OUT =2.2m F tr/tf=5m sI OUTI OUTV OUTV OUTI OUT =50mA<-->100mA V IN =6.0V C IN =2.2m F C OUT =2.2m F tr/tf=5m sn TECHNICAL NOTESWhen using these ICs, be sure to consider following points:l Make V DD and GND line sufficient. When the impedance of these is high, there is a case to pick up the noise or not to work correctly.l Connect the capacitor with a capacitance as much as 2.2m F between V DD and GND as close as possible.l Set external components, especially Output Capacitor, as close as possible to the ICs and make wiring shortest.In these ICs, phase compensation is made for securing stable operation even if the load current is varied. For this purpose, be sure to use a capacitor C OUT with good frequency characteristics and ESR (Equivalent Series Resistance) of which is in the range described as follows:3412R1122NXX1BCEVDDVOUTGNDESRCeramic Cap.IOUTS.A.Spectrum AnalyzerVINCeramic Cap.Measuring Circuit for white noise; R1122NXX1BThe relations between I OUT (Output Current) and ESR of Output Capacitor are shown below. The conditions when the white noise level is under 40m V(Avg.) are marked as the hatched area in the graph.(note: When the additional ceramic capacitors are connected to the Output Pin with Output capacitor for phase compensation,the operation might be unstable. Because of this, test these ICs with as same external components as ones to be used on the PCB.)<measuring conditions>(1)V IN =V OUT +1V(2)Frequency band :10Hz to 1MHz (3)Temperature : 25°CR11X2N151BR11X2N151BC OUT =2.2uF,C IN =2.2uF0.010.1110100306090120150I OUT [mA]E S R [O h m ]C OUT =4.7uF,C IN =2.2uF0.010.1110100306090120150I OUT [mA]E S R [O h m ]R11X2N301BR11X2N301BC OUT =2.2uF,C IN =2.2uF0.010.1110100306090120150I OUT [mA]E S R [O h m ]C OUT =4.7uF,C IN =2.2uF0.010.1110100306090120150I OUT [mA]E S R [O h m ]。

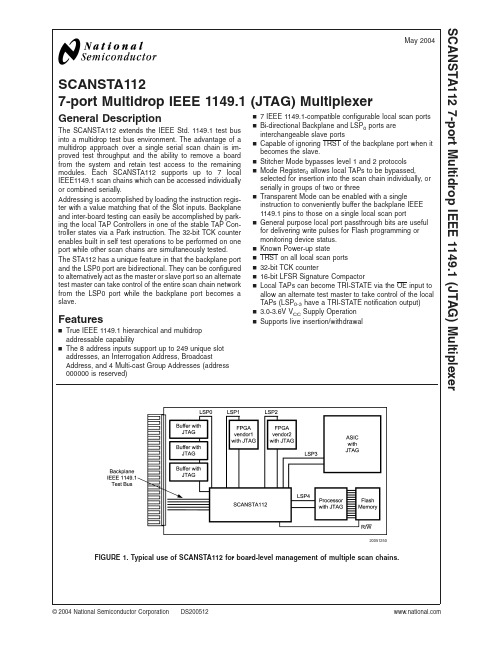

SCANSTA112中文资料

SCANSTA1127-port Multidrop IEEE 1149.1(JTAG)MultiplexerGeneral DescriptionThe SCANSTA112extends the IEEE Std.1149.1test bus into a multidrop test bus environment.The advantage of a multidrop approach over a single serial scan chain is im-proved test throughput and the ability to remove a board from the system and retain test access to the remaining modules.Each SCANSTA112supports up to 7local IEEE1149.1scan chains which can be accessed individually or combined serially.Addressing is accomplished by loading the instruction regis-ter with a value matching that of the Slot inputs.Backplane and inter-board testing can easily be accomplished by park-ing the local TAP Controllers in one of the stable TAP Con-troller states via a Park instruction.The 32-bit TCK counter enables built in self test operations to be performed on one port while other scan chains are simultaneously tested.The STA112has a unique feature in that the backplane port and the LSP0port are bidirectional.They can be configured to alternatively act as the master or slave port so an alternate test master can take control of the entire scan chain network from the LSP0port while the backplane port becomes a slave.Featuresn True IEEE 1149.1hierarchical and multidrop addressable capabilityn The 8address inputs support up to 249unique slot addresses,an Interrogation Address,BroadcastAddress,and 4Multi-cast Group Addresses (address 000000is reserved)n 7IEEE 1149.1-compatible configurable local scan ports n Bi-directional Backplane and LSP 0ports are interchangeable slave portsn Capable of ignoring TRST of the backplane port when it becomes the slave.n Stitcher Mode bypasses level 1and 2protocols n Mode Register 0allows local TAPs to be bypassed,selected for insertion into the scan chain individually,or serially in groups of two or threen Transparent Mode can be enabled with a singleinstruction to conveniently buffer the backplane IEEE 1149.1pins to those on a single local scan portn General purpose local port passthrough bits are useful for delivering write pulses for Flash programming or monitoring device status.n Known Power-up staten TRST on all local scan ports n 32-bit TCK countern 16-bit LFSR Signature Compactorn Local TAPs can become TRI-STATE via the OE input to allow an alternate test master to take control of the local TAPs (LSP 0-3have a TRI-STATE notification output)n 3.0-3.6V V CC Supply Operation n Supports live insertion/withdrawal20051250FIGURE 1.Typical use of SCANSTA112for board-level management of multiple scan chains.May 2004SCANSTA1127-port Multidrop IEEE 1149.1(JTAG)Multiplexer©2004National Semiconductor Corporation IntroductionThe SCANSTA112is the third device in a series that enable multi-drop address and multiplexing of IEEE-1149.1scan chains.The SCANSTA112is a superset of its predecessors -the SCANPSC110and the SCANSTA111.The STA112has all features and functionality of these two previous devices.The STA112is essentially a support device for the IEEE 1149.1standard.It is primarily used to partition scan chains into managable sizes,or to isolate specific devices onto a seperate chain (Figure 1).The benefits of multiple scan chains are improved fault isolation,faster test times,faster programiing times,and smaller vector sets.In addition to scan chain partitioning,the device is also addressable for use in a multidrop backplane environment (Figure 2).In this configuration,multiple IEEE-1149.1acces-sible cards with an STA112on board can utilize the same backplane test bus for system-level IEEE-1149.1access.This approach facilitates a system-wide commitment to structural test and programming throughout the entire sys-tem life sycle.ArchitectureFigure 3shows the basic architecture of the ’STA112.The device’s major functional blocks are illustrated here.The TAP Controller,a 16-state state machine,is the central control for the device.The instruction register and various test data registers can be scanned to exercise the various functions of the ’STA112(these registers behave as defined in IEEE Std.1149.1).The ’STA112selection controller provides the functionality that allows the 1149.1protocol to be used in a multi-drop environment.It primarily compares the address input to the slot identification and enables the ’STA112for subsequent scan operations.The Local Scan Port Network (LSPN)contains multiplexing logic used to select different port configurations.The LSPN control block contains the Local Scan Port Controllers (LSPC)for each Local Scan Port (LSP 0,LSP 1...LSP n ).This control block receives input from the ’STA112instruction register,mode registers,and the TAP controller.Each local port contains all four boundary scan signals needed to inter-face with the local TAPs plus the optional Test Reset signal (TRST).The TDI/TDO Crossover Master/Slave logic is used to define the bidirectional B0and B1ports in a Master/Slave configuration.20051251FIGURE 2.Example of SCANSTA112in a multidrop addressable backplane.S C A N S T A 112 2SCANSTA112 Array20051202FIGURE3.SCANSTA112Block Diagram3Connection Diagrams20051201(BGA Top view)S C A N S T A 112 4SCANSTA112 Connection Diagrams(Continued)20051260TQFP pinout5TABLE 1.Pin DescriptionsPin Name DescriptionNo.Pins I/O VCC 10N/A Power GND 10N/A GroundRESET 1I RESET Input:will force a reset of the device regardless of the current state.ADDMASK 1I ADDRESS MASK input:Allows masking of lower slot input pins.MPsel B1/B01I MASTER PORT SELECTION:Controls selection of LSP B0or LSP B1as the backplane port.The unselected port becomes LSP 00.A value of "0"will select LSP B0as the master port.SB/S 1I Selects ScanBridge or Stitcher Mode.LSPsel (0-6)7I In Stitcher Mode these inputs define which LSP’s are to be included in the scan chain TRANS1ITransparent Mode enable input:The value of this pin is loaded into the TRANSENABLE bit of the control register at power-up.This value is used to control the presence of registers and pad-bits in the scan chain while in the stitcher mode.TLR_TRST 1ISets the driven value of TRST 0-5when LSP TAPs are in TLR and the device is not being reset.During RESET ="0"or TRST B ="0"(IgnoreReset ="0")TRST n ="0".This pin is to be tied low to match the function of the SCANSTA111TLR_TRST 61I This pin affects TRST of LSP 6only.This pin is to be tied low to match the function of the SCANSTA111TDI B0,TDI B12IBACKPLANE TEST DATA INPUT:All backplane scan data is supplied to the ’STA112through this input pin.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.This input has a 25K Ωinternal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this input appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;notfloating but tied to V SS )this input appears to be a capacitive load with the pull-up to ground.TMS B0,TMS B12I/OBACKPLANE TEST MODE SELECT:Controls sequencing through the TAP Controller of the ’STA112.Also controls sequencing of the TAPs which are on the local scan chains.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.This bidirectional TRISTATE pin has 24mA of drive current,with a 25K Ωinternal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this input appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;not floating but tied to V SS )this input appears to be a capacitive load with the pull-up to ground.TDO B0,TDO B12I/OBACKPLANE TEST DATA OUTPUT:This output drives test data from the ’STA112and the local TAPs,back toward the scan master controller.This bidirectional TRISTATE pin has 12mA of drive current.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.Output is sampled during interrogation addressing.When the device is power-off (V DD =0V or floating),this output appears to be a capacitive load (Note 1).TCK B0,TCK B12I/OTEST CLOCK INPUT FROM THE BACKPLANE:This is the master clock signal that controls all scan operations of the ’STA112and of the local scan ports.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.These bidirectional TRISTATE pins have 24mA of drive current with hysterisis.This input has no pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this input appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;not floating but tied to V SS )this input appears to be a capacitive load to ground.TRST B0,TRST B12I/OTEST RESET:An asynchronous reset signal (active low)which initializes the ’STA112logic.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.This bidirectional TRISTATE pin has 24mA of drive current,with a 25K Ωinternal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this pin appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;not floating but tied to V SS )this input appears to be a capacitive load with the pull-up to ground.S C A N S T A 112 6TABLE 1.Pin Descriptions(Continued)Pin Name DescriptionNo.Pins I/O TRIST B0,TRIST B12OBACKPLANE TRI-STATE NOTIFICATION OUTPUT:This signal is high when the backplane scan port is TRI-STATEd.This pin is used for backplane physical layer changes (i.e.;TTL to LVDS).This TRISTATE output has 12mA of drive current.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.A0B0,A1B0,A0B1,A1B14IBACKPLANE PASS-THROUGH INPUT:A general purpose input which is driven to the Y n of a single selected LSP.(Not available when multiple LSPs are selected).This input has a 25K Ωinternal pull-up resistor.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.Y0B0,Y1B0,Y0B1,Y1B14OBACKPLANE PASS-THROUGH OUTPUT:A general purpose output which is driven from the A n of a single selected LSP.(Not available when multiple LSPs are selected).ThisTRISTATE output has 12mA of drive current.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.S (0-7)8I SLOT IDENTIFICATION:The configuration of these pins is used to identify (assign a unique address to)each ’STA112on the system backplaneOE1IOUTPUT ENABLE for the Local Scan Ports,active low.When high,this active-low control signal TRI-STATEs all local scan ports on the ’STA112,to enable an alternate resource to access one or more of the local scan chains.TDO (01-06)6O TEST DATA OUTPUTS:Individual output for each of the local scan ports .These TRISTATE outputs have 12mA of drive current.TDI (01-06)6I TEST DATA INPUTS:Individual scan data input for each of the local scan ports.This input has a 25K Ωinternal pull-up resistor.TMS (01-06)6OTEST MODE SELECT OUTPUTS:Individual output for each of the local scan ports.TMS n does not provide a pull-up resistor (which is assumed to be present on a connected TMS input,per the IEEE 1149.1requirement).These TRISTATE outputs have 24mA of drive current.TCK (01-06)6O LOCAL TEST CLOCK OUTPUTS:Individual output for each of the local scan ports.These are buffered versions of TCK B .These TRISTATE outputs have 24mA of drive current.TRST (01-06)6O LOCAL TEST RESETS:A gated version of TRST B .These TRISTATE outputs have 24mA of drive current.A001,A1012ILOCAL PASS-THROUGH INPUTS:General purpose inputs which can be driven to thebackplane pin Y B .(Only on LSP 0and LSP 1.Only available when a single LSP is selected).These inputs have a 25K Ωinternal pull-up resistor.Y001,Y1012OLOCAL PASS-THROUGH OUTPUT:General purpose outputs which can be driven from the backplane pin A B .(Only on LSP 0and LSP 1.Only available when a single LSP is selected).These TRISTATE outputs have 12mA of drive current.TRIST (01-03)3OLOCAL TRI-STATE NOTIFICATION OUTPUTS:This signal is high when the local scan ports are TRI-STATEd .These pins are used for backplane physical layer changes (i.e.;TTL to LVDS).These TRISTATE outputs have 12mA of drive current.Note 1:Refer to the IBIS model on our website for I/O characteristics.Application OverviewADDRESSING SCHEME -The SCANSTA112architecture extends the functionality of the IEEE 1149.1Standard by supplementing that protocol with an addressing scheme which allows a test controller to communicate with specific ’STA112s within a network of ’STA112s.That network can include both multi-drop and hierarchical connectivity.In ef-fect,the ’STA112architecture allows a test controller to dynamically select specific portions of such a network for participation in scan operations.This allows a complex sys-tem to be partitioned into smaller blocks for testing purposes.The ’STA112provides two levels of test-network partitioningcapability.First,a test controller can select individual ’STA112s,specific sets of ’STA112s (multi-cast groups),or all ’STA112s (broadcast).This ’STA112-selection process is supported by a Level-1communication protocol.Second,within each selected ’STA112,a test controller can select one or more of the chip’s seven local scan-ports.That is,individual local ports can be selected for inclusion in the (single)scan-chain which a ’STA112presents to the test controller.This mechanism allows a controller to select spe-cific scan-chains within the overall scan network.The port-selection process is supported by a Level-2protocol.HIERARCHICAL SUPPORT -Multiple SCANSTA112’s can be used to assemble a hierarchical boundary-scan tree.InSCANSTA1127Application Overview(Continued)such a configuration,the system tester can configure the local ports of a set of ’STA112s so as to connect a specific set of local scan-chains to the active scan ing this capability,the tester can selectively communicate with spe-cific portions of a target system.The tester’s scan port is connected to the backplane scan port of a root layer of ’STA112s,each of which can be selected using multi-drop addressing.A second tier of ’STA112s can be connected to this root layer,by connecting a local port (LSP)of a root-layer ’STA112to the backplane port of a second-tier ’STA112.This process can be continued to construct a multi-level scan hierarchy.’STA112local ports which are not cas-caded into higher-level ’STA112s can be thought of as the terminal leaves of a scan tree.The test master can select one or more target leaves by selecting and configuring the local ports of an appropriate set of ’STA112s in the test tree.STANDARD SCANBRIDGE MODE -ScanBridge mode re-fers to functionality and protocol that has been used by National since the introduction of the PSC110in 1993.This functionality consists of a multidrop addressable IEEE1149.1switch.This enables one (or more)device to be selected from many that are connected to a parallel IEEE1149.1bus or backplane.The second function that ScanBridge mode accomplishes is to act as a mux for multiple IEEE1149.1local scan chains.The Local Scan Ports (LSP)of the device creates a connection between one or more of the local scan chains to the backplane bus.To accomplish this functionality the ScanBridge has two levels of protocol and an operational mode.Level 1protocolrefers to the required actions to address/select the desired ScanBridge.Level 2protocol is required to configuring the mux’ing function and enable the connection (UNPARK)be-tween the local scan chain and the backplane bus via an LSP .Upon completion of level 1and 2protocols the Scan-Bridge is prepared for its operational mode.This is where scan vectors are moved from the backplane bus to the desired local scan chain(s).STITCHER MODE -Stitcher Mode is a method of skipping level 1and 2protocol of the ScanBridge mode of operation.This is accomplished via external pins.When in stitcher mode the SCANSTA112will go directly to the operational mode.TRANSPARENT MODE -Transparent mode refers to a condition of operation in which there are no pad-bits or SCANSTA112registers in the scan chain.The Transparent mode of operation is available in both ScanBridge and Stitcher modes.Only the activation method differs.Once transparent mode has been activated there is no difference in operation.Transparent mode allows for the use of vectors that have been generated for a chain where these bits were not included.Check with your ATPG tool vendor to ensure support of these features.For details regarding the internal operation of the SCAN-STA112device,refer to applications note AN-1259SCAN-STA112Designers Reference.S C A N S T A 112 8Absolute Maximum Ratings(Note2) Supply Voltage(V CC)−0.3V to+4.0V DC Input Diode Current(I IK)V I=−0.5V−20mA DC Input Voltage(V I)−0.5V to+3.9V DC Output Diode Current(I OK)V O=−0.5V−20mA DC Output Voltage(V O)−0.3V to+3.9V DC Output Source/Sink Current(I O)±50mA DC V CC or Ground Current±50mA per Output PinDC Latchup Source or Sink Current±300mA Junction Temperature(Plastic)+150˚C Storage Temperature−65˚C to+150˚C Lead Temperature(Solder,4sec)100L FBGA220˚C 100L TQFP220˚C Max Package Power Capacity@25˚C100L FBGA 3.57W 100L TQFP 2.11W Thermal Resistance(θJA)100L FBGA35˚C/W 100L TQFP59.1˚C/W Package Derating above+25˚C100L FBGA28.57mW/˚C 100L TQFP16.92mW/˚C ESD Last Passing Voltage(HBM Min)2500V Recommended Operating ConditionsSupply Voltage(V CC)’STA112 3.0V to3.6V Input Voltage(V I)0V to V CC Output Voltage(V O)0V to V CC Operating Temperature(T A)Industrial−40˚C to+85˚C Note2:Absolute maximum ratings are those values beyond which damage to the device may occur.The databook specifications should be met,without exception,to ensure that the system design is reliable over its power supply, temperature,and output/input loading variables.National does not recom-mend operation of SCAN STA products outside of recommended operation conditions.DC Electrical CharacteristicsOver recommended operating supply voltage and temperature ranges unless otherwise specifiedSymbol Parameter Conditions Min Max UnitsV IH Minimum High Input Voltage V OUT=0.1V or 2.1VV CC−0.1VV IL Maximum Low Input Voltage V OUT=0.1V or0.8VV CC−0.1VV OH Minimum High Output Voltage I OUT=−100µA V CC-0.2v V All Outputs and I/O Pins V IN=V IH or V ILV OH Minimum High Output Voltage I OUT=−12mA 2.4V TDO B0,TDO B1,TRIST B0,TRIST B1,Y0B0,Y1B0,Y0B1,Y1B1,TDO(01-06),Y001,Y101,TRIST(01-03)All Outputs LoadedV OH Minimum High Output Voltage I OUT=−24mA 2.2V TMS B0,TMS B1,TCK B0,TCK B1,TRST B0,TRST B1,TMS(01-06),TCK(01-06),TRST(01-06)V OL Maximum Low Output Voltage I OUT=+100µA0.2V All Outputs and I/O Pins V IN=V IH or V ILV OL Maximum Low Output Voltage I OUT=+12mA0.4V TDO B0,TDO B1,TRIST B0,TRIST B1,Y0B0,Y1B0,Y0B1,Y1B1,TDO(01-06),Y001,Y101,TRIST(01-03)V OL Maximum Low Output Voltage I OUT=+24mA0.55V TMS B0,TMS B1,TCK B0,TCK B1,TRST B0,TRST B1,TMS(01-06),TCK(01-06),TRST(01-06)VIKL Maximum Input Clamp Diode Voltage IIK=-18mA-1.2VI IN Maximum Input Leakage Current V IN=V CC or GND±5.0µA(non-resistor input pins)SCANSTA1129DC Electrical Characteristics(Continued)Over recommended operating supply voltage and temperature ranges unless otherwise specifiedSymbol ParameterConditionsMin Max Units I ILRInput Current LowV IN =GND-45-200µA(Input and I/O pins with pull-up resistors:TDI B0,TDI B1,TMS B0,TMS B1,TRST B0,TRST B1,A0B0,A1B0,A0B1,A1B1,TDI (01-06),A001,A101)I IHInput High Current(Input and I/O pins with pull-up resistors:TDI B0,TDI B1,TMS B0,TMS B1,TRST B0,TRST B1,A0B0,A1B0,A0B1,A1B1,TDI (01-06),A001,A101)V IN =V CC5.0µAI OFFPower-off Leakage CurrentOutputs and I/O pins without pull-up resistors V CC =0V,V IN =3.6V (Note 3)±5.0µA Outputs and I/O pins with pull-up resistors±200µA I OZ Maximum TRI-STATE Leakage Current ±5.0µAOutputs and I/O pins without pull-up resistors I CC Maximum Quiescent Supply Current V IN =V CC or GND 3.8mA I CCDMaximum Dynamic Supply CurrentV IN =V CC or GND,Input Freq =25MHz68mANote 3:Guaranteed by equivalent test method.AC Electrical Characteristics:Scan Bridge ModeOver recommended operating supply voltage and temperature ranges unless otherwise specified (Note 5).Symbol Parameter Conditions Typ Max Units t PHL ,Propagation Delay 8.513.5ns t PLH TCK B0to TDO B0or TDO B1t PHL ,Propagation Delay 8.514.0ns t PLH TCK B1to TDO B0or TDO B1t PHL ,Propagation Delay 7.512.5ns t PLH TCK B0to TDO (01-06)t PHL ,Propagation Delay 7.513.0ns t PLH TCK B1to TDO (01-06)t PHL ,Propagation Delay 8.012.0ns t PLH TMS B0to TMS B1t PHL ,Propagation Delay 8.012.0ns t PLH TMS B1to TMS B0t PHL ,Propagation Delay 8.012.0ns t PLH TMS B0to TMS (01-06)t PHL ,Propagation Delay 8.012.0ns t PLH TMS B1to TMS (01-06)t PHL ,Propagation Delay 8.012.0ns t PLH TCK B0to TCK B1t PHL ,Propagation Delay 8.012.0ns t PLH TCK B1to TCK B0t PHL ,Propagation Delay 7.512.0ns t PLH TCK B0to TCK (01-06)t PHL ,Propagation Delay 7.512.0ns t PLH TCK B1to TCK (01-06)t PHL ,Propagation Delay 11.518.0ns t PLH TCK B0to TRST B1t PHL ,Propagation Delay 11.518.0nst PLHTCK B1to TRST B0S C A N S T A 11210SCANSTA112 AC Electrical Characteristics:Scan Bridge Mode(Continued)Over recommended operating supply voltage and temperature ranges unless otherwise specified(Note5).Symbol Parameter Conditions Typ Max Unitst PHL,Propagation Delay12.018.5nst PLH TCK B0to TRST(01-06)t PHL,Propagation Delay12.018.5nst PLH TCK B1to TRST(01-06)t PHL Propagation Delay8.512.5ns TCK Bn to TRIST Bnt PHL Propagation Delay8.012.0ns TCK Bn to TRIST(01-03)t PZL,Propagation Delay9.014.5nst PZH TCK Bn to TDO Bn or TDO(01-06)t PHL,Propagation Delay 6.09.0nst PLH An to YnAC Timing Characteristics:Scan Bridge ModeOver recommended operating supply voltage and temperature ranges unless otherwise specified(Notes4,5).Symbol Parameter Conditions Min Max Unitst S Setup Time 2.5ns TMS Bn to TCK Bnt H Hold Time 1.5ns TMS Bn to TCK Bnt S Setup Time 3.0ns TDI Bn to TCK Bnt H Hold Time 2.0ns TDI Bn to TCK Bnt S Setup Time 1.0ns TDI(01-06)to TCK Bnt H Hold Time 3.5ns TDI(01-06)to TCK Bnt REC Recovery Time 1.0ns TCK Bn from TRST Bnt W Clock Pulse Width t R/t F=1.0ns10.0ns TCK Bn(H or L)t W L Reset Pulse Width t R/t F=1.0ns 2.5ns TRST Bn(L)F MAX Maximum Clock Frequency(Note6)t R/t F=1.0ns25MHzNote4:Guaranteed by Design(GBD)by statistical analysisNote5:R L=500Ωto GND,C L=50pF to GND,t R/t F=2.5ns,Frequency=25MHz,V M=1.5VNote6:When sending vectors one-way to a target device on an LSP(such as in FPGA/PLD configuration/programming),the clock frequency may be increased above this specification.In Scan Mode(expecting to capture returning data at the LSP),the F MAX must be limited to the above specification.11AC Electrical Characteristics:Stitcher Transparent ModeOver recommended operating supply voltage and temperature ranges unless otherwise specified (Note 5).Symbol ParameterConditionsTypMax Units t PHL ,Propagation Delay12.5nst PLH TDI B0to TDO B1,TDI B1to TDO B0t PHL ,Propagation Delay12.5nst PLH TDI B0to TDO 01,TDI B1to TDO 01t PHL ,Propagation Delay 12.5nst PLH TDI LSPn to TDO LSPn+1t PHL ,Propagation Delay12.5nst PLH TMS B0to TMS B1,TMS B1to TMS B0t PHL ,Propagation Delay12.5nst PLH TMS B0to TMS (01-06),TMS B1to TMS (01-06)t PHL ,Propagation Delay12.5nst PLH TRST B0to TRST B1,TRST B1to TRST B0t PHL ,Propagation Delay12.5nst PLHTRST B0to TRST (01-06),TRST B1to TRST (01-06)Timing Diagrams20051236Waveforms for an Unparked STA112in the Shift-DR (IR)TAP Controller StateS C A N S T A 112 12Timing Diagrams(Continued)20051238Reset Waveforms20051239Output Enable WaveformsCapacitance &I/O CharacteristicsRefer to National’s website for IBIS models at /scanSCANSTA11213Physical Dimensionsinches (millimeters)unless otherwise noted100-Pin BGANS Package Number SLC100a Ordering Code SCANSTA112SM100-Pin TQFPNS Package Number VJD100a Ordering Code SCANSTA112VSS C A N S T A 112 14NotesLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implant into the body,or(b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification(CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas CustomerSupport CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerSupport CenterEmail:ap.support@National SemiconductorJapan Customer Support CenterFax:81-3-5639-7507Email:jpn.feedback@Tel:81-3-5639-7560 SCANSTA112 7-port Multidrop IEEE 1149.1 (JTAG) MultiplexerNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

TP112中文资料

TP112100Base-TX/FX Converter1TP112-DS-P02 Jan 5, 2000Featuren 100Base-TX IEEE 802.3u compatible n Full and Half duplex with Auto-negotiation n Fully integrated adaptive equalizers n 125MHz clock generator and clock recoveryn Include transmit waveform shaping to reduce EMI andfiltern Include baseline wander correctionn Support one TX interface and one Fiber moduleinterface(ECL interface).n Support transmit, receive/link, full duplex LED n Single 5 Voltage supply operation n 128-pin PQFPGeneral DescriptionThe TP112 is a single chip media converter for 100Base-TX to 100Base-FX. The TP112 support one 100Base-TX port over CAT5 twisted pair cable and one ECL interface to connect with fiber module to apply in 100Base-TX/FX converter application. On the 100Base-TX side, The TP112 is directly connected to external transformersThe chip performs data recovery, clock recovery, adaptive equalization, auto negotiation, and baseline wander correction function. The TP112 is compliant with the IEEE 802.3u standard.Typical Applicationn 100Base-TX to 100Base-FX ConverterTP1122TP112-DS-P02 Jan 5, 2000PIN AssignmentsNC A G N DFXRDP FXRDM FXSD AVCC FXTDM FXTDP AGND BGRES DGND BGGND DVCC DVCC FXLRLED*HALFONLYMDC MDIO NCNC DVCC NC DVCC DVCC FXTLED*DGND TXER1NC AGND NC NC AVCC NC NC AGND DVCC OSCI/X1X2DGNC DVCC DGND NC FDXLED*NC NC NC DVCC NC NC RESET*TXLED*LRLED*DGND RXD00RXD10T X E R 0T X D 30T X D 20T X D 10T X D 00D V C CT X C L K 0T X E N 0DGND R X D 01R X D 11R X D 21R X D 31R X C L K 1DVCC R X E R 1R X D V 1N CD V C CD G N DFORCEONTXD31TXD21TXD11TXD01TXCLK1T X E N 1N CD V C CN CD V C CD G N DTMODENC NC RXD20RXD30RXCLK0DVCC RXER0RXDV0N CD G N DA V C CAVCC A V C CA V C CA V C CDVCC G N DAVCC T X O PT X O MA G N DA G N DR X I PR X I MA G N DAGND AVCC A G N DA V C CN CA G N DN CN CA V C CA G N DN CA V C CA G N DA G N DA V C CTP1123TP112-DS-P02Jan 5, 2000PIN DescriptionTYPE DESCRIPTION I Used as Input pin O Used as Output pin I/O Used as Input and Output pin O Used as Output with Open DrainPIN NO. LABEL TYPE DESCRIPTION Media Connections104,105 RXIP ,RXIM IReceiver Pair Differential data from external transformers RD ± pair. 111,110 TXOP ,TXOM OTransmit Pair Differential data to external transformers TD ± pair. 1,2 FXRDP ,FXRDM IFiber Receiver Data Pair Used to receiver the data from the fiber transceiver module, need external pull high resistor and pull low resistor, depend on impedance match of the fiber transceiver module. 8,7 FXTDP ,FXTDM OFiber Transmit Data Pair It used as output the data into the fiber transceiver module, need external pull high resistor and pull low resistor, depend on impedance match of the fiber transceiver module. 3 FXSD IFiber Signal Detect Used as an input pin from the Fiber transceiver module to indicate a valid signal quality had been detect.MII Interface59 30 TXER0 TXER1 ITransmit Error Active high. When an error happened in the transmit datastream.52 39 TXEN0 TXEN1 ITransmit Enable Active high. Indicate 4B data valid on TXD[3:0]53 35 TXCLK0 TXCLK1 I/OTransmit Clock Output is 25MHz continuous clock.58,57,56,55 31,32,33,34 TXD[3:0]0 TXD[3:0]1 ITransmit Data Input 4B transmit data.65 45 RXDV0 RXDV1 O3sReceive Data valid Active high. Indicates that a received frame is in progress,and data on RXD pin is valid 70 46 RXER0 RXER1 OReceive Error It Indicate that there's an error during a receive frame whenhigh72 47 RXCLK0 RXCLK1 OReceive Clock 25MHz output. The clock is recovered from the incoming dataon the cable inputs 73,74,75,76 48,49,50,51 RXD[3:0]0 RXD[3:0]1 OReceive Data Output 4B data output and synchronously to RXCLK.TP1124TP112-DS-P02 Jan 5, 2000PIN Description (continued)PIN NO. LABEL TYPE DESCRIPTION Modes36 MDC IManagement Data Clock MII management data clock input, maximum clock rate is 2.5MHz37 MDIO I/OManagement Data I/O MII management data input/output 19 TMODE ITest Mode Active high. Set TP112 into test mode, and low for normal operation. There’s an internal pull low resistor so default is normal operation18 HALFONLY I/IPL Half Duplex Mode Only 1: half duplex 0: full duplex15 FORCEON I/IPLForce Mode Enable 1: force mode enable0: auto negotiation mode enableLEDs69 FDXLED* OFull Duplex LED Before link OK, this pin is tri-stated. After link OK this pin indicate current duplex operation for TP112. High for half duplex and low for full duplex 78 28 LRLED* FXLRLED* OLink/Receive LED Active low. Indicates the link status of the port, driven lowwhen link to the port is good. Output for 20mS clock while the TP112 is receiving data from external media 79 27 TXLED* FXTLED* OTransmit LED Active low. Indicates that data is being transmittingReset & Clock80 RESET* IReset Active low. Reset TP112, remain low at least 1us. 91 OSCI/X1 IOscillator input or crystal input (25MHz±50ppm).90 X2 O Crystal output. Leave it unconnected (i.e., as a NC pin) whenoscillator is used.Current Reference10 BGRES IBand Gap Resistor A 6.2KOhm 1% resistor that supply 200uA reference current for receive11 BGGND IBand Gap Resistor Ground Band gap resistor ground reference inputTP1125TP112-DS-P02Jan 5, 2000PIN Description (continued)PIN NO.LABELTYPEDESCRIPTIONPower & Ground 4,5,12,97,98, 103,108,112, 114,117,116 121,126 AVCC I Analog VCC +5V 9,93,101,102, 106,107,109, 113,115,120, 122,123,127,128 AGND I Analog Ground 0V13,16,17,23, 25,26,41,43, 61,62,77,83, 86,88,92, DVCC I Digital VCC +5V 14,29, 42,54,63,71, 85,87,89 DGND I Digital Ground 0V 6,20,21,22,24, 38,40,44,60,64, 66,67,68,81,82, 84,94,95,96, 99,100,118,119,124,125NCNo ConnectionTP1126TP112-DS-P02 Jan 5, 2000Absolute Maximum RatingSupply Voltage.......................VCC –0.25 to VDD +0.25V Storage Temperature ....................................-65 to 150°C Ambient Operating Temperature (Ta).................0 to 70°CStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Functional operation under these conditions is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect product reliability.Electricaln Operating ConditionsParameter Sym. Min. Typ. Max. Unit Conditions AVCC 4.75 5 5.25 VSupply Voltage DVCC 4.75 5 5.25 V VCC =5.0VPower Consumption ICC TBD Wn Input ClockParameter Sym. Min. Typ. Max. Unit Conditions Frequency 25 MHz Frequency Tolerance -50 +50 PPMn I/O Electrical CharacteristicsParameter Sym. Min. Typ. Max. Unit Conditions Input Low Voltage I V IL 0.8 V Input High Voltage I V IH 2.0 V Output Low Voltage O V OL 0.4 V I OH =4mA, VCC=5.0V Output High voltage O V OH 2.4 V I OL =4mA, VCC=5.0Vn TX Transceiver Electrical CharacteristicsParameter Sym. Min. Typ. Max. Unit ConditionsTransmitterPeak Differential Output Voltage V P 0.95 1.0 1.05 V Signal Amplitude Symmetry - 98 100 102 % Signal Rise/Fall Time T RF 3 4 5 ns Rise/Fall Time Symmetry T RFS 0.5 ns Duty Cycle Distortion - 0.5 ns Overshoot V O 5 %TP112 Order InformationPart No. PIN NoticeTP112 128 PIN PQFP -7TP112-DS-P02Jan 5, 2000TP1128TP112-DS-P02 Jan 5, 2000Package DetailQFP 128L Outline DimensionsUnit: Inches/mmDimensions In InchesDimensions In mmSymbol Min. Nom. Max. Min. Nom. Max. A 1 0.010 0.014 0.018 0.25 0.35 0.45 A 2 0.107 0.112 0.117 2.73 2.85 2.97b 0.007 0.009 0.011 0.17 0.22 0.27c 0.004 0.006 0.008 0.09 0.15 0.20 H D 0.669 0.677 0.685 17.00 17.20 17.40 D 0.547 0.551 0.555 13.90 14.00 14.10 H E 0.906 0.913 0.921 23.00 23.20 23.40 E 0.783 0.787 0.791 19.90 20.00 20.10 e - 0.020 - - 0.50 - L 0.025 0.035 0.041 0.65 0.88 1.03 L 1 - 0.063 - - 1.60 - y - - 0.004 - - 0.10θ0°-12°0°-12°Note:1. Dimension D & E do not include mold protrusion.2. Dimension B does not include dambar protrusion.Total in excess of the B dimension at maximum material condition. Dambar cannot be located on the lower radius of the foot.。

TS12中文资料