第9章_MC9S12XS128定时器模块及其应用实例

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

MC9S12XS128 PIT模块

言归正传,开始讲PIT,讲PIT,我准备先简单讲讲寄存器,之前不讲主要是基本上买的到的书都是DG128的,里面关于IO口的寄存器和PWM的寄存器都是完全可以照搬的,而这一章的东西照搬是要出问题的。

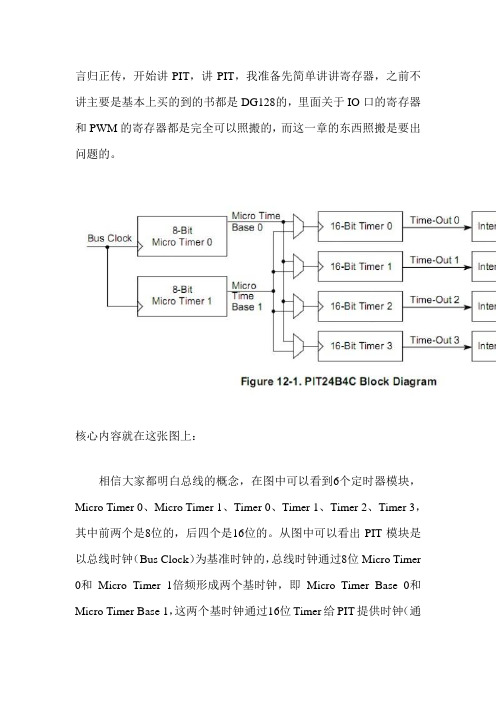

核心内容就在这张图上:相信大家都明白总线的概念,在图中可以看到6个定时器模块,Micro Timer 0、Micro Timer 1、Timer 0、Timer 1、Timer 2、Timer 3,其中前两个是8位的,后四个是16位的。

从图中可以看出PIT模块是以总线时钟(Bus Clock)为基准时钟的,总线时钟通过8位Micro Timer 0和Micro Timer 1倍频形成两个基时钟,即Micro Timer Base 0和Micro Timer Base 1,这两个基时钟通过16位Timer给PIT提供时钟(通过寄存器PITMUX设置)。

原理讲完了,其实相对于PIT模块是一个24位的定时器(51单片机最多也就16位),这个计数范围还是蛮大的。

下面是一些寄存器的解释,解释完还是看代码吧。

S12PIT24B4CV1是一个模数递减计数器。

首先给计数寄存器设定一个初值,每经过一个总线周期,计数器进行一次减一操作,当计数器自减溢出时,触发中断。

因为总线周期是已知的,即可以通过计数器自减实现定时。

在XS128PIT模块中,需要用到得是如下几个寄存器。

1)、PIT Contorl and force Lad Micro Timer Register(PITCFLMT)该寄存器用于PIT模块的使能设置和工作方式设置。

通常设置该寄存器中的PITE为即可,即PITCFLMT_PITE=1,使PIT使能。

2)、PIT Channel Enable Register(PITCE)该寄存器用于对PIT模块中的4个通道使能进行设置。

如果使用某个通道时,对对应位进行置一即可,即PITCE_PCEx=1,其中x代表通道序号,为0~3。

MC9S12XS128中文资料

PWMCNTx:

PWM通道计数寄存器。

每个通道都有一个独立的8位计数器,其计数速率由所选择的时钟源决定。计数器的值可以随时读取而不影响计数器运行,也不影响PWM波形输出。在左对齐模式时,计数器从0计数至周期寄存器的值减1;在中心对齐模式,计数器从0计数至周期寄存器的值,然后再倒计数至0。

CFORC:

定时器比较强制寄存器。复位值为0x00。

FOCx=1将强制该位对应通道产生输出比较成功动作,但CxF中断标志位不置位。任何通道的强制比较成功动作若与普通比较成功动作同时发生,则强制比较成功动作优先发生,且CxF标志位不会置位。

被置位后瞬间将自动清除该位,所以任何时候对该寄存器的读动作都将返回0x00。

OC7M:

输出比较通道7屏蔽寄存器。复位值为0x00。

Setting the OC7Mx (x ranges from 0 to 6) will set the corresponding port to be an output port when the corresponding TIOSx (x ranges from 0 to 6) bit is set to be an output compare and the corresponding OCPDx (x ranges from 0 to 6) bit is set to zero to enable the timer port.A successful channel 7 output compare overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.

MC9S12XS128例程

SCI程序串行通信时MCU与外部设备之间进行通信的一种简单而有效的硬件方法。

无论用查询方式还是中断方式进行串行通信编程,在程序初始化时均必须对SCI进行初始化。

初始化主要包括波特率设置、通信格式的设置、发送接收数据方式的设置等。

对SCI进行初始化,需要设置如下几部分:(1)定义波特率一般选内部总线时钟为串行通信的时钟源。

通过设置SCI波特率寄存器SCI0BD的波特率选择位SBR[12:0],来选择合适的分频系数。

(2)写控制字到SCI控制寄存器1(SCI0CR1)设置是否允许SCI、数据长度、输出格式、选择唤醒方法、是否校验等。

(3)写控制字到SCI控制寄存器2(SCI0CR2)设置是否允许发送与接收、是中断接收还是查询接收等。

串行通信程序如下:/** write in “Init.h” **/#include <hidef.h> /* common defines and macros */#include "derivative.h" /* derivative-specific definitions *///void InitBusClk(void); //可以不使用锁相环void InitSci(void);/** write in “Init.c” **///初始化程序#include "Init.h"/*//------------初始化Bus Clock------------//void InitBusClk(void) {DisableInterrupts;CLKSEL=0X00; //PLLSEL 1 : Bus Clock=PLLCLK/2// 0 : Bus Clock=OSCCLK/2PLLCTL_PLLON=1; //开启PLLSYNR=0; //OSCCLK=16MHzREFDV=0X0F; //PLLCLK=2*OSCCLK*[(1+SYNR)/(1+REFDV]=32/16=2MHz while(!(CRGFLG_LOCK==1)); //直到LOCK=1,when PLL is ready,退出循环CLKSEL_PLLSEL=1; //PLLSEL 1 : Bus Clock=PLLCLK/2=2MHz/2=1MHz// 0 : Bus Clock=OSCCLK/2=16M/2=8MHz}*///---------------初始化SCI---------------//void InitSci(void){SCI0BD=4545; //设波特率为110//SCI baud rate = SCI module clock/(16*SCIBD)=Bus Clock/(16*SCIBD)// = 8MHz/(16*4545)=500kHz/4545=110bps//SCIBD : SBR12-SBR0,Value from 1 to 8191SCI0CR1=0;SCI0CR2=0X2C; // 0010 1100 RIE=1,TE=1,RE=1// RIE=1 RDRF and OR interrupt requests enabled// TE=1 Transmitter enabled// RE=1 Receiver enabled}/** write in “SCI.h” **///函数声明unsigned char SciRead();void SciWrite(byte);/** write in “SCI.c” **///串行通信程序#include "Init.h"#include "SCI.h"//---------------读SCI数据---------------//unsigned char SciRead(){if(SCI0SR1_RDRF==1){//数据从移位寄存器传送到SCI数据寄存器SCIDRL//SCI0SR1_RDRF==1表明数据寄存器SCI0DRL为满,可以接收新的数据SCI0SR1_RDRF=1; //读取SCI数据寄存器会将RDRF清除,重新置位return SCI0DRL; //返回数据寄存器的数值}}//---------------写SCI数据---------------//void SciWrite(byte sci_value){while(!(SCI0SR1&0X80));//SCI0SR1_TDRE==1表明数据寄存器SCI0DRL为空,可以发送新的数据SCI0DRH=0;SCI0DRL=sci_value; //发送新的数据至数据寄存器SCI0DR}//---------------中断程序-----------------//#pragma CODE_SEG NON_BANKEDinterrupt 20 void Sci_Intrrupt(void){ //SCI的中断向量号为20byte text;DisableInterrupts; //关中断text=SciRead(); //接收数据寄存器SCI0DRL中的数据asm nop;asm nop;SciWrite(text); //发送数据至数据寄存器SCI0DRLDDRA=0XFF; //设A口为输出,用来显示是否执行中断,可以不用PORTA_PA6=!PORTA_PA6;EnableInterrupts; //开中断}#pragma CODE_SEG DEFAULT/** write in “main.c”” **/#include "Init.h"#include "SCI.h"void main(void) {/* put your own code here */_DISABLE_COP(); //关看门狗DisableInterrupts; //关中断//InitBusClk();InitSci();EnableInterrupts; //开中断for(;;) {// _FEED_COP(); /* feeds the dog */} /* loop forever *//* please make sure that you never leave main */}A/D转换应用实例要让ATD 开始转换工作,必须经过以下三个步骤:1.将ADPU 置1,使ATD 启动;2.按照要求对转换位数、扫描方式、采样时间、时钟频率及标志检查等方式进行设置;3.发出启动命令;如果上电默认状态即能满足工作要求,那么只要将ADPU 置1,然后通过控制寄存器发出转换命令,即可实现转换。

飞思卡尔MC9S12XS128功能模块驱动

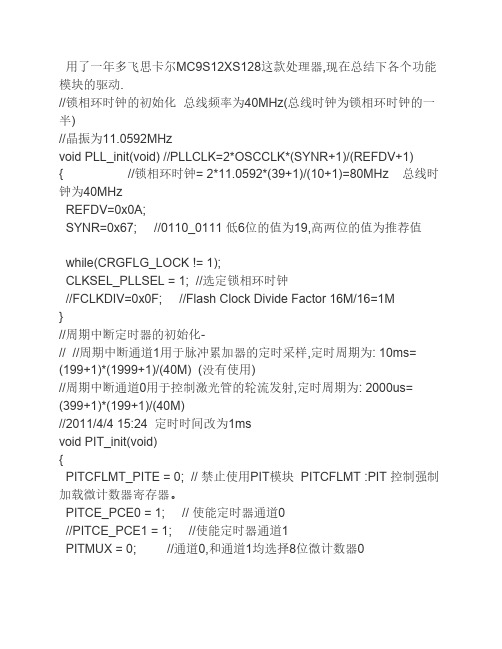

用了一年多飞思卡尔MC9S12XS128这款处理器,现在总结下各个功能模块的驱动.//锁相环时钟的初始化总线频率为40MHz(总线时钟为锁相环时钟的一半)//晶振为11.0592MHzvoid PLL_init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) { //锁相环时钟= 2*11.0592*(39+1)/(10+1)=80MHz 总线时钟为40MHzREFDV=0x0A;SYNR=0x67; //0110_0111 低6位的值为19,高两位的值为推荐值while(CRGFLG_LOCK != 1);CLKSEL_PLLSEL = 1; //选定锁相环时钟//FCLKDIV=0x0F; //Flash Clock Divide Factor 16M/16=1M}//周期中断定时器的初始化-// //周期中断通道1用于脉冲累加器的定时采样,定时周期为: 10ms= (199+1)*(1999+1)/(40M) (没有使用)//周期中断通道0用于控制激光管的轮流发射,定时周期为: 2000us= (399+1)*(199+1)/(40M)//2011/4/4 15:24 定时时间改为1msvoid PIT_init(void){PITCFLMT_PITE = 0; // 禁止使用PIT模块 PITCFLMT :PIT 控制强制加载微计数器寄存器。

PITCE_PCE0 = 1; // 使能定时器通道0//PITCE_PCE1 = 1; //使能定时器通道1PITMUX = 0; //通道0,和通道1均选择8位微计数器0//修改时间只需要改下面四行PITMTLD0 = 199; //向8位微计数器中加载的值PITLD0 = 199; //向16位计数器中加载的值//PITMTLD1 = 39; //向8位微计数器中加载的值 8位,最大值不要超过255//PITLD1 = 1999; //向16位计数器中加载的值PITINTE |= 0x01; //使能定时器通道0的中断PITCFLMT_PITE = 1;//使能PIT模块}//脉冲累加器的初始化, PT7口外接光电编码器//最新修改: 2011/3/25 16:53void PT7_PulAcc_Init(void){DDRT &= 0x77;//设置PT7,PT3口为输入(硬件上PT7,PT3通过跳线联到了一块)PERT |= 0x80; //使能通道7的上拉电阻PPST &= 0x7f; //电阻设为上拉电阻TCTL4 &= 0x3f; //禁止PT3的输入捕捉功能PACTL = 0x50; //启动脉冲累加计数器,上升沿触发,禁止触发中断和溢出中断,主定时器禁止}//通道1用于控制舵机1 PWM 高电平有效,//通道3用于控制电机1 PWM 低电平有效,这与前两代车高电平有效有区别!!!!!//通道7用于给上排激光管提供PWM信号 PWM高电平有效!!!!!//通道6用于给下排激光管提供PWM信号 PWM高电平有效!!!!!// 2011-03-17 7:56 增加了A端口的使用新增通道6//2011-6-9 23:03 //增加了通道4,5的联合使用,用于控制下排方向舵机 void PWM_init(void){PWME = 0x00;//PWM禁止PWMPRCLK = 0x03; // ClockA=40M/8=5M, Clock B = 40M/1=40M PWMSCLB = 10; // Clock SB= 40/2*10= 2MHz(供电机)PWMSCLA = 5; // SA = Clock A/2*5 = 5M/10 = 500K = SA 用于控制舵机PWMPOL = 0xe2; //1110_0010通道7,通道6与通道1、通道5先输出高电平然后输出低电平,POLx=1先输出高电平后输出低电平; PPOLx=0先输出低电平)PWMCAE = 0x00; // 左对齐输出(CAEx=0为左对齐,反之为中心对齐)//PWMCLK = 0010_1010 (0 1 4 5位控制SA_1;或A_0; 2 3 6 7位控制SB_1 或B_0)//为PWM通道1选择时钟 SA(500KHz),//为PWM通道5选择时钟 SA(500KHz),//为通道3选择时钟 SB(10MHz)//为通道7选择时钟B(40MHz)//为通道6选择时钟B(40MHz)PWMCLK = 0x2A; //0010_1010PWMCTL = 0x70; //0111_0000 CON45=1,把通道4,5联合使用。

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释//**************************************************************************// 武狂狼2014.5.1 整理// 新手入门的助手////***************************************************************************注释不详细/*********************************************************/函数名称:void ATD0_init(void)函数功能:ATD初始化入口参数:出口参数:/***********************************************************/void ATD0_init(void){ATD0DIEN=0x00; //使用模拟输入功能|=1;数字输入功能// ATD0CTL0=0x07; //Bit[3:0]WRAP[3:0] 反转通道选择位ATD0CTL1=0x40; // 12位精度,采样前不放电 Bit[7]ETRIGSEL(外部触发源选择位。

=0选择A/D通道AN[15:0] |=1选择 ERTIG3~0)和Bit[3:0]ETRIGCH[3:0]选择外部触发通道// Bit[6:5]SRES[1:0]A/D分辨率选择位。

Bit[4]SMP_DIS =0采样前不放电|=1采样前内部电容放电,这会增加2个A/D时钟周期的采样时间,有助于采样前进行开路检测ATD0CTL2=0x40; // 快速清零,禁止中断,禁止外部触发ATD0CTL3=0x90; // 右对齐,转换序列长度为2,非FIFOATD0CTL4=0x03; // 采样时间4个周期,PRS=31,F(ATDCLK)=F(BUS)/(2(PRS+1))// ATD0CTL5=0x30; //启动AD转换序列//:对每项数据采集时,用到哪个通道采样可在相应子函数内设置某一通道(见Sample_AD.c)while(!ATD0STAT2L_CCF0);/*********************************************************/函数名称:void PIT_init(void)函数功能:初始化PIT 设置精确定时时间(1s)入口参数:无出口参数:无说明:无/***********************************************************/void PIT_init(void){PITCFLMT=0x00; //禁止PIT模块Bit[7] PITE:PIT模块使能位,0禁用|1使能// Bit[6] PITSWAI:等待模式下PIT停止位,0等待模式下,PIT模块正常运行| 1等待模式下,PIT模块停止产生时钟信号,冻结PIT模块// Bit[5] PITFRZ: 冻结模式下PIT计数器冻结位。

飞思卡尔MC9S12XS128(定时器)ECT寄存器详解

1、定时器IC/OC功能选择寄存器TIOSIOS[7..0]IC/OC功能选择通道0 相应通道选择为输入捕捉(IC)1 相应通道选择为输出比较(OC)2、定时器比较强制寄存器 CFORCFOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。

【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。

3、输出比较7屏蔽寄存器 OC7MOC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于OC7的管理之下。

OC7M中的各位与PORTT口寄存器的各位一一对应。

当通过TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状态。

【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7DOC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。

当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。

OC7D中的各位与PORTT口寄存器的各位一一对应。

当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输出到PORTT的对应引脚。

【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。

比如:OC7M0=1,则通道0处在OC7的管理下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。

飞思卡尔2014mc9s12xs128学习及智能车制作笔记

S128学习笔记(一)GPIO 模块S128 IO操作主要有三个寄存器数据寄存器(PORTX)数据方向寄存器(DDRX) 上拉上拉电阻控制寄存器PUCR)一. GPIO概述通用I/O:GPIO(General Purpose I/O),是I/O的最基本形式,它是一组输入或输出引脚,有时也称为并行I/O(parallel I/O)。

作为普通输入引脚,MCU内部程序可以读取该引脚,知道该引脚是“1”(高电平)或“0”(低电平),即开关量输入。

作为普通输出引脚,MCU内部程序由该引脚输出“1”(高电平)或“0”(低电平),即开关量输出。

大多数通用I/O引脚可以通过编程来设定工作方式为输入或输出,称之为双向通用I/O。

2. I/O口的使用方法MC9S12DG128 MCU有10个普通I/O口,分别是A口、B口、E口、H口、J口、K口、M 口、P口、S口、T口。

这些引脚中的大部分具有双重功能,其中A、B、E、K口只用做GPIO 功能,这里仅讨论它们编程方法。

使用这些I/O口主要设置如下寄存器:1)数据方向寄存器(Data Direction Register x,DDRx)DDRx的第7~0位分别记为DDRx7~DDRx0,这些位分别控制着x口引脚PORTx7~PORTx0是输入还是输出,若DDRxn=0,则引脚PORTAxn为输入,若DDRxn=1,则引脚PORTxn为输出。

复位时DDRx为$00。

(注:x代表A、B、E、K口中的某一个,n表示某一位)2)数据寄存器(Port x I/O Register,PORTx)PORTx的第7~0位分别记为PORTx7~PORTx0。

若A口的某一引脚PORTxn被定义。

成输出,程序使x口I/O寄存器PORTx的相应位PORTxn=0,则引脚PORTxn输出“低电平”;程序使PORTxn=1,则引脚PORTxn输出“高电平”。

若x口的某一引脚PORTxn被定义成输入,程序通过读取x口I/O寄存器PORTx,获得输入情况,0表示输入为“低电平”,1表示输入为“高电平”。

飞思卡尔MC9S12XS128单片机中断优先级设置简易教程

本教程试图用最少的时间教你飞思卡尔XS128单片机的中断优先级设置方法和中断嵌套的使用,如果是新手请先学习中断的基本使用方法。

先来看看XS128 DataSheet 中介绍的相关知识,只翻译有用的:七个中断优先级每一个中断源都有一个可以设置的级别高优先级中断的可以嵌套低优先级中断复位后可屏蔽中断默认优先级为1同一优先级的中断同时触发时,高地址(中断号较小)的中断先响应注意:高地址中断只能优先响应,但不能嵌套同一优先级低地址的中断下面直接进入正题,看看怎么设置中断优先级:XS128中包括预留的中断一共有128个中断位,如果为每个中断都分配一个优先级寄存器的话会非常浪费资源,因此飞思卡尔公司想出了这样一种办法:把128个中断分为16个组,每组8个中断。

每次设置中断时,先把需要的组别告诉某个寄存器,再设置8个中断优先寄存器的某一个,这样只需9个寄存器即可完成中断的设置。

分组的规则是这样的:中断地址位7到位4相同的中断为一组,比如MC9SX128.h中这些中断的位7到位3都为D,他们就被分成了一组。

0~F正好16个组。

INT_CFADDR就是上面说到的用来设置组别的寄存器:我们需要设置某个组别的中断时,只要写入最后8位地址就行了,比如设置SCI0的中断优先级,就写入0xD0。

设置好组别之后,我们就要该组中相应的中断进行设置,设置中断的寄存器为这其实是一组寄存器,一共有8个,每个都代表中断组中的一个中断。

对应规则是这样的:中断地址的低四位除以2比如还是SCI0,低四位是6,除以二就是3,那么我们就需要设置INT_CFDATA3 往INT_CFDATAx中写入0~7就能设置相应的中断优先级了拿我本次比赛的程序来举个例子:我们的程序中需要3个中断:PIT0,PORTH,SCI0。

PIT0定时检测传感器数值,PORTH连接干簧管进行起跑线检测,SCI0接收上位机指令实现急停等功能。

因此中断优先级要SCI0>PORTH>PIT0。

基于MC9S12XS128单片机智能寻迹小车的设计

基于MC9S12XS128单片机智能寻迹小车的设计摘要:本文给出了智能小车寻迹系统的软硬件方案设计和开发流程。

采用飞思卡尔mc9s12xs128单片机作为智能小车控制芯片,设计了电源、电机驱动、激光传感器以及测速等模块,小车的速度、转向控制采用pid控制方法,测试结果表明,小车能够平稳实现寻迹功能。

关键词:智能寻迹电机驱动激光传感器 pid控制中图分类号:u26 文献标识码:a 文章编号:1674-098x(2013)05(b)-0080-02该文以飞思卡尔杯智能车大赛为研究背景,研究了智能寻迹小车的软硬件方案设计和开发流程。

硬件电路方面采用飞思卡尔mc9s12xs128作为核心处理器,通过对比不同设计方案的性能,给出了智能小车电源、电机驱动、光电传感器以及测速等模块的设计方案并加以实现。

通过大量的实验调试完成了智能车的组装与机械部分调整,使得智能车结构更为合理。

在软件方面,主要设计了主程序、光电信号采集程序、pid控制程序、电机和舵机驱动程序等相关程序。

实验及实际比赛结果表明,软硬件配合良好,整个车辆稳定运行[1][2]。

1 系统总体方案智能车总体上分为单片机系统、传感器模块,电机驱动模块和显示模块。

首先,单片机通过激光传感器实现对路面黑色中心位置信息的实时检测,同时对反馈回来的偏移中心轨道的大小的信息进行算法处理后发出方向控制命令,输出相应的驱动信号至电机驱动模块,同时编码器测速装置也在实时获取小车速度,利用pid控制方法控制舵机和直流电机,提高小车的稳定性。

通过lcd显示器方便进行人机交互。

系统总体框图如图1所示。

2 硬件电路设计2.1 主控制器小车控制芯片采用freescale的mc9s12xs128单片机。

mc9s12xs128是一款增强型16位单片机,在mc9s12xe系列基础上去掉xgate协处理器,采用cpu12x的v2内核,可运行在40mhz总线频率上,它不仅在汽车电子、工业控制、中高档机电产品等应用领域具有广泛的用途,而且在flash存储控制及加密方面也有很强的功能。

x9 S12增强型定时器模块及其应用实例

第9章 S12增强型定时器模块

9.1 ECT 模块概述 9.2 ECT 模块的自由运行计数器及定时器基本寄存器 9.3 ECT 模块的输入捕捉功能及寄存器设置 9.4 ECT 模块的输出比较功能及寄存器设置 9.5 ECT 模块的脉冲累加器功能及寄存器设置 9.6 ECT 模块的模数递减计数器功能及寄存器设置 9.7 ECT 模块基础应用实例

9.2 输入捕捉模块框图

《基于 HCS 12的嵌入式系统设计》

1

Generated by Foxit PDF Creator © Foxit Software For evaluation only.

9.1 ECT 模块概述(5)

4. 模数递减计数器

《基于 HCS 12的嵌入式系统设计》

1. 输入捕捉

输入捕捉(Input Capture, IC):输入引脚上的 跳变沿(上升沿或下降沿)触发输入捕捉,将当 前自由运行计数器中的计数值复制到通道寄存 器中,并置位中断标志,如果允许中断,则产 生一次输入捕捉中断。 带保持寄存器的IC通道可以在不产生中断的条 件下,连续记录两次自由运行计数器的值。

9.1 ECT 模块概述(4)

2. 输出比较

输出比较(Output Compare,OC):根据需要设置 输出比较寄存器的值,自由运行计数器的值与输出 比较寄存器的值每隔4个总线周期比较一次,当两 者相等时,会在规定的通道引脚上输出预定的电平。 如果允许中断,会产生一次输出比较中断。

9.3 输出比较模块框图

9.1.1 ECT的基本组成与工作原理

ECT 组成:

♦ 1个16位自由运行计数器 ♦ 8个16位输入捕捉/输出比较通道 ♦ 2个16位脉冲累加器 ♦ 1个16位模数递减计数器MDC

mc9s12xs128程序教程

711 次

该寄存器是 0~7 通道 PWM 输出起始极性控制位,用来设置 PWM 输出的起始 电平。

用法:PWMPOL_PPOL0=1--- 通道 0 在周期开始时输出为高电平,当计数 器等于占空比寄存器的值时,输出为低电平。对外输出波形先是高电平然后再变 为低电平。

2、PWM 波形对齐寄存器 PWMCAE

该控制寄存器设定通道的级联和两种工作模式:等待模式和冻结模式。这 两种模式如图 10 和图 11 所示。

图 10 等待模式

图 11 冻结模式

只有当相应的通道关闭后,才能改变 这些控制字。 用法: PWMCTL_CON67=1 --- 通道6、7 级联成一个 16 位的 PWM 通道。此 时只有7 通道的控制字起作用,原通道 7 的使能位、PWM 输出极性选择位、时 钟选择控制位以及对齐方式选择位用来设置级联后的 PWM 输出特性 PWMCTL_CON67=0 --- 通道6,7 通道不级联 CON45、CON23、CON01 的用法同 CON67 相似。设置此控制字的意 义在于扩大了PWM 对外输出脉冲的频率范围。 PSWAI=1 --- MCU 一旦处于等待状态,就会停止时钟的输入。这样就不 会因时钟在空操作而费电;当它置为0,则MCU 就是处于等待状态,也允许 时钟的输入。 PFRZ=1 --- MCU 一旦处于冻结状态,就会停止计数器工作。 (责任编辑:dzsj8)

1、PWM 预分频寄存器 PWMPRCLK

PWMPRCLK 寄存器每一位如图 3 所示:

复位默认值:0000 0000B

813 次

图3 PWMPRCLK 寄存器

PWMPRCLK 寄存器包括 ClockA 预分频和 ClockB 预分频的控制位。ClockA、 ClockB 的值为总线时钟的 1/2n (0≤n≤7),具体设置参照图 4 和图 5

MC9S12XS128串口操作例程

MC9S12XS128串口操作例程MC9S12XS128 串口操作例程Code Warrior 4.7Target : MC9S12XS128Crystal: 16.000Mhzbusclock: 8.000MHzpllclock:16.000MHz本程序主要包括以下功能:1.设置锁相环和总线频率;2.IO口使用;3.共四路ATD使用及显示方法。

LED计数,根据灯亮可以读取系统循环了多少次************************************************************** ***************************/#include /* common defines and macros */#include /* derivative information */#include#include#include#pragma LINK_INFO DERIVATIVE "mc9s12xs128"#pragma CODE_SEG DEFAULT#define CR_as_CRLF TRUE // if true , you can use "\n" to act as CR/LF,// if false, you have to use "\n\r",but can get a higher speed static int do_padding;static int left_flag;static int len;static int num1;static int num2;static char pad_character;unsigned char uart_getkey(void){while(!(SCI0SR1&0x80)) ; //keep waiting when not emptyreturn SCI0DRL;}/*void uart_init(void) {SCI0CR2=0x0c;SCI0BDH=0x00;//16MHz,19200bps,SCI0BDL=0x1aSCI0BDL=0x34;//16MHz,9600bps,SCI0BDL=0x34}*/void uart_putchar(unsigned char ch){if (ch == '\n'){while(!(SCI0SR1&0x80)) ;SCI0DRL= 0x0d; //output'CR'return;}while(!(SCI0SR1&0x80)) ; //keep waiting when not empty SCI0DRL=ch;}void putstr(char ch[]){unsigned char ptr=0;while(ch[ptr]){uart_putchar((unsigned char)ch[ptr++]);}}static void padding( const int l_flag){int i;if (do_padding && l_flag && (len < num1))for (i=len; i<="" p="">uart_putchar( pad_character);}static void outs( char* lp){/* pad on left if needed */len = strlen( lp);padding( !left_flag);/* Move string to the buffer */while (*lp && num2--) uart_putchar( *lp++);/* Pad on right if needed */len = strlen( lp);padding( left_flag);}static void reoutnum(unsigned long num, unsigned int negative, const long base ){char* cp;char outbuf[32];const char digits[] = "0123456789ABCDEF";/* Build number (backwards) in outbuf */cp = outbuf;do {*cp++ = digits[(int)(num % base)];} while ((num /= base) > 0);if (negative) *cp++ = '-';*cp-- = 0;/* Move the converted number to the buffer and *//* add in the padding where needed. */len = strlen(outbuf);padding( !left_flag);while (cp >= outbuf)uart_putchar( *cp--);padding( left_flag);}static void outnum(long num, const long base ,unsigned char sign)//1, signed 0 unsigned{unsigned int negative;if ( (num < 0L) && sign ){negative=1;num = -num;}else negative=0;reoutnum(num,negative,base);}static int getnum( char** linep){int n;char* cp;n = 0;cp = *linep;while (isdigit(*cp))n = n*10 + ((*cp++) - '0');*linep = cp;return(n);}void printp( char* ctrl, ...){int long_flag;int dot_flag;char ch;va_list argp;va_start( argp, ctrl);for ( ; *ctrl; ctrl++) {/* move format string chars to buffer until a format control is found. */ if (*ctrl != '%') {uart_putchar(*ctrl);#if CR_as_CRLF==TRUEif(*ctrl=='\n') uart_putchar('\r');#endifcontinue;}/* initialize all the flags for this format. */dot_flag = long_flag = left_flag = do_padding = 0;pad_character = ' ';num2=32767;try_next:ch = *(++ctrl);if (isdigit(ch)){if (dot_flag)num2 = getnum(&ctrl);else {if (ch == '0')pad_character = '0';num1 = getnum(&ctrl);do_padding = 1;}ctrl--;goto try_next;}switch (tolower(ch)) {case '%':uart_putchar( '%');continue;case '-':left_flag = 1;break;case '.':dot_flag = 1;break;case 'l':long_flag = 1;break;case 'd':if (long_flag ==1 ){if(ch == 'D') {outnum( va_arg(argp, unsigned long), 10L , 0);continue;}else /* ch == 'd' */ {outnum( va_arg(argp, long), 10L,1);continue;}}else{if(ch == 'D') {outnum( va_arg(argp, unsigned int),10L,0);continue;}else /* ch == 'd' */{outnum( va_arg(argp, int), 10L,1); continue;}}case 'x': // X 无符号,x 有符号if (long_flag ==1 ){if(ch == 'X'){outnum( va_arg(argp, unsigned long), 16L,0); continue;}else /* ch == 'x' */{outnum( va_arg(argp, long), 16L,1); continue;}}else{if(ch == 'X'){outnum( va_arg(argp, unsigned int), 16L,0); continue;}else /* ch == 'x' */{outnum( va_arg(argp, int), 16L,1);continue;}} //如果按照16进制打印,将全部按照无符号数进行continue;case 's':outs( va_arg( argp, char*));continue;case 'c':uart_putchar( va_arg( argp, int));continue;default:continue;}goto try_next;}va_end( argp);}#pragma CODE_SEG __NEAR_SEG NON_BANKED void interrupt 20 SCI0_ISR(void){SCI0CR2_RIE=0;//此处为串口中断需要处理的事情uart_putchar(uart_getkey());PORTA_PA0=~PORTA_PA0;SCI0CR2_RIE = 1;}#pragma CODE_SEG DEFAULT//-----------------------------------------------------void setbusclock(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR=1;REFDV=1; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=32MHz;_asm(nop); //BUS CLOCK=16M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}//-----------------------------------------------------static void SCI_Init(void){SCI0CR1 =0x00;SCI0CR2 =0x2c; //enable Receive Full Interrupt,RX enable,Tx enable SCI0BD =0x68; //SCI0BDL=busclk/(16*SCI0BDL) //busclk 8MHz, 9600bps,SCI0BD=0x34//busclk 16MHz, 9600bps,SCI0BD=0x68//busclk 24MHz, 9600bps,SCI0BD=0x9C} //busclk 32MHz, 9600bps,SCI0BD=0xD0//busclk 40MHz, 9600bps,SCI0BD=0x106//-----------------------------------------------------void Dly_ms(int ms){int ii,jj;if (ms<1) ms=1;for(ii=0;ii<ms;ii++)< p="">for(jj=0;jj<2670;jj++); //busclk:16MHz--1ms}void main(void){unsigned char LedCnt=0;setbusclock();SCI_Init();DDRA=0xFF;PUCR_PUPBE=1;EnableInterrupts;for(;;){LedCnt=(LedCnt>0XFE?0:++LedCnt);Dly_ms(1000); //修改延时以修改数据发送频率//低电平灯亮用这句,注释掉下面那句PORTA_PA0=~PORTA_PA0;//高电平灯亮用这句,注释掉上面那句//PORTB=LedCnt;putstr("\nhttp:%/%//doc/4115489903.html,");printp("\n Minute elapsed: %03ds",LedCnt); }}</ms;ii++)<>。

MC9S12XS模块及其应用实例

5.3.1 控制输出设备LED实例

由电路图可知,使用MC9S12XS128的PORTB端口控制8只 LED,PORTB端口输出低电平点亮相应LED。本例中流水灯的流动 速度没有实现精确控制,即延时时间没有精确计算,本书后面章节 会论述如何实现精确定时。

5.3.1 控制输出设备LED实例

流水灯应用实例程序清单如下所示。

3.数据方向寄存器(DDRx)

DDRx决定对应引脚配置为输出口还是输入口,如果某位为“0”,则对应 引脚设定为输入;如果某位为“1”,则对应引脚设定为输出。复位后,DDRx 值为0x00,即MCU复位后引脚默认为输入口。

PORTT、PORTS、PORTM、PORTP、PORTH和PORTJ

4.驱动控制寄存器(RDRx)

5.上拉/下拉使能寄存器(PERx)

如果端口为输入口或者“线或”模式时,可以通过上拉/下拉使能寄存器 PERx使能选择使用内置上拉/下拉电阻。如果PERx某位为“1” 时,则对应引 脚允许使用内置上拉/下拉电阻;如果某位为“0” 时,则对应引脚禁用内置上 拉/下拉电阻。

PORTT、PORTS、PORTM、PORTP、PORTH和PORTJ

6.1.2 中断 1.不可屏蔽中断 不可屏蔽中断包括软件中断、非法指令陷阱和XIRQ中断,下面简要 介绍常用的几个不可屏蔽中断。 (1)软件中断 SWI实质上是一条指令,但其执行过程与中断相同,即通过中断矢 量确定目标地址,中断矢量为$FFF6~$FFF7,它自动保存MCU的寄存 器和返回地址,最后必须通过RTI指令返回。 (2)非法指令陷阱 MCU正常工作时,每次获得的都是由汇编或编译程序生成的有效操 作码,MCU能够正确解释并执行它们,但当受到干扰或系统出现混乱时, 可能得到无法识别的操作码,即非法指令,这时MCU自动产生一次中断, 中断矢量地址为$FFF8~$FFF9。

MC9S12XS128 中 PIT (周期中断定时器) 的使用

while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;

CLKSEL_PLLSEL =1; //engage PLL to system;

}

/*-----------------PIT0初始化------------------*/

那么如何通过编程来实现 PIT 来定时呢?在 数据手册的 363 页给出了 汇编代码的实现,当初我使用的时候已经把汇编转化成 C 语言了。

下面简单地来说下 PIT 的编程过程->:

1、8-Bit Micro Timer 0 跟 8-Bit Micro Timer 1 从 Bus Clock 里面获取时钟信号,通过编程 PITMTLDX 这

在 MC9S12XS128 这款单片机中 没有像 51 或者 AVR 那样的递减计数器,即在一个计时计数器中装一个数,单片机 让这个数在一定的时钟周期性 减 1 ,直道这个数减到 0 为止来实现多少时间的定时。当寄存器的值变为0时又重新装入数来再计时,装数有自动装载和手动装载两种,学过 51 跟 AVR 的朋友应该明白这两种模式。虽然 MC9S12XS128 这款单片机没有这样的定时器,但是它提供了 PIT 定时器,即 Periodic Interrupt Timer (S12PIT24B4CV1),即周期性中断定时器。PIT 分为 PIT0、PIT1、PIT2、PIT3 ,它们均是以中断的方式来实现定时的,具体能够实现多大范围的定时可参考 datasheet . PIT0、PIT1、PIT2、PIT3 对应的中断向量号分别为 66、67、68、69。还要注意 PIT 是没有外部引脚的。

void Pit0_Init(void)

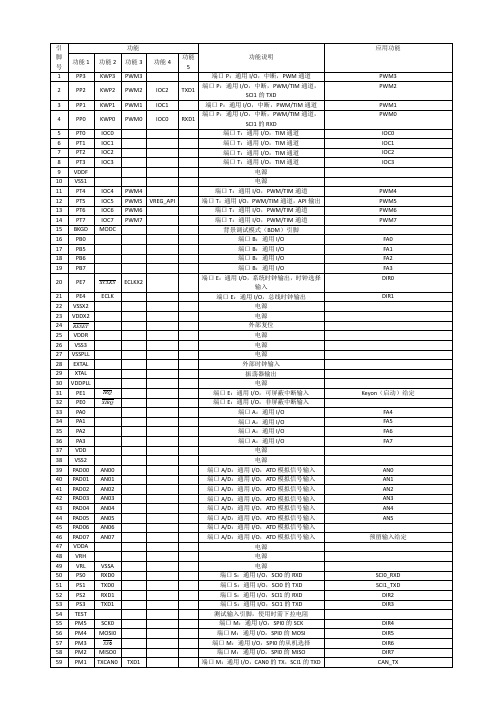

改进版:飞思卡尔MC9S12XS128(64pin)引脚功能说明

21

PE4

ECLK

端口E:通用I/O,总线时钟输出

DIR1

22

VSSX2

电源

23

VDDX2

电源

24

外部复位

25

VDDR

电源

26

VSS3

电源

27

VSSPLL

电源

28

EXTAL

外部时钟输入

29

XTAL

振荡器输出

30

VDDPLL

电源

31

PE1

端口E:通用I/O,可屏蔽中断输入

Keyon(启动)给定

AN5

45

PAD06

AN06

端口A/D:通用I/O,ATD模拟信号输入

46

PAD07

AN07

端口A/D:通用I/O,ATD模拟信号输入

预留输入给定

47

VDDA

电源

48

VRH

电源

49

VRL

VSSA

电源

50

PS0

RXD0

端口S:通用I/O,SCI0的RXD

SCI0_RXD

51

PS1

TXD0

端口S:通用I/O,SCI0的TXD

DIR5

57

PM3

端口M:通用I/O,SPI0的从机选择

DIR6

58

PM2

MISO0

端口M:通用I/O,SPI0的MISO

DIR7

59

PM1

TXCAN0

TXD1

端口M:通用I/O,CAN0的TX,SCI1的TXD

N_TX

60

PM0

RXCAN0

RXD1

端口M:通用I/O,CAN0的RX,SCI1的RXD

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第9章 MC9S12XS128定时器模块 及其应用实例

本节内容

• 9.3 TIM模块的自由运行计数器和定时 器基本寄存器及设置

• 9.3.1 自由运行主定时器与时钟频率设置

• 9.3.2 TIM模块基本寄存器及设置

第9章 MC9S12XS128定时器模块及 其应用实例

9.3 TIM模块的自由运行计数器和定时器基本寄存器及设置

【状态寄存器】

第9章 MC9S12XS128定时器模块及 其应用实例

9.1 TIM模块概述

9.2.4 TIM模块中断系统

【ECT模块中断源】 • • • TIM模块共有11个中断源: 1个自由运行定时器溢出中断 8个定时器通道中断

• 1个脉冲累加器输入中断

• • 1个脉冲累加器溢出中断 TIM模块只检测中断并产生中断

9.3 TIM模块的自由运行计数器和定时器基本寄存器及设置

9.3.1 自由运行主定时器与时钟频率设置 • 定时器系统控制寄存器TSCR1中的TEN位是TIMCLK时钟的总开关。

第9章 MC9S12XS128定时器模块及 其应用实例

• 当TEN=0时,自由运行主定时器的时钟被关断,定时器停止工作,但 并不影响脉冲累加器在事件计数方式下的正常工作。 • 输出比较通道7(OC7)对自由运行主定时器具有特殊的控制功能。 • 当定时器系统控制寄存器TSCR2中的控制位TCRE=1时,如果OC7比较成 功,则定时器计数寄存器TCNT自动复位到$0000。这样可利用OC7实现 TCNT在$0000~$xxxx(<$FFFF)之间的循环计数,从而在保持较高时 钟频率(高分辨力)前提下,缩短计数周期,以满足特殊需要。

• 9.2.3 TIM模块寄存器

• 9.2.4 TIM模块中断系统

第9章 MC9S12XS128定时器模块 及其应用实例 9.2 TIM模块结构和工作原理

9.2.1 TIM模块结构

• 【TIM组成】

• 1个16位自由运行计数器

• • • • • • • 8个16位输入捕捉/输出比较通道 1个16位脉冲累加器 【特点】 模块时钟输入具有7位预分频器 8个输入捕捉通道带有边沿检测器 8个输出比较通道的输出极性可选择 16位脉冲累加器带有边沿检测器

请求,不会对中断请求进行处理 ,用户根据需要自行编写中断服 务程序处理相应的中断事件。

第9章 MC9S12XS128定时器模块及 其应用实例

9.1 TIM模块概述

• •

•

9.1.3 ECT模块的中断系统

【ECT模块中断源】 默认中断优先级次序:从上到下优先级为从高到低。

写入HPRIO中的代码值实际上是中断矢量起始地址的低字节。

• TIM模块的寄存器分为3类:控制寄存器、数据寄存器和状态寄存器 。

第9章 MC9S12XS128定时器模块及 其应用实例

9.1 TIM模块概述

9.2.3 TIM模块寄存器 • 【控制寄存器】

第9章 MC9S12XS128定时器模块及 其应用实例

9.1 TIM模块概述

• 【数据寄存器】 9.2.3 TIM模块寄存器

• 门控时间累加方式下,输入引脚上的有效电平将触发脉冲累加器开始对 ECLK/64时钟进行计数,输入引脚上有效电平结束时的跳变沿将停止计数 ,同时置位中断标志。如果允许脉冲累加器中断,则产生一次中断申请。

第9章 MC9S12XS128定时器模块及 其应用实例

9.1 TIM模块概述

9.2.3 TIM模块寄存器

• 计数器——计数脉冲来自于芯片外部引脚,即驱动脉冲为外部时钟 信号。

第9章 MC9S12XS128定时器模块 及其应用实例 9.1 TIM模块概述

嵌入式系统中定时器/计数器模块的作用:

• 【产生波形输出】从MCU的I/O引脚向外输出一系列符合一定时序规 范的周期信号。

• 【测量输入波形】从MCU的I/O引脚上检测外部输入的一系列周期信 号的脉宽、周期或频率。

断申请,利用中断服务程序可读取通道计数器数值, 获得事件发生的时刻或信号变化的时刻。

9.1 TIM模块概述

第9章 MC9S12XS128定时器模块及 其应用实例

9.2.2 TIM模块工作原理 • 【输出比较】

• 输出比较(Output Compare,OC):输出 比较功能利用编程实现特定时刻输出需 要的电平,实现对外部电路的控制。 • 用户根据需要设置输出比较寄存器值, 自由运行计数器值与输出比较寄存器值

第9章 MC9S12XS128定时器模块及 其应用实例

9.2 TIM模块结构 和工作原理

9.2.2 TIM模块工作原 理 • 【工作模式】

停止(STOP)模式

冻结(Freeze)模式

等待(Wait)模式 正常(Normal)模式

• 【定时器模块框图】

第9章 MC9S12XS128定时器模块 及其应用实例 9.2 TIM模块结构和工作原

9.3.1 自由运行主定时器与时钟频率设置

• 16位自由运行主定时器的工作频率决定输入捕捉/输出比较的分辨能力。

• 定时器计数寄存器TCNT对多路转换器输出的时钟信号进行计数,当计数值从 $FFFF溢出变为$0000时,主定时器中断标志寄存器TFLG2中的中断标志TOF置 位,如果此时定时器系统控制寄存器TSCR2中的中断允许位TOI=1,将向CPU申 请中断。 • 设置TOI=0将禁止自由运行计数器溢出中断,向TFLG2中写入$80将清除TOF标 志。

• MC9S12XS128的TIM模块共有48个寄存器,其中9个是系统保留寄存器 。

• TIM模块的内存映射表给出了这些寄存器的地址、名称和访问权限。

• 对于每个寄存器,所列的地址是地址偏移量,每个寄存器的绝对地 址是TIM模块的基本地址与每个寄存器地址偏移量之和。

• TIM模块的基本地址是0x0040。

第9章 MC9S12XS128定时器模块及 其应用实例 9.1 TIM模块概述

9.2.2 TIM模块工作原理 • 【输入捕捉】

• 输入捕捉(Input Capture,IC):通过捕获自由运行计 数器的计数值来检测外部事件和记录选定的输入信号 跳变边沿的时间。 • 当外部事件发生或信号发生变化时,指定的输入捕捉 通道对应的引脚上产生一个规定的跳变沿(上升沿或 下降沿)。定时器输入通道根据相应引脚上的电平变 化,将当前自由运行计数器中的计数值捕捉到通道寄 存器中。 • 如果此时允许输入捕捉中断,则产生一次输入捕捉中

• 定时器计数寄存器TCNT——自由运行主定时器的数据寄存器,用来 对TIMCLK时钟计数。 • 主定时器中断标志寄存器TFLOG2——表示主定时器是否产生溢出。

第9章 MC9S12XS128定时器模块 及其应用实例 9.3 TIM模块的自由运行计数器和定时器基本寄存器及设置

9.3.2 TIM模块基本寄存器及设置

《MC9S12XS单片机原理 及嵌入式系统开发》

合肥工业大学

吴 晔,张 阳,滕 勤

第9章 MC9S12XS128定时器模块 及其应用实例 本章内容

• 9.1 TIM模块概述

• 9.2 TIM模块结构和工作原理

• 9.3 TIM模块的自由运行计数器和定时器基本寄存器及设

置 • 9.4 TIM模块的输入捕捉功能及寄存器设置 • 9.5 TIM模块的输出比较功能及寄存器设置 • 9.6 TIM模块的脉冲累加器功能及寄存器设置 • 9.7 TIM模块应用实例

每隔4个总线周期比较一次,当两者相等 时,会在相应通道引脚上输出预先设定 的电平。

• 如果允许输出比较中断,则产生一次中

断申请。

第9章 MC9S12XS128定时器模块 9.1 TIM模块概述 及其应用实例

9.2.2 TIM模块工作原理

•

•

【脉冲累加器】

脉冲累加器(Pulse accumulator,PA):通过检测相应引脚上的有效边沿统计脉冲个数 。TIM模块只有一个16位的脉冲累加器,与PT7引脚复用,其工作方式有事件计数方式

第9章 MC9S12XS128定时器模块及 其应用实例

9.1 TIM模块概述

定时器/计数器的特点:

• (1)可以有多种工作方式——定时方式或计数方式等。 • (2)计数器的模值可变——计数的最大值有一定的限制,取决于计数 器的位数。计数的最大值限制了定时的最大值。 • (3)可以根据规定的定时或计数值,当定时时间到或到达计数终点时 ,发出中断请求信号,以便实现定时或计数控制。 • 定时器——计数脉冲来自于系统工作时钟或经过分频后的系统时钟 ,即驱动脉冲为内部时钟信号;

• 【统计脉冲或边沿个数】对端口引脚输入的、由外部事件产生的触 发信号进行计数。 • 【作为定时基准】产生内部定时,例如用于定时采样等。 • MC9S12XS128定时器模块称为TIM(Timer Module)。

第9章 MC9S12XS128定时器模块 及其应用实例 本节内容

• 9.2 TIM模块结构和工作原理 • 9.2.1 TIM模块结构 • 9.2.2 TIM模块工作原理

理

9.2.2 TIM模块工作原理

• 【详细功能框图】

第9章 MC9S12XS128定时器模块 及其应用实例 9.2 TIM模块结构和工作原理

9.2.2 TIM模块工作原理 • 【自由运行计数器】

• TIM的核心——16位自由运行计数器,也称为自由运行主定时器。 • 系统复位时——自由运行计数器为$0000。 • 模块运行时——自由运行计数器从$0000~$FFFF循环递增计数。 • 溢出复零时——置位中断标志。 • 时钟源TIMCLK—— PCLK,PACLK,PACLK/256,PACLK/65536。 • 预分频器时钟PCLK——由总线时钟经过一个7位预分频器得到。 • 预分频系数—— 8种。

第9章 MC9S12XS128定时器模块及 其应用实例

9.3 TIM模块的自由运行计数器和定时器基本寄存器及设 置 9.3.2 TIM模块基本寄存器及设置