LTC4052-42中文资料

LTC4056-4.2中文资料

U APPLICATIO S

s s s s s

500 400 300 200 100

CHRG TIMER/SHDN PROG GND

UNDERVOLTAGE CHARGE CURRENT LIMITING

+

1-CELL 4.2V Li-Ion

4056-4.2 TA01

0 4.40 4.45

U

CONSTANT CURRENT UNDERVOLTAGE LOCKOUT AT 4.35V 4.50 4.55 4.60 4.65 4.70 ar Telephones Handheld Computers Digital Cameras Charging Docks and Cradles Low Cost and Small Size Chargers

TYPICAL APPLICATIO

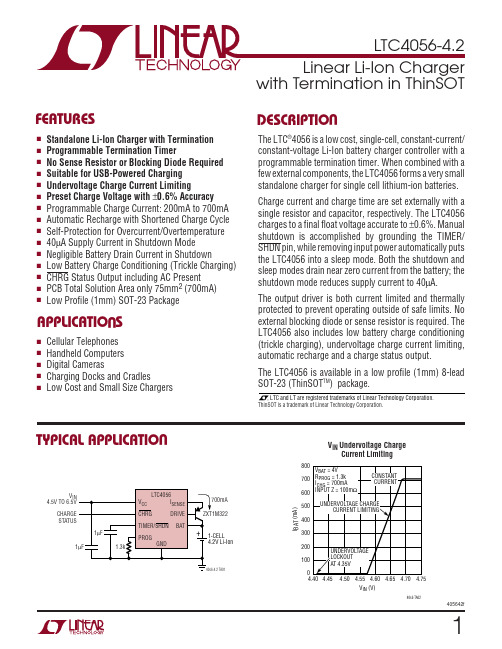

VIN Undervoltage Charge Current Limiting

800 VBAT = 4V 700 RPROG = 1.3k ICHG = 700mA INPUT Z = 100mΩ 600 700mA ZXT1M322

IBAT (mA)

VIN 4.5V TO 6.5V CHARGE STATUS 1µF 1µF 1.3k

VCC

LTC4056 ISENSE DRIVE BAT

Input Supply Voltage (VCC) ........................– 0.3V to 10V BAT, CHRG ................................................– 0.3V to 10V DRIVE, PROG, TIMER/SHDN ....... – 0.3V to (VCC + 0.3V) Output Current (ISENSE) ...................................... 900mA Short-Circuit Duration (BAT, ISENSE) ............Continuous Junction Temperature ........................................... 125°C Operating Ambient Temperature Range (Note 2) .............................................. – 40°C to 85°C Storage Temperature Range ................. – 65°C to 150°C Lead Temperature (Soldering, 10 sec).................. 300°C

LTC4054-4.2中文资料

LTC4054-4.2/LTC4054X-4.2 Standalone Linear Li-Ion Battery Charger with Thermal Regulation in ThinSOT

FEATURES

s s

DESCRIPTIO

s

s

s

s s

s s s s s s s s

Cellular Telephones, PDAs, MP3 Players Charging Docks and Cradles Bluetooth Applications

TYPICAL APPLICATIO

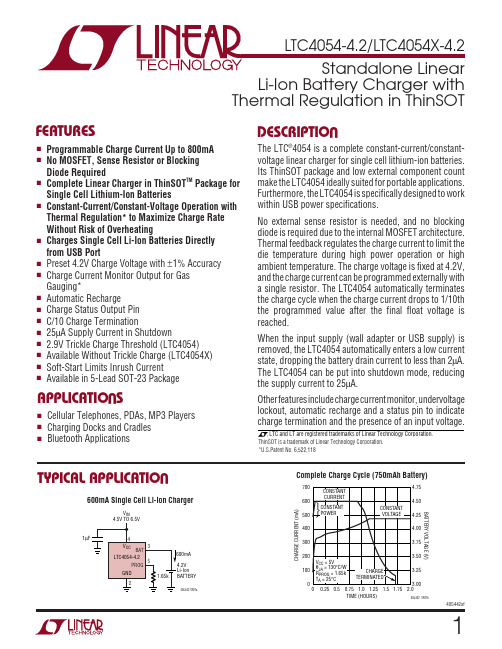

VIN 4.5V TO 6.5V

Complete Charge Cycle (750mAh Battery)

The LTC®4054 is a complete constant-current/constantvoltage linear charger for single cell lithium-ion batteries. Its ThinSOT package and low external component count make the LTC4054 ideally suited for portable applications. Furthermore, the LTC4054 is specifically designed to work within USB power specifications. No external sense resistor is needed, and no blocking diode is required due to the internal MOSFET architecture. Thermal feedback regulates the charge current to limit the die temperature during high power operation or high ambient temperature. The charge voltage is fixed at 4.2V, and the charge current can be programmed externally with a single resistor. The LTC4054 automatically terminates the charge cycle when the charge current drops to 1/10th the programmed value after the final float voltage is reached. When the input supply (wall adapter or USB supply) is removed, the LTC4054 automatically enters a low current state, dropping the battery drain current to less than 2µA. The LTC4054 can be put into shutdown mode, reducing the supply current to 25µA. Other features include charge current monitor, undervoltage lockout, automatic recharge and a status pin to indicate charge termination and the presence of an input voltage.

LTC1232 精密电源监控模块说明书

123sn1232 1232fasSYMBOL PARAMETER CONDITIONSMINTYP MAX UNITSV CC Supply Voltage● 4.555.5V V IH ST and PB RST Input High Level ●2V CC +0.3V V ILST and PB RST Input Low Level●–0.30.8VDC ELECTRICAL CHARACTERISTICSSYMBOL PARAMETER CONDITIONS MINTYP MAX UNITS I IL Input Leakage (Note 3)●–11µA I OH Output Current at 2.4V (Note 5)●–1–13mA I OL Output Current at 0.4V (Note 5)●26mAI CC Supply Current (Note 4)●0.52mA V CCTP V CC Trip Point TOL = GND ● 4.5 4.62 4.74 V V CCTP V CC Trip PointTOL = V CC●4.254.37 4.49 V V HYS V CC Trip Point Hysteresis 40mV V RSTRST Output Voltage at V CC = 1VI SINK = 10µA4200mVThe ● denotes the specifications which applyover the full operating temperature. V CC = full operating range.The ● denotes the specifications which apply over the full operatingtemperature. V CC = full operating range.SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITS t PB PB RST = V IL ●40ms t RST RESET Active Time ●2506101000ms t ST ST Pulse Width●20ns t RPD V CC Detect to RST and RST ●100ns t f V CC Slew Rate 4.75V–4.25V ●300µs t RPU V CC Detect to RST and RSTt R = 5µs●2506101000ms (Reset Active Time)t R V CC Slew Rate 4.25V–4.75V ●0nst TDST Pin Detect to RST and RST TD = GND ●60150250ms (Watchdog Time-Out Period)TD = Floating ●2506101000ms TD = V CC●50012002000ms C IN Input Capacitance 5pF C OUTOutput Capacitance5pFNote 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.Note 2: All voltage values are with respect to GND.Note 3: The PB RST pin is internally pulled up to V CC with an internal impedance of 10k typical. The TD pin has internal bias current.Note 4: Measured with outputs open.Note 5: The RST pin is an open drain output.The ● denotes the specifications which apply over the full operating temperature.V CC = full operating range.AC CHARACTERISTICSRECO E D ED OPERATI G CO DITIO SU U U U WW456Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.7Linear Technology Corporation 1630 McCarthy Blvd., Milpitas, CA 95035-7417 (408) 432-1900 ● FAX: (408) 434-0507 ● LW/TP 1002 1K REV A • PRINTED IN USA © LINEAR TECHNOLOGY CORPORA TION 19928。

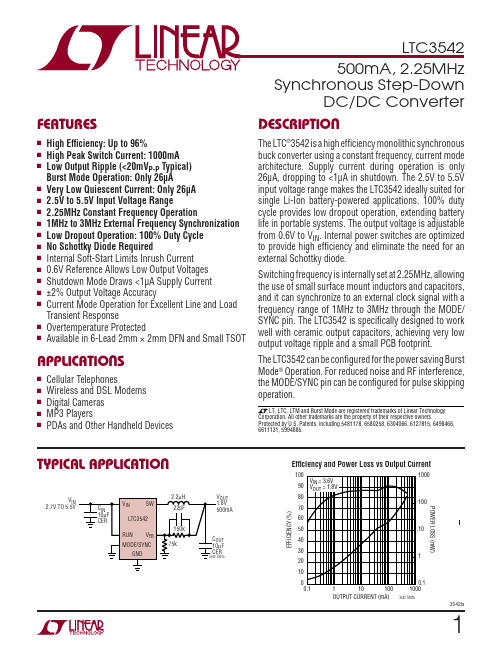

LTC3542资料

13542faSynchronous Step-DownDC/DC ConverterThe LTC ®3542 is a high effi ciency monolithic synchronous buck converter using a constant frequency, current mode architecture. Supply current during operation is only 26μA, dropping to <1μA in shutdown. The 2.5V to 5.5V input voltage range makes the LTC3542 ideally suited for single Li-Ion battery-powered applications. 100% duty cycle provides low dropout operation, extending battery life in portable systems. The output voltage is adjustable from 0.6V to V IN . Internal power switches are optimized to provide high effi ciency and eliminate the need for an external Schottky diode.Switching frequency is internally set at 2.25MHz, allowing the use of small surface mount inductors and capacitors, and it can synchronize to an external clock signal with a frequency range of 1MHz to 3MHz through the MODE/SYNC pin. The LTC3542 is specifi cally designed to work well with ceramic output capacitors, achieving very low output voltage ripple and a small PCB footprint.The LTC3542 can be confi gured for the power saving Burst Mode ® Operation. For reduced noise and RF interference, the MODE/SYNC pin can be confi gured for pulse skipping operation.■Cellular Telephones■ Wireless and DSL Modems ■ D igital Cameras ■ MP3 Players■ PDAs and Other Handheld Devices■High Effi ciency: Up to 96%■ High Peak Switch Current: 1000mA ■ Low Output Ripple (<20mV P-P Typical) Burst Mode Operation: Only 26μA■ Very Low Quiescent Current: Only 26μA ■ 2.5V to 5.5V Input Voltage Range■ 2.25MHz Constant Frequency Operation■ 1MHz to 3MHz External Frequency Synchronization ■ Low Dropout Operation: 100% Duty Cycle ■ No Schottky Diode Required■ Internal Soft-Start Limits Inrush Current ■ 0.6V Reference Allows Low Output Voltages ■Shutdown Mode Draws <1μA Supply Current ■ ±2% Output Voltage Accuracy■ Current Mode Operation for Excellent Line and Load Transient Response ■ Overtemperature Protected■ Available in 6-Lead 2mm × 2mm DFN and Small TSOTProtected by U.S. Patents, including 5481178, 6580258, 6304066, 6127815, 6498466, 6611131, 5994885.μF V IN2.7V TO 5.5VOUT Effi ciency and Power Loss vs Output CurrentOUTPUT CURRENT (mA)30E F F I C I E N C Y (%)POWER LOSS (mW)90100201080507060400.11010010003542 TA01b10010001010.11FEATURESDESCRIPTIONAPPLICATIONSTYPICAL APPLICATION23542faELECTRICAL CHARACTERISTICSInput Supply Voltage (V IN ) ...........................–0.3V to 6V V FB , RUN Voltages .......................................–0.3V to V IN MODE Voltage ................................–0.3V to (V IN + 0.3V)SW Voltage ....................................–0.3V to (V IN + 0.3V)Operating Temperature Range (Note 2)LTC3542E ............................................–40°C to 85°C LTC3542I ...........................................–40°C to 125°CThe ● denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. V IN = 3.6V unless otherwise noted.SYMBOL PARAMETERCONDITIONSMINTYP MAX UNITSV IN Operating Voltage Range ●2.5 5.5V I FB Feedback Input Current ±30nA V FB Feedback Voltage (Note 4)●0.5880.60.612V ΔV LINE_REG Reference Voltage Line Regulation (Note 4)V IN = 2.5V to 5.5V 0.040.2%/V ΔV LOAD_REGOutput Voltage Load Regulation (Note 4)I LOAD = 100mA to 500mA 0.020.2%Junction Temperature (Note 7) .............................125°C Storage Temperature Range ...................–65°C to 150°C Lead Temperature (Soldering, 10 sec) TSOT-23 ............................................................300°C Refl ow Peak Body Temperature (DFN) ..................260°CABSOLUTE MAXIMUM RATINGS (Note 1)TOP VIEWRUN SWV FB V IN GND DC PACKAGE6-LEAD (2mm × 2mm) PLASTIC DFN4576321MODE/SYNC T JMAX = 125°C, θJA = 102°C/W, θJC = 20°C/W (SOLDERED TO A 4-LAYER BOARD, NOTE 3)EXPOSED PAD (PIN 7) IS GND, MUST BE SOLDERED TO PCBV IN 1GND 2V FB 36 SW 5 MODE/SYNC 4 RUNTOP VIEWS6 PACKAGE6-LEAD PLASTIC TSOT-23T JMAX = 125°C, θJA = 215°C/WPIN CONFIGURATIONORDER INFORMATIONLEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTION TEMPERATURE RANGE LTC3542EDC#PBF LTC3542EDC#TRPBF LCFR 6-Lead (2mm × 2mm) Plastic DFN –40°C to 85°C LTC3542IDC#PBF LTC3542IDC#TRPBF LCFR 6-Lead (2mm × 2mm) Plastic DFN –40°C to 125°C LTC3542ES6#PBF LTC3542ES6#TRPBF LCFS 6-Lead Plastic TSOT-23–40°C to 85°C LTC3542IS6#PBFLTC3542IS6#TRPBFLCFS6-Lead Plastic TSOT-23–40°C to 125°CConsult LTC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container.Consult LTC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: /leadfree/ For more information on tape and reel specifi cations, go to: /tapeandreel/33542faTYPICAL PERFORMANCE CHARACTERISTICSNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. No pin should exceed 6V.Note 2: The LTC3542 is guaranteed to meet performance specifi cations from 0°C to 85°C. Specifi cations over the –40°C to 85°C operatingtemperature range are assured by design, characterization and correlation with statistical process controls. The LTC3542I is guaranteed over the full –40°C to 125°C operating temperature range.Note 3: Failure to solder the Exposed Pad of the package to the PC board will result in a thermal resistance much higher than 102°C/W.SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITS I SInput DC Supply Current (Note 5)Active Mode Sleep Mode Shutdown V FB = 0.5VV FB = 0.7V, MODE = 0V RUN = 0V 260.1500351μA μA μA f OSC Oscillator Frequency V FB = 0.6V ●1.82.252.7MHz f SYNC Synchronous Frequency V FB = 0.6V13MHz I LIM Peak Switch CurrentV IN = 3V, V FB = 0.5V, Duty Cycle < 35%6501000mA R DS(ON)P-Channel On Resistance (Note 6)N-Channel On Resistance (Note 6)I SW = 100mA I SW = –100mA0.50.350.650.55ΩΩI SW(LKG)Switch Leakage Current V IN = 5V, V RUN = 0V, V SW = 0V or 5V ±0.01±1μA V UVLO Undervoltage Lockout Threshold V IN Rising V IN Falling1.82.01.9 2.3V V V RUN RUN Threshold ●0.31.5V I RUN RUN Leakage Current ●±0.01±1μA V MODE/SYNC MODE/SYNC Threshold ●0.31.2V I MODE/SYNCMODE/SYNC Leakage Current●±0.01±1μANote 4: The converter is tested in a proprietary test mode that connects the output of the error amplifi er to the SW pin, which is connected to an external servo loop.Note 5: Dynamic supply current is higher due to the internal gate charge being delivered at the switching frequency.Note 6: The DFN switch on resistance is guaranteed by correlation to wafer level measurements.Note 7: T J is calculated from the ambient temperature T A and power dissipation P D according to the following formula: T J = T A + (P D ) • (θJA).Burst Mode OperationPulse Skip Mode OperationStart-Up from ShutdownSW 2V/DIVV IN = 3.6V V OUT = 1.8V I LOAD = 25mAFIGURE 3a CIRCUIT2μs/DIV 3542 G01V OUT 50mV/DIV AC COUPLED I L100mA/DIVSW 2V/DIV I L100mA/DIVV IN = 3.6V V OUT = 1.8V I LOAD = 25mAFIGURE 3a CIRCUIT400ns/DIV 3542 G02VOUT 50mV/DIV AC COUPLED RUN2V/DIV I L100mA/DIVV IN = 3.6V V OUT = 1.8V I LOAD = 0AFIGURE 3a CIRCUIT400μs/DIV3542 G03V OUT 1V/DIVT A = 25°C unless otherwise specifi ed.ELECTRICAL CHARACTERISTICSThe ● denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. V IN = 3.6V unless otherwise noted.43542faStart-Up from ShutdownLoad StepReference Voltage vs TemperatureOscillator Frequency vs TemperatureOscillator Frequency vs Supply VoltageOutput Voltage vs Supply VoltageOutput Voltage vs Load CurrentR DS(ON) vs Input VoltageRUN 2V/DIV I L500mA/DIVV IN = 3.6VV OUT = 1.8V I LOAD = 500mA FIGURE 3a CIRCUIT400μs/DIV 3542 G04V OUT 1V/DIV V OUT 100mV/DIV AC COUPLEDI L500mA/DIVV IN = 3.6V V OUT = 1.8VI LOAD = 30mA TO 500mA FIGURE 3a CIRCUIT20μs/DIV 3542 G05ILOAD 500mA/DIVLoad StepV OUT100mV/DIV AC COUPLEDI L500mA/DIV V IN = 3.6VV OUT = 1.8VI LOAD = 0mA TO 500mA FIGURE 3a CIRCUIT20μs/DIV 3542 G06I LOAD 500mA/DIVTEMPERATURE (°C)–50V R E F (V )0.61000.60750.60500.60250.60000.59750.59500.59250.59000.58750.58500.58250.61250.6150050753542 G07–2525100125INPUT VOLTAGE (V)2–0.5V O U T E R R O R (%)–0.4–0.2–0.100.50.234 4.53542 G10–0.30.30.40.1 2.53.55 5.56LOAD CURRENT (mA)10V O U T E R R O R (%)1.02.010*******3542 G11–1.0–0.50.51.5–1.5–2.0V IN (V)10R D S (O N ) (9)0.10.30.40.550.93542 G120.2326470.60.70.8TEMPERATURE (°C)–50–30–1010305070901101.8F R E Q U E N C Y (M H z )1.92.12.22.32.73542 G082.02.42.52.6SUPPLY VOLTAGE (V)F R E Q U E N C Y (M H z )2.22.32.4563542 G092.12.01.82341.92.72.52.6TYPICAL PERFORMANCE CHARACTERISTICST A = 25°C unless otherwise specifi ed.53542faR DS(ON) vs TemperatureSwitch Leakage vs Input VoltageEffi ciency vs Input VoltageTEMPERATURE (°C)–500R D S (O N ) (Ω)0.10.30.40.5500.93542 G130.20–2575100251250.60.70.8Switch Leakage vs TemperatureTEMPERATURE (°C)–50S W I T C H L E A K A G E (n A )20025030025753542 G15150100–255010012550V IN (V)0L E A K A G E C U R R E N T (p A )20040060012343542 G14580010001003005007009006INPUT VOLTAGE (V)2.510090807060504030453542 G1633.54.55.5E F F I C I E N C Y (%)Effi ciency vs Load CurrentOUTPUT CURRENT (mA)30E F F I C I E N C Y (%)90100201080507060400.11010010003542 G171Effi ciency vs Load CurrentEffi ciency vs Load CurrentOUTPUT CURRENT (mA)30E F F I C I E N C Y (%)90100201080507060400.11010010003542 G181OUTPUT CURRENT (mA)30E F F I C I E N C Y (%)90100201080507060400.11010010003542 G191TYPICAL PERFORMANCE CHARACTERISTICST A = 25°C unless otherwise specifi ed.63542fa3542 BDV FB (Pin 1/Pin 3): Output Feedback Pin. Receives the feedback voltage from an external resistive divider across the output. Nominal voltage for this pin is 0.6V.V IN (Pin 2/Pin 1): Power Supply Pin. Must be closely decoupled to GND.GND (Pin 3/Pin 2): Ground Pin.SW (Pin 4/Pin 6): Switch Node Connection to Inductor. This pin connects to the drains of the internal main and synchronous power MOSFET switches.MODE/SYNC (Pin 5/Pin 5): Mode Selection and Oscillator Synchronization Pin. This pin controls the operation of the device. When tied to GND or V IN , Burst Mode operation orpulse skipping mode is selected, respectively. Do not fl oat this pin. The oscillation frequency can be synchronized to an external oscillator applied to this pin and pulse skipping mode is automatically selected.RUN (Pin 6/Pin 4): Converter Enable Pin. Forcing this pin above 1.5V enables this part, while forcing it below 0.3V causes the device to shut down. In shutdown, all functions are disabled drawing <1μA supply current. This pin must be driven; do not fl oat.GND (Pin 7, DFN Package Only): Exposed Pad. The Ex-posed Pad is ground. It must be soldered to PCB ground to provide both electrical contact and optimum thermal performance.PIN FUNCTIONS(DFN/TSOT-23)BLOCK DIAGRAMThe LTC3542 uses a constant frequency, current mode, step-down architecture. The operating frequency is set at 2.25MHz and can be synchronized to an external oscillator. To suit a variety of applications, the selectable MOD E/SYNC pin allows the user to trade-off noise for effi ciency.The output voltage is set by an external divider returned to the V FB pin. An error amplifi er compares the divided output voltage with a reference voltage of 0.6V and adjusts the peak inductor current accordingly.Main Control LoopDuring normal operation, the top power switch (P-channel MOSFET) is turned on at the beginning of a clock cycle when the V FB voltage is below the reference voltage. The current fl ows into the inductor and the load increases until the current limit is reached. The switch turns off and energy stored in the inductor fl ows through the bottom switch (N-channel MOSFET) into the load until the next clock cycle. The peak inductor current is controlled by the internally compensated output of the error amplifi er. When the load current increases, the V FB voltage decreases slightly below the reference. This decrease causes the error amplifi er to increase its output voltage until the average inductor cur-rent matches the new load current. The main control loop is shut down by pulling the RUN pin to ground.Low Load Current OperationBy selecting MODE/SYNC pin, two modes are available to control the operation of the LTC3542 at low load currents. Both modes automatically switch from continuous opera-tion to the selected mode when the load current is low. To optimize effi ciency, the Burst Mode operation can be selected. When the converter is in Burst Mode operation, the peak current of the inductor is set to approximately 60mA regardless of the output load. Each burst event can last from a few cycles at light loads to almost continuously cycling with short sleep intervals at moderate loads. In between these burst events, the power MOSFETs and any unneeded circuitry are turned off, reducing the quiescent current to 26μA. In this sleep state, the load current is being supplied solely from the output capacitor. As the output voltage drops, the EA amplifi er’s output rises above the sleep threshold and turns the top MOSFET on. This process repeats at a rate that is dependent on the load demand. By running cycles periodically, the switching losses which are dominated by the gate charge losses of the power MOSFETs are minimized.For lower ripple noise at low load currents, the pulse skip mode can be used. In this mode, the regulator continues to switch at a constant frequency down to very low load currents, where it will begin skipping pulses.Dropout OperationWhen the input supply voltage decreases toward the output voltage, the duty cycle increases to 100%, which is the dropout condition. In dropout, the PMOS switch is turned on continuously with the output voltage being equal to the input voltage minus the voltage drops across the internal P-channel MOSFET and the inductor. An important design consideration is that the R DS(ON) of the P-channel switch increases with decreasing input supply voltage (See Typical Performance Characteristics). Therefore, the user should calculate the power dissipation when the LTC3542 is used at 100% duty cycle with low input voltage (See Thermal Considerations in the Applications Information Section). Low Supply OperationTo prevent unstable operation, the LTC3542 incorporates an undervoltage lockout circuit which shuts down the part when the input voltage drops below about 2V.Internal Soft-StartAt start-up when the RUN pin is brought high, the internal reference is linearly ramped from 0V to 0.6V in about 1ms. The regulated feedback voltage follows this ramp resulting in the output voltage ramping from 0% to 100% in 1ms. The current in the inductor during soft-start is defi ned by the combination of the current needed to charge the output capacitance and the current provided to the load as the output voltage ramps up. The start-up waveform, shown in the Typical Performance Characteristics, shows the output voltage start-up from 0V to 1.8V with a 500mA load and V IN = 3.6V (refer to Figure 3a).OPERATION73542fa83542faA general LTC3542 application circuit is shown in Figure1. External component selection is driven by the load require-ment and begins with the selection of the inductor L. Once the inductor is chosen, C IN and C OUT can be selected.the burst clamp. Lower inductor values result in higher ripple current which causes the transition to occur at lower load currents. This causes a dip in effi ciency in the upper range of low current operation. In Burst Mode operation, lower inductance values cause the burst frequency to increase.Inductor Core SelectionD ifferent core materials and shapes change the size/current and price/current relationships of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don’t radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends more on the price vs size requirements and any radiated fi eld/EMI requirements than on what the LTC3542 requires to operate. Table 1 shows some typi-cal surface mount inductors that work well in LTC3542 applications.Input Capacitor (C IN ) SelectionIn continuous mode, the input current of the converter is a square wave with a duty cycle of approximately V OUT /V IN . To prevent large voltage transients, a low equivalent series resistance (ESR) input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given by:I I RMS MAXIN≈where the maximum average output current I MAX equals the peak current minus half the peak-to-peak ripple cur-rent, I MAX = I LIM – ΔI L /2. This formula has a maximum at V IN = 2V OUT , where I RMS = I OUT /2. This simple worst-case is commonly used to design because even signifi cant deviations do not offer much relief. Note that capacitor manufacturer’s ripple current ratings are often based on only 2000 hours life time. This makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet the size or height requirements of theV IN2.7V TO 5.5VOUT Figure 1. LTC3542 General SchematicInductor SelectionThe inductor value has a direct effect on ripple current ΔI L , which decreases with higher inductance and increases with higher V IN or V OUT , as shown in following equation: ΔI V L V V L OUT OOUT IN =⎛⎝⎜⎞⎠⎟ƒ•–1where f O is the switching frequency. A reasonable starting point for setting ripple current is ΔI L = 0.4 • I OUT(MAX), where I OUT(MAX) is 500mA. The largest ripple current ΔI L occurs at the maximum input voltage. To guarantee that the ripple current stays below a specifi ed maximum, the inductor value should be chosen according to the follow-ing equation:L V I V V OUT O L OUT IN MAX =⎛⎝⎜⎞⎠⎟ƒ•–()Δ1The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation. Thus, a 600mA rated inductor should be enough for most applications (500mA + 100mA). For better effi ciency, chose a low DC-resistance inductor.The inductor value will also have an effect on Burst Mode operation. The transition to low current operation begins when the inductor’s peak current falls below a level set byAPPLICATIONS INFORMATION93542fadesign. An additional 0.1μF to 1μF ceramic capacitor is also recommended on V IN for high frequency decoupling, when not using an all ceramic capacitor solution.Output Capacitor (C OUT ) SelectionThe selection of C OUT is driven by the required ESR to minimize voltage ripple and load step transients. Typically, once the ESR requirement is satisfi ed, the RMS current rating generally far exceeds the I RIPPLE(P-P) requirement, except for an all ceramic solution. The output ripple (ΔV OUT ) is determined by:ΔΔV I ESR C OUT L OUT ≈+⎛⎝⎜⎞⎠⎟18••ƒO where f O is the switching frequency, C OUT is the outputcapacitance and ΔI L is the inductor ripple current. For a fixed output voltage, the output ripple is highest at maximum input voltage since ΔI L increases with input voltage. If tantalum capacitors are used, it is critical that the capaci-tors are surge tested for use in switching power supplies. An excellent choice is the AVX TPS series of surface mount tantalums, available in case heights ranging from 2mm to 4mm. These are specially constructed and tested for low ESR so they give the lowest ESR for a given volume. Other capacitor types include Sanyo POSCAP , Kemet T510 andT495 series, and Sprague 593D and 595D series. Consult the manufacturer for other specifi c recommendations.Ceramic Input and Output CapacitorsHigher value, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current rating, high voltage rating and low ESR are tempting for switching regulator use. However, the ESR is so low that it can cause loop stability problems. Since the LTC3542’s control loop does not depend on the output capacitor’s ESR for stable operation, ceramic capacitors can be used to achieve very low output ripple and small circuit size. X5R or X7R ceramic capacitors are recommended because these dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size.Great care must be taken when using only ceramic input and output capacitors. When a ceramic capacitor is used at the input and the power is being supplied through long wires, such as from a wall adapter, a load step at the output can induce ringing at the V IN pin. At best, this ringing can couple to the output and be mistaken as loop instability. At worst, the ringing at the input can be large enough to damage the part. For more information, see Application Note 88. The recommended capacitance value to use is 10μF for both input and output capacitors.Table 1. Representative Surface Mount InductorsMANUFACTURER PART NUMBERVALUE (μH)MAX DC CURRENT (A)DCR (Ω)SIZE (mm 3)SumidaCDRH2D11-2RM 2.20.7800.098 3.2 × 3.2 × 1.2CDRH3D16 2.2 1.20.075 3.8 × 3.8 × 1.8CMD4D11 2.20.950.116 4.4 × 5.8 × 1.2CDH2D09B 3.30.850.15 2.8 × 3 × 1CLS4D094.70.750.15 4.9 × 4.9 × 1Murata LQH32CN 2.20.790.097 2.5 × 3.2 × 1.55LQH43CN 4.70.750.15 4.5 × 3.2 × 2.6TDKIVLC453232 2.20.850.18 4.8 × 3.4 × 3.4VLF3010AT-2R2M1R02.21.00.122.8 × 2.6 × 1APPLICATIONS INFORMATIONOutput Voltage ProgrammingThe output voltage is set by a resistive divider according to the following formula:V V R ROUT =+⎛⎝⎜⎞⎠⎟06121.To improve the frequency response, a feed-forward capaci-tor, C F, may also be used. Great care should be taken to route the V FB line away from noise sources, such as the inductor or the SW line.Mode Selection and Frequency SynchronizationThe MODE/SYNC pin is a multipurpose pin that provides mode selection and frequency synchronization. Connect-ing this pin to GND enables Burst Mode operation, which provides the best low current effi ciency at the cost of a higher output voltage ripple. Connecting this pin to V IN selects pulse skip mode operation, which provides the lowest output ripple at the cost of low current effi ciency. The LTC3542 can also be synchronized to an external clock signal with range from 1MHz to 3MHz by the MODE/SYNC pin. During synchronization, the mode is set to pulse skip and the top switch turn-on is synchronized to the falling edge of the external clock.Effi ciency ConsiderationsThe effi ciency of a switching regulator is equal to the output power divided by the input power times 100%. It is often useful to analyze individual losses to determine what is limiting the effi ciency and which change would produce the most improvement. Effi ciency can be expressed as: Effi ciency = 100% – (L1 + L2 + L3 + ...)where L1, L2, etc. are the individual losses as a percent-age of input power. Although all dissipative elements in the circuit produce losses, three main sources usually account for most of the losses in LTC3542 circuits: 1) V IN quiescent current, 2) I2R loss and 3) switching loss. V IN quiescent current loss dominates the power loss at very low load currents, whereas the other two dominate at medium to high load currents. In a typical effi ciency plot, the effi ciency curve at very low load currents can be misleading since the actual power loss is of no consequence as illustrated in Figure 2.1) The V IN quiescent current is the DC supply current given in the Electrical Characteristics which excludes MOSFET charging current. V IN current results in a small (<0.1%) loss that increases with V IN, even at no load.2) I2R losses are calculated from the DC resistances of the internal switches, R SW, and external inductor, R L. In continuous mode, the average output current fl ows through inductor L, but is “chopped” between the internal top and bottom switches. Thus, the series resistance looking into the SW pin is a function of both top and bottom MOSFET R DS(ON) and the duty cycle (D) as follows:R SW = (R DS(ON)TOP)(D) + (R DS(ON)BOT)(1 – D)The R DS(ON) for both the top and bottom MOSFETs can be obtained from the Typical Performance Characteristics curves. Thus, to obtain I2R losses:I2R losses = I OUT2(R SW + R L)Figure 2. Power Loss vs Load CurrentOUTPUT CURRENT (mA)1POWERLOSS(mW)1010010000.11010010003542 F020.11APPLICATIONS INFORMATION103542fa3) The switching current is MOSFET gate charging current, that results from switching the gate capacitance of the power MOSFETs. Each time a MOSFET gate is switched from low to high to low again, a packet of charge dQ moves from V IN to ground. The resulting dQ/dt is a current out of V IN that is typically much larger than the DC bias current. In continuous mode, I GATECHG = f O(Q T + Q B), where Q T and Q B are the gate charges of the internal top and bottom MOSFET switches. The gate charge losses are proportional to V IN and thus their effects will be more pronounced at higher supply voltages.Other “hidden” losses such as copper trace and internal battery resistances can account for additional effi ciency degradations in portable systems. The internal battery and fuse resistance losses can be minimized by making sure that C IN has adequate charge storage and very low ESR at the switching frequency. Other losses include diode conduction losses during dead-time and inductor core losses generally account for less than 2% total ad-ditional loss.Thermal ConsiderationsIn most applications the LTC3542 does not dissipate much heat due to its high effi ciency. But in applications where the LTC3542 is running at high ambient temperature with low supply voltage and high duty cycles, such as in dropout, the heat dissipated may exceed the maximum junction temperature of the part. If the junction temperature reaches approximately 60°C, both power switches will be turned off and the SW node will become high impedance.To avoid the LTC3542 from exceeding the maximum junction temperature, the user need to do some thermal analysis. The goal of the thermal analysis is to determine whether the power dissipated exceeds the maximum junction temperature of the part. The temperature rise is given by:T R = (P D)(θJA)where P D is the power dissipated by the regulator and θJA is the thermal resistance from the junction of the die to the ambient.The junction temperature, T J, is given by:T J = T A + T Rwhere T A is the ambient temperature.As an example, consider the LTC3542 in dropout at an input voltage of 2.7V, a load current of 500mA and an ambient temperature of 70°C. From the typical performance graph of switch resistance, the R DS(ON) of the P-channel switch at 70°C is approximately 0.7Ω. Therefore, power dissipated by the part is:P D = I LOAD2 • R DS(ON) = 175mWFor the DFN package, the θJA is 102°C/W. Thus, the junc-tion temperature of the regulator is:T J = 70°C + 0.175 • 102 = 87.9°Cwhich is below the maximum junction temperature of 125°C.Note that at higher supply voltages, the junction temperature is lower due to reduced switch resistance (R DS(ON)). Checking Transient ResponseThe regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in load current. When a load step occurs, V OUT immediately shifts by an amount equal to ΔI LOAD • ESR, where ESR is the effective series resistance of C OUT. ΔI LOAD also begins to charge or dis-charge C OUT, generating a feedback error signal used by the regulator to return V OUT to its steady-state value. During this recovery time, V OUT can be monitored for overshoot or ringing that would indicate a stability problem.The output voltage settling behavior is related to the stability of the closed-loop system and will demonstrate the actual overall supply performance. For a detailed explanation of optimizing the compensation components, including a re-view of control loop theory, refer to Application Note 76. In some applications, a more severe transient can be caused by switching loads with large (>1μF) bypass capacitors. The discharged bypass capacitors are effectively put inAPPLICATIONS INFORMATION113542fa。

LTC4213 1 4213f 电子电路保护器说明书

2µs/DIV4213 TA01b124213fBias Supply Voltage (V CC )...........................–0.3V to 9V Input VoltagesON, SENSEP, SENSEN.............................–0.3V to 9V I SEL ..........................................–0.3V to (V CC + 0.3V)Output VoltagesGATE .....................................................–0.3V to 15V READY.....................................................–0.3V to 9V Operating Temperature RangeLTC4213C ...............................................0°C to 70°C LTC4213I.............................................–40°C to 85°C Storage Temperature Range.................–65°C to 150°C Lead Temperature (Soldering, 10sec)...................300°CORDER PART NUMBER DDB PART*MARKING T JMAX = 125°C, θJA = 250°C/WEXPOSED PAD (PIN 9)PCB CONNECTION OPTIONALConsult LTC Marketing for parts specified with wider operating temperature ranges.*The temperature grade is identified by a label on the shipping container.LBHVLTC4213CDDB LTC4213IDDB ABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOUUW (Note 1)ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV CC Bias Supply Voltage ● 2.36V V SENSEP SENSEP Voltage ●06V I CC V CC Supply Current●1.63mA V CC(UVLR)V CC Undervoltage Lockout Release V CC Rising● 1.8 2.07 2.23V ∆V CC(UVHYST)V CC Undervoltage Lockout Hysteresis ●30100160mV I SENSEP SENSEP Input Current V SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA I SENSENSENSEN Input CurrentV SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA V SENSEP = V SENSEN = 5V,50280µAReset Mode or Fault ModeV CBCircuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●22.52527.5mV V CB = V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●455055mV I SEL = V CC, V SENSEP = V CC ●90100110mV V CB(FAST)Fast Circuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●63100115mV V CB(FAST)= V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●126175200mV I SEL = V CC, V SENSEP = V CC ●252325371mV I GATE(UP)GATE Pin Pull Up Current V GATE = 0V●–50–100–150µA I GATE(DN)GATE Pin Pull Down Current ∆V SENSEP – V SENSEN = 200mV, V GATE = 8V ●1040mA ∆V GSMAX External N-Channel Gate Drive V SENSEN = 0, V CC ≥ 2.97V, I GATE = –1µA ● 4.8 6.58V V SENSEN = 0, V CC = 2.3V, I GATE = –1µA ● 2.65 4.38V ∆V GSARMV GS Voltage to Arm Circuit BreakerV SENSEN = 0, V CC ≥ 2.97V ● 4.4 5.47.6V V SENSEN = 0, V CC = 2.3V●2.53.57VTOP VIEWDDB PACKAGE8-LEAD (3mm × 2mm) PLASTIC DFN567894321READY ON I SEL GND V CC SENSEP SENSEN GATE34213f∆V GSMAX – ∆V GSARM Difference Between ∆V GSMAX and V SENSEN = 0, V CC ≥ 2.97V ●0.3 1.1V ∆V GSARMV SENSEN = 0, V CC = 2.3V●0.150.8VV READY(OL)READY Pin Output Low Voltage I READY = 1.6mA, Pull Down Device On ●0.20.4V I READY(LEAK)READY Pin Leakage Current V READY = 5V, Pull Down Device Off ●0±1µA V ON(TH)ON Pin High Threshold ON Rising, GATE Pulls Up ●0.760.80.84V ∆V ON(HYST)ON Pin Hysteresis ON Falling, GATE Pulls Down104090mV V ON(RST)ON Pin Reset Threshold ON Falling, Fault Reset, GATE Pull Down ●0.360.40.44V I ON(IN)ON Pin Input Current V ON = 1.2V●0±1µA ∆V OV Overvoltage Threshold ●0.410.7 1.1V ∆V OV = V SENSEP – V CCt OVOvervoltage Protection Trip Time V SENSEP = V SENSEN = Step 5V to 6.2V 2565160µs t FAULT(SLOW)V CB Trips to GATE Discharging ∆V SENSE Step 0mV to 50mV,●71627µs V SENSEN Falling, V CC = V SENSEP = 5V t FAULT(FAST)V CB(FAST) Trips to GATE Discharging ∆V SENSE Step 0V to 0.3V, V SENSEN Falling,●12.5µs V SENSEP = 5Vt DEBOUNCE Startup De-Bounce Time V ON = 0V to 2V Step to Gate Rising,2760130µs (Exiting Reset Mode)t READY READY Delay Time V GATE = 0V to 8V Step to READY Rising,2250115µs V SENSEP = V SENSEN = 0t OFF Turn-Off Time V ON = 2V to 0.6V Step to GATE Discharging 1.5510µs t ON Turn-On Time V ON = 0.6V to 2V Step to GATE Rising,4816µs (Normal Mode)t RESETReset TimeV ON Step 2V to 0V2080150µsNote 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOLPARAMETERCONDITIONSMIN TYP MAX UNITSNote 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.4564213ft RESET vs Temperaturet FAULT(SLOW) vs V CCt FAULT(SLOW) vs Temperaturet FAULT(FAST) vs V CCt FAULT(FAST) vs TemperatureTYPICAL PERFOR A CE CHARACTERISTICSU WSpecifications are at T A = 25°C. V CC = 5Vunless otherwise noted.t F A U L T (F A S T ) (µs )4213 G230.90.80.71.01.11.21.3TEMPERATURE (°C)–50050100125–252575BIAS SUPPLY VOLTAGE (V)2.010t F A U L T (S L O W ) (µs )14121618 3.0 4.0 5.0 6.04213 G202022 2.53.54.55.5TEMPERATURE (°C)–500501001254213 G21–25257510t F A U L T (S L O W ) (µs )141216182022TEMPERATURE (°C)–500501001254213 G19–252575t R E S E T (µs )60708090100BIAS SUPPLY VOLTAGE (V)2.0t F A U L T (F A S T ) (µs )3.04.05.06.04213 G222.53.54.55.50.90.80.71.01.11.21.374213fPI FU CTIO SU U UREADY (Pin 1): READY Status Output. Open drain output that goes high impedance when the external MOSFET is on and the circuit breaker is armed. Otherwise this pin pulls low.ON (Pin 2): ON Control Input. The LTC4213 is in reset mode when the ON pin is below 0.4V. When the ON pin increases above 0.8V, the device starts up and the GATE pulls up with a 100µA current source. When the ON pin drops below 0.76V, the GATE pulls down. To reset a circuit breaker fault, the ON pin must go below 0.4V.I SEL (Pin 3): Threshold Select Input. With the I SEL pin grounded, float or tied to V CC the V CB is set to 25mV, 50mV or 100mV, respectively. The corresponding V CB(FAST)values are 100mV, 175mV and 325mV.GND (Pin 4): Device Ground.GATE (P in 5): GATE D rive Output. An internal charge pump supplies 100µA pull-up current to the gate of the external N-channel MOSFET. Internal circuitry limits thevoltage between the GATE and SENSEN pins to a safe gate drive voltage of less than 8V. When the circuit breaker trips, the GATE pin abruptly pulls to GND.SENSEN (Pin 6): Circuit Breaker Negative Sense Input.Connect this pin to the source of the external MOSFET.During reset or fault mode, the SENSEN pin discharges the output to ground with 280µA.SENSEP (P in 7): Circuit Breaker Positive Sense Input.Connect this pin to the drain of external N-channel MOSFET.The circuit breaker trips when the voltage across SENSEP and SENSEN exceeds V CB . The input common mode range of the circuit breaker is from ground to V CC + 0.2V when V CC < 2.5V. For V CC ≥ 2.5V, the input common mode range is from ground to V CC + 0.4V.V CC (Pin 8): Bias Supply Voltage Input. Normal operation is between 2.3V and 6V. An internal under-voltage lockout circuit disables the device when V CC < 2.07V.Exposed Pad (Pin 9): Exposed pad may be left open or connected to device ground.8910114213fsupply transient dips below 1.97V of less than 80µs are ignored.ON FunctionWhen V ON is below comparator COMP1’s threshold of 0.4V for 80µs, the device resets. The system leaves reset mode if the ON pin rises above comparator COMP2’s threshold of 0.8V and the UVLO condition is met. Leaving reset mode, the GATE pin starts up after a t DEBOUNCE delay of 60µs. When ON goes below 0.76V, the GATE shuts off after a 5µs glitch filter delay. The output is discharged by the external load when V ON is in between 0.4V to 0.8V. At this state, the ON pin can re-enable the GATE if V ON exceeds 0.8V for more than 8µs. Alternatively, the device resets if the ON pin is brought below 0.4V for 80µs. Once reset, the GATE pin restarts only after the t DEBOUNCE 60µs delay at V ON rising above 0.8V. To protect the ON pin from overvoltage stress due to supply transients, a series resistor of greater than 10k is recommended when the ON pin is connected directly to the supply. An external resis-tive divider at the ON pin can be used with COMP2 to set a supply undervoltage lockout value higher than the inter-nal UVLO circuit. An RC filter can be implemented at the ON pin to increase the powerup delay time beyond the internal 60µs delay.Gate FunctionThe GATE pin is held low in reset mode. 60µs after leaving reset mode, the GATE pin is charged up by an internal 100µA current source. The circuit breaker arms when V GATE > V SENSEN + ∆V GSARM . In normal mode operation,the GATE peak voltage is internally clamped to ∆V GSMAX above the SENSEN pin. When the circuit breaker trips, an internal MOSFET shorts the GATE pin to GND, turning off the external MOSFET.READY StatusThe READY pin is held low during reset and at startup. It is pulled high by an external pullup resistor 50µs after the circuit breaker arms. The READY pin pulls low if the circuit breaker trips or the ON pin is pulled below 0.76V, or V CC drops below undervoltage lockout.∆V GSARM and V GSMAXEach MOSFET has a recommended V GS drive voltage where the channel is deemed fully enhanced and R DSON is minimized. Driving beyond this recommended V GS volt-age yields a marginal decrease in R DSON . At startup, the gate voltage starts at ground potential. The GATE ramps past the MOSFET threshold and the load current begins to flow. When V GS exceeds ∆V GSARM , the circuit breaker is armed and enabled. The chosen MOSFET should have a recommended minimum V GS drive level that is lower than ∆V GSARM . Finally, V GS reaches a maximum at ∆V GSMAX.Trip and Reset Circuit BreakerFigure 2 shows the timing diagram of V GATE and V READY after a fault condition. A tripped circuit breaker can be reset either by cycling the V CC bias supply below UVLO thresh-old or pulling ON below 0.4V for >t RESET . Figure 3 shows the timing diagram for a tripped circuit breaker being reset by the ON pin.Calculating Current LimitThe fault current limit is determined by the R DSON of the MOSFET and the circuit breaker voltage V CB .I V R LIMIT CB DSON=()2The R DSON value depends on the manufacturer’s distribu-tion, V GS and junction temperature. Short Kelvin-sense connections between the MOSFET drain and source to the LTC4213 SENSEP and SENSEN pins are strongly recommended.For a selected MOSFET, the nominal load limit current is given by:I V R LIMIT NOM CB NOM DSON NOM ()()()()=3The minimum load limit current is given by:I V R LIMIT MIN CB MIN DSON MAX ()()()()=4APPLICATIO S I FOR ATIOW UUU1213144213fOperating temperature of 0° to 70°C.R DSON @ 25°C = 100%R DSON @ 0°C = 90%R DSON @ 70°C = 120%MOSFET resistance variation:R DSON(NOM) = 15m • 0.82 = 12.3m ΩR DSON(MAX) = 15m • 1.333 • 0.93 • 1.2 = 15m • 1.488= 22.3m ΩR DSON(MIN) = 15m • 0.667 • 0.80 • 0.90 = 15m • 0.480= 7.2m ΩV CB variation:NOM V CB = 25mV = 100%MIN V CB = 22.5mV = 90%MAX V CB = 27.5mV = 110%The current limits are:I LIMIT(NOM) = 25mV/12.3m Ω = 2.03A I LIMIT(MIN) = 22.5mV/22.3m Ω = 1.01A I LIMIT(MAX) = 27.5mV/7.2m Ω = 3.82AFor proper operation, the minimum current limit must exceed the circuit maximum operating load current with margin. So this system is suitable for operating load current up to 1A. From this calculation, we can start with the general rule for MOSFET R DSON by assuming maxi-mum operating load current is roughly half of the I LIMIT(NOM). Equation 7 shows the rule of thumb.I V R OPMAX CB NOM DSON NOM =()()•()27Note that the R DSON(NOM) is at the LTC4213 nominal operating ∆V GSMAX rather than at typical vendor spec.Table 1 gives the nominal operating ∆V GSMAX at the various operating V CC . From this table users can refer to the MOSFET’s data sheet to obtain the R DSON(NOM) value.Table 1. Nominal Operating ∆V GSMAX for Typical Bias Supply VoltageV CC (V)∆V GSMAX (V)2.3 4.32.5 5.02.7 5.63.0 6.53.37.05.07.06.07.0Load Supply Power-Up after Circuit Breaker Armed Figure 4 shows a normal power-up sequence for the circuit in Figure 1 where the V IN load supply power-up after circuit breaker is armed. V CC is first powered up by an auxiliary bias supply. V CC rises above 2.07V at time point 1. V ON exceeds 0.8V at time point 2. After a 60µs debounce delay, the GATE pin starts ramping up at time point 3. The external MOSFET starts conducting at time point 4. At time point 5, V GATE exceed ∆V GSARM and the circuit breaker is armed. After 50µs (t READY delay), READY pulls high by an external resistor at time point 6. READY signals the V IN load supply module to start its ramp. The load supply begins soft-start ramp at time point 7. The load supply ramp rate must be slow to prevent circuit breaker tripping as in equation (8).∆∆V t I I C IN OPMAX LOADLOAD<−()8Where I OPMAX is the maximum operating current defined by equation 7.For illustration, V CB = 25mV and R DSON = 3.5m Ω at the nominal operating ∆V GSMAX . The maximum operating current is 3.5A (refer to equation 7). Assuming the load can draw a current of 2A at power-up, there is a margin of 1.5A available for C LOAD of 100µF and V IN ramp rate should be <15V/ms. At time point 8, the current through the MOSFET reduces after C LOAD is fully charged.APPLICATIO S I FOR ATIOW UUU1516174213fThe selected MOSFET V GS absolute maximum rating should meet the LTC4213 maximum ∆V GSMAX of 8V.Other MOSFET criteria such as V BDSS , I DMAX , and R DSON should be reviewed. Spikes and ringing above maximum operating voltage should be considered when choosing V BDSS . I DMAX should be greater than the current limit. The maximum operating load current is determined by the R DSON value. See the section on “Calculating Current Limit” for details.Supply RequirementsThe LTC4213 can be powered from a single supply or dual supply system. The load supply is connected to the SENSEP pin and the drain of the external MOSFET. In the single supply case, the V CC pin is connected to the load supply, preferably with an RC filter. With dual supplies,V CC is connected to an auxiliary bias supply V AUX where V AUX voltage should be greater or equal to the load supply voltage. The load supply voltage must be capable of sourcing more current than the circuit breaker limit. If the load supply current limit is below the circuit breaker trip current, the LTC4213 may not react when the output overloads. Furthermore, output overloads may trigger UVLO if the load supply has foldback current limit in a single supply system.V IN Transient and Overvoltage ProtectionInput transient spikes are commonly observed whenever the LTC4213 responds to overload. These spikes can be large in amplitude, especially given that large decoupling capacitors are absent in hot swap environments. These short spikes can be clipped with a transient suppressor of adequate voltage and power rating. In addition, the LTC4213can detect a prolonged overvoltage condition. WhenAPPLICATIO S I FOR ATIOW UUU point 6 should be within the circuit breaker limits. Other-wise, the system fails to start and the circuit breaker trips immediately after arming. In most applications additional external gate capacitance is not required unless C LOAD is large and startup becomes problematic. If an external gate capacitor is employed, its capacitance value should not be excessive unless it is used with a series resistor. This is because a big gate capacitor without resistor slows down the GATE turn off during a fault. An alternative method would be a stepped I SEL pin to allow a higher current limit during startup.In the event of output short circuit or a severe overload, the load supply can collapse during GATE ramp up due to load supply current limit. The chosen MOSFET must withstand this possible brief short circuit condition before time point 6 where the circuit breaker is allowed to trip. Bench short circuit evaluation is a practical verification of a reliable design. To have current limit while powering a MOSFET into short circuit conditions, it is preferred that the load supply sequences to turn on after the circuit breaker is armed as described in an earlier section.Power-Off CycleThe system can be powered off by toggling the ON pin low.When ON is brought below 0.76V for 5µs, the GATE and READY pins are pulled low. The system resets when ON is brought below 0.4V for 80µs.MOSFET SelectionThe LTC4213 is designed to be used with logic (5V) and sub-logic (3V) MOSFETs for V CC potentials above 2.97V with ∆V GSMAX exceeding 4.5V. For a V CC supply range between 2.3V and 2.97V, sub-logic MOSFETs should be used as the minimum ∆V GSMAX is less than 4.5V.1819Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.201630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2005LT/TP 0405 500 • PRINTED IN USA。

IC集成电路型号大全及40系列芯片功能大全

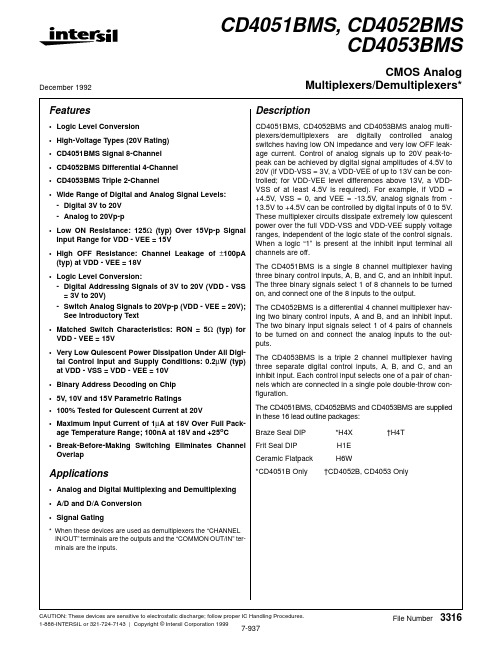

IC集成电路型号大全及40系列芯片功能大全CD4001 四2输入端或者非门CD4002 双4输入端或者非门CD4006 18位串入/串出移位寄存器CD4007 双互补对加反相器CD4008 4位超前进位全加器CD4009 六反相缓冲/变换器CD4010 六同相缓冲/变换器CD4011 四2输入端与非门CD4012 双4输入端与非门CD4013 双主-从D型触发器CD4014 8位串入/并入-串出移位寄存器CD4015 双4位串入/并出移位寄存器CD4016 四传输门CD4017 十进制计数/分配器CD4018 可预制1/N计数器CD4019 四与或者选择器CD4020 14级串行二进制计数/分频器CD4021 08位串入/并入-串出移位寄存器CD4022 八进制计数/分配器CD4023 三3输入端与非门CD4024 7级二进制串行计数/分频器CD4025 三3输入端或者非门CD4026 十进制计数/7段译码器CD4027 双J-K触发器CD4028 BCD码十进制译码器CD4029 可预置可逆计数器CD4030 四异或者门CD4031 64位串入/串出移位存储器CD4032 三串行加法器CD4033 十进制计数/7段译码器CD4034 8位通用总线寄存器CD4035 4位并入/串入-并出/串出移位寄存CD4038 三串行加法器CD4040 12级二进制串行计数/分频器CD4041 四同相/反相缓冲器CD4042 四锁存D型触发器CD4043 三态R-S锁存触发器("1"触发)CD4044 四三态R-S锁存触发器("0"触发)CD4046 锁相环CD4047 无稳态/单稳态多谐振荡器CD4048 四输入端可扩展多功能门CD4049 六反相缓冲/变换器CD4050 六同相缓冲/变换器CD4051 八选一模拟开关CD4052 双4选1模拟开关CD4053 三组二路模拟开关CD4054 液晶显示驱动器CD4055 BCD-7段译码/液晶驱动器CD4056 液晶显示驱动器CD4059 “N”分频计数器 NSC/TICD4060 14级二进制串行计数/分频器CD4063 四位数字比较器CD4066 四传输门CD4067 16选1模拟开关CD4068 八输入端与非门/与门CD4069 六反相器CD4070 四异或者门CD4071 四2输入端或者门CD4072 双4输入端或者门CD4073 三3输入端与门CD4075 三3输入端或者门CD4076 四D寄存器CD4077 四2输入端异或者非门CD4078 8输入端或者非门/或者门CD4081 四2输入端与门CD4082 双4输入端与门CD4085 双2路2输入端与或者非门CD4086 四2输入端可扩展与或者非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器CD4095 三输入端J-K触发器CD4096 三输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器CD4099 8位可寻址锁存器CD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器CD40107 双2输入端与非缓冲/驱动器CD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动CD40147 10-4线编码器CD40160 可预置BCD加计数器CD40161 可预置4位二进制加计数器CD40162 BCD加法计数器CD40163 4位二进制同步计数器CD40174 六锁存D型触发器CD40175 四D型触发器CD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) CD40193 可预置4位二进制加/减计数器CD40194 4位并入/串入-并出/串出移位寄存CD40195 4位并入/串入-并出/串出移位寄存CD40208 4×4多端口寄存器CD4501 4输入端双与门及2输入端或者非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或者非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐) CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或者选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD22100 4×4×1交叉点开关0206A 天线开关集成电路03VFG9 发射压控振荡集成电路1021AC 发射压控振荡集成电路1097C 升压集成电路140N 电源取样比较放大集成电路14DN363 伺服操纵集成电路15105 充电操纵集成电路15551 管理卡升压集成电路1710 视频信号处理集成电路1N706 混响延时集成电路20810-F6096 存储集成电路2252B 微处理集成电路2274 延迟集成电路24C01ACEA 存储集成电路24C026 存储集成电路24C04 存储集成电路24C64 码片集成电路24LC16B 存储集成电路24LC65 电可改写编程只读存储集成电路27C1000PC-12 存储集成电路27C2000QC-90 存储集成电路27C20T 存储集成电路27C512 电可改写编程只读存储集成电路2800 红外遥控信号接收集成电路28BV64 码片集成电路28F004 版本集成电路31085 射频电源集成电路32D54 电源、音频信号处理集成电路1732D75 电源、音频信号处理集成电路32D92 电源中频放大集成电路4066B 电子开关切换集成电路4094 移位寄存串入、并出集成电路424260SDJ 存储集成电路4260 动态随机存储集成电路4270351/91B9905 中频放大集成电路4370341/90M9919 中频处理集成电路4464 存储集成电路4558 双运算放大集成电路4580D 双运算放大集成电路47C1638AN-U337 微处理集成电路47C1638AU-353 微处理集成电路47C432GP 微处理集成电路47C433AN-3888 微处理集成电路49/4CR1A 中频放大集成电路5101 天线开关集成电路5G052 发光二极管四位显示驱动集成电路5G24 运算放大集成电路5W01 双运算放大集成电路649/CRIA70612 中频放大集成电路673/3CR2A 多模转换集成电路74122 可重触发单稳态集成电路74HC04 逻辑与非门集成电路74HC04D 六反相集成电路74HC123 单稳态集成电路74HC125 端口功能扩展集成电路74HC14N 六反相集成电路74HC157A 多路转换集成电路74HC165 移相寄存集成电路1874HC245 总线收发集成电路74HC32 或者门四2输入集成电路74HC374八D 触发集成电路74HC573D 存储集成电路74HCT157 多路转换双输入集成电路74HCT4046A 压控振荡集成电路74HCT4538D 单稳态集成电路74HCT4538N 触发脉冲集成电路74HCT86D 异或者门四2输入集成电路74HCU04 与非门集成电路74LS125 端口功能扩展集成电路74LS373 锁存集成电路74LS393 计数双四位二进制集成电路74LS74双D 触发集成电路78014DFP 系统操纵处理集成电路811N 伴音阻容偏置集成电路83D33 压控振荡集成电路85712 场扫描信号校正处理集成电路85713 行扫描信号校正集成电路87C52 微处理集成电路87CK38N-3584 微处理集成电路87CK38N-3627 微处理集成电路89C52 系统操纵处理集成电路89C55 系统操纵处理集成电路93C66 电可改写编程只读存储集成电路93LC56 电可改写编程存储集成电路9821K03 系统操纵集成电路A1642P 背景歌声消除集成电路A701 红外遥控信号接收集成电路A7950 场频识别集成电路19A8772AN 色差信号延迟处理集成电路A9109 功率放大集成电路AAB 电源集成电路ACA650 色度信号解调集成电路ACFP2 色度、亮度信号分离集成电路ACP2371 多伴音、多语言改善集成电路ACVP2205 色度、亮度信号分离集成电路AD1853 立体声数/模转换集成电路AD1858 音频解调集成电路AD722 视频编码集成电路ADC2300E 音频数/模转换集成电路ADC2300J 音频数/模转换集成电路ADC2310E 音频数/模转换集成电路ADV7172 视频编码集成电路ADV7175A 视频编码集成电路AE31201 频率显示集成电路AJ7080 射频调制集成电路AK4321-VF-E1 音频数/模转换集成电路AN1319 双高速电压比较集成电路AN1358S 双运算放大集成电路AN1393 双运算放大集成电路AN1431T 稳压电源集成电路AN1452 音频前置放大集成电路AN1458S 双运算放大集成电路AN206 伴音中频及前置放大集成电路AN222 自动频率操纵集成电路AN236 副载波信号处理集成电路AN239Q 图像、伴音中频放大集成电路AN247P 图像中频放大、AGC操纵集成电路AN253P 调频/调幅中频放大集成电路20AN262 音频前置放大集成电路AN2661NK 视频信号处理集成电路AN2663K 视频信号处理集成电路AN272 音频功率放大集成电路AN2751FAP 视频信号处理集成电路AN281 色度解码集成电路AN2870FC 多功能操纵集成电路AN295 行、场扫描信号处理集成电路AN301 伺服操纵集成电路AN305 视频自动增益操纵集成电路AN306 色度自动相位操纵集成电路AN318 直流伺服操纵集成电路AN320 频率操纵、调谐显示驱动集成电路AN3215K 视频信号处理集成电路AN3215S 视频信号处理集成电路AN3224K 磁头信号记录放大集成电路AN3248NK 亮度信号记录、重放处理集成电路AN331 视频信号处理集成电路AN3311K 磁头信号放大集成电路AN3313 磁头信号放大集成电路AN3321S 录像重放信号处理集成电路AN3331K 磁头信号处理集成电路AN3337NSB 磁头信号放大集成电路AN3380K 磁头信号处理集成电路AN3386NK 磁头信号处理集成电路AN3495K 色度、亮度信号降噪集成电路AN355 伴音中频放大、检波集成电路AN3581S 视频驱动集成电路AN366 调频/调幅中频放大集成电路AN3791 移位操纵集成电路21AN3792 磁鼓伺服操纵接口集成电路AN3795 主轴伺服操纵接口集成电路AN3814K 电机驱动集成电路AN4265 音频功率放大集成电路AN4558 运算放大集成电路AN5010 电子选台集成电路AN5011 电子选台集成电路AN5015K 电子选台集成电路AN5020 红外遥控信号接收集成电路AN5025S 红外遥控信号接收集成电路AN5026K 红外遥控信号接收集成电路AN5031 电调谐操纵集成电路AN5034 调谐操纵集成电路AN5036 调谐操纵集成电路AN5043 调谐操纵集成电路AN5071 频段转换集成电路AN5095K 电视信号处理集成电路AN5110 图像中频放大集成电路AN5130 图像中频、视频检波放大集成电路AN5138NK 图像、伴音中频放大集成电路AN5156K 电视信号处理集成电路AN5177NK 图像、伴音中频放大集成电路AN5179K 图像、伴音中频放大集成电路AN5183K 中频信号处理集成电路AN5195K 中频、色度、扫描信号处理集成电路AN5215 伴音信号处理集成电路AN5520 伴音中频放大及鉴频集成电路AN5222 伴音中频放大集成电路AN5250 伴音中频放大、鉴频及功率放大集成电路AN5262 音频前置放大集成电路22AN5265 音频功率放大集成电路AN5270 音频功率放大集成电路AN5273 双声道音频功率放大集成电路AN5274 双声道音频功率放大集成电路AN5275 中置、3D放大集成电路AN5285K 双声道前置放大集成电路AN5295NK 音频信号切换集成电路AN5312 视频、色度信号处理集成电路AN5313NK 视频、色度信号处理集成电路AN5342 图像水平轮廓校正集成电路AN5342FB 水平清晰度操纵集成电路AN5344FBP 色度信号处理集成电路AN5348K 人工智能信号处理集成电路AN5385K 色差信号放大集成电路AN5410 行、场扫描信号处理集成电路AN5421 同步检测集成电路AN5422 行、场扫描信号处理集成电路AN5512 场扫描输出集成电路AN5515 场扫描输出集成电路AN5521 场扫描输出集成电路AN5532 场扫描输出集成电路AN5534 场扫描输出集成电路AN5551 枕形校正集成电路AN5560 场频识别集成电路AN5600K 中频、亮度、色度及扫描信号处理集成电路AN5601K 视频、色度、同步信号处理集成电路AN5607K 视频、色度、行场扫描信号处理集成电路AN5615 视频信号处理集成电路AN5620X 色度信号处理集成电路AN5621 场扫描输出集成电路23AN5625 色度信号处理集成电路AN5633K 色度信号处理集成电路AN5635 色度解码集成电路AN5635NS 色度解码集成电路AN5637 色度解码、亮度延迟集成电路AN5650 同步信号分离集成电路AN5682K 基色电子开关切换集成电路AN5693K 视频、色度、行场扫描信号处理集成电路AN5712 图像中频放大、AGC操纵集成电路AN5722 图像中频放大、检波集成电路AN5732 伴音中频放大、鉴频集成电路AN5743 音频功率放大集成电路AN5750 行自动频率操纵及振荡集成电路AN5757S 行扫描电源电压操纵集成电路AN5762 场扫描振荡、输出集成电路AN5764 光栅水平位置操纵集成电路AN5765 电源稳压操纵集成电路AN5767 同步信号处理集成电路AN5768 光栅倾斜校正操纵集成电路AN5769 行、场会聚操纵集成电路AN5790N 行扫描信号处理集成电路AN5791 同步脉冲相位与脉宽调整集成电路AN5803 双声道立体声解调集成电路AN5836 双声道前置放大集成电路AN5858K 视频信号操纵集成电路AN5862 视频信号操纵集成电路AN5862S-E1 视频信号开关操纵集成电路AN5870K 模拟信号切换集成电路AN5891K 音频信号处理集成电路AN614 行枕形校正集成电路24AN6210 双声道前置放大集成电路AN6306S 亮度信号处理集成电路AN6308 模拟电子开关集成电路AN6327 视频重放信号处理集成电路AN6341N 伺服操纵集成电路AN6342N 基准分频集成电路AN6344 伺服操纵集成电路AN6345 分频集成电路AN6346N 磁鼓伺服操纵集成电路AN6350 磁鼓伺服操纵集成电路AN6357N 主轴接口集成电路AN6361N 色度信号处理集成电路AN6367NK 色度信号处理集成电路AN6371S 自动相位操纵集成电路AN6387 电机伺服操纵集成电路AN6550 卡拉OK音频放大集成电路AN6554 四运算放大集成电路AN6561 双运算放大集成电路AN6562SG 双运算放大集成电路AN6609N 电机驱动集成电路AN6612 电机稳速操纵集成电路AN6650 电机速度操纵集成电路AN6651 电机速度操纵集成电路AN6652 电机稳速操纵集成电路AN6875 发光二极管五位显示驱动集成电路AN6877 发光二极管七位显示驱动集成电路AN6884 发光二极管五位显示驱动集成电路AN6886 发光二极管五位显示驱动集成电路AN6888 发光二极管显示驱动集成电路AN6914 双电压比较集成电路25AN7085N5 单片录、放音集成电路AN7105 双声道音频功率放大集成电路AN7106K 双声道音频功率放大集成电路AN7108 单片立体声放音集成电路AN710S 单片放音集成电路AN7110E 音频功率放大集成电路AN7114 音频功率放大集成电路AN7116 音频功率放大集成电路AN7118 双声道音频功率放大集成电路AN7118S 双声道音频功率放大集成电路AN7120 音频功率放大集成电路AN7124 双声道音频功率放大集成电路AN7145 双声道音频功率放大集成电路AN7148 双声道音频功率放大集成电路AN7158N 音频功率放大7.5W×2集成电路AN7161N 音频功率放大集成电路AN7164 双声道音频功率放大集成电路AN7171NK 音频功率放大集成电路AN7205 调频/调谐及高频放大集成电路AN7220 调频/调幅中频放大集成电路AN7222 调频/调幅中频放大集成电路AN7223 调频/调幅中频放大集成电路AN7226 调频/调幅中频放大集成电路AN7256 调频/调谐及中频放大集成电路AN7311 双声道前置放大集成电路AN7312 双声道前置放大集成电路AN7315 双声道前置放大集成电路AN7315S 双声道前置放大集成电路AN7320 音频前置放大集成电路AN7396K 双声道前置放大集成电路26AN7397K 双声道前置放大集成电路AN7410 调频立体声多路解码集成电路AN7414 调频立体声解码集成电路AN7420N 调频立体声解码集成电路AN7470 调频立体声解码集成电路AN7805 三端电源稳压+5V/1A集成电路AN7806 三端电源稳压+6V/1A集成电路AN7807 三端电源稳压+7V/1A集成电路AN7808 三端电源稳压+8V/1A集成电路AN7809 电源稳压+9V/1A集成电路AN7810 三端电源稳压+10V/1A集成电路AN7812 三端电源稳压+12V/1A集成电路AN7815 三端电源稳压+15V/1A集成电路AN7818 三端电源稳压+18V/1A集成电路AN7820 三端电源稳压+20V/1A集成电路AN7824 三端电源稳压+24V/1A集成电路AN78L05 三端电源稳压+5V/0.1A集成电路AN78L06 三端电源稳压+6V/0.1A集成电路AN78L08 三端电源稳压+8V/0.1A集成电路AN78L09 三端电源稳压+9V/0.1A集成电路AN78L10 三端电源稳压+10V/0.1A集成电路AN78L12 三端电源稳压+12V/0.1A集成电路AN78L15 三端电源稳压+15V/0.1A集成电路AN78L18 三端电源稳压+18V/0.1A集成电路AN78L20 三端电源稳压+20V/0.1A集成电路AN78L24 三端电源稳压+24V/0.1A集成电路AN78M05 三端电源稳压+5V/0.5A集成电路AN78M06 三端电源稳压+6V/0.5A集成电路AN78M08 三端电源稳压+8V/0.5A集成电路AN78M09 三端电源稳压+9V/0.5A集成电路27AN78M10 三端电源稳压+10V/0.5A集成电路AN78M12 三端电源稳压+12V/0.5A集成电路AN78M15 三端固定式稳压+15V/0.5A集成电路AN78M18 三端电源稳压+18V/0.5A集成电路AN78M20 三端电源稳压+20V/0.5A集成电路AN78M24 三端电源稳压+24V/0.5A集成电路AN7905 三端电源稳压-5V/1A集成电路AN7906 三端电源稳压-6V/1A集成电路AN7908T 三端电源稳压-8V/1A集成电路AN7909T 三端电源稳压-9V/1A集成电路AN7910T 三端电源稳压-10V/1A集成电路AN7912 三端电源稳压-12V/1A集成电路AN7915 三端电源稳压-15V/1A集成电路AN7918 三端电源稳压-18V/1A集成电路AN7920 三端电源稳压-20V/1A集成电路AN7924 三端电源稳压-24V/1A集成电路AN79L05 三端电源稳压-5V/0.1A集成电路AN79L06 三端电源稳压-6V/0.1A集成电路AN79L08 三端电源稳压-8V/0.1A集成电路AN79L09 三端电源稳压-9V/0.1A集成电路AN79L10 三端电源稳压-10V/0.1A集成电路AN79L12 三端电源稳压-12V/0.1A集成电路AN79L15 三端电源稳压-15V/0.1A集成电路AN79L18 三端电源稳压-18V/0.1A集成电路AN79L20 三端电源稳压-20V/0.1A集成电路AN79L24 三端电源稳压-24V/0.1A集成电路AN79M05 三端电源稳压-5V/0.5A集成电路AN79M06 三端电源稳压-6V/0.5A集成电路AN79M08 三端电源稳压-8V/0.5A集成电路AN79M09 三端电源稳压-9V/0.5A集成电路28AN79M10 三端电源稳压-10V/0.5A集成电路AN79M12 三端电源稳压-12V/0.5A集成电路AN79M15 三端电源稳压-15V/0.5A集成电路AN79M18 三端电源稳压-18V/0.5A集成电路AN79M20 三端电源稳压-20V/0.5A集成电路AN79M24 三端电源稳压-24V/0.5A集成电路AN8028 自激式开关电源操纵集成电路AN8270K 主轴电机操纵集成电路AN8280 电机驱动集成电路AN8281S 电机驱动集成电路AN8290S 主轴电机驱动集成电路AN8355S 条形码扫描接收集成电路AN8370S 光电伺服操纵集成电路AN8373S 射频伺服处理集成电路AN8375S 伺服处理集成电路AN8389S-E1 电机驱动集成电路AN8480NSB 主轴电机驱动集成电路AN8481SB-E1 主轴电机驱动集成电路AN8482SB 主轴电机驱动集成电路AN8623FBQ 主轴伺服处理集成电路AN8788FB 电机驱动集成电路AN8802CE1V 伺服处理集成电路AN8813NSBS 主轴电机驱动集成电路AN8819NFB 伺服驱动、直流交换集成电路AN8824FBQ 前置放大集成电路AN8825NFHQ-V 聚焦、循迹误差处理集成电路AN8831SC 视频预视放集成电路AN8832SB-E1 射频放大、伺服处理集成电路AN8837SB-E1 伺服处理集成电路AN89C2051-24PC 微处理集成电路29APU2400U 音频信号处理集成电路APU2470 音频信号处理集成电路AS4C14405-60JC 动态随机存储1M×4集成电路AS4C256K16ED-60JC 存储集成电路ASD0204-015 图文操纵集成电路ASD0204GF-022-3BA显示操纵集成电路AT24C08 存储集成电路AT24C08A 存储集成电路AT24C256-10CI 码片集成电路AT27C010 电可改写编程只读存储集成电路AT27C020 存储集成电路ATMEL834 存储集成电路AVM-1 视频信号处理厚膜集成电路AVM-2 音频信号处理厚膜集成电路AVSIBCP08 倍压整流切换集成电路B0011A 存储集成电路B1218 电子快门操纵集成电路BA033T 三端电源稳压+3.3V集成电路BA10324 四运算放大集成电路BA10393N 双运算放大集成电路BA1102F 杜比降噪处理集成电路BA1106F 杜比降噪处理集成电路BA12ST 电源稳压集成电路BA1310 调频立体声解码集成电路BA1332L 调频立体声解码集成电路BA1350 调频立体声解码集成电路BA1351 调频立体声解码集成电路BA1356 调频立体声解码集成电路BA1360 调频立体声解码集成电路BA15218N 双运算放大集成电路30BA225 可触发双单稳态振荡集成电路BA302 音频前置放大集成电路BA311 音频前置放大集成电路BA313 音频前置放大集成电路BA3283 单片放音集成电路BA328F 双声道前置放大集成电路BA329 双声道前置放大集成电路BA3304F 录放音前置均衡放大集成电路BA3306 音频、前置放大集成电路BA3312N 话筒信号前置放大集成电路BA3313L 自动音量操纵集成电路BA3314 话筒信号前置放大集成电路BA335 自动选曲集成电路BA336 自动选曲集成电路BA340 音频前置放大集成电路BA3402F 双声道前置放大集成电路BA3404F 自返转放音集成电路BA343 双声道前置放大集成电路BA3503F 双声道前置放大集成电路BA3506 单片放音集成电路BA3513FS 单片放音集成电路BA3516 单片放音集成电路BA3706 自动选曲集成电路BA3707 录音带曲间检测集成电路BA3812L 五频段音调补偿集成电路BA3818F 电压比较运放集成电路BA3822LS 双声道五频段显示均衡集成电路BA3828 电子选台预置集成电路BA3880 音频处理集成电路31BA401 调频中频放大集成电路BA402 调频中频放大集成电路BA4110 调频中频放大集成电路BA4234L 调频中频放大集成电路BA4402 调频调谐收音集成电路BA4403 调频高频放大、混频、本振集成电路BA4560 双运算放大集成电路BA5096 数字混响集成电路BA5102A 音频功率放大集成电路BA514 音频功率放大集成电路BA516 音频功率放大集成电路BA5208AF 音频功率放大集成电路BA532 音频功率放大集成电路BA534 音频功率放大集成电路BA5406 双声道音频功率放大集成电路BA5412 音频功率放大集成电路BA547 音频功率放大1.5W集成电路BA5912AFP-YE2 电机驱动、倾斜、加载集成电路BA5981FP-E2 聚焦、循迹驱动集成电路BA5983FB 四通道伺服驱动集成电路BA5983FM-E2 电机驱动集成电路BA6104 发光二极管五位显示驱动集成电路BA6107A 电机伺服操纵集成电路BA6109 加载电机驱动集成电路BA6125 发光二极管五位显示驱动集成电路BA6137 发光二极管五位显示驱动集成电路BA6191 音频操纵集成电路BA6196FP 伺服驱动集成电路BA6208 电机驱动集成电路BA6208D 电机驱动集成电路32BA6209 电机驱动集成电路BA6209N 双向驱动电机集成电路BA6218 加载电机驱动集成电路BA6219 电机驱动集成电路BA6219B 电机驱动集成电路BA6227 电机稳速操纵集成电路BA6238 电机驱动集成电路BA6239 电机双向驱动集成电路BA6239A 电机双向驱动集成电路BA6246M 加载、转盘电机驱动集成电路BA6248 电机驱动集成电路BA6286 电机驱动集成电路BA6287 电机驱动集成电路BA6290 电机驱动集成电路BA6295AFP-E2 加载、倾斜驱动集成电路BA6296FP 电机速度操纵集成电路BA6297AFP 伺服驱动集成电路BA6302A 电机伺服操纵集成电路BA6305 操纵放大集成电路BA6305F 操纵放大集成电路BA6308 电子开关切换集成电路BA6321 电机伺服操纵集成电路BA6392 伺服驱动集成电路BA6395 主轴电机驱动集成电路BA6396FP 伺服驱动集成电路BA6411 电机驱动集成电路BA6435S 主轴电机驱动集成电路BA6459P1 电机驱动集成电路BA6570FP-E2 聚焦、循迹驱动集成电路33BA6664FM 三相主电机驱动集成电路BA6791FP 四通道伺服驱动集成电路BA6796FP 电机驱动集成电路BA6810S 音频显示驱动集成电路BA6844AFP-E2 三相主电机驱动集成电路BA6849FP 主轴电机驱动集成电路BA689 发光二极管十二位显示驱动集成电路BA6893KE2 直流变换驱动集成电路BA6956AN 加载电机驱动集成电路BA6993 双运算放大集成电路BA7001 音频切换集成电路BA7004 测试信号发生集成电路BA7005AL 射频调制集成电路BA7007 信号检测集成电路BA7021 视频信号选择集成电路BA7024 视频信号测试集成电路BA7025L 信号检测集成电路BA7042 振荡集成电路BA7047 调频检波集成电路BA7048N 包络信号检测集成电路BA7106LS 检测信号操纵集成电路BA7180FS 磁头信号放大集成电路BA7212S 磁头信号放大集成电路BA7253S 磁头信号放大集成电路BA7254S 四磁头信号放大集成电路BA7258AS 亮度信号处理集成电路BA7264S 视频信号处理集成电路BA7274S 磁头信号放大集成电路BA7357S 中频放大集成电路BA7604N 电子开关切换集成电路34BA7606F 色差信号切换集成电路BA7655 色度信号处理集成电路BA7665FS-E2 视频输出放大集成电路BA7725FS 混响立体声放大集成电路BA7725S 信号压缩及扩展处理集成电路BA7743FS 磁头信号放大集成电路BA7751ALS 音频信号录放处理集成电路BA7752LS 音频信号处理集成电路BA7755 磁头开关集成电路BA7755AF-E2 磁头开关集成电路BA7765AS 音频信号处理集成电路BA7766SA 音频信号处理集成电路BA7767AS 音频信号处理集成电路BA7797F 音频信号处理集成电路BA8420 特技操纵处理集成电路BAL6309 场同步信号发生集成电路BH3866AS 音频、色度信号前置放大集成电路BH4001 微处理集成电路BH7331P 音频功率放大集成电路BH7770KS 音频信号处理集成电路BL3207 亮度延时集成电路BL3208B 音频延迟混响集成电路BL5132 中频放大集成电路BL54573 电子调频波段转换集成电路BL5612 视频放大、色差矩阵集成电路BM5060 微处理集成电路BM5061 字符发生集成电路BM5069 微处理集成电路BN5115 图像中频放大集成电路BOC31F 单片微处理集成电路35BP5020 视频电源转换集成电路BT852 视频编码集成电路BT864 视频编码集成电路BT866PQFP 微处理集成电路BU12102 时序信号发生解码集成电路BU2092F 扩展集成电路BU2185F 同步信号处理集成电路BU2285FV 时钟信号发生集成电路BU2820 伺服操纵集成电路BU2841FS 视频、蓝背景信号发生集成电路BU2872AK 操作系统操纵、屏显驱动集成电路BU3762AF 红外遥控信号发射集成电路BU4053B 电子开关切换集成电路BU5814F 红外遥控信号发射集成电路BU5994F 红外遥控信号发射集成电路BU6198F 屏幕显示集成电路BU9252F 音频延时集成电路BU9252S 数/模转换集成电路BU9253FS 话筒音频混响集成电路BX1303 音频功率放大集成电路BX1409 红外遥控信号接收集成电路BX7506 主轴电机电源操纵集成电路C1363CA 红外遥控电子选台集成电路C1490HA 红外遥控信号接收集成电路C187 分配、十进制计数集成电路C301 译码BCD-10段集成电路C68639Y 微处理集成电路C75P036 微处理集成电路CA0002 调幅模拟声解调集成电路CA2004 音频功率放大集成电路36CA2006 音频功率放大集成电路CA270AW 视频检波放大集成电路CA3075 调频中频放大集成电路CA3089 调频中频放大集成电路CA3120E 视频信号处理集成电路CA3140 运算放大集成电路CA810 音频功率放大集成电路CA920 行扫描信号处理集成电路CAS126 天线开关集成电路CAT24C16 电可改写编程只读存储集成电路CAT35C104HP 存储集成电路CC4000 或者非门双3输入集成电路CC4008 计数4位二进制集成电路CC40107 与非双2输入缓冲、驱动集成电路CC40174 六D触发集成电路CC40194 移位寄存集成电路CC4025 或者非门3输入集成电路CC4026 译码、驱动、十进制计数集成电路CC4027 上升沿J-K触发集成电路。

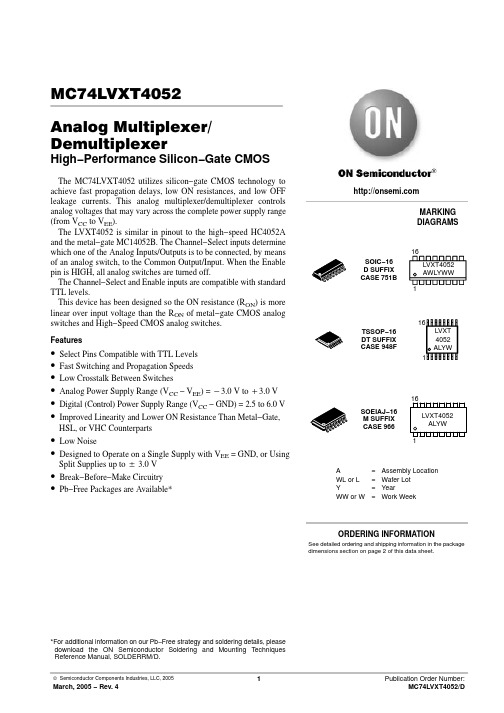

LVXT4052资料

MC74LVXT4052Analog Multiplexer/DemultiplexerHigh−Performance Silicon−Gate CMOSThe MC74LVXT4052 utilizes silicon−gate CMOS technology to achieve fast propagation delays, low ON resistances, and low OFF leakage currents. This analog multiplexer/demultiplexer controls analog voltages that may vary across the complete power supply range (from V CC to V EE ).The LVXT4052 is similar in pinout to the high−speed HC4052A and the metal−gate MC14052B. The Channel−Select inputs determine which one of the Analog Inputs/Outputs is to be connected, by means of an analog switch, to the Common Output/Input. When the Enable pin is HIGH, all analog switches are turned off.The Channel−Select and Enable inputs are compatible with standard TTL levels.This device has been designed so the ON resistance (R ON ) is more linear over input voltage than the R ON of metal−gate CMOS analog switches and High−Speed CMOS analog switches.Features•Select Pins Compatible with TTL Levels •Fast Switching and Propagation Speeds •Low Crosstalk Between Switches•Analog Power Supply Range (V CC − V EE ) = *3.0 V to )3.0 V •Digital (Control) Power Supply Range (V CC − GND) = 2.5 to 6.0 V •Improved Linearity and Lower ON Resistance Than Metal−Gate,HSL, or VHC Counterparts •Low Noise•Designed to Operate on a Single Supply with V EE = GND, or Using Split Supplies up to $3.0 V •Break−Before−Make Circuitry •Pb−Free Packages are Available**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting TechniquesReference Manual, SOLDERRM/D.MARKING DIAGRAMSA=Assembly Location WL or L =Wafer Lot Y=YearWW or W=Work WeekTSSOP−16DT SUFFIX CASE 948FSOEIAJ−16M SUFFIX CASE 966SOIC−16D SUFFIX CASE 751BSee detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATIONLVXT4052AWLYWWLVXT 4052ALYWLVXT4052ALYW116116116151614131211102134567V CC 98X2X1X X0X3A B Y0Y2Y Y3Y1Enable V EEGNDFigure 1. Pin Connection and Marking Diagram(Top View)Figure 2. Logic DiagramDouble−Pole, 4−Position Plus Common OffFUNCTION TABLEL L H H XL H L H XControl InputsON Channels Enable SelectB A X0X1X2X3L L L L H X = Don’t CareY0Y1Y2Y3NONEXANALOGINPUTS/OUTPUTSCHANNEL-SELECTINPUTSCC EE COMMONOUTPUTS/INPUTSYNOTE: This device allows independent control of each switch.Channel−Select Input A controls the X−Switch, Input B controls the Y−Switch.ORDERING INFORMATIONSpecifications Brochure, BRD8011/D.*This package is inherently Pb−Free.values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied,damage may occur and reliability may be affected.1.Tested to EIA/JESD22−A114−A.2.Tested to EIA/JESD22−A115−A.3.Tested to JESD22−C101−A.4.Tested to EIA/JESD78.RECOMMENDED OPERATING CONDITIONSDEVICE JUNCTION TEMPERATURE VERSUSTIME TO 0.1% BOND FAILURES11101001000Figure 3. Failure Rate vs. Time Junction TemperatureN O R M A L I Z E D F A I L U R E R A T ETIME, YEARSDC CHARACTERISTICS−Digital Section (Voltages Referenced to GND)DC ELECTRICAL CHARACTERISTICS−Analog SectionAC CHARACTERISTICS(Input t = t = 3 ns)AC CHARACTERISTICS(C L = 50 pF, Input t r = t f = 3 ns)ed to determine the no−load dynamic power consumption: P D = C PD V CC f + I CC V CC. ADDITIONAL APPLICATION CHARACTERISTICS(GND = 0 V)Figure 4. On Resistance, Test Set−UpFigure 5. Maximum Off Channel Leakage Current,Any One Channel, Test Set−Up Figure 6. Maximum On Channel Leakage Current,Channel to Channel, Test Set−UpFigure 7. Maximum On Channel Bandwidth, Test Set−UpV V V N/CFigure 8. Maximum Off Channel Feedthrough Isolation, Test Set−UpFigure 9. Maximum Common−Channel Feedthrough Isolation, Test Set−UpConfig = Network Format = T/R (dB)CAL = Trans CalDisplay = Rectan X *A )B Scale Ref = Auto Scale View = Off, Off, Off Trig = Cont ModeSource Amplitude = )13 dB Reference Attenuation = 20 dB Test Attenuation = 0 dBV ISO (dB) = 20 log (V T1/V R1)Format = T/R (dB)CAL = Trans CalDisplay = Rectan X *A )B Scale Ref = Auto Scale View = Off, Off, Off Trig = Cont ModeSource Amplitude = )13 dB Reference Attenuation = 20 dB Test Attenuation = 0 dBV ISOC (dB) = 20 log (V T1/V R1)Figure 10. Charge Injection, Test Set−UpV OUTV INOUTFigure 11. Maximum On Channel Feedthrough On Loss, Test Set−UpFormat = T/R (dB)CAL = Trans CalDisplay = Rectan X *A )B Scale Ref = Auto Scale View = Off, Off, Off Trig = Cont ModeSource Amplitude = )13 dB Reference Attenuation = 20 dB Test Attenuation = 20 dBV ONL (dB) = 20 log (V T1/V R1)Figure 12. Break−Before−Make, Test Set−Up Figure 13. Break−Before−Make TimeCC*TESTPOINTL *TESTPOINT W PZH PZL Figure 16. Propagation Delays, Enable toAnalog Out Figure 17. Propagation Delay, Test Set−UpEnable to Analog OutFigure 18. Power Dissipation Capacitance, Test Set−UpFigure 19. Total Harmonic Distortion, Test Set−UpAPPLICATIONS INFORMATIONThe Channel Select and Enable control pins should be at V CC or GND logic levels. V CC being recognized as a logic high and GND being recognized as a logic low. In this example:V CC = )5 V = logic high GND = 0 V = logic lowThe maximum analog voltage swing is determined by the supply voltages V CC and V EE . The positive peak analog voltage should not exceed V CC . Similarly, the negative peak analog voltage should not go below V EE . In this example,the difference between V CC and V EE is five volts. Therefore,using the configuration of Figure 21, a maximum analog signal of five volts peak−to−peak can be controlled. Unused analog inputs/outputs may be left floating (i.e., not connected). However, tying unused analog inputs andoutputs to V CC or GND through a low value resistor helps minimize crosstalk and feedthrough noise that may be picked up by an unused switch.Although used here, balanced supplies are not a requirement. The only constraints on the power supplies are that:V EE − GND = 0 to *6 volts V CC − GND = 2.5 to 6 volts V CC − V EE = 2.5 to 6 voltsand V EE v GNDWhen voltage transients above V CC and/or below V EE are anticipated on the analog channels, external Germanium or Schottky diodes (D x ) are recommended as shown in Figure 22. These diodes should be able to absorb the maximum anticipated current surges during clipping.Figure 20. Application Example +3.0 V −3.0 V+3.0 V −3.0 VFigure 21. Application Example+5 V GND+5 V GNDFigure 22. External Germanium or Schottky Clipping DiodesFigure 23. Function Diagram, LVXT4052X0X1X2X3Y0Y1Y2Y3YABENABLEXPACKAGE DIMENSIONSNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST DIM MIN MAX MIN MAX INCHESMILLIMETERS A 9.8010.000.3860.393B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2290.244R0.250.500.0100.019____SOIC−16D SUFFIX CASE 751B−05ISSUE JTSSOP−16DT SUFFIX CASE 948F−01ISSUE ADIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.180.280.0070.011J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W−.____16X REF KSOEIAJ−16M SUFFIX CASE 966−01ISSUE OON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further noticeto any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

cd4052中文资料_数据手册_参数

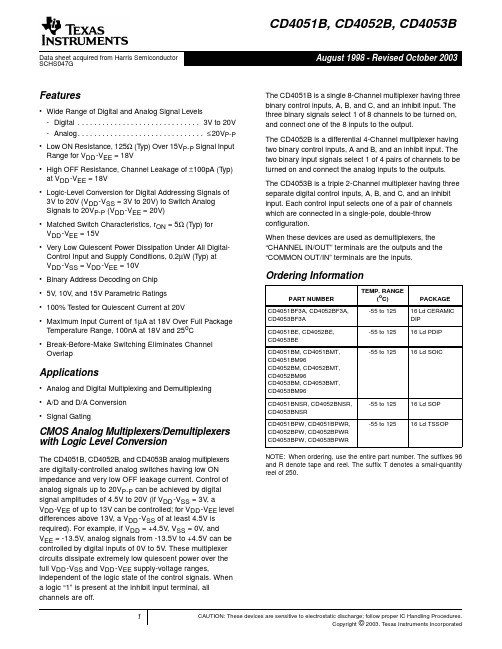

NOTE: When ordering, use the entire part number. The suffixes 96 and R denote tape and reel. The suffix T denotes a small-quantity reel of 250.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

-55 to 125 16 Ld SOIC

CD4051BNSR, CD4052BNSR, CD4053BNSR

-55 to 125 16 Ld SOP

CD4051BPW, CD4051BPWR, CD4052BPW, CD4052BPWR CD4053BPW, CD4053BPWR

-55 to 125 16 Ld TSSOP

- Digital . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3V to 20V

- Analog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤20VP-P

[ /Title • Low ON Resistance, 125Ω (Typ) Over 15VP-P Signal Input (CD405 Range for VDD-VEE = 18V

1B,

• High OFF Resistance, Channel Leakage of ±100pA (Typ)

LOGIC LEVEL CONVERSION

利特尔比特ltc4059 ltc4059a-900ma-线性锂离子电池充电器用热控制在2-2 dfn