AD5934YRSZ-REEL7中文资料

W947D6HBHX5E;W947D2HBJX5E;中文规格书,Datasheet资料

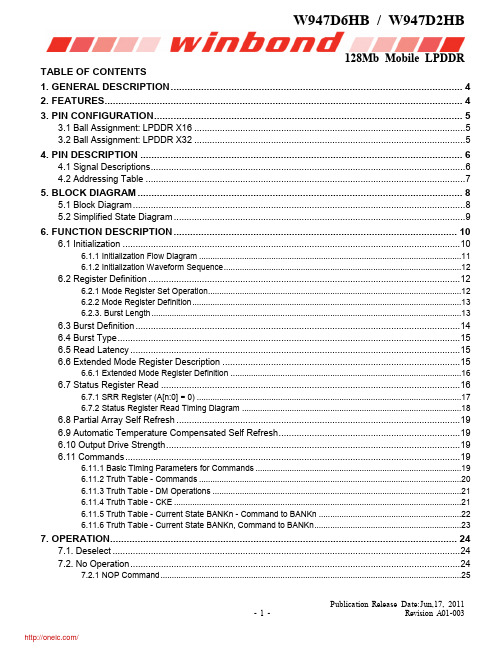

TABLE OF CONTENTS1. GENERAL DESCRIPTION (4)2. FEATURES (4)3. PIN CONFIGURATION (5)3.1 Ball Assignment: LPDDR X16 (5)3.2 Ball Assignment: LPDDR X32 (5)4. PIN DESCRIPTION (6)4.1 Signal Descriptions (6)4.2 Addressing Table (7)5. BLOCK DIAGRAM (8)5.1 Block Diagram (8)5.2 Simplified State Diagram (9)6. FUNCTION DESCRIPTION (10)6.1 Initialization (10)6.1.1 Initialization Flow Diagram (11)6.1.2 Initialization Waveform Sequence (12)6.2 Register Definition (12)6.2.1 Mode Register Set Operation (12)6.2.2 Mode Register Definition (13)6.2.3. Burst Length (13)6.3 Burst Definition (14)6.4 Burst Type (15)6.5 Read Latency (15)6.6 Extended Mode Register Description (15)6.6.1 Extended Mode Register Definition (16)6.7 Status Register Read (16)6.7.1 SRR Register (A[n:0] = 0) (17)6.7.2 Status Register Read Timing Diagram (18)6.8 Partial Array Self Refresh (19)6.9 Automatic Temperature Compensated Self Refresh (19)6.10 Output Drive Strength (19)6.11 Commands (19)6.11.1 Basic Timing Parameters for Commands (19)6.11.2 Truth Table - Commands (20)6.11.3 Truth Table - DM Operations (21)6.11.4 Truth Table - CKE (21)6.11.5 Truth Table - Current State BANKn - Command to BANKn (22)6.11.6 Truth Table - Current State BANKn, Command to BANKn (23)7. OPERATION (24)7.1. Deselect (24)7.2. No Operation (24)7.2.1 NOP Command (25)7.3 Mode Register Set (25)7.3.1 Mode Register Set Command (25)7.3.2 Mode Register Set Command Timing (26)7.4. Active (26)7.4.1 Active Command (26)7.4.2 Bank Activation Command Cycle (27)7.5. Read (27)7.5.1 Read Command (28)7.5.2 Basic Read Timing Parameters (28)7.5.3 Read Burst Showing CAS Latency (29)7.5.4 Read to Read (29)7.5.5 Consecutive Read Bursts (30)7.5.6 Non-Consecutive Read Bursts (30)7.5.7 Random Read Bursts (31)7.5.8 Read Burst Terminate (31)7.5.9 Read to Write (32)7.5.10 Read to Pre-charge (32)7.5.11 Burst Terminate of Read (33)7.6 Write (33)7.6.1 Write Command (34)7.6.2 Basic Write Timing Parameters (34)7.6.3 Write Burst (min. and max. tDQSS) (35)7.6.4 Write to Write (35)7.6.5 Concatenated Write Bursts (36)7.6.6 Non-Consecutive Write Bursts (36)7.6.7 Random Write Cycles (37)7.6.8 Write to Read (37)7.6.9 Non-Interrupting Write to Read (37)7.6.10 Interrupting Write to Read (38)7.6.11 Write to Precharge (38)7.6.12 Non-Interrupting Write to Precharge (38)7.6.13 Interrupting Write to Precharge (39)7.7 Precharge (39)7.7.1 Precharge Command (40)7.8 Auto Precharge (40)7.9 Refresh Requirements (40)7.10 Auto Refresh (40)7.10.1 Auto Refresh Command (41)7.11 Self Referesh (41)7.11.1 Self Refresh Command (42)7.11.2 Auto Refresh Cycles Back-to-Back (42)7.11.3 Self Refresh Entry and Exit (43)7.12 Power Down (43)7.12.1 Power-Down Entry and Exit (43)7.13 Deep Power Down (44)128Mb Mobile LPDDR7.13.1 Deep Power-Down Entry and Exit (44)7.14 Clock Stop (45)7.14.1 Clock Stop Mode Entry and Exit (45)8. ELECTRICAL CHARACTERISTIC (46)8.1 Absolute Maximum Ratings (46)8.2 Input/Output Capacitance (46)8.3 Electrical Characteristics and AC/DC Operating Conditions (47)8.3.1 Electrical Characteristics and AC/DC Operating Conditions (47)8.4 IDD Specification Parameters and Test Conditions (48)8.4.1 IDD Specification Parameters and Test Conditions (48)8.5 AC Timings (51)8.5.1 CAS Latency Definition (With CL=3) (54)8.5.2 Output Slew Rate Characteristics (55)8.5.3 AC Overshoot/Undershoot Specification (55)8.5.4 AC Overshoot and Undershoot Definition (55)9. PACKAGE DIMENSIONS (56)9.1: LPDDR X 16 (56)9.2: LPDDR X 32 (57)10. ORDERING INFORMATION (58)11. REVISION HISTORY (59)1. GENERAL DESCRIPTIONW947D6HB / W947D2HB is a high-speed Low Power double data rate synchronous dynamic random access memory (LPDDR SDRAM), An access to the LPDDR SDRAM is burst oriented. Consecutive memory location in one page can be accessed at a burst length of 2, 4, 8 and 16 when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the LPDDR SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle. The multiple bank nature enables interleaving among internal banks to hide the pre-charging time. By setting programmable Mode Registers, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. The device supports special low power functions such as Partial Array Self Refresh (PASR) and Automatic Temperature Compensated Self Refresh (ATCSR).2. FEATURESVDD = 1.7~1.95VVDDQ = 1.7~1.95V;Data width: x16 / x32Clock rate: 200MHz(-5),166MHz(-6),133MHz(-75)Partial Array Self-Refresh(PASR)Auto Temperature Compensated Self-Refresh(ATCSR) Power Down ModeDeep Power Down Mode (DPD Mode)Programmable output buffer driver strengthFour internal banks for concurrent operationData mask (DM) for write dataClock Stop capability during idle periodsAuto Pre-charge option for each burst accessDouble data rate for data outputDifferential clock inputs (CK and C K)Bidirectional, data strobe (DQS)C AS Latency: 2 and 3Burst Length: 2, 4, 8 and 16Burst Type: Sequential or Interleave 64 ms Refresh periodInterface: LVCMOS compatibleSupport package:Operating Temperature Range :3. PIN CONFIGURATION3.1 Ball Assignment: LPDDR X16(Top View) Pin Configuration 3.2 Ball Assignment: LPDDR X32(Top View) Pin Configuration4. PIN DESCRIPTION 4.1 Signal Descriptions4.2 Addressing Table5. BLOCK DIAGRAM 5.1 Block Diagram5.2 Simplified State Diagram6. FUNCTION DESCRIPTION6.1 InitializationLPDDR SDRAM must be powered up and initialized in a predefined manner. Operations procedures other than those specified may result in undefined operation. If there is any interruption to the device power, the initialization routine should be followed. The steps to be followed for device initialization are listed below.The Mode Register and Extended Mode Register do not have default values. If they are not programmed during the initialization sequence, it may lead to unspecified operation. The clock stop feature is not available until the device has been properly initialized from Step 1 through 11.●Step 1: Provide power, the device core power (VDD) and the device I/O power (VDDQ) must be brought upsimultaneously to prevent device latch-up. Although not required, it is recommended that VDD and VDDQ are from the same power source. Also Assert and hold Clock Enable (CKE) to a LVCMOS logic high level ●Step 2: Once the system has established consistent device power and CKE is driven high, it is safe to applystable clock.●Step 3: There must be at least 200μs of valid clocks before any command may be given to the DRAM. During thistime NOP or DESELECT commands must be issued on the command bus.●Step 4: Issue a PRECHARGE ALL command.●Step 5: Provide NOPs or DESELECT commands for at least tRP time.●Step 6: Issue an AUTO REFRESH command followed by NOPs or DESELECT command for at least tRFC time.Issue the second AUTO REFRESH command followed by NOPs or DESELECT command for at least tRFC time. Note as part of the initialization sequence there must be two Auto Refresh commands issued.The typical flow is to issue them at Step 6, but they may also be issued between steps 10 and 11.●Step 7: Using the MRS command, program the base mode register. Set the desired operation modes.●Step 8: Provide NOPs or DESELECT commands for at least tMRD time.●Step 9: Using the MRS command, program the extended mode register for the desired operating modes. Note theorder of the base and extended mode register programmed is not important.●Step 10: Provide NOP or DESELECT commands for at least tMRD time.●Step 11: The DRAM has been properly initialized and is ready for any valid command.分销商库存信息:WINBONDW947D6HBHX5E W947D2HBJX5E。

Proteus-ISIS-7库元件中英对照表

Proteus-ISIS-7库元件中英对照表AD芯片-----TECHWELL TW6805A仿真软件里的AD0809有问题,用0808代替定时/计数器的使用方法:CLK:计数和测频状态时,数字波的输入端。

(counter enable)CE:计数使能端;通过属性设置高还是低有效。

无效暂停计数RST:复位端(RESET),可设上升沿(Low-High)或者下降沿(High-Low)有效。

4种工作方式:通过属性Operating Mode 来选择。

Default : 缺省方式,计数器方式。

Time(secs):100S定时方式,由CE和RST控制暂停和重新开始。

Time(hms):10小时定时方式,同上。

Frequency: 测频方式,CE和RST有效时,显示CLK端数字波频率Count:计数方式。

+++++++++++++++++++++++++ +++++++++++++++++++++++++ +++++++++++常用元件列表:POT-HG 可调电位器7SEG-MPX8-CC-BLUE 8位数码管COMPIM 串口SW- 开关7SEG-BCD 含译码驱动的数显Speaker 扬声器2N5771和2N5772,15V对管300MARES , CAP,BUTTON 按钮开关KEYPAD-PHONE 3*4电话键盘KEYPAD-SMALLCALC 4*4计算器键盘KEYPAD-CALCULATOR 4*6计算器键盘PG160128A 128*128液晶++++++++元件库详细分类1.analog ics 模拟集成器件8个子类:amplifier 放大器comparators 比较器display drivers 显示驱动器filters 滤波器miscellaneous 混杂器件regulators 三端稳压器timers 555定时器voltage references 参考电压2,capacitors CAP电容,23个分类别 animated 可显示充放电电荷电容audio grade axial 音响专用电容 axial lead polypropene 径向轴引线聚丙烯电容axial lead polystyrene 径向轴引线聚苯乙烯电容ceramic disc 陶瓷圆片电容 decoupling disc 解耦圆片电容 high temp radial 高温径向电容 high temp axial electrolytic高温径向电解电容metallised polyester film 金属聚酯膜电容metallised polypropene 金属聚丙烯电容metallised polypropene film 金属聚丙烯膜电容miniture electrolytic 微型电解电容 multilayer metallised polyester film 多层金属聚酯膜电容mylar film 聚酯薄膜电容nickel barrier 镍栅电容non polarised 无极性电容polyester layer 聚酯层电容radial electrolytic 径向电解电容 resin dipped 树脂蚀刻电容tantalum bead 钽珠电容variable 可变电容vx a xial electrolytic VX 轴电解电容3,CMOS 4000 series 4000系列数字电路 adders 加法器buffers & drivers 缓冲和驱动器 comparators 比较器counters 计数器decoders 译码器encoders 编码器flip-flops & latches 触发器和锁存器frequency dividers & tiner 分频和定时器gates & inverters 门电路和反相器memory 存储器misc.logic 混杂逻辑电路mutiplexers 数据选择器multivibrators 多谐振荡器phase-locked loops(PLL) 锁相环registers 寄存器signal switcher 信号开关4,connectors 接头;8个分类:audio 音频接头D-type D型接头DIL 双排插座header blocks 插头miscellaneous 各种接头PCB transfer PCB 传输接头 SIL 单盘插座ribbon cable 蛇皮电缆terminal blocks 接线端子台5,data converters 数据转换器:4个分类: A/D converters 模数转换器D/A converters 数模转换器sample & hold 采样保持器temperature sensors 温度传感器6,debugging tools 调试工具数据:3个类别: breakpoint triggers 断点触发器logic probes 逻辑输出探针logic timuli 逻辑状态输入7,diodes 二极管;8个分类:bridge rectifiers 整流桥generic 普通二极管rectifiers 整流二极管schottky 肖特基二极管switching 开关二极管tunnel 隧道二极管varicap 稳压二极管8,inductors 电感:3个类别:generic 普通电感SMT inductors 表面安装技术电感transformers 变压器9,laplace primitives 拉普拉斯模型:7个类别:1st order 一阶模型2nd order 二阶模型controllers 控制器non-linear 非线性模型operators 算子poles/zeros 极点/零点symbols 符号10,memory ICs 存储器芯片:7个分类: dynamic RAM 动态数据存储器EEPROM 电可擦出程序存储器EPROM 可擦出程序存储器I2C memories I2C总线存储器memory cards 存储卡SPI Memories SPI总线存储器static RAM 静态数据存储器11,microprocessor ICs 微处理器:13个分类:12,modelling primitivvves 建模源:9个分类:13,operational amplifiers 运算放大器:7个分类:dual 双运放ideal 理想运放macromodel 大量使用的运放octal 8运放quad 4运放single 单运放triple 三运放14,optoelectronics 光电器件:11个分类: 7-segment displays 7段显示alphanumeric LCDs 液晶数码显示bargraph displays 条形显示dot matrix displays 点阵显示graphical LCDs 液晶图形显示 lamps 灯LCD controllers 液晶控制器LCD controllers 液晶面板显示 LEDs 发光二极管optocouplers 光电耦合serial LCDs 串行液晶显示15,resistors 电阻:11个分类:0.6w metal film 0.6w金属膜电阻10 watt wirewound 10w绕线电阻2w metal film 2w 金属膜电阻3 watt wirewound 3w 绕线电阻7 watt wirewound 7w 绕线电阻generix 普通电阻high voltage 高压电阻NTC 负温度系数热敏电阻resistor packs 排阻variable 滑动变阻器varisitors可变电阻参考试验中采用的可变电阻是:POT-HG16,simulator primitives 仿真源:3个类别: flip-flops 触发器gates 门电路sources 电源17,switches and relays 开关和继电器:4个类别:key pads 键盘relays 普通继电器relays(specific) 专用继电器switches 开关18,switching devices 开关器件:4个分类:DIACs 两端交流开关generic 普通开关元件SCRs 可控硅TRIACs 三端双向可控硅19,真空管:20,传感器:2个分类:pressure 压力传感器temperature 温度传感器21,晶体管:8个分类:bipolar 双极型晶体管generic 普通晶体管(错误)IGBT 绝缘栅双极晶体管JFET 结型场效应管MOSFET 金属氧化物场效应管RF power LDMOS 射频功率LDMOS管RF power VDMOS 射频功率VDMOS管unijunction 单结晶体管Electromechanical 电机MOTOR AC 交流电机MOTOR SERVO 伺服电机双相步进电机motor-bistepper(Bipolar Stepper Motor),四相步进电机motor-stepper(unipolar stepper motor)驱动电路,用ULN2003可以,proteus中推荐的L298和L6201(电子元件-步进电机中有L298资料)+++++++++++++++++++++++++ +++++++++++++++++++++++++ +++++++++++++++++++步进电机,可以用MTD2003,UN2916等专用芯片Proteus中图形液晶模块驱动芯片一览表LM3228 LM3229 LM3267 LM32 83LM3287 LM4228 LM4265 LM42 67LM4283 LM4287 PG12864F PG 24064FPG128128A PG160128AAGM1232G EW12A03GLY HDM32 GS12-B HDM32GS12Y-BHDG12864F-1 HDS12864F-3 HDG 12864L-4 HDG12864L-6NOKIA7110 TG126410GFSB TG13 650FEYAMPIRE128x64 LGM12641BS1RPROTEUS原理图元器件库详细说明Device.lib 单双向可控硅、包括电阻、电容、二极管、三极管和PCB的连接器符号、ACTIVE.LIB 包括虚拟仪器和有源器件、拨动开关、键盘、可调电位器和开关、DIODE.LIB 包括二极管和整流桥、稳压管、变容二极管、大功率二极管、高速二极管、可控硅、DISPLAY.LIB 包括LCD、LED、LED阵列BIPOLAR.LIB 包括三极管FET.LIB 包括场效应管ASIMMDLS.LIB 包括模拟元器件AS 稳压二极管、全桥、74系列、及其他。

半导体传感器ADG1408YRUZ中文规格书

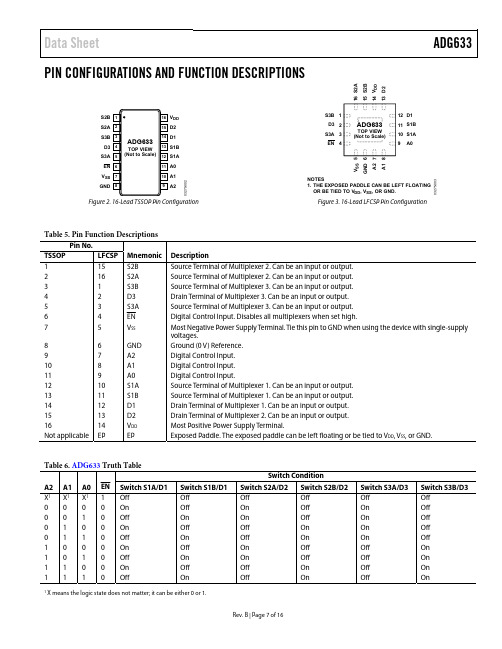

Data SheetADG633Rev. B | Page 7 of 16 PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONSS2A S3B D3V SS EN S3A S2B GND D2D1S1B A1A2A0S1A V DD 03275-002Figure 2. 16-Lead TSSOP Pin Configuration NOTES 1.THE EXPOSED PADDLE CAN BE LEFT FLOATING OR BE TIED TO V DD , V SS , OR GND.S3B D3S3A EN S1B D1S1A A0V S S G N D A 2A 1S 2B S 2A V D DD 203275-00312111013492657816151413ADG633TOP VIEW (Not to Scale)Figure 3. 16-Lead LFCSP Pin Configuration1 X means the logic state does not matter; it can be either 0 or 1.ADG633Data SheetRev. B | Page 14 of 16OUTLINE DIMENSIONSCOPLANARITY 0.10COMPLIANT TO JEDEC STANDARDS MO-153-AB Figure 31. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters4.104.00 SQ 3.900.350.300.25 2.252.10 SQ1.9510.65BSC BOTTOM VIEW TOP VIEW 16589121340.700.600.50SEATING PLANE0.05 MAX 0.02 NOM 0.203 REF 0.25 MINCOPLANARITY 0.08PIN 1INDICATOR 0.800.750.70COMPLIANT TO JEDEC STANDARDS MO-220-WGGC.FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SECTION OF THIS DATA SHEET.04-15-2016-A P K G -004025/5112PIN 1INDIC ATOR AREA OPTIONS (SEE DETAIL A)DETAIL A (JEDEC 95)EXPOSED PAD Figure 32. 16-Lead Frame Chip Scale Package [LFCSP] 4 mm × 4 mm Body and 0.75 mm Package Height (CP-16-23) Dimensions shown in millimetersORDERING GUIDEModel 1Temperature Range Package Description Package Option ADG633YRU−40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG633YRU-REEL7−40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG633YRUZ−40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG633YRUZ-REEL7−40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG633YCPZ−40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP] CP-16-23 ADG633YCPZ-REEL7−40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP] CP-16-23 1 Z = RoHS Compliant Part.。

ADZS-BF609-EZLITE;ADZS-BF609-EZBRD;中文规格书,Datasheet资料

ADSP-BF609 EZ-KIT Lite®Evaluation System ManualRevision 1.0, March 2012Part Number82-000269-01 Analog Devices, Inc.One T echnology WayaNorwood, Mass. 02062-9106Copyright Information© 2012 Analog Devices, Inc., ALL RIGHTS RESERVED. This docu-ment may not be reproduced in any form without prior, express writtenconsent from Analog Devices, Inc.Printed in the USA.DisclaimerAnalog Devices, Inc. reserves the right to change this product withoutprior notice. Information furnished by Analog Devices is believed to beaccurate and reliable. However, no responsibility is assumed by AnalogDevices for its use; nor for any infringement of patents or other rights ofthird parties which may result from its use. No license is granted by impli-cation or otherwise under the patent rights of Analog Devices, Inc. Trademark and Service Mark NoticeThe Analog Devices logo, Blackfin, CrossCore, EZ-Board, EZ-Extender, and EZ-KIT Lite are registered trademarks of Analog Devices, Inc.All other brand and product names are trademarks or service marks oftheir respective owners.Regulatory ComplianceThe ADSP-BF609 EZ-KIT Lite is designed to be used solely in a labora-tory environment. The board is not intended for use as a consumer end product or as a portion of a consumer end product. The board is an open system design which does not include a shielded enclosure and therefore may cause interference to other electrical devices in close proximity. This board should not be used in or near any medical equipment or RF devices.The ADSP-BF609 EZ-KIT Lite is currently being processed for certifica-tion that it complies with the essential requirements of the EuropeanEMC directive 2004/108/EC and therefore carries the “CE” mark.The EZ-KIT Lite evaluation system contains ESD (electrostatic discharge)sensitive devices. Electrostatic charges readily accumulate on the humanbody and equipment and can discharge without detection. Permanent dam-age may occur on devices subjected to high-energy discharges. Proper ESDprecautions are recommended to avoid performance degradation or loss offunctionality. Store unused EZ-KIT Lite boards in the protective shippingpackage.PREFACEProduct Overview (xii)Purpose of This Manual (xv)Intended Audience (xv)Manual Contents (xvi)What’s New in This Manual (xvi)Technical or Customer Support (xvii)Supported Processors (xvii)Product Information (xviii)Analog Devices Web Site (xviii)EngineerZone (xviii)Related Documents (xix)Notation Conventions (xx)USING ADSP-BF609 EZ-KIT LITEPackage Contents .......................................................................... 1-2 ADSP-BF609 EZ-Board ................................................................ 1-3 Default Configuration ................................................................... 1-3 Supported Operating Systems ....................................................... 1-5ADSP-BF609 EZ-KIT Lite Evaluation System Manual vSystem Requirements .................................................................... 1-5 EZ-KIT Lite Installation ............................................................... 1-6 EZ-KIT Lite Session Startup ......................................................... 1-7 Evaluation License Restrictions ................................................... 1-10 Memory Map ............................................................................. 1-10 DDR2 SDRAM .......................................................................... 1-12 SPI Interface .............................................................................. 1-13 SMC Interface ............................................................................ 1-13 Ethernet Interface ....................................................................... 1-13 USB OTG HS Interface .............................................................. 1-14 CAN Interface ............................................................................ 1-14 UART Interface .......................................................................... 1-15 SD Interface ............................................................................... 1-16 Rotary Encoder Interface ............................................................ 1-16 Temperature Sensor Interface ...................................................... 1-17 Link Ports Interface .................................................................... 1-17 General-Purpose I/O (GPIO) ...................................................... 1-18 JTAG Interface ........................................................................... 1-18 Power-On-Self Test ..................................................................... 1-20 Expansion Interface III ............................................................... 1-20 Power Architecture ..................................................................... 1-21 Power Measurements .................................................................. 1-21 Example Programs ...................................................................... 1-22 Reference Design Information ..................................................... 1-22vi ADSP-BF609 EZ-KIT Lite Evaluation System ManualADSP-BF609 EZ-KIT LITE HARDWARE REFERENCE System Architecture ...................................................................... 2-2 Software-Controlled Switches (SoftConfig) .................................... 2-3 Overview of SoftConfig ........................................................... 2-3SoftConfig on the ADSP-BF609 EZ-KIT LITE ...................... 2-7Programming SoftConfig Switches ........................................... 2-8 Push Buttons and Switches .......................................................... 2-17 JTAG Interface Switches (SW1, SW3–5) ................................ 2-18Boot Mode Select Switch (SW2) ............................................ 2-19IRQ/Flag Enable Switches (SW6–7) ....................................... 2-20Reset Switch (SW8) ............................................................... 2-20Rotary Encoder With Momentary Switch (SW9) .................... 2-20Wake Push Switch (SW10) .................................................... 2-21 Power Jumpers ............................................................................ 2-21 LEDs .......................................................................................... 2-22 GPIO LEDs (LED1–4) ......................................................... 2-23Thermal Limit LED (LED5) ................................................. 2-23Power LED (LED6) ............................................................... 2-23Reset LED (LED7) ................................................................ 2-24SPD LED (LED6) ................................................................. 2-24 Connectors ................................................................................. 2-24 DCE UART Connector (J2) .................................................. 2-25Link Port /JTAG Connectors (J3 and P8) ............................... 2-25JTAG Connector (P1) ........................................................... 2-25 ADSP-BF609 EZ-KIT Lite Evaluation System Manual viiJTAG Connector (ZP1) ......................................................... 2-26Expansion Interface III Connectors (P1A–C, P2A, P3A) ........ 2-26USB Connector (P7) ............................................................. 2-26Power Connector (P18) ......................................................... 2-26CAN Connector (J4) ............................................................ 2-27SD Connector (J5) ................................................................ 2-27Ethernet Connector (J1) ....................................................... 2-27Ethernet Connectors (P16-17) ............................................... 2-27 ADSP-BF609 EZ-KIT LITE BILL OF MATERIALSADSP-BF609 EZ-KIT LITE SCHEMATICTitle Page ..................................................................................... B-1 Processor DDR2 Interface ............................................................ B-2 Processor Signals ........................................................................... B-3 Processor Power and Ground ......................................................... B-4 Temp Sensor, Boot Switch, DSP CLK, USB Conn ......................... B-5 Memory ....................................................................................... B-6 UART0 ........................................................................................ B-7 CAN and Rotary Encoder ............................................................. B-8 Ethernet ....................................................................................... B-9JTAG, Link Port 0 and 1 ........................................................... B-10 Push Buttons, Reset, LEDs ......................................................... B-11 SoftConfig Switches, IO Extender ICs ......................................... B-12 Expansion Interface, Page 1 ........................................................ B-13viii ADSP-BF609 EZ-KIT Lite Evaluation System ManualExpansion Interface, Page 2 ........................................................ B-14 Expansion Interface, Page 3 ........................................................ B-15 Power ........................................................................................ B-16 INDEXADSP-BF609 EZ-KIT Lite Evaluation System Manual ixx ADSP-BF609 EZ-KIT Lite Evaluation System Manual分销商库存信息: ANALOG-DEVICESADZS-BF609-EZLITE ADZS-BF609-EZBRD。

W25Q64中文资料精编版

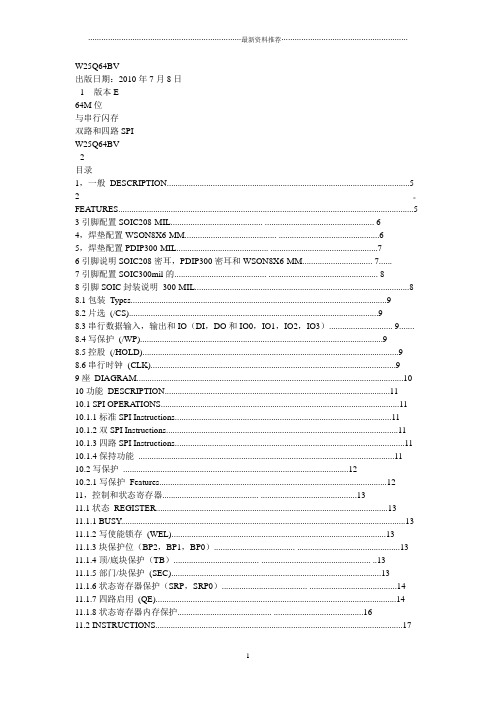

W25Q64BV出版日期:2010年7月8日- 1 - 版本E64M位与串行闪存双路和四路SPIW25Q64BV- 2 -目录1,一般DESCRIPTION (5)2。

FEATURES (5)3引脚配置SOIC208-MIL.......................................... .. (6)4,焊垫配置WSON8X6-MM.......................................... . (6)5,焊垫配置PDIP300-MIL.......................................... . (7)6引脚说明SOIC208密耳,PDIP300密耳和WSON8X6-MM................................ 7......7引脚配置SOIC300mil的.......................................... .. (8)8引脚SOIC封装说明300-MIL (8)8.1包装Types (9)8.2片选(/CS) (9)8.3串行数据输入,输出和IO(DI,DO和IO0,IO1,IO2,IO3)............................. 9.......8.4写保护(/WP) (9)8.5控股(/HOLD) (9)8.6串行时钟(CLK) (9)9座DIAGRAM (10)10功能DESCRIPTION (11)10.1 SPI OPERATIONS (11)10.1.1标准SPI Instructions (11)10.1.2双SPI Instructions (11)10.1.3四路SPI Instructions (11)10.1.4保持功能 (11)10.2写保护 (12)10.2.1写保护Features (12)11,控制和状态寄存器............................................ .. (13)11.1状态REGISTER (13)11.1.1 BUSY (13)11.1.2写使能锁存(WEL) (13)11.1.3块保护位(BP2,BP1,BP0)..................................... .. (13)11.1.4顶/底块保护(TB)....................................... .................................................. ..1311.1.5部门/块保护(SEC) (13)11.1.6状态寄存器保护(SRP,SRP0)....................................... . (14)11.1.7四路启用(QE) (14)11.1.8状态寄存器内存保护........................................... .. (16)11.2 INSTRUCTIONS (17)11.2.1制造商和设备标识........................................... .. (17)11.2.2指令集表1 (18)W25Q64BV11.2.3指令表2(阅读说明书)....................................... (19)出版日期:2010年7月8日- 3 - 修订版E11.2.4写使能(06h) (20)11.2.5写禁止(04h) (20)11.2.6读状态寄存器1(05H)和读状态寄存器2(35H).............................. (21)11.2.7写状态寄存器(01H)......................................... .................................................. .. (22)11.2.8读取数据(03h) (23)11.2.9快速阅读(0Bh) (24)11.2.10快速读双输出(3BH)........................................ .................................................. 0.25 11.2.11快速读四路输出(6BH)........................................ .. (26)11.2.12快速读双I / O (BBh) (27)11.2.13快速读取四I/ O (EBh) (29)11.2.14八进制字读取四I/ O(E3H)..................................... (31)11.2.15页编程(02h) (33)11.2.16四路输入页编程(32H)........................................ . (34)11.2.17扇区擦除(20H) (35)11.2.1832KB的块擦除(52H) (36)11.2.1964KB的块擦除(D8h) (37)20年2月11日芯片擦除(C7H/ 60h) (38)21年2月11日擦除挂起(75h) (39)22年2月11日擦除恢复(7Ah) (40)23年11月2日掉电(B9h) (41)24年2月11日高性能模式(A3H)......................................... (42)25年2月11日发布掉电或高性能模式/设备ID(ABH) (42)26年2月11日读制造商/设备ID(90H)....................................... . (44)27年2月11日阅读唯一的ID号(4BH)........................................ . (45)28年2月11日读JEDEC的ID (9Fh) (46)29年2月11日连续读取模式复位(FFH或FFFFH)...................................... .. (47)12,电气特性.............................................. (48)12.1绝对最大Ratings (48)12.2操作范围 (48)12.3上电时序和写抑制阈值......................................... (49)12.4直流电气Characteristics (50)12.5 AC测量条件.............................................. .. (51)12.6 AC电气Characteristics (52)12.7 AC电气特性(续)......................................... . (53)12.8串行输出Timing (54)12.9输入Timing (54)12.10持有Timing (54)13包装SPECIFICATION (55)W25Q64BV13.18引脚SOIC208密耳(包装代号SS)..................................... .. (55)- 4 -13.28引脚PDIP300密耳(封装代码DA)..................................... (56)13.38触点WSON8x6毫米(封装代码ZE)....................................... (57)13.416引脚SOIC300密耳(封装代码SF)..................................... . (58)14订货INFORMA TION (59)14.1有效的部件号和顶端标记.......................................... (60)15版本HISTORY (61)W25Q64BV出版日期:2010年7月8日- 5 - 修订版E1概述该W25Q64BV(64M位)串行Flash存储器提供了有限的系统存储解决方案空间,引脚和电源。

AD7874ARZ-REEL中文资料

One Technology Way, P.O. Box 9106, Norwood, M329-4700 Fax: 617/326-8703

元器件交易网

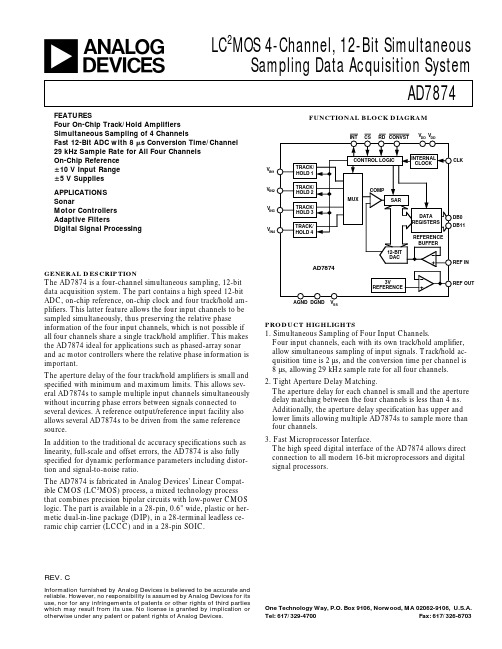

AD7874–SPECIFICATIONS external. All specifications T

Parameter SAMPLE-AND-HOLD Acquisition Time2 to 0.01% Droop Rate2, 3 –3 dB Small Signal Bandwidth3 Aperture Delay2 Aperture Jitter2, 3 Aperture Delay Matching2 SAMPLE-AND-HOLD AND ADC DYNAMIC PERFORMANCE Signal-to-Noise Ratio Total Harmonic Distortion Peak Harmonic or Spurious Noise Intermodulation Distortion 2nd Order Terms 3rd Order Terms Channel-to-Channel Isolation2 DC ACCURACY Resolution Relative Accuracy Differential Nonlinearity Positive Full-Scale Error4 Negative Full-Scale Error4 Full-Scale Error Match Bipolar Zero Error Bipolar Zero Error Match ANALOG INPUTS Input Voltage Range Input Current REFERENCE OUTPUTS REF OUT REF OUT Error @ +25°C TMIN to TMAX REF OUT Temperature Coefficient Reference Load Change REFERENCE INPUT Input Voltage Range Input Current Input Capacitance3 LOGIC INPUTS Input High Voltage, VINH Input Low Voltage, VINL Input Current, IIN Input Capacitance, CIN3 LOGIC OUTPUTS Output High Voltage, VOH Output Low Voltage, VOL DB0–DB11 Floating-State Leakage Current Floating-State Output Capacitance Output Coding POWER REQUIREMENTS VDD VSS IDD ISS Power Dissipation A Version B Version S Version Units 2 1 500 0 40 200 4 2 1 500 0 40 200 4 2 2 500 0 40 200 4 µs max mV/ms max kHz typ ns min ns max ps typ ns max

ADS947中文资料

The low-cost ADS-947 is a 14-bit, 10MHz sampling A/D converter. This device accurately samples full-scale input signals up to Nyquist frequencies with no missing codes. Excellent differential nonlinearity error (DNL), signal-to-noise ratio (SNR), and total harmonic distortion (THD) make the ADS-947 the ideal choice for both time-domain (CCD/FPA imaging, scanners, process control) and frequency-domain (radar, telecommunications, spectrum analysis) applications.

Requiring only +5V and –5.2V supplies, the ADS-947 typically dissipates just 2 Watts. The device is offered with a bipolar input range of ±2V. Models are available for use in either commercial (0 to +70°C) or military (–55 to +125°C) operating

—

–83

–76

—

–78

–72

AD8310ARM-REEL7资料

Fast, Voltage-Out DC–440 MHz,95 dB Logarithmic AmplifierAD8310 Rev.EInformation furnished by Analog Devices is believed to be accurate and reliable.However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: Fax: 781.461.3113© 2005 Analog Devices, Inc. All rights reserved.FEATURESMultistage demodulating logarithmic amplifierVoltage output, rise time <15 nsHigh current capacity: 25 mA into grounded R L95 dB dynamic range: −91 dBV to +4 dBVSingle supply of 2.7 V min at 8 mA typDC–440 MHz operation, ±0.4 dB linearitySlope of +24 mV/dB, intercept of −108 dBVHighly stable scaling over temperatureFully differential dc-coupled signal path100 ns power-up time, 1 mA sleep current APPLICATIONSConversion of signal level to decibel formTransmitter antenna power measurementReceiver signal strength indication (RSSI)Low cost radar and sonar signal processingNetwork and spectrum analyzersSignal-level determination down to 20 HzTrue-decibel ac mode for multimetersGENERAL DESCRIPTIONThe AD8310 is a complete, dc−440 MHz demodulating logarithmic amplifier (log amp) with a very fast voltage mode output, capable of driving up to 25 mA into a grounded load in under 15 ns. It uses the progressive compression (successive detection) technique to provide a dynamic range of up to 95 dB to ±3 dB law conformance or 90 dB to a ±1 dB error bound up to 100 MHz. It is extremely stable and easy to use, requiring no significant external components. A single-supply voltage of 2.7 V to 5.5 V at 8 mA is needed, corresponding to a power consumption of only 24 mW at 3 V. A fast-acting CMOS-compatible enable pin is provided.Each of the six cascaded amplifier/limiter cells has a small-signal gain of 14.3 dB, with a −3 dB bandwidth of 900 MHz.A total of nine detector cells are used to provide a dynamic range that extends from −91 dBV (where 0 dBV is defined as the amplitude of a 1 V rms sine wave), an amplitude of about ±40 μV, up to +4 dBV (or ±2.2 V). The demodulated outputis accurately scaled, with a log slope of 24 mV/dB and an intercept of −108 dBV. The scaling parameters are supply-and temperature-independent.FUNCTIONAL BLOCK DIAGRAMSUPPLY+INPUT–INPUTCOMMON184-1Figure 1.The fully differential input offers a moderately high impedance (1 kΩ in parallel with about 1 pF). A simple network can match the input to 50 Ω and provide a power sensitivity of −78 dBm to+17 dBm. The logarithmic linearity is typically within ±0.4 dBup to 100 MHz over the central portion of the range, but it is somewhat greater at 440 MHz. There is no minimum frequency limit; the AD8310 can be used down to low audio frequencies. Special filtering features are provided to support this wide range.The output voltage runs from a noise-limited lower boundary of 400 mV to an upper limit within 200 mV of the supply voltagefor light loads. The slope and intercept can be readily altered using external resistors. The output is tolerant of a wide varietyof load conditions and is stable with capacitive loads of 100 pF. The AD8310 provides a unique combination of low cost, small size, low power consumption, high accuracy and stability, high dynamic range, a frequency range encompassing audio to UHF, fast response time, and good load-driving capabilities, making this product useful in numerous applications that require the reduction of a signal to its decibel equivalent.The AD8310 is available in the industrial temperature range of−40°C to +85°C in an 8-lead MSOP package.AD8310Rev. E | Page 2 of 24TABLE OF CONTENTSSpecifications.....................................................................................3 Absolute Maximum Ratings............................................................4 ESD Caution..................................................................................4 Pin Configuration and Function Descriptions.............................5 Typical Performance Characteristics.............................................6 Theory of Operation........................................................................9 Progressive Compression............................................................9 Slope and Intercept Calibration................................................10 Offset Control.............................................................................10 Product Overview...........................................................................11 Enable Interface..........................................................................11 Input Interface............................................................................11 Offset Interface...........................................................................12 Output Interface.........................................................................12 Using the AD8310..........................................................................14 Basic Connections......................................................................14 Transfer Function in Terms of Slope and Intercept...............15 dBV vs. dBm...............................................................................15 Input Matching...........................................................................15 Narrow-Band Matching............................................................16 General Matching Procedure....................................................16 Slope and Intercept Adjustments.............................................17 Increasing the Slope to a Fixed Value......................................17 Output Filtering..........................................................................18 Lowering the High-Pass Corner Frequency of the OffsetCompensation Loop..................................................................18 Applications.....................................................................................19 Cable-Driving.............................................................................19 DC-Coupled Input.....................................................................19 Evaluation Board............................................................................20 Outline Dimensions.......................................................................22 Ordering Guide.. (22)REVISION HISTORY6/05—Rev. D to Rev. EChanges to Figure 6..........................................................................6 Change to Basic Connections Section.........................................14 Changes to Equation 10.................................................................17 Changes to Ordering Guide..........................................................22 10/04—Rev. C to Rev. DFormat Updated..................................................................Universal Typical Performance Characteristics Reordered..........................6 Changes to Figures 41 and 42.......................................................20 7/03—Rev. B to Rev. CReplaced TPC 12...............................................................................5 Change to DC-Coupled Input Section........................................14 Replaced Figure 20.........................................................................15 Updated Outline Dimensions.......................................................16 2/03—Rev. A to Rev. BChange to Evaluation Board Section...........................................15 Change to Table III.........................................................................16 Updated Outline Dimensions.......................................................16 1/00—Rev. 0 to Rev. A10/99—Revision 0: Initial VersionAD8310SPECIFICATIONST A = 25°C, V S = 5 V, unless otherwise noted.Table 1.Parameter Conditions Min Typ Max Unit INPUT STAGE Inputs INHI, INLOMaximum Input1Single-ended, p-p ±2.0 ±2.2 V4 dBV Equivalent Power in 50 Ω Termination resistor of 52.3 Ω 17 dBmDifferential drive, p-p 20 dBmNoise Floor Terminated 50 Ω source 1.28 nV/√Hz Equivalent Power in 50 Ω 440 MHz bandwidth −78 dBm Input Resistance From INHI to INLO 800 1000 1200 ΩInput Capacitance From INHI to INLO 1.4 pFDC Bias Voltage Either input 3.2 V LOGARITHMIC AMPLIFIER Output VOUT±3 dB Error Dynamic Range From noise floor to maximum input 95 dB Transfer Slope 10 MHz ≤ f ≤ 200 MHz 22 24 26 mV/dBOvertemperature, –40°C < T A < +85°C 20 26 mV/dB Intercept (Log Offset)210 MHz ≤ f ≤ 200 MHz −115 −108 −99 dBVEquivalent dBm (re 50 Ω) −102 −95 −86 dBmOvertemperature, −40°C ≤ T A ≤ +85°C −120 −96 dBVEquivalent dBm (re 50 Ω) −107 −83 dBmTemperature sensitivity −0.04 dB/°C Linearity Error (Ripple) Input from –88 dBV (–75 dBm) to +2 dBV (+15 dBm) ±0.4 dBOutput Voltage Input = –91 dBV (–78 dBm) 0.4 VInput = 9 dBV (22 dBm) 2.6 V Minimum Load Resistance, R L100 Ω Maximum Sink Current 0.5 mAOutput Resistance 0.05 ΩVideo Bandwidth 25 MHzRise Time (10% to 90%) Input Level = −43 dBV (−30 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 15 nsInput Level = −3 dBV (+10 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 20 nsFall Time (90% to 10%) Input Level = −43 dBV (−30 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 30 nsInput Level = −3 dBV (+10 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 40 nsOutput Settling Time to 1% Input Level = −13 dBV (0 dBm), R L ≥ 402 Ω, C L ≤ 68 pF 40 ns POWER INTERFACESSupply Voltage, VPOS 2.7 5.5 V Quiescent Current Zero-signal 6.5 8.0 9.5 mA Overtemperature −40°C < T A < +85°C 5.5 8.5 10 mA Disable Current 0.05 μALogic Level to Enable Power High condition, −40°C < T A < +85°C 2.3 VInput Current when High 3 V at ENBL 35 μALogic Level to Disable Power Low condition, −40°C < T A < +85°C 0.8 V1 The input level is specified in dBV, because logarithmic amplifiers respond strictly to voltage, not power. 0 dBV corresponds to a sinusoidal single-frequency input of1 V rms. A power level of 0 dBm (1 mW) in a 50 Ω termination corresponds to an input of 0.2236 V rms. Therefore, the relationship between dBV and dBm is a fixedoffset of 13 dBm in the special case of a 50 Ω termination.2 Guaranteed but not tested; limits are specified at six sigma levels.Rev. E | Page 3 of 24AD8310Rev. E | Page 4 of 24ABSOLUTE MAXIMUM RATINGSTable 2.Parameter Value Supply Voltage, V S 7.5 V Input Power (re 50 Ω), Single-Ended 18 dBm Differential Drive 22 dBm Internal Power Dissipation 200 mW θJA 200°C/W Maximum Junction Temperature 125°COperating Temperature Range −40°C to +85°C Storage Temperature Range−65°C to +150°C Lead Temperature (Soldering 60 sec)300°CStresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.AD8310Rev. E | Page 5 of 24PIN CONFIGURATION AND FUNCTION DESCRIPTIONS01084-002INLOCOMM OFLT VOUTFigure 2. Pin ConfigurationTable 3. Pin Function DescriptionsPin No. Mnemonic Function1 INLO One of Two Balanced Inputs. Biased roughly to VPOS/2.2 COMM Common Pin. Usually grounded.3 OFLT Offset Filter Access. Nominally at about 1.75 V.4 VOUT Low Impedance Output Voltage. Carries a 25 mA maximum load. 5 VPOS Positive Supply. 2.7 V to 5.5 V at 8 mA quiescent current.6 BFIN Buffer Input. Used to lower post-detection bandwidth.7 ENBL CMOS Compatible Chip Enable. Active when high. 8INHISecond of Two Balanced Inputs.AD8310Rev. E | Page 6 of 24TYPICAL PERFORMANCE CHARACTERISTICSINPUT LEVEL (dBV)3.00–12020–100(–87dBm)R S S I O U T P U T (V )–80–60–40–200(+13dBm)2.52.01.51.00.501084-011Figure 3. RSSI Output vs. Input Level, 100 MHz Sine Input at T A = −40°C,+25°C, and +85°C, Single-Ended InputINPUT LEVEL (dBV)3.0–120–100(–87dBm)R S S I O U T P U T (V )–80–60–40–20(+13dBm)202.52.01.51.00.5001084-012Figure 4. RSSI Output vs. Input Level at T A = 25°C for Frequencies of 10 MHz, 50 MHz, and 100 MHzINPUT LEVEL (dBV)3.00–12020–100(–87dBm)R S S I O U T P U T (V )–80–60–40–200(+13dBm)2.52.01.51.00.501084-013Figure 5. RSSI Output vs. Input Level at T A = 25°C for Frequencies of 200 MHz, 300 MHz, and 440 MHz01084-043P IN (dBm)R S S I O U T P U T (V )E R R O R (d B )Figure 6. Log Linearity of RSSI Output vs. Input Level, 100 MHz Sine Input at T A = −40°C, +25°C, and +85°CINPUT LEVEL (dBV)–12020–100(–87dBm)E R R O R (d B )–80–60–40–20(+13dBm)01084-015Figure 7. Log Linearity of RSSI Output vs. Input Level, at T A = 25°C, for Frequencies of 10 MHz, 50 MHz, and 100 MHzINPUT LEVEL (dBV)–12020–100(–87dBm)E R R O R (d B )–80–60–40–20(+13dBm)01084-016Figure 8. Log Linearity of RSSI Output vs. Input Level at T A = 25°Cfor Frequencies of 200 MHz, 300 MHz, and 440 MHzAD8310Rev. E | Page 7 of 2401084-009Figure 9. Small-Signal AC Response of RSSI Output with External BFINCapacitance of 100 pF, 3300 pF, and 0.01 μFFigure 10. Large-Signal RSSI Pulse Response with C L = 100 pFand RL = 100 Ω, 154 Ω, and 200 Ω01084-006Figure 11. RSSI Pulse Response with R L = 402 Ω and C L = 68 pF,for Inputs Stepped from 0 dBV to −33 dBV, −23 dBV, −13 dBV, and −3 dBV 01084-010Figure 12. Small-Signal RSSI Pulse Responsewith R L = 402 Ω and C L = 68 pF01084-007Figure 13. Large-Signal RSSI Pulse Response with R L = 100 Ωand C L = 33 pF, 68 pF, and 100 pF01084-008Figure 14. Small-Signal RSSI Pulse Response with R L = 50 Ω and Back Termination of 50 Ω (Total Load = 100 Ω)AD8310Rev. E | Page 8 of 24ENABLE VOLTAGE (V)1000.000010.52.50.7S U P P L Y C U R R E N T (m A )0.9 1.1 1.3 1.5 1.7 1.9 2.1 2.31010.10.010.0010.000101084-003Figure 15. Supply Current vs. Enable Voltage at T A = −40°C, +25°C, and +85°CFREQUENCY (MHz)3029201100010R S S I S L O P E(m V /d B )100242322212625282701084-017Figure 16. RSSI Slope vs. FrequencySLOPE (mV/dB)21.522.0C O U N T22.523.023.524.024.501084-019Figure 17. Transfer Slope Distribution, V S= 5 V, Frequency = 100 MHz, 25°C01084-004Figure 18. Power-On/Off Response Time with RF Input of −83 dBV to −3 dBVFREQUENCY (MHz)–99–101–1191100010R S S I I N T E R C E P T (d B V )100–111–113–115–117–107–109–103–10501084-018Figure 19. RSSI Intercept vs. FrequencyINTERCEPT (dBV)1240–115–113C O U N T210861416–111–109–107–105–103–101–99–971820222401084-020Figure 20. Intercept Distribution V S = 5 V, Frequency = 100 MHz, 25°CAD8310Rev. E | Page 9 of 24THEORY OF OPERATIONLogarithmic amplifiers perform a more complex operation than classical linear amplifiers, and their circuitry is significantlydifferent. A good grasp of what log amps do and how they do itcan help users avoid many pitfalls in their applications. For a complete discussion of the theory, see the AD8307 data sheet. The essential purpose of a log amp is not to amplify (though amplification is needed internally), but to compress a signal of wide dynamic range to its decibel equivalent. It is, therefore, a measurement device. An even better term might be logarithmic converter, because the function is to convert a signal from one domain of representation to another via a precise nonlinear transformation:⎟⎟⎠⎞⎜⎜⎝⎛=X IN Y OUT V V V V log (1) where:V OUT is the output voltage. V Y is the slope voltage. The logarithm is usually taken to base ten, in which case V Y is also the volts-per-decade. V IN is the input voltage. V X is the intercept voltage. Log amps implicitly require two references (here V X and V Y )that determine the scaling of the circuit. The accuracy of a log amp cannot be any better than the accuracy of its scaling reference s . In the AD8310, these are provided by a band gapreference.VFigure 21. General Form of the Logarithmic FunctionWhile Equation 1, plotted in Figure 21, is fundamentally correct, a different formula is appropriate for specifying the calibration attributes or demodulating log amps like theAD8310, operating in RF applications with a sine wave input.()O IN SLOPE OUT P P V V −= (2)where:V OUT is the demodulated and filtered baseband (video or RSSI) output.V SLOPE is the logarithmic slope, now expressed in V/dB (25 mV/dB for the AD8310).P IN is the input power, expressed in dB relative to some reference power level.P O is the logarithmic intercept, expressed in dB relative to the same reference level.A widely used reference in RF systems is dB above 1 mW in 50 Ω, a level of 0 dBm. Note that the quantity (P IN – P O ) is dB. The logarithmic function disappears from the formula, because the conversion has already been implicitly performed in stating the input in decibels. This is strictly a concession to popular convention. Log amps manifestly do not respond to power(tacitly, power absorbed at the input), but rather to input voltage. The input is specified in dBV (decibels with respect to 1 V rms) throughout this data sheet. This is more precise, although still incomplete, because the signal waveform is also involved. Many users specify RF signals in terms of power(usually in dBm/50 Ω), and this convention is used in this datasheet when specifying the performance of the AD8310.PROGRESSIVE COMPRESSION High speed, high dynamic-range log amps use a cascade ofnonlinear amplifier cells to generate the logarithmic functionas a series of contiguous segments, a type of piecewise linear technique. The AD8310 employs six cells in its main signal path, each having a small-signal gain of 14.3 dB (×5.2) and a −3 dB bandwidth of about 900 MHz. The overall gain is about 20,000 (86 dB), and the overall bandwidth of the chain is approximately 500 MHz, resulting in a gain-bandwidth product(GBW) of 10,000 GHz, about a million times that of a typical op amp. This very high GBW is essential to accurate operationunder small-signal conditions and at high frequencies. The AD8310 exhibits a logarithmic response down to inputs as small as 40 μV at 440 MHz.Progressive compression log amps either provide a baseband video response or accept an RF input and demodulate thissignal to develop an output that is essentially the envelope of the input represented on a logarithmic or decibel scale. TheAD8310 is the latter kind. Demodulation is performed in a total of nine detector cells. Six are associated with the amplifier stages, and three are passive detectors that receive a progres-sively attenuated fraction of the full input. The maximum signal frequency can be 440 MHz, but, because all the gain stages are dc-coupled, operation at very low frequencies is possible.AD8310Rev. E | Page 10 of 24SLOPE AND INTERCEPT CALIBRATIONAll monolithic log amps from Analog Devices use precision design techniques to control the logarithmic slope and intercept. The primary source of this calibration is a pair of accurate voltage references that provide supply- andtemperature-independent scaling. The slope is set to 24 mV/dB by the bias chosen for the detector cells and the subsequent gain of the postdetector output interface. With this slope, the full 95 dB dynamic range can be easily accommodated within the output swing capacity, when operating from a 2.7 V supply. Intercept positioning at −108 dBV (−95 dBm re 50 Ω) has likewise been chosen to provide an output centered in the available voltage range.Precise control of the slope and intercept results in a log amp with stable scaling parameters, making it a true measurement device as, for example, a calibrated received signal strength indicator (RSSI). In this application, the input waveform is invariably sinusoidal. The input level is correctly specified in dBV . It can alternatively be stated as an equivalent power, in dBm, but in this case, it is necessary to specify the impedance in which this power is presumed to be measured. In RF practice, it is common to assume a reference impedance of 50 Ω, in which 0 dBm (1 mW) corresponds to a sinusoidal amplitude of 316.2 mV (223.6 mV rms). However, the power metric is correct only when the input impedance is lowered to 50 Ω, either by a termination resistor added across INHI and INLO, or by the use of a narrow-band matching network.Note that log amps do not inherently respond to power, but to the voltage applied to their input. The AD8310 presents a nominal input impedance much higher than 50 Ω (typically 1 kΩ at low frequencies). A simple input matching network can considerably improve the power sensitivity of this type of log amp. This increases the voltage applied to the input and, therefore, alters the intercept. For a 50 Ω reactive match, the voltage gain is about 4.8, and the whole dynamic range moves down by 13.6 dB. The effective intercept is a function of wave-form. For example, a square-wave input reads 6 dB higher than a sine wave of the same amplitude, and a Gaussian noise input reads 0.5 dB higher than a sine wave of the same rms value. OFFSET CONTROLIn a monolithic log amp, direct coupling is used between the stages for several reasons. First, it avoids the need for coupling capacitors, which typically have a chip area at least as large as that of a basic gain cell, considerably increasing die size. Second, the capacitor values predetermine the lowest frequency at which the log amp can operate. For moderate values, this can be as high as 30 MHz, limiting the application range. Third, the parasitic back-plate capacitance lowers the bandwidth of the cell, further limiting the scope of applications.However, the very high dc gain of a direct-coupled amplifier raises a practical issue. An offset voltage in the early stages of the chain is indistinguishable from a real signal. If it were as high as 400 μV , it would be 18 dB larger than the smallest ac signal (50 μV), potentially reducing the dynamic range by this amount. This problem can be averted by using a global feedback path from the last stage to the first, which corrects this offset in a similar fashion to the dc negative feedback applied around an op amp. The high frequency components of the feedback signal must, of course, be removed to prevent a reduction of the HF gain in the forward path.An on-chip filter capacitor of 33 pF provides sufficient suppres-sion of HF feedback to allow operation above 1 MHz. The −3 dB point in the high-pass response is at 2 MHz, but theusable range extends well below this frequency. To further lower the frequency range, an external capacitor can be added at OFLT (Pin 3). For example, 300 pF lowers it by a factor of 10. Operation at low audio frequencies requires a capacitor of about 1 μF. Note that this filter has no effect for input levels well above the offset voltage, where the frequency range would extend down to dc (for a signal applied directly to the input pins). The dc offset can optionally be nulled by adjusting the voltage on the OFLT pin (see the Applications section).PRODUCT OVERVIEWThe AD8310 has six main amplifier/limiter stages. These six cells and their and associated g m styled full-wave detectors handle the lower two-thirds of the dynamic range. Three top-end detectors, placed at 14.3 dB taps on a passive attenuator, handle the upper third of the 95 dB range. The first amplifier stage provides a low noise spectral density (1.28 nV/√Hz). Biasing for these cells is provided by two references: onedetermines their gain, and the other is a band gap circuit that determines the logarithmic slope and stabilizes it against supply and temperature variations. The AD8310 can be enabled or disabled by a CMOS-compatible level at ENBL (Pin 7). The differential current-mode outputs of the nine detectors are summed and then converted to single-sided form, nominally scaled 2 μA/dB. The output voltage is developed by applying this current to a 3 kΩ load resistor followed by a high speed gain-of-four buffer amplifier, resulting in a logarithmic slope of 24 mV/dB (480 mV/decade) at VOUT (Pin 4). The unbuffered voltage can be accessed at BFIN (Pin 6), allowing certain functional modifications such as the addition of an external postdemodulation filter capacitor and the alteration or adjustment of slope and intercept.–INPUT01084-022Figure 22. Main Features of the AD8310The last gain stage also includes an offset-sensing cell. This generates a bipolarity output current, if the main signal path exhibits an imbalance due to accumulated dc offsets. This current is integrated by an on-chip capacitor that can beincreased in value by an off-chip component at OFLT (Pin 3). The resulting voltage is used to null the offset at the output of the first stage. Because it does not involve the signal inputconnections, whose ac-coupling capacitors otherwise introduce a second pole into the feedback path, the stability of the offset correction loop is assured.The AD8310 is built on an advanced, dielectrically isolated, complementary bipolar process. In the following interface diagrams shown in Figure 23 to Figure 26, resistors labeled as R are thin-film resistors that have a low temperature coefficient of resistance (TCR) and high linearity under large-signal conditions. Their absolute tolerance is typically within ±20%.Similarly, capacitors labeled as C have a typical tolerance of ±15% and essentially zero temperature or voltage sensitivity. Most interfaces have additional small junction capacitances associated with them, due to active devices or ESD protection, which might not be accurate or stable. Component numbering in these interface diagrams is local.ENABLE INTERFACEThe chip-enable interface is shown in Figure 23. The currents in the diode-connected transistors control the turn-on and turn-off states of the band gap reference and the bias generator. They are a maximum of 100 μA when ENBL is taken to 5 V under worst-case conditions. For voltages below 1 V , the AD8310 is disabled and consumes a sleep current of less than 1 μA. When tied to the supply or a voltage above 2 V , it is fully enabled. The internal bias circuitry is very fast (typically <100 ns for either off or on). In practice, however, the latency period before the log amp exhibits its full dynamic range is more likely to be limited by factors relating to the use of ac-coupling at the input or the settling of the offset-control loop (see the following sections).01084-023Figure 23. Enable InterfaceINPUT INTERFACEFigure 24 shows the essentials of the input interface. C P and C M are parasitic capacitances, and C D is the differential input capacitance, largely due to Q1 and Q2. In most applications, both input pins are ac-coupled. The S switches close whenenable is asserted. When disabled, bias current I E is shut off and the inputs float; therefore, the coupling capacitors remain charged. If the log amp is disabled for long periods, small leakage currents discharge these capacitors. Then, if they are poorly matched, charging currents at power-up can generate a transient input voltage that can block the lower reaches of the dynamic range until it becomes much less than the signal. A single-sided signal can be applied via a blocking capacitor to either Pin 1 or Pin 8, with the other pin ac-coupled to ground. Under these conditions, the largest input signal that can be handled is 0 dBV (a sine amplitude of 1.4 V) when using a 3 V supply; a 5 dBV input (2.5 V amplitude) can be handled with a 5 V supply. When using a fully balanced drive, this maximum input level is permissible for supply voltages as low as 2.7 V . Above 10 MHz, this is easily achieved using an LC matching network. Such a network, having an inductor at the input, usefully eliminates the input transient noted above.。

AD7324BRUZ;AD7324BRUZ-REEL;AD7324BRUZ-REEL7;中文规格书,Datasheet资料

12-bit plus sign

AD7323 500 00 kSPS 12-bit plus sign

AD7321 500 kSPS

12-bit plus sign

Number of Channels 8 8 8 4 2 2

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

3. 1 MSPS serial interface. SPI®-/QSPI™-/DSP-/MICROWIRE™compatible interface.

4. Low power, 31 mW maximum, at 1 MSPS throughput rate.

5. Channel sequencer.

Table 1. Similar Products Selection Table

Device Throughput

Number Rate

Number of bits

AD7329 1000 kSPS 12-bit plus sign

AD7328 1000 kSPS 12-bit plus sign

AD7327 500 kSPS

ESD Caution.................................................................................. 8 Pin Configuration and Function Description .............................. 9 Typical Performance Characteristics ........................................... 10 Terminology .................................................................................... 14 Theory of Operation ...................................................................... 16

ADG1219BRJZ-REEL7中文资料

charge injection over the entire signal range of the device. iCMOS construction also ensures ultralow power dissipation, making the parts ideally suited for portable and batterypowered instruments.

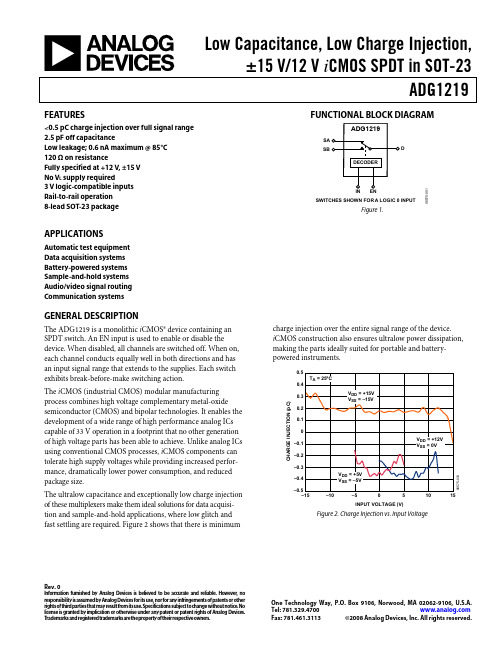

FUNCTIONAL BLOCK DIAGRAM

ADG1219

SA

SB

D

DECODER

06575-001

IN EN SWITCHES SHOWN FOR A LOGIC 0 INPUT

Figure 1.

APPLICATIONS

Automatic test equipment Data acquisition systems Battery-powered systems Sample-and-hold systems Audio/video signal routing Communication systems

Ordering Guide .......................................................................... 15

Rev. 0 | Page 2 of 16

元器件交易网

ADG1219

SPECIFICATIONS

元器件交易网

ADG1219

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3

AD5757中文手册

AD5757

产品特性

16位分辨率和单调性 用于热管理或外部PMOS模式的动态电源控制 电流输出范围:0 mA至20 mA、4 mA至20 mA或0 mA至 24 mA 总不可调整误差(TUE):±0.05%(最大值) 用户可编程失调与增益 片内诊断 片内基准电压源(±10 ppm/°C,最大值) 温度范围:−40°C至+105°C 各通道均有一个相应的CHART引脚,因此HART信号可以 耦合到AD5757的电流输出端。 该器件采用多功能三线式串行接口,能够以最高30 MHz 的时钟速率工作,并与标准SPI、QSPI™、MICROWIRE™、 DSP 和 微 控 制 器 接 口 标 准 兼 容 。 该 接 口 还 提 供 可 选 的 CRC-8分组错误校验功能,以及用于监控接口活动的看门 狗定时器。

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

AD5757 目录

产品特性 ......................................................................................... 1 应用 .................................................................................................. 1 概述 .......................................................................

AD8572AR-REEL7资料