第五章 状态机设计

状态机设计总结

状态机设计简介状态机的设计被广泛地用于时序控制逻辑中,它是许多数字系统的核心。

状态机可以应付众多应用场合的需求,覆盖宽范围的性能和复杂度;例如微处理器与VLSI外围接口的低级别控制,常规微处理器中的总线裁决和时序产生,定制的位片微处理器,数据加密和解密,传输协议等。

通常在设计周期中,控制逻辑的细节安排在最后处理,因为系统需求的改变和特征的增强会对其造成影响。

对于控制逻辑设计,可编程逻辑是一个很宽松的解决方案,因为它允许简单的修改而不必扰乱PCB板布局。

其灵活性提供了在不影响市场化时间的前提下,允许设计改动的机会。

大多数带寄存器的PAL器件应用都是需要使用状态机设计技术的时序控制逻辑。

随着技术的发展,新的高速、高性能的器件不断出现,它们简化了状态机设计的任务。

对于状态机设计,宽范围的不同功能与性能的解决方案是可行的。

在本次讨论中,我们将检验状态机执行的功能,它们在多种器件中的实现,以及它们的选择。

什么是状态机?状态机是一个以有序的方式,遍历预定的状态序列的数字设备。

状态是在电路的不同部分,测量到的一组数值。

一个简单状态机可以由以下几部分构成:基于PAL器件的组合逻辑,输出寄存器和状态寄存器。

这样一个序列发生器中的状态由状态寄存器和/或输出寄存器中所存储的值来决定。

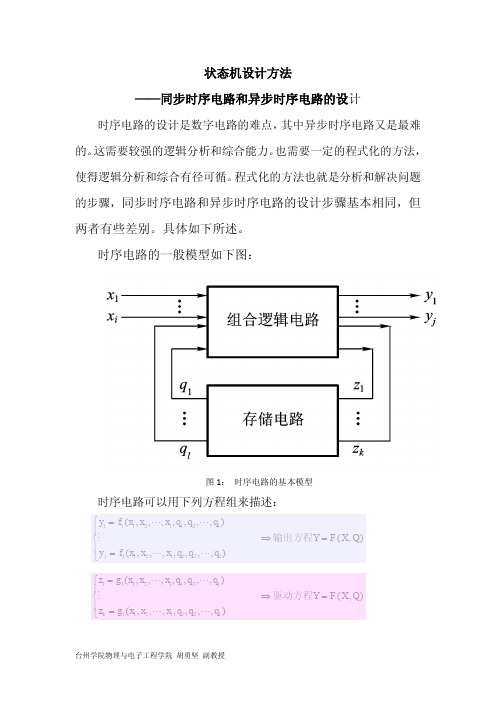

状态机的通用形式可以用图1所示的设备来描述。

除了这一设备的输入和输出,状态机还有两个必需的组成元件:组合逻辑和存储器(寄存器)。

这类似于前面所讨论的带寄存器的记数器设计,它们本质上就是简单的状态机。

存储器用来存储状态机的状态,组合逻辑可以看成两个截然不同的功能模块:下一状态解码器和输出解码器(图2)。

当输出解码器产生实际的输出时,下一状态解码器决定状态机的下一状态。

尽管它们执行截然不同的两个功能,但是它们通常被组合成如图1所示的组合逻辑阵列。

状态机的基本操作有两部分:<!--[if !supportLists]-->1、状态机遍历状态序列,下一状态解码器基于当前状态和输入条件来决定下一状态。

第五讲 状态机设计及其指导原则

第五讲状态机设计及其指导原则 11/ 38

带流水线的Mealy 状态机

下一个状态 = F(当前状态,输入信号); 输出信号 = G(当前状态,输入信号);

组合逻辑

时序逻辑 当前状态

组合逻辑 输出 译码器 G

时序逻辑

输出流 水线寄 存器 clk 输入

输入

状态 激励信号 状态 寄存器 译码器 F

第五讲状态机设计及其指导原则 3/ 38

原语描述

module noconditional (clk,nrst,state,event); input clk,nrst input state; output event; reg event;

reg reg [2:0] CS; //CurrentState [2:0] NS; //NextState

制作人:梁瑞宇 单位:河海大学

第五讲状态机设计及其指导原则 5/ 38

制作人:梁瑞宇 单位:河海大学

第五讲状态机设计及其指导原则 6/ 38

状态机的本质--对具有逻辑顺序或

时序规律事件的一种描述方法

状态机的两个应用思路: - 从状态变量入手

- 明确电路的输出的关系

制作人:梁瑞宇 单位:河海大学

制作人:梁瑞宇 单位:河海大学

第五讲状态机设计及其指导原则 17/ 38

case……endcase 语法格式: case (case_expression) case_item1:case_item_statement1; case_item2:case_item_statement2; case_item3:case_item_statement3; case_item4:case_item_statement4; default:case_item_statement5; endcase 使用default关键字来描述FSM所需状态的补集状态 下的操作,避免FSM进入死循环。 建议初学者使用完整的case 结构,而不使用casex 或casez。

电子设计自动化第五章 状态机

精品课件

第一节 一般状态机的设计

一、 1、数据类型定义语句

精品课件

精品课件

子类型SUBTYPE的语句格式如下: SUBTYPE 子类型名 IS 基本数据类型 RANGE 约

束范围; SUBTYPE digits IS INTEGER RANGE 0 to 9 ;

精品课件

2、枚举类型 枚举类型是用文字符号来表示一组实际

三、在主控组合进程中定义状态的转移

在进程中插入CASE WHEN 语句, 因为空闲语句是状态的起点和终点,因 此,作为WHEN 之后的第一项,再列出状 态转移到其他状态的条件,即可写出状 态转移的流程。

精品课件

第二节 Moore型有限状态机的设计

从状态机的信号输出方式分:Moore型和 Mealy型两类状态机。从输出时序上看,前者属于 同步输出状态机,后者属于异步输出状态机。 Mealy型状态机的输出是当前状态和所有输入信号的 函数,它的输出是在输入变化后立即发生的,不依 赖时钟的同步。 Moore型状态机的输出仅为当前状态的函数,这类状 态机在输入发生变化后还必须等待时钟的到来,时 钟使状态发生变化时才导致输出的变化所以比 Mealy型状态机要多等待一个时钟周期。

精品课件

(2)主控时序进程 完成当前状态向下一个的跃迁,

但不负责进入下一状态的具体状态取值, 只是在时钟沿到来时,当前状态进入下 一个状态。

在这一部分也可完成同步或异步清零 或置位方面的控制信号。

精品课件

(3)主控组合进程

根据外部输入的控制信号(包括来自 状态机的外部信号和来自状态机内部其 它非主控的组合或时序进程的信号)、 或(和)当前状态的状态值确定下一状 态的取向,以及确定对外输出或对内部 其它组合或时序进程输出控制信号的内 容。

状态机图(精品)

状态机图1.概述状态机图(State Machine Diagram)是用来显示状态机的图,包括简单状态、转换和嵌套的复合状态等,一个典型的状态机图如图1所示:图1. 状态机图2.基本表示符号状态机图的基本元素包括:状态、转移、事件、伪状态和复合状态。

2.1状态(State)状态是对象生命周期中的一个条件或形态。

状态由对象的属性值、与其他对象的关系以及正在执行的活动来确定。

在UML中,状态用圆角矩形和状态名表示,初始状态用实心圆表示,终止状态用牛眼表示,如图2所示:图2. 状态状态可以有一个或多个分栏,这些分栏是可选的,包括名称分栏、嵌套区域、内部转换分栏等,如图3所示:图3. 带分栏的状态状态也可用圆角矩形上带有状态名称标签的方框表示,如图4所示:图4. 带有名称标签符号的状态2.2转移(Transaction)转移表示状态之间可能的路径,可以表示外部转换(用箭头表示),也可以表示内部转换(嵌套在状态内部)。

如图5所示:图5. 转移2.3事件(Event)事件是对,在特定时间和空间上,所发生的有意义的事情。

在状态机中,事件触发转移,事件或者显示在转换之上,或显示在状态以内。

共有四种类型的事件:信号事件、调用事件、时间事件、改变事件。

信号用于对象间异步传递的信息包,它没有任何操作,只有自身携带的信息。

信号事件是通过信号来触发的事件,在UML中,信号如图6所示:图6. 信号调用事件是请求在类语境的实例上调用特定的操作,在UML中,调用事件如图7所示:图7. 调用事件时间事件用关键字after表示,说明事件被触发的临界时间。

改变事件用关键字when表示,说明将事件改变所满足的条件。

如图8所示:图8. 时间事件和改变事件2.4伪状态(Pseudo State)伪状态指在一个状态机中具有状态的形式,同时具有特殊行为的顶点。

它是一个瞬时状态,用于构造转换的细节。

当伪状态处于活动时,状态机还没有完成从运行到完成的步骤,也不会处理事件。

如何设计自动驾驶系统的状态机

如何设计自动驾驶系统的状态机状态机模块在(自动驾驶)系统中扮演着关键的角色,它负责管理和控制各个功能的状态转换和行为执行。

今天我们来聊聊如何设计自动驾驶系统的状态机。

0.闲谈作为自动驾驶系统(工程师),从参与项目开始,就必不可少的与状态管理模块打交道,因为状态机在系统运行的全功能周期内起管理作用。

状态机这个模块,从技术实现角度来说,并没有什么难度,在网上有很多关于FSM(Fini(te)-state machine)的介绍文章,有兴趣可以自行了解。

但如何设计得巧妙、周到、精致,却很考验设计者的底蕴与对系统的理解。

大部分的(AD)AS功能都需要状态机进行状态管理,笔者手中就有不下十几份状态机的设计文档,包括FCW/LDW/AEB/(AC)C/LKA/NOP/APA/AVP等等,设计大相径庭,但细细想来内核却大同小异。

其中NOP功能的状态跳转还是比较复杂的,涉及横向、纵向控制与功能降级等逻辑,需要长期的雕琢与迭代才能设计出符合项目要求的效果。

笔者最近也在负责APA功能的状态机设计,虽然比较简单,但还是想借此机会对状态机模块做一点总结,也是对以往工作的回顾。

1.模块概述状态机模块的主要作用是跟踪系统的当前状态,并根据特定的事件和条件进行状态转换。

它可以根据(传感器)数据、车辆状态和系统输入来判断当前功能的可用性和执行条件。

状态机模块还能够监控系统的运行情况,及时响应来自驾驶决策或用户的指令,并根据需要触发相应的功能执行。

状态机模块通过定义和维护一组状态,以及状态之间的转换条件和行为,确保系统在不同的场景和条件下正确地执行相应的功能。

例如,当(检测)到前方车辆与本车距离过近时,FCW功能会被触发,状态机模块会根据预设的逻辑条件和行为来切换到相应的预警状态,并触发声音或振动等警示措施。

状态机模块的设计需要考虑各个功能之间的优先级、依赖关系和冲突情况。

它需要具备灵活性和可扩展性,以应对不同的道路情况和交通场景。

机器人程序设计中的状态机设计

机器人程序设计中的状态机设计一、前言工业机器人系统通常分为机器人本体和控制器两大部分。

微控制器的主要作用是根据用户的指令对机器人本体进行操作和控制,为每一个不同的机器人设计不同功能的控制程序是一个设计者经常感到困扰的难题。

许多机器人都是有多个任务的,这些任务间是相关联的,且每个任务都有明确的细致要求,这就使得机器人的控制设计难度增大。

在此,有一种叫状态机理论的相关概念,它能用在机器人的控制程序设计上。

二、有限状态机理论有限状态机,又称有限状态自动机,简称状态机。

有限状态机理论构成有限状态机的具体内容是:有限状态机是由寄存器组和组合逻辑构成的硬件时序电路。

它是由有限个状态相互间的转换构成的,下一个状态不但取决于各个输入值,还取决于当前的所有状态。

在任意时刻,当前状态就只能存在一个。

只有在有事件输入的条件下,状态才会产生并发出一个输出。

对在给定时刻要进行的活动的描述的是动作。

它包括了进入动作、退出动作、输入动作和转移动作四个动作。

三、有限状态机的优、缺点有限状态机,又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。

它具有以下优缺点:优点:思路明确,内容简单易懂,状态间的关系明了,容易编程;只需要改动输出就可以改动机器人的动作要求;当发现程序不对时,更能快速的找到错误的点。

缺点:在每一个时刻,有且只有一个状态,没有并发性的表达方式,更不能描述异步并发系统;当设计需求的状态太多时,反而编程变得更耗时和困难。

四、基于状态转换方法的机器人的程序控制的设计实例状态机是具有基于状态的动态行为的机器。

它是一个动态系统,对时间和状态产生的时间做出反应。

一个状态机包含一组有限的状态和一组转换的集合。

其中状态描述运算中不同的阶段,而转换所描述的是如何使运算从一个状态变化到另一个状态。

依赖于此理论的有限性,才能发此理论用在机器人的编程设计上,设计时可以把机器人的每个动作按要求先合理分成多个状态,并给予特定的符号代表每个状态,在每个状态给予相应的输出要求,及机器人的动作和反映。

《状态机程序设计》课件

02

状态机的实现方式

状态机的编程语言实现

编程语言选择

根据应用场景和需求,选择适合的编 程语言来实现状态机。常见的编程语 言如C、C、Java等都可以用来实现 状态机。

编程语言实现方法

使用条件语句(如if-else语句)或 switch语句来描述状态转移逻辑。可 以使用枚举类型或常量来定义状态, 使用变量来存储当前状态。

状态机的图形化工具实现

图形化工具介绍

使用图形化工具可以方便地设计状态 机,减少编程的工作量。常见的图形 化工具如Stateflow、Simulink等。

图形化工具实现方法

在图形化工具中,可以通过拖拽状态 和转移来构建状态机。通常图形化工 具会提供丰富的状态机元素和功能, 如状态转换、事件触发等。

状态机的硬件实现

03

状态转换明确

状态转换应具有明确的触发条件和执行动作。在状态机中,从一个状态

转换到另一个状态时,应清晰地定义转换条件、输入和输出以及相应的

处理逻辑。

状态机的设计技巧

使用子状态

当一个状态的内部行为复杂时,可以考虑将其拆分为子状态。 子状态可以进一步细化和描述该状态的内部行为和逻辑。

使用分层状态机

当一个系统具有多个层级或多个子系统时,可以考虑使用分层状 态机。上层状态机可以控制下层状态机的行为,而下层状态机负

案例三:交通信号控制系统的状态机设计

总结词

复杂、多因素控制

详细描述

交通信号控制系统涉及多个信号灯的状态转 换,如红、黄、绿等。通过状态机的设计, 可以实现对交通信号的精确控制,确保交通 流畅、安全。同时,需要考虑多种因素,如 车流量、行人流量等,以实现最优的状态转 换策略。

05

状态机设计的常见问 题与解决方案

状态机设计.5

POINTS_D2: ="0000";

ELSE POINTS_D2: =POINTS_D2+'1'; END IF; ELSE

POINTS_D1: =POINTS_D1+'1';

END IF;

26

END IF; END IF;

AA2<=POINTS_A2;AA1<=POINTS_A1;

AA0<=“0000”; BB2<=POINTS_B2;BB1<=POINTS_B1;

17

ELSIF (A='0„ AND B='1„ AND C='0„ AND D='0')

THEN A1<=„0‟; B1<=„1‟; C1<=„0‟; D1<=„0‟; STATES<=W2; ELSIF (A='0„ AND B='0„ AND C='1„ AND D='0') THEN A1<=„0‟; B1<=„0‟; C1<=„1‟;

POINTS_C2: ="0000";

ELSE POINTS_C2: =POINTS_C2+'1'; END IF; ELSE

POINTS_C1: =POINTS_C1+'1';

END IF;

25

ELSIF CHOS="1000" THEN

-- D抢答

IF POINTS_D1="1001" THEN POINTS_D1: ="0000"; IF POINTS_D2="1001" THEN

状态机的设计

• 状态:也叫状态变量。在逻辑设计中,使用状态划分逻辑顺 序和时序规律。比如设计伪随机码发生器时,可以用移位寄 存器序列作为状态;在设计电机控制电路时,可以将电机的 不同转速作为状态;在设计通信系统时,可以将信令的状态 作为状态变量等。 • 输出:输出指在某一个状态时特定发生的事件。如设计电机 控制电路时,如果电机转速过高,则输出为转速过高报警, 也可以伴随减速指令或降温措施等。 • 输入:指状态机中进入每个状态的条件,有的状态机没有输 入条件,其中的状态转移较为简单,有的状态机有输入条件, 当某个输入条件存在时才能转移到相应的状态。

Out[7] …... …... Out[0]

为什么要设计有限状态机?

组合逻辑举例之二:一个八位三态数据通路控制器 `define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire LinkBusSwitch; wire [7:0] outbuf; inout [7:0] bus; assign bus = (LinkBusSwitch== `ON) ? outbuf : 8 ‘hzz always@(posedge clk) Begin … If(!linkbusswitch) Inbuf<=bus; …. End

• 状态转移图

状态转移图是状态机描述中最自然的方式,状 态转移图经常在设计规划阶段定义逻辑功能时使 用,也可以在分析已有源代码中的状态机时使用, 这种图形化的描述方式非常有助于理解设计意图。

• 状态转移列表 状态转移列表是用列表的方式描述状态机, 是数字逻辑电路常用的设计方法之一,经常被 用于状态化筒,对于可编程逻辑设计而言,由 于可用逻辑资源比较丰富,而且状态编码要考 虑设计的稳定性、安全性等因素,所以并不经 常使用状态转移列表优化状态. • HDL 语言描述状态机 如何使用HDL 语言描述状态机是本课程所要 讨论的重点,使用HDL 语言描述状态机应具有 一定的灵活性,但是决不是天马行空,而是有 章可循的.通过使用一些规范的描述方法,可以 使HDL 语言描述状态机更安全、更稳定、更高 效、更易于维护.

状态机

when read1 => oe <=„1‟; we<=„0‟; addr<=„00‟; if (ready = “0” ) then next_state<=read1; elsif (burst =„0‟) then next_state<=idle; else next_state<=read2; endif; when read2 => oe <=„1‟; we<=„0‟; addr<=„01‟; if (ready = “1” ) then next_state<=read3; else next_state<=read2; endif;

状态机异步复位

State_clocked: PROCESS(clk,reset) BEGIN IF reset=„1‟ THEN Present_state<=idle; ELSIF(clk‟ event AND clock=„1‟ )THEN Present_state<=Next_state; END IF; END PROCESS; 异步复位适用于上电复位和系统错误复位 比同步复位占用资源多。

when idle => oe <=„0‟; we<=„0‟; addr<=„00‟; if (bus_id = “11110011” ) then next_state<=decision; else next_state<=idle; endif; when decision => oe <=„0‟; we<=„0‟; addr<=„00‟; if (read_wirte = “0” ) then next_state<=read1; else next_state<=write; endif;

状态机设计

状态机设计FSM简介:FSM 分两大类:米里型和摩尔型,组成要素有输入(包括复位),状态(包括当前状态的操作),状态转移条件,状态的输出条件,图1为状态机结构图。

设计FSM 的方法和技巧多种多样,但是总结起来有两大类:第一种,将状态转移和状态的操作和判断等写到一个模块(process、block)中。

另一种是将状态转移单独写成一个模块,将状态的操作和判断等写到另一个模块中(在Verilog代码中,相当于使用两个“always” block)。

其中较好的方式是后者。

其原因如下:首先FSM 和其他设计一样,最好使用同步时序方式设计,好处不再赘述。

而状态机实现后,状态转移是用寄存器实现的,是同步时序部分。

状态的转移条件的判断是通过组合逻辑判断实现的,之所以第二种比第一种编码方式合理,就在于第二种编码将同步时序和组合逻辑分别放到不同的程序块(process,block)中实现。

这样做的好处不仅仅是便于阅读、理解、维护,更重要的是利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。

图1为状态机结构图显式的FSM 描述方法可以描述任意的FSM(参考Verilog 第四版P181 有限状态机的说明)。

两个always 模块。

其中一个是时序模块,一个为组合逻辑。

时序模块设计与书上完全一致,表示状态转移,可分为同步与异步复位。

同步:always @(posedge clk)if (!reset)…………异步:always @(posedge clk or negedge reset)if (!reset)…………组合逻辑用case 语句,sensitive list 包括当然状态(current state)和输入(a,b,c…)。

编者注:以下是编者从“State Machine Coding Styles for Synthesis”一文中摘取的程序代码,是一个简单状态机的示例,采用两个always块的方法:module bm1_s (err, n_o1, o2, o3, o4,i1, i2, i3, i4, clk, rst);output err, n_o1, o2, o3, o4;input i1, i2, i3, i4, clk, rst;reg err, n_o1, o2, o3, o4;parameter [2:0] //可以在此处添加综合约束属性来限定状态机的编码:binary,one-hot,gray,etc…IDLE = 3'd0,S1 = 3'd1,S2 = 3'd2,S3 = 3'd3,ERROR = 3'd4;reg [2:0] state, next;always @(posedge clk or posedge rst)//异步复位,时序逻辑if (rst) state <= IDLE;else state <= next;always @(state or i1 or i2 or i3 or i4) begin //组合逻辑,敏感列表包含当前状态以及所有的状态机输入next = 3'bx;//设置默认值,以便防止因为if或者case语句不完整综合生成锁存器err = 0; n_o1 = 1;o2 = 0; o3 = 0; o4 = 0;case (state)IDLE: beginnext = ERROR;//如果下面所有的if条件都不符合,则对next赋该默认值if (!i1) next = IDLE;if (i1 & i2) next = S1;if (i1 & !i2 & i3) next = S2;endS1: beginnext = ERROR;if (!i2) next = S1;if (i2 & i3) next = S2;if (i2 & !i3 & i4) next = S3;n_o1 = 0;o2 = 1;endS2: beginnext = ERROR;if (i3) next = S2;if (!i3 & i4) next = S3;o2 = 1;o3 = 1;endS3: beginnext = S3;if (!i1) next = IDLE;if (i1 & i2) next = ERROR;o4 = 1;endendmodule对于状态机的输出可以通过寄存器寄存一下,消除毛刺,这将另外需要一个always 块,也就是状态机三个always块的写法。

状态机设计方法

图 2 格雷码计数器状态转换图

台州学院物理与电子工程学院 胡勇坚 副教授

2. 根据状态转换图列出状态转换表:

3.根据状态转换表画出 Q2,Q1,Q0 三个触发器的卡诺图

4. 将状态方程化成 JK 触发器状态方程的标准形式。

Qn1 JQ KQ

台州学院物理与电子工程学院 胡勇坚 副教授

Q2 n 1 Q2Q0 Q1 Q0 Q1 Q0 (Q2 Q2 ) Q0Q2 (Q0 Q1 Q0 )Q2 Q1 Q0 Q2

台州学院物理与电子工程学院 胡勇坚 副教授

5.检查自启动:状态循环中已包含所有状态,能自启动 6.电路实现:略。

二、异步时序电路的设计方法与步骤

如前所述异步时序电路设计方法和步骤与同步时序电路基本相 同,相同的是次态逻辑依然是组合逻辑,状态变化也是触发器输出的 变化。不同的是同步状态机所有触发器都是在同一时钟的作用下翻 转,异步状态机是在不同的时钟作用下翻转,这就导致在求驱动方程 和状态方程时不同的处理方法。至此我们应该已明白,触发器是时序 电路的电路的核心,触发器状态变化有两个条件,一个是输入,一个 是控制条件:即时钟的有效边沿或有效电平。对于同步状态机,时钟 控制条件是同时具备或不具备, 因此现态的输入对同步状态机都是确 定的。而异步状态机的时钟条件不是同时具备的,当时钟条件不具备 时,触发器的现态输入不会影响触发器的输出,因此此时输入是无关 项,因此异步状态机实现比同步状态机电路更简单。另一个不同则是 要为异步状态机的各个触发器分配时钟。 分配时钟的方法是利用状态 转换表或状态转换的波形图,观察每个触发器的翻转次数,得出各个 触发器时钟的频率比, 再利用触发器的输出频率是时钟频率的二分频

J 2 Q1 Q0 , K 2 (Q0 Q1 Q0 ) Q1 Q0

状态机设计

要注意它只是组合电路输出, 并不是寄存器状态本身。 列写方程时用组合输出方程式, 而不是状态方程式。

⑶确定寄存器状态变量Q。

按照设计所需要的状态数目来确定

状态变量的位数 若 有 n 位 状 态 变 量 Q0,Q1,….. Qn-1 则可确定2n个状态数。

1、MEALY机

从Mealy机的结构图可以看出:

输出Z是由输入A和现态Q所决定的函数。在

输出端,现态先产生输出Z,再产生次态Q。

对外部来说,输出Z产生后,先进入一个寄存

器暂存起来,等到状态机进入下一状态时才 出现。也就是说,我们实际看到的Mealy机 的输出已经被延迟了一个时钟周期。

2、MOORE机

状态机的一般形式如下图所示

除了输入输出端外

状态机包括两个主要部分:

即组合逻辑和存储器(寄存器)

存储器用于存储机器的状态;

组合逻辑包含下一个状态译码器和输出译码

器两个功能块—— 下一状态译码器确定状态机的下一个状态, 输出译码器产生实际的输出。

状态机的基本操作有两种:

1.以有序的方法经历一系列状态

对于这两类状态机,控制序列都取决于状

态和输入信号。

大多数实用的状态机都是同步的 时序电路

它由时钟信号触发状态的转移

时钟信号与所有的边沿触发的输入触发器和

输出触发器相连,状态的改变发生于时钟的 边沿。 此外,还有利用组合逻辑中的传播延时实现 状态机存储功能的异步状态机,但此类状态 机很容易出故障,设计难度也较大,故不常 用。

下一状态由其状态译码器,根据现行状态和

输入条件确定。

2.根据状态转换给出输出信号序列 这些输出信号由输出译码器,根据现行状态

状态机图优选全文

4 组合状态

4.1 组合状态

--把若干个状态组织在一起可构成一个组合状态;组合状态内 所包含的状态称为该组合状态的子状态。把内容不包含其他 状态的状态称为简单状态。

--组合状态中包含的子状态可以是顺序子状态,也可以是并发 的子状态。

– 1) On Event

• Event:对一个在时间和空间 上占有一定位置的有意义事 情的规格说明

• Arguments:由所有与事件相 关的可选参量组成

• Condition:可能包含一个条 件布尔表达式

7 转换规范

7.1 General标签

7.2 Detail标签

• 监护条件(Guard Condition)

1 基本概念

1.2 状态Βιβλιοθήκη 模--通过分析系统(或者其构成元素)的状态以及它们之 间的转移,并以状态、转移等概念来建立系统模型称 为状态建模。

1 基本概念

1.3 状态机图

– 状态机图描述了一个对象在其生命周期内所经 历的各种状态,状态之间的转移,发生转移的 动因、条件以及转移中所执行的活动。

图书状态机图

借阅者状态机图

5 状态规范

– 状态(起始状态和终止状 态)和活动的规范窗口都 包含下列标签:

• General标签 • Actions标签 • Transitions标签 • Swimlanes标签

– 1) General标签

• 复选标记State/activity history:状态/活动历史, 历史提供了一种通过子 状态直接转换到最近访 问过的状态的机制。

– 图形表示:

第五讲状态机设计及其指导原则全篇

第五讲状态机设计及其指导原则1/ 38第五讲状态机设计及其指导原则1/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则1 状态机是一种设计思想方法2状态机结构3状态机设计的其他技巧4状态机设计步骤第五讲状态机设计及其指导原则2/ 38第五讲状态机设计及其指导原则2/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学z 状态机是一种设计思想方法第五讲状态机设计及其指导原则3/ 38第五讲状态机设计及其指导原则3/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学原语描述module noconditional (clk,nrst,state,event);input clk,nrst input state;output event;reg event;reg [2:0] CS; //CurrentState reg[2:0] NS; //NextStateparameter [2:0] //one hot with zero idleidle = 3’b000,dorm = 3'b001,diningroom = 3'b010,classroom = 3'b100;第五讲状态机设计及其指导原则4/ 38第五讲状态机设计及其指导原则4/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学//sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst) CS <= idle; else CS <= NS; //combinational condition judgment always @ (nrst or CS)begincase (CS)idle:idle_task;NS = dorm;dorm:dorm_task;NS = diningroom;diningroom:diningroom_task;NS = classroom;classroom:classroom_task;NS = dorm;default:idle_task;NS = dorm;endcase end endmodule第五讲状态机设计及其指导原则5/ 38第五讲状态机设计及其指导原则5/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则6/ 38第五讲状态机设计及其指导原则6/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学 状态机的本质--对具有逻辑顺序或时序规律事件的一种描述方法 状态机的两个应用思路:-从状态变量入手-明确电路的输出的关系第五讲状态机设计及其指导原则7/ 38第五讲状态机设计及其指导原则7/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学对于逻辑电路而言,小到一个简单的时序逻辑,大到复杂的微处理器,都适合用状态机方法进行描述。

状态机设计

CLK

State Machine(2/2)

有時組合邏輯會加上外部輸入的參數。 例如做一個可載入式計數器,當外在強 迫輸入某值後,使計數器從某設定的數 值開始計數。

Current State 狀態資訊 Next State Input 組合邏輯 Output 外在輸入

範例(7/20)

為你的狀態機命名 (別和Project的名字相同,不然之後無法從 symbol中呼叫)

範例(8/20)

定義輸入/輸出的埠

按New新增一個定義 在Name為定義命名 在Direction Frame 選擇方向為Input or Output Output可在Bus處設 定所欲輸出的數量 (狀態數)

範例(11/20)

新增狀態(內定從S1開始)

範例(12/20)

畫上狀態轉換的方向

範例(13/20)

設定狀態轉換之條件式

ABEL

Verilog

Condition = True才和轉換

& # ! $

&& || ! ^

AND OR NOT XOR

範例(14/20)

Q=0

定義狀態輸出值(多個輸出以分號分開)

範例(9/20)

選擇所欲使用狀態機的數量

範例(10/20)

狀態機設計器的面板

State Machine中所有的 Input & Output

Port Properties

設定Port Name, 如果為Vector形式的話, 請設定Range

如果是設成Registered的形式, 可能會造成輸出Delay 1 Clock

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0

1

X

0

0

0

0

1

0

X

0

0

0

0

1

1

X

0

0

0

0

由状态转换表推导 触发器的驱动方程

ASM图的硬件实现

ASM图法状态机设计——硬件实现

• 由状态转换表推导触发器的驱动方程

对于复杂的ASM图和相应的状态表可用 卡诺图对次态进行化简,得到简化的驱 动方程。

用计数器法实现ASM图的流程

ASM图状态分配

ASM图除了可以得到状态表和驱动方程 外,还可以得到输出方程

state = Gmajor_green = 1, minor_green = 0; state = Rmajor_green = 0, minor_green = 1;

• 根据题意,画出ASM图:

G MAJOR=GRN MINOR=RED

0 CAR

1

START_TIME

R MAJOR=RED MINOR=GRN

会延迟到下一个时钟周期。可见,Moore型状态机的最大优点就是可以将输入部分和 输出部分隔离开。 • 对于Mealy型有限状态机来说,由于它的输出是输入信号的函数,因此如果输入信号发 生改变,那么输出可以在一个时钟周期内发生改变。

状态 \ 输入

S0

a=‘1’ S1

b=‘1’ S2

default

S1

S2

S0

S2

S0

MDS图

有限状态机的描述方法

• ASM图法设计状态机

• ASM本质上是一个有限状态机,主要用于同步时序系统。 • ASM精确地表示出状态转换的时间关系。 • 从形式上看,这种流程图类似于描述软件程序的流程图,但它能和实现它的硬件很好

时序电路的概念

下面以一个简单的三位计数器为例,说明时序电路的结构。

•设计分析

• 3位计数器,由时钟上升沿触发,计数从000~111,到111后则重新回到000。 • 采用上升沿触发的D触发器作为状态寄存器,D触发器的示意图和真值表如下:

D 1D

Q

C

C1

Q

D

C

Q+

Q+

0

0

1

1

1

0

-

0

Q

Q

-

1

Q

Q

时序电路的概念

的对应起来。 • 本章主要学习使用ASM图法描述状态机。

ASM图法状态机设计——ASM图组成

• ASM图的组成

• 状态框

• 用一个矩形框来表示一个状态。状态的名称写在左上角;状态的二进制编码写在右上角; 操作内容写在矩形框内。在同步系统中,状态经历的时间至少是一个时钟周期,也可以是 几个周期。

状态名 二进制码

Q SET D Q1n+1

Q CLR

学习ASM图的硬件实现有助 于我们更好的理解后续的内 容,下面我们将学习如何使 用VHDL实现ASM图。

Q SET D Q CLR

Q2n+1

CP

• A举例SM图法状态机设计——举例

• 要求设计一套交叉路口交通信号灯,该路口有一条交通干线与支线, 支线上装有传感器,当支线有车通过时,传感器输出信号CAR=1。 正常的工作状态时干线亮绿灯,支线亮红灯;当CAR=1时,干线亮 红灯,支线亮绿灯,并开始计时,START_TIEMR=1,当计时结束, 即信号TIMED=1时,重新回到正常工作状态(干线亮绿灯,支线亮 红灯)。

电路的竞争与冒险

• 竞争与冒险

• 所谓竞争与冒险,就是在组合电路中,信号经不同途径传输后,达到电路中某一汇合 点的时间有先有后,这种现象成为竞争。由于竞争而使电路输出发生瞬间错误的现象, 称为冒险。

• 在时序逻辑电路中,产生次态的电路和输出电路是组合逻辑电路。组合逻辑电路存在 竞争与冒险,可能导致时序系统进入不正确的状态。

• 用计数器实现ASM图 • 用多路选择器实现ASM图 • 每个状态一个触发器(定序型) • 基于ROM法实现ASM图(微程序型)

• ASM图的硬件实现一共有4种方法,这里我们重点介绍用计数器实现ASM图 的方法。

ASM图法状态机设计——硬件实现

• ASM图的状态分配

用计数器法实现ASM图的流程

N个状态变量可以描 述2^n个状态。该

表中01未指定状态,采用计数器实现,因此需考虑因 偶然因素出现01状态时,应强迫其次态为00,所以一 旦出现01状态后,经过一个时钟周期就可以自动回到 有用状态循环。

用计数器法实现ASM图的流程

ASM图状态分配

状态转换表

现态

次态

输出

Q2

Q1

X

Q2n+1 Q1n+1

Z1

Z2

0

0

0

1

0

1

1

0

0

1

1

1

1

0

Major Road

Sensor

Minor Road

ASM图法状态机设计——举例

• 设计步骤

• 根据设计要求,我们先确定系统的输入:

clock, car, timed.

• 然后确定系统的输出:

start_timer; major_green, minor_green. (枚举类型)

• 分析系统所有可能出现的状态:

tpd

C C

D

E

F

毛刺

电路的竞争与冒险

• 状态机克服竞争冒险的方法

• 在次态产生组合逻辑电路中,可以通过时序逻辑消除毛刺,从而克服竞争冒险。

• 通过输出端时序同步的方法消除竞争与冒险(即使用同步时序逻辑电路设计方法。详 细实例见后面介绍)。

有限状态机的描述方法

ASM图(主要讲解) 状态转移图

状态转移列表

但必须指向状态框。

条件

✓仅包含一个状态框,无判

断框和条件框的ASM块是一

个简单块。

S3 10

✓每个状态单元表示一个时

钟周期内系统所处的状态,

R0 S2 11

在该状态下完成块内的若干 操作。

ASM图法状态机设计——硬件实现

• 用ASM图描述一个系统控制器时,实际上是描述了该控制器的硬件结构和 时序工作过程,因此ASM图与硬件有很好的对应关系,ASM图的硬件实现 有以下几种方法:

时序电路与状态机的关系

• 日常生活中的状态机

• 通过状态机的方式,我们可以清晰地描述一 个学生的在校生活方式。

条件:周末

地点:宿舍 功能:睡觉

条件:非周末

地点:花前 月下 功能:

条件:周末

条件: 非周末

且 下午7点

地点:教室 功能:学习

条件:周末

地点:食堂 功能:吃饭

条件:非周末

条件: 非周末

且 下午6点

时序电路与状态机的关系

• 状态机的基本要素

• 状态:也叫状态变量。在逻辑设计中,使用状态划分逻辑顺序和时序规律。 • 输出:输出指在某一个状态时特定发生的事件。 • 输入:指状态机中进入每个状态的条件,有的状态机没有输入条件,其中的状态转移

较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态。

条件: 非周末

且 下午2点

地点:体育馆 功能:运动

时序电路与状态机的关系

• 描述时序电路的状态机的组成

• 组合逻辑

• 组合逻辑又可分为次态逻辑和输出逻辑两个部分。其中:次态逻辑的功能是用来确定有限 状态机的下一个状态;输出逻辑是用来确定有限状态机的输出。

• 存储逻辑

• 寄存器逻辑的功能:用来存储有限状态机的内部状态。

ASM图状态分配

ASM图中有3个状态,

所以需要两个状态 变量。设两个状态

状态转换表

变量为Q2Q1,我们

选用2个D触发器。

由状态转换表推导

用二进制计数序列

触发器的驱动方程

依次表示状态。

ASM图的硬件实现

ASM图法状态机设计——硬件实现

• 状态转换表

因为10和11状态与输入X无关,所以X值可作任意值处 理。

0

1

条件

引出分支 引出分支

ASM图法状态机设计——ASM图组成

• ASM图组成

• 条件框

• 用椭圆框表示。条件框一定是与判断框的一个转移分支相连接,仅当判断框中判断变量满 足相应的转移条件时,才进行条件框中标明的操作和信号输出。

• 虽然条件框和状态框都能执行操作和输出信号,但二者有很大区别。

寄存器操作或输出

状态转换表

由状态转换表推导 触发器的驱动方程

ASM图的硬件实现

ASM图法状态机设计——硬件实现

X

•采A用SM计图的数硬器件法实现实现ASM图,

0

&

Z2

0

0

一旦ASM图有很小的改动, 就需要重新设计与次态相关 的组合电路部分。此外,当

0

&

0

0

Z1

0

&

0

0

系统的状态超过8个时,ASM 图的硬件实现也很复杂。

ASM图法状态机设计——ASM图组成

• 状态(a框) 与条件框的区别 A

(b)

A

1 C

0

Y

W

1 C

0

Y

W

ASM图法状态机设计——ASM图组成

Clock ASM(a)

Z

Y,C=1 Y,C=0

W ASM(b)

Z

Y,C=1

W,C=1

Y,C=0

W,C=0

ASM图法状态机设计——ASM图组成

状态框

P

00

• Mealy有限状态机框图:

从信号输出方式上分