误码率在线测试电路设计

SDH误码测试

SDH误码测试一、误码特性1、基本概念:差错(Error误码):在数字通信中,发送和接收序列的任何不一致都叫差错,在我国习惯上把差错称为误码。

比特差错(Bit Error):发送和接收序列中对应的单个数字不一致就是比特差错,G.821建议中所用的术语"误码"就是指比特差错。

块差错(Block Error):将一组码看成是一个整体,在其中有一个或多个比特差错,则称块差错。

G.826建议中所用的术语"误块"就是指块差错。

误码秒(ES):在一秒时间周期有一个或多个比特差错,称为误码秒。

误块秒(ES):在一秒时间周期有一个或多个误块,称为误块秒。

差错秒(ES):误码秒和误块秒的统称。

严重误码秒、严重误块秒或严重差错秒(SES):在误码秒、误块秒或差错秒中,有一部分差错量特别多,定义为SES。

2、误码机理:(1)造成误码的主要内部机理有:*各种内部噪声源*色散引起的码间干扰*定位抖动产生的误码(2)外部机理:主要是由一些具有突发性质的外部脉冲干扰源所引起,诸如外部电磁干扰、静电放电、设备故障、电源瞬态干扰和人为活动等。

这些脉冲干扰有可能超过系统固有的高信噪比门限造成突发误码。

二、误码性能指标:1、低于基群速率的数字连接的误码性能ITU-T G.821建议规范了用于语音业务或用作数据型业务载体信道的N′64kbit/s电路交换数字连接(1£N£24或32)的误码性能事件、参数和指标。

G.821定义以下事件:*误码秒(ES):在一秒时间周期有1个或更多差错比特。

*严重误码秒(SES):在一秒时间周期的差错比特比3 10-3。

G.821定义的误码性能参数有:*误码秒比(ESR):在一个固定测试时间间隔上的可用时间内,ES与总秒数之比。

*严重误码秒比(SESR):在一个固定测试时间间隔上的可用时间内,SES与总秒数之比。

G.821对64kbit/s全程27500km假设参考通道(HRP)端到端连接的性能指标见表1。

通信测试方案

3.确保通信系统在各类环境下具有良好的稳定性和可靠性;

4.评估通信系统的安全性能,确保用户信息安全;

5.为通信系统的后续升级和扩容提供技术支持。

三、测试内容

1.信号质量测试:

-测试通信系统在不同频段、不同环境下的信号覆盖范围;

-评估信号强度、信噪比等指标,确保通信质量。

5.稳定性测试:

-对通信系统进行长时间运行测试,观察系统稳定性;

-在极端环境下进行测试,确保系统在恶劣条件下的可靠性。

6.安全性测试:

-对通信系统进行安全漏洞扫描,确保无安全风险;

-模拟攻击场景,测试系统的安全防护能力。

四、测试方法与步骤

1.信号质量测试:

-使用专业测试设备,如信号分析仪、场强测试仪等;

-模拟攻击场景,测试系统安全防护能力;

-评估系统安全性能。

五、测试团队与职责

1.项目经理:

-负责整体测试工作的组织与协调;

-监督测试进度,确保按时完成测试任务;

-负责与相关单位沟通,解决测试过程中的问题。

2.测试工程师:

-负责具体测试工作的实施,包括测试环境来自建、测试脚本编写、测试数据收集等;

-参与测试数据分析,协助优化系统性能;

-在不同网络环境下进行测试,记录传输速率;

-对比测试数据,评估系统性能。

3.误码率测试:

-使用误码率测试仪,模拟不同信噪比、传输速率;

-记录测试数据,分析误码率;

-确保误码率满足技术要求。

4.系统容量测试:

-使用网络性能测试软件,模拟大量用户在线;

-观察系统运行情况,记录关键指标;

-评估系统容量。

5.稳定性测试:

PDH接口的在线监测原理

PDH接口的在线监测原理一、仪表在线监测的种类:1、在线跨接测试在线跨接误码测试是将仪表的接收端连接到DDF(数字配线架)上的发送或接收端口的测试方式。

这种方式一般以并联的方式将仪表的接收端接入DDF架的三通头上,与此会造成同时线路的阻抗下降。

为了保持线路的阻抗,一般选用至少十倍的阻抗接入即所谓的以“高阻跨接接入”(如采用75欧姆的同轴电缆,高阻的要求至少为750欧姆),一般高阻都会大于2000欧姆。

2、在线桥接测试在线桥接测试方式是将2Mb/s信号直接通过仪表进行传输。

这种方式在仪表接入时会造成在用业务中断。

二、2M数据结构的种类1、非成帧类型信号传送过程中只进行连续的比特传送,不进行帧结构的划分。

这种结构多用于工程测试和日常维护中环回测试。

需要特别提醒注意的是:(1)大多数SDH设备厂家默认的PDH接口都设置为非成帧结构,这种设置最大的好处是数据可以“透明”通过SDH设备。

无论进入SDH设备的PDH信号是带帧结构还是没有帧结构都可以进行传输。

如果我们将端口设置为带帧结构,而输入的信号不带帧结构,那么传送过程中一部分时隙就会错误当作帧同步码或者校验位,造成业务中断。

(2)G.826分析是以块为基础进行误码性能分析,不提供比特误码测试。

2、成帧类型成帧类型又可以分为PCM31、PCM30、PCM31+CRC和PCM30+CRC。

具体的帧结构比较复杂,这里不再阐述。

在测试过程中,需要根据不同的帧结构类型设置仪表,否则仪表上无法进行正常测试。

可喜的是,现在的仪表大多数都可以完成帧结构的自动识别。

三、PDH端口在线监测的内容因为用户的话音数据是随机的、不可预知的,因而仪表无法实现对两个码组逐帧、逐位的比较,不可能测试出真正的比特误码率。

1、非成帧信号的测试:由于信号中没有帧头,也就是说没有任何开销字节,所有字节都是业务信号。

仪表是无法“智能”判断业务信号是否有误码或正确与否,但能够监测:(1)LOSS(因为没有帧定位码,所以没有帧失步告警)(2)AIS(3)编码错误:ITU-T详细规定了信号的编码规则,仪表可以完成对信号编码的检测。

E1数据误码测试仪补充说明

7 应用层6 表示层5 会话层4 传输层3 网络层2 数据链路层1 物理层其中高层,既7、6、5、4层定义了应用程序的功能,下面3层,既3、2、1层主要面向通过网络的端到端的数据流。

下面我给大家介绍一下这7层的功能:(1)应用层:与其他计算机进行通讯的一个应用,它是对应用程序的通信服务的。

例如,一个没有通信功能的字处理程序就不能执行通信的代码,从事字处理工作的程序员也不关心OSI的第7层。

但是,如果添加了一个传输文件的选项,那么字处理器的程序员就需要实现OSI的第7层。

示例:telnet,HTTP,FTP,WWW,NFS,SMTP等。

(2)表示层:这一层的主要功能是定义数据格式及加密。

例如,FTP 允许你选择以二进制或ASII格式传输。

如果选择二进制,那么发送方和接收方不改变文件的内容。

如果选择ASII格式,发送方将把文本从发送方的字符集转换成标准的ASII后发送数据。

在接收方将标准的ASII转换成接收方计算机的字符集。

示例:加密,ASII等。

(3)会话层:他定义了如何开始、控制和结束一个会话,包括对多个双向小时的控制和管理,以便在只完成连续消息的一部分时可以通知应用,从而使表示层看到的数据是连续的,在某些情况下,如果表示层收到了所有的数据,则用数据代表表示层。

示例:RPC,SQL等。

(4)传输层:这层的功能包括是否选择差错恢复协议还是无差错恢复协议,及在同一主机上对不同应用的数据流的输入进行复用,还包括对收到的顺序不对的数据包的重新排序功能。

示例:TCP,UDP,SPX。

(5)网络层:这层对端到端的包传输进行定义,他定义了能够标识所有结点的逻辑地址,还定义了路由实现的方式和学习的方式。

为了适应最大传输单元长度小于包长度的传输介质,网络层还定义了如何将一个包分解成更小的包的分段方法。

示例:IP,IPX等。

(6)数据链路层:他定义了在单个链路上如何传输数据。

这些协议与被讨论的歌种介质有关。

示例:ATM,FDDI等。

LITE3000常见功能使用流程

LITE3000常见功能使用流程运维中心漕溪维护部杨坚多用途手持式2M传输测试仪LITE3000是日本安立ANRITSU公司生产的一款功能强大的传输及信令测试仪表,它能够完成从快速故障定位到全面深入分析传输和信令问题等任务。

在中继测试仪的基础上,配备不同的功能选件还可完成SS7信令、随路信令、ISDN协议、ISDN仿真、A-bis接口、A接口,MAP协议、V5接口、数据接口及多音频信令等测试工作。

作为交换专业的维护人员,在日常工作中经常用到的LITE3000的功能包括:传输质量在线监测、传输误码率测试、在线语音信号监听和在线Abis信令解析。

下面就对上述功能的简单使用流程做一介绍:一、传输质量在线监测在介绍该功能前首先需要明确一些基本的原则:常见的传输2M级别PCM告警主要有:OK(正常)、NO SIGNAL(无信号)、AIS(业务不可用全“1”告警)、DISTANT ALARM(业务远端告警,即本端收对端不可用)、NO SYNC(帧失去同步)五种,其中NO SIGNAL、NO SYNC为客观性告警,不是设备产生;而交换类设备(MSC、BSC、BTS、SGSN等)仅可能发出OK、DISTANT ALARM告警;传输类设备(SDH、WDM等)仅可能发出OK、AIS告警。

LITE3000监测传输质量的流程为:1、按左上角ON/OFF开关,打开仪表。

2、待出现主界面后发现左上角“NO SIGNAL”红色灯亮起,即可开始使用3、将连接线接口插入欲检测的DDF架2M速率LINK监测口4、仪表左侧面板上相应告警说明边的红色告警灯亮起,即表示为该告警,如最上方绿色灯亮起,则表示线路“OK ”,如果想知道具体的告警时间,可将Measurement 设为log 方式,Signalling Reception 设为Off 。

5、如果该传输链路上存在误码,Signal Impaired 灯会闪烁,如想了解误码情况,可参看下节。

星间异步通信链路的误码率测试技术

误码率测试分为数据直传模式下的单程误码率

万方数据

2010年第1期

刘磊等:星间异步通信链路的误码率测试技术

125

图4发送数据帧格式设置框图

图5误码率统计框图

图6发送数据格式框图

上位机每收到一帧,将该帧与发送的数据相比 较,检测到错误后,将总误码数加l。由于LNA接13 为有线接口,且TCP协议中本身含有校验和重传机 制。故由LNA接口带来的误码可以忽略不计。待测 试完成(发送的帧数达到要求)后,上位机应用软件 自动完成误码率计算。

参考文献

于志坚,丁溯泉,罗伦.航天测控与数传接收综合信 息构想[J].遥测遥控,2002,23(4):8~ll 丁溯泉,于志坚.s/X航天测控与数传接收统一信道 体制研究[c].中国空间科学学会空间探测专业委员 会第十五次学术会议论文集.P121~P127.2002 Ma ling,Huang Bo,et ai.Inter—satellite optical eommu—

nications:The influence of shake of a satellite 7 s platform

on the bit error rate『C J.Aero Sense98,Orlando,1998:

智慧家庭考试题库

1. [单选题] 在确定了光缆的路由走向后,沿光缆路由,在墙面上安装螺钉扣。

螺钉扣用Φ6mm膨胀管及螺丝钉固定。

两个螺钉扣之间的间距为( )。

(1分)1. 20cm2. 40cm3. 60cm4. 80cm正确答案: C2. [单选题] 客户需要在电信室内布线服务,电信按照4米内()元/点收取费用(1分)1. 152. 203. 254. 30正确答案: B3. [单选题] 以下ONU接收光信号中,哪一种会引发用户掉线()(1分)1. -6dbm2. -13dbm3. -23dbm4. -25dbm正确答案: A4. [单选题] EPON上下行数据分别采用不同的波长进行传输,其中CATV信号采用的波长为()(1分)1. 1300nmB2. 1310nm3. 1490nm4. 1550nm正确答案: D5. [单选题] 将本地计算机上的文件拷贝到远程计算机上称为(1分)1. 上传2. 下载3. 复制4. 剪切正确答案: A6. [单选题] 在光通信中,ODN1:16光分路器的损耗最大不超:()(1分)1. 9db2. 12db3. 14db4. 16db正确答案: C7. [单选题] 光信号能够在光纤中以极低的损耗传输,是利用了光纤的( )原理(1分)1. 反射2. 折射3. 全反射4. 透射正确答案: C8. [单选题] E8-C可以支持几个SSID?()(1分)1. 12. 23. 34. 4正确答案: D9. [单选题] 制作直连网线时,通常工程中用的比较多的是()标准(1分)1. T569A2. T568A3. T569B4. T568B正确答案: D10. [单选题] 误码率是衡量哪项传输性能的指标( ) (1分)1. 可靠性2. 速率3. 容量4. 吞吐量正确答案: A11. [单选题] EPON传输上行采用是()(1分)1. 竞争方式2. 广播方式3. 空分方式4. 时分方式正确答案: D12. [单选题] “智宽生活“的含义是( ) (1分)1. 智慧家庭、智慧生活2. 智能光宽带、智慧新生活3. 智慧光宽带、智能新生活4. 智慧家庭、带宽生活正确答案: B13. [单选题] Internet中采用的交换技术是( ) (1分)1. 电路交换2. 报文交换3. 分组交换4. 信元交换正确答案: C14. [单选题] 架空自承式光缆与电力线交越时,交越距离保持( )以上(1分)1. 0.6m2. 0.8m3. 1m4. 1.2m正确答案: C15. [单选题] 监控摄像头无线网络接入方式为(1分)1. wifi2. Zigebb3. 蓝牙4. DNFC正确答案: A16. [单选题] 选用螺钉固定方式时,应根据线槽及其配件上标注的螺钉固定位置,将线槽及其配件固定在墙面上,一般1米直线槽需用( )螺钉进行固定。

测试误码率的简单装置

测试误码率的简单装置测试误码率的简单装置按照传统,数字接收机的接收质量是用BER(误码率)来表示的。

这一数值与在给定的周期内接收到的错误码成比例。

一般来说,你可在实验室里测量BER,方法是把一个被伪随机码调制的RF 信号加到被测接收机。

本文设计实例提出一种使用单纯方波的代替方法。

这种方法也许并不优于常用技术,但由于它不需要复杂的同步,实现起来简便,测量结果可靠。

不可否认的是,方波信号并不能真正代表正常使用中接收机收到的数据(图1)。

调制射频载波的方波被移相,为的是把接收机的延迟考虑在内。

一个“异或”门在每个位转移处――一般在数据位宽度10% 的地方产生一个采样脉冲。

这个采样脉冲对接收器产生的原始数据进行采样,从而提供干净的数据。

图1,这一时序图说明了一个种简单的BER 测试仪的工作原理。

理解这一技术的关键是要记住:一个由两个连续的“1”或“0”组成的位串表示一个错误。

实现一个1 位延迟的D 触发器能检测到这种错误。

图2 ,BER 测试仪使用一个采用OOK(通/断键控)调制的信号发生器。

你可以将错误脉冲显示在示波器上,或者用一个频率计数器来进行计数。

图 2 示出了一个典型的测试设置。

你要按规定的数据速率对RF 发生器进行调制。

要注意的是,一个500Hz 方波等效于1kbps 波特率。

调制信号和接收到的数据都送入BER 测试板。

你可调整采样信号,使之靠近数据脉冲接收末端。

在许多数字接收机中,这种安排相当好地近似于一个相关接收机。

错误脉冲显示在示波器上。

举例来说,如果你希望调节RF 电平,以获得1/100 的BER,那你就要降低加到接收机的RF 电平,在一次100 ms 的扫描中平均看到每次扫描有一个错误脉冲。

图3,简单BER 测试仪使用了一个可调移相器和一个差分器。

在图 3 中,IC1 和电位器P1 构成一个基本的可调移相器。

R2 提供滞后,R1、C1 和IC2 构成一。

ddsds

高速接口中的PRBS模块的设计

KevinWan

在高速设计中为了测试高速串行通道传输的误码率,通常通过发送PRBS码来进行测试。

原理:用生成函数产生一段随机码流,然后按周期循环。

PRBS码的周期长度与其阶数有关,常用的阶数有7、9、11、15、20、23、31。

对于n阶PRBS码,每个周期的序列长度为2^n-1。

在每个周期内,“0”和“1”是随机分布的,并且“0”和“1”的个数相等。

连续个“1”的最大数目为n,连续个“0”的最大数目为n-1(反转后就是n-1个连“1”和n个连“0”)。

在对高速信号链路进行误码测试时,基本上都是利用PRBS码流来模拟真实的线网码流环境,因为在线网中,所有的数据都是随机出现的,没有任何规律可言,而PRBS码流在一定程度上具有这种“随机数据”特性,二进制“0”和“1”随机出现,其频谱特征与白噪声非常接近。

PRBS码流的阶数越高,其包含的码型就越丰富,就越接近真实的线网环境,测试的结果就越准确。

一个PRBS序列可以串/并转换成多路(2、4、8、16…路),每路输出的速率降低,但仍然保持原序列的一切特征;反之,同一时钟源低速率多路(2、4、8、16…路)同一n数的PRBS可以经并/串转换成高速率的n阶PRBS。

本文采用Verilog来设计PRBS模块,可以通过外部的参数配置输出prbs7, prbs9, prbs15, prbs23, prbs31

TX_Data <= PRBS_reg[PRBS_WIDTH-1:0]; end

end

assign PRBS_Data = TX_Data;

endmodule。

AV5233C 型误码测试仪 用户手册说明书

AV5233C型误码测试仪 用户手册中电科仪器仪表有限公司前言非常感谢您选择、使用中电科仪器仪表有限公司生产的AV5233C型误码测试仪!本所产品集高、精、尖于一体,在同类产品中质量性价比最高,为方便您使用,请仔细阅读本手册。

我们将以最大限度满足您的需求为己任,为您提供高品质的测量仪器,同时带给您一流的售后服务。

我们的一贯宗旨是“质量优良,服务周到”,提供满意的产品和服务是我们对用户的承诺,我们竭诚欢迎您的垂询,垂询电话:服务咨询*************技术支持*************质量监督*************传真*************网址电子信箱*************地址山东省青岛经济技术开发区香江路98号邮编 266555本手册介绍了中电科仪器仪表有限公司生产的AV5233C型误码测试仪的用途、性能特性、基本工作原理、使用方法、使用注意事项等,以帮助您尽快熟悉和掌握仪器的操作方法和使用要点。

请仔细阅读本手册,并正确按照书中指导操作。

由于时间紧迫和笔者水平有限,本手册错误和疏漏之处在所难免,恳请各位用户批评指正!由于我们的工作失误给您造成的不便我们深表歉意。

声明:本手册版本号是AV5233C 型误码测试仪用户手册第一版。

本手册中的内容如有变更,恕不另行通知。

本手册内容及所用术语解释权属于中电科仪器仪表有限公司。

本手册版权属于中电科仪器仪表有限公司,任何单位或个人非经本所授权,不得对本手册内容进行修改或篡改,并且不得以赢利为目的对本手册进行复制、传播,违者中电科仪器仪表有限公司保留对侵权者追究法律责任的权利。

编者2002年11月目录第一章概述---------------------------------------------------------------------------------------------- 1 第一篇使用说明 ---------------------------------------------------------------------------------------- 2 第二章操作指导 ---------------------------------------------------------------------------------------- 3 第一节内部结构特征 ---------------------------------------------------------------------------- 3 第二节前面板特征 ------------------------------------------------------------------------------- 4 第三节后面板特征 ------------------------------------------------------------------------------- 6 第四节前面板按键及菜单操作----------------------------------------------------------------- 6 第二篇技术说明 ---------------------------------------------------------------------------------------- 13 第三章工作原理 ---------------------------------------------------------------------------------------- 14 第一节概要 ---------------------------------------------------------------------------------------- 14 第二节工作原理 ---------------------------------------------------------------------------------- 14 第四章技术指标和指标测试 ------------------------------------------------------------------------- 16 第一节发射部分技术指标----------------------------------------------------------------------- 16 第二节接收部分技术指标----------------------------------------------------------------------- 16 第三节其它技术指标 ----------------------------------------------------------------------------- 17 第四节指标测试 ----------------------------------------------------------------------------------- 18 第三篇维修说明 ---------------------------------------------------------------------------------------- 25 第五章维护和保养-------------------------------------------------------------------------------------- 26 第一节维护保养 ---------------------------------------------------------------------------------- 26 第二节一般维修 ---------------------------------------------------------------------------------- 26 附录A AV5233C 误码测试仪中误码参数的定义 ------------------------------------------------- 28 附录B A V5233C 误码测试仪中比特误码和编码误码的检测方法 ----------------------------- 29附录C 英文名词缩写及解释-------------------------------------------------------------------------- 31第一章概述第一章 概述A V5233C型误码测试仪是利用DDS(直接数字合成)技术产生内部时钟的误码测试仪,可用于50b/s~50Mb/s(内部时钟,选件1)和1kb/s~50Mb/s(外部时钟)的数据通信系统误码测试,也可用于PCM 1~3次群电信系统的误码、告警测试。

浅谈sdh系统中的误码测试及分析

灵敏度) :对于光功率正常,但光缆距离过长的,就要考虑色散问题,

因为色散受F髓巨离不同。 ( 三) 确定误码产生的段落 确定误码是由光板产生的,还是由光缆段产生的,大致可采用以

下 方法 :一 种方 法是 将有 误 码的 相邻 两个 站的 线 路板 进行 东西 向对 换,

观察误码是跟着光板走,还是固定在某个方向;另一种是,将一段光路

码。根据误码的特点,首先检查一下测试仪表是否处于正常状态,测试 连接是否正确,测试塞绳是否完好。然后检查SDH设备出现了什么告 警 信息。

㈡对光功率检测

光功 率是 个重 要的 因素 ,所 以对 出现 误码 的光 路需 要了 解这 几点 : 光板类型、发光功率、收光功率、光纤衰减值、光缆距离、过载点、灵 敏度;如果光功率有异常情况,要进行相应调整( 主要指接近过载点或

㈡对于线路E的B2、B3"i !鸫,常见的原因是

单板的故障;时钟同步性能不好等;机房条件,包括温度、电源

稳定 性以及接 地情况等 。

.

㈤如果只出现芄路t 的v5误码,则常见的原因是

交叉板与支路板之间配合有问题、支路板有问题等,应检查支路

板或交叉板:也有可能是外界干扰引起,如设备接地不好,设备附近有

大的 干扰源 ,EMC屏蔽不 好( 主要针 对34M/45M/1 55M高频信号)

日常 维护采 取在线 测试的 方法, 工程 测试则 采用中 断测试 的方法 。 1)SDH设备进 行24小时误码 测试时,根 据不同类型 的端口进行

抽测,要求如下:1) 对于2.5Gbi t /s系 统,每个25Gbi 怕系统测试2 个155Mbi t /s接口 :2) 对于2Mbi t /s数字通道,每 个155Mbi t /s 系 统,测 试1个 2Mbi t /s支 路;3) 凡两端 均不连接STM一1复用设 备和 一端连 接STM一1另 一端不连接 STM一1的复 用设备,均 只在 1 55Mbi t /s支路口测 试。

误码测试

第五部分误码测试5、1 误码特性一、基本概念:差错(Error误码):在数字通信中,发送和接收序列的任何不一致都叫差错,在我国习惯上把差错称为误码。

比特差错(Bit Error):发送和接收序列中对应的单个数字不一致就是比特差错,G.821建议中所用的术语“误码”就是指比特差错。

块差错(Block Error):将一组码看成是一个整体,在其中有一个或多个比特差错,则称块差错。

G.826建议中所用的术语“误块”就是指块差错。

误码秒(ES):在一秒时间周期有一个或多个比特差错,称为误码秒。

误块秒(ES):在一秒时间周期有一个或多个误块,称为误块秒。

差错秒(ES):误码秒和误块秒的统称。

严重误码秒、严重误块秒或严重差错秒(SES):在误码秒、误块秒或差错秒中,有一部分差错量特别多,定义为SES。

二、误码机理:1、造成误码的主要内部机理有:●各种内部噪声源●色散引起的码间干扰●定位抖动产生的误码2、外部机理:主要是由一些具有突发性质的外部脉冲干扰源所引起,诸如外部电磁干扰、静电放电、设备故障、电源瞬态干扰和人为活动等。

这些脉冲干扰有可能超过系统固有的高信噪比门限造成突发误码。

5、2 误码性能指标:1、低于基群速率的数字连接的误码性能ITU-T G.821建议规范了用于语音业务或用作数据型业务载体信道的N⨯64kbit/s电路交换数字连接(1≤N≤24或32)的误码性能事件、参数和指标。

G.821定义以下事件:*误码秒(ES):在一秒时间周期有1个或更多差错比特。

*严重误码秒(SES):在一秒时间周期的差错比特比≥ 10-3。

G.821定义的误码性能参数有:*误码秒比(ESR):在一个固定测试时间间隔上的可用时间内,ES与总秒数之比。

*严重误码秒比(SESR):在一个固定测试时间间隔上的可用时间内,SES与总秒数之比。

G.821对64kbit/s全程27500km假设参考通道(HRP)端到端连接的性能指标见表1。

一款功能全面的M8020A比特误码率测试仪技术资料

Keysight J-BERT M8020A高性能比特误码率测试仪技术资料版本 2.0(新增内容: 集成可调节码间干扰ISI)永远从容应对下一个设计说明是德科技高性能 J-BERT M8020A 能够对速度高达 16 或 32 Gb/s 的单通道和多通道器件进行快速、精确的接收机表征。

M8020A 提供目前最全面的综合功能,可以简化您的测试设置。

并且,在线自动信号条件校准可以确保精确、可重复的测量结果,通过交互式的链路训练,它可以充当您的被测器件的链路伙伴。

集如此众多优势于一身,J-BERT M8020A 将会加速您的设计验证。

主要特性:–数据速率高达 8.5 和 16 Gb/s,可扩展至 32Gb/s–在 5 插槽 AXIe 机箱内可提供 1 至 4 个比特误码率测试仪通道–综合和校准的抖动注入:RJ、P J1、P J2、SJ、BUJ、正弦干扰(共模和差摸)、SSC (三角波、任意波形和剩余噪声) 和时钟/2–8 分接去加重,正值和负值–集成和可调 ISI–PCI Express 交互式链路培训–内置时钟恢复和均衡–所有选件和模块均可升级应用:J-BERT M8020A 以研发和测试工程师为设计对象,帮助他们表征和验收芯片、器件、电路板以及在消费类产品、计算机、移动计算机、数据中心和通信行业内具有 16 Gb/s 和 32 Gb/s 串行 I/O 端口的系统。

J-BERT M8020A 可以测试各种流行总线标准,例如 PCI Express ®、SATA/SAS、DisplayPort、USB 超高速、MIPI ® M-PHY ®、SD UHS-II、光纤通道、QPI、存储器总线、背板、中继器、有源光纤、Thunderbolt (雷电) 连接器标准、10/40 GbE/SFP+/QSFP、100GbE/CFP2。

M8000 系列比特误码率 (BER) 测试解决方案开发下一代计算机、消费电子产品或通信设备时,简化时效性测试十分必要。

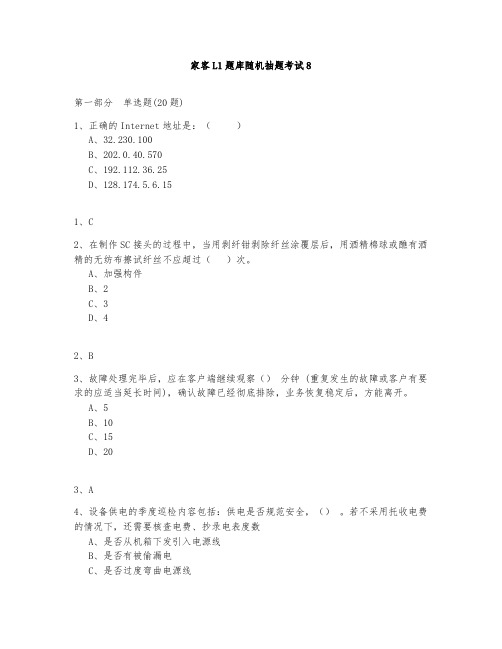

家客L1题库测试与答案2020第8部分

家客L1题库随机抽题考试8第一部分单选题(20题)1、正确的Internet地址是:()A、32.230.100B、202.0.40.570C、192.112.36.25D、128.174.5.6.151、C2、在制作SC接头的过程中,当用剥纤钳剥除纤丝涂覆层后,用酒精棉球或醮有酒精的无纺布擦试纤丝不应超过()次。

A、加强构件B、2C、3D、42、B3、故障处理完毕后,应在客户端继续观察()分钟 (重复发生的故障或客户有要求的应适当延长时间),确认故障已经彻底排除,业务恢复稳定后,方能离开。

A、5B、10C、15D、203、A4、设备供电的季度巡检内容包括:供电是否规范安全,()。

若不采用托收电费的情况下,还需要核查电费、抄录电表度数A、是否从机箱下发引入电源线B、是否有被偷漏电C、是否过度弯曲电源线D、是否供电为唯一接入4、B5、如果C类子网的掩码为255.255.255.224,则包含的子网位数、子网数目、每个子网中主机数目正确的是( )A、2,2,62B、3,6,30C、4,14,14D、5,30,65、B6、如果使用大量的连接请求攻击计算机,使得所有可用的系统资源都被消耗殆尽,最终计算机无法再处理合法用户的请求,这种手段属于()攻击。

A、拒绝服务B、口令入侵C、网络监听D、IP欺骗6、A7、要跟踪到达主机的路径,PC机输入的命令是()。

A、tracert mB、rout mC、ping mD、netstat m7、A8、频率变化____的称为漂移。

()A、高于10HzB、低于10HzC、等于10HzD、不等于10Hz8、B9、通常维护中,线路打环测试的目的是A、检查设备的完好性B、检查线路的完好性C、检查线路至设备的完好性D、不清楚9、C10、在Windows操作系统中,“回收站”可以恢复()上使用<Del>键删除的文件或文件夹。

A、软盘B、硬盘C、U 盘D、软盘和硬盘10、B11、故障处理完毕后,应在客户端继续观察()分钟 (重复发生的故障或客户有要求的应适当延长时间),确认故障已经彻底排除,业务恢复稳定后,方能离开。

基于E1接口的简易误码仪的设计与实现

基于E1接口的简易误码仪的设计与实现[摘要]本文针对传统误码测试仪的不足,提出了基于E1接口的简易误码仪的设计与实现,以及其特点与优点,它是一种新型的简易误码仪,使用方便且成本低廉。

[关键词]误码率误码测试仪FPGAE1当今社会风云万变,掌握了就是掌握了财富,因此通信无疑成为人们生活中不可或缺的部分。

而在某些敏感部门,如邮政储蓄、银行、保险、税务、军事,航空航天等,传输的可靠性就显得犹为重要,在数字通信系统传输过程中,无论是设备故障,还是传播衰落、码间的干扰、邻近波道干扰等,都可能造成系统性能变差,信息内容改变,甚至造成通信中断,而其结果都是可以通过码元差错的形式表现出来的。

误码测试仪就是通过检测数据传输系统的误码性能指标,对其系统传输质量进行评估,并反映数据传输设备和其信道工作质量的一个重要设备。

在目前的相关领域,需要检测通信系统的可靠性时,通常用的都是传统误码检测仪,它多为国外产品,虽然检测内容丰富,结果直观,但价格比较昂贵,操作复杂,维修困难,而国内产品又有待于改进,这都给测试工作带来了诸多不便。

另一方面,在电信传输系统中基于E1(2M)单元的传输链路应用非常广泛,我国电信传输网就是以E1作为标准。

此外,它还普遍应用于DDN数据业务、ISDN综合业务,同时也是GSM移动通信网络接口及Abi接口的标准。

在互联网宽带接入技术中,E1也是一种常用的接口方式,相应配套的E1传输设备产品种类的数量也很多,因而对E1传输误码仪的需求量也非常大。

此外,FPGA核心控制技术在通信系统中的已经相当成熟,这使得基于E1接口FPGA简易误码仪的开发成为现实。

该测试仪的优点主要是实现了单程测试,即发射机和接受机处于异地。

它结合FPGA及单片机的结构特点进行编程,在2Mb/基带速率上实现位同步和码同步,用户可以在LCD显示模块上直观的了解信道的误码情况。

一、概述误码测试仪对线路误码测试的方法很多,但是不管使用何种测试仪,其测试的原理是一样的,都有一套收发电路。

Rn参考点纠错前误码率(Pre-FEC)指标分析、主光通道接口参数要求、ROADM级联时的滤波带宽

A A附 录 A(资料性附录)Rn 参考点纠错前误码率(Pre-FEC )指标分析A.1 背景基于50GHz 的N×400Gb/s WDM 系统目前采用常规OSNR 测试方法无法实现在线测试,新的测试方法尚不成熟,给N×400Gb/s WDM 系统继续采用OSNR 指标进行在线运行维护工作将带来不便。

因此有必要引入一种便于在线评估N×400Gb/s WDM 系统性能的辅助指标,以进一步增强N×400Gb/s WDM 系统的运行维护能力。

Rn 参考点纠错前误码率(Pre-FEC BER )是满足上述要求的有效的辅助手段之一。

A.2 理论基础误码率(BER )是衡量一个数字传输系统最本质的参数,但是在低误码率传输系统中,BER 的准确测试需要非常长的时间,使用起来极其不便,因此一般可采用与BER 密切相关的Q 因子进行表征,其定义见式A.1:101-)Q(σσμμ+=Linear ……………………………………………………………….(A.1)式中,μ1和μ0分别表示接收机接收到的“1”和“0”信号的电流/电压平均值,σ1和σ0分别表示接收机接收到的“1”和“0”信号的电流/电压标准差。

对于强度调制光传输系统,在接收机噪声为高斯分布,接收机处于最佳判决和最佳取样等假设条件下,Pre-FEC BER 与Q (Linear )之间近似关系如式A.2:)2)(Q erfc(BER FEC -Pre 21Linear =……………………………………………(A.2)式中,erfc 是互补误差函数。

在高斯噪声近似的带EDFA 的WDM 系统中,在ASE 噪声与信号光偏振方向一致等假设条件下,OSNR 与Q 值之间近似关系如式A.3:eoB B Linear OSNR Linear OSNR Linear 2)(211)()(Q ++=……………………………………(A.3) 式中,B o 和B e 分别表示传输链路末级接收机的光带宽和电带宽。

误码仪培训资料详资料

培训资料第一部分:基础知识1. 常见通信网络电接口1) 数字中继接口:2Mb/s(E1)、155Mb/s、622Mb/s、2.5Gb/s、10Gb/s2) 数据通信接口:G.703 64Kb/s同向、V.24、V.35、RS-449、RS-485、X.21、V.36、EIA-530/530A3) 模拟中继接口:2/4W E&M4) 局间模拟中继接口:FXO(LGE)5) 用户线模拟接口:FXS(LGS)2. 误码的概念误码是指在传输过程中码元发生了错误。

确切地讲,误码是接收与发送数字信号之间单个数字的差错,图中发送和接收序列之差(即模二加)称差错序列。

该序列是最基本和直观的描述。

测量并记录差错序列就能对误码做进一步的分析处理,得出误码指标规范中的各个参数,如误码秒(ES)、严重误码秒(SES)等。

3. 误码检测分类发现差错的所有手段统称差错检测,可分为两大类,在线差错检测和停业务差错检测。

4. 测试判断所依据的ITU规范1)G.821分析数据及指标•统计时间误码率:从开始测试至当前时刻这一时间段内,扣除不可用时间得到的平均误码率。

•1秒周期差错率:在一个测量周期内统计得到的平均误码率。

这一参数的功能是可在测试过程中动态地了解当前线路传输的差错情况,每过1秒数据便重新刷新。

•差错秒(ES):在一秒时间间隔内,至少发生了一个比特差错,则这一秒记为差错秒。

•严重差错秒(SES):可用时间内的严重误码秒计数,如果1秒内的误码率大于或等于10-3,则这1秒判为严重误码秒。

•严重差错秒比(%SES):严重误码秒数与可用时间的百分比率。

•差错秒比(%ES):可用时间内的误码秒数与可用时间的百分比率。

•劣化分(DM):可用时间内的劣化分记数,劣化分定义:误码率大于或等于10^-6的秒累加到60秒时,记为1个劣化分,其中不包括严重误码秒。

•劣化分比(%DM):劣化分与可用时间扣除严重误码秒后的时间的百分比。

误码率测试电路设计

误码率测试电路设计题目名称: 误码率测试电路设计目录一、设计内容及要求 .................................................2 1.1设计内容 (3)1.2设计要求 (3)二、设计方案 (3)三、系统的硬件设计 (3)3.1误码率检测电路的设计 (3)3.1.1FPGA芯片的介绍 (4)3.1.2FPGA电路的具体实现 (4)3.2 CPU模块的设计 ............................................... 4 3.3 8255扩展模块的设计 ........................................... 7 3.4数码管显示模块的设计 ......................................... 10 四、系统软件设计 .................................................. 114.1FPGA部分的设计 (11)4.1.1误码检测电路的设计 (11)4.1.2 误码率测试电路的仿真和调试 (13)4.2 单片机部分的设计 (14)4.2.1数据处理模块 (14)4.2.2显示模块 (15)五、心得体会 (16)六、参考文献 (17)一、设计内容及要求1.1设计内容实现一个误码率测试电路。

误码率=接受出现差错的比特数/总的发送的比特数。

在数字通信中,必须在数字信号序列中插入标示码,否则接收端将无法识别数字序列中每个字符或一帧的起始码元位置。

对于接收端来说,信息序列是随机的,不可预知的,但帧同步码则是已知的,所以可以通过检测帧同步码的错码情况来确定整个系统的误码率。

1.2设计要求本系统的核心单元是误码率测试电路,误码测试主要是检测同步头的误码个数,这部分用FPGA来实现,要求数据的速率为19.2Mb/s,同步头为7个128位的伪随机码。

通信系统误码测试

通信系统误码测试一.实验目的1.学习误码仪使用方法2.学习通信系统误码率测试方法二.实验仪器1.RZ8621D实验箱1台2.20MHz双踪示波器1台3.误码仪一台(推荐误码仪型号为RZ88521)三.实验电路连接及误码仪简介误码率是数字通信系统重要的质量指标,误码仪发数据和收数据通常是位于通信系统中发信端与收信端,并且两端之间信号无论经过各式各样的变换或传输,但对这两个测试端点而言信号应呈现“透明”状态。

这是选择测试点必须考虑的。

本实验箱误码率的测试点可选为:FSK调制输入与FSK解调输出;PSK调制输入与PSK调制输出;AMI/HDB3码编码输入与译码输出等。

使用误码仪另一主要因素是如何选择时钟,一般有内时钟和外时钟,用实验箱实验时,外时钟可接实验箱时钟,或将收发时钟接在一起。

若被测系统有时延,则收时钟应接在接收端的时钟提取输出。

下面我们给出FSK、PSK误码测试方框图。

S03误码仪测试时钟输出S04误码仪测试数据输入FSK/PSK系统误码仪发数据发时钟收时钟收数据外时钟TP910/TP705或TP70710-1外时钟同步误码测试连接方框图10-2 内时钟同步误码测试连接方框图四.实验内容及步骤(一)FSK 外时钟同步误码测试1.打开实验箱右侧电源开关,电源指示灯亮。

2.按外时钟同步误码测试方框图将误码仪与实验箱连接:误码仪外时钟接实验箱S03;误码仪发数据接实验箱S04;误码仪收数据按TP910或TP707。

3.K703位于FDATA。

4. 薄膜键盘选择9:误码测试,再选择01FSK后按“确认”液晶屏显示9:误码测试01 FSK。

5. 打开误码仪电源开关,误码仪发码率置于2K,一般采用伪随机码,按下测量、则从误码仪屏幕可读出误码。

(此处尚须补充)(二)PSK外时钟同步误码测试该项目测试方法与上相似,不同的是(1)薄膜键盘应选择9:误码测试02FSK;(2)当收码测试点选择TP707时,K703置于PDATA;(3)误码仪发数据速率应选为2KHz或32KHz.(三)内时钟同步误码测试该项测试除电路连接与上述(一)、(二)略有不同外,则其它方法均相同,电路连接是将误码仪外同步与实验箱S03断开,并且发时钟与收时钟相连即可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大连民族学院本科毕业设计(论文)误码率在线测试电路设计学院(系):机电信息工程学院专业:电子信息工程学生姓名:佟贵滨学号:04021618指导教师:李春杰评阅教师:完成日期:2008年6月15号大连民族学院摘要由于种种原因数字信号在传输过程中不可避免地会产生差错,本文设计一误码率在线测试电路。

它可以有效的检测通信系统的可靠性。

本文介绍了通信系统中帧同步的相关概念及其捕捉的方法,对误码率测试系统的基本原理进行了分析,提出了误码率测试系统的设计方案。

本系统主要有FPGA和单片机两部分。

用FPGA芯片实现了误码率测试的检测电路,用AT89S52单片机实现了误码率在线测试电路的主控部分,将FPGA的高可靠、高速的特点与单片机良好的数据处理和控制管理能力结合起来,使整个系统具有了良好的性能。

FPGA主要用MAX+plusⅡ为软件平台,基于FLEX10K芯片,通过硬件描述语言VHDL,采用自顶向下的设计流程完成误码的检测,并进行了时序仿真及调试,结果正确。

这部分是本系统的核心。

单片机主要完成误码率测试系统的数据的算法处理和实时显示的功能。

其次单片机还起主控的作用,将误码率测试系统的其他模块连接起来。

关键词:误码率;现场可编程逻辑门阵列;帧同步AbstractDue to various reasons digital signal transmission in the process inevitably will produce errors, the paper design of a bit-error rate online test circuit. It can effectively test the reliability of communications systems.This paper describes the communication system in the frame synchronization of related concepts and methods of capture, the bit error rate testing system for the basic principles of the analysis, the bit-error rate test system design. This system is mainly a FPGA and Single Chip Microcomputer in two parts. FPGA chip with a bit error rate testing of the detection circuit, with AT89S52 Single Chip Microcomputer the bit-error rate online test circuit main section, the FPGA will be highly reliable, high-speed MCU and the characteristics of a good data-processing and control Ability to integrate the management, so that the whole system is a good performance.FPGA main MAX + plus Ⅱfor the software platform, based on FLEX10K chips, hardware description language VHDL, a top-down design process to complete the error detection, and the timing simulation and debugging, the results correct. This part is the core of the system. Single Chip Microcomputer to complete the main test system bit error rate of data processing algorithms and real-time display functions. This was followed by Single Chip Microcomputer also has the role of control, the bit-error rate testing system linking the other modules.Key Words:bit-error; FPGA; frame synchronization目录摘要 (I)Abstract (II)1 绪论 (1)1.1 课题介绍 (1)1.2 FLEX10K芯片 (1)1.3 VHDL语言 (2)1.4课题的主要内容 (3)2 误码率测试的原理 (4)2.1误码率的概念 (4)2.2 帧的概念 (4)2.3 帧同步码插入和捕捉的方法 (5)2.4 同步状态保护和搜捕过程校核 (6)2.4.1同步状态的保护 (6)2.4.2 搜捕过程校核 (6)3 误码率测试系统的硬件实现 (8)3.1系统的总体设计方案 (8)3.2误码率检测电路的设计 (8)3.2.1 FPGA芯片介绍 (8)3.2.2 FPGA电路的具体实现 (9)3.3 CPU模块的设计 (10)3.3.1 AT89S52功能简介 (10)3.3.2 单片机最小系统的实现 (13)3.4 8255扩展模块的设计 (14)3.4.1 8255芯片的结构 (14)3.4.28255的端口选择和控制字 (16)3.4.3 扩展电路的电路的具体实现 (17)3.5数码管显示模块的设计 (17)4 软件设计 (19)4.1 FPGA部分的设计 (19)4.1.1 误码检测电路的设计 (19)4.1.2 误码率测试电路的仿真和调试 (20)4.2 单片机部分的设计 (22)4.2.1数据处理模块 (22)4.2.2显示模块 (23)结论 (25)参考文献 (26)致谢 (27)1 绪论1.1 课题介绍在一些电磁环境比较恶劣的情况下,一些大规模集成电路常常会受到干扰,导致不能正常工作。

特别是像RAM这种利用双稳态进行存储的器件,往往会在强干扰下发生翻转,使原来存储的"0"变为"1",或者"1"变为"0",造成的后果往往是很严重的。

例如导致一些控制程序跑飞,存储的关键数据出错等等。

现在,随着芯片集成度的增加,发生错误的可能性也在增大。

在通信系统的设计实现过程中,都需要测试系统的误码性能。

而常见的误码率测试仪多数专用于测试各种标准高速信道,不便于测试实际应用中大量的专用信道,并且价格昂贵,搭建测试平台复杂。

随着大规模集成电路的迅速发展,FPGA 在保持其集成度高,体积小,功耗低,性价比高特性的同时能够实现越来越复杂设计功能,日益广泛的应用于通信设各的设计实现。

FPGA (Field Programmable Gate Array)技术是近几年发展起来的新型电路实现技术。

它是一种将门阵列的通用结构与PLD的现场可编程特性结合于一体的新型器件,具有集成度高、通用性好、设计灵活、编程方便等多方而的优点。

用FPGA实现专用电路,不仅可以实现某些特殊功能,而且还可以简化接口和控制,有利于提高系统的整体性能和工作可靠性,并为进一步实现系统集成创造条件。

[1]1.2 FLEX10K芯片Altera的PLD器件包括APEX20K、Excalibur、Mercury、Stratix、 ACEX1K、FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX3000、Classic等系列。

根据各种器件的比较和实际的应用情况,在本设计中选用FLEX10K系列中的FLEX10KE器件。

FLEX10K是工业界第一个嵌入式的可编程逻辑器件,采用可重构的CMOS SRAM工艺,把连续的快速通道互连与独特的嵌入式阵列相结合,同时也结合了众多可编程器件的优点来完成普通门阵列的宏功能。

由于其具有高密度、低成本、低功率等特点,所以脱颖而出称为当今Altera PLD中应用最好的器件系列,其集成度己达到25万门。

它能让设计人员轻松开发出集存储器、数字信号处理器及特殊逻辑包含32位多总线系统等强大功能于一身的芯片。

FLEX10K系列器件主要由嵌入式阵列块、逻辑阵列块、快速通道互连和I/O单元四部分组成,如图1.1所示。

由图可以看出,一组LE构成一个LAB, LAB是排成行和列的,每一行也包含一个EAB。

LAB和EAB是由快速通道连接的。

IOE位于快速通道连线的行列的两端。

图1.1 FLEX10K元器件内的总线总体结构嵌入式阵列由一系列嵌入式阵列块(EAB)构成。

当用来实现有关存储功能时,每个EAB提供2048位用来构造RAM, ROM, FIFO或双口RAM等功能。

当用来实现乘法器、微控制器、状态机以及DSP等复杂逻辑时,每个EAB可以贡献100到600个门,EAB可以单独使用,也可以组合起来使用。

逻辑阵列由一系列逻辑阵列块(LAB)构成。

每个LAB包含八个LE和一些局部互连。

每个LE含有一个四输入查找表(LUT)、一个可编程触发器、进位链和级联链。

八个LE 可以构成一个中规模的逻辑块,如八位计算器、地址译码器和状态机。

多个LAB组合起来可以构成更大的逻辑块。

每个LAB代表大约96个可用逻辑门。

器件内部信号的互连和器件引脚之间的信号互连由快速通道连线提供,快速通道互连是一系列贯通器件长、宽的快速连续通道。

[2]1.3 VHDL语言VHDL是随着可编辑逻辑器件(CPLD)的发展而发展起来的一种硬件描述语言。

现在,VHDL作为IEEE的工业标准硬件描述语言,得到了众多EDA公司的支持,在电子工程领域,己成为事实上的通用硬件描述语言。

VHDL主要用于描述数字系统的结构、行为、功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法和一般的计算机高级语言十分相似。

应用VHDL进行工程设计的优点是多方面的。

1、与其他语言相比,VHDL具有强大的行为描述能力,在EDA上具和VHDL综合器的支持下,可以避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统;2、VHDL中丰富的仿真语句和库函数,使得在任何大系统的设计早期(设计尚未完成),就能查验设计系统的功能可行性,随时可对设计进行仿真模拟;3、VHDL语句的行为描述能力和程序结构决定了它具有支持大规模设计的分解和己有设计的再利用功能;4、对于用VHDL完成的一个确定的设计,可以利用EDA上进行逻辑综合和优化,并自动地把VHDL描述设计转变为门级网表(根据不同的实现芯片)。