SoC系统级软件测试

soc考试仅供参考

由此得到满足条件的测试码为 (x1x 2 x 3 x 4 x 5 ) (100xx), (00xxx)和(0x11x)。

单故障测试矢量:

dF(x) X i s-a-1故障:T1 = x i =1 d x i dF(x) X i s-a-0故障:T0 = x i =1 dx i

例 9-1 求图 9-7 电路 x 2 处存在故障的测试集。 解:由图可得

F(x) x1 * x 2 x1 * x 2

一、 名词解释(35) 1、 Top-down: 自顶向下的设计方法。这是一种从系统概念出发,最终到系统的物理实 现,逐步细化的层次化设计方法。 2、 IP 核:(Intellectual Property) IP core 是已经通过功能验证的设计成果,可以是一个 完整的系统,也可以是一个子系统。表现形式主要是“硬件描述语言”(VHDL 或者 Verilog HDL) 。 3、 ASIC—Application Specific Integrated Circuit,专用集成电路,是一种为专门目的而设 计的集成电路。 4、 HDPLD—High Density Programmable Logic Device, 高密度可编程逻辑器件。是 IC 制造 商大批量生产的半定制产品,规模从几十门到数百万门不等(宏单元) 。主要用于小 批量生产和系统功能的验证。 5、 Water-fall model:即瀑布模型。它将软件的生存周期的各项活动规定为按固定顺序连 接的若干工作阶段,方案从一个阶段转移到另一个阶段,从不回到之前的状态,形 如瀑布。 6、 Spiral model: 在螺旋模型中,设计团队同时进行多个方面的设计,逐渐地提高各自 设计部分的完整度。 (In the spiral model, the design team works on multiple aspects of the design simultaneously, incrementally improving in each area as the design converges on completion.) 7、 Construct by Correction: 通过设计一种允许一个单独的工程师小组以多重迭代进行 设计的体制和一个开发计划,团队能够注意到他们的过失并予以改正,然后在芯片 被最终生产出来之前,再多次改善设计。团队把这个迭代和改进的过程称 作 “construct by correction”。 By designing an organization and a development plan that allowed a single group of engineers to take the design through multiple complete iterations, the team was able to see their mistakes, correct them, and refine the design several times before the chip was finally released to fabrication. The team called this process of iteration and refinement “construct by correction.” 8、 Locality: 即本地化, 当你知道到哪里去查找问题时,问题是最容易被发现和解决的。 在缩短设计时间和提高设计质量方面,使时序和验证问题本地化远比使它们处于全 局状态会获得更大的收益。仔细的模块和接口设计是本地化的根本。 9、 System On Chip 简称 SOC:系统集成芯片—将数据采集、数据处理、数据输出集成在 一片半导体芯片上。是以功能 IP 核为基础的系统模块和电路的综合。

如何搭建SoC项目的基本Testbench(eetop)

先啰嗦几句。

其实老早就想写这个帖子,自己犯懒一直木有写。

前阵子写了一个初版,然后发给了几个做验证的朋友看了看,普遍反映没看明白. 说是我写的东西和我搭的环境结合的太过紧密了,不结合代码,理解的不透彻。

可惜代码是公司的,我不能把代码发出来。

我后来写了一个带很多代码截屏的版本,但是很抱歉没法发到论坛上来。

我个人觉得下面的文字已经能表达我的想法和思想了,希望能对帖的有一点帮助吧。

---------------------------------------------写这个文档的目的是让大家对搭建SoC项目的Testbench有一个比较清晰的认识,可以根据这个文档来一步一步的搭建起一个SoC项目的基本的testbench。

本文档重点是指导大家搭建基本环境,以及能解决搭建Testbench过程中容易遗漏的问题或者容易遇到的“地雷”。

我搭的SoC项目的testbench会有一些相对特殊的点:1)要有嵌入式的软件。

这里包括两部分,一是初始化的bootloader(一般是固化在rom或者存放在外部的flash里),一是boot起来以后放在外部易失性存储介质上的应用层的程序。

2)正常启动起来(一级boot可以切到应用程序了)以后,为了简化流程,我们要使用ISS的环境。

--- 这是比较特殊的一个点3)环境主要脚本的维护和修改。

主要是单个仿真和批量仿真(regression)核心脚本4)为了优化仿真和编译速度,我们要能把不用的模块dummy掉。

5)文件列表的处理6)SoC软件与Testbench都能访问的“共享空间”的处理7)公用函数的准备,比如根据CPU看到的地址空间直接访问外部DRAM的数组,进行初始化写、数据写和数据读操作。

8)环境变量的维护。

9)Define文件的维护10)DDRC的替换(一个是AXI_SLV_VIP的替换,一个是简单AXI_SLV模型的替换)磨刀不误砍柴工,把需要的东西提前准备好,搭建Testbench就像搭积木一样简单快速了。

soc测试方法

soc测试方法SOC测试方法是一种用于评估软件系统安全性的方法。

它通过模拟真实攻击场景,测试系统的漏洞和弱点,以确保系统在面临各种威胁时能够保持稳定和安全。

在SOC测试中,首先需要确定测试的目标和范围。

这包括确定测试的系统组件和功能,以及测试的时间和资源限制。

然后,测试团队将根据系统的设计和实现文档,分析系统的安全需求和威胁模型,并制定测试策略和计划。

在测试策略中,测试团队将选择合适的测试方法和技术,以评估系统的安全性。

常用的SOC测试方法包括黑盒测试、白盒测试和灰盒测试。

黑盒测试是在没有系统内部信息的情况下进行的,模拟真实攻击者的行为,测试系统的安全性。

白盒测试则是基于系统的内部信息进行的,测试系统的实现是否符合安全标准和最佳实践。

灰盒测试则结合了黑盒测试和白盒测试的特点,既考虑系统的外部行为,又考虑系统的内部结构和实现。

在具体的SOC测试过程中,测试团队将根据测试策略和计划,执行一系列的测试用例和攻击场景。

测试用例是一组输入和预期输出的组合,用于评估系统的功能和安全性。

攻击场景则是模拟真实攻击者的行为,测试系统的弱点和漏洞。

在测试过程中,测试团队将记录和分析测试结果,并根据结果调整测试策略和计划。

测试结果包括系统的漏洞和弱点,以及相应的修复建议。

测试团队还将评估系统的安全性能和可靠性,以确保系统在面临威胁时能够保持稳定和安全。

SOC测试方法是一种评估软件系统安全性的方法,通过模拟真实攻击场景,测试系统的漏洞和弱点。

它是确保系统安全性的重要手段,可以帮助组织保护其信息资产和业务运行的安全。

通过合理的测试策略和计划,以及准确的评估和分析,SOC测试可以提高系统的安全性,并帮助组织及时发现和修复系统中的安全问题。

智能安全操作中心(SOC)的实施与管理

管理原则和策略

明确职责:明确SOC各成员的职责和权限

持续改进:不断优化SOC的管理方法和策略,提高其管理水平

绩效考核:对SOC成员进行绩效考核,激励其提高工作效率和质量

制定流程:制定SOC的日常工作流程和应急响应流程

风险评估:定期对SOC进行风险评估,及时发现并解决潜在问题

培训教育:定期对SOC成员进行培训和教育,提高其技能和素要性和意义

提高企业运营效率

增强企业竞争力

提高企业安全防护能力

降低企业安全风险

智能安全操作中心(SOC)的实施

02

实施前的准备工作

确定SOC的目标和需求

制定SOC的实施计划和预算

培训和选拔SOC团队成员

评估现有安全基础设施和资源

准备SOC的物理和网络环境

确定SOC的监控和响应流程

实施过程中的关键步骤

硬件采购:采购所需的硬件设备,如服务器、网络设备等

需求分析:明确SOC的目标、功能、性能等需求

系统设计:设计SOC的架构、功能模块、接口等

培训与维护:对相关人员进行培训,确保SOC的正常运行和维护

数据整合:整合来自不同系统的安全数据,如日志、告警等

安全监控:监控SOC的运行状态,及时发现和解决问题

智能安全操作中心(SOC)的实施与管理

单击此处添加副标题

汇报人:XX

目录

01

智能安全操作中心(SOC)概述

02

智能安全操作中心(SOC)的实施

03

智能安全操作中心(SOC)的管理

04

智能安全操作中心(SOC)的未来发展

05

智能安全操作中心(SOC)的实践案例

智能安全操作中心(SOC)概述

01

soc验证方法

soc验证方法一、SOC验证方法简介SOC(System on Chip)是指将多个不同的功能模块集成到一个芯片上,形成一个完整的系统。

SOC验证是指对芯片内部各个模块之间的通信、控制和数据传输等进行验证,以确保芯片能够正常工作。

SOC 验证方法包括仿真验证、硬件验证和软件验证等。

二、仿真验证1. 概述仿真验证是SOC设计中最基本的一种验证方法,主要用于检验芯片设计是否符合规范要求,以及各个模块之间的接口是否正确。

仿真验证分为逻辑仿真和时序仿真两种。

2. 逻辑仿真逻辑仿真是通过对芯片设计中各个逻辑单元进行测试,检验其是否符合设计要求。

逻辑仿真主要包括功能仿真和代码覆盖率测试。

(1)功能仿真:通过对芯片设计中各个逻辑单元进行测试,检验其是否能够按照预期完成相应的功能。

(2)代码覆盖率测试:通过对代码进行分析,确定每一行代码被执行的次数,并根据结果来评估测试覆盖率。

3. 时序仿真时序仿真是通过对芯片设计中各个时序单元进行测试,检验其是否能够按照预期完成相应的时序要求。

时序仿真主要包括时序分析和时序约束测试。

(1)时序分析:通过对芯片设计中各个时序单元进行分析,确定其是否能够按照预期完成相应的时序要求。

(2)时序约束测试:通过对芯片设计中各个时序单元进行测试,检验其是否能够按照预期完成相应的时序要求。

三、硬件验证1. 概述硬件验证是指通过搭建硬件平台来验证SOC设计的正确性和可靠性。

硬件验证主要包括原型验证和FPGA验证两种。

2. 原型验证原型验证是指将SOC设计转换为实际的硬件电路,并将其集成到一个完整的系统中进行测试。

原型验证主要用于检验芯片设计是否符合规范要求,以及各个模块之间的接口是否正确。

3. FPGA验证FPGA验证是指将SOC设计转换为FPGA电路,并将其集成到一个完整的系统中进行测试。

FPGA验证主要用于检验芯片设计在实际应用场景下的性能和稳定性。

四、软件验证1. 概述软件验证是指通过编写软件程序来对SOC设计进行测试。

SoC可测性设计与测试概述知识讲解

S o C可测性设计与测试概述SoC可测性设计与测试概述Summarization for DFT and test of SoCBy MYJY2012-4 in NJ摘要:本文简述了SoC的可测性设计的意义,以及SoC测试相关知识,并介绍了一些SoC测试数据压缩的方法,旨在对SoC的测试有更好更全面的了解。

关键词:SoC,可测性设计,测试,压缩Abstract:This paper present the significance of DFT and knowledge related to SoC test. It also introduce several data compression techniques. As a result, we can learn more about SoC test.Key words:SoC,DFT,test,compression1 引言随着社会与科技的不断发展,VLSI(Very Large Scale Integration)复杂程度不断提高尺寸也日益缩小,VLSI的设计与测试也愈发受到关注。

SoC(System on chip)作为集成电路发展的必然趋势,确保其有效性也作为VLSI发展的一个愈发重要的课题,所以SoC测试在产品的整个开发过程中也占据了越来越重要的地位。

2 Soc定义SoC的定义多种多样,通常具有采用深亚微米DSM技术、IP核复用、软硬件协同设计这三个特征。

Soc结构应用越来越广泛,其基于核的设计复用技术大大提高了复杂的电子系统的设计效率,所以SoC 也是集成电路未来发展的趋势。

3 SoC可测性设计3.1 SoC可测性设计的必要性相较于传统的IC设计,SoC具有多个不同的的特点:(1)SoC由数量级高达百万甚至更多的元器件组成,电路结构复杂,设计起点比普通ASIC高,需采用数模混合方法验证。

(2)SoC一般使用深亚微米甚至超深亚微米(VDSM,<0.25μm)技术进行生产,延迟成为必须考虑的因素,加上线间和层间由于间隔很小而导致耦合作用增强等各方面因素,设计验证变的相对困难。

基金委员会信息科学二处(原计算机科学学科)资助面上项目一览表

2004年国家自然科学基金委员会信息科学二处(原计算机科学学科)资助面上项目一览表批准号项 目 名 称负责人 单 位 资助金额(万元) 类别60403001 基于非线性动力学的DNA 计算研究张强大连大学24青年基金 60403002 研究DNA 计算机编码理论的一种新方法-模板框方法刘文斌 华中科技大学 24 青年基金60403003 基于相变现象的算法设计与难解实例构造研究 许可 北京航空航天大学 24 青年基金 60403004 量子密码协议与量子纠错码研究 马智 中国科学院研究生院 23 青年基金 60403005 高保障分布式数字签名技术的研究 王宏中国科学院研究生院5 青年基金 60403006 分布式系统的脆弱性模型研究 连一峰 中国科学院研究生院 20 青年基金 60403007 基于双线性对的密码体制的研究张方国中山大学23青年基金 60403008 基于迭代神经网络的复杂结构模式的表示与分类方法研究王庆 西北工业大学 23 青年基金60403009 一阶谓词Bayes 网理论研究及实验系统实现 邢永康 重庆大学 7 青年基金 60403010 指纹识别算法中图像采集设备无关性问题的研究 尹义龙 山东大学 22 青年基金 60403011 基于新小波的图形特征表示与提取尤新革 湖北大学 22 青年基金 60403012 具有较小空间复杂性的交替式下推自动机的研究徐建良中国海洋大学22青年基金 60403013 共代数方法及其在形式化描述和验证软件体系结构中的应用周晓聪 中山大学 6 青年基金60403014 面向Internet 应用的自省软件协同技术研究 马晓星 南京大学 21 青年基金 60403015 知识驱动的自动化程序理解方法与支持系统研究 张路 北京大学 22 青年基金 60403016 测试用例集优化约简技术的若干问题研究聂长海东南大学 25青年基金 60403017 动态二进制翻译及优化中低开销技术的研究武成岗中国科学院计算技术研究所22青年基金 60403018 基于语言模型的图像数据库自动语义标注及多模式检索研究周向东 复旦大学 21 青年基金60403019 数据库物理存储布局优化及其自动设计技术研究 王晓玲 复旦大学 24 青年基金 60403020 基于本体和约束理论的统一时空数据模型研究 金培权 中国科学技术大学24 青年基金 60403021 面向大规模流数据的完备性挖掘方法研究 靳晓明 清华大学 23 青年基金 60403022 基于反射机制的在线自适应编译优化系统研究戴桂兰清华大学 5青年基金 60403023 网格运行时结构—网格进程的研究 刘淘英 中国科学院计算技术研究所 23 青年基金60403024 虚拟流媒体存储系统理论和实现技术研究吴松华中科技大学 5青年基金 60403025 面向计算密集型算法的实时可重构专用体系研究江先阳中国科学院计算技术研究所 26 青年基金60403026 单芯片多处理器容错设计模型及其可信性评价研究 姚文斌 清华大学 24 青年基金 60403027 基于多自治域的信息交换风险评估模型研究李瑞轩华中科技大学23青年基金 60403028 基于网络流量的DDoS 安全防御体系与关键技术研究杨新宇西安交通大学26青年基金60403029 基于移动Agent 的网格监控体系结构及关键技术研究唐亚哲 西安交通大学 24 青年基金60403030 应用驱动的软件中间件自适应方法与关键技术研究 黄罡北京大学21 青年基金 60403031 P2P 网络资源定位研究谢高岗 中国科学院计算技术23青年基金研究所60403032 匿名通信理论、方法与关键技术研究王伟平 中南大学 25 青年基金 60403033 基于蠕虫对抗的internet 蠕虫主动遏制的研究 云晓春 哈尔滨工业大学 23 青年基金 60403034 P2P 网络模型研究及应用邓倩妮 上海交通大学 21 青年基金 60403035 服务质量路由的无连接层次化体系结构研究 崔勇 清华大学 22 青年基金 60403036 数字人工程中数据分割和带约束的拟合问题研究 王铠 山东经济学院 25 青年基金 60403037 运动数据的艺术化合成与编辑 费广正 北京广播学院 20 青年基金 60403038 基于视频的全景人体动画王进 浙江大学 21 青年基金 60403039 移动图形计算中的若干关键问题研究与应用王建民中山大学 23 青年基金 60403040 基于医学图象序列的心脏运动和材料特性鲁棒估计 刘华锋 浙江大学 25 青年基金 60403041 面向隐私保护的数据挖掘方法研究童云海北京大学 22青年基金 60403042 基于布料运动实例数据的虚拟人服装动画方法研究 夏时洪中国科学院计算技术研究所 23青年基金60403043 面向大规模视频服务的自适应存储体系研究 刘鹏 中国人民解放军理工大学 23 青年基金60403044 3D 动态数字遮片技术研究 肖双九 上海交通大学 21 青年基金 60403045 稳健数字图象水印的研究康显桂 中山大学 23 青年基金 60403046 基于森林动态生长模型的虚拟仿真研究 范菁 浙江工业大学 24 青年基金 60403047 多种条件下自动插值方法的研究雍俊海清华大学 22青年基金 60403048 SOC 系统级功能验证关键技术研究李暾 中国人民解放军国防科学技术大学 24 青年基金60403049 面向内容检索的三维实体模型相似评价研究刘玉生浙江大学 23青年基金 60403050 基于本体的中文网络信息结构化研究 王挺 中国人民解放军国防科学技术大学 26 青年基金60463001 不可满足公式的结构以及证明方法的研究 许道云 贵州大学 22 地区基金 60463002 软件演化过程研究李彤 云南大学 23 地区基金 60463003 多数据库挖掘的模式发现系统群张师超广西师范大学23地区基金 60463004 “三江并流”代表性植物空间数据仓库及其多样性研究王丽珍 云南大学22地区基金60463005 现代维语信息处理技术方法和信息库构造研究 玉素甫.艾白都拉 新疆师范大学 25 地区基金60473001 动态变化网络路由协议理论及关键技术张宏科北京交通大学 25自由基金 60473002 基于运动库检索和视频分析的三维人体运动重构 李锦涛 中国科学院计算技术研究所 23 自由基金60473003 约束推理与约束程序孙吉贵 吉林大学 23 自由基金 60473004 系统规范表示与验证的认识逻辑途径 苏开乐 中山大学 23 自由基金 60473005 程序及代数结构的逻辑性质王驹 广西师范大学 7 自由基金 60473006 基于进程代数的电子商务协议形式化研究傅育熙上海交通大学 20自由基金 60473007 Petri 网系统合成与性质保持研究 焦莉 中国科学院软件研究所 22 自由基金60473008 三值光计算机的若干关键技术研究 金翊 西北工业大学 24 自由基金 60473009 Domain 理论与拓扑学研究白世忠 五邑大学 7 自由基金 60473010 网络设计经济综合优化问题的算法研究韩军北京航空航天大学23自由基金60473011 若干幻方新问题的理论及应用研究 谢涛 中国人民解放军国防科学技术大学 26 自由基金60473012 蚁群算法并行化、收敛性和新型模型研究 陈崚 扬州大学 6 自由基金 60473013 NP 类问题的共性与个性探索 陈镜超 东华大学 21 自由基金 60473014 动力学演化算法的理论及其应用研究 李元香 武汉大学 22 自由基金 60473015 高性能计算中的快速算法及其应用研究 施保昌 华中科技大学 23 自由基金 60473016 信息隐藏分析理论与技术研究 钮心忻 北京邮电大学 5 自由基金 60473017 密码研究中的几个编码问题 裴定一 广州大学 22 自由基金 60473018 图上的纠错码研究唐元生 扬州大学 24 自由基金 60473019 信息安全中的密码体制理论与应用研究 郑志明 北京大学 23 自由基金 60473020 基于统计力学方法的公钥密码系统研究郑东上海交通大学 22自由基金 60473021 可证安全理论研究与椭圆曲线密码体制设计祝跃飞中国人民解放军信息工程大学 24 自由基金60473022 信息伪装安全性理论与隐写分析技术研究 平西建 中国人民解放军信息工程大学 22 自由基金60473023 网络容侵机制与算法研究王丽娜 武汉大学 5 自由基金 60473024 网络信息安全协议的形式化分析和验证研究 王卫红浙江工业大学23 自由基金 60473025 多重伪随机序列的复杂度研究 戴宗铎 中国科学院研究生院 22 自由基金 60473026 密码系统的适应性安全叶顶锋 中国科学院研究生院 22 自由基金 60473027 电子拍卖系统的关键安全技术研究 王育民 西安电子科技大学 24 自由基金 60473028 流密码中若干重要问题的研究 肖国镇 西安电子科技大学 25 自由基金 60473029 新型快速公钥密码的设计与安全性分析 胡予濮 西安电子科技大学23 自由基金 60473030 面向群的分布式网络密钥管理 何明星 西华大学 23 自由基金 60473031 软件容错测量理论与技术研究张大方湖南大学23 自由基金 60473032 基于规范和程序输入域分析的软件测试数据生成方法研究赵瑞莲北京化工大学23自由基金60473033 软硬件可测性设计新途径——软硬件交互式测试及可测性设计研究徐拾义 上海大学 20 自由基金60473034 关于神经网络结构复杂性与本质逼近阶研究 曹飞龙 绍兴文理学院 23 自由基金 60473035 增强型线性判别分析及其推广性研究 陈松灿 南京航空航天大学23 自由基金 60473036 面向多Agent 系统模型检测的逻辑和算法 曹子宁北京大学18 自由基金 60473037 动态环境下优化问题的演化计算方法曾三友 中国地质大学(武汉)5自由基金 60473038 基于矢量熵运动约束及非规则多分辨率Gibbs 场的3-D 弹性体运动估计汪亚明 浙江理工大学 22 自由基金60473039 大规模多姿态人脸图像库的两步识别方案研究 金忠 南京理工大学 24 自由基金 60473040 超并列模式分类器的问题分解与模块集成研究 吕宝粮 上海交通大学 22 自由基金 60473041 基于哼唱输入的音乐检索系统关键技术的研究 吴亚栋 上海交通大学 5 自由基金 60473042 应对规划研究谷文祥东北师范大学 22自由基金 60473043 人脸主动网格模型方法研究崔国勤中国科学院计算技术研究所21 自由基金60473044 基于广义粒子模型的分布并行智能处理的理论和方法帅典勋 华东理工大学 23 自由基金60473045 加权模糊规则的泛化能力研究王熙照河北大学18自由基金60473046 多标记学习的研究 周志华 南京大学 20 自由基金 60473047 光线变化下的人脸表示方法研究 王阳生 中国科学院自动化研究所23自由基金60473048 凸区域提取的动态内核投票方法杨青 中国科学院自动化研究所 5 自由基金60473049 基于立体视觉的动态手势识别与语义描述方法 贾云得 北京理工大学 23 自由基金 60473050 面向agent 的需求工程赵建民浙江师范大学24自由基金 60473051 面向海量移动数据挖掘的过程神经网络算法与应用研究杨冬青 北京大学 23自由基金60473052 普适计算中的网格接入:轻量级Portal 、动态协同及语义支持李善平 浙江大学 22 自由基金60473053 程序行为控制的语义约束方法研究 曾庆凯 南京大学 23 自由基金 60473054 软件可靠性与安全性综合评估方法研究 赵明 贵州大学 25 自由基金 60473055 感知时间和情景的存取控制策略建模与实施 虞慧群 华东理工大学 23 自由基金 60473056 余代数及其在软件方法学中的应用张乃孝北京大学 22自由基金 60473057 基于进程代数的复杂安全协议的形式化分析与验证 李舟军中国人民解放军国防科学技术大学23自由基金60473058 基于Petri 网的工作流系统构造技术与验证方法研究张世琨 北京大学 5 自由基金60473059 软件构架库的组织管理原理和应用支持机制研究谢冰北京大学 22自由基金 60473060 基于组织实体能力的软件过程建模方法研究 王青 中国科学院软件研究所 22 自由基金60473061 动态软件体系结构建模技术研究 赵文耘 复旦大学 23 自由基金 60473062 基于本体的软件构件描述与检索方法 钱乐秋 复旦大学 22 自由基金 60473063 程序理解中特征挖掘理论与方法的研究 陈平 西安电子科技大学6 自由基金 60473064 元模型理论与建模方法研究邵维忠 北京大学 22 自由基金 60473065 基于新型程序切片的质量软件控制关键技术研究 李必信 东南大学 24 自由基金 60473066 基于反射机制的软件体系结构重用方法研究 应时 武汉大学 24 自由基金 60473067 基于测试的构件软件系统可靠性评估技术研究 白成刚 北京航空航天大学 24 自由基金 60473068 类型论在软件安全方面的应用研究 陈意云 中国科学技术大学 5 自由基金 60473069 网格环境下数据库信息检索新技术研究 王珊 中国人民大学 22 自由基金 60473070 高性能多种结构类型的数据索引模型的研究胡运发复旦大学22自由基金 60473071 基于基因表达式编程(GEP)的知识发现核心技术研究唐常杰 四川大学 23自由基金60473072 面向多维数据的自动导航和知识发现的理论与方法研究谭少华 北京大学 23自由基金60473073 支持嵌入式计算的非线性实时数据流管理技术的研究于戈 东北大学 25 自由基金60473074 自适应的P2P 数据集成系统关键技术研究 王国仁 东北大学 5 自由基金 60473075 传感器网络数据管理关键技术的研究李建中 哈尔滨工业大学 24 自由基金 60473076 面向Internet 的统一代理模型、方法与系统研究 彭智勇 武汉大学 5 自由基金 60473077 水印关系数据库关键技术研究王建民 清华大学 22 自由基金 60473078 基于信息过滤的个性化服务理论和技术研究邢春晓清华大学24自由基金60473079 同时多线程超长指令字DSP 的体系结构关键技术研究陈书明中国人民解放军国防科学技术大学 24自由基金60473080 多维可扩展自适应流体系结构研究 张春元 中国人民解放军国防科学技术大学 5 自由基金60473081 动态多目标TSP 的并行算法研究康立山 武汉大学 20 自由基金 60473082 Internet 中覆盖网络应用支撑环境的研究徐恪清华大学25自由基金 60473083 面向下一代网络的管理信息访问算法和存储策略研究张金祥 清华大学 21 自由基金60473084 移动IP 无缝切换技术研究李未 北京航空航天大学 22 自由基金 60473085 网络计算环境下的接入控制与负载调度策略 谭连生 华中师范大学 23 自由基金 60473086 应用层支持的视频组播系统中安全传输的理论研究尹浩清华大学23自由基金 60473087 基于应用层组播的流媒体系统设计和在Internet中的实验研究邓北星 清华大学 24 自由基金60473088 基于节点自治的完全分布式网络计算模型杨愚鲁南开大学5自由基金 60473089 下一代互联网中支持ABC 的公平自适应智能QoS 感知型路由选择机制的研究 王兴伟 东北大学 5 自由基金60473090 对等网络中的分布式路由技术研究 秦志光 电子科技大学 24 自由基金 60473091 电子市场匹配模型与算法研究 王红兵 东南大学 26 自由基金 60473092 网格环境下事务处理技术的研究李明禄 上海交通大学 21 自由基金 60473093 操作系统的安全结构及其在单向网关上的应用 黄皓 南京大学 23 自由基金 60473094 网格程序层次模型及其理论 蒋昌俊 同济大学 24 自由基金 60473095 网络计算的作业调度方法研究李廉兰州大学 26自由基金 60473096 基于MEANS 结构的网络服务器平台的研究 雷迎春 中国科学院计算技术研究所 23 自由基金60473097 移动网络中移动台智能跟踪策略及路由优化研究 朱艺华 浙江工业大学 24 自由基金 60473098 基于软件再生的中间件运行时环境关键问题研究 齐勇 西安交通大学 23 自由基金 60473099 网格应用程序执行性能的实时监控和预报胡亮吉林大学23自由基金 60473100 普适计算中基于上下文感知的个性化智能人机交互研究王衡 北京大学 23 自由基金60473101 自主分布式网络存储关键技术研究 舒继武 清华大学 23 自由基金 60473102 计算机产生体视全息图的研究韦穗安徽大学24自由基金 60473103 面向图案创新设计的非真实感绘制理论与方法的研究孟祥旭 山东大学 22 自由基金60473104 矢量场分割、聚类与降维研究沈一帆复旦大学 23自由基金 60473105 基于深度图像的复杂虚拟场景的自动建模与绘制 吴恩华 中国科学院软件研究所 25 自由基金60473106 点云曲面的数字拓扑与几何的若干基础问题研究 张三元 浙江大学 23 自由基金 60473107 体数据可视化中传输函数的研究 林海 浙江大学 23 自由基金 60473108 三维图形学中若干关键问题的研究刘勇奎大连民族学院7自由基金 60473109 面向公共安全的人群行为建模及虚拟人群仿真技术研究纪庆革 中山大学 23自由基金60473110 基于植物生长模型的森林景观演变模拟及其应用 张晓鹏 中国科学院自动化研究所25自由基金60473111 三维几何模型水印技术的研究 潘志庚 浙江大学 24 自由基金 60473112 计算机图形学中的GPU 计算技术研究秦开怀 清华大学 24 自由基金 60473113 分布式虚拟环境中可扩展主动兴趣管理技术研究潘金贵南京大学22自由基金 60473114 多元有理插值与逼近的理论、方法及其在图形图象中的应用研究檀结庆 合肥工业大学 23 自由基金60473115 循证医学信息化的智能技术研究鲁明羽清华大学 21自由基金 60473116 卫星云图与降水关系的发现与挖掘研究 李国辉 中国人民解放军国防科学技术大学 22自由基金60473117 视频高层语义的自动提取与挖掘技术研究吴玲达 中国人民解放军国防科学技术大学21自由基金60473118 基于脊椎疾病的医学图像数据挖掘技术和可视化研究潘旌红 复旦大学 19 自由基金60473119 真实场景与虚拟物体混合的增强视频技术研究吴成柯西安电子科技大学24自由基金 60473120 基于运动神经控制机理的人机手写技能的复制和再生研究王国利 中山大学 24 自由基金60473121 虚拟耳显微手术关键技术的研究与实现 谢叻 上海交通大学 20 自由基金 60473122 中国Web Graph 的挖掘与应用研究 俞勇 上海交通大学 23 自由基金 60473123 迁移工作流模型理论和系统方法研究 曾广周 山东大学 5 自由基金 60473124 Norm 驱动的虚拟组织关键技术研究 顾宁 复旦大学 22 自由基金 60473125 沉积微相划分中知识发现机理的研究李国和石油大学(北京)24自由基金 60473126 解空间平滑及其在片上系统布图规划和互连资源规划中的应用研究董社勤 清华大学 23 自由基金60473127 三维“点云”模型碰撞检测问题的研究屠长河山东大学 23自由基金 60473128 中国数字化可视人体分割数据集的建立 张绍祥 中国人民解放军第三军医大学 22 自由基金60473129 个性化三维服装的多层次联动参数化建模方法研究 陆国栋 浙江大学 21 自由基金 60473130 CAD 中的极小曲面与优化方法的研究 汪国昭 浙江大学 23 自由基金 60473131 织物热湿传输仿真模型研究王若梅 中山大学 24 自由基金 60473132 动态隐式曲面重构技术及其应用的研究冯玉瑜中国科学技术大学24自由基金 60473133 基于准LIGA 技术的MEMS 制造误差修正方法计算机仿真研究郑津津 中国科学技术大学 24自由基金60473134 基于知识进化的多层次结构产品整体方案创新设计技术郝博 沈阳工业学院 7自由基金60473135 面向信息处理的现代藏语语法属性库研究 江荻 中国社会科学院民族研究所 25 自由基金60473136 面向非结构化文本的领域知识获取方法的研究 郑庆华 西安交通大学 22 自由基金 60473137 新疆维、哈、柯文印刷字符识别研究哈力木拉提新疆大学23自由基金 60473138 基于汉英句对库的句子结构推导和翻译模板获取研究王厚峰 北京大学 23自由基金60473139 大规模中文文本语料库分词与词性标注一致性检验技术研究郑家恒 山西大学 23 自由基金60473140 基于内容分析的话题检测和追踪关键技术研究 朱靖波东北大学23 自由基金 60473141 多维信号的局域波分析与应用研究徐晓刚 中国人民解放军海军24自由基金大连舰艇学院60473142 紧优双环网络及其无限族的研究周建钦安徽工业大学7 自由基金。

soc面试基础知识

soc面试基础知识SOC(System on Chip)是指在一个芯片上集成了处理器核心、内存、外设接口等多个功能模块的集成电路。

SOC技术的发展使得计算机系统可以更加紧凑和高效,广泛应用于各种设备和领域。

在SOC面试中,基础知识是面试官们常常会考察的内容之一。

下面就来介绍一些SOC面试的基础知识。

一、SOC的定义和特点SOC是一种集成电路技术,将多个功能模块集成到一个芯片上。

这些功能模块可以包括处理器核心、内存、外设接口等,可以根据需要进行定制和设计。

SOC的特点是集成度高、功耗低、性能高、体积小等。

二、SOC的应用领域SOC技术已经广泛应用于各个领域,包括消费电子、通信、汽车、工业控制等。

在消费电子领域,SOC被广泛应用于智能手机、平板电脑、智能电视等设备中。

在通信领域,SOC被用于移动通信设备、网络设备等。

在汽车领域,SOC被用于汽车电子系统、车载娱乐系统等。

在工业控制领域,SOC被用于工业自动化设备、机器人等。

三、SOC的体系结构和设计方法SOC的体系结构可以根据应用需求来设计,可以采用单核心、多核心、异构核心等不同的结构。

在设计SOC时,需要考虑功耗、性能、可靠性等因素。

SOC的设计方法有自顶向下和自底向上两种。

自顶向下的设计方法是从系统级需求出发,逐步细化到电路级。

自底向上的设计方法是从电路级出发,逐步组合成系统级。

四、SOC的测试和验证SOC的测试和验证是确保SOC功能正常的重要环节。

SOC的测试可以分为结构测试、功能测试和系统测试等多个层次。

结构测试主要用于检测电路的连通性和正确性。

功能测试主要用于检测SOC的各个功能模块是否正常工作。

系统测试主要用于检测整个SOC系统是否满足设计需求。

SOC的验证可以采用仿真验证、硬件验证和软件验证等方法。

五、SOC的性能和功耗优化在SOC设计过程中,性能和功耗是两个重要的优化指标。

性能优化可以通过优化算法、增加处理器核心数量、增加缓存等方法来实现。

SOC软件设计流程和方法

SOC软件设计流程和方法SOC(System-on-a-Chip)软件设计流程和方法指的是在一个芯片上集成多种功能模块的软件开发流程和方法。

本文将详细介绍SOC软件设计流程和方法,并探讨其优势和挑战。

一、设计流程1.确定需求:明确芯片上集成的功能和性能要求。

这需要与系统设计人员紧密合作,以确保软件设计与硬件设计相互匹配。

2.系统划分:将整个功能划分为多个模块,并确定它们之间的通信方式和接口标准。

3. 开发模块:选择适当的编程语言和开发工具(如C/C++、Python 等),分别开发不同功能模块的软件。

4.软件集成:将所有的软件模块集成到一个整体中,并进行功能和性能测试。

5.调试和优化:通过对整体系统的调试和优化,确保系统的稳定性和高效性能。

6.验证和认证:对整个系统进行验证和认证,以确保符合规定的标准和规范。

二、设计方法1.模块化设计:将整个系统划分为多个模块,每个模块独立开发、调试和测试,降低了系统的复杂性。

2.面向对象设计:使用面向对象的设计方法,将系统中的功能和数据进行封装,提高了系统的可维护性和扩展性。

3.异步通信:由于系统上存在多个功能模块,采用异步通信方式可以提高系统的并发性能和响应能力。

4.软硬件协同设计:与硬件设计团队密切合作,通过软硬件协同设计方法,提高系统的集成程度和性能效率。

三、优势1.简化系统设计:SOC软件设计将多个功能模块集成到一个芯片上,简化了系统设计和开发流程。

2.提高系统性能:通过整合多个功能模块,SOC软件设计可以提高系统的并发能力和运行效率。

3.降低功耗:SOC软件设计可以优化系统的功耗管理和资源利用,提高系统的能效比。

4.提高可维护性:SOC软件设计使用模块化和面向对象的设计方法,提高了系统的可维护性和代码重用性。

四、挑战1.复杂性管理:SOC软件设计需要处理多个功能模块之间的复杂关系,对开发人员的能力和经验要求较高。

2.软硬件协同:软硬件协同设计需要密切合作和沟通,对团队协同能力和沟通能力要求较高。

SoC 测试概念

SoC测试的概念及实例详解本文主要介绍了一个具有可测性设计和可制造性设计的新型单片系统,该系统由硬盘控制器(HDC)、16位微控制器、微控制器使用的程序和数据SRAM以及用8M位DRAM实现的片上缓存组成,再加上时钟综合PLL、带外部旁路晶体管的稳压器使用的片上控制电路组成一个完整的系统。

该器件采用的是0.18μm的铜工艺,与前几代技术相比增加了性能、降低了功耗。

另外,DRAM也采用了深亚微米技术,因此在一个器件中可以包含进一个完整的系统缓存(1MB)以及自动刷新逻辑,而且使用的硅片面积还比以前小。

本文还讨论了DFT和DFM所采取的对策,包括为了实现更快的良品率学习曲线而采用面向分析工具的设计、为减少测试成本而采取的并行测试方法。

DFT和分析存取是通过IEEE 1149.1的JTAG控制器实现的。

除了专门的存储器测试和ATPG扫描外,JTAG控制器还能为组成完整SoC的各个不同单元提供各种测试模式配置。

所采用的设计对策决不是只有唯一一种可能性。

由于存储器在器件中占了45%的硅片面积和86%的晶体管数量,因此需要对存储器加以重点关注。

存储器测试是重点考虑和努力开发的对象。

图1:扫描模式配置。

SRAM有两种测试方法,具体取决于SRAM在系统中的用途:CPU存储器(代码和数据)是通过微控制器进行测试的,需要特殊硬件配置和测试模式的支持;与HDC相关的SRAM采用存储器BIST电路进行测试。

DRAM则通过BI ST控制器进行测试,而DRAM BIST自身利用扫描和ATPG进行测试。

大多数数字逻辑是完全综合过的,而所有数字逻辑都要经过ATPG扫描测试。

另外,象PLL和稳压器控制等模拟电路则采用特殊编制的程序在特殊测试模式下进行测试。

本文首先介绍系统级芯片本身,包括SRAM和嵌入式DRAM,然后简要讨论用于指导DFT和DFM开发工作的分析与生产测试对象,最后阐述了SoC中采取的分析和生产测试对策。

系统级芯片概要为了有助于了解生产测试与分析所采取的对策,首先让我们看一下SoC 的一些细节,当然本文提到的所有性能都需要进行测试。

SOC测试

SOC测试胡瑜韩银和李晓维摘 要 本文介绍芯片系统(System-on-a-Chip, SOC)测试面临的挑战、现有测试技术和未来研究方向。

随着芯片规模按照摩尔定律增长,复用IP(Intellectual Property)核构建SOC逐渐成为芯片设计的主流。

基于IP核的SOC 测试技术受到广泛关注。

本文结合中科院计算技术研究所测试及可信计算课题组开展的研究工作,综述四类IP核的测试技术和SOC测试资源优化技术,介绍两个标准化组织开展的SOC测试标准工作,展望SOC测试的研究方向。

1 SOC面临的挑战1.1 芯片设计规模集成电路制造工艺的进步使芯片上晶体管的数量按照摩尔定律增长,预计将在2010年达到百亿数量级。

如图1所示,每十二个月,芯片的集成度就可提高58%,而设计能力只能提高21%[1],导致芯片制造能力与设计能力的差距越来越大。

为了减小制造与设计之间的差距,必须采用新的设计方法学:通过复用已经过验证的电路功能模块,加上一些自定义逻辑以及胶合逻辑,来构成整个芯片设计,使芯片设计周期大大缩短。

当一块基于电路功能模块复用的单一芯片能实现一个完整的复杂系统时,该芯片就被称为芯片系统。

而那些可复用的经过验证的电路功能模块,则被称为IP核。

由于复用IP核可快速构建系统,因此基于IP核的SOC设计方法一经提出,就得到了集成电路(Integrated Circuits, IC)设计商、电子设计自动化(Electronic Design Automation, EDA)厂商和无晶圆半导体公司(Fabless)的热烈响应。

Dataquest调查表明,2000年SOC的产值占到IC产业产值的11.8%,预计2005年将达到25.3%,即460亿美元。

仅2000年IP核市场的增长率就达到40.1%。

IP 核种类也日渐丰富,例如ARM, MIPS, IBM PowerPC处理器核;SRAM, ROM, Flash, DRAM, CAM (Content Addressable Memory)类型的存储器核;TI, Pine, Oak公司的DSP核;用于外设控制的DMA (Direct Memory Access), MMU(Memory Management Unit), BIU(Bus Interface Unit)核;PCI, USB (Universal Serial Bus), UART(Universal Asynchronous Receiver/Transmitter)接口核;JPEG压缩核和MPEG解码器核等多媒体核;以及以太网控制器核、ATM SAR (Segmentation and Reassembly), MAC(Media Access Control)核等与网络处理相关的核。

信息安全片上系统(SoC)平台技术研究的开题报告

信息安全片上系统(SoC)平台技术研究的开题报告一、背景及意义随着互联网的飞速发展和智能化的深入推进,信息安全问题越来越突出。

安全片上系统(SoC)平台是当前信息安全防护的重要手段之一。

它不仅可以将各种不同安全机制融合到一个芯片中,局部化安全处理,同时还可以实现复杂的安全策略和协议的完整性验证,从而有效地保护了数据和系统的安全。

然而,由于安全片上系统平台的技术复杂性相对较大,虽然目前有很多成熟的方案和平台,但是在实际应用中仍然面临着很多问题和挑战。

因此,对安全片上系统平台的技术研究和探索具有重要的意义和价值。

二、研究内容本次课题的主要研究内容包括:1. 安全片上系统平台的基础原理和技术体系研究,包括芯片架构、信任链、硬件安全、软件安全等相关技术。

2. 安全片上系统平台的设计与实现,包括安全算法的选取、内存管理、引导加载、进程管理等。

3. 安全片上系统平台的综合优化研究,包括功耗优化、性能优化、可靠性优化等。

4. 安全片上系统平台的应用与实践,包括安全芯片、智能终端、物联网设备等领域的应用。

三、研究方法和技术路线本次研究将采用文献调研、理论分析和实验仿真相结合的方法进行。

具体的研究路线如下:1. 阅读相关文献,了解安全片上系统平台的基本原理、发展历程和现状。

2. 分析当前安全片上系统平台存在的问题和挑战,构建研究模型。

3. 设计并实现安全片上系统平台的基本功能,并对其进行测试和验证。

4. 进行综合优化设计,包括硬件算法优化、软件算法优化、功耗优化、性能优化。

5. 在硬件实验平台上进行安全片上系统平台应用场景的测试与实践。

四、预期研究结果通过本次研究,预期得到以下研究成果:1. 掌握安全片上系统平台的基本原理、技术细节和设计方法。

2. 设计和实现一款高效、稳定、安全的安全片上系统平台,具有一定的实用性和推广价值。

3. 发表1~2篇高质量的学术论文或著作。

五、进度安排1. 前期:2022年3月-2022年6月完成文献调研和研究模型构建。

SOC软件设计流程和方法

SOC软件设计流程和方法SOC(System-on-a-chip)软件设计流程和方法是指在SOC系统中进行软件设计和开发的一系列过程。

SOC是一种将处理器核心、存储器、外设等集成到一个芯片上的集成电路技术。

在SOC系统中,软件设计是确保系统正确运行和发挥性能的关键环节。

下面将介绍SOC软件设计流程和方法的具体内容。

1.需求分析:在SOC软件设计的起始阶段,需要明确系统的需求。

这涉及到系统功能需求、性能需求、接口要求等方面的分析。

通过与系统用户和技术团队的沟通,明确系统的功能和目标。

2.系统设计:在需求分析的基础上,进行系统设计。

系统设计包括软件架构设计和通信协议设计两个方面。

软件架构设计是将系统分解为模块,并定义各模块之间的关系和功能。

通信协议设计是定义系统中各模块之间的数据传输方式和协议。

3.模块设计:在系统设计的基础上,进行模块设计。

模块设计是将系统分解为更小的单元,即各个软件模块。

模块设计包括模块功能设计、接口设计和数据结构设计等方面。

4.编码实现:在模块设计完成后,进行编码实现。

编码实现是将模块设计的结果转化为实际的代码。

在编码实现过程中,需要注意代码质量和可读性,以便于后续的测试和维护。

5.调试测试:在编码实现完成后,进行调试和测试。

调试是对系统进行功能验证和故障排除的过程。

测试是对系统进行性能评估和稳定性测试的过程。

通过调试和测试,发现和修复软件中的问题和错误。

6.优化改进:在调试测试过程中,通过性能评估和稳定性测试,发现系统中的瓶颈和问题。

通过优化和改进,提高系统的性能和稳定性。

优化改进的方式包括算法优化、代码优化和系统配置优化等。

7.集成部署:在优化改进完成后,进行系统的集成和部署。

集成是将各个模块组装到一起,并进行接口测试和功能验证。

部署是将系统部署到目标设备上,使得系统能够正常运行。

8.维护升级:在系统部署后,需要进行系统的维护和升级。

维护是对系统进行故障修复和性能监控的过程。

一款高端数字SOC设计的系统级验证

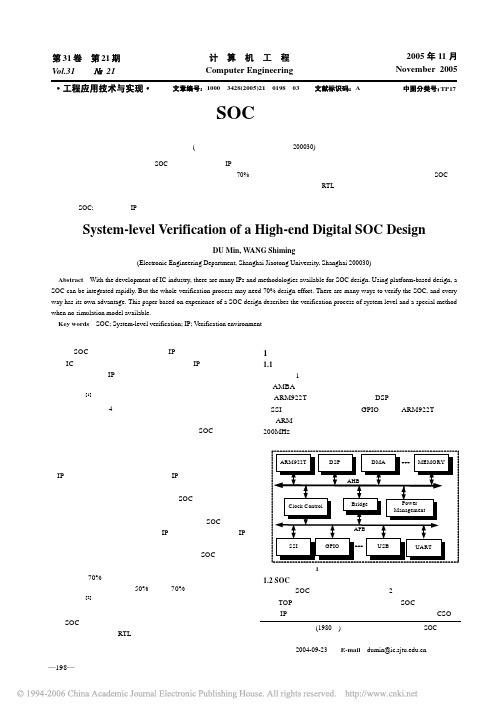

—198— 一款高端数字SOC 设计的系统级验证杜 敏, 王世明(上海交通大学电子工程系,上海 200030)摘 要:集成电路行业的发展,为SOC 设计积累了丰富的IP 库和设计方法。

采用系统设计常用的基于平台的方法,可以快速完成系统的集成。

但要完成对整个系统的验证,可能要占到整个设计周期70%以上的时间。

而验证的方法是具有多样性的。

该文以一款高端SOC 的设计经历,简单描述了系统级验证过程,并以同步串联接口模块为例详细介绍了在系统级对RTL 和门级网表的验证,以及验证所采用的特殊方法。

关键词:SOC; 系统验证;IP ;验证环境System-level Verification of a High-end Digital SOC DesignDU Min, WANG Shiming(Electronic Engineering Department, Shanghai Jiaotong University, Shanghai 200030)【Abstract 】With the development of IC industry, there are many IPs and methodologies available for SOC design. Using platform-based design, a SOC can be integrated rapidly. But the whole verification process may need 70% design effort. There are many ways to verify the SOC, and every way has its own advantage. This paper based on experience of a SOC design describes the verification process of system level and a special method when no simulation model available.【Key words 】SOC; System-level verification; IP; Verification environment计 算 机 工 程Computer Engineering 第31卷 第21期Vol.31 № 21 2005年11月November 2005·工程应用技术与实现·文章编号:1000—3428(2005)21—0198—03文献标识码:A中图分类号:TP17在SOC 的设计中,主要利用了IP 复用技术。

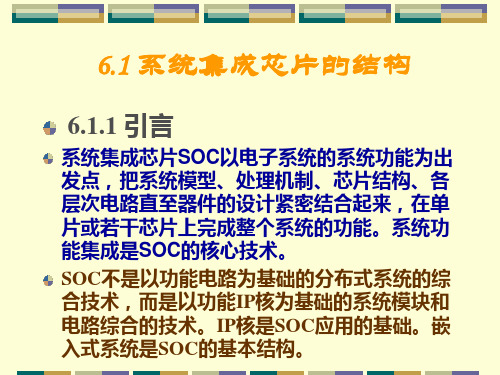

第6章SOC的体系结构

超流水线技术

提高流水线处理效率的另一个方法是缩短机器周期。 一般是将一个机器周期划分为若干个子周期,每个子 周期均发射一条新的指令,亦即每个机器周期发射多 条指令,从而提高计算机的性能。这种处理方式称为 超流水线处理技术。

取指1 取指2 译码 执行 存贮1 存贮2 检查标志 写结果 取指3 取指4 译码 执行 存贮3 存贮4 检查标志

(2) 可扩展性:所有的数据结构和接口应能方便加入新 的模块。

(3) 可综合性:处理器核的描述应该能够综合,以得到 实际电路的实现。

(4) 可测试性:处理器核的设计应该便于进行系统测试 和性能分析。

(5) 分布性:处理器的控制设计成分布式控制,便于指 令集扩展和处理器适应新的应用要求。分布式控制主要 负责流水级管理和每个流水级之间的状态通信。

微指令的结构限制了CISC CPU速度的进一步提 高。

CISC结构不利于并行处理方法。

6.1.3 嵌入式软件

有些SOC需要嵌入式实时操作系统(Real Time Operational System,简称为RTOS)的支持。

嵌入式实时操作系统是计算机操作系统的技术 和设计理念在嵌入式系统中的应用。

6.2 SOC中的嵌入式精简指令集处理 器RISC

CPU核

地址产生电路

运算电路

时序控制电路

指令译码 取指电路

DSP核

地址产生电路

运算电路

指令译码

CPU与DSP同指令流、同地址

CPU核

地址产生电路

运算电路

时序控制电路

指令译码 取指电路

DSP核 运算电路 指令译码

6.2.6 RISC核的设计

RISC核的设计原则:

(1) 模块化:若需加入新的指令,只需要修改相关的部 分,系统结构不应变化。

汽车soc 测试标准

汽车SOC测试标准

1.测试设备:使用覆盖10Hz~400kHz频率范围的测量设备。

2.测试状态:分别在行驶状态和充电状态下进行测量。

行驶状态测量时,所有能由驾驶员或乘客手动打开,且持续工作时间超过60s 的车载电器都应处于典型负载状态,并调节座椅至上下可动范围内的最低位置。

测试过程中,电动汽车和混合动力汽车的SOC应在20%~80%之间。

3.测试方法:在充电状态下,所有充电时允许驾驶员打开的车载电器应处于典型负载状态,并使用覆盖10Hz~400kHz频率范围的测量设备对车内和车外充电接口位置进行测试,在有多种传导充电模式时,应分别进行测量。

以上信息仅供参考,如果您还有疑问,建议咨询专业人士。

soc设计方法与实现

soc设计方法与实现SOC设计方法与实现。

在当今的信息时代,系统芯片(SOC)已经成为各种电子设备的核心。

它集成了处理器、存储器、外设和互联网络等功能模块,为电子产品的设计提供了便利。

本文将就SOC设计方法与实现进行探讨,以期为相关领域的研究者和从业者提供一些参考和帮助。

首先,SOC设计的方法是关键。

在进行SOC设计时,需要考虑到整个系统的功能需求、性能指标、功耗要求等方面的因素。

在这个过程中,需要进行系统级的设计和分析,包括需求分析、体系结构设计、接口设计等。

同时,还需要考虑到系统的可测试性、可靠性和安全性等方面的问题。

因此,在SOC设计过程中,需要采用系统化的方法,包括面向对象的设计方法、面向接口的设计方法、面向性能的设计方法等。

其次,SOC设计的实现也是至关重要的。

在进行SOC设计实现时,需要考虑到硬件和软件的协同设计、工艺制造、封装测试等方面的问题。

在这个过程中,需要进行芯片级的设计和验证,包括RTL级的设计、综合布局布线、时序收敛等。

同时,还需要进行软件级的设计和验证,包括嵌入式软件的开发、系统级仿真验证等。

因此,在SOC设计实现过程中,需要采用综合化的方法,包括硬件软件协同设计方法、工艺制造一体化方法、封装测试一体化方法等。

综上所述,SOC设计方法与实现是一个综合性的工程,需要综合考虑多个方面的因素。

在进行SOC设计时,需要采用系统化的方法,包括面向对象的设计方法、面向接口的设计方法、面向性能的设计方法等。

在进行SOC设计实现时,需要采用综合化的方法,包括硬件软件协同设计方法、工艺制造一体化方法、封装测试一体化方法等。

希望本文的内容能够为相关领域的研究者和从业者提供一些参考和帮助,推动SOC设计方法与实现的进一步发展和应用。

soc设计流程

soc设计流程

一、SOC设计流程

1、了解系统架构

首先要了解系统的具体功能、技术架构和可用资源,以便正确的设计和实现SOC。

2、制定技术架构

根据系统要求,构建和定义系统的技术架构,包括计算能力、存储能力、通信能力和可编程性能等。

3、硬件设计

根据技术架构,设计和实现SOC的硬件部分,包括集成电路、运放、存储系统等。

4、软件设计

根据技术架构,设计和实现SOC的软件部分,包括驱动程序、系统软件、应用软件等。

5、联调测试

联调硬件和软件,进行系统测试,验证SOC设计的正确性和完整性。

6、调试定制

根据用户技术架构要求,进行系统调试和定制,以满足用户特定的应用需求。

二、SOC设计原则

1、必要性原则

在SOC设计过程中,只有必要的功能,才能被选取加入硬件设计,从而节省空间和成本。

2、通用性原则

在SOC设计过程中,应尽量选择和使用通用的技术架构和部件,以降低开发成本。

3、性能调整原则

在SOC设计过程中,应根据实际需求,进行细致的性能调整,以提高SOC整体性能。

4、经济原则

在SOC设计过程中,应考虑成本因素,以降低成本和优化可视化效果,而不是完全按技术架构要求来设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

f u n c t i o n a l v e r i f i c a t i o nW h i t e P a P e rHybrid eSl/rtl co-verificationplatform for SyStem levelSoftware teStingpiotr K. luSzczaK, mentor grapHicSprepared for presentation at arm techcon 2011 (class code: atc-100)AbstrActHere’s one of the most oft-cited facts of semiconductor device design today: the increasing complexity ofsocs and multicore designs continues to create new verification challenges. Virtual platforms addresssuch challenges by abstracting designs to the transaction. However, such platforms introduce newproblems, including that hardware-software interface debugging is limited to high-level abstract EsLmodels. combining tLM 2.0 and rtL models allows for detecting hardware and software issues in greaterdetail than is possible with transaction level models alone. this paper discusses an EsL/rtL modelswapping technique that gives flexibility to debug and analyze systems at any development stage and onany hardware representation. the benefits of the technique include greater accuracy, optimizedperformance and faster product delivery.introductionAccording to the latest surveys, most SoC designs include one or more processors. This trend is due to theincreased cost of hardware verification for custom logic, the relatively flat cost of IP development and the broadavailability of synthesizable, high-performance and low-power processors. Verifying devices that include processorsrequires new techniques since hardware and software are involved in the final product.There are many approaches to this complex problem. One is traditional stimulation of the entire subsystem usingsequences based on the combination of constrained random and direct tests (the latter to cover corner cases).While the algorithmic approach enables relatively fast coverage closure, it does not include system-level softwareexecution on the processor. Typical examples of system software include BIOS or device firmware. The processor’sfirmware in particular can only be verified in relation to the hardware, thus the need for a system-level test thatexercises the program and checks if all elements of the integrated system are functioning properly.Running software on the processor model can be very slow during event-driven simulation at the RTL level. Oneway to speed things up is to abstract the design to the transaction level and simulate the SoC using a virtualplatform. Executing software on such a platform generates TLM 2.0 transactions.figure 1: General esl flow,including modeling, assembly,verification, analysis and theeventual virtual prototypetHE “Lt” And “At” siMuLAtion ModEs, And tHE LiMitAtions of A tLM-onLy ApproAcHCollecting and analyzing system software interactions with the TLM 2.0 based models allows for easy measurementcertain aspects of simulation coverage, which in turn enables advanced analysis. As shown in figure 1 on theprevious page, a typical ESL flow consists of modeling, platform assembly, verification, analysis and eventualcreation of a virtual prototype. There are two possible modes of simulation: loosely-timed (LT) and approximately-timed (AT). The LT mode allows runs the simulation faster and is suitable for executing simple software tasks. Theacceleration mechanism uses directed memory interface (DMI) for all memory accesses. Because the I/Ocomponents are accessed through the bus, which does not support DMI, the transactions are shown aspronounced spikes in LT simulation.The AT mode, in which CPUs, I/Os and memories are active and show correct transaction timing, enables morerealistic simulation. The timing information in this mode can be used to provide system performance data,including power consumption of different IPs at different times, transaction throughput from specific sockets andaverage transaction latency. Additionally, the processor core cache can be traced and analyzed through cachemonitors to allow display of I-cache and D-cache performance.The TLM level runs the virtual platform fast enough to execute system level software at a reasonable speed.However, the pure ESL verification platform lacks the ability to verify that the system level software, or morespecifically, that such software developed on the virtual platform using SystemC models for particular subsystemsworks with target hardware at the RTL level. A TLM-only approach does not allow for detection, repair andunderstanding of critical problems across different abstraction levels and language boundaries, a limitation whichmay lead to multiple software patches or, worse still, hardware respins. All too often, because of the large amountof legacy RTL IP that will be reused, a detailed RTL functional verification for portion of the design may still benecessary.figure 2: tlm simulationwaveforms for lt and at modesfigure 2: an example of actualpower consumption in atsimulation modeHow A Hybrid pLAtforM cAn HELpA hybrid ESL/RTL verification platform can address these limitations by integrating the RTL model of the subsysteminto the ESL base platform, thus replacing the corresponding SystemC implementation. In this configuration, a UVMtestbench is used to convert abstract TLM 2.0 transactions representing bus accesses on the SoC’s bus fabric to pin-level representation on the RTL subsystem interface. The testbench also converts the TLM 2.0 general payloadtransactions into sequences that are passed to the verification IP (VIP) component. On completion of a bus cycle,the VIP returns a response that is passed back to the virtual platform as a TLM 2.0 response.In addition, the ESL CPU model is swapped for a model that provides both a signal and TLM interface. Such hybridarchitecture allows for directly connecting some pin-level signals to the processor at the RTL level. One example isinterrupt signals, which, when connected at the signal level, give better control over interrupt timing critical for theembedded system verification flow. Combining transaction level and RTL models exposes more details abouthardware-software issues than does pure TLM abstraction.Since the hybrid configuration uses a processor model with a mixed TLM/RTL interface, it allows for an accurateswitchable processor as well. The configuration allows for instruction-level accuracy, including fetching instructionsand reading from/writing to memory either with TLM 2.0 transactions or software memory accesses using acoherent memory server implemented as an API connected directly to the instruction set simulator (ISS) of the CPU.In this case, the program and data memory is mapped as optimized accesses. This mechanism reduces the TLM/RTL traffic to I/O communications and allows for visualizing both the number of hardware and software cycles andthe number of executed instructions.figure 4: example of a combinedesl/rtl verification platformfigure 5: a collection of codecoverage dataBy enabling the ability to turning on or off logic simulationtransactions, optimized memory access allows for controllingwhich address spaces need to be mapped to coherent servers.Thus, the ratio between HDL simulation speed and debugvisibility is fully scalable. Cycle-accurate-level simulation is alsopossible when an RTL processor model is used. In this mode,the processor model communicates at the pin-level with otherSoC components. The various processor models make itpossible to dynamically switch simulation accuracy; theswitching mechanism propagates CPU states between ISS/RTLlevels and transfers the contents of caches.The hybrid ESL/RTL platform allows for concurrently observingand debugging hardware and software domains. It does so bylinking the software debugger with the logic simulator, whichgives full visibility of the processor while running the entiredesign in the HDL logic simulator. Since the software debugger is fully synchronizedwith the logic simulator, it’s possible to propagateof four levels of logic into the software’sdebugging environment. This capability allows fordetection of problems that would otherwiseinvisible without four-state logic, such as X statesused in comparisons or computation, or thereferencing of uninitialized memory or registers.figure 6: software execution acceleration mechanismfigure 7: hybrid esl/rtl platformfor hW/sW debuggingfigure 8: arm® 1176 cpU register window showing X states©2011 mentor graphics corporation, all rights reserved. this document contains information that is proprietary to mentor graphics corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. in accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. all trademarksmentioned in this document are the trademarks of their respective owners.f o r t h e l a t e s t p r o d u c t i n f o r m a t i o n , c a l l u s o r v i s i t :concLusionIn sum, the hybrid ESL/RTL coverification platform provides the following benefits:■Higher speed compared to pure RTL simulation■Ability to check properties of RTL code using target software running on the CPU■Ability to debug critical timing of software functions at the transactional and pin level■Full visibility of the processor while running the entire design in the HDL logic simulator■Ability to debug the hardware-software interface at a greater level of detail than is possible with an abstractESL model■Multiple levels of accuracy (instruction or cycle-accurate)。