DSP硬件结构.ppt

dsp课件

DSP的特点

DSP具有高效性

由于DSP采用数字信号处理器 进行信号处理,因此其处理效 率高,能够实现高速实时信号

处理。

DSP具有高精度

数字信号处理器可以实现对信 号的高精度处理,避免了模拟 信号处理中可能出现的误差和 失真。

快速傅里叶变换(FFT)

01

FFT是一种高效计算离散傅里叶变换(DFT)及其逆变换的算法

。

数字滤波器设计

02

数字滤波器是一种用于信号处理的算法,可以实现对信号的滤

波、去噪等功能。

数字信号处理(DSP)算法

03

DSP算法包括多种数字信号处理方法,如频域分析、时域分析

、功率谱分析等。

CHAPTER 04

DSP课件

目 录

• DSP概述 • DSP硬件平台 • DSP软件编程 • DSP在信号处理中的应用 • DSP的优化与扩展 • DSP的发展趋势与未来展望

CHAPTER 01

DSP概述

DSP的定义

数字信号处理(DSP)是一门涉及信号处理、算法设计、系统实现等领域的学科 。它主要研究如何利用数字信号处理器(DSP)对数字信号进行采集、变换、滤 波、估值、压缩等处理,以满足人们在不同领域的需求。

DSP扩展板

内存扩展板

用于扩展DSP的内存容量,提高数据处理能力。

数字IO扩展板

用于扩展DSP的数字输入输出接口,实现与外部设备的通信。

音频视频接口扩展板

用于扩展DSP的音频视频接口,实现音频视频数据的采集和输出。

DSP与其他设备的连接

DSP原理及应用第二章DSP的硬件结构总结(精)

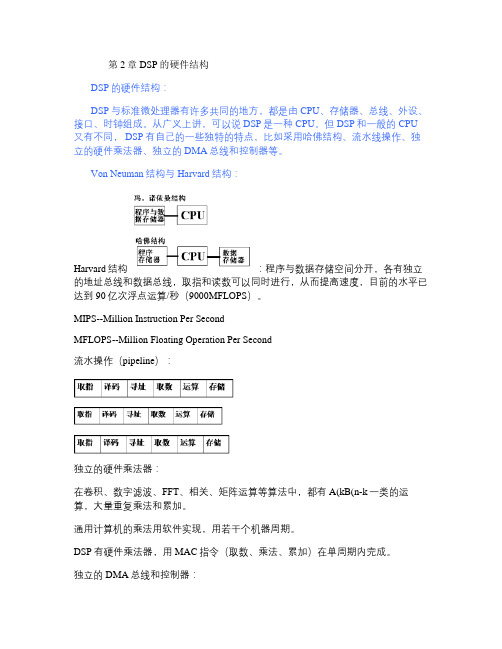

第2章DSP的硬件结构DSP的硬件结构:DSP与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP和一般的CPU 又有不同, DSP有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA总线和控制器等。

Von Neuman结构与Harvard结构:Harvard结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90亿次浮点运算/秒(9000MFLOPS)。

MIPS--Million Instruction Per SecondMFLOPS--Million Floating Operation Per Second流水操作(pipeline):独立的硬件乘法器:在卷积、数字滤波、FFT、相关、矩阵运算等算法中,都有A(kB(n-k一类的运算,大量重复乘法和累加。

通用计算机的乘法用软件实现,用若干个机器周期。

DSP有硬件乘法器,用MAC指令(取数、乘法、累加)在单周期内完成。

独立的DMA总线和控制器:有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU工作的条件下,DMA速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10个机器周期,乘法是一系列的移位和加法,需要数十个机器周期。

DSP的CPU设置硬件乘法器,可以在单周期内完成乘法和累加.移位:通用微处理器的移位,每调用一次移位指令移动1-bitDSP可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换.溢出:通用CPU中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP把移位输出的最高位(MSB)存放在一个位检测状态寄存器中,检测到MSB=1时,就通知下一次会发生溢出,可以采取措施防止.数据地址发生器(DAG):在通用CPU中,数据地址的产生和数据的处理都由ALU来完成在DSP中,设置了专门的数据地址发生器(实际上是专门的ALU),来产生所需要的数据地址,节省公共ALU的时间.外设(peripherals):时钟发生器(振荡器与PLL)定时器(Timer)软件可编程等待状态发生器通用I/O同步串口(SSP)与异步串口(ASP)JTAG扫描逻辑电路(IEEE 1149.1标准便于对DSP作片上的在线仿真和多DSP条件下的调试’C54x的内部结构:中央处理器CPU 、内部总线控制、特殊功能寄存器、数据存储器RAM 、程序存储器ROM、I/O功能扩展接口、串行口、、主机通信接口HPI、定时系统、中断系统。

2.TIDSP系列及硬件结构解析

8

Biased Exponent -e

23

Mantissa -f

第2章TMS320C2的CPU结构和存储器配置

2.1 TMS320C2xx系列DSP结构1、结构2和结构3

主要的功能单元:´2DSP的CPU(或称为DSP内核)、内部存储器和外围 设备。所有‘C2系列产品(‘C24 ‘C20 ‘C240)都具有相同的CPU (DSP Core) 。

1.4 数字运算基础

数的定标

Q表示法:小数点放在i位之后称为Qi表示 D15 Di • D0

i越大,表示的数值范围越小(绝对值小于215-i),但精度越高 (小数精度为1/2i),最高位D15为符号位

转换

某数(x)转换为定点数(xq) Qi :xq = int[x*2i]把小数点左移i位

将Qi表示的定点数(xq)转换为数据(x):x = float [xq*2-i] 例如,数x=0.4,用Q15表示,则对应定点数为 xq=int[0.4*215 ]=13107

返回

各模块 的I/O引 脚比较 清楚

信号 第5章

返回

给出给 出了 F240更 具体的 内部结 构特点 给

返回

X240系 列引脚图

PQ= 132 引脚 bumper ed QFP

返回

2.2 'C2的总线结构

总线全部为16位

2.3 'C2系列CPU结构

CPU寄存器 包括: ACC、TREG PREG、 ST0、ST1

DSP定点数算术运算

定点加/减法必须保证两个操作数的定标值一样。 如果两个数据的Q值不同,在保证数据准确性的前提下调整Q值使数据精度 最高,即尽量将Q值小的数调整为与另一个数的Q一样大。 例如,|X|<1 |Y|<4 用Q13表示 定点数的乘法 两个16位定点数的乘法分以下几种情况: 小数乘小数(即数用Q15表示) Q15*Q15=Q30,两位符号位,左移一位 整数乘整数(即数用Q0表示法) Q0*Q0=Q0 混合表示法(操作数采用Q0与Q15之间的表示法) 非线性运算 库函数math.h、查表法和混合法

CDSP硬件结构

ALU框图:

2019/1/12

DSP技术及其应用

14

2. 累加器:

累加器ACCA和ACCB存放从ALU或乘法器/加法器单元 输出的数据,累加器也能输出到ALU或乘法器/加法器中。 执行MIN和MAX指令或并行指令LD||MAC时,一个累加 器加载数据,另一个完成运算 保护位作为计算时的头区(Head margin),用作数据位余量, 以防止自相关等迭代运算时溢出 A和B不同之处:A的高16位可作为乘/加单元的一个输入

2019/1/12

DSP技术及其应用

16

3. 桶形移位器

2019/1/12

DSP技术及其应用

17

4. 辅助寄存器算术单元

‘C54x通过使用两个辅助寄存器算术单元(ARAU0 和ARAU1),每周期能产生两个数据存储器地址。 PB总线能把存储在程序空间的数据操作数(如系数表) 传送到乘法器和加法器中进行乘/累加运算,或者在数 据移动指令(MVPD和READA)中传送到数据空间。 这种能力再加上双操作数读的特性,支持单周期3操作 数指令的执行,如FIRS指令。 ‘C54x还有一组寻址片内外设的片内双向总线,通过 CPU接口中的总线交换器与DB和EB 相连接。对这组 总线的访问,需要两个或更多的机器周期来进行读和 写,具体所需周期数由片内外设的结构决定。

2019/1/12

DSP技术及其应用

15

3. 桶形移位器

40位的桶形移位器是对一些操作进行定标和标准化 ‘C54x的桶形移位器有一个与累加器或数据存储器 (CB,DB)相连接的40-bit输入,和一个与ALU或 数据存储器(EB)相连接的40-bit输出。 桶形移位器能把输入的数据进行0到31bits的左移和0 到16bits的右移。 所移的位数由ST1中的移位数域(ASM)或被指定作 为移位数寄存器的暂存器(TREG)决定。

第2章 TMS320C6000系列DSP硬件结构

二级内部存储器

• 2.一级数据Cache(L1D) • 一级数据Cache(L1D)是含有64个集的4KB的双路联合集缓存,每 行大小为32字节,由于存取的最小单位为字,所以每一个申请提交的 地址的最低2位都将被L1D忽略,位2作为字地址,位3和位4作为4个8 字节子行的选择子,其后的6位选择缓存中相应的组,地址中剩余的 其他位作为申请数据的唯一标示,如图2-27所示。

外部存储器接口

当同时存在多个请求同时到达,EMIF根据优先级进行仲裁并响应各 个请求。TMS320C620x/C670xDSP中的EMIF位置如图2-30的阴影部 分。

外部存储器接口EMIF

• 1.TMS320C6201/C6701的外部存储器接口 • 图2-31为TMS320C6201/C6701外部存储器接口信号图。表2-17为接 口信号的详细说明。

TMS320C62x/C67x/C64x系列DSP的CPU 数据通路分别如图所示。 其数据通路的主要组成部分如下:

DSP硬件系统概述

• 而DSP并行执行上述4个步骤,所以指令周期等于 机器周期.也就是说,上述4步DSP以流水线方式 运行,提高了CPU执行速度.

• 流水线有一个建立的过程,只有在完整的流水线 时,才会发挥DSP最高效率,所以在程序中应尽量 避免破坏流水线.

DSP芯片的厂家

目前世界上生产DSP芯片的公司主要 有TI德州仪器公司,AD美国模拟器件公司 ,Technologics朗讯技术公司和Motorola摩 托罗拉公司四大公司,而TI公司则是世界上 最大的DSP芯片供应商.TMS320系列产品 就是该公司的DSP产品.

德州仪器公司的DSP产品

• DSP器件的应用对象可以分为三类 – 工业控制领域 – 低成本嵌入式应用系统 – 需要用复杂算法对大量数据进行处理 的应用

多总线结构

• 数据、地址和控制总线是微处理器访问各种部 件的基础,我们称之为3总线.

• MCU无论片内还是片外均为三总线结构,而DSP 片内为多总线结构多条数据、地址和控制总线 片外为三总线结构,有的DSP甚至片外也有多条 总线.

多总线结构:片内多条数据、地址和控制总线.

外部地址 总线

外部数 据总线

数字信号处理器的流水线

流水线结构将指令的执行分解为取指、译 码、取操作数和执行等几个阶段

– TMS320C54xx DSP 采用6级流水线 – TMS320C6xxx DSP 采用8级流水线 – TMS320C55xx DSP的流水线分为

• 指令流水线 • 执行流水线

数字信号处理器的其他特点

• 硬件乘法累加单元

• 存储器

– Flash存储器、RAM存储器

• 功耗 – 低工作电压 、休眠或空闲模式 、可编程时钟分 频器 、外围控制

dsp课件

在代码实现完成后,进行代码调试,确保程序的正确性和稳定性。

调试与测试结果分析总结

调试过程

在代码调试完成后,进行系统调试,确保各个模块之间的协调和正 常运行。

测试结果分析

对测试结果进行分析,包括性能测试、功能测试等,找出可能存在 的问题和不足。

总结

根据调试和测试结果,对项目进行总结,包括经验教训、改进方向等 ,为后续的项目提供参考和借鉴。

DSP课件

目录

• DSP概述 • DSP硬件结构与工作原理 • DSP软件编程与开发环境 • 典型应用案例分析 • DSP发展趋势与挑战 • 实践项目设计与实现

01 DSP概述

定义与发展

定义

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及多个学科 的交叉学科,主要研究将模拟信号转换为数字信号,并对数字信号进行各种处 理。

通信信号处理应用

总结词

通信信号处理是数字信号处理的另一个重要应用领域,涉及信号的调制、传输和解调等环节。

详细描述

在通信信号处理中,数字信号处理技术可以用于信号的调制、编码、解调和解码等环节,同时还可以 进行信号特征提取、分类和识别等任务。具体的应用包括移动通信、卫星通信、数字电视和雷达信号 处理等。

未来DSP将进一步提高处理速度和效率,满足更 多复杂应用的需求。

更低的功耗

通过不断优化技术,降低DSP的功耗,延长设备 的使用寿命。

更广泛的应用领域

DSP将在更多领域得到应用,如智能家居、自动 驾驶、医疗保健等。

06 实践项目设计与 实现

项目需求分析与设计思路

明确项目目标

01

在开始实践项目之前,需要明确项目的目标,包括要实现的功

DSP第2章 'C54x的硬件结构2

2013年8月15日

DSP原理及应用

6

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的配置,反映 处理器的工作状态。

15~7 6 5 4 AVIS 3 2 1 0 SST

IPTR MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

③ 暂存器SPRAM。

2013年8月15日

DSP原理及应用

14

特殊功能寄存器

功能:主要用于程序的运算处理和寻址方式的选

择和设定。地址范围:0000H~001FH。 外设寄存器 ’C5402的CPU寄存器共有27个,CPU访问这 功能:用来控制片内外设电路的状态和存放数据。 些寄存器时,不需要插入等待时间。 地址范围:0020H~005FH。 包括串行口通信控制寄存器组、定时器定时控 暂存器SPRAM 制寄存器组、时钟周期设定寄存器组等。 功能:用来暂存变量。地址范围:0060H~007FH。

中断屏蔽寄存器 10H 中断标志寄存器 11H 保留 ( 用于测试 ) 12H 保留 ( 用于测试 ) 13H 保留 ( 用于测试 ) 14H 保留 ( 用于测试 ) 15H 状态寄存器0 16H 状态寄存器1 17H 累加器A低字(15~0位) 18H 累加器A高字(31~16位) 19H 累加器A保护位(39~32位) 1AH 累加器B低字(15~0位) 1BH 累加器B高字(31~16位) 1CH 累加器B保护位(39~32位) 1DH 暂存寄存器 1EH DSP原理及应用 状态转移寄存器 1FH

2013年8月15日

存储器映像的CPU寄存器, 存储器映像的外设寄存器 特殊功能寄存器

1-TMS320C54x的硬件结构

TMS320C54x的硬件结构

中央处理单元(CPU)

桶形移位器

桶形移位器能把输入的数据进行0到31位的左移和0到16位的右移。

桶形移位器的功能框图

21

TMS320C54x的硬件结构

中央处理单元(CPU)

桶形移位器

桶形移位寄存器的输入可以为: ①DB,取得16位输入数据; ②DB和CB ,取得32位输入数据; ③40位累加器A或B。 桶形移位寄存器的输出连到: ① ALU的一个输入端, ②经过MSW/LSW(最高有效字/最低有效字)写选择单元至EB 总线。

TMS320C54x的硬件结构

TMS320C54x的内部结构和主要特性

TMS320C54x的主要特性

1.CPU 部分 先进的多总线结构(1条程序总线、3条数据总线和4条对应的 地址总线)。 40位算术逻辑运算单元(ALU),包括1个40位桶形移位寄存 器和2个独立的40位累加器。 17位×17位并行乘法器与40位专用加法器相连,用于非流水线 式单周期乘法/累加(MAC)运算。 比较、选择、存储单元(CSSU),用于加法、比较、选择运 算。 指数编码器,是一个支持单周期指令EXP的专用硬件,可以在 单个周期内计算40位累加器中数值的指数。 双地址生成器,包括8个辅助寄存器和2个辅助寄存器算术运算 6 单元(ARAU)。

23

乘法器/加法器单元

乘法器输入: X:T,A, DB0~15 Y:A, DB0~15, CB0~15, PB0~15 乘法器输出:加法器 加法器输入: X:乘法器 Y:A,B, 加法器输出:A,B,0零 乘法器/加法器单元功能框图

12

TMS320C54x的硬件结构

总线结构

(3) 4条地址总线(PAB、CAB、DAB和EAB) 4条地址总线(PAB、CAB、DAB和EAB)用于传送执行指 令所需要的地址。 TMS320C54x可以利用两个辅助寄存器算术运算单元 (ARAU0 和 ARAU1),在每个周期产生两个数据存储器 的地址。 TMS320C54x还有一条访问片内外设的片内双向总线。这条 双向总线通过CPU接口内的总线交换器与DB和EB相连。利 用这条双向总线的访问过程需要2个或更多个周期来读/写, 具体时间取决于外围电路的结构。由此可见,DSP处理系统 中应当尽量避免器件内外大量数据交换,以保证系统高速特 13 性。

TI C6x DSP硬件结构与应用

5/19/05 COA/Zhaofeng Lec 8.15

• 达芬奇( arm921 + C64x + 低功耗 )

5/19/05

COA/Zhaofeng Lec 8.2

TMS320™ DSP Family Overview

fastest TI DSPs running at clock speeds up to 1 GHz Tms320 C6416

•from 1200 to 8000 MIPS for fixed-point •From 600 to 1350 MFLOPS for floating point

5/19/05 COA/Zhaofeng Lec 8.8

6000 DSP Architecture and Core

• The TMS320C62x™ and TMS320C67x™ devices are based on VelociTI™, an advanced Very Long Instruction Word (VLIW) architecture. • The C64x™ DSP generation features TI's VelociTI.2™ VLIW architecture

5/19/05 COA/Zhaofeng Lec 8.3

TMS320C6000 DSPs ROADMAPs

C6201 C6203 C6204 C6205 C6416 DM642

数字信号处理器(DSP)原理与应用.ppt

数字信号处理的实现方法

实现方法 PC机 高级语言 编程 速度 中等 快 慢 应用场合 非嵌入式 非嵌入式 嵌入式 适应性 复杂算法 复杂算法 简单算法

Tianjin University

性价比 较好 中等 较好

PC机+高 速处理

单片机

硬件+ 专用指令

汇编语言 编程

通用DSP

专用DSP

专用指令

硬件+ 专用指令

•机器人视觉

•图像传输/压缩 •同态处理 •模式识别 •工作站

•动画/数字地图

Tianjin University

DSP芯片的主要应用领域

(1)信号处理

•频谱分析

(2)图像处理

•函数发生器

•模式匹配 •地震信号处理 •数字滤波 •锁相环

(3)仪器

(4)声音/语言 (5)控制 (6)军事应用 (7)电信 (8)无线电

MIPS(Million Instruction per second)是 一种评估DSP速度的一个指标。DSP运行频率也 是评估DSP的一个指标,他们二者之间的联系 需要考虑到DSP体系结构(是否多路并行结构、 是执行定点还是浮点运算)。

Tianjin University

价格 商业级 :一般应用;适用于实验室等环境较好 场合; 工业级 :可靠性好;适用于工业现场等环境恶 劣场合; 军品 :可靠性高;适用于各种恶劣场合; 航空级 :可靠性很高;适用于特殊场合;

Tianjin University

血压计

DSP系统基本构成

Tianjin University

输入

抗混叠 滤波 A/D DSP

平滑 滤波 D/A

输出

存储器

Tianjin University

DSP硬件系统概述

多总线结构:片内多条数据、地址和控制总线。

ROM/ Flash 外部地址 总线

SARAM

B0 DARAM

B1, B2 DARAM PAB DRAB DWAB

MemoryMapped Registers

外部数 据总线

PRDB DRDB

DWEB

Control Bus On-Chip Peripherals/ Registers

C2的CPU运行于4级流水线方式

CPUCLK 取指令 译码 N N-1 N+1 N N+2 N+1 N+3 N+2

取操作数

执行

N-2

N-3

N-1

N-2

N

N-1

N+1

N

图 四级流水线

DSP与MCU软件开发比较

模块化:按功能模块编程 工程化:软/硬人员分离 MCU: ORG xxxx,绝对定位 优点:简单、容易上手 缺点:模块化编程差 工程化不支持 DSP: Section:相对定位 缺点:灵活、上手较难 优点:模块编程好 工程化编程支持

DSP总体设计

根据需求写出任务说明书

根据任务书确定技术指标

DSP芯片及外围芯片

总体设计确定软硬件分工

软件设计说明书 硬件设计说明书

软件编程与调试

系统集成

硬件(.sch / .pcb )

硬件调试

系统测试、样机完成、中试、产品测试与生产

DSP 软件 设计

硬件系统设计

确定硬件方案 系 统 分 析

器件选型

数字信号处理器的其他特点

• 硬件乘法累加单元

独立的硬件乘法单元

• 零开销循环

DSP原理及结构PPT课件

(8)军事与尖端科技:雷达和声纳信号处理、雷达成像、导弹制导等。 (9)计算机与工作站:计算机加速卡、图形加速卡。 (10)消费电子:数字电视、图形/声音压缩解压装置。

第11页/共87页

4、DSP产品的现状 定点DSP有200多种,浮点DSP有100多种。主要生产:TI 公司、

单3.3V电压输出:TI公司的TPS7133、TPST7233 单电源可调电压输出:TI公司的TPS7101、TPST7201 双电源输出(两路输出的芯片):TPS73H301、TPS73H325、TPS73H318

第44页/共87页

(5)3.3V和5V混合逻辑系统设计 各种电平转换标准

第45页/共87页

第35页/共87页

(3)加电次序 理想情况下,两个电源应同时加电,但在一些场合很难做到。不同型号器件上电顺序不一样。

第36页/共87页

TMS320VC5402与大多数DSP芯片的上电 顺序:

低电压电源CVdd先上电;高电压电源 DVdd后电压;

高电压电源DVdd先断电;低电压电源 CVdd后断电;

列处理器的指令周期已经从第一代的200ns降至20ns以下。快速的指令周 期使DSP芯片能够实时实现许多DSP应用

第30页/共87页

二、TMS320系列DSP的结构 第31页/共87页

1、多总线结构 由哈佛结构决定了具有独立的程序总线和数据总线,以及独立的程序

存储器和数据存储器,这样就可以同时获得指令字和操作数互不干扰,即一 个指令周期内可以同时准备好指令和操作数。

*若不遵照此次序,那么CVdd与DVdd的差 值必须小于2.8V。

TMS320VC549具有静电保护结构,所以上 电 顺 序 与 上 相 反 。第37页/共87页

DSP原理及应用第二章DSP的硬件结构总结

第2 章DSP 的硬件结构DSP的硬件结构:DSP 与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP 和一般的CPU 又有不同,DSP 有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA 总线和控制器等。

Von Neuman结构与Harvard 结构:Harvard 结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90 亿次浮点运算/秒( 9000MFLOPS)。

MIPS--Million Instruction Per Second算,大量重复乘法和累加。

通用计算机的乘法用软件实现,用若干个机器周期。

DSP 有硬件乘法器,用MAC 指令(取数、乘法、累加)在单周期内完成独立的DMA 总线和控制器:有一组或多组独立的DMA 总线,与CPU 的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA 内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU 工作的条件下,DMA 速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU 和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10 个机器周期,乘法是一系列的移位和加法,需要数十个机器周期。

DSP 的CPU设置硬件乘法器,可以在单周期内完成乘法和累加.移位:通用微处理器的移位,每调用一次移位指令移动1-bitDSP 可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换.溢出:通用CPU 中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP 把移位输出的最高位(MSB )存放在一个位检测状态寄存器中,检测到MSB=1 时,就通知下一次会发生溢出,可以采取措施防止.数据地址发生器(DAG ):在通用CPU 中,数据地址的产生和数据的处理都由ALU 来完成在DSP中,设置了专门的数据地址发生器(实际上是专门的ALU ),来产生所需要的数据地址,节省公共ALU 的时间.外设(peripherals):时钟发生器(振荡器与PLL )定时器(Timer)软件可编程等待状态发生器通用I/O同步串口(SSP)与异步串口(ASP)JTAG 扫描逻辑电路(IEEE 1149.1标准便于对DSP 作片上的在线仿真和多DSP条件下的调试' C54的x 内部结构:中央处理器CPU 、内部总线控制、特殊功能寄存器、数据存储器RAM 、程序存储器ROM、I/O 功能扩展接口、串行口、、主机通信接口HPI、定时系统、中断系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

独立的DMA总线和控制器

有一组或多组独立的DMA总线, 与CPU的程序总线和数据总线并行工 作,在不影响CPU工作的条件下, DMA速度目前已达800 MBps(Millions Bytes/s )

DSP技术讲义,2010

1.0 TMS320C2000系列DSP

• TI公司的TMS320C2000系列DSP控制器,集成了flash存储器、 高速A/D和可靠的CAN模块,主要应用于数字化的控制。

DSP技术讲义,2010

3.在片外围电路(Peripherals on chip)

● 具有软件可编程等待状态发生器 ● 设有可编程分区转换逻辑电路 ● 带有内部振荡器或外部时钟源的片内锁相环(PLL)发 生器 ● 支持全双工操作的串行口,可进行8位或16位串行通信 ● 带4位预定标器的16位可编程定时器 ● 设有与主机通信的并行接口(HPI) ● 具有外部总线判断控制,以断开外部的数据总线、地 址总线和控制信号 ● 数据总线具有总线保持特性

134

135

136

137

138

139

140

141

142

143

144

1

108

2

107

3

106

4

105

5

104

6

103

7

102

8

101

9

100

10

99

11

98

12

97

13

96

14

95

15 16

TMS320VC5402

94 93

17

92

18

91

19

90

20

89

21

88

22

87

23

86

24

85

25

84

26

83

数据总线DB 地址总线AB

外部存储 器接口

DSP技术讲义,2010

哈佛结构

哈佛(Harvard)结构

I/O口

串行接口

并行接口

CPU

外部管理数据总线 外部管理地址总线 数据数据总线 数据地址总线

程序数据总线 程序地址总线RMRAM外部存储 器接口

改进型的哈佛结构是采用双存储空间和数条总线,即一 条程序总线和多条数据总线。

TMS320C54x

系统 控制 接口

系统控制

PAGEN

DAGEN

程序地址生成特器寄殊存功器能数据地址生成器

PA

程序存储器

BPB

CA BCB

的 硬

DA BDB

件 结

EA BEB

数据存储器 串行口 并行口 定时器 计数器 中断

外部 存储器

接口

外部 设备 接口

构 图

乘法 累加器

CPU

算术/逻辑 运算单元

比较器

• 1、用来保存一个乘数的16位暂时寄存器(TREG)

• 2、乘法器

Data read bus(DRDB) Program read bus

•

3、32位乘积寄存器(PREG) Data read bus

(PRDB)

MUX

• 4、乘积移位器

(DRDB)

TREG

Multiplier

16*16

PREG

Product shifter(32 bits)

DSP技术讲义,2010

2.3 TMS320C54x引脚功能

TMS320C5402共有144个引脚,引脚分布如图。 电源引脚

109

110

111

112

113

114

115

116

117

130 129 128 127 126 125 124 123 122 121 120 119 118

131

132

133

• C2000系列,主要有C24x和C28x两个系列。

DSP技术讲义,2010

1.1 TMS320C24x的内核CPU

• TMS320C24x中央处理单元(CPU)采用并行 的体系结构,CPU可在单指令周期内执行高速的 算术运算。CPU包括三个基本组成部分:输入定 标单元、乘单元和中央算术逻辑单元(CALU), 结构如下图所示 – 输入定标单元 – 乘单元 – 中央算术逻辑单元(CALU)

DSP技术讲义,2010

独立的硬件乘法器

❖在卷积、数字滤波、FFT、相关、矩阵 运算等算法中,都有 A(k)B(n-k) 一类的运算,大量重复乘法和累加。

❖通用计算机的乘法用软件实现,需用若 干个机器周期。

❖DSP有硬件乘法器,用MAC指令(取数、 乘法、累加)在单周期内完成。

DSP技术讲义,2010

Data read bus(DRDB) Program read bus(PRDB)

/数据空间至CALU间

MUX

数据通路一部分,不会占用

31

16 15

0

时钟的开销。

I nput shif t er(32 bit s)

DSP技术讲义,2010

➢ 乘单元

• C24x使用16位×16位的硬件乘法器在单周期内产生有符 号或无符号的32位结果,乘单元包括:

累加器A

39 ••• 32 31 ••• 16 15 ••• 0

AAGGG

保护位

AAHH

高阶位

AL

低阶位

39 ••• 32 31 ••• 16 15 ••• 0

累加器B

BBGGG

BBHH

BL

保护位

高阶位

低阶位

保护位:AG、BG 39~32,作为算术计算时的数据位余量, 以防止迭代运算中的溢出。

高阶位:AH、BH 31~16; 低阶位:AL、 BL 15~0。

1.2 C24x存储器与I/O空间

➢ 544字×16位片内数据/程序双口RAM ➢ 16K字×16位片内程序ROM或FLASH ➢ 224K字×16位最大寻址空间(64K字程序空 间、64K字数据空间、64K字I/O空间和32K字全 局数据空间) ➢ 外部存储器接口模块:软件等待状态发生器、 16位地址/数据总线 ➢ 支持硬件等待状态

DSP技术讲义,2010

【例1】累加器A=FF 0123 4567H,执行带移位的STH和STL 指令后,求暂存器T和A的内容。

STHL A,-88,,TT

; ;A的A的内内容容左右右移移8位8位,,AHLA存L存入入TT

AG

AH

AL

A FF 0123 4567

DSP技术讲义,2010

流水线

流水线操作是由6个操作阶段或操作周期组成。在任何 一个机器周期内,可以有1 ~ 6条不同的指令在同时工作, 每条指令可在不同的周期内工作在不同的操作阶段。

预取指P 取指F 译码D 寻址A 读数R 执行X 预取指P 取指F 译码D 寻址A 读数R 执行X 预取指P 取指F 译码D 寻址A 读数R 执行X 预取指P 取指F 译码D 寻址A 读数R 执行X

40位 桶 形 移 位 器

寻址单元

40位 累 加 器 A 40位 累 加 器 B

8个 辅 助 寄 存 器 2个 寻 址 单 元

DSP技术讲义,2010

IEEE 1149.1标准 测试/仿真

McBSP0 (多 通 道 缓 冲 串 口 0)

McBSP1 (多 通 道 缓 冲 串 口 1)

定时器

软件等待状态发生器

PLL 时钟发生器

2.1 TMS320C54x主要特性

1.CPU

● 采用先进的多总线结构,通过1组程序总线 、3组数据总线和4组地址总线来实现。

● 40位算术逻辑运算单元ALU,包括1个40 位桶形移位寄存器和2个独立的40位累加器。

● 17×17位并行乘法器,与40位专用加法器 相连,可用于进行非流水线的单周期乘法-累加运算 。

桶形 移位器

DSP技术讲义,2010

A(15-0)

4K-Word Program ROM

16K-Word Program/Data RAM

D(15-0)

乘加器

17X17乘 法 器 40位 加 法 器

舍入饱和

移位器

算术逻辑单元

40位 算 术 逻 辑 单 元 Viterbiy译 码 器 指数编码器

累加器

DSP技术讲义,2010

DSP技术讲义,2010

DSP技术讲义,2010

2.4 TMS320C54x的中央处理器CPU

CPU包括下列基本部件: ① 40位算术逻辑运算单元ALU; ② 2个40位的累加器A和B; ③ 支持-16~31位移位范围的桶形移位寄存器; ④ 能完成乘法-加法运算的乘法累加器MAC; ⑤ 16位暂存寄存器T; ⑥ 16位转移寄存器TRN; ⑦ 比较、选择、存储单元CSSU; ⑧ 指数译码器; ⑨ CPU状态和控制寄存器。

DSP技术讲义,2010

2.4.1 算术逻辑运算单元ALU

CB15~CB0

T CB

DB15~DB0

A

MUX

DS

MUX

桶形移位 器输出

A

B

MUX

A MAC输出 M

B U

SXM 符号ctr

符号ctr SXM

Y

X

ALU

OVM C16 C OVA/OVB ZA/ZB TC

DSP技术讲义,2010

2.4.2 累加器A和B

DSP技术讲义,2010

C24x的CPU

Data write bus(DWEB) Data read bus(DRDB)

Program read bus(PRDB)

MUX

31 16

15

0

Input shifter(32 bits)