ADSP-BF534_08中文资料

AD534中文资料

特点Pretrimmed到60.25%最大4象限错误(AD534L)所有输入(X、Y和Z)差别,高阻抗为[(X1 - X2) (Y1 - Y2) /10 V] + Z2传递函数称因素可调整提供由X100获取低噪声设计决定:90 mV rms,10赫兹10处理有差别的比率和百分比计算的千赫便宜,整体建筑优秀长的期限稳定应用高质量模拟信号代数和三角函数综合多种频率,高冠rms对dc转换准确电压控制振荡器和过滤器可利用在芯片形成产品说明AD534是一台整体laser被整理的四象限多钳子分切器仅安排准确性规格早先被发现在昂贵的杂种或模件产品。

一个最大增殖错误±0.25%为AD534L被保证,不用任何外在饰物。

优秀供应拒绝、低温系数和在芯片薄膜电阻器的长的期限稳定和被埋没的Zener 参考甚而在用途的不利条件下保存准确性。

它是充分地提供差别的第一个乘算器,高阻抗操作在所有输入,包括Z输入,很大地增加它的导电线ibility和易用的特点。

换算系数是pretrimmed到10.00 V的标准价值; 通过外在电阻器,这可以减少到价值低到3 V。

应用广泛领域和几个等级的可及性称赞这个乘算器作为第一个选择为所有新的设计。

AD534J (±1%最大错误),AD534K (±0.5%最大)和AD534L (±0.25%最大)为操作指定在0°C对+70°C温度范围。

AD534S (±1%最大)和AD534T (±0.5%最大)指定在延长的蛋彩画ture范围,- 55°C对+125°C。

所有等级是可利用的在她metically密封了TO-100金属罐头和TO-116陶瓷垂度包裹。

AD534J、K、S和T芯片也是可利用的。

REV. 模拟装置装备的B信息认为是准确和可靠的。

然而,责任没有由模拟装置承担为它的使用,亦不对专利或也许起因于它的用途第三方的其他权利的任何违反。

基于ADSP-BF533光纤熔接监控设计

第30卷 第2期2007年4月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.2Ap r.2007Design of Fused Fiber Splicing Mon itor ing Technology B ased on ADSP 2BF5333Z H AO Wen 2xi a n ,L I U J in 2ga o ,L I W ai 2y un(Dept.of Elect ronics Sci ence Technol ogy ,East Chi na Normal Uni versit y ,S hang hai 200062,China)Abstract :A systemic design to remot el y monitor fused fi ber splicing ba se d on AD I ADSP 2B F533wit h real -t ime characteri stics a nd hi gh p reci sion i s descri bed.The analog video si gnal i s di gitized i n t he video deco de module ADV7183B and t he digit al vi deo signal i s encoded i n t he video encode module ADV7171.Hi gh ca 2paci t y exter nal SDRAM memory i s use d to buffer t he digit al video f rame.The cent ral cont rol a nd di gital vi deo da ta processi ng unit is complet ed i n ADSP 2B F533.The system ca n do real time video compression ,so analog video from different vi dicons can display on t he same mo nitor and t he f used fi ber splici ng process can be re motel y monitored.K ey w or ds :ADSP 2B F533;ADV7183B ;ADV7171;vi deo decode ;video encode EEACC :1265;6430;6140基于ADSP 2BF533光纤熔接监控设计3赵雯娴,刘锦高,李外云(华东师范大学电子科学技术系,上海200062)收稿日期62323基金项目上海市科研计划项目的资助(5)作者简介赵雯娴(82)女,华东师范大学信息学院电子系在读硕士研究生,主要研究通信与信息系统,5@摘 要:介绍了在光纤熔接监控系统中基于ADI ADSP -B F533的设计方法,用于实时地、高图像精度地远程监控光纤熔接过程.其中视频解码模块ADV7183B 完成模拟视频信号数字化,视频编码模块ADV7171完成数字视频信号模拟化,同时采用外部SDRAM 存储器作为数字视频帧缓存,整个系统以ADSP 2B F533为核心模块进行视频编解码的控制和数字视频数据的处理.此系统可以进行实时的视频压缩处理,完成多个视频源的模拟视频同时显示在一台模拟监控器上,分辨率高,达到了远程实时监控光纤熔接过程的目的.关键词:ADSP 2BF533;ADV7183B ;ADV7171;视频解码;视频编码中图分类号:TN 27 文献标识码:A 文章编号:100529490(2007)022******* 光纤熔接监控系统可以用于远程控制光纤的熔接,和一般的监控系统相比具有实时性强和图像精度高的特点,这就要求核心芯片必须具备强大的MCU 功能,能够对视频编解码芯片进行很好的配置,同时还必须具备强大的DSP 功能,尤其要在数字视频数据处理方面性能突出,经过项目组的再三斟酌,最后决定选用ADI 公司的ADSP 2B F533作为核心芯片实现对视频编解码芯片的控制和数字视频数据的处理.系统结构框图如图1所示.系统的工作流程大致如下:两个模拟视频摄像头分别从两个角图1 系统结构框图度对光纤的熔接过程进行拍摄,摄取的模拟视频信号经过ADV7183B 视频解码,解码后的数字视频数据存储在外部SDRAM 中,并通过ADSP 2B F533进:20001:012:.行数字视频数据处理,处理后的数字视频数据经过ADV7171视频编码,最后实现在模拟监视器上同时显示两个角度的视频,从而达到监控的目的.1 主要功能模块介绍1.1 A DSP 2BF533美国模拟器件公司(ADI)是全世界领先的高性能信号处理集成电路制造商,是全球主要的可编程DSP 芯片供应商之一.Bl ackfin DSP 是该公司16位产品的一个大系列,采用ADI 和Intel 联合开发的微信号体系结构(MSA),集DSP 和MCU 功能于一身,指令集增加了专门指令以支持多媒体视频和音频功能,特别适合于完成视频、音频等数字信号处理.ADS P 2B F533是Blackfi n DSP 系列的一个成员,拥有16位定点DSP 内核,可以实现600M Hz 的持续工作,内核包括2个16位乘法器,2个40位累加器,2个40位算术逻辑单元(AL U ),4个8位视频ALU ,以及1个40位移位寄存器.ADSP 2B F533的结构体系将存储器构造成统一的4G B 地址空间,用32位地址寻址.包括内部存储器、外部存储器、PCI 地址空间和I/O 控制寄存器在内的所有资源,在这个统一的地址空间中独立占据各自的一段.此外,ADSP 2B F533还有12通道的DMA ,3个支持PWM 的定时/计数器以及满足I TU 2656数字视频格式的并行外部接口(PPI)[1].1.2 视频解码芯片ADV 7183BADV7183B 是ADI 公司推出的模拟视频解码芯片,能够将兼容国际标准N TSC 、PAL 或S E 2CAM 的模拟基带视频信号转换成兼容I TU 2656标准的8/16位YCrCb 型4∶2∶2数字视频数据.ADV7183B 集成了3个54M Hz 、10位的模数转换器(ADC ),具有12路模拟视频输入信道.ADV7183B 处理功能强大,能够处理CVB S ,Y/C 和YPr Pb 等不同格式的模拟视频信号,实现对输入模拟视频信号的亮度色度分离、采样,同步信号的抽取等功能.ADV7183B 采用I 2C 与微处理器实现通信[2].1.3 视频编码芯片ADV 7171ADV7171是ADI 公司推出的综合数字视频编码芯片.ADV7171具有4个高质量的10位视频数字模拟转换器(DAC ),可将兼容ITU 2656标准的8/16位Y Cr Cb 型4∶2∶2数字视频数据转换成兼容国际标准的N TS 、L 等制式的模拟视频信号,其中D 输出VBS 信号,D B 输出BL U VB S U 信号,D 输出R D S 2V C/V 信号,DAC D 输出G R EEN/S 2Vi deo Y/Y 信号.每个DAC 都可以独立工作和进行单独控制,而不影响其他DAC 的输出.ADV7171同样采用I 2C 与微处理器进行通信[3].2 系统实现2.1 ADSP 2BF533和编解码芯片的I 2C 通信过程ADSP 2B F533通过I 2C 通信对ADV7183B 和ADV7171进行配置.由于编解码芯片的ALSB 接地,所以读写ADV7183B 的器件地址分别为0X41(读操作)和0X40(写操作);读写ADV7171的器件地址分别为0X 55(读操作)和0X54(写操作).I 2C 通信数据传输时序如图2所示,其中S 是开始信号,P 是结束信号.图2 I 2C 通信时序图ADS P 2B F533和编解码芯片的通信流程大致如下:①B F533发送开始信号,实现方法是在保持SCL K 线高时,SDA 线由高变低;②BF533发送8位器件写操作地址(ADV7183B 为0X40,ADV7171为0X 54);③B F533等待AC K 信号,AC K 信号是在第9个时钟脉冲时SDA 线被拉低;④B F533发送8位编解码芯片寄存器地址值;⑤B F533等待AC K 信号;⑥B F533发送8位寄存器配置值;⑦B F533等待AC K 信号;⑧B F533发送结束信号,实现方法是在保持SCL K 线高时,SDA 线由低变高.2.2 编解码芯片的配置2.2.1 解码芯片的配置ADV7183B 的12路模拟视频输入信道通过不同的配置可以支持11路CVB S 信号、3路Y C 信号和2路YPr Pb 信号.通过INSEL 寄存器位可控制输入的类型和信道的选择.整个处理过程通过I 2C 通信对相关寄存器进行配置.下面是部分配置程序:void Init_ADV (void){ int te mp Reg ;te mpReg =3p Fla shA_Port A_Out ;clr_bit (tempReg ,R ST_7171);3p FlashA_PortA_Out =temp Re g |(1<<RST_7183)|(1<<P PICL K_ADV7183_SEL ECT );te mpReg =3p FIO_IN EN ;3FIO_IN N =R |(<<DV 83_O );设置B F533的F 寄存器R =3FIO_DIR ;506第2期赵雯娴,刘锦高等:基于ADSP 2B F533光纤熔接监控设计C PA AC A C AC E/C /AC C E /ideop E temp eg 1A 71E //P te mp eg p3p F IO_DIR=te mpReg|(1<<ADV7183_O E);//设置B F533的P F2引脚为输出引脚tempRe g=3pF IO_FL AG_C;3p FIO_FLA G_C=tempReg|(1<<ADV7183_OE);} 2.2.2 编码芯片的配置ITU2656YCrCb型4:2:2数据以27M Hz的速率输入到ADV7171之后,被分成Y、Cr、Cb三路信号,Y信号范围为16到235,CrCb信号范围为16到240.通过正确的寄存器配置,产生需要的模拟基带视频信号.下面是部分配置程序:void Init_DAV(void){ int tempReg,i;tempRe g=3pFlashA_Po rtA_Out;clr_bit(tempReg,R ST_7183);clr_bit(tempReg,PPICL K_ADV7183_SEL ECT);3pFlashA_PortA_Out=tem pReg|(1<<RS T_7171);} 2.3 ADSP2BF533并行通信接口PP IPPI是半双工形式的并行外部接口,具有双向端口,最大可输入/输出16位数据.它有1个专用的时钟引脚、3个帧同步引脚、4个专用的数据引脚和12个P F复用的数据引脚.应用系统中的ADV7183B和ADV7171共用P PI接口数据引脚PP[3:0],并通过程序配置将B F533芯片的P F管脚PF[15:12]设为PP I数据管脚,从而实现8位PPI数据传送.ADV7183B、ADV7171和B F533的连接如图3所示.图3 BF533P PI连接图 PP I支持ITU2656[4]输入的3种模式和输出的1种模式.ITU2656的3种输入模式是:活动视频模式、VBI模式和整场模式.应用系统采用活动视频模式,在该模式中,PP I不读入图像结束数据EA V和开始数据SAV之间的所有数据以及V=1时的所有数据,同时插入在消隐信号中的控制字被PPI过滤掉,P PI只有在检测到SAV信号时才开始读入数据,在PP I_FRAME寄存器中设置每帧活动视频的行数.在这种模式下,发送视频流之前数据和控制代码必须在内存中设置好.输出以二维DMA的方式实现.2.4 直接存储访问方式DMABF533通过使用二维DMA方式实现存储器空间和编解码器之间的数字视频数据传送.数据传送使用PP I通道,由于B F533只有一个半双工PPI收发的DMA通道[7],同时进行数据收发容易产生数据冲突,所以系统采用不同的读取方式进行和编解码器之间的数据传送;DV83B的数据输入到B F533存储器采用单次数据传送,即一次传输任务完成之后,自动停止该DMA通道,此时运行状态标志位DMA_RU N从1变为0,但DMA配置寄存器的DMA使能位没有变化.若要重新启动该DMA 通道,只要重新设置DMA配置寄存器即可.将B F533存储器图像数据输出到ADV7171时采用自动缓冲模式,即当一个传输任务完成之后,控制寄存器将被它们的原始设置值重载,这样DMA可以不断重复同一个操作,直到将DMA配置寄存器的DMA使能位清零为止.DMA初始化程序大致如下[526]:void Init_DMA_Input(void){3pDMA0_CON FI G=0;3pDMA0_S TAR T_ADDR=SDRAM INADD;//DMA目标地址3pDMA0_X_COUNT=X_RAM_Length_In;//X_RAM_ Le ngth_In个32位数字图像数据传输3pDMA0_X_MODIF Y=0x4;//32位数字图像数据传输3DM_Y_OUN T=Y_R M_L_IN;Y_R M_ L_IN个3位数字图像数据传输3DM_Y_MODIF Y=x;3位数字图像数据传输606电 子 器 件第30卷A71p A0C A ength//A e ngth2p A004//23pDMA0_PERIP HERAL_MAP=0x0;//使用PP I外设3pDMA0_CONF IG=DMAEN|DI_EN|WNR|WD2 S IZE_32|R ES TAR T|DMA2D|DI_EN;//设置DMA配置寄存器}void Init_DMA_Output(void){3pDMA0_CONF IG=0x1090;3pDMA0_S TAR T_ADDR=SDRAMOU TADD;3pDMA0_X_COUN T=X_RAM_Lengt h_out;3pDMA0_X_MODIF Y=0x1;3pDMA0_Y_COUN T=Y_RAM_Length_out;3pDMA0_Y_MODI F Y=0x1;}2.5 数字视频数据处理应用系统处理存储在外部SDRAM中的I TU2 656YCr Cb型4∶2∶2格式的数字视频数据,过程如下:两个模拟摄像头同步摄取的两场模拟视频经过ADV7183B解码成为数字视频数据之后通过B F533的PP I DMA通道,滤除消隐数据保留活动数字视频数据,将这两场活动数字视频数据存储在SDRAM的一段连续空间中.然后B F533对其中一场的第一行进行奇数位像素数据的采样,采样数据存储在SDRAM的另一段空间中,紧接着对另一场的第一行进行偶数位像素数据的采样,采样数据紧接着前一段采样数据连续存储.用同样的方法依次采样两场数字视频的剩余行.最终存储的采样数据经过ADV7171编码就可以实现两个摄像头拍摄的画面在模拟监示器上左右同时显示的效果.采用不同的采样方法可以实现不同的显示效果,比如两幅画面上下显示或层叠显示等[8].外部SDRA M和B F533的引脚连接如图4所示.图4 外部SDRAM和ADSP-B F533引脚连接图3 结束语应用系统在Blackfi n系列的软件开发环境Vi s2 ual DSP++3.5下开发和调试.系统的设计充分利用了ADSP2B F533强大的控制和数字信号处理功能,结合视频编解码芯片,实现了监控光纤熔接过程的目的,实时性好,图像精度高,能够用于远程控制光纤的熔接.该系统后续开发的空间很大,在今后的设计中可以考虑增加更为复杂完善的功能.参考文献:[1] Analo g Devices[R],ADSP2B F533Blackfin TM Pro cessorHardware Reference,Preli m i nary Revi s io n,2003.3:2452503.[2] Analog Devices[R],Mul tifor m at SD TV Vi deo Deco derADV7183B Data Sheet,Revi s io n0,2004.9:60289.[3] Analo g Devi ces[R],Di gi t al PAL/N TSC Video Encoder wit h102Bit SSAF and Advanced Power Managem ent ADV7170/ADV7171Dat a Sheet,Revi s i on A,2001:21223.[4] I TU2R B T.65624.Int erfaces for Digit al C o m po nent Vi deo Sig2nal s i n5252li ne and6252li ne Televi sion Syst ems Op erati ng att he4:2:2L evel of Recommendatio n ITU2R B T.601,1998[S].[5] Cappell ini V,C o nst anti ni des A.G.Digit al S i gnal Processing[M].Academic Press Inc.L td,1980:822109.[6] Samuel D Steams,Rut h A David.S i gnal Proces s i ng Algo2ri t hms[M].Prentice Hall,1988:2012206.[7] 陈峰.Blackfin系列DSP原理与系统设计[M].北京:电子工业出版社,2004:612119.[8] 张新芝.电视技术[M].北京:高等教育出版社,2003:102100.706第2期赵雯娴,刘锦高等:基于ADSP2B F533光纤熔接监控设计。

基于ADSP-BF533的图像匹配处理机的硬件平台设计

( .天津大学 1 摘 天津 307 ; 2 0 0 2 .太原理工大 学 太原 002) 30 4

要 :图像 匹配处理 机是 目标 识别系统的重要组成部 分 , 是机器人视觉 系统 的核心技术 , 在现 代信号处理特别 是 图 、 l h和 双端 口 Fa s

Ab ta t Pitr thn n i o tn ato a g trc g io y tm. I h e c n lg f mp trvso sr c: cu emac ig i a s mp ra tp r f r e e o nt ns se t i t st ek yt h oo yo i e o c u e iin

关键 词 :A PB 5 3 DS -F 3 ;图像处理 ;图像匹配

中 图 分 类 号 :T 3 1 4 P 9.1 文 献 标 识 码 :A

Ha d r sg fpit r a c ng s se a e o ADS BF5 3 DS r wa ede i n o c u em thi y t m b s d n P- 3 P

维普资讯

电

子

测

量

技

术

第3 0卷 第 1 期

ELE r R0NI M EAs 乐 EM [ r TECHN0L C I E r 0GY

20 0 7年 1月

基 于 ADS - F 3 P B 5 3的 图像 匹配 处 理 机 的硬 件 平 台设 计

像处理 中占有 重要地 位 。本文 提 出 了 以 A PB 53作 为核 心 处 理器 并 配 以外 围器件 s 、_ F 3 【

R AM 组 成图像匹配处理机的硬件方案 。本 文对该硬 件设计 方案 进行 了详 细分 析 和论 述 , 给 出了硬件 总体 实现框 并 图。该处理 机硬件 系统结构简单 , 实时性好 , 可靠性高 。实验结果证 明, 本系统完全可 以实时可靠地完成图像匹配任务 。

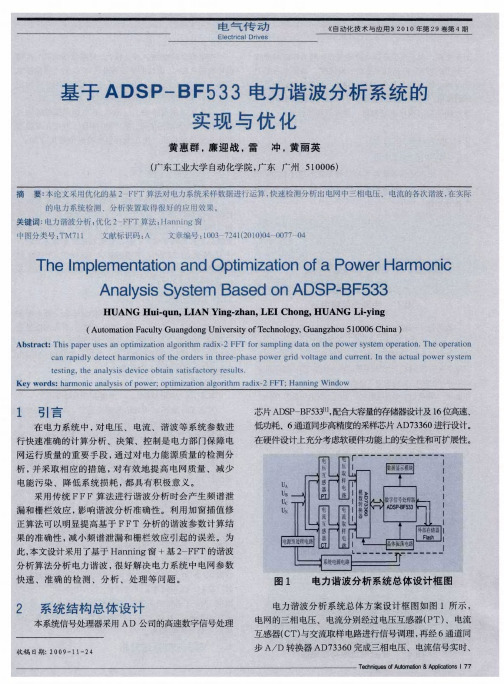

基于ADSP-BF533电力谐波分析系统的实现与优化

频率附近波动 。用 F T进行谐波 测量时 , F 首先对 信号进 行采样 , 然后建立数据 窗 口, 获取一组 F T分析的数据 , F 经过 F T 变换 , F 得到谐波结果 。在 以上过程 中, 为避免

引起 混 叠 , 须 满 足 采 样 定 律 [ 必 。

l E 这—干扰, 可在电源输入端并接一个 2D 8K压敏电阻R, 0 61

自动 化 技 术 与 应 用 2 1 0 第 2 0年 9卷第 4期

序流程 图如图 5 并在 电力谐波分析系统 中运行 良好 , , 有效

算 法等方法 , 以提 高谐波分析 系统的总体性 能、准确性 和快 速性 。系统投运后取得 了 良好的运行效 果 , 通过对 用户 的用 电负荷状 态进行分析 、 比较 , 有效地 掌握用户

数)取 k=1, , 就可在 个采样数据之中均匀抽取 l 8个 2

U。

数据, 满足了采样 频率和信号频率同步 。从 中可以看 出, 采样频率越 高,z , 越大 , 数据抽取越均匀 。从而实现采样

频 率和信 号频率 同步 。

U

图 4 交流 电压取样 电路 图

4 3 基 2 F T 法分析 . 一F算

和栅栏 效应l , 4 影响谐波 测量 准确度 。 1

l A 1

I ^ 2

在 系统 中采用基 一 2的 1 2 0 4点 F T算法 , 8 F 即 个信 号周 期 ,每一 个 信号 周 期需 要 采 集 128个 数据 。把

A 730 D 36 的采样速率置为8;s,S  ̄ D P从信号上升期过 /

电阻值的大小可 以根据压敏电阻的特性选择 ; 为防止供 电电 网电压内带有高频干扰源对系统的同步振荡电路及数据采集 等电路产生影响, 电源中并联电容器 C, 在 电容器可以通低频 阻高频 ; 在每相上串接共模 电感 L 防 I , 卜 系统共模信号的干扰。

ADSP—BF531在嵌入式语音识别系统中的应用

Vo . 0 12

No 1 .2

电子 设计 工程

El cr ni sg g n e i g e to c De i n En i e rn 来自21 0 2年 6月

Jn 2 1 u.02

AD P B 5 1在嵌入 式语音识别 系统 中的应用 ・ — F3 S

Ap l a in o pi t fADS BF 3 n e b d e p e h r c g i o y t m c o P— 5 1 i m e d d s e c e o n t n s se i

W ANG e— i n W iq a g

( I C iaAib reMisl Ac d my u y n 71 0 AV C hn ron s i a e ,L oa g4 0 9,C ia e hn )

通 过设置 E P O 存储 器 的 SI 模式 启动 ( ER M P主 即设 置

A A

0眦 L D 个 P D F K O F l Ⅷ D I S r s∞ S D D J B D = 1 , 实 配 置 B 5 1为连 接一 S BS 2存 储 器 的 主 设 MO E I )现 F3 I

备 和存 储 器 的 加 载 。为 了 正 常 工 作 , 加 载 模 式 需 要 在 M S 该 IO 加 上拉 电 阻 。 否 则 , F 3 将 从 MIO 引 脚 读 取 到 O F ( B51 S xF 即

图 1 系统 硬件 结 构 图

Fi .1 Ha d r tu t r ft e s se g r wa e sr c u e o h y t m

种 主要 方 法 。 虽 然 在 孤 立 词 语 音 识 别 中取 得 了不 错 的性 DI W

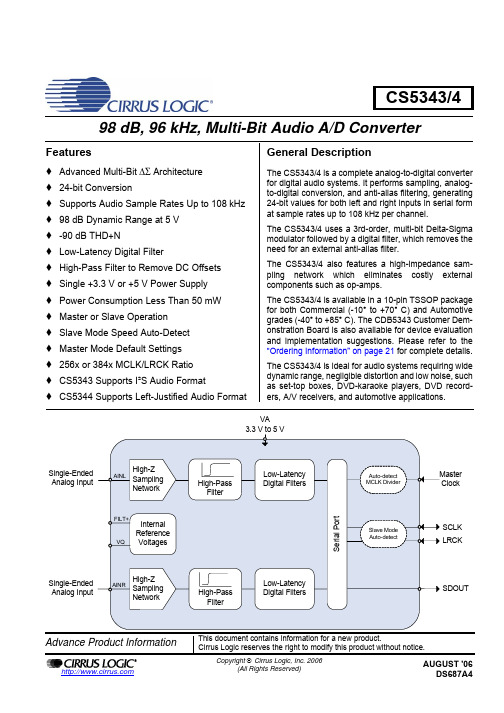

CS5343中文资料

Master Clock

SCLK LRCK

Serial Port

Single-Ended Analog Input

High-Z AINR Sampling

Network

High-Pass Filter

Low-Latency Digital Filters

SDOUT

The CS5343/4 also features a high-impedance sampling network which eliminates costly external components such as op-amps.

The CS5343/4 is available in a 10-pin TSSOP package for both Commercial (-10° to +70° C) and Automotive grades (-40° to +85° C). The CDB5343 Customer Demonstration Board is also available for device evaluation and implementation suggestions. Please refer to the “Ordering Information” on page 21 for complete details.

Advance Product Information

This document contains inic reserves the right to modify this product without notice.

SPECIFIED OPERATING CONDITIONS ............................................................................................... 5 ABSOLUTE MAXIMUM RATINGS ......................................................................................................... 5 ANALOG CHARACTERISTICS - COMMERCIAL GRADE .................................................................... 6 ANALOG CHARACTERISTICS - AUTOMOTIVE GRADE ..................................................................... 7 DIGITAL FILTER CHARACTERISTICS ................................................................................................ 8 DC ELECTRICAL CHARACTERISTICS ................................................................................................ 8 DIGITAL CHARACTERISTICS .............................................................................................................. 9 SYSTEM CLOCKING AND SERIAL AUDIO INTERFACE ................................................................... 10 3. TYPICAL CONNECTION DIAGRAM ................................................................................................... 12 4. APPLICATIONS ................................................................................................................................... 13 4.1 Operation as Clock Master or Slave ............................................................................................... 13

ADSP-BF531_cn

每个 MAC 每周期可完成一个 16 位乘 16 位的乘法运 算,并把结果累加到 40 位的累加器中。支持符号型和无符

-2-

对于某些指令,两个 16 位 ALU 操作可以同时在寄存 器对(运算寄存器的高 16 位和低 16 位)中执行,也可以 使用第二个 ALU,进行四个 16 位运算。

40 位的移位器可以执行移位和循环移位,可以用于标 准化、提取和存储等操作。

任务。这些指令包括位操作(例如域提取和计算总数)、模 232 乘法、除法、饱和与舍入、符号/指数检测等;专用的一 套视频指令包括字节对准和压缩操作,16 位和 8 位截断加,

程序控制器控制指令执行的顺序,包括指令对准和译 码。对于程序流程,程序控制器支持相对于 PC 和间接条 件跳转(支持静态分支预测)。硬件提供对零耗循环的支持。 这种结构是完全互锁的,这就意味着,当有数据相关的指 令时,不存在可见的流水线影响。

地址算术单元能够提供两套地址,用于从存储器中同 时进行双存取。一个多端口寄存器组由 4 套 32 位的索引、 修改、长度、基地址(用于循环缓冲)寄存器和 8 个另外 的 32 位指针寄存器(用于 C 风格的索引堆栈操作)组成。

开发板精品网www.mcu361.com为您提供各种开发板和电子技术资料

2003年3月

初步技术数据

ADSP-BF53x

号型数据格式,舍入与饱和等操作。

ALU 除执行一套传统的 16 位或 32 位数据的算术和逻 辑运算外,还包含许多特殊指令用于加速不同的信号处理 8 位平均操作,8 位减法/绝对值/累加(SAA)操作等;还提 供有比较/选择和矢量搜索指令。

基于ADSP BF533和FPGA的接口设计

信号 产生 组件 、 定位 通信组 件 、 电源 、 终端 、 数据 处理

组件 、 线 座及 天线 驱动 等部分 组成 。 天

由于 主 站 和用 户 机 组成 结 构 大致 相 同 , 给 出 特 其 中主站 系统 简要 框 图 , 图 1所 示 。从 图 中 容易 如 看 出 : 系统 主要 由终端 、 此 数据 处 理 组 件 、 位通 信 定

( 址解码模块) 地

数 据 采 集 模 块

图 2 FP GA 软 件 流 程 图

图 3 地 址 解 析 模 块

从 图 2中 较 易 看 出 , P F GA 与 AD P B 5 3连 S —F3

表 1 地 址 解 析 表

地 址 低 四位

0 0 00

0 001 O O O1 O O11

的相 应 模 块 选 择 情 况 。

西 悦 , 一 雠 j 一

一

接 口模 块 的 F GA 软 件 流 程 如 图 2 示 。 P 所

一。… 。 。 一 一~~

一

地 址 总 线 ≥ 片 选 信 号 线

A D D RESS ECO D E D

数 据 发 送 模 块 门 限设 置 模 块

ADSP-BF533上的H.264解码器优化实现

关于CPU, BF533 具有 16 位定点DSP 内 可以采用600M z 核, H 的 持续工作时钟, 小型寻址空间为4GB; 关于存储器, BF533 的Ll

指令存储器包括 80KB SRAM, 其中 16KB 可配置成4 路联合 Cache, L1 数据存储器包括 2 个 32KB SRAM 的BANK, 每个 BANK均由2 个 16KB SRAM组成, 其中 1 个 16KB 可配置成 Cache; 关于UO接 口, BF533 支持 12 通路DM 操作, A 支持片外同步或异步存储器; 关于功耗, BF533 的核心供电电 压为0.7- 1.2V, 1 部分为33V} /0 3. 基于Blackfin 的H.264 解码器的优化实现

(4)扶壁数和中 距

lm 墙应有的扶壁数 n=266.3/318.3=0.837 个

担曦

新砌技今 盛 苦 伞 今遂挤 解

;会夏 之舰 窦

扶 中 1 2一 1 9 (in) 壁距 , .7

取 为1.2m

车 乍

即在6m 的内横墙上需4 个扶壁柱, 平均中距为 1.2m 3、 加固方法 (1) 由 于底层己有贯通的竖向裂缝, 施工前应进行卸载, 所以 用钢顶撑 托 板为 步 墙 力, 用 力 法 4裂缝。 支 楼 进一 减少 体压 另 压 灌浆 修 (2) 将新旧砌体接触面间的 粉刷层剥去, 并冲洗干净。 (3) 采用两侧加砖扶壁柱的方法加固一、二层内横墙, 在扶壁 柱部位原墙灰缝打人间距为240 的96 连接筋, 如果打人连接筋有困 难, 可先用电钻钻孔, 然后将连接筋打人,连接筋的水平间距不大 于 120mm, 在开口 边扎c 的 p6 封口 如图3 示 筋, (4) 采用M 砖, u10 M10 的 混合砂浆砌筑扶壁柱, 砌至楼板下 5 皮砖时, 在砂浆中掺加水泥膨胀剂, 以保证补强砌体有效地发挥

ADS5444_08中文资料

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

AVDD to GND DRVDD to GND

Analog input to GND

Clock input to GND

CLK to CLK

Digital data output to GND

Operating temperature range

Maximum junction temperature

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

元器件交易网

RECOMMENDED OPERATING CONDITIONS

SUPPLIES

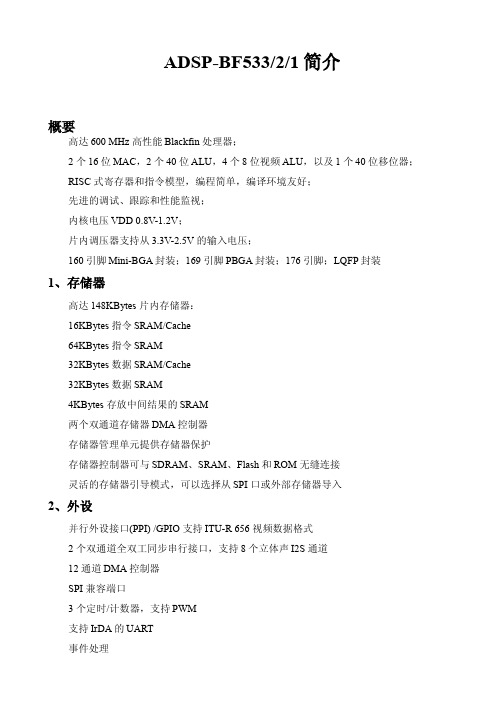

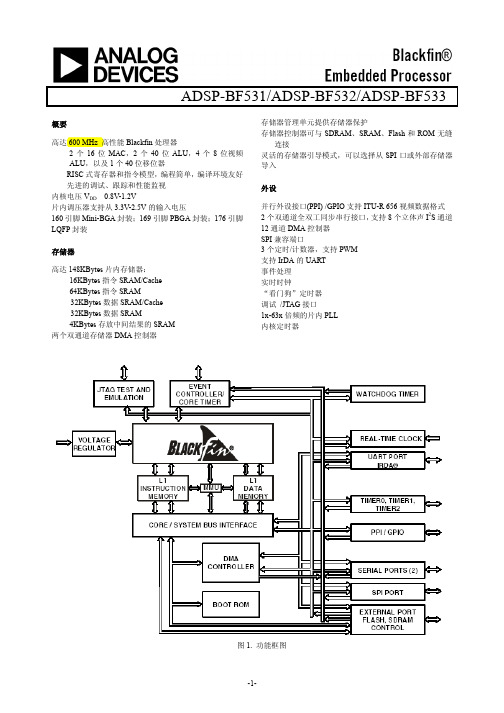

ADSP-BF533简介

ADSP-BF533/2/1简介概要高达600 MHz 高性能Blackfin 处理器;2 个16 位MAC,2 个40 位ALU,4 个8 位视频ALU,以及1 个40 位移位器;RISC 式寄存器和指令模型,编程简单,编译环境友好;先进的调试、跟踪和性能监视;内核电压VDD 0.8V-1.2V;片内调压器支持从3.3V-2.5V 的输入电压;160 引脚Mini-BGA 封装;169 引脚PBGA 封装;176 引脚;LQFP 封装1、存储器高达148KBytes 片内存储器:16KBytes 指令SRAM/Cache64KBytes 指令SRAM32KBytes 数据SRAM/Cache32KBytes 数据SRAM4KBytes 存放中间结果的SRAM两个双通道存储器DMA 控制器存储器管理单元提供存储器保护存储器控制器可与SDRAM、SRAM、Flash 和ROM 无缝连接灵活的存储器引导模式,可以选择从SPI 口或外部存储器导入2、外设并行外设接口(PPI) /GPIO 支持ITU-R 656 视频数据格式2 个双通道全双工同步串行接口,支持8 个立体声I2S 通道12 通道DMA 控制器SPI 兼容端口3 个定时/计数器,支持PWM支持IrDA 的UART事件处理实时时钟“看门狗”定时器调试 /JTAG 接口1x-63x 倍频的片内PLL内核定时器图1. 功能框图3、概述处理器比较ADSP-BF531/2/3 处理器是Blackfin 系列产品的成员,融合了Analog Devices/Intel 的微信号结构(Micro Signal Architecture) (MSA)。

Blackfin 处理器这种体系结构将艺术级的dual-MAC 信号处理引擎,简洁的RISC 式微处理器指令集的优点,以及单指令多数据(SIMD)多媒体能力结合起来,形成了一套独特的指令集结构。

ADSP-BF531/2/3 处理器的代码和管脚完全兼容,它们之间的差别仅仅在于具有不同的性能和片内存储器容量。

第三课-ADSP处理器串行外设,定时器和GPIO.

ADSP处理器的串行外设 定时器

GPIO

ADSP处理器的串行外设

SPORT接口

SPORT概述

ADSP-BF533处理器提供2个双通道同步串行端口(SPORT0和 SPORT1)来完成串行和多处理器的通信工作。每个SPORT都有2套 独立的发送和接收引脚,支持I2S立体声8通道 。 每个SPORT都支持3到32位长度的串行数据字,以最高有效位在前或 最低有效位在前的格式传送;每个发送和接收端口在无论每个数据字 有无帧同步信号的情况下都能运行。 每个SPORT都能根据ITU推荐的G711标准完成A律和μ律压扩。 处理器能够链接或串接SPORT和存储器之间的多个DMA序列 。

TFS TCLK RCLK RFS

SPORT的结构框图

要发送的数据首先写入发送缓冲TX

FIFO,然后进入发送寄存器 SPORT_TX,再经过A律或律压缩或者不压缩,进入移位寄存器当 中,最后从DTxPRI/DTxSEC引脚逐位移出。SPORT的接收部分, 从DRxPRI/DRxSEC引脚接收数据,等接收完整个字,经过A律或u 律扩张或者不扩张,进入SPORT的接收寄存器SPORT_RX,最后 进入处理器可以访问的RX FIFO

多通道操作

SPORT口可以工作在时分复用(TMD)的多通道操作模式下,这时一 个数据块的每个字节将占用一个独立的通道。可以从1024个通道中最 多选择连续的128个通道,某一个时刻只能从这128个通道中选择一个 通道对数据进行传送或者接收,但是发送方和接收方选择的128个通道 必须相同。SPORT在每个通道中可以进行以下操作:发送数据,接收 数据,同时发送和接收数据。 在多通道模式下,将TSCLK和RSCLK连接在一起,作为发送和接收数 据的时钟。发送方和接收方都用RFS作为帧同步信号 。

ADSP-BF53123中文手册

两个双通道存储器 DMA 控制器

存储器管理单元提供存储器保护 存储器控制器可与 SDRAM、SRAM、Flash 和 ROM 无缝

连接 灵活的存储器引导模式,可以选择从 SPI 口或外部存储器 导入

外设

并行外设接口(PPI) /GPIO 支持 ITU-R 656 视频数据格式 2 个双通道全双工同步串行接口,支持 8 个立体声 I2S 通道 12 通道 DMA 控制器 SPI 兼容端口 3 个定时/计数器,支持 PWM 支持 IrDA 的 UART 事件处理 实时时钟 “看门狗”定时器 调试 /JTAG 接口 1x-63x 倍频的片内 PLL 内核定时器

ADI Blackfin ADSP—BF531处理器

k p ) 11- 1 - C I u 。

t

一

74

今 日 电子

2008 年7 月

维普资讯

为 评 考 以 E

网友个人评论 , 不代表本杂志观 点 , 更多 论请参

/ h t t p ://w w w

. s e n i ]a p p s . C O U I . “ 1

p k . p h 『) 1

l l t l l) ://W W W . e p c F 5 3 1 处理器

A D S P — B F 5 3 l 是 13 1a c k f i n 处 理 器 系 列的 低 成本 切 入 点 。 它实现 了性 能 、 外设 集 成和 价格之 间的最佳平 衡 , 并且 是 对 成本最 为敏 感的 应 用 (包括便携 式测试 设备 、 嵌 入式调制解调器 、 生物特征识 别以及 消费类音频等 ) 的上 佳选择。

APM-AUTO-AUDIO-2014_ADI公司针对汽车信息娱乐主机和音频功放的芯片组解决方案

RGB解码器、标清/高清电视、6通道输入、NTSC/PAL/SECAM输入、 8位/16位BT656输出 CVBS解码器、标清电视、SE/差分输入、NTSC/PAL/SECAM输入、 8位BT656输出、电缆诊断 CVBS 解码器、标清电视、4/8通道输入、NTSC/PAL/SECAM输入、 8位BT656输出/MIPI输出、隔行转逐行

第四代SHARC,更高的MHz,硬件加速单元 第四代SHARC的低成本版本

第四代SHARC的低成本版本

低成本,通用 低功耗,多种外设,Lockbox 低功耗,通用 CAN PHY CAN PHY,导航/娱乐/音频处理 多种系统连接

硬件协处理器,众多功能,高模拟性能

同类最佳模拟性能

同类最佳模拟性能 单端/差分输入,电缆诊断 MIPI输出,隔行转逐行 单端/差分输入,MIPI输入出,带诊断 单端/差分输入,MIPI输出,隔行转逐行, 带诊断

方案编号:APM-AUTO-AUDIO-2014

ADI公司针对汽车信息娱乐主机和音频 功放的芯片组解决方案

应用描述 汽车信息娱乐主机和音频功放是汽车信息娱乐系统的主要部分。 信息娱乐主机系统集音频/视频播放、导航和远程信息系统于一体,为乘客提供舒适便利的驾乘体验。该系统的典型功能包括:FM/AM、 数字和卫星收音机、CD/DVD播放器、多媒体外设连接、后座娱乐、导航辅助、摄像头集成、蓝牙、以及其他电信连接能力。 独立的音频功放接驳多通道扬声器,在车内营造各种音效环境,提供高保真的音频享受。系统的典型功能包括强大的音效处理、车厢内 主动降噪以及引擎声效模拟。 系统要求和设计挑战 除了基本的音频/视频播放功能以外,新式信息娱乐主机和音频功放系统还应当能提供更高的音频/视频性能、更多连接、更轻松的人机 界面以及更低的功耗。更多的数字信号处理和更先进的音频算法集成到系统中,以便改善音响体验并补偿车内响应。 ADI公司解决方案 作为专注于高性能信号处理并在汽车电子领域拥有丰富经验的一家领先公司,ADI公司针对信息娱乐主机和音频功放系统提供广泛的通过 车规认证的产品。 我们提供多种多样的视频解码器、编码器和协处理器,其信号性能和功能在同类产品中首屈一指。我们的音频编解码器提供多种不同的 通道选项以及高信噪比/总谐波失真(SNR/THD)。我们提供具有高分辨率和强大噪声滤波功能的阻性及容性触摸屏接口器件,以及低功耗的 HDMI®/MHL/APIX2接口器件。 定点音频SigmaDSP®处理器和浮点音频SHARC®处理器已被广泛用作音频协处理器,以提供高性能及高效率的音频后处理和路由/混频。 屡获嘉奖的GUI工具SigmaStudio™让DSP编程变得像画流程图一样简单。 ADI的高度集成式Blackfin® DSP系列适用于多媒体连接、网络连接和软件音频处理应用。 除DSP以外,我们还提供广泛的软件模块,如解码器、环绕声和虚拟化模块。

基于ADSP-BF533处理器的去方块滤波器的实现及优化

直 边 缘

、

、

还会随着重构帧积累下去 , 从而严重地影响图像 的质

量 和压缩 效率 。 为 了解 决 这一 问题 , 24中 的去 方 H.6

~

平边缘

、 -

块滤波技术采用较为复杂的 自 适应滤波器来有效地去

了 A 在 D公司的 B 53处理器上对其进行优化的方法。试验结果表 明, F3 优化后的去方块滤波模块满足

了实时解码 的要 求。

关键 词 : 24 去 方块 滤波 ; D PB 53 算 法优化 H.6 ; A S —F3 ;

中图分类 号 : N 1 、 3 T 9 1 7

O 引 言

莫启敏 , 吴启 宗, 朱秀 昌

( 南京 邮电 大学通信 与信 息 工程 学院 , 苏省 南京 市 200 ) 江 10 3

摘

要 : 、6/ V H 24 A C视频标准 中去方块滤波对提 高重建图像质量起着重要的作用, 但较 高的计算

复杂度是 其应 用所 面 临的主要 问题 。 简要 介 绍 了 H.6 24中的 去方 块 滤 波 器的原 理 和 工作 过 程 , 出 提

P 块与O 块之 间的边缘

器 , 输 入 的 P 、0 Q 、 1进 行 滤 波 调 整 得 到新 的 对 1P 、0 Q Q 、0 如 果 内部 有虚假 边界 , 0P , 则进 一步 调整 Q 、 1的 1P

值。

当B S值是 4时 , 对应 的是采用 帧 内编码模 式 的 则 宏 块边 缘 , 采用 较强 的 滤 波 以达 到 增强 图像 质量 的 应 目的 。对 于亮 度分 量 , 条件 ( 0一Q <( 》2 若 1 P 0l ( ) + ) & as P 2 ) b( 2一P 成 立 , 选 择 5抽 头 滤 波 器 对 O) 则 P 、2进行 滤 波 , 0P 使用 较强 的 4抽 头滤 波器对 P 进 行 1 滤 波 ; 条件 不成立 , 只使用 较弱 的 3抽头 滤波器 对 若 则 P 0进行 滤 波 , P 、 2的值 保 持 不 变 。对 于 色 度 分 而 1P 量 , 上述条 件满 足 , 若 则对 P 0进行 3抽 头滤 波 , 条件 若

热电公司母线保护运行规程

热电公司母线保护运行规程220kV为双母线主接线,配置两套母线保护。

第一套母线保护选用深圳南瑞的BP2C-B12MS型微机母线保护柜;第二套母线保护选用南瑞继保的PRC15GA-409型微机母线保护柜,两套保护均含断路器失灵保护。

一、保护配置1、第一套母线保护柜:BP2C-B12MS型微机母线保护柜,柜内包括BP-2B型微机母线保护装置、BP-636型刀闸强制装置和打印机。

2、第二套母线保护柜:PRC15GA-409型微机母线保护柜,柜内包括RCS-915GA型微机母线保护装置和MNP3-A型母线模拟屏及打印机。

二、装置的具体配置1、第一套母线保护柜:BP2C-B12MS型微机母线保护柜1.1、B P-2B型母线保护装置:1.1.1、装置的应用范围及特点:本装置适用于500kV及以下电压等级,包括单母线、单母分段、双母线、双母分段以及3/2接线在内的各种主接线方式。

若母线保护接入3相CT的最大主接线规模为24个支路,若仅接入两相CT,母线上连接元件的最大规模为36个支路。

1.1.2、保护配置:实现母线差动、母联充电保护、母联过流保护、母联失灵保护、母联死区保护、母联非全相保护以及断路器失灵保护等功能。

1.1.3、装置的构成:装置采用标准14U(整层)机箱,后插式结构。

装置标配由交流板、管理CPU板、保护CPU、闭锁CPU板、出口板、信号板、开入板、电源板插件和总线背板(面板)组成。

1.1.4、主要性能特点:11.4.1、快速,高灵敏复式比率差动保护,整组动作时间小于15ms;1.1.4.2、自适应全波饱和检测器,差动保护在区外饱和时有极强的抗饱和能力,又能快速切除转换性故障,适用于任何按技术要求正确选型的保护电流互感器;1.1.4.3、允许电流互感器型号,变比不同,电流互感器变比可以现场设定;1.1.4.4、母线运行方式自适应,电流校验自动纠正刀闸辅助接点的错误;1.1.4.5、超大的汉字液晶显示,查询,打印,校时等操作,不影响保护运行;ι.ι.4.6、完善的事件和运行报文记录,与C OMTRADE兼容的故障录波,录波波形液晶即时显示;1. 1.4.7、灵活的后台通讯方式,配有RS-232,RS-422/RS-485通讯接口,支持电力行业标准通讯规约D1/T667-1999(IEC60870-5-103),同时支持IEC61850规约;1.1.4.8、采用旋转机柜,插件强弱电分开的新型结构,装置电磁兼容特性满足就地布置运行的要求。

处理器开关式稳压器设计时需要考虑的事项

图2 内部稳压器电路

内部稳压器电路(图2)包括一个基准电压、一图1 基本的降压变换器

期间,开关将电源电压(V in)接,使得电感中的电流急剧上升。

图3 Ton期间的开关特性

图4 Toff期间的开关特性

图5 电感波型图

图6 开关闭合时的损耗模型

图7 开关断开时的损耗模型

降压转换器通常工作在连续模式下。

在连续模图8 连续 IL和不连续IL的比较

在上面的不连续模式图中,T off和随后的T on之间的间隔被称为“死区时间”。

图9 电感电流

请注意,这个D值落在预计的30%-63%的电感可以满足上述的Lmin

∆I Lpp = 62mA

现在,可以计算最小电容。

已知10mV

大的电压纹波值,可以使用Cmin等式:

C min = 6.2µF

Z = 1.56Ω

为降低输出阻抗、改善瞬态响应,电容增加到

0.39 Ω。

F pole = 4109 Hz = ~5kHz

变为:

F zero = 26.5kHz

Fzero值在需要的稳定度范围内。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Blackfin and the Blackfin logo are registered trademarks of Analog Devices, Inc.Blackfin Embedded ProcessorADSP-BF534/ADSP-BF536/ADSP-BF537 Rev. EInformation furnished by Analog Devices is believed to be accurate and reliable.However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: Fax: 781.461.3113©2008 Analog Devices, Inc. All rights reserved.FEATURESUp to 600MHz high performance Blackfin processorThree 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifterRISC-like register and instruction model for ease ofprogramming and compiler-friendly support Advanced debug, trace, and performance monitoring0.8V to 1.3V core V DD with on-chip voltage regulation2.5V and3.3V-compliant I/O with specific 5V-tolerant pins 182-ball and 208-ball CSP_BGA packagesMEMORYUp to 132K bytes of on-chip memoryInstruction SRAM/cache and instruction SRAMData SRAM/cache plus additional dedicated data SRAM Scratchpad SRAM (see Table1 on Page3 for availablememory configurations)External memory controller with glueless support for SDRAM and asynchronous 8-bit and 16-bit memoriesFlexible booting options from external flash, SPI and TWI memory or from SPI, TWI, and UART host devicesMemory management unit providing memory protection PERIPHERALSIEEE 802.3-compliant 10/100 Ethernet MAC (ADSP-BF536 and ADSP-BF537 only)Controller area network (CAN) 2.0B interfaceParallel peripheral interface (PPI), supporting ITU-R 656 video data formats2 dual-channel, full-duplex synchronous serial ports (SPORTs), supporting eight stereo I2S channels12 peripheral DMAs, 2 mastered by the Ethernet MAC2 memory-to-memory DMAs with external request lines Event handler with 32 interrupt inputsSerial peripheral interface (SPI) compatible2 UARTs with IrDA support2-wire interface (TWI) controllerEight 32-bit timer/counters with PWM supportReal-time clock (RTC) and watchdog timer32-bit core timer48 general-purpose I/Os (GPIOs), 8 with high current drivers On-chip PLL capable of 0.5؋ to 64؋ frequency multiplication Debug/JTAG interfaceFigure 1.Functional Block DiagramADSP-BF534/ADSP-BF536/ADSP-BF537 TABLE OF CONTENTSFeatures (1)Memory (1)Peripherals (1)Revision History (2)General Description (3)Automotive Products (3)Portable Low Power Architecture (3)System Integration (3)Blackfin Processor Peripherals (3)Blackfin Processor Core (4)Memory Architecture (5)DMA Controllers (8)Real-Time Clock (9)Watchdog Timer (9)Timers (9)Serial Ports (SPORTs) (10)Serial Peripheral Interface (SPI) Port (10)UART Ports (10)Controller Area Network (CAN) (11)TWI Controller Interface (11)10/100 Ethernet MAC (11)Ports (12)Parallel Peripheral Interface (PPI) (12)Dynamic Power Management (13)Voltage Regulation (14)Clock Signals (14)Booting Modes (16)Instruction Set Description (17)Development Tools (17)Designing an Emulator-Compatible Processor Board (18)Related Documents (18)Pin Descriptions (19)Specifications (24)Operating Conditions (24)Electrical Characteristics (26)Absolute Maximum Ratings (29)ESD Sensitivity (30)Package Information (30)Timing Specifications (31)Output Drive Currents (53)Power Dissipation (55)Test Conditions (55)Thermal Characteristics (59)182-Ball CSP_BGA Ball Assignment (60)208-Ball Sparse CSP_BGA Ball Assignment (63)Outline Dimensions (66)Surface Mount Design (67)Ordering Guide (68)REVISION HISTORY3/08—Rev. D to Rev. EAdded new Automotive section. See Automotive Products 3Added all 600 MHz data. See Processor Comparison (3)Operating Conditions (23)Electrical Characteristics (25)Timing Specifications (30)Added detailed static and dynamic power data and ActivityScaling Factors.Static Current–Low Power Process(mA) (27)Static Current–High Speed Process (mA) (27)Activity Scaling Factors (28)Corrected General-Purpose Port Timing (45)Revised Figure30, 10/100 Ethernet MAC Controller Timing:RMII Receive Signal (51)Revised Ordering Guide (67)Rev. E|Page 2 of 68|March 2008ADSP-BF534/ADSP-BF536/ADSP-BF537Rev. E |Page 3 of 68|March 2008GENERAL DESCRIPTIONThe ADSP-BF534/ADSP-BF536/ADSP-BF537 processors are members of the Blackfin ® family of products, incorporating the Analog Devices/Intel Micro Signal Architecture (MSA).Blackfin processors combine a dual-MAC, state-of-the-art sig-nal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruc-tion, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture.The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors are completely code and pin compatible. They differ only withrespect to their performance, on-chip memory, and presence of the Ethernet MAC module. Specific performance, memory, and feature configurations are shown in Table 1.By integrating a rich set of industry-leading system peripherals and memory, the Blackfin processors are the platform of choice for next-generation applications that require RISC-like pro-grammability, multimedia support, and leading-edge signal processing in one integrated package.AUTOMOTIVE PRODUCTSSome ADSP-BF534 models are available for automotive appli-cations with controlled manufacturing. Note that these specialmodels may have specifications which differ from the general release models. For information on which models are available as automotive, see the Ordering Guide on Page 67.PORTABLE LOW POWER ARCHITECTUREBlackfin processors provide world-class power management and performance. They are produced with a low power and low voltage design methodology and feature on-chip dynamicpower management, which is the ability to vary both the voltage and frequency of operation to significantly lower overall power consumption. This capability can result in a substantial reduc-tion in power consumption, compared with just varying the frequency of operation. This allows longer battery life for portable appliances.SYSTEM INTEGRATIONThe Blackfin processor is a highly integrated system-on-a-chip solution for the next generation of embedded network-con-nected applications. By combining industry-standard interfaces with a high performance signal processing core, cost-effective applications can be developed quickly, without the need for costly external components. The system peripherals include an IEEE-compliant 802.3 10/100 Ethernet MAC (ADSP-BF536 and ADSP-BF537 only), a CAN 2.0B controller, a TWI controller, two UART ports, an SPI port, two serial ports (SPORTs), nine general-purpose 32-bit timers (eight with PWM capability), a real-time clock, a watchdog timer, and a parallel peripheral interface (PPI).BLACKFIN PROCESSOR PERIPHERALSThe ADSP-BF534/ADSP-BF536/ADSP-BF537 processors con-tain a rich set of peripherals connected to the core via severalhigh bandwidth buses, providing flexibility in system configura-tion as well as excellent overall system performance (seeFigure 1). The processors contain dedicated network communi-cation modules and high speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources, and power manage-ment control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.All of the peripherals, except for the general-purpose I/O, CAN, TWI, real-time clock, and timers, are supported by a flexible DMA structure. There are also separate memory DMA channels dedicated to data transfers between the processor’s various memory spaces, including external SDRAM and asynchronous memory. Multiple on-chip buses running at up to 133MHz provide enough bandwidth to keep the processor core running along with activity on all of the on-chip and external peripherals.Table 1.Processor ComparisonFeatures A D S P -B F 534A D S P -B F 536A D S P -B F 537Ethernet MAC —11CAN 111TWI 111SPORTs 222UARTs 222SP 111GP Timers 888Watchdog Timers 111RTC 111Parallel Peripheral Interface 111GP I Os 48 48 48Memory Configuration L1 Instruction SRAM/Cache16K bytes 16K bytes 16K bytes L1 Instruction SRAM48K bytes 48K bytes 48K bytes L1 Data SRAM/Cache32K bytes 32K bytes 32K bytes L1 Data SRAM 32K bytes —32K bytes L1 Scratchpad 4K bytes 4K bytes 4K bytes L3 Boot ROM 2K bytes 2K bytes 2K bytesMaximum Speed Grade 500 MHz 400 MHz 600 MHz Package Options:Sparse CSP_BGA CSP_BGA 208-Ball 182-Ball 208-Ball 182-Ball 208-Ball 182-BallADSP-BF534/ADSP-BF536/ADSP-BF537The Blackfin processors include an on-chip voltage regulator in support of the processors’ dynamic power management capabil-ity. The voltage regulator provides a range of core voltage levels when supplied from a single 2.25V to 3.6V input. The voltage regulator can be bypassed at the user’s discretion. BLACKFIN PROCESSOR COREAs shown in Figure2, the Blackfin processor core contains two 16-bit multipliers, two 40-bit accumulators, two 40-bit ALUs, four video ALUs, and a 40-bit shifter. The computation units process 8-, 16-, or 32-bit data from the register file.The compute register file contains eight 32-bit registers. When performing compute operations on 16-bit operand data, the register file operates as 16 independent 16-bit registers. All operands for compute operations come from the multiported register file and instruction constant fields.Each MAC can perform a 16-bit by 16-bit multiply in each cycle, accumulating the results into the 40-bit accumulators. Signed and unsigned formats, rounding, and saturationare supported.The ALUs perform a traditional set of arithmetic and logical operations on 16-bit or 32-bit data. In addition, many special instructions are included to accelerate various signal processing tasks. These include bit operations such as field extract and pop-ulation count, modulo 232 multiply, divide primitives, saturation and rounding, and sign/exponent detection. The set of video instructions include byte alignment and packing operations, 16-bit and 8-bit adds with clipping, 8-bit average operations, and 8-bit subtract/absolute value/accumulate (SAA) operations. Also provided are the compare/select and vector search instructions.For certain instructions, two 16-bit ALU operations can be per-formed simultaneously on register pairs (a 16-bit high half and 16-bit low half of a compute register). If the second ALU is used, quad 16-bit operations are possible.The 40-bit shifter can perform shifts and rotates, and is used to support normalization, field extract, and field deposit instructions.The program sequencer controls the flow of instruction execu-tion, including instruction alignment and decoding. For program flow control, the sequencer supports PC relative and indirect conditional jumps (with static branch prediction), and subroutine calls. Hardware is provided to support zero-over-head looping. The architecture is fully interlocked, meaning that the programmer need not manage the pipeline when executing instructions with data dependencies.Figure 2.Blackfin Processor CoreRev. E|Page 4 of 68|March 2008ADSP-BF534/ADSP-BF536/ADSP-BF537Rev. E |Page 5 of 68|March 2008The address arithmetic unit provides two addresses for simulta-neous dual fetches from memory. It contains a multiported register file consisting of four sets of 32-bit index, modify, length, and base registers (for circular buffering), and eight additional 32-bit pointer registers (for C-style indexed stack manipulation).Blackfin processors support a modified Harvard architecture in combination with a hierarchical memory structure. Level 1 (L1) memories are those that typically operate at the full processor speed with little or no latency. At the L1 level, the instruction memory holds instructions only. The two data memories hold data, and a dedicated scratchpad data memory stores stack and local variable information.In addition, multiple L1 memory blocks are provided, offering a configurable mix of SRAM and cache. The memory manage-ment unit (MMU) provides memory protection for individual tasks that may be operating on the core and can protect system registers from unintended access.The architecture provides three modes of operation: user mode, supervisor mode, and emulation mode. User mode hasrestricted access to certain system resources, thus providing a protected software environment, while supervisor mode has unrestricted access to the system and core resources.The Blackfin processor instruction set has been optimized so that 16-bit opcodes represent the most frequently used instruc-tions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. Blackfin processors support a limited multi-issue capability, where a 32-bit instruc-tion can be issued in parallel with two 16-bit instructions,allowing the programmer to use many of the core resources in a single instruction cycle.The Blackfin processor assembly language uses an algebraic syn-tax for ease of coding and readability. The architecture has been optimized for use in conjunction with the C/C++compiler, resulting in fast and efficient software implementations.MEMORY ARCHITECTUREThe ADSP-BF534/ADSP-BF536/ADSP-BF537 processors view memory as a single unified 4G byte address space, using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of thisaddress space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low latency on-chip memory as cache or SRAM, and larger, lower cost, and performance off-chip memory systems. (See Figure 3).The on-chip L1 memory system is the highest performance memory available to the Blackfin processor. The off-chip mem-ory system, accessed through the external bus interface unit (EBIU), provides expansion with SDRAM, flash memory, and SRAM, optionally accessing up to 516M bytes of physical memory.The memory DMA controller provides high bandwidth data-movement capability. It can perform block transfers of code or data between the internal memory and the external memory spaces.Internal (On-Chip) MemoryThe ADSP-BF534/ADSP-BF536/ADSP-BF537 processors have three blocks of on-chip memory providing high-bandwidth access to the core.The first block is the L1 instruction memory, consisting of 64K bytes SRAM, of which 16K bytes can be configured as a four-way set-associative cache. This memory is accessed at full processor speed.The second on-chip memory block is the L1 data memory, con-sisting of up to two banks of up to 32K bytes each. Each memory bank is configurable, offering both cache and SRAM functional-ity. This memory block is accessed at full processor speed.The third memory block is a 4K byte scratchpad SRAM, which runs at the same speed as the L1 memories, but is only accessible as data SRAM, and cannot be configured as cache memory.External (Off-Chip) MemoryExternal memory is accessed via the EBIU. This 16-bit interface provides a glueless connection to a bank of synchronous DRAM (SDRAM) as well as up to four banks of asynchronous memory devices including flash, EPROM, ROM, SRAM, and memory mapped I/O devices.The PC133-compliant SDRAM controller can be programmed to interface to up to 512M bytes of SDRAM. A separate row can be open for each SDRAM internal bank, and the SDRAM con-troller supports up to 4 internal SDRAM banks, improving overall performance.The asynchronous memory controller can be programmed to control up to four banks of devices with very flexible timing parameters for a wide variety of devices. Each bank occupies a 1M byte segment regardless of the size of the devices used, so that these banks are only contiguous if each is fully populated with 1M byte of memory.I/O Memory SpaceThe ADSP-BF534/ADSP-BF536/ADSP-BF537 processors do not define a separate I/O space. All resources are mappedthrough the flat 32-bit address space. On-chip I/O devices have their control registers mapped into memory-mapped registers (MMRs) at addresses near the top of the 4G byte address space. These are separated into two smaller blocks, one which contains the control MMRs for all core functions, and the other which contains the registers needed for setup and control of the on-chip peripherals outside of the core. The MMRs are accessible only in supervisor mode and appear as reserved space to on-chip peripherals.ADSP-BF534/ADSP-BF536/ADSP-BF537BootingThe Blackfin processor contains a small on-chip boot kernel, which configures the appropriate peripheral for booting. If the Blackfin processor is configured to boot from boot ROM mem-ory space, the processor starts executing from the on-chip boot ROM. For more information, see Booting Modes on Page16. Event HandlingThe event controller on the Blackfin processor handles all asyn-chronous and synchronous events to the processor. The Blackfin processor provides event handling that supports both nesting and prioritization. Nesting allows multiple event service routines to be active simultaneously. Prioritization ensures that servicing of a higher priority event takes precedence over servic-ing of a lower priority event. The controller provides support for five different types of events:•Emulation – An emulation event causes the processor toenter emulation mode, allowing command and control of the processor via the JTAG interface.•Reset – This event resets the processor.•Nonmaskable Interrupt (NMI) – The NMI event can begenerated by the software watchdog timer or by the NMIinput signal to the processor. The NMI event is frequently used as a power-down indicator to initiate an orderly shut-down of the system.•Exceptions – Events that occur synchronously to program flow (in other words, the exception is taken before theinstruction is allowed to complete). Conditions such asdata alignment violations and undefined instructions cause exceptions.•Interrupts – Events that occur asynchronously to program flow. They are caused by input pins, timers, and otherperipherals, as well as by an explicit software instruction. Each event type has an associated register to hold the return address and an associated return-from-event instruction. When an event is triggered, the state of the processor is saved on the supervisor stack.The Blackfin processor event controller consists of two stages: the core event controller (CEC) and the system interrupt con-troller (SIC). The core event controller works with the system interrupt controller to prioritize and control all system events.Figure 3.ADSP-BF534/ADSP-BF536/ADSP-BF537 Memory MapsRev. E|Page 6 of 68|March 2008ADSP-BF534/ADSP-BF536/ADSP-BF537Rev. E |Page 7 of 68|March 2008Conceptually, interrupts from the peripherals enter into the SIC, and are then routed directly into the general-purpose inter-rupts of the CEC.Core Event Controller (CEC)The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers, leaving seven prioritized interrupt inputs to support the peripherals of the Blackfin processor. Table 2 describes the inputs to the CEC, identifies their names in the event vector table (EVT), and lists their priorities.System Interrupt Controller (SIC)The system interrupt controller provides the mapping and rout-ing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the processor provides a default mapping, the user can alter the mappings and priorities of interrupt events by writ-ing the appropriate values into the interrupt assignmentregisters (IAR). Table 3 describes the inputs into the SIC and the default mappings into the CEC.Table 2.Core Event Controller (CEC)Priority(0 Is Highest)Event ClassEVT Entry 0Emulation/Test Control EMU 1ResetRST 2Nonmaskable Interrupt NMI 3ExceptionEVX 4Reserved—5Hardware Error IVHW 6Core TimerIVTMR 7General-Purpose Interrupt 7IVG78General-Purpose Interrupt 8IVG89General-Purpose Interrupt 9IVG910General-Purpose Interrupt 10IVG1011General-Purpose Interrupt 11IVG1112General-Purpose Interrupt 12IVG1213General-Purpose Interrupt 13IVG1314General-Purpose Interrupt 14IVG1415General-Purpose Interrupt 15IVG15Table 3.System Interrupt Controller (SIC)Peripheral Interrupt Event Default Mapping Peripheral Interrupt ID PLL WakeupIVG70DMA Error (Generic)IVG71DMAR0 Block Interrupt IVG71DMAR1 Block Interrupt IVG71DMAR0 Overflow Error IVG71DMAR1 Overflow Error IVG71CAN ErrorIVG72Ethernet Error (ADSP-BF536 and ADSP-BF537 only)IVG72SPORT 0 Error IVG72SPORT 1 Error IVG72PPI Error IVG72SPI Error IVG72UART0 Error IVG72UART1 Error IVG72Real-Time Clock IVG83DMA Channel 0 (PPI)IVG84DMA Channel 3 (SPORT 0 Rx)IVG95DMA Channel 4 (SPORT 0 Tx)IVG96DMA Channel 5 (SPORT 1 Rx)IVG97DMA Channel 6 (SPORT 1 Tx)IVG98TWIIVG109DMA Channel 7 (SPI)IVG1010DMA Channel 8 (UART0 Rx)IVG1011DMA Channel 9 (UART0 Tx)IVG1012DMA Channel 10 (UART1 Rx)IVG1013DMA Channel 11 (UART1 Tx)IVG1014CAN Rx IVG1115CAN TxIVG1116DMA Channel 1 (Ethernet Rx,ADSP-BF536 and ADSP-BF537 only)IVG1117Port H Interrupt AIVG1117DMA Channel 2 (Ethernet Tx,ADSP-BF536 and ADSP-BF537 only)IVG1118Port H Interrupt B IVG1118Timer 0IVG1219Timer 1IVG1220Timer 2IVG1221Timer 3IVG1222Timer 4IVG1223Timer 5IVG1224Timer 6IVG1225Timer 7IVG1226Port F, G Interrupt A IVG1227Port G Interrupt BIVG1228Rev. E |Page 8 of 68|March 2008ADSP-BF534/ADSP-BF536/ADSP-BF537Event ControlThe Blackfin processor provides a very flexible mechanism to control the processing of events. In the CEC, three registers are used to coordinate and control events. Each register is 16 bits wide:•CEC interrupt latch register (ILAT) – Indicates when events have been latched. The appropriate bit is set when the processor has latched the event and cleared when the event has been accepted into the system. This register is updated automatically by the controller, but it may be writ-ten only when its corresponding IMASK bit is cleared.•CEC interrupt mask register (IMASK) – Controls themasking and unmasking of individual events. When a bit is set in the IMASK register, that event is unmasked and is processed by the CEC when asserted. A cleared bit in the IMASK register masks the event, preventing the processor from servicing the event even though the event may be latched in the ILAT register. This register may be read or written while in supervisor mode. (Note that general-pur-pose interrupts can be globally enabled and disabled with the STI and CLI instructions, respectively.)•CEC interrupt pending register (IPEND) – The IPEND register keeps track of all nested events. A set bit in the IPEND register indicates the event is currently active or nested at some level. This register is updated automatically by the controller but may be read while in supervisor mode. The SIC allows further control of event processing by providing three 32-bit interrupt control and status registers. Each register contains a bit corresponding to each of the peripheral interrupt events shown in Table 3 on Page 7.•SIC interrupt mask register (SIC_IMASK) – Controls the masking and unmasking of each peripheral interrupt event. When a bit is set in the register, that peripheral event is unmasked and is processed by the system when asserted. A cleared bit in the register masks the peripheral event, pre-venting the processor from servicing the event.•SIC interrupt status register (SIC_ISR) – As multiple peripherals can be mapped to a single event, this register allows the software to determine which peripheral event source triggered the interrupt. A set bit indicates theperipheral is asserting the interrupt, and a cleared bit indi-cates the peripheral is not asserting the event.•SIC interrupt wake-up enable register (SIC_IWR) – By enabling the corresponding bit in this register, a peripheral can be configured to wake up the processor, should the core be idled when the event is generated. (For more infor-mation, see Dynamic Power Management on Page 13.)Because multiple interrupt sources can map to a single general-purpose interrupt, multiple pulse assertions can occur simulta-neously, before or during interrupt processing for an interrupt event already detected on this interrupt input. The IPEND reg-ister contents are monitored by the SIC as the interrupt acknowledgement.The appropriate ILAT register bit is set when an interrupt rising edge is detected (detection requires two core clock cycles). The bit is cleared when the respective IPEND register bit is set. The IPEND bit indicates that the event has entered into the proces-sor pipeline. At this point the CEC recognizes and queues the next rising edge event on the corresponding event input. The minimum latency from the rising edge transition of the general-purpose interrupt to the IPEND output asserted is three core clock cycles; however, the latency can be much higher, depend-ing on the activity within and the state of the processor.DMA CONTROLLERSThe Blackfin processors have multiple, independent DMA channels that support automated data transfers with minimal overhead for the processor core. DMA transfers can occurbetween the processor’s internal memories and any of its DMA-capable peripherals. Additionally, DMA transfers can be accom-plished between any of the DMA-capable peripherals and external devices connected to the external memory interfaces, including the SDRAM controller and the asynchronous mem-ory controller. DMA-capable peripherals include the Ethernet MAC (ADSP-BF536 and ADSP-BF537 only), SPORTs, SPI port, UARTs, and PPI. Each individual DMA-capable peripheral has at least one dedicated DMA channel.The DMA controller supports both one-dimensional (1-D) and two-dimensional (2-D) DMA transfers. DMA transfer initial-ization can be implemented from registers or from sets of parameters called descriptor blocks.The 2-D DMA capability supports arbitrary row and column sizes up to 64K elements by 64K elements, and arbitrary row and column step sizes up to ±32K elements. Furthermore, the column step size can be less than the row step size, allowing implementation of interleaved data streams. This feature is especially useful in video applications where data can be de-interleaved on the fly.Examples of DMA types supported by the DMA controller include• A single, linear buffer that stops upon completion • A circular, auto-refreshing buffer that interrupts on each full or fractionally full buffer•1-D or 2-D DMA using a linked list of descriptors •2-D DMA using an array of descriptors, specifying only the base DMA address within a common page.DMA Channels 12 and 13 (Memory DMA Stream 0)IVG1329DMA Channels 14 and 15(Memory DMA Stream 1)IVG1330Software Watchdog Timer IVG1331Port F Interrupt BIVG1331Table 3.System Interrupt Controller (SIC) (Continued)Peripheral Interrupt Event Default Mapping Peripheral Interrupt ID。