TMS320x2833x Multichannel Buffered Serial Port (McBSP) Reference Guide第四章 译文

TMS320x2833x Multichannel Buffered Serial Port (McBSP) Reference Guide第二章翻译

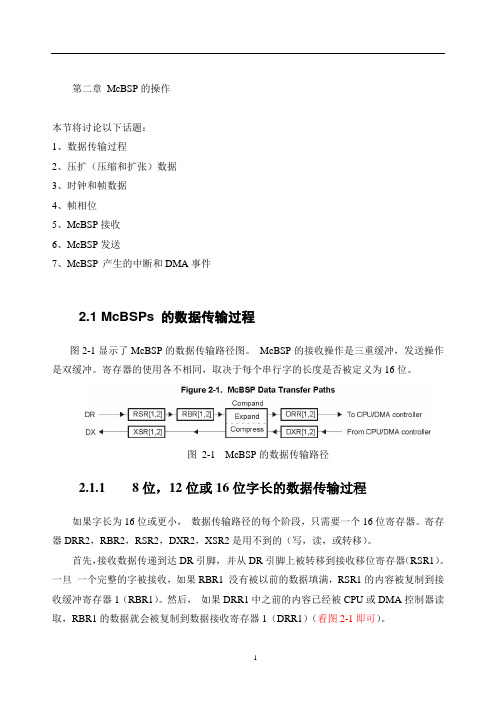

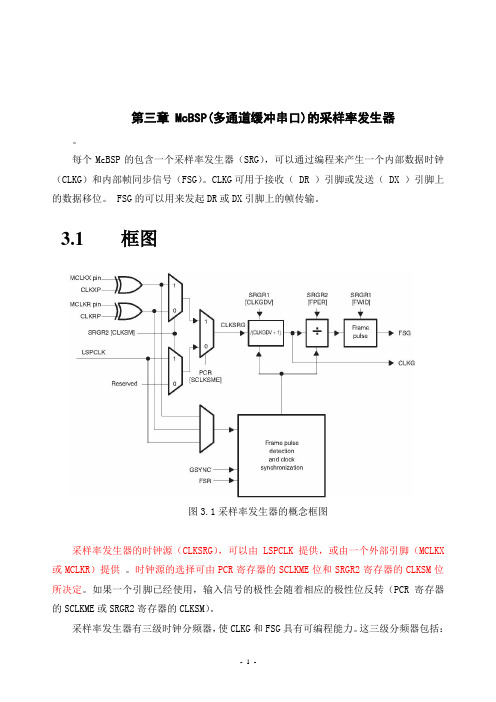

第二章McBSP的操作本节将讨论以下话题:1、数据传输过程2、压扩(压缩和扩张)数据3、时钟和帧数据4、帧相位5、McBSP接收6、McBSP发送7、McBSP 产生的中断和DMA事件2.1 McBSPs 的数据传输过程图2-1显示了McBSP的数据传输路径图。

McBSP的接收操作是三重缓冲,发送操作是双缓冲。

寄存器的使用各不相同,取决于每个串行字的长度是否被定义为16位。

图2-1 McBSP的数据传输路径2.1.1 8位,12位或16位字长的数据传输过程如果字长为16位或更小,数据传输路径的每个阶段,只需要一个16位寄存器。

寄存器DRR2,RBR2,RSR2,DXR2,XSR2是用不到的(写,读,或转移)。

首先,接收数据传递到达DR引脚,并从DR引脚上被转移到接收移位寄存器(RSR1)。

一旦一个完整的字被接收,如果RBR1 没有被以前的数据填满,RSR1的内容被复制到接收缓冲寄存器1(RBR1)。

然后,如果DRR1中之前的内容已经被CPU或DMA控制器读取,RBR1的数据就会被复制到数据接收寄存器1(DRR1)(看图2-1即可)。

如果McBSP压扩功能被执行,则所需的字长为8位,而且,在接收数据被从RBR1到DRR1传递之前,接收数据被扩展到适当的格式。

有关接收过程的更多细节,请参见2.5节。

传输数据是由CPU或DMA控制器写入到数据传输寄存器(DXR1)。

如果在发送移位寄存器(XSR1)中没有数据,在DXR1的数据被复制到XSR1,否则,则当XSR1中之前的数据的最后一位被转移到DX引脚时,DXR1的数据被复制到XSR1中。

如果数据被选中,在传递到XSR1之前,压扩模块会压缩16位的数据成为合适的8位格式的数据。

帧同步传输后,发送器开始从XSR1位到DX引脚进行移位。

有关传输的更多细节,请参见第2.6节。

2.1.2 字长为20,24,32位的数据传输进程如果字长大于16位的,在数据传输路径的每个阶段,则需要两个16位寄存器,寄存器DRR2,RBR2,RSR2,DXR2,XSR2保存最高位的bits。

TMS320F28335核心板:Core28335软件调试指南

如果出现下图所示,则表示仿真器和开发板已连接成功。

第三步: 新建一个工程,如下图

第四步: 选择路径,输入工程项目名,并确定,则如下图所示

第五步: 添加源文件,添加 CMD 文件,如下图所示: 注意:源文件有*.c 文件,也有*.asm 文件

添加 CMD 文件跟添加源文件的方法相似,在这里不在赘述。添加完成后整个工程如下所示:

版权© 2013,株洲市索思达电子有限公司

前言

阅前必读

简介:

本 用 户指 南是 TMS320F28335 DSP 处 理 模板 硬 件使 用说 明书 ,详 细描 述 了

28335实用版 的硬件构成、原理,以及它的使用方法和编程指导。

保修:

所有由株洲市索思达电子有限公司生产制造的硬件和软件产品, 保修期为从发货 之日起一 年。 在保修期内由于产品质量原因引起的损坏, 株洲市索思达电子有限公司负责免费维修。当在 保修期内软件进行了升级, 株洲市索思达电子有限公司将免费提供。

参考资料:

TMS320F28x DSP CPU and Instruction Set Reference Guide (文献号 SPRU430) : 介 绍 TMS320F28x 系列 DSP 的 CPU 结构、指令组、流水线及中断。 TMS320C28x Floating Point Unit and Instruction Set Reference Guide (文献号 SPRUEO2)介绍浮点单元和FPU指令集。 TMS320x28xx, 28xxx Peripheral Reference Guide(文献号 绍 TMS320F28x 系列 DSP 的外设。 TMS320x2833x 献 号 System Control and Interrupts Reference Guide ( 文 SPRU566):介

TMS320F28335教程

2个增强型的eCAN2.0B接口模块

DSP技术应用

2个多通道缓冲串口(MBSP) 1个12C总线接口 12位模数转换模块

80ns转换时间

2X8通道复用输入接口

两个采样保持电路

单/连续通道转换

高达88个可配置通用目的I/O引脚

先进的仿真调试功能

DSP技术应用

硬件支持适时仿真功能

DSP技术应用

(5) 军事——如保密通信、雷达处理、声纳处理、

导航、导弹制导等; (6) 仪器仪表——如频谱分析、函数发生、锁相环 、地震处理等; (7) 自动控制——如引擎控制、声控、自动驾驶、 机器人控制、磁盘控制等; (8) 医疗——如助听、超声设备、诊断工具、病人 监护等;

(9) 家用电器——如高保真音响、音乐合成、音调 控制、玩具与游戏、数字电话/视等。

C28x

TM

GPIO 16/32-bit

EMIF SPI

88

32x32-bit

Multiplier

通讯接口 32-bit Timers (3) Each McBSP configurable as SPI Real CAN 2.0b with 32 mailboxes Time 2C at 400 Kbps JTAG I 开发套件 SEED-DEC28335+SEED-XDSusb2.0 Code Composer Studio™ IDE V3.3 DSP技术应用 Software libraries

Sectored

A(18-0) 22 32 32 32

32-bit Auxiliary

Flash

RAM

ROM

D(15-0)

32x32 bit Multiplier

TMS320x2833x Multichannel Buffered Serial Port (McBSP) Reference Guide 第七章 翻译译文

第7章接收器配置配置McBSP接收器,请执行以下步骤:1 将McBSP/接收器复位(见7.2节)。

2 对McBSP寄存器进行操作,使其处在接受所需的状态(参见7.1节)。

3 使接收器摆脱复位状态(见7.2节)。

(翻译不明)7.1对McBSP寄存器进行编程,使其处在接受所需的状态下面是当你配置的McBSP接收器时一个重要的任务列表。

每个任务对应一个或多个的McBSP寄存器位字段。

•全局操作:将接收引脚设置为McBSP的引脚。

1.启用/禁用数字回环模式。

2.启用/停用时钟停止模式。

3.启用/禁用接收多频道选择模式。

•数据操作1.选择1或2阶段为接收帧。

2.设置接收字长度(S)。

3.设置接收帧的长度。

4.启用/禁用接收帧同步忽略功能。

5.设置接收压扩模式。

6.设置接收数据的延迟。

7.设置接收符号扩展和理由模式。

8.设置接收中断模式。

•帧同步操作1.设置接收帧同步模式。

2.设置接收帧同步极性。

3.设置采样率发生器(SRG的)帧同步周期和脉冲宽度。

• 时钟操作1.设置接收时钟模式。

2.设置接收时钟极性。

3.设置SRG时钟分频的参数。

4.设置SRG的时钟同步模式。

5.设置SRG的时钟模式(选择输入时钟)。

7.2复位和启用接收器接收器的配置过程的第一步是要使接收器复位,最后一步是使接收器处于使能状态(使它摆脱复位状态)。

表7-1描述了这两个步骤中所使用的位。

7.2.1复位的注意事项串行端口可以通过下面的两步进行初始化:1. DSP复位(XRS信号驱动为低电平)会使接收器,发射器,采样率发生器复位。

当设备复位信号被取消(XRS信号发布),GRST = FRST = RRST = XRST = 0整个串行端口保持在复位状态。

(翻译的我都不明白)2. 直接使用串口控制寄存器RRST和XRST位使串口发射器和接收器复位。

直接使用在SPCR2的GRST位使采样率发生器复位。

由于器件复位或接收器/发射器直接复位而使串口复位时,McBSP引脚的状态如表7-2。

TMS28335资料

TMS320x2833x,2823x Enhanced Capture (eCAP)ModuleReference GuideLiterature Number:SPRUFG4AAugust2008–Revised June20092SPRUFG4A–August2008–Revised June2009Submit Documentation FeedbackPreface (6)1Introduction (9)2Description (9)3Capture and APWM Operating Mode (11)4Capture Mode Description (12)4.1Event Prescaler (12)4.2Edge Polarity Select and Qualifier (13)4.3Continuous/One-Shot Control (13)4.432-Bit Counter and Phase Control (14)4.5CAP1-CAP4Registers (15)4.6Interrupt Control (15)4.7Shadow Load and Lockout Control (16)4.8APWM Mode Operation (17)5Capture Module-Control and Status Registers (18)6Register Mapping (26)7Application of the ECAP Module (26)7.1Example1-Absolute Time-Stamp Operation Rising Edge Trigger (27)7.2Example2-Absolute Time-Stamp Operation Rising and Falling Edge Trigger (30)7.3Example3-Time Difference(Delta)Operation Rising Edge Trigger (32)7.4Example4-Time Difference(Delta)Operation Rising and Falling Edge Trigger (34)8Application of the APWM Mode (36)8.1Example1-Simple PWM Generation(Independent Channel/s) (36)8.2Example2-Multi-channel PWM Generation With Phase Control (37)Appendix A Revision History (40)SPRUFG4A–August2008–Revised June2009Table of Contents3 Submit Documentation FeedbackList of Figures1Multiple eCAP Modules In A2823x/2833x System (10)2Capture and APWM Modes of Operation (11)3Capture Function Diagram (12)4Event Prescale Control (13)5Prescale Function Waveforms (13)6Details of the Continuous/One-shot Block (14)7Details of the Counter and Synchronization Block (15)8Interrupts in eCAP Module (16)9PWM Waveform Details Of APWM Mode Operation (17)10Time-Stamp Counter Register(TSCTR) (18)11Counter Phase Control Register(CTRPHS) (18)12Capture-1Register(CAP1) (18)13Capture-2Register(CAP2) (18)14Capture-3Register(CAP3) (19)15Capture-4Register(CAP4) (19)16ECAP Control Register1(ECCTL1) (19)17ECAP Control Register2(ECCTL2) (21)18ECAP Interrupt Enable Register(ECEINT) (23)19ECAP Interrupt Flag Register(ECFLG) (24)20ECAP Interrupt Clear Register(ECCLR) (24)21ECAP Interrupt Forcing Register(ECFRC) (25)22Capture Sequence for Absolute Time-stamp and Rising Edge Detect (28)23Capture Sequence for Absolute Time-stamp With Rising and Falling Edge Detect (30)24Capture Sequence for Delta Mode Time-stamp and Rising Edge Detect (32)25Capture Sequence for Delta Mode Time-stamp With Rising and Falling Edge Detect (34)26PWM Waveform Details of APWM Mode Operation (36)27Multi-phase(channel)Interleaved PWM Example Using3eCAP Modules (38)4SPRUFG4A–August2008–Revised June2009 List of FiguresSubmit Documentation FeedbackList of Tables1Time-Stamp Counter Register(TSCTR)Field Descriptions (18)2Counter Phase Control Register(CTRPHS)Field Descriptions (18)3Capture-1Register(CAP1)Field Descriptions (18)4Capture-2Register(CAP2)Field Descriptions (19)5Capture-3Register(CAP3)Field Descriptions (19)6Capture-4Register(CAP4)Field Descriptions (19)7ECAP Control Register1(ECCTL1)Field Descriptions (20)8ECAP Control Register2(ECCTL2)Field Descriptions (21)9ECAP Interrupt Enable Register(ECEINT)Field Descriptions (23)10ECAP Interrupt Flag Register(ECFLG)Field Descriptions (24)11ECAP Interrupt Clear Register(ECCLR)Field Descriptions (25)12ECAP Interrupt Forcing Register(ECFRC)Field Descriptions (25)13Control and Status Register Set (26)A-1Changes Made in This Revision (40)SPRUFG4A–August2008–Revised June2009List of Tables5 Submit Documentation FeedbackPrefaceSPRUFG4A–August2008–Revised June2009The enhanced capture(eCAP)module is used in systems where accurate timing of external events is important.This guide describes the TMS320x2833x,2823x Enhanced Capture(eCAP)Module module and how to use it.The eCAP module described in guide is a Type0eCAP.See the TMS320C28xx,28xxx DSP Peripheral Reference Guide for a list of all devices with a eCAP module of the sametype,to determine the differences types,and for a list of device-specific differences within a type.Related Documentation From Texas InstrumentsThe following documents describe the TMS320C2833x/2823x and related support tools and can bedownloaded from the TI website():Data Manual and Errata—ofCPU User's Guides—TMS320C28x CPU and Instruction Set Reference Guide describes the central processing(CPU)and the assembly language instructions of the TMS320C28x fixed-point digital signal processors(DSPs).It also describes emulation features available on these DSPs.TMS320C28x Floating Point Unit and Instruction Set Reference Guide describes theunit and includes the instructions for the FPU.Peripheral Guides—TMS320x28xx,28xxx DSP Peripheral Reference Guide describes the peripheral referenceof the28x digital signal processors(DSPs).TMS320x2833x,2823x System Control and Interrupts Reference Guide describes theinterrupts and system control features of the2833x and2823x digital signal controllers (DSCs).TMS320x2833x,2823x Analog-to-Digital Converter(ADC)Reference Guide describesto configure and use the on-chip ADC module,which is a12-bit pipelined ADC.TMS320x2833x,2823x DSC External Interface(XINTF)Reference Guide describes thewhich is a nonmultiplexed asynchronous bus,as it is used on the2833x and2823x devices.TMS320x2833x,2823x Boot ROM Reference Guide describes the purpose and features ofbootloader(factory-programmed boot-loading software)and provides examples of code.It also describes other contents of the device on-chip boot ROM and identifies where all of the informationis located within that memory.6Preface SPRUFG4A–August2008–Revised June2009Submit Documentation Feedback Related Documentation From Texas Instruments TMS320x2833x,2823x Multichannel Buffered Serial Port(McBSP)Reference Guidethe McBSP available on the2833x and2823x devices.The McBSPs allow direct interface between a DSP and other devices in a system.TMS320x2833x,2823x Direct Memory Access(DMA)Module Reference Guidethe DMA on the2833x and2823x devices.TMS320x2833x,2823x Enhanced Pulse Width Modulator(ePWM)Module Referencedescribes the main areas of the enhanced pulse width modulator that include digital motor control,switch mode power supply control,UPS(uninterruptible power supplies),and other forms ofpower conversion.TMS320x2833x,2823x High-Resolution Pulse Width Modulator(HRPWM)Referencedescribes the operation of the high-resolution extension to the pulse width modulator (HRPWM).TMS320x2833x,2823x Enhanced Capture(eCAP)Module Reference Guide describescapture module.It includes the module description and registers.TMS320x2833x,2823x Enhanced Quadrature Encoder Pulse(eQEP)Module Referencedescribes the eQEP module,which is used for interfacing with a linear or rotary incremental encoder to get position,direction,and speed information from a rotating machine inhigh-performance motion and position control systems.It includes the module description andregisters.TMS320x2833x,2823x Enhanced Controller Area Network(eCAN)Reference Guidethe eCAN that uses established protocol to communicate serially with other controllers in electrically noisy environments.TMS320x2833x,2823x Serial Communications Interface(SCI)Reference Guidethe SCI,which is a two-wire asynchronous serial port,commonly known as a UART.The SCI modules support digital communications between the CPU and other asynchronous peripheralsthat use the standard non-return-to-zero(NRZ)format.TMS320x2833x,2823x DSC Serial Peripheral Interface(SPI)Reference Guide describes-a high-speed synchronous serial input/output(I/O)port-that allows a serial bit stream of programmed length(one to sixteen bits)to be shifted into and out of the device at a programmedbit-transfer rate.TMS320x2833x,2823x Inter-Integrated Circuit(I2C)Module Reference Guide describesand operation of the inter-integrated circuit(I2C)module.Tools Guides—TMS320C28x Assembly Language Tools v5.0.0User's Guide describes the assemblytools(assembler and other tools used to develop assembly language code),assembler directives,macros,common object file format,and symbolic debugging directives for theTMS320C28x device.TMS320C28x Optimizing C/C++Compiler v5.0.0User's Guide describes theC/C++compiler.This compiler accepts ANSI standard C/C++source code and produces TMS320DSP assembly language source code for the TMS320C28x device.TMS320C28x Instruction Set Simulator Technical Overview describes the simulator,within the Code Composer Studio for TMS320C2000IDE,that simulates the instruction set of the C28x™core.TMS320C28x DSP/BIOS5.32Application Programming Interface(API)Reference Guidedevelopment using DSP/BIOS.SPRUFG4A–August2008–Revised June2009Read This First7 Submit Documentation FeedbackRelated Documentation From Texas Instruments TrademarksTMS320C28x,C28x are trademarks of Texas Instruments.Read This First8SPRUFG4A–August2008–Revised June2009Submit Documentation Feedback1Introduction2DescriptionReference GuideSPRUFG4A–August 2008–Revised June 2009The enhanced Capture (eCAP)module is essential in systems where accurate timing of external events is important.This reference guide is applicable for the eCAP found on the TMS320x2823x and the TMS320x2833x family of processors.This includes all Flash-based,ROM-based,and RAM-based devices within the 2823x and 2833x families .Uses for eCAP include:•Speed measurements of rotating machinery (e.g.,toothed sprockets sensed via Hall sensors)•Elapsed time measurements between position sensor pulses •Period and duty cycle measurements of pulse train signals•Decoding current or voltage amplitude derived from duty cycle encoded current/voltage sensors The eCAP module described in this guide includes the following features:•32-bit time base with 6.67-ns time resolution with a 150-MHz system clock •4-event time-stamp registers (each 32bits)•Edge polarity selection for up to four sequenced time-stamp capture events •Interrupt on either of the four events•Single shot capture of up to four event time-stamps•Continuous mode capture of time-stamps in a four-deep circular buffer •Absolute time-stamp capture•Difference (Delta)mode time-stamp capture•All above resources dedicated to a single input pin•When not used in capture mode,the ECAP module can be configured as a single channel PWM outputThe eCAP module represents one complete capture channel that can be instantiated multiple times depending on the target device.In the context of this guide,one eCAP channel has the following independent key resources:•Dedicated input capture pin •32-bit time base (counter)•4x 32-bit time-stamp capture registers (CAP1-CAP4)•4-stage sequencer (Modulo4counter)that is synchronized to external events,ECAP pin rising/falling edges.•Independent edge polarity (rising/falling edge)selection for all 4events •Input capture signal prescaling (from 2-62)•One-shot compare register (2bits)to freeze captures after 1to 4time-stamp events•Control for continuous time-stamp captures using a 4-deep circular buffer (CAP1-CAP4)scheme •Interrupt capabilities on any of the 4capture eventsMultiple identical eCAP modules can be contained in a system as shown in Figure 1.The number of modules is device-dependent and is based on target application needs.SPRUFG4A–August 2008–Revised June 2009Enhanced Capture (eCAP)Module 9Submit Documentation FeedbackPeripheral Frame 1PeripheralDescription Figure1.Multiple eCAP Modules In A2823x/2833x System10Enhanced Capture(eCAP)Module SPRUFG4A–August2008–Revised June2009Submit Documentation Feedback Capture and APWM Operating Mode 3Capture and APWM Operating ModeYou can use the eCAP module resources to implement a single-channel PWM generator(with32bitcapabilities)when it is not being used for input captures.The counter operates in count-up mode,providing a time-base for asymmetrical pulse width modulation(PWM)waveforms.The CAP1and CAP2 registers become the active period and compare registers,respectively,while CAP3and CAP4registers become the period and capture shadow registers,respectively.Figure2is a high-level view of both the capture and auxiliary pulse-width modulator(APWM)modes ofFigure2.Capture and APWM Modes of OperationA A single pin is shared between CAP and APWM functions.In capture mode,it is an input;in APWM mode,it is anoutput.B In APWM mode,writing any value to CAP1/CAP2active registers also writes the same value to the correspondingshadow registers CAP3/CAP4.This emulates immediate mode.Writing to the shadow registers CAP3/CAP4invokesthe shadow mode.4Capture Mode Description4.1Event PrescalerCapture Mode Description Figure 3shows the various components that implement the capture function.Figure 3.Capture Function Diagram•An input capture signal (pulse train)can be prescaled by N =2-62(in multiples of 2)or can bypass the prescaler.This is useful when very high frequency signals are used as inputs.Figure 4shows a functional diagram and Figure 5shows the operation of the prescale function.12Enhanced Capture (eCAP)ModuleSPRUFG4A–August 2008–Revised June 2009ECAPx pin (from GPIO)PSoutECAPxPSout div 2PSout div 4PSout div 6PSout div 8PSout div 104.2Edge Polarity Select and Qualifier4.3Continuous/One-Shot Control Capture Mode DescriptionFigure 4.Event Prescale ControlAWhen a prescale value of 1is chosen (i.e.ECCTL1[13:9]=0,0,0,0,0)the input capture signal by-passes the prescale logic completely.Figure 5.Prescale Function Waveforms•Four independent edge polarity (rising edge/falling edge)selection MUXes are used,one for each capture event.•Each edge (up to 4)is event qualified by the Modulo4sequencer.•The edge event is gated to its respective CAPx register by the Mod4counter.The CAPx register is loaded on the falling edge.•The Mod4(2bit)counter is incremented via edge qualified events (CEVT1-CEVT4).•The Mod4counter continues counting (0->1->2->3->0)and wraps around unless stopped.•A 2-bit stop register is used to compare the Mod4counter output,and when equal stops the Mod4counter and inhibits further loads of the CAP1-CAP4registers.This occurs during one-shot operation.CEVT1CEVT2CEVT3CEVT4ECCTL2[CONT/ONESHT]4.432-Bit Counter and Phase ControlCapture Mode Description The continuous/one-shot block controls the start/stop and reset (zero)functions of the Mod4counter via a mono-shot type of action that can be triggered by the stop-value comparator and re-armed via software control.Once armed,the eCAP module waits for 1-4(defined by stop-value)capture events before freezing both the Mod4counter and contents of CAP1-4registers (i.e.,time-stamps).Re-arming prepares the eCAP module for another capture sequence.Also re-arming clears (to zero)the Mod4counter and permits loading of CAP1-4registers again,providing the CAPLDEN bit is set.In continuous mode,the Mod4counter continues to run (0->1->2->3->0,the one-shot action is ignored,and capture values continue to be written to CAP1-4in a circular buffer sequence.Figure 6.Details of the Continuous/One-shot BlockThis counter provides the time-base for event captures,and is clocked via the system clock.A phase register is provided to achieve synchronization with other counters,via a hardware and software forced sync.This is useful in APWM mode when a phase offset between modules is needed.On any of the four event loads,an option to reset the 32-bit counter is given.This is useful for time difference capture.The 32-bit counter value is captured first,then it is reset to 0by any of the LD1-LD4signals.Enhanced Capture (eCAP)Module14SPRUFG4A–August 2008–Revised June 2009SYNCOSYNCECCTL2[SYNCI_EN]Delta−modeCTR−OVFCTR[31−0]4.5CAP1-CAP4Registers4.6Interrupt Control Capture Mode DescriptionFigure 7.Details of the Counter and Synchronization BlockThese 32-bit registers are fed by the 32-bit counter timer bus,CTR[0-31]and are loaded (i.e.,capture a time-stamp)when their respective LD inputs are strobed.Loading of the capture registers can be inhibited via control bit CAPLDEN.During one-shot operation,this bit is cleared (loading is inhibited)automatically when a stop condition occurs,i.e.StopValue =Mod4.CAP1and CAP2registers become the active period and compare registers,respectively,in APWM mode.CAP3and CAP4registers become the respective shadow registers (APRD and ACMP)for CAP1and CAP2during APWM operation.An Interrupt can be generated on capture events (CEVT1-CEVT4,CTROVF)or APWM events (CTR =PRD,CTR =CMP).A counter overflow event (FFFFFFFF->00000000)is also provided as an interrupt source (CTROVF).The capture events are edge and sequencer qualified (i.e.,ordered in time)by the polarity select and Mod4gating,respectively.One of these events can be selected as the interrupt source (from the eCAPx module)going to the PIE.Seven interrupt events (CEVT1,CEVT2,CEVT3,CEVT4,CNTOVF,CTR=PRD,CTR=CMP)can be generated.The interrupt enable register (ECEINT)is used to enable/disable individual interrupt eventsources.The interrupt flag register (ECFLG)indicates if any interrupt event has been latched and contains the global interrupt flag bit (INT).An interrupt pulse is generated to the PIE only if any of the interrupt events are enabled,the flag bit is 1,and the INT flag bit is 0.The interrupt service routine must clear the global interrupt flag bit and the serviced event via the interrupt clear register (ECCLR)before any other interrupt pulses are generated.You can force an interrupt event via the interrupt force register (ECFRC).This is useful for test purposes.4.7Shadow Load and Lockout ControlCapture Mode Description Note:The CEVT1,CEVT2,CEVT3,CEVT4flags are only active in capture mode (ECCTL2[CAP/APWM ==0]).The CTR=PRD,CTR=CMP flags are only valid in APWM mode (ECCTL2[CAP/APWM ==1]).CNTOVF flag is valid in both modes.Figure 8.Interrupts in eCAP ModuleIn capture mode,this logic inhibits (locks out)any shadow loading of CAP1or CAP2from APRD and ACMP registers,respectively.In APWM mode,shadow loading is active and two choices are permitted:•Immediate -APRD or ACMP are transferred to CAP1or CAP2immediately upon writing a new value.•On period equal,i.e.,CTR[31:0]=PRD[31:0]Enhanced Capture (eCAP)Module16SPRUFG4A–August 2008–Revised June 20094.8APWM Mode OperationAPRDACMPtime Capture Mode DescriptionMain operating highlights of the APWM section:•The time-stamp counter bus is made available for comparison via 2digital (32-bit)comparators.•When CAP1/2registers are not used in capture mode,their contents can be used as Period and Compare values in APWM mode.•Double buffering is achieved via shadow registers APRD and ACMP (CAP3/4).The shadow register contents are transferred over to CAP1/2registers either immediately upon a write,or on a CTR =PRD trigger.•In APWM mode,writing to CAP1/CAP2active registers will also write the same value to thecorresponding shadow registers CAP3/CAP4.This emulates immediate mode.Writing to the shadow registers CAP3/CAP4will invoke the shadow mode.•During initialization,you must write to the active registers for both period and compare.Thisautomatically copies the initial values into the shadow values.For subsequent compare updates,i.e.,during run-time,you only need to use the shadow registers.Figure 9.PWM Waveform Details Of APWM Mode OperationThe behavior of APWM active high mode (APWMPOL ==0)is as follows:CMP =0x00000000,output low for duration of period (0%duty)CMP =0x00000001,output high 1cycle CMP =0x00000002,output high 2cycles CMP =PERIOD,output high except for 1cycle (<100%duty)CMP =PERIOD+1,output high for complete period (100%duty)CMP >PERIOD+1,output high for complete periodThe behavior of APWM active low mode (APWMPOL ==1)is as follows:CMP =0x00000000,output high for duration of period (0%duty)CMP =0x00000001,output low 1cycle CMP =0x00000002,output low 2cycles CMP =PERIOD,output low except for 1cycle (<100%duty)CMP =PERIOD+1,output low for complete period (100%duty)CMP >PERIOD+1,output low for complete periodCapture Module-Control and Status Registers 5Capture Module-Control and Status RegistersFigure10.Time-Stamp Counter Register(TSCTR)310TSCTRR/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetTable1.Time-Stamp Counter Register(TSCTR)Field Descriptions Bit(s)Field Description31:0TSCTR Active32-bit counter register that is used as the capture time-baseFigure11.Counter Phase Control Register(CTRPHS)310CTRPHSR/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetTable2.Counter Phase Control Register(CTRPHS)Field Descriptions Bit(s)Field Description31:0CTRPHS Counter phase value register that can be programmed for phase lag/lead.This register shadowsTSCTR and is loaded into TSCTR upon either a SYNCI event or S/W force via a control edto achieve phase control synchronization with respect to other eCAP and EPWM time-bases.Figure12.Capture-1Register(CAP1)310CAP1R/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetTable3.Capture-1Register(CAP1)Field DescriptionsBit(s)Field Description31:0CAP1This register can be loaded(written)by:)Time-Stamp(i.e.,counter value TSCTR)during a captureevent)Software-may be useful for test purposes/initialization)APRD shadow register(i.e.,CAP3)when used in APWM modeFigure13.Capture-2Register(CAP2)310CAP2R/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after reset18SPRUFG4A–August2008–Revised June2009 Enhanced Capture(eCAP)Module Capture Module-Control and Status RegistersTable4.Capture-2Register(CAP2)Field DescriptionsBit(s)Field Description31:0CAP2This register can be loaded(written)by:•Time-Stamp(i.e.,counter value)during a capture event•Software-may be useful for test purposes•APRD shadow register(i.e.,CAP4)when used in APWM modeNote:In APWM mode,writing to CAP1/CAP2active registers also writes the same value to thecorresponding shadow registers CAP3/CAP4.This emulates immediate mode.Writing to theshadow registers CAP3/CAP4invokes the shadow mode.Figure14.Capture-3Register(CAP3)310CAP3R/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetTable5.Capture-3Register(CAP3)Field DescriptionsBit(s)Field Description31:0CAP3In CMP mode,this is a time-stamp capture register.In APWM mode,this is the period shadow(APRD)register.You update the PWM period value through this register.In this mode,CAP3(APRD)shadows CAP1.Figure15.Capture-4Register(CAP4)310CAP4R/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetTable6.Capture-4Register(CAP4)Field DescriptionsBit(s)Field Description31:0CAP4In CMP mode,this is a time-stamp capture register.In APWM mode,this is the compare shadow(ACMP)register.You update the PWM compare value via this register.In this mode,CAP4(ACMP)shadows CAP2.Figure16.ECAP Control Register1(ECCTL1)15141312111098 FREE/SOFT PRESCALE CAPLDEN R/W-0R/W-0R/W-076543210 CTRRST4CAP4POL CTRRST3CAP3POL CTRRST2CAP2POL CTRRST1CAP1POL R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetCapture Module-Control and Status Registers Table7.ECAP Control Register1(ECCTL1)Field DescriptionsBit(s)Field Value Description15:14FREE/SOFT Emulation Control00TSCTR counter stops immediately on emulation suspend01TSCTR counter runs until=01x TSCTR counter is unaffected by emulation suspend(Run Free)13:9PRESCALE Event Filter prescale select00000Divide by1(i.e,.no prescale,by-pass the prescaler)00001Divide by200010Divide by400011Divide by600100Divide by800101Divide by10...11110Divide by6011111Divide by628CAPLDEN Enable Loading of CAP1-4registers on a capture event0Disable CAP1-4register loads at capture event time.1Enable CAP1-4register loads at capture event time.7CTRRST4Counter Reset on Capture Event40Do not reset counter on Capture Event4(absolute time stamp operation)1Reset counter after Capture Event4time-stamp has been captured(used in difference mode operation)6CAP4POL Capture Event4Polarity select0Capture Event4triggered on a rising edge(RE)1Capture Event4triggered on a falling edge(FE)5CTRRST3Counter Reset on Capture Event30Do not reset counter on Capture Event3(absolute time stamp)1Reset counter after Event3time-stamp has been captured(used in difference mode operation)4CAP3POL Capture Event3Polarity select0Capture Event3triggered on a rising edge(RE)1Capture Event3triggered on a falling edge(FE)3CTRRST2Counter Reset on Capture Event20Do not reset counter on Capture Event2(absolute time stamp)1Reset counter after Event2time-stamp has been captured(used in difference mode operation)2CAP2POL Capture Event2Polarity select0Capture Event2triggered on a rising edge(RE)1Capture Event2triggered on a falling edge(FE)1CTRRST1Counter Reset on Capture Event10Do not reset counter on Capture Event1(absolute time stamp)1Reset counter after Event1time-stamp has been captured(used in difference modeoperation)0CAP1POL Capture Event1Polarity select0Capture Event1triggered on a rising edge(RE)1Capture Event1triggered on a falling edge(FE)20SPRUFG4A–August2008–Revised June2009 Enhanced Capture(eCAP)Module Capture Module-Control and Status RegistersFigure17.ECAP Control Register2(ECCTL2)15111098Reserved APWMPOL CAP/APWM SWSYNCR-0R/W-0R/W-0R/W-076543210 SYNCO_SEL SYNCI_EN TSCTRSTOP REARM STOP_WRAP CONT/ONESHT R/W-0R/W-0R/W-0R/W-0R/W-1R/W-1R/W-0LEGEND:R/W=Read/Write;R=Read only;-n=value after resetTable8.ECAP Control Register2(ECCTL2)Field DescriptionsBit(s)Field Description15:11Reserved Reserved10APWMPOL APWM output polarity select.This is applicable only in APWM operating mode0Output is active high(i.e.,Compare value defines high time)1Output is active low(i.e.,Compare value defines low time)9CAP/APWM CAP/APWM operating mode select0ECAP module operates in capture mode.This mode forces the followingconfiguration:•Inhibits TSCTR resets via CTR=PRD event•Inhibits shadow loads on CAP1and2registers•Permits user to enable CAP1-4register load•CAPx/APWMx pin operates as a capture input1ECAP module operates in APWM mode.This mode forces the followingconfiguration:•Resets TSCTR on CTR=PRD event(period boundary•Permits shadow loading on CAP1and2registers•Disables loading of time-stamps into CAP1-4registers•CAPx/APWMx pin operates as a APWM output8SWSYNC Software-forced Counter(TSCTR)Synchronizing.This provides a convenientsoftware method to synchronize some or all ECAP time bases.In APWM mode,the synchronizing can also be done via the CTR=PRD event.0Writing a zero has no effect.Reading always returns a zero1Writing a one forces a TSCTR shadow load of current ECAP module and anyECAP modules down-stream providing the SYNCO_SEL bits are0,0.After writinga1,this bit returns to a zero.Note:Selection CTR=PRD is meaningful only in APWM mode;however,you canchoose it in CAP mode if you find doing so useful.7:6SYNCO_SEL Sync-Out Select00Select sync-in event to be the sync-out signal(pass through)01Select CTR=PRD event to be the sync-out signal10Disable sync out signal11Disable sync out signal5SYNCI_EN Counter(TSCTR)Sync-In select mode0Disable sync-in option1Enable counter(TSCTR)to be loaded from CTRPHS register upon either a SYNCIsignal or a S/W force event.4TSCTRSTOP Time Stamp(TSCTR)Counter Stop(freeze)Control0TSCTR stopped1TSCTR free-running。

28335多缓冲串口中文资料

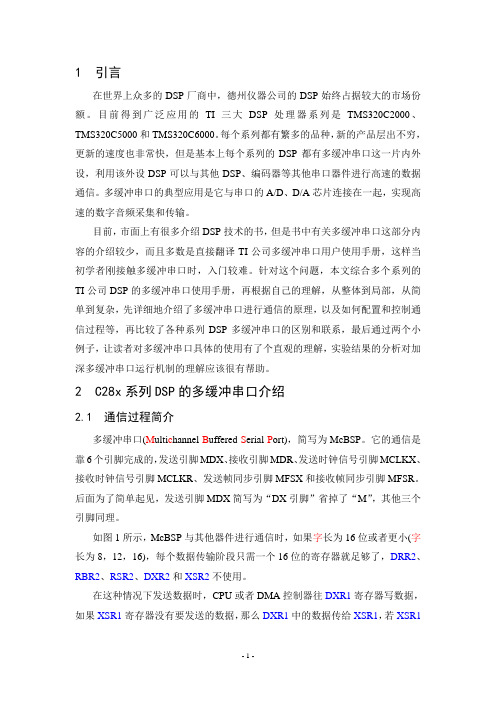

1 引言在世界上众多的DSP厂商中,德州仪器公司的DSP始终占据较大的市场份额。

目前得到广泛应用的TI三大DSP处理器系列是TMS320C2000、TMS320C5000和TMS320C6000。

每个系列都有繁多的品种,新的产品层出不穷,更新的速度也非常快,但是基本上每个系列的DSP都有多缓冲串口这一片内外设,利用该外设DSP可以与其他DSP、编码器等其他串口器件进行高速的数据通信。

多缓冲串口的典型应用是它与串口的A/D、D/A芯片连接在一起,实现高速的数字音频采集和传输。

目前,市面上有很多介绍DSP技术的书,但是书中有关多缓冲串口这部分内容的介绍较少,而且多数是直接翻译TI公司多缓冲串口用户使用手册,这样当初学者刚接触多缓冲串口时,入门较难。

针对这个问题,本文综合多个系列的TI公司DSP的多缓冲串口使用手册,再根据自己的理解,从整体到局部,从简单到复杂,先详细地介绍了多缓冲串口进行通信的原理,以及如何配置和控制通信过程等,再比较了各种系列DSP多缓冲串口的区别和联系,最后通过两个小例子,让读者对多缓冲串口具体的使用有了个直观的理解,实验结果的分析对加深多缓冲串口运行机制的理解应该很有帮助。

2 C28x系列DSP的多缓冲串口介绍2.1 通信过程简介多缓冲串口(M ulti c hannel B uffered S erial P ort),简写为McBSP。

它的通信是靠6个引脚完成的,发送引脚MDX、接收引脚MDR、发送时钟信号引脚MCLKX、接收时钟信号引脚MCLKR、发送帧同步引脚MFSX和接收帧同步引脚MFSR。

后面为了简单起见,发送引脚MDX简写为“DX引脚”省掉了“M”,其他三个引脚同理。

如图1所示,McBSP与其他器件进行通信时,如果字长为16位或者更小(字长为8,12,16),每个数据传输阶段只需一个16位的寄存器就足够了,DRR2、RBR2、RSR2、DXR2和XSR2不使用。

在这种情况下发送数据时,CPU或者DMA控制器往DXR1寄存器写数据,如果XSR1寄存器没有要发送的数据,那么DXR1中的数据传给XSR1,若XSR1中还有要发送的数据(上次DXR1传给它的值还没有完全从DX引脚移出),那么DXR1等待上次的值的最后一位从DX引脚移出时才将数据传给XSR1,如果选择了压缩扩展模式(使用虚线框中的Compand Logic,压缩扩展主要是针对μ率或者A率来说的),那么Compand Logic会将16位的数据压缩成合适的8位的数据格式,然后才将数据传给XSR1。

28335概述

得益于F28335浮点运算单元,从 而简化 软件开发,缩短开发周期。降低开发成本。

DSP技术应用

采用高性能的静态CMOS技术 主频达150MHZ(6.67ns)

低功耗设计,1.9V内核电压,3.3V

Flash编程电压为3.3V

I/O电压

支持JTAG边界扫描接口

高性能32位CPU

16*16位和32*32位的乘法累加操作

C28x

TM

GPIO 16/32-bit

EMIF SPI

88

32x32-bit

Multiplier

通讯接口 32-bit Timers (3) Each McBSP configurable as SPI Real CAN 2.0b with 32 mailboxes Time 2C at 400 Kbps JTAG I 开发套件 SEED-DEC28335+SEED-XDSusb2.0 Code Composer Studio™ IDE V3.3 DSP技术应用 Software libraries

2个增强型的eCAN2.0B接口模块

DSP技术应用

2个多通道缓冲串口(MBSP) 1个12C总线接口 12位模数转换模块

80ns转换时间

2X8通道复用输入接口

两个采样保持电路

单/连续通道转换

高达88个可配置通用目的I/O引脚

先进的仿真调试功能

DSP技术应用

硬件支持适时仿真功能

16*16位的双乘法累加器 哈佛总线结构

DSP技术应用

快速中断响应和处理能力 统一寻址模式 4M的程序/数据寻址空间

高效的代码转换功能

片上存储器

最多达256K

最多达128K

TMS320F28335中文资料(难得的资料)

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.XINT2 = &ISRExint; //告诉中断入口地址

EDIS; // This is needed to disable write to EALLOW protected registers

F28335 是带浮点运算的,动态范围更大。 F2833x 的执行速度,比相同时钟频率的 F28xx 系列定点芯片,快 50%。处理数学运算性能提

升 2.45 倍,控制算法性能提升 1.57 倍,DSP 性能提升 1.38 倍。总体性能提升近 2 倍。

TMS320F28335 的 ADC

TMS320F28335 上有 16 通道、12 位的模数转换器 ADC。他可以被配置为两个独立的 8 通道输 入模式,也可以通过配置 AdcRegs.ADCTRL1.bit.SEQ_CASC=1,将其设置为一个 16 通道的级 联输入模式。输入的方式可以通过配置 AdcRegs.ADCTRL1.bit.ACQ_PS=1,将其设置为顺序

{

EALLOW; // Before setting PLLCR turn off missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1; SysCtrlRegs.PLLCR.bit.DIV = val; EDIS;

// Optional: Wait for PLL to lock. // During this time the CPU will switch to OSCCLK/2 until // the PLL is staPU will

TMS320x2833x, 2823x DSP Enhanced Controller Area Network (eCAN) User's Guide

TMS320F2833x,2823xEnhanced Controller Area Network(eCAN) Reference GuideLiterature Number:SPRUEU1January20092SPRUEU1–January2009Submit Documentation FeedbackPreface (7)1Architecture (9)1.1CAN Overview (10)1.1.1Features (10)1.1.2Block Diagram (11)1.1.3eCAN Compatibility With Other TI CAN Modules (11)1.2The CAN Network and Module (12)1.2.1CAN Protocol Overview (12)1.3eCAN Controller Overview (13)1.3.1Standard CAN Controller(SCC)Mode (14)1.3.2Memory Map (15)1.3.3eCAN Control and Status Registers (18)1.4Message Objects (19)1.5Message Mailbox (19)1.5.1Transmit Mailbox (23)1.5.2Receive Mailbox (24)1.5.3CAN Module Operation in Normal Configuration (24)2eCAN Registers (25)2.1Mailbox Enable Register(CANME) (26)2.2Mailbox-Direction Register(CANMD) (27)2.3Transmission-Request Set Register(CANTRS) (28)2.4Transmission-Request-Reset Register(CANTRR) (29)2.5Transmission-Acknowledge Register(CANTA) (30)2.6Abort-Acknowledge Register(CANAA) (31)2.7Received-Message-Pending Register(CANRMP) (32)2.8Received-Message-Lost Register(CANRML) (33)2.9Remote-Frame-Pending Register(CANRFP) (34)2.9.1Handling of Remote Frames (34)2.10Global Acceptance Mask Register(CANGAM) (36)2.11Master Control Register(CANMC) (37)2.11.1CAN Module Action in SUSPEND (39)2.12Bit-Timing Configuration Register(CANBTC) (40)2.13Error and Status Register(CANES) (42)2.14CAN Error Counter Registers(CANTEC/CANREC) (44)2.15Interrupt Registers (45)2.15.1Global Interrupt Flag Registers(CANGIF0/CANGIF1) (45)2.15.2Global Interrupt Mask Register(CANGIM) (48)2.15.3Mailbox Interrupt Mask Register(CANMIM) (50)2.15.4Mailbox Interrupt Level Register(CANMIL) (51)2.16Overwrite Protection Control Register(CANOPC) (52)2.17eCAN I/O Control Registers(CANTIOC,CANRIOC) (53)SPRUEU1–January2009Contents3 Submit Documentation Feedback2.18Timer Management Unit (55)2.18.1Time Stamp Functions (55)2.18.2Time-Out Functions (58)2.18.3Behavior/Usage of MTOF0/1Bit in User Applications (60)2.19Mailbox Layout (61)2.19.1Message Identifier Register(MSGID) (61)2.19.2CPU Mailbox Access (62)2.19.3Message-Control Register(MSGCTRL) (63)2.19.4Message Data Registers(CANMDL,CANMDH) (64)2.20Acceptance Filter (65)2.20.1Local-Acceptance Masks(CANLAM) (65)3eCAN Configuration (67)3.1CAN Module Initialization (68)3.1.1CAN Bit-Timing Configuration (69)3.1.2CAN Bit Rate Calculation (69)3.1.3Bit Configuration Parameters for75-MHz CAN Clock (70)3.1.4Bit Configuration Parameters for50-MHz CAN Clock (71)3.1.5EALLOW Protection (72)3.2Steps to Configure eCAN (72)3.2.1Configuring a Mailbox for Transmit (73)3.2.2Transmitting a Message (73)3.2.3Configuring Mailboxes for Receive (73)3.2.4Receiving a Message (74)3.2.5Handling of Overload Situations (74)3.3Handling of Remote Frame Mailboxes (74)3.3.1Requesting Data From Another Node (74)3.3.2Answering a Remote Request (75)3.3.3Updating the Data Field (75)3.4Interrupts (75)3.4.1Interrupts Scheme (77)3.4.2Mailbox Interrupt (77)3.4.3Interrupt Handling (78)3.5CAN Power-Down Mode (80)3.5.1Entering and Exiting Local Power-Down Mode (80)3.5.2Precautions for Entering and Exiting Device Low-Power Modes(LPM) (80)3.5.3Enabling/Disabling Clock to the CAN Module (81)3.5.4Possible Failure Modes External to the CAN Controller Module (81)4SPRUEU1–January2009 ContentsSubmit Documentation FeedbackList of Figures1-1eCAN Block Diagram and Interface Circuit (11)1-2CAN Data Frame (12)1-3Architecture of the eCAN Module (13)1-4eCAN-A Memory Map (16)1-5eCAN-B Memory Map (17)2-1Mailbox-Enable Register(CANME) (26)2-2Mailbox-Direction Register(CANMD) (27)2-3Transmission-Request Set Register(CANTRS) (28)2-4Transmission-Request-Reset Register(CANTRR) (29)2-5Transmission-Acknowledge Register(CANTA) (30)2-6Abort-Acknowledge Register(CANAA) (31)2-7Received-Message-Pending Register(CANRMP) (32)2-8Received-Message-Lost Register(CANRML) (33)2-9Remote-Frame-Pending Register(CANRFP) (34)2-10Global Acceptance Mask Register(CANGAM) (36)2-11Master Control Register(CANMC) (37)2-12Bit-Timing Configuration Register(CANBTC) (40)2-13Error and Status Register(CANES) (42)2-14Transmit-Error-Counter Register(CANTEC) (44)2-15Receive-Error-Counter Register(CANREC) (44)2-16Global Interrupt Flag0Register(CANGIF0) (46)2-17Global Interrupt Flag1Register(CANGIF1) (46)2-18Global Interrupt Mask Register(CANGIM) (48)2-19Mailbox Interrupt Mask Register(CANMIM) (50)2-20Mailbox Interrupt Level Register(CANMIL) (51)2-21Overwrite Protection Control Register(CANOPC) (52)2-22TX I/O Control Register(CANTIOC) (53)2-23RX I/O Control Register(CANRIOC) (54)2-24Time-Stamp Counter Register(CANTSC) (56)2-25Message Object Time Stamp Registers(MOTS) (57)2-26Message-Object Time-Out Registers(MOTO) (58)2-27Time-Out Control Register(CANTOC) (59)2-28Time-Out Status Register(CANTOS) (60)2-29Message Identifier Register(MSGID)Register (61)2-30Message-Control Register(MSGCTRL) (63)2-31Message-Data-Low Register With DBO=0(CANMDL) (64)2-32Message-Data-High Register With DBO=0(CANMDH) (64)2-33Message-Data-Low Register With DBO=1(CANMDL) (64)2-34Message-Data-High Register With DBO=1(CANMDH) (64)2-35Local-Acceptance-Mask Register(LAM n) (66)3-1Initialization Sequence (68)3-2CAN Bit Timing (69)3-3Interrupts Scheme (76)SPRUEU1–January2009List of Figures5 Submit Documentation FeedbackList of Tables1-1Register Map (18)1-2eCAN-A Mailbox RAM Layout (20)1-3Addresses of LAM,MOTS and MOTO registers for mailboxes(eCAN-A) (21)1-4eCAN-B Mailbox Ram Layout (22)1-5Addresses of LAM,MOTS,and MOTO Registers for Mailboxes(eCAN-B) (23)1-6Message Object Behavior Configuration (23)2-1Mailbox-Enable Register(CANME)Field Descriptions (26)2-2Mailbox-Direction Register(CANMD)Field Descriptions (27)2-3Transmission-Request Set Register(CANTRS)Field Descriptions (28)2-4Transmission-Request-Reset Register(CANTRR)Field Descriptions (29)2-5Transmission-Acknowledge Register(CANTA)Field Descriptions (30)2-6Abort-Acknowledge Register(CANAA)Field Descriptions (31)2-7Received-Message-Pending Register(CANRMP)Field Descriptions (32)2-8Received-Message-Lost Register(CANRML)Field Descriptions (33)2-9Remote-Frame-Pending Register(CANRFP)Field Descriptions (34)2-10Global Acceptance Mask Register(CANGAM)Field Descriptions (36)2-11Master Control Register(CANMC)Field Descriptions (37)2-12Bit-Timing Configuration Register(CANBTC)Field Descriptions (40)2-13Error and Status Register(CANES)Field Descriptions (42)2-14Global Interrupt Flag Registers(CANGIF0/CANGIF1)Field Descriptions (47)2-15Global Interrupt Mask Register(CANGIM)Field Descriptions (48)2-16Mailbox Interrupt Mask Register(CANMIM)Field Descriptions (50)2-17Mailbox Interrupt Level Register(CANMIL)Field Descriptions (51)2-18Overwrite Protection Control Register(CANOPC)Field Descriptions (52)2-19TX I/O Control Register(CANTIOC)Field Descriptions (53)2-20RX I/O Control Register(CANRIOC)Field Descriptions (54)2-21Time-Stamp Counter Register(CANTSC)Field Descriptions (56)2-22Message Object Time Stamp Registers(MOTS)Field Descriptions (57)2-23Message-Object Time-Out Registers(MOTO)Field Descriptions (58)2-24Time-Out Control Register(CANTOC)Field Descriptions (59)2-25Time-Out Status Register(CANTOS)Field Descriptions (60)2-26Message Identifier Register(MSGID)Field Descriptions (61)2-27Message-Control Register(MSGCTRL)Field Descriptions (63)2-28Local-Acceptance-Mask Register(LAM n)Field Descriptions (66)3-1BRP Field for Bit Rates(BT=15,TSEG1reg=10,TSEG2reg=2,Sampling Point=80%) (70)3-2Achieving Different Sampling Points With a BT of15 (70)3-3BRP Field for Bit Rates(BT=10,TSEG1reg=6,TSEG2reg=1,Sampling Point=80%) (71)3-4Achieving Different Sampling Points With a BT of20 (71)3-5eCAN Interrupt Assertion/Clearing (78)6SPRUEU1–January2009 List of TablesSubmit Documentation FeedbackPrefaceSPRUEU1–January2009About This ManualThis document describes the enhanced controller area network(eCAN)on the F2833x and F2823xdevices.Notational ConventionsThis document uses the following conventions.•Hexadecimal numbers are shown with the suffix h.For example,the following number is40 hexadecimal(decimal64):40h.Related Documentation From Texas InstrumentsThe following documents describe the F2833x and related peripherals.Copies ofthese documents are available for downloading atData Manual and Errata—ofCPU User's Guides—SPRU430—describes the centralTMS320C28x fixed-point digital signal processors(DSPs).It also describes emulation features available on these DSPs.SPRUEO2—describes thePeripheral Guides—SPRU566—describes the peripheral referenceSPRUFB0—TMS320x2833x,2823x System Control and Interrupts Reference Guide describes the various interrupts and system control features of the2833x digital signal controllers(DSCs).SPRU812—describes how toSPRU949—describes the XINTF,whichis aSPRU963—describes the purpose andand provides examples of code.It also describes other contents of the device on-chip boot ROM and identifies where all ofthe information is located within that memory.SPRUEU1–January2009Read This First7 Submit Documentation FeedbackRelated Documentation From Texas Instruments SPRUFB7—describesthe a DSPand other devices in a system.SPRUFB8—describes the DMAonSPRUG04—switch mode power supply control,UPS(uninterruptible power supplies),and other forms of powerconversion.SPRUG02—describes theSPRUFG4—describes theSPRUG05—encoder to get position,direction,and speed information from a rotating machine in highperformance motion and position control systems.It includes the module description and registers.SPRUEU1—in electrically noisy environments.SPRUFZ5—describesthe SCImodules support digital communications between the CPU and other asynchronous peripherals thatuse the standard non-return-to-zero(NRZ)format.SPRUEU3—describes the SPI-a ofprogrammed length(one to sixteen bits)to be shifted into and out of the device at a programmedbit-transfer rate.SPRUG03—describes theTools Guides—SPRU513—describes the assembly languagetools code),assembler directives,macros,common object file format,and symbolic debugging directives for the TMS320C28x device.SPRU514—describes the TMS320C28x™C/C++code and produces TMS320DSP assembly language source code for the TMS320C28x device.SPRU608—describes the simulator,simulates the instruction set of the C28x™core.SPRU625—Read This First8SPRUEU1–January2009Submit Documentation FeedbackChapter1SPRUEU1–January2009The enhanced Controller Area Network(eCAN)module implemented in the C28x™DSP is a full-CAN controller and is compatible with the CAN 2.0B standard(active).It uses established protocol to communicate serially with other controllers in electrically noisy environments.With32fully configurable mailboxes and time–stamping feature,the eCAN module provides a versatile and robust serial communication interface.The eCAN module described in guide is a Type2eCAN.Refer to theTMS320x28xx,28xxx DSP Peripheral Reference Guide for a list of other devices with a eCAN module of the sametype,to determine the differences and for a list of device-specific differences within a type.Some devices have a second CAN module,eCAN-B.The word eCAN is generically used to refer to the CAN modules.The specific module reference(A or B)is used where appropriate.For a given CAN module,the same address space is used for the module registers in all28xx/28xxx devices.Topic PageSPRUEU1–January2009Architecture9 Submit Documentation Feedback1.1CAN Overview1.1.1FeaturesCAN Overview Figure 1–1shows the major blocks of the eCAN and the interface circuits.The eCAN module has the following features:•Fully compliant with CAN protocol,version 2.0B•Supports data rates up to 1Mbps•Thirty-two mailboxes,each with the following properties:–Configurable as receive or transmit–Configurable with standard or extended identifier–Has a programmable acceptance filter mask–Supports data and remote frame–Supports 0to 8bytes of data–Uses a 32-bit time stamp on received and transmitted message–Protects against reception of new message–Allows dynamically programmable priority of transmit message–Employs a programmable interrupt scheme with two interrupt levels–Employs a programmable interrupt on transmission or reception time-out•Low–power mode•Programmable wake–up on bus activity•Automatic reply to a remote request message•Automatic retransmission of a frame in case of loss of arbitration or error•32-bit time-stamp counter synchronized by a specific message (communication in conjunction with mailbox 16)•Self–test mode–Operates in a loopback mode receiving its own message.A “dummy”acknowledge is provided,thereby eliminating the need for another node to provide the acknowledge bit.10Architecture SPRUEU1–January 2009Submit Documentation Feedback1.1.2Block DiagramControlsAddressDataECAN1INTECAN0INT1.1.3eCAN Compatibility With Other TI CAN Modules CAN OverviewFigure 1-1.eCAN Block Diagram and Interface CircuitA The communication buffers are transparent to the user and are not accessible by user code.The eCAN module is identical to the “High-end CAN Controller (HECC)”used in the TMS470™series microcontrollers from Texas Instruments with some minor changes.The eCAN module features several enhancements (such as increased number of mailboxes with individual acceptance masks,time stamping,etc.)over the CAN module featured in 240x™series of DSPs.For this reason,code written for 240x CAN modules cannot be directly ported to eCAN.However,eCAN follows the same register bit-layout structure and bit functionality as that of 240x CAN (for registers that exist in both devices)i.e.,many registers and bits perform exactly identical functions across these two platforms.This makes code migration a relatively easy task,more so with code written in C language.1.2The CAN Network and Module1.2.1CAN Protocol OverviewBit length– 11-bit identifier + RTR bit for standard frame format– 29-bit identifier + SRR bit + IDE bit + RTR bit for extended frame format Where: RTR = Remote Transmission Request SRR = Substitute Remote Request IDE = Identifier ExtensionNote: Unless otherwise noted, numbers are amount of bits in field.The CAN Network and Module The controller area network (CAN)uses a serial multimaster communication protocol that efficientlysupports distributed real-time control,with a very high level of security,and a communication rate of up to 1Mbps.The CAN bus is ideal for applications operating in noisy and harsh environments,such as in the automotive and other industrial fields that require reliable communication.Prioritized messages of up to eight bytes in data length can be sent on a multimaster serial bus using an arbitration protocol and an error-detection mechanism for a high level of data integrity.The CAN protocol supports four different frame types for communication:•Data frames that carry data from a transmitter node to the receiver nodes•Remote frames that are transmitted by a node to request the transmission of a data frame with the same identifier•Error frames that are transmitted by any node on a bus-error detection•Overload frames that provide an extra delay between the preceding and the succeeding data frames or remote frames.In addition,CAN specification version 2.0B defines two different formats that differ in the length of the identifier field:standard frames with an 11-bit identifier and extended frames with 29-bit identifier.CAN standard data frames contain from 44to 108bits and CAN extended data frames contain 64to 128bits.Furthermore,up to 23stuff bits can be inserted in a standard data frame,and up to 28stuff bits in an extended data frame,depending on the data-stream coding.The overall maximum data frame length is then 131bits for a standard frame and 156bits for an extended frame.The bit fields that make up standard/extended data frames,along with their position as shown in Figure 1-2include the following:•Start of frame•Arbitration field containing the identifier and the type of message being sent •Control field indicating the number of bytes being transmitted.•Up to 8bytes of data•Cyclic redundancy check (CRC)•Acknowledgment •End-of-frame bitsFigure 1-2.CAN Data FrameThe eCAN controller provides the CPU with full functionality of the CAN protocol,version 2.0B.The CAN controller minimizes the CPU’s load in communication overhead and enhances the CAN standard by providing additional features.The architecture of eCAN module,shown in Figure 1-3,is composed of a CAN protocol kernel (CPK)and a message controller.12ArchitectureSPRUEU1–January 2009 eCAN Controller OverviewFigure1-3.Architecture of the eCAN ModuleA The receive and transmit buffers are transparent to the user and are not accessible by user code.Two functions of the CPK are to decode all messages received on the CAN bus according to the CAN protocol and to transfer these messages into a receive buffer.Another CPK function is to transmitmessages on the CAN bus according to the CAN protocol.The message controller of a CAN controller is responsible for determining if any message received by the CPK must be preserved for the CPU use or be discarded.At the initialization phase,the CPU specifies to the message controller all message identifiers used by the application.The message controller is alsoresponsible for sending the next message to transmit to the CPK according to the message’s priority.1.3eCAN Controller OverviewThe eCAN is a CAN controller with an internal32-bit architecture.The eCAN module consists of:•The CAN protocol kernel(CPK)•The message controller comprising:–The memory management unit(MMU),including the CPU interface and the receive control unit (acceptance filtering),and the timer management unit–Mailbox RAM enabling the storage of32messages–Control and status registersAfter the reception of a valid message by the CPK,the receive control unit of the message controllerdetermines if the received message must be stored into one of the32message objects of the mailboxRAM.The receive control unit checks the state,the identifier,and the mask of all message objects todetermine the appropriate mailbox location.The received message is stored into the first mailbox passing the acceptance filtering.If the receive control unit could not find any mailbox to store the receivedmessage,the message is discarded.A message is composed of an11-or29-bit identifier,a control field,and up to8bytes of data.eCAN Controller Overview When a message must be transmitted,the message controller transfers the message into the transmit buffer of the CPK in order to start the message transmission at the next bus-idle state.When more than one message must be transmitted,the message with the highest priority that is ready to be transmitted is transferred into the CPK by the message controller.If two mailboxes have the same priority,then themailbox with the higher number is transmitted first.The timer management unit comprises a time-stamp counter and apposes a time stamp to all messages received or transmitted.It generates an interrupt when a message has not been received or transmitted during an allowed period of time(time-out).The time-stamping feature is available in eCAN mode only.To initiate a data transfer,the transmission request bit(TRS.n)has to be set in the corresponding control register.The entire transmission procedure and possible error handling are then performed without any CPU involvement.If a mailbox has been configured to receive messages,the CPU easily reads its data registers using CPU read instructions.The mailbox may be configured to interrupt the CPU after every successful message transmission or reception.1.3.1Standard CAN Controller(SCC)ModeThe SCC Mode is a reduced functionality mode of the eCAN.Only16mailboxes(0through15)areavailable in this mode.The time stamping feature is not available and the number of acceptance masks available is reduced.This mode is selected by default.The SCC mode or the full featured eCAN mode is selected using the SCB bit(CANMC.13).14Architecture SPRUEU1–January2009 eCAN Controller Overview 1.3.2Memory MapThe eCAN module has two different address segments mapped in the memory.The first segment is used to access the control registers,the status registers,the acceptance masks,the time stamp,and thetime-out of the message objects.The access to the control and status registers is limited to32-bit wide accesses.The local acceptance masks,the time stamp registers,and the time-out registers can beaccessed8-bit,16-bit and32-bit wide.The second address segment is used to access the mailboxes.This memory range can be accessed8-bit,16-bit and32-bit wide.Each of these two memory blocks,shown in Figure1-4,uses512bytes of address space.The message storage is implemented by a RAM that can be addressed by the CAN controller or the CPU.The CPU controls the CAN controller by modifying the various mailboxes in the RAM or the additionalregisters.The contents of the various storage elements are used to perform the functions of theacceptance filtering,message transmission,and interrupt handling.The mailbox module in the eCAN provides32message mailboxes of8-byte data length,a29-bit identifier, and several control bits.Each mailbox can be configured as either transmit or receive.In the eCAN mode, each mailbox has its individual acceptance mask.Note:LAMn,MOTSn and MOTOn registers and mailboxes not used in an application(disabled inthe CANME register)may be used as general-purpose data memory by the CPU.1.3.2.132-bit Access to Control and Status RegistersAs indicated in Section1.3.2,only32-bit accesses are allowed to the Control and Status registers.16-bit access to potentially corrupt the register contents or return false data.The DSPheader files released by TI employs a shadow register structure that aids in32-bit access.Following are a few examples of how the shadow register structure may be employed to perform32-bit reads/writes:Example1-1.Modifying a bit in a registerECanaShadow.CANTIOC.all=ECanaRegs.CANTIOC.all;//Step1ECanaShadow.CANTIOC.bit.TXFUNC=1;//Step2ECanaRegs.CANTIOC.all=ECanaShadow.CANTIOC.all;//Step3Step1:Perform a32-bit read to copy the entire register to its shadowStep2:Modify the needed bit(s)in the shadowStep3:Perform a32-bit write to copy the modified shadow to the original register.Note:Some bits like TAn and RMPn are cleared by writing a1to it.Care should be taken not toclear bits inadvertently.Example1-2.Checking the value of a bit in a registerdo{ECanaShadow.CANTA.all=ECanaRegs.CANTA.all;}while(ECanaShadow.CANTA.bit.TA25==0);//Wait for TA5bit to be set..In the above example,the value of TA25bit needs to be checked.This is done by first copying the entire CANTA register to its shadow(using a32-bit read)and then checking the relevant bit,repeating thisoperation until that condition is satisfied.TA25bit should NOT be checked with the following statement: while(ECanaRegs.CANTA.bit.TA25==0);eCAN−A Control and Status Registers6110h−616118h−61eCAN Controller Overview Figure 1-4.eCAN-A Memory MapArchitecture16SPRUEU1–January 2009 eCAN Controller OverviewFigure1-5.eCAN-B Memory MapeCAN−B Control and Status RegisterseCAN Controller Overview 1.3.3eCAN Control and Status RegistersThe eCAN registers listed in Table1-1are used by the CPU to configure and control the CAN controller and the message objects.Table1-1.Register MapREGISTER NAME(1)ECAN-A ECAN-B SIZE DESCRIPTIONADDRESS ADDRESS(x32)CANME0x60000x62001Mailbox enableCANMD0x60020x62021Mailbox directionCANTRS0x60040x62041Transmit request setCANTRR0x60060x62061Transmit request resetCANTA0x60080x62081Transmission acknowledgeCANAA0x600A0x620A1Abort acknowledgeCANRMP0x600C0x620C1Receive message pendingCANRML0x600E0x620E1Receive message lostCANRFP0x60100x62101Remote frame pendingCANGAM0x60120x62121Global acceptance maskCANMC0x60140x62141Master controlCANBTC0x60160x62161Bit-timing configurationCANES0x60180x62181Error and statusCANTEC0x601A0x621A1Transmit error counterCANREC0x601C0x621C1Receive error counterCANGIF00x601E0x621E1Global interrupt flag0CANGIM0x60200x62201Global interrupt maskCANGIF10x60220x62221Global interrupt flag1CANMIM0x60240x62241Mailbox interrupt maskCANMIL0x60260x62261Mailbox interrupt levelCANOPC0x60280x62281Overwrite protection controlCANTIOC0x602A0x622A1TX I/O controlCANRIOC0x602C0x622C1RX I/O controlCANTSC0x602E0x622E1Time stamp counter(Reserved in SCC mode)CANTOC0x60300x62301Time-out control(Reserved in SCC mode)CANTOS0x60320x62321Time-out status(Reserved in SCC mode)(1)These registers are mapped to Peripheral Frame1.Note:Only32-bit accesses are allowed to the control and status registers.This restriction does notapply to the mailbox RAM area.See Section1.3.2.1for more information.18Architecture SPRUEU1–January2009 Message Objects 1.4Message ObjectsThe eCAN module has32different message objects(mailboxes).Each message object can be configured to either transmit or receive.Each message object has itsindividual acceptance mask.A message object consists of a message mailbox with:•The29-bit message identifier•The message control register•8bytes of message data•A29-bit acceptance mask•A32-bit time stamp•A32-bit time-out valueFurthermore,corresponding control and status bits located in the registers allow control of the message objects.1.5Message MailboxThe message mailboxes are the RAM area where the CAN messages are actually stored after they are received or before they are transmitted.The CPU may use the RAM area of the message mailboxes that are not used for storing messages as normal memory.Each mailbox contains:•The message identifier–29bits for extended identifier–11bits for standard identifier•The identifier extension bit,IDE(MSGID.31)•The acceptance mask enable bit,AME(MSGID.30)•The auto answer mode bit,AAM(MSGID.29)•The transmit priority level,TPL(MSGCTRL.12-8)•The remote transmission request bit,RTR(MSGCTRL.4)•The data length code,DLC(MSGCTRL.3-0)•Up to eight bytes for the data fieldEach of the mailboxes can be configured as one of four message object types(see Table1-5).Transmit and receive message objects are used for data exchange between one sender and(1to n communication link),whereas request and reply message objects are used to set up a one-to-onecommunication link.Table1-2lists the mailbox RAM layout.Message Mailbox Table1-2.eCAN-A Mailbox RAM LayoutMailbox MSGID MSGCTRL CANMDL CANMDHMSGIDL-MSGIDH MSGCTRL-Rsvd CANMDL_L-CANMDL_H CANMDH_L-CANMDH_H 06100-6101h6102-6103h6104-6105h6106-6107h16108-6109h610A-610Bh610C-610Dh610E-610Fh26110-6111h6112-6113h6114-6115h6116-6117h36118-6119h611A-611Bh611C-611Dh611E-611Fh46120-6121h6122-6123h6124-6125h6126-6127h56128-6129h612A-612Bh612C-612Dh612E-612Fh66130-6131h6132-6133h6134-6135h6136-6137h76138-6139h613A-613Bh613C-613Dh613E-613Fh86140-6141h6142-6143h6144-6145h6146-6147h96148-6149h614A-614Bh614C-614Dh614E-614Fh106150-6151h6152-6153h6154-6155h6156-6157h116158-6159h615A-615Bh615C-615Dh615E-615Fh126160-6161h6162-6163h6164-6165h6166-6167h136168-6169h616A-616Bh616C-616Dh616E-616Fh146170-6171h6172-6173h6174-6175h6176-6177h156178-6179h617A-617Bh617C-617Dh617E-617Fh166180-6181h6182-6183h6184-6185h6186-6187h176188-6189h618A-618Bh618C-618Dh618E-618Fh186190-6191h6192-6193h6194-6195h6196-6197h196198-6199h619A-619Bh619C-619Dh619E-619Fh2061A0-61A1h61A2-61A3h61A4-61A5h61A6-61A7h2161A8-61A9h61AA-61ABh61AC-61ADh61AE-61AFh2261B0-61B1h61B2-61B3h61B4-61B5h61B6-61B7h2361B8-61B9h61BA-61BBh61BC-61BDh61BE-61BFh2461C0-61C1h61C2-61C3h61C4-61C5h61C6-61C7h2561C8-61C9h61CA-61CBh61CC-61CDh61CE-61CFh2661D0-61D1h61D2-61D3h61D4-61D5h61D6-61D7h2761D8-61D9h61DA-61DBh61DC-61DDh61DE-61DFh2861E0-61E1h61E2-61E3h61E4-61E5h61E6-61E7h2961E8-61E9h61EA-61EBh61EC-61EDh61EE-61EFh3061F0-61F1h61F2-61F3h61F4-61F5h61F6-61F7h3161F8-61F9h61FA-61FBh61FC-61FDh61FE-61FFh20SPRUEU1–January2009 Architecture。

【世界五百强机密文件】dsp28335相关文档

TMS320x281x和TMS320x2833x/TMS320x2823x之间的区别最近在使用TI的28355芯片,由于以前没有接触过,在网上资料也不多,就去TI官网找英文来看;281x和283/23x都是C2000™系列的芯片,后者较前者有很多增强的地方,下面分开一条一条来写:1:CPU(浮点)2833x增加了FPU32位单精度浮点运算单元,不过新的指令是作为标准C28x指令集的扩展来加进去的,所以能够对定点运算100%兼容,锁存上溢和下溢标志位和PIE相连,方便调试;2:CCS开发环境安装后要装专门的升级包,按顺序装好才能使用28335芯片,然后使用2833x的头文件;然后进入ccs后还有设置一下32浮点运算,加入库文件,这部分在网上有详细介绍,编译器,汇编器,连接器最好5.0以上;3:封装管脚不兼容,需重新画板;4:运行频率和供电电压281x:135MHZ以下1.8v,以上到150MHZ1.9v28335:100MHZ以下1.8v,以上到150MHZ1.9vIO口供电电压都是为3.3v5:上电顺序281x:Vddio先,Vdd后28335:可同时上电,也可使用281x的上电顺序;6:SARAM281x:18*16字;28355:34*16字;最大SARAM块4k*16字,变小了;双内存映射;DMA直接访问SARAM;7:FlashF28335: 256K x 16 FlashF2812:128*16 Flash8:外设28355去除了EV,用3个新的外设代替ePWM,eCAP,eQEP增加了DMA:6通道,每个通道有自己的中断,2种运行方式;I2C Bus;文档升级;ADC:电容10uf-2.2uf,电阻24.9k-22k,AD转换接触后有3个中断可以触发,DMA直接读取结果寄存器;CSM密码位置不同;外部存储器接口DMA可直接读取;去除McBSP上的FIFOs,用DMA替代;eCAN增多1个;SCI增多1个9:中断新增外设中断,5个新的外部中断基于TMS320F28335信号处理板的设计与实现TMS320F28335是,TI公司最新推出的一款32位浮点数字信号控制器,兼顾了DSP强大的处理核心和M CU丰富的片上外设。

DMA模块使用说明—28335