LP62E16128AU-70LLI中文资料

W9812G2GB-6I中文资料

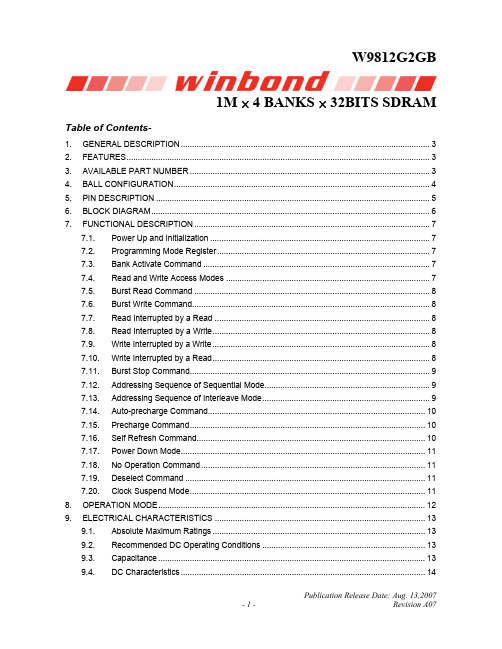

1M × 4 BANKS × 32BITS SDRAM Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.AVAILABLE PART NUMBER (3)4.BALL CONFIGURATION (4)5.PIN DESCRIPTION (5)6.BLOCK DIAGRAM (6)7.FUNCTIONAL DESCRIPTION (7)7.1.Power Up and Initialization (7)7.2.Programming Mode Register (7)7.3.Bank Activate Command (7)7.4.Read and Write Access Modes (7)7.5.Burst Read Command (8)7.6.Burst Write Command (8)7.7.Read Interrupted by a Read (8)7.8.Read Interrupted by a Write (8)7.9.Write Interrupted by a Write (8)7.10.Write Interrupted by a Read (8)7.11.Burst Stop Command (9)7.12.Addressing Sequence of Sequential Mode (9)7.13.Addressing Sequence of Interleave Mode (9)7.14.Auto-precharge Command (10)7.15.Precharge Command (10)7.16.Self Refresh Command (10)7.17.Power Down Mode (11)7.18.No Operation Command (11)7.19.Deselect Command (11)7.20.Clock Suspend Mode (11)8.OPERATION MODE (12)9.ELECTRICAL CHARACTERISTICS (13)9.1.Absolute Maximum Ratings (13)9.2.Recommended DC Operating Conditions (13)9.3.Capacitance (13)9.4.DC Characteristics (14)9.5.AC Characteristics and Operating Condition (15)10.TIMING WAVEFORMS (17)mand Input Timing (17)10.2.Read Timing (18)10.3.Control Timing of Input/Output Data (19)10.4.Mode Register Set Cycle (20)11.OPERATING TIMING EXAMPLE (21)11.1.Interleaved Bank Read (Burst Length = 4, CAS Latency = 3) (21)11.2.Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge) (22)11.3.Interleaved Bank Read (Burst Length = 8, CAS Latency = 3) (23)11.4.Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge) (24)11.5.Interleaved Bank Write (Burst Length = 8) (25)11.6.Interleaved Bank Write (Burst Length = 8, Auto-precharge) (26)11.7.Page Mode Read (Burst Length = 4, CAS Latency = 3) (27)11.8.Page Mode Read / Write (Burst Length = 8, CAS Latency = 3) (28)11.9.Auto-precharge Read (Burst Length = 4, CAS Latency = 3) (29)11.10.Auto-precharge Write (Burst Length = 4) (30)11.11.Auto Refresh Cycle (31)11.12.Self Refresh Cycle (32)11.13.Burst Read and Single Write (Burst Length = 4, CAS Latency = 3) (33)11.14.Power Down Mode (34)11.15.Auto-precharge Timing (Read Cycle) (35)11.16.Auto-precharge Timing (Write Cycle) (36)11.17.Timing Chart of Read to Write Cycle (37)11.18.Timing Chart of Write to Read Cycle (37)11.19.Timing Chart of Burst Stop Cycle (Burst Stop Command) (38)11.20.Timing Chart of Burst Stop Cycle (Precharge Command) (38)11.21.CKE/DQM Input Timing (Write Cycle) (39)11.22.CKE/DQM Input Timing (Read Cycle) (40)12.PACKAGE SPECIFICATION (41)12.1.TFBGA 90 Balls pitch=0.8mm (41)13.REVISION HISTORY (42)1. GENERAL DESCRIPTIONW9812G2GB is a high-speed synchronous dynamic random access memory (SDRAM), organized as 1,048,576 words × 4 banks × 32 bits. Using pipelined architecture and 0.11 µm process technology, W9812G2GB delivers a data bandwidth of up to 166MHz words per second (-6). For different application, W9812G2GB is sorted into two speed grades: -6/-6I and -75. The –6 is compliant to the 166MHz/CL3 specification (the -6I grade which is guaranteed to support -40°C ~ 85°C). The -75 is compliant to the 133MHz/CL3 specification.Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle. The multiple bank nature enables interleaving among internal banks to hide the precharging time.By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9812G2GB is ideal for main memory in high performance applications.2. FEATURES• 3.3V ± 0.3V Power Supply•Up to 166 MHz Clock Frequency• 1,048,576 Words × 4 banks × 32 bits organization• Self Refresh Mode•CAS Latency: 2 and 3•Burst Length: 1, 2, 4, 8 and full page•Burst Read, Single Writes Mode•Byte Data Controlled by DQM•Auto-precharge and Controlled Precharge•4K Refresh cycles / 64 mS• Interface: LVTTL•Packaged in TFBGA 90 Ball•W9812G2GB is using lead free materials with RoHS compliant3. AVAILABLE PART NUMBERPART NUMBER SPEEDMAXIMUM SELFREFRESH CURRENTOPERATINGTEMPERATUREW9812G2GB-6 166MHz/CL3 2mA 0°C ~ 70°C W9812G2GB-6I 166MHz/CL3 2mA -40°C ~ 85°C W9812G2GB-75 133MHZ/CL3 2mA 0°C ~ 70°C4. BALL CONFIGURATION5. PIN DESCRIPTION6. BLOCK DIAGRAM7. FUNCTIONAL DESCRIPTION7.1. Power Up and InitializationThe default power up state of the mode register is unspecified. The following power up and initialization sequence need to be followed to guarantee the device being preconditioned to each user specific needs.During power up, all V DD and V DDQ pins must be ramp up simultaneously to the specified voltage when the input signals are held in the “NOP” state. The power up voltage must not exceed V DD +0.3V on any of the input pins or V DD supplies. After power up, an initial pause of 200 µS is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power up, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. An additional eight Auto Refresh cycles (CBR) are also required before or after programming the Mode Register to ensure proper subsequent operation.7.2. Programming Mode RegisterAfter initial power up, the Mode Register Set Command must be issued for proper device operation. All banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of RA,S CAS, CS and WE at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued following the mode register set command once a delay equal to t RSC has elapsed. Please refer to the next page for Mode Register Set Cycle and Operation Table.7.3. Bank Activate CommandThe Bank Activate command must be applied before any Read or Write operation can be executed. The operation is similar to RAS activate in EDO DRAM. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must not be less than the RAS to CAS delay time (t RCD). Once a bank has been activated it must be precharged before another Bank Activate command can be issued to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device (t RC). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time (t RRD). The maximum time that each bank can be held active is specified as t RAS (max).7.4. Read and Write Access ModesAfter a bank has been activated, a read or write cycle can be followed. This is accomplished by setting S RCD delay. WE pin voltage level RAS high and CA low at the clock rising edge after minimum of tdefines whether the access cycle is a read operation (WE high), or a write operation (WE low). The address inputs determine the starting column address.Reading or writing to a different row within an activated bank requires the bank be precharged and a new Bank Activate command be issued. When more than one bank is activated, interleaved bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between multiple banks, seamless data access operation amongmany different pages can be realized. Read or Write Commands can also be issued to the same bank or between active banks on every clock cycle.7.5. Burst Read CommandThe Burst Read command is initiated by applying logic low level to CS and CAS while holding RAS and WE high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The Mode Register sets type of burst (sequential or interleave) and the burst length (1, 2, 4, 8 and full page) during the Mode Register Set Up cycle. Table 2 and 3 in the next page explain the address sequence of interleave mode and sequential mode.7.6. Burst Write CommandThe Burst Write command is initiated by applying logic low level to CS, CAS and WE while holding RAS high at the rising edge of the clock. The address inputs determine the starting column address. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. Data supplied to the DQ pins after burst finishes will be ignored.7.7. Read Interrupted by a ReadA Burst Read may be interrupted by another Read Command. When the previous burst is interrupted, the remaining addresses are overridden by the new read address with the full burst length. The data from the first Read Command continues to appear on the outputs until the CAS Latency from the interrupting Read Command the is satisfied.7.8. Read Interrupted by a WriteTo interrupt a burst read with a Write Command, DQM may be needed to place the DQs (output drivers) in a high impedance state to avoid data contention on the DQ bus. If a Read Command will issue data on the first and second clocks cycles of the write operation, DQM is needed to insure the DQs are tri-stated. After that point the Write Command will have control of the DQ bus and DQM masking is no longer needed.7.9. Write Interrupted by a WriteA burst write may be interrupted before completion of the burst by another Write Command. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.7.10. Write Interrupted by a ReadA Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is activated. The DQs must be in the high impedance state at least one cycle before the new read data appears on the outputs to avoid data contention. When the Read Command is activated, any residual data from the burst write cycle will be ignored.7.11. Burst Stop CommandA Burst Stop Command may be used to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank, if the burst length is full page. Use of the Burst Stop Command during other burst length operations is illegal. The Burst Stop Command is defined by having RAS and CAS high with CS and WE low at the rising edge of the clock. The data DQs go to a high impedance state after a delay which is equal to the CAS Latency in a burst read cycle interrupted by Burst Stop.7.12. Addressing Sequence of Sequential ModeA column access is performed by increasing the address from the column address which is input to the device. The disturb address is varied by the Burst Length as shown in Table 2.Table 2 Address Sequence of Sequential Mode7.13. Addressing Sequence of Interleave ModeA column access is started in the input column address and is performed by inverting the address bit in the sequence shown in Table 3.Table 3 Address Sequence of Interleave Mode7.14. Auto-precharge CommandIf A10 is set to high when the Read or Write Command is issued, then the auto-precharge function is entered. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge automatically before all burst read cycles have been completed. Regardless of burst length, it will begin a certain number of clocks prior to the end of the scheduled burst cycle. The number of clocks is determined by CAS Latency.A Read or Write Command with auto-precharge can not be interrupted before the entire burst operation is completed. Therefore, use of a Read, Write or Precharge Command is prohibited during a read or write cycle with auto-precharge. Once the precharge operation has started, the bank cannot be reactivated until the Precharge time (t RP) has been satisfied. Issue of Auto-precharge command is illegal if the burst is set to full page length. If A10 is high when a Write Command is issued, the Write with Auto-precharge function is initiated. The SDRAM automatically enters the precharge operation two clocks delay from the last burst write cycle. This delay is referred to as Write t WR. The bank undergoing auto-precharge can not be reactivated until t WR and t RP are satisfied. This is referred to as t DAL, Data-in to Active delay (t DAL = t WR + t RP). When using the Auto-precharge Command, the interval between the Bank Activate Command and the beginning of the internal precharge operation must satisfy t RAS (min).7.15. Precharge CommandThe Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is entered when CS, RAS and WE are low and CAS is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or all banks simultaneously. Three address bits, A10, BS0, and BS1, are used to define which bank(s) is to be precharged when the command is issued. After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time (t RP).7.16. Self Refresh CommandThe Self Refresh Command is defined by having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. All banks must be idle prior to issuing the Self Refresh Command. Once the command is registered, CKE must be held low to keep the device in Self Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The device will exit Self Refresh operation after CKE is returned high. A minimum delay time is required when the device exits Self Refresh Operation and before the next command can be issued. This delay is equal to the t AC cycle time plus the Self Refresh exit time.If, during normal operation, AUTO REFRESH cycles are issued in bursts (as opposed to being evenly distributed), a burst of 4,096 AUTO REFRESH cycles should be completed just prior to entering and just after exiting the self refresh mode. The period between the Auto Refresh command and the next command is specified by t RC.7.17. Power Down ModeThe Power Down mode is initiated by holding CKE low. All of the receiver circuits except CKE are gated off to reduce the power. The Power Down mode does not perform any refresh operations, therefore the device can not remain in Power Down mode longer than the Refresh period (t REF) of the device.The Power Down mode is exited by bringing CKE high. When CKE goes high, a No Operation Command is required on the next rising clock edge, depending on t CK. The input buffers need to be enabled with CKE held high for a period equal to t CKS (min) + t CK (min).7.18. No Operation CommandThe No Operation Command should be used in cases when the SDRAM is in a idle or a wait state to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.7.19. Deselect CommandThe Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when CS is brought high, the RAS, CAS, and WE signals become don’t cares.7.20. Clock Suspend ModeDuring normal access mode, CKE must be held high enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends any clocked operation that was currently being executed. There is a one clock delay between the registration of CKE low and the time at which the SDRAM operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.8. OPERATION MODEFully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 1 shows the truth table for the operation commands.Table 1 Truth Table (Note (1), (2))Notes:(1) v =valid x =Don’t care L =Low Level H =High Level(2) CKEn signal is input level when commands are provided.CKEn-1 signal is the input level one clock cycle before the command is issued.(3) These are state of bank designated by BS0, BS1 signals.(4) Device state is full page burst operation.(5) Power Down Mode can not be entered in the burst cycle.When this command asserts in the burst cycle, device state is clock suspend mode.9. ELECTRICAL CHARACTERISTICS9.1. Absolute Maximum RatingsRATINGUNIT PARAMETER SYMBOLInput/Output Voltage V IN, V OUT -0.3 ~ V DD +0.3 VPower Supply Voltage V DD, V DDQ-0.3 ~ 4.6 VOperating Temperature (-6/-75) T OPR0 ~ 70 °C°C85Operating Temperature (-6I) T OPR -40~°C150Storage Temperature T STG -55~Soldering Temperature (10s) T SOLDER 260 °CW Power Dissipation P D 1mA Short Circuit Output Current I OUT 50Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.9.2. Recommended DC Operating Conditions(Ta = 0 to 70°C for -6/-75, Ta= -40 to 85°C for -6I)UNIT PARAMETER SYMBOL MIN.MAX.TYP.Power Supply Voltage V DD 3.0 3.3 3.6 VPower Supply VoltageV DDQ 3.0 3.3 3.6 V(for I/O Buffer)V DD +0.3 VInput High Voltage V IH 2.0 -Input Low Voltage V IL -0.3 - 0.8 VNote: V IH(max) = V DD/ V DDQ+1.2V for pulse width < 5 nSV IL(min) = V SS/ V SSQ-1.2V for pulse width < 5 nS9.3. Capacitance(V DD= 3.3V, f = 1 MHz, Ta 25°C)Note: These parameters are periodically sampled and not 100% tested.9.4. DC Characteristics(VDD =3.3V± 0.3V, Ta = 0 to 70°C for-6/-75, Ta= -40 to 85°C for -6I)NOTESUNIT PARAMETER SYMBOL MIN.MAX.Input Leakage CurrentI I(L) -5 5 µA (0V ≤V IN≤ V DD, all other pins not under test = 0V)Output Leakage CurrentI O(L) -5 5 µA (Output disable , 0V ≤ V OUT≤ V DDQ)LVTTL Output ″H″ Level VoltageV OH 2.4 - V(I OUT = -2 mA )LVTTL Output ″L″ Level VoltageV OL - 0.4 V(I OUT = 2 mA )9.5. AC Characteristics and Operating Condition(VDD =3.3V ± 0.3V, Ta = 0 to 70°C for -6/-75, Ta= -40 to 85°C for -6I, Notes: 5, 6, 7, 8, 9, 10)-6/-6I -75PARAMETER SYM.MIN. MAX. MIN. MAX.UNIT NOTESRef/Active to Ref/Active Command Period t RC 60 65 Active to precharge Command Period t RAS 42 10000045 100000 nSActive to Read/Write Command Delay Timet RCD 18 20 Read/Write(a) to Read/Write(b) Command Periodt CCD 1 1 t CKPrecharge to Active Command Period t RP 18 20 Active(a) to Active(b) Command Period t RRD 12 15 nS CL* = 2 22 t CKWrite Recovery Time CL* = 3 t WR 22CL* = 2 101000101000CLK Cycle TimeCL* = 3t CK6 1000 7.5 1000CLK High Level widtht CH 2 2.5 9 CLK Low Level widtht CL 2 2.59CL* = 2 6 6 Access Time from CLKCL* = 3t AC 5 5.4 10 Output Data Hold Timet OH 3 3 10 Output Data High Impedance Time t HZ 3 6 3 7.5 8 Output Data Low Impedance Time t LZ 0 0 10 Power Down Mode Entry Time t SB 0 6 0 7.5Transition Time of CLK (Rise and Fall) t T 0.1 1 0.1 1 7 Data-in Set-up Time t DS 1.5 1.5 9 Data-in Hold Time t DH 1.0 1.0 9 Address Set-up Time t AS 1.5 1.5 9 Address Hold Time t AH 1.0 1.0 9 CKE Set-up Time t CKS 1.5 1.5 9 CKE Hold Time t CKH 1.0 1.0 9 Command Set-up Time t CMS 1.5 1.5 9 Command Hold Time t CMH 1.0 1.0nS9Refresh Timet REF 64 64 mS Mode register Set Cycle Time t RSC 12 15 nS Exit self refresh to ACTIVE commandt XSR72 75 nS*CL = CAS LatencyNotes:1. Operation exceeds “Absolute Maximum Ratings” may cause permanent damage to the devices.2. All voltages are referenced to V SS3. These parameters depend on the cycle rate and listed values are measured at a cycle rate with the minimum values of t CK and t RC .4. These parameters depend on the output loading conditions. Specified values are obtained with output open.5. Power up sequence is further described in the “Functional Description” section.6. AC Testing ConditionsPARAMETER CONDITIONSOutput Reference Level1.4VOutput LoadSee diagram belowInput Signal Levels (V IH /V IL ) 2.4V/0.4VTransition Time (t T : tr/tf) of Input Signal 1/1 nS Input Reference Level 1.4V7. Transition times are measured between V IH and V IL .8. t HZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output level.9. Assumed input transition Time (t T ) = 1nS.If tr & tf is longer than 1nS, transient time compensation should be considered, i.e., [(tr + tf)/2-1]nS should be added to the parameter(The t T maximum can’t be more than 10nS for low frequency application.)10. If clock rising time (t T ) is longer than 1nS, (t T /2-0.5)nS should be added to the parameter.10. TIMING WAVEFORMS 10.1. Command Input Timing10.2. Read Timing10.3. Control Timing of Input/Output Data10.4. Mode Register Set Cycle11. OPERATING TIMING EXAMPLE11.1. Interleaved Bank Read (Burst Length = 4, CAS Latency = 3)11.2. Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge)11.3. Interleaved Bank Read (Burst Length = 8, CAS Latency = 3)11.4. Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge)11.5. Interleaved Bank Write (Burst Length = 8)11.6. Interleaved Bank Write (Burst Length = 8, Auto-precharge)11.7. Page Mode Read (Burst Length = 4, CAS Latency = 3)11.8. Page Mode Read / Write (Burst Length = 8, CAS Latency = 3)11.9. Auto-precharge Read (Burst Length = 4, CAS Latency = 3)11.10. Auto-precharge Write (Burst Length = 4)11.11. Auto Refresh Cycle11.12. Self Refresh Cycle11.13. Burst Read and Single Write (Burst Length = 4, CAS Latency = 3)11.14. Power Down Mode11.15. Auto-precharge Timing (Read Cycle)11.17. Timing Chart of Read to Write Cycle11.18. Timing Chart of Write to Read Cycle11.19. Timing Chart of Burst Stop Cycle (Burst Stop Command)11.20. Timing Chart of Burst Stop Cycle (Precharge Command)11.21. CKE/DQM Input Timing (Write Cycle)11.22. CKE/DQM Input Timing (Read Cycle)12. PACKAGE SPECIFICATION12.1. TFBGA 90 Balls pitch=0.8mmPublication Release Date:Aug. 13,2007- 41 - Revision A07Publication Release Date: Aug. 13,2007- 42 - Revision A0713. REVISION HISTORYVERSION DATEPAGEDESCRIPTIONA01 Mar. 24, 2006 All Create new datasheet A02 Jul. 05, 2006 8 Burst Stop commandA03 Sep. 08, 2006 10 Exit Auto refresh to next command is specified by t RC A04 Sep. 27, 200615,16Modify Characteristics Notes 9 and add Notes 10 (t T ) A05 Apr. 12, 2007 15,32,34,41Add t XSR timing specification and package dimension ball openingA06 Jun. 21, 2007 3,13,14,15Add -6I gradeA07 Aug. 13, 200716Revise transient time t T AC test condition and calculate formula for compensation consideration in Notes 6, 9 of AC Characteristics and Operating ConditionImportant NoticeWinbond products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.。

NTE7208 集成电路常电流单输出LED驱动器说明书

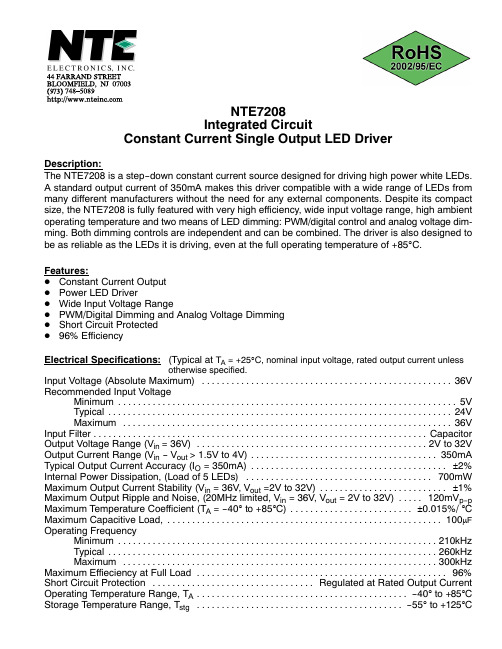

NTE7208Integrated CircuitConstant Current Single Output LED DriverDescription:The NTE7208 is a step-down constant current source designed for driving high power white LEDs.A standard output current of 350mA makes this driver compatible with a wide range of LEDs from many different manufacturers without the need for any external components. Despite its compact size, the NTE7208 is fully featured with very high efficiency, wide input voltage range, high ambient operating temperature and two means of LED dimming: PWM/digital control and analog voltage dim‐ming. Both dimming controls are independent and can be combined. The driver is also designed to be as reliable as the LEDs it is driving, even at the full operating temperature of +85°C.Features:D Constant Current OutputD Power LED DriverD Wide Input Voltage RangeD PWM/Digital Dimming and Analog Voltage DimmingD Short Circuit ProtectedD96% EfficiencyElectrical Specifications:(Typical at T A = +25°C, nominal input voltage, rated output current unlessotherwise specified.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input Voltage (Absolute Maximum)36V Recommended Input Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Minimum5V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Typical24V Maximum36V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Input Filter Capacitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Output Voltage Range (V in= 36V)2V to 32V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Output Current Range (V in - V out> 1.5V to 4V)350mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Typical Output Current Accuracy (I O = 350mA)±2%. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Internal Power Dissipation, (Load of 5 LEDs)700mW. . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Output Current Stability (V in = 36V, V out =2V to 32V)±1%. . . . . Maximum Output Ripple and Noise, (20MHz limited, V in = 36V, V out = 2V to 32V)120mV p-p. . . . . . . . . . . . . . . . . . . . . . . . .Maximum Temperature Coefficient (T A = -40° to +85°C)±0.015%/ °C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Capacitive Load,100μF Operating Frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Minimum210kHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Typical260kHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Maximum300kHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Effieciency at Full Load96%. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Short Circuit Protection Regulated at Rated Output Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Operating Temperature Range, T A-40° to +85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Storage Temperature Range, T stg-55° to +125°CElectrical Specifications (Cont'd):(Typical at T A = +25°C, nominal input voltage, rated output currentunless otherwise specified.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Case Tempeature, T C+100°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Thermal Impedance (Nature Convection)+55°C/W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Case Material Non Conductive Black Plastic Potting Material Epoxy (UL94-V0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Wave Soldering Profile (10 seconds)+235°C PWM Dimming and ON/OFF Control (Leave Open if Not Used):Remote ON/OFFDC/DC ON,Open or 0V < V r < 0.6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC/DC OFF (Standby)0.6 < V r < 2.9V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DC/DC OFF (Shutdown), 2.9 < V r < 6V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Remote Pin Drive Current (V r = 5V)1mA Maximum Quiescent Input Current in Shutdown Mode (V in = 36V, V r > 2.9V)200μA. . . . . . . . . . . .. . . . . . . Maximum PWM Frequency for Linear Operation (measured 10% to 90% Dimming)200Hz Analog Dimming Control (Leave Open if Not Used):. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Input Voltage Range0 to 15V Control Voltage Range Limits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Full On0.13V ± 50mV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Full Off 4.5V ± 50mV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Analog Pin Drive Current (V c = 5V)0.2mA Environmental:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Relative Humidity (See Note)5% to 95% RH, non-condensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Conducted Emissions EN55022, Class B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Radiated Emissions EN55022, Class B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ESD EN61000-4-2, Class A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Radiated Immunity EN61000-4-3, Class A Fast Transient EN61000-4-4, Class A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Conducted Immunity EN61000-4-6, Class A MTBF (RCD-24-0.70, Nominal V in, Full Load)+25°C605 x 103 hours . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Using MIL-HDBK 217F, +71°C516 x 103 hoursNote: Requires an input filter to meet EN55022 Class B conducted emissions, see below.。

ISIS7Professional元件库列表及中英文对照整理版

模拟芯片(Analog ICs)放大器(Amplifiers)比较器(Comparators)显示驱动器(Display Drivers)过滤器(Filters)数据选择器(Multiplexers)稳压器(Regulators)定时器(Timers)基准电压(V oltage Reference)杂类(Miscellananeous)电容(Capacitors)可动态显示充放电电容(Animated)音响专用轴线电容(Audio Grade Axial)轴线聚苯烯电容(Axial Lead Polypropene)轴线聚苯烯电容(Axial Lead Polystyrene)陶瓷圆片电容(Ceramic Disc)去耦片状电容(Decoupling Disc)普通电容(Generic)高温径线电容(High Temp Radial)高温径线电解电容(High Temperature Axial Electrolytic)金属化聚酯膜电容(Metallised Polyester Film)金属化聚烯电容(Metallised Polypropene)金属化聚烯膜电容(Metallised Polypropene Film)小型电解电容(Miniture Electrolytic)多层金属化聚酯膜电容(Multilayer Metallised Polyestern Film) 聚脂膜电容(Mylar Film)镍栅电容(Nickel Barrier)无极性电容(Non Polarised)聚脂层电容(Polyester Layer)径线电解电容(Radial Electrolytic)树脂蚀刻电容(Resin Dipped)钽珠电容(Tantalum Bead)可变电容(Variable)VX轴线电解电容(VX Axial Electolytic)连接器(Connectors)音频接口(Audio)D 型接口(D-Type)双排插座(DIL)插头(Header Blocks)PCB转接器(PCB Transfer)带线(Ribbon Cable)单排插座(SIL)连线端子(Terminal Blocks)杂类(Miscellananeous)数据转换器(Data Converter)模/数转换器(A/D converters)数/模转换器(D/A converters)采样保持器(Sample & Hold)温度传感器(Temperature Sensore) 调试工具(Debugging Tools)断点触发器(Breakpoint Triggers)逻辑探针(Logic Probes)逻辑激励源(Logic Stimuli)二极管(Diode)整流桥(Bridge Rectifiers)普通二极管(Generic)整流管(Rectifiers)肖特基二极管(Schottky)开关管(Switching)隧道二极管(Tunnel)变容二极管(Varicap)齐纳击穿二极管(Zener)ECL 10000系列(ECL 10000 Series) 各种常用集成电路机电(Electromechanical)各种直流和步进电机电感(Inductors)普通电感(Generic)贴片式电感(SMT Inductors)变压器(Transformers)拉普拉斯变换(Laplace Primitives) 一阶模型(1st Order)二阶模型(2st Order)控制器(Controllers)非线性模式(Non-Linear)算子(Operators)极点/零点(Poles/Zones)符号(Symbols)存储芯片(Memory Ics)动态数据存储器(Dynamic RAM) 电可擦除可编程存储器(EEPROM) 可擦除可编程存储器(EPROM)I2C总线存储器(I2C Memories) SPI总线存储器(SPI Memories)存储卡(Memory Cards)静态数据存储器(Static Memories) 微处理器芯片(Microprocess ICs) 6800 系列(6800 Family)8051 系列(8051 Family)ARM 系列(ARM Family)A VR 系列(A VR Family)Parallax 公司微处理器(BASIC Stamp Modules)HCF11 系列(HCF11 Family)PIC10 系列(PIC10 Family)PIC12 系列(PIC12 Family)PIC16 系列(PIC16 Family)PIC18 系列(PIC18 Family)Z80系列(Z80 Family)CPU 外设(Peripherals)杂项(Miscellaneous)含天线、ATA/IDE硬盘驱动模型、单节与多节电池、串行物理接口模型、晶振、动态与通用保险、模拟电压与流符号、交通信号灯建模源(Modelling Primitives)模拟(仿真分析)(Analogy-SPICE)数字(缓冲器与门电路)(Digital--Buffers&Gates)数字(杂类)(Digital--Miscellaneous)数字(组合电路)(Digital--Combinational)数字(时序电路)(Digital--Sequential)混合模式(Mixed Mode)可编程逻辑器件单元(PLD Elements)实时激励源(Realtime Actuators)实时指示器(Realtime Indictors)运算放大器(Operational Amplifiers)单路运放(Single)二路运放(Dual)三路运放(Triple)四路运放(Quad)八路运放(Octal)理想运放(Ideal)大量使用的运放(Macromodel)光电子类器件(Optoelectronics)七段数码管(7-Segment Displays)英文字符与数字符号液晶显示器(Alphanumeric LCDs)条形显示器(Bargraph Displays)点阵显示屏(Dot Matrix Display)图形液晶(Grphical LCDs)灯泡(Lamp)液晶控制器(LCD Controllers)液晶面板显示(LCD Panels Displays)发光二极管(LEDs)光耦元件(Optocouplers)串行液晶(Serial LCDs)可编程逻辑电路与现场可编程门阵列(PLD&FPGA)无子类电阻(Resistors)0.6W金属膜电阻(0.6W Metal Film)10W 绕线电阻(10W Wirewound)2W 金属膜电阻(2W Metal Film)3W 金属膜电阻(3W Metal Film)7W 金属膜电阻(7W Metal Film)通用电阻符号(Generic)高压电阻(High Voltage)负温度系数热敏电阻(NTC)排阻(Resisters Packs)滑动变阻器(Variable)可变电阻(Varistors)仿真源(Simulator Primitives)触发器(Flip-Flop)门电路(Gates)电源(Sources)扬声器与音响设备(Speaker&Sounders)无子分类开关与继电器(Switch&Relays)键盘(Keypads)普通继电器(Generic Relays)专用继电器(Specific Relays)按键与拨码(Switchs)开关器件(Switching Devices)双端交流开关元件(DIACs)普通开关元件(Generic)可控硅(SCRs)三端可控硅(TRIACs)热阴极电子管(Thermionic Valves)二极真空管(Diodes)三极真空管(Triodes)四极真空管(Tetrodes)五极真空管(Pentodes)转换器(Transducers)压力传感器(Pressures)温度传感器(Temperature)晶体管(Transistors)双极性晶体管(Bipolar)普通晶体管(Generic)绝缘栅场效应管(IGBY/Insulated Gate Bipolar Transistors 结型场效应晶体管(JFET)金属-氧化物半导体场效应晶体管(MOSFET)射频功率LDMOS晶体管(RF Power LDMOS)射频功率VDMOS晶体管(RF Power VDMOS)单结晶体管(Unijunction)CMOS 4000系列(CMOS 4000 seriesTTL 74系列(TTL 74 series)TTL 74增强型低功耗肖特基系列(TTL 74ALS Series) TTL 74增强型肖特基系列(TTL 74AS Series)TTL 74高速系列(TTL 74F Series)TTL 74HC系列/CMOS工作电平(TTL 74HC Series) TTL 74HCT系列/TTL工作电平(TTL 74HCT Series)TTL 74低功耗肖特基系列(TTL 74LS Series)TTL 74肖特基系列(TTL 74S Series)加法器(Adders)缓冲器/驱动器(Buffers&Drivers)比较器(Comparators)计数器(Counters)解码器(Decoders)编码器(Encoders)存储器(Memory)触发器/锁存器(Flip-Flop&Latches)分频器/定时器(Frequency Dividers & Timers)门电路/反相器(Gates&Inverters)数据选择器(Multiplexers)多谐振荡器(Multivibrators)振荡器(Oscillators)锁相环(Phrase-Locked-Loop,PLL)寄存器(Registers)信号开关(Signal Switches)收发器(Tranxceivers)杂类逻辑芯片(Misc.Logic)Proteus isis 的元件库中英对照Proteus 元件名称对照1元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG[size=+0]转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

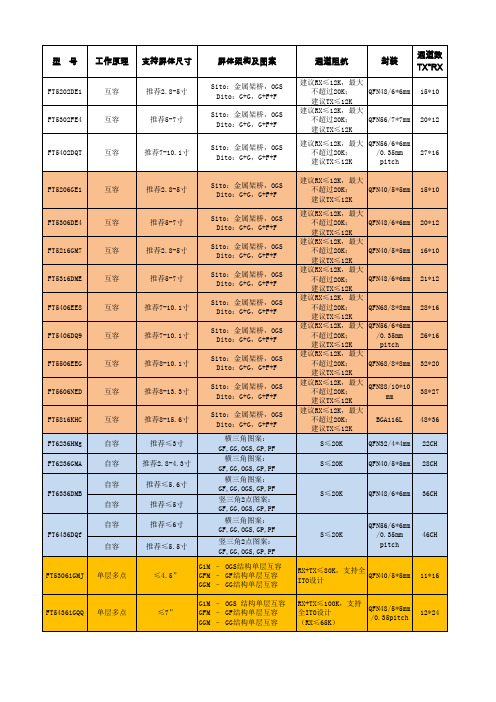

敦泰触摸IC参数对照表

20*12

FT5402DQT

互容

推荐7-10.1寸

27*16

FT5206GE1

互容

推荐2.8-5寸

Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F Sito:金属架桥,OGS Dito:G+G,G+F+F 横三角图案: GF,GG,OGS,GP,PF 横三角图案: GF,GG,OGS,GP,PF 横三角图案: GF,GG,OGS,GP,PF 竖三角2点图案: GF,GG,OGS,GP,PF 横三角图案: GF,GG,OGS,GP,PF 竖三角2点图案: GF,GG,OGS,GP,PF G1M – OGS结构单层互容 GFM – GF结构单层互容 GGM – GG结构单层互容 G1M – OGS 结构单层互容 GFM – GF结构单层互容 GGM – GG结构单层互容

工作电流:6mA 待机电流:4mA 睡眠电流:30uA

工作温度: -20~+85 储存温度: -55~+150 工作温度: -20~+85 储存温度: -55~+150

[实用参考]常用集成电路手册.doc

![[实用参考]常用集成电路手册.doc](https://img.taocdn.com/s3/m/830bbd67a5e9856a56126070.png)

AN5195B(4N01/5N01)(中放,解码,行场扫描小信号处理) (6)AN5199(3N10,5N10)(图像/伴音中放,解码,行场扫描小信号处理) (7)`AN5265伴音功放 (9)AN5274伴音功放 (9)AN5277-伴音功放 (9)AN5521场扫描输出电路 (10)AN5534场扫描电路 (10)AN5539场扫描输出电路 (10)AN5891—高音,低音,平衡,环绕处理电路 (11)AT24C04电可檫编程只读存储器 (11)AT24C08电可檫编程只读存储器 (11)CC3005CPU(5M10) (12)CTV222S(A机芯)微处理器 (12)DBL2044-波段切换 (13)DBL2044真值表输入控制 DBL2044真值表输出控制 (13)DDP3310B-视频解码 (14)DPTV-3D引脚功能 (14)TV和RGB接口部分 (15)DPTV-DG引脚功能 (16)显示接口(DAC&DDP)引脚功能 (17)拟支持接口引脚功能 (17)模拟输入接口(ADC)引脚功能 (17)俘获接口(TV&RGB)的引脚功能 (18)帧缓冲器记忆存储接口 (18)DPTV-IG引脚功能 (19)GAL16V8C——VGA同步切换处理 (22)HEF4052-电子切换开关 (22)HL4066-双向模拟电子开关 (22)IS42G32256-89-PQ存储器 (23)KA2107伴音处理器 (23)KA2500三基色视频放大电路 (24)KA5Q1265RF-电源IC (25)KA5Q1565RF-电源IC (25)KA7631-带复位功能电源IC (25)KS88C8424/C8432/P8432---CPU(微处理器) (25)L78MR05——5V三端稳压电路 (26)LA4285音频放大器 (27)LA75665—中放处理电路 (27)LA75665真值表 (28)LA7680(P机芯)—中放,解码,行场扫描小信号处理 (28)LA7830场输出电路 (29)LA7838场输出电路 (30)LA7840场输出电路 (30)LA7846场输出电路 (30)LA7910波段切换电路 (31)LA7954四选一电子开关 (31)LA86C3348A(P机芯)微处理器 (32)LM324运算放大器 (33)LM1269-为一块110MHz适合I2C总线控制的RGB视频放大系统 (33)LV1116-音频处理 (34)M37225ECSP-CPU (36)M37274(5M10机芯)微处理器 (37)M37280——微处理器 (37)M37281——微处理器 (38)M52797—(3T30机芯)总线控制AV开关 (39)MCU—(3S28)微处理器 (39)MCU(Z233)—微处理器 (40)MN152810(4N机芯)微处理器 (41)MN181768(5N10机芯)微处理器 (42)MN18P73284DP—微处理器 (43)MN3868彩色基带延迟线 (44)MTV880微处理器 (45)MSM518222引脚功能 (45)MSM5412222引脚功能 (46)MSP3410-丽音解码(电阻单位是KΩ,电压单位是V) (46)NJM2192AL-WOW高级音效处理(电阻单位KΩ,电压单位V) (47)NJM2700-WOW高级音效处理(以6M20为参考) (48)NN5199解码 (49)NV320P数字视频处理电路 (50)OM8361(4P01,5P01机芯)解码 (52)OM8838—视频解码 (53)OM8839—视频解码 (54)P87C766 (56)PCA84C440(CPU) (57)PCF8594—存储器 (58)PT2213—遥控发射IC (58)Q83652(5D01机芯)微处理器 (59)SAA4951—存储控制器 (60)SAA4961P/N制梳状滤波器 (61)SAA7158引脚功能表 (62)SAA7282—丽音解码 (63)SAA7283ZP—丽音解码 (64)SDA9187—画中画A/D转换电路 (65)SDA9189画中画处理电路 (66)SDA9220图像数字处理 (66)SDA存储器 (67)SDA9280显示处理器 (67)SDA9290图像处理电路 (68)SDA9361可编程扫描控制器 (68)SDA9362行场扫描处理 (69)SDA9400—P,U,V数字处理电路 (70)ST24C16-存储器 (70)ST63156(4S01机芯)CPU (71)STV5112视放电路 (72)ST63T87微处理器 (72)ST6388(5S01机芯)微处理器 (73)ST92196----微处理器 (74)STR-S6309电源厚膜电路 (75)STR-S6709电源厚膜电路 (76)STR-F6653 (76)STR-F6656的引脚功能及其在路参数 (76)STR-F6656时绝对最大额定值 (77)STV2116(4S01,5S01机芯)解码 (77)STV2180彩色基带延迟线 (78)STV2246中放,解码,行,场扫描小信号处理 (78)STV2248中放,解码,行,场扫描小信号处理 (80)STV5111视放 (81)STV6888-行场扫描小信号处理 (82)STV8203伴音解调器引脚功能与数据 (82)STV8223中放 (83)STV9306-带I2C总线控制的场扫描及枕校处理电路 (84)STV9379-场扫描处理电路 (84)TA1218-带I2C总线控制的电子切换开关 (84)TA1219音频视频电子开关 (85)TA1275Z管脚功能 (86)TA1316-RGB及同步处理(以6M20为参考) (87)TA1343-音调、音量调节处理(以6M20为参考) (88)TA8173环绕声处理器 (88)TA8200AH的引脚功能及维修数据 (89)TA8256引脚功能 (89)TA8403K场扫描输出集成块 (90)TA8427场扫描输出集成块 (90)TA8659(A机芯)视频色度扫描信号处理电路 (90)TA8776N环绕声处理电路 (92)TA8859场偏转处理电路 (93)TB1238AN(T机芯)解码 (93)TB1240AN解码引脚功能及数据表 (95)TC4052(2×4)多路开关 (96)TC74HC157多路开关 (97)TC9090接地脚引脚说明 (97)TDA1905音频功率放大器 (98)TDA20PP引脚功能及电压对照表 (98)TA8200AH引脚功能及电压对照表 (98)TDA2030引脚功能 (99)TDA2461伴音中放 (99)TDA2549中频放大,检波集成电路 (99)TDA2616音频放大器 (100)TDA3653场扫描和场输出集成块 (100)TDA3857准分离伴音处理器 (101)TDA4555 (101)TDA4661 (102)TDA4665基带彩色延迟线 (102)TDA4670亮色瞬态补偿电路 (102)TDA4780引脚功能与维修数据表 (103)TDA4863A引脚功能 (104)TDA6103Q视放IC (104)TDA6107Q三路视频输出放大器 (104)TDA6108Q引脚功能及维修数据表 (105)TDA6111视频放输出大器 (105)TDA7057伴音功放处理电路 (105)TDA7263A引脚功能 (106)TDA7269A引脚功能: (106)TDA7439伴音平衡处理器 (106)TDA7496引脚功能 (107)TDA8139引脚功能 (108)TDA8174场扫描输出集成电路 (108)TDA8214行场处理集成电路 (108)TDA8219解码 (109)TDA8222引脚功能及工作电压,对地电阻 (110)TDA8224中放 (110)TDA8310画中画(PAL/NTSC)彩色处理器 (111)TDA8351引脚功能与维修数据 (112)TDA8354Q引脚功能及维修数据参考说明 (113)TDA8362中频,视频,色度扫描小信号处理 (113)TDA8395PSECAM解调 (114)TDA8425立体声音频处理器 (115)TDA8540引脚功能表 (115)TDA8707引脚功能 (116)TDA8732引脚功能及参考电压 (116)TDA8755引脚功能表 (117)TDA9141/43(5D01机芯)解码 (118)TDA9151地各引脚的功能及维修数据 (118)TDA9177引脚功能 (119)TDA9302各脚功能 (120)TDA9370的引脚功能 (120)TDA9801为伴音中频处理IC其引脚功能如下: (122)TDA9808K图像/伴音中频信号处理集成电路 (122)TDA9859引脚及功能 (123)TDA9860音频处理电路引脚功能及数据 (123)TDA9875为一高保真丽音解码集成电路 (124)TEA20PP视频开关 (125)TEA5101视频放大器 (125)TEA6415C引脚功能 (125)TEA5114A-三基色开关 (126)TL082双运放 (126)TLC2932-锁相环 (127)TMPA8803CSN内部接口电路及终端信号 (127)UC3842-DC/DC变换(以6M20为参考) (129)VCT3803A引脚功能 (129)VPC3210-视频处理电路 (131)VPC3215引脚功能——视频处理(PC数字处理) (132)VPG3226引脚功能解码 (133)47-00001-42或Z9022306(5P03)微处理器 (134)AN5071波段开关(4N01机芯)脚号名称电压(V)1 BU输出 02 VL输出03 BAND0 0.24 BAND1 0.25 GND 06 电源31.77 BH出98 空09 电源9AN5195B(4N01/5N01)(中放,解码,行场扫描小信号处理)脚号有信号电压(V)正向对地电阻(KΩ)反向对地电阻(KΩ)引脚功能1 4.2 10 13 R箝位2 4.2 10 13 G箝位3 4.2 10 12 B箝位4 2.6 10 12 消色识别滤波5 3.5 10 13 彩色制式识别输出6 2.4 10 13 APC滤波7 2.6 10 13 外接4.43MHz晶振8 2.8 10 13 外接3.58MHz晶振9 4 10 13 黑电平延伸控制10 0 0.4 0.4 字符消隐输入11 2.6 10 15 字符R输入12 2.6 10 15 字符G输入13 2.6 10 15 字符B输入14 9 0.65 0.65 9V电源15 3.8 1 1.1 R输出16 3.8 1 1.1 G输出17 3.8 1 1.1 B输出18 5.8 10 12 行同步检测输出19 0 0 0 地20 3 10 14 自动亮度控制21 4.4 7.5 14 数据总线22 4.5 7.5 14 时钟总线23 5 0.7 0.7 5VVcc3-124 2.6 10 13 中频输入25 2.6 10 13 中频输入26 0 0 0 中频地27 3.4 5.5 5.5 高放AGC输出28 3.4 2.5 2.7 音频输出29 4.6 10 13 音频去加重30 4.2 10 13 中放AFT输出31 1.6 10 14 外部视频输入32 2.6 10 15 伴音中频滤波33 5.5 4.5 4.5 4.5MHzSIF输入34 3 10 14 外接音频输入35 2.6 10 14 6.5MHzSIF输入36 2.6 10 14 6.0MHzSIF输入37 2.2 10 14 中放AGC38 1.9 10 14 第一视频输入39 3 10 14 伴音中频APC滤波40 1.8 10 14 第二视频41 2.6 10 11 视频检波输出42 2.6 10 14 APC滤波43 3.7 10 13 19MHz中频振荡44 4.7 10 12 视频输出45 3.8 10 14 亮度信号输入46 1.8 10 14 行同步信号输入47 5 0.8 0.8 5V电源48 4.2 6 6 色度信号输入49 0 0 0 地50 0.3 3 3 行脉冲输入51 6.2 7 18 行振荡电源52 2.4 10 50 行AFC滤波53 4 10 49 行AFC1滤波54 2.4 8.5 9 500Hz振荡55 0 7 7 G射线保护56 1.2 3.5 3.5 行激励脉冲输出57 2 10 15 场同步分离58 3.8 7.5 12 场脉冲输出59 1.2 10 15 SECAM控制输出60 2.2 10 15 -(B-P)输出61 2.2 10 15 -(R-P)输出62 1 10 13 沙堡脉冲输出63 3.4 10 15 -(B-P)输入64 3.4 10 15 -(R-P)输入AN5199(3N10,5N10)(图像/伴音中放,解码,行场扫描小信号处理)脚号电压(V)正向电阻(KΩ)反向电阻(KΩ)引脚功能1 0 6 9.5 测试脚2 4.3 7 11 时钟线3 4.8 11 15 色度APC滤波脚4 3 11 15 自动亮度控制脚5 0.2 2 2 字符消隐脚6 1 11 16 R字符输入7 1 11 16 G字符输入8 1 11 16 B字符输入9 8.6 0.5 0.7 Vcc19V供电脚10 2.2 11 12 R信号输出11 2.4 11 12 G信号输出12 2.4 11 12 B信号输出13 0 0 0 接地脚14 2.6 11 15 外接4.43MHz晶振15 0 0 0 SECAM制PLL脚16 8.6 0.7 0.7 9V供电脚17 0 0 0 SECAM钟形滤波18 2.6 11 14 图像中频输入19 2.6 11 14 图像中频输入20 0 0 0 VIF和SIF地21 2.4 10 12 准分离SIF输入22 1.6 10 14 射频AGC输出23 3.4 11 14 AFT输出24 2.5 11 15 外部视频/C信号入25 1.4 11 15 中频AGC滤波26 0 11 15 VIFAPC滤波27 3.6 11 16 准分离SIF检波出28 2.6 12 15 伴音中频输入29 3 12 15 外部伴音输入30 4 12 16 音频输出31 3.6 12 15 黑电平检测滤波脚32 4 12 12 去加重滤波/音频监听输出33 8.6 0.7 0.7 色度处理电路供电34 3.6 12 16 图像检波输出35 5 60 36 5V供电脚36 3.6 12 14 视频输出37 0 12 16 测试38 3.6 12 16 亮度/场同步信号输入39 3.7 12 16 行同步信号输入脚40 2.4 12 15 外接3.58晶振41 6 8 16 6.3V行供电脚42 1 1.7 1.7 行脉冲信号输出43 3.4 12 22 AFC1滤波脚44 2.2 12 15 音频去耦合滤波脚45 1.2 12 15 场锯齿波形成电容46 3 12 15 场同步触发脉冲出47 2.2 12 15 场扫描AGC脚48 5 5.5 10 5V供电49 0.1 7 7 SCP/G射线保护50 0 0 0 Vss供电脚51 0.6 8 14 数据线52 0.3 2 2 场逆程输入脚`AN5265伴音功放引脚名称电压功能1 Vcc1 13 电源12 IN 6 输入3 MUTE 0 静音(高电平有效)4 VOL 12 音量5 FILTER 9.6 滤波6 FEED 10 反馈7 GND 0 地8 OUT 10 输出9 Vcc2 20 电源2AN5274伴音功放脚号有信号电压(V)正向电阻(KΩ)反向电阻(KΩ)引脚功能1 0 12 14 静音控制脚2 6 12 声道1输入脚3 1.2 12 70 音量控制脚4 10 8 35 空脚5 6 12 80 声道2输入脚6 14 10 24 纹波滤波脚7 9 10 48 声道2输出脚8 9 12 14 声道2负反馈脚9 0 0 0 接地脚10 18 7 24 供电脚11 9 12 15 声道1负反馈12 8.2 10 47 声道1输出AN5277-伴音功放序号电压(V)功能说明对地电阻(KΩ)红笔接地黑笔接地1 -空脚+∞+∞2 0 L声道输入10.0 10.83 24.3 外接滤波端口9.0 15.54 0 地0 05 0 R声道输入10.0 10.86 -空脚+∞+∞7 12.5 R声道输出7.5 20.58 3.4 外接滤波端口 6.6 7.99 0 地0 010 25.0 电源 4.6 20.511 12.1 待机控制9.0 60.012 12.5 L声道输出7.5 20.5AN5521场扫描输出电路脚号电压(V)正向电阻(KΩ)反向电阻(KΩ)引脚功能1 0 0 0 地2 14 2 2 场输出3 27 7 11 场输出电源4 0.8 1.7 1.7 场脉冲输入5 -0.2 56 回扫启动脉冲输入6 1 10 10 泵电源输出7 27 4 5.5 电源AN5534场扫描电路引脚名称电压(V)功能1 Vcc1 8.4 电源12 TRI.IN 1.5 触发输入3 V.SIZE 2.9 场幅控制4 50/60Hz 0 50/60Hz场幅调整5 RAMP 4.8 锯齿波形成6 NFB 4.6 交直流负反馈7 Vcc2 26 电源28 FUMP 1.4 泵电源9 GND 0 地10 V.OUT 13 场扫描输出11 Vcc3 28 电源312 OSC.PROT 1.2 去耦AN5539场扫描输出电路脚号电压(V)正向电阻(KΩ)反向电阻(KΩ)引脚功能1 0 0 0 接地脚2 12 8 30 场激励输出脚3 24 9 50 场输出供电脚4 2.4 3 2.5 正激励信号输入5 2.4 10 12 负激励信号输入6 24 6 28 供电脚7 1 11 70 泵电源供电脚AN5891—高音,低音,平衡,环绕处理电路脚号名称引脚功能脚号名称引脚功能1 PF1 相位滤波1 13 SCL 时钟2 AGC AGC电平检测14 SDA 数据3 LIN 左声道输入15 ROUT 右声道输出4 RF2 相位滤波2 16 TD 高音D/A转换5 PF3 相位滤波3 17 BLD 平衡D/A转换6 PF4 相位滤波4 18 RT 右高音调节7 GND 地19 RB 右低音调节8 LT 左高音变调节20 BB 低音增益调节9 LB 左低音调节21 VREF 1/2Vcc10 BD 低音D/A转换22 RIN 右声输入11 VD 音量D/A转换23 Vcc Vcc电源12 LOUT 左声道输出24 MODE 模式控制AT24C04电可檫编程只读存储器脚号电压(V)红笔测(KΩ)黑笔测(KΩ)引脚功能1 5 8.5 14 地址线02 0 0 0 地址线13 0 0 0 地址线24 0 0 0 地5 2.7 6.2 15 串行数据入/出6 2.9 6.2 15 串行时钟7 0 0 0 写保护8 5 5.5 8 电源AT24C08电可檫编程只读存储器脚号名称功能直流电压(V)1 W 写一保护输入02 NC 空脚03 A2 地址输入2 04 Vss 地05 SDA I2C总线串行数据入/出 4.9摆动6 SCL I2C总线串行时钟入 4.9摆动7 PRE 程序时间控制出08 Vcc 供电 5CC3005CPU(5M10)引脚功能引脚功能引脚功能1 P/C信号检测 20 未用39 供电5V2 遥控信号输入21 接地40-42 地3-4 未用22 5V 43 地5 待机控制端23-27 未用44 S端子检测6 消磁电路控制28 行同步45 P/N控制7-9 未用29 场保护信号46 地10 复位信号输出30-32 未用47 未用11-14 未用33 SDA 48 静音脚15 地34 SCL 49 地16 键控输入35 复位50 待机指示17-18 未用26-37 12MHz晶振51 开机指示19 AFC输出38 地52 开机控制CTV222S(A机芯)微处理器引脚电压(V)正向电阻(KΩ)反向电阻(KΩ)引脚功能1 1.8可变7 9.5 调谐电压VT2 0 7 12 音量控制3 1.6 7 11 亮度控制4 1.6 7 13 色度控制5 3.67 12 对比度控制6 2.6 6.5 13 平衡控制7 0 7 13 VHF-H频段控制8 3 7 13 UHF频段控制9 2.4 4.5 4.5 AGC信号输入端10 4.6 7 14 VHF-L频段控制11 0/5 7 13 S端子控制12 4/0 7 14 A V/TV选择开关13~19 4.6 11 14 键盘输入端20 4.6 11 14 系统模式选择输出21 0 0 0 地22 0 7.5 9.5 R输出23 0 7 9.5 G输出24 0 7 9.5 B输出25 0 7 13 消隐信号输出26 0 10 15 行逆程脉冲输入27 0.8 10 16 场逆程脉冲输入28~29 4.8 10.5 11 字符振荡30 0 0 0 地31 1 11 30 10MHz晶振32 2 11 15 10MHz晶振33 4.8/0 9.5 12 复位34 4.8 9 11 识别信号输入35 4.4 10 16 遥控信号输入36 0/5 7 12 环绕声控制37~38 0 0 0 地39 0 5.5 7.5 数据线40 5 5.5 7.5 时钟线41 0/5 7 12 开/关机控制42 5 4 4.5 电源DBL2044-波段切换脚号正向对地电阻(KΩ)反向对地电阻(KΩ)功能1 +∞10 BL出2 2.2 2.2 BU出3 16 12 BAND0控制4 16 12 BAND1控制5 0 0 接地6 6.5 18 偏置7 2.5 2.5 BH出8 1 1 空9 0.5 0.5 电源DBL2044真值表输入控制DBL2044真值表输出控制3脚 4脚 1脚 2脚 7脚L L H L LL H L L HH L L H LDDP3310B-视频解码引脚功能引脚功能引脚功能1 供电24 红色输出47 倍频以后的色度信号输入2 地25 绿色输出483 VGA场同步入26 蓝色输出494 读记数器复位27 接地505 读启动信号28 供电51 数字电路供电6 写启动信号29 外接电容到地52 接地7 写记数器复位30 字符消隐输入53 系统时钟入8 行驱动输出31 字符红色输入54 倍频以后的亮度信号输入9 行消隐信号入32 字符绿色输入5510 安全模式33 字符蓝色输入5611 场保护输入34 VGA消隐输入5712-14 接地35 VGA红色输入5815 接高电平36 VGA绿色输入5916 接高电平37 VGA蓝色输入6017 暗平衡检测入38 接地6118 接地39 复位脚(低)62 时钟输入19 场正激励输出40 D/A转换控制63 行同步信号20 场负激励输出41 外接电阻到地64 场同步信号21 场抛物波输出42-46 接地65-56 外接5M晶振22 RGB箝位67 SDA23 扫描速度调制68 SCLDPTV-3D引脚功能序号类型标识释义CPU主接口部分165-172 I/O AD[T:O] 多路地址和数据线4 I ADDRESS IC总线地址选择脚5 I RESET# 系统复位6 I PS 外部CPU出入使能端175 I ALE 地址寄存器使能端176 I WR# CPU写177 I RD# CPU读178 I/O SD IC数据线179 I SC IC时钟线180 I/O INT 中断173 I VSS 数字地174 I VDD 数字电源模拟支持接口部分163 AI GTLI 时钟输入164 AI/O GTLO 时钟输出158 AI MLF 记忆时钟环路低通滤波161 AI VLF 视频时钟环路低通滤波157 AI A VDD1 记忆时钟模拟供电159 AI A VSS1 记忆时钟模拟地160 AI A VSS2 视频时钟模拟地162 AI A VDD2 视频时钟模拟供电模拟输入接口部分183 AI CVBS1 复合视频输入1184 AI CVBS2 复合视频输入2185 AI CVBS3 复合视频/S端子亮度信号输入186 AI CVBS4 复合视频4/P分量输入188 AI/O CVBS-OUT1 复合视频输出1189 AI/O CVBS-OUT2 复合视频输出2196 AI C S端子C输入197 AI Cr Cr分量输入207 AI Cb Cb分量输入201 AI RB1 10Bit分量/Luma底电压基准202 AI RT1 10Bit分量/Luma顶电压基准203 AI RT2 10Bit分量/Chroma顶电压基准204 AI RB2 10Bit分量/Chroma底电压基准208、198、187 AI CCLP[3:1] 接模拟箝位误差电压存储电容181、190、194、199、205 AI A VDDA 模拟电源182、191、195、200、206 AI A VSSA 模拟地192 I VDD-ADC 模拟电源193 I VSS 模拟地TV和RGB接口部分1 I V5SF 5V基准电压2 I TEST 预留测试脚3 I/O INT2/TESTPCLK 第二/CPU中断7~14 I/O CAPD[23:16]RGB RGB底位15-22 I/O CAPD[15:8]RGB RGB高位或副正面38 I/O CLKPIP TV副画面时钟39 I/O HSPNCPIP PV行同步或副画面HDE40 I/O VHPNCPIP TV场同步或副画面VDE41 I/O CLKRGB RGB时钟42 I/O HSPNCRGB RGB行同步或HDE43 I/O VSPNCRGB RGB场同步或VDE44-51 I/O CAPD[7:0]RGB RGB高位23 I VDD 数字电源24 I VSS 数字地显示接口部分26 AO VM VM控制D/A变换器27 AO R 红基色D/A变换器28 AO G 绿基色D/A变换器29 AO B 蓝基色D/A变换器31 AI IRSET D/A变换电源偏置34 TO HSPNC 偏转处理行同步信号35 TO VSPNC 偏转处理场同步信号36 I/O HFLB 保护行逆程脉冲输入37 I/O VPROT 场保护/箝位32 AI A VDD 模拟电源25、30、33 AI A VSS 模拟地帧缓冲记忆接口部分113-112109-102 O MAI[9:0] 帧缓冲存储地址154-142、139-127 IO BA 64Bit帧缓冲存储数据124-119、89-8279-68、65-5499 TO RAS# RAS#信号100 TO CAS# CAS3信号101 TO WE# 写使能98 TO CSI# CSI信号97 TO CSO# CSO信号96 TO MCLK SGRAMSDRAM时钟信号118-115、90-93 T O DQM[7:0] 读写使能52、66、80、94、110 I VDD 数字电源125、140、15653、67、81、95、111 I VSS 数字地126、141、155114 I/O BA SGRAMSDRAM槽地址选择DPTV-DG引脚功能I=DigitalInputO=DigitalOutputAG=AnalogPinPWR=Power(Input)GND=Ground(Input)TG=PinhasTri-statecharacteristicsCPU主接口引脚功能引脚标识类型功能4 ADDRSEL I I2C地址选择引脚。

Leshan Radio Company LBC807型号一般目的调制晶体管说明书

1General Purpose TransistorsLBC807-16LT1G LBC807-25LT1G LBC807-40LT1GSOT–231. FR–5 = 1.0 x 0.75 x 0.062 in.2. Alumina = 0.4 x 0.3 x 0.024 in. 99.5% alumina.PNP SiliconFEATUREƽCollector current capability I C =-500 mA.ƽCollector-emitter voltage V CEO (max) = -45 V.ƽGeneral purpose switching and amplification.ƽPNP complement: LBC807 Series.ƽDEVICE MARKING AND ORDERING INFORMATIONDeviceMarkingShipping LBC807-16LT1G 5A13000/Tape&Reel LBC807-16LT3G5A110000/Tape&Reel LBC807-25LT1G 5B13000/Tape&Reel LBC807-25LT3G5B110000/Tape&Reel LBC807-40LT1G 5C13000/Tape&Reel LBC807-40LT3G5C110000/Tape&ReelMAXIMUM RATINGSRatingSymbol Value Unit Collector–Emitter Voltage V CEO –45V Collector–Base Voltage V CBO –50V Emitter–Base VoltageVEBO–5.0V Collector Current — ContinuousI C–500mAdcTHERMAL CHARACTERISTICSCharacteristicSymbol MaxUnitTotal Device Dissipation FR– 5 Board, (1)P DT A = 25°C225mW Derate above 25°C1.8mW/°C Thermal Resistance, Junction to Ambient R θJA 556°C/WT otal Device DissipationP DAlumina Substrate, (2) T A = 25°C 300mW Derate above 25°C2.4mW/°C Thermal Resistance, Junction to Ambient R θJA 417°C/W Junction and Storage T emperatureT J , T stg–55 to +150°CEMITTER1We declare that the material of product compliance with RoHS requirements.23LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GELECTRICAL CHARACTERISTICS(T A= 25°C unless otherwise noted.)Characteristic Symbol Min Typ Max UnitOFF CHARACTERISTICSCollector–Emitter Breakdown Voltage(I C= –10 mA)V(BR)CEO–45——VCollector–Emitter Breakdown Voltage(V EB= 0, I C = –10µA)V(BR)CES–50——VEmitter–Base Breakdown Voltage(I E= –1.0µA)V(BR)EBO–5.0——VCollector Cutoff Current I CBO(V CB= –20 V)——–100nA(V CB= –20 V, T J= 150°C)——–5.0µA ELECTRICAL CHARACTERISTICS(T A= 25°C unless otherwise noted)Characteristic Symbol Min Typ Max UnitON CHARACTERISTICSDC Current Gain h FE—(I C= –100 mA, V CE= –1.0 V) LBC807–16100—250LBC807–25160—400LBC807–40250—600(I C= –500 mA, V CE= –1.0 V) 40——Collector–Emitter Saturation VoltageV CE(sat)——–0.7 V(I C = –500 mA, I B = –50 mA)Base–Emitter On VoltageV BE(on) — — –1.2 V(I C = –500 mA, V CE= –1.0 V)SMALL–SIGNAL CHARACTERISTICSCurrent–Gain — Bandwidth Productf T100— — MHz(I C = –10 mA, V CE = –5.0 V dc, f = 100 MHz)Output Capacitance C—10—pFobo(V CB = –10 V, f = 1.0 MHz)LESHAN RADIO COMPANY, LTD.LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS −LBC807−16LT1GFigure 1. DC Current Gain vs. CollectorCurrentFigure 2. Collector Emitter Saturation Voltagevs. Collector CurrentI C , COLLECTOR CURRENT (A)I C , COLLECTOR CURRENT (A)Figure 3. Base Emitter Saturation Voltage vs.Collector Current Figure 4. Base Emitter Voltage vs. CollectorCurrentI C , COLLECTOR CURRENT (A)I C , COLLECTOR CURRENT (A)h F E , D C C U R R E N T G A I NV C E (s a t ), C O L L E C T O R −E M I T T E RS A T U R A T I O N V O L T A G E (V )V B E (s a t ), B A S E −E M I T T E R S A T U R A T I O N V O L T A G E (V )V B E (o n ), B A S E −E M I T T E R V O L T A G E (V )LESHAN RADIO COMPANY, LTD.LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS − LBC807−16LT1GI B , BASE CURRENT (mA)Figure 5. Saturation Region100101.0V R , REVERSE VOLTAGE (VOLTS)Figure 6. Temperature CoefficientsIC , COLLECTOR CURRENTFigure 7. CapacitancesV C E , C O L L E C T O R -E M I T T E R V O L T A G E (V O L T S )V , T E M P E R A T U R E C O E F F I C I E N T S (m V /C )°θC , C A P A C I T A N C E (p F )LESHAN RADIO COMPANY, LTD.LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS − LBC807−25LT1GFigure 8. DC Current Gain vs. CollectorCurrentFigure 9. Collector Emitter Saturation Voltagevs. Collector CurrentI C , COLLECTOR CURRENT (A)I C , COLLECTOR CURRENT (A)100200300400500Figure 10. Base Emitter Saturation Voltage vs.Collector CurrentFigure 11. Base Emitter Voltage vs. CollectorCurrentI C , COLLECTOR CURRENT (A)I C , COLLECTOR CURRENT (A)0.20.30.50.60.70.81.01.1h F E , D C C U R R E N T G A I NV C E (s a t ), C O L L E C T O R −E M I T T E R S A T U R A T I O N V O L T A G E (V )V B E (s a t ), B A S E −E M I T T E R S A T U R A T I O N V O L T A G E (V )V B E (o n ), B A S E −E M I T T E R V O L T A G E (V )0.40.9Figure 12. Current Gain Bandwidth Productvs. Collector CurrentI C , COLLECTOR CURRENT (A)f T , C U R R E N T −G A I N −B A N D W I D T H P R O D U C T (M H z )LESHAN RADIO COMPANY, LTD.LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS − LBC807−25LT1GI B , BASE CURRENT (mA)Figure 13. Saturation Region100101.0V R , REVERSE VOLTAGE (VOLTS)Figure 14. Temperature CoefficientsI C , COLLECTOR CURRENTFigure 15. CapacitancesV C E , C O L L E C T O R -E M I T T E R V O L T A G E (V O L T S )V , T E M P E R A T U R E C O E F F I C I E N T S (m V /C )°θC , C A P A C I T A N C E (p F )LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS − LBC807−40LT1GFigure 16. DC Current Gain vs. CollectorCurrentFigure 17. Collector Emitter Saturation Voltagevs. Collector CurrentI C , COLLECTOR CURRENT (A)I C , COLLECTOR CURRENT (A)Figure 18. Base Emitter Saturation Voltage vs.Collector CurrentFigure 19. Base Emitter Voltage vs. CollectorCurrentI C , COLLECTOR CURRENT (A)I C , COLLECTOR CURRENT (A)h F E , D C C U R R E N T G A I NV C E (s a t ), C O L L E C T O R −E M I T T E R S A T U R A T I O N V O L T A G E (V )V B E (s a t ), B A S E −E M I T T E R S A T U R A T I O N V O L T A G E (V )V B E (o n ), B A S E −E M I T T E R V O L T A G E (V )Figure 20. Current Gain Bandwidth Productvs. Collector CurrentI C , COLLECTOR CURRENT (A)f T , C U R R E N T −G A I N −B A N D W I D T H P R O D U C T (M H z )LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS − LBC807−40LT1GI B , BASE CURRENT (mA)Figure 21. Saturation RegionV R , REVERSE VOLTAGE (VOLTS)Figure 22. Temperature Coefficients +1.0I C , COLLECTOR CURRENTFigure 23. Capacitances-2.0-1.0V C E , C O L L E C T O R -E M I T T E R V O L T A G E (V O L T S )V , T E M P E R A T U R E C O E F F I C I E N T S (m V /C )°θC , C A P A C I T A N C E (p F )-1.0-0.8-0.6-0.4-0.2LESHAN RADIO COMPANY, LTD.LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1GTYPICAL CHARACTERISTICS −LBC807−16LT1G, LBC807−25LT1G, LBC807−40LT1GFigure 24. Safe Operating AreaV CE , COLLECTOR EMITTER VOLTAGE (V)I C , C O L L E C T O R C U R R E N T (A )LESHAN RADIO COMPANY, LTD.NOTES:1. DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2. CONTROLLING DIMENSION: INCH.INCHES MILLIMETERSDIM MIN MAX MIN MAX A 0.11020.1197 2.80 3.04B 0.04720.0551 1.20 1.40C 0.03500.04400.89 1.11D 0.01500.02000.370.50G 0.07010.0807 1.78 2.04H 0.00050.00400.0130.100J 0.00340.00700.0850.177K 0.01400.02850.350.69L 0.03500.04010.89 1.02S 0.08300.1039 2.10 2.64V0.01770.02360.450.60SOT-23LBC807-16LT1G,LBC807-25LT1G,LBC807-40LT1G。

L6562中文资料_数据手册_参数

7.5 Comparison between the L6562A and the L6562 . . . . . . . . . . . . . . . . . . 17

8

Application examples and ideas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

doubles as an ON/OFF control iror amplifier. A compensation network is placed between this

2

COMP pin and INV to achieve stability of the voltage control loop and ensure high

August 2007

Package DIP-8 SO-8 SO-8

Rev 3

Packaging Tube Tube

Tape & Reel

1/26

26

Contents

Contents

L6562A

1

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

L6562A

Transition-mode PFC controller

Features

■ Proprietary multiplier design for minimum THD ■ Very accurate adjustable output overvoltage

L6202中文资料

ing speeds. All the logic inputs are TTL, CMOS and µC compatible. Each channel (half-bridge) of the device is controlled by a separate logic input, while a common enable controls both channels.

Boostrap Peak Voltage

Total Power Dissipation: Tpins = 90°C for L6201

for L6202 Tcase = 90°C for L6201PS/L6203 Tamb = 70°C for L6201 (Note 2)

for L6202 (Note 2)

VIN, VEN = L VIN, VEN = H

– 0.3

0.8

V

2

7

V

–10

µA

30

BLOCK DIAGRAM

MULTIPOWER BCD TECHNOLOGY

Powerdip 12+3+3

SO20 (12+4+4)

Multiwatt11

PowerSO20

ORDERING NUMBERS: L6201 (SO20) L6201PS (PowerSO20) L6202 (Powerdip18) L6203 (Multiwatt)

Device

L6201PS L6202

16

1

2

17

2

3 2,3,9,12, 3 18,19

4,5

–

4

–

1, 10

5

L6201,L6202,L6203,L297,L298中文资料

独的DMOS场效应晶体管,另外还混合MOS管/二极

表1

输入 IN1 IN2

场效应管的输出(*)

L

L

Sink1,Sink2

VEN=L L H

Sink1,Source2

HL

Source1,Sink2

H H Source1.Source2

VEN=L X X 所有场效应管关断

L表示低电平 H表示高电平 X表示任意状态

图1。典型和Tj的示意图

图3。典型Is和Vs的示意图

图2。典型静态电流和频率的示意图

图4。典型Rds和 Vref的示意图(Vref从Vs到Vref)

图5。正常状态(25°C)Rds的阻止与温度变化的示意图

图6(a),同步整流下二极管的状态(L6201)

图7(a)。典型功耗与IL的示意图(L6201)

由上升时间可以推导,下降时间应该有类似的公式: EON/OFF = [RDS (ON) ⋅ IL2 ⋅ Tf] ⋅ 2/3

静态功耗 驱动器能耗的最后组成部分是静态功耗,公式如下:

E静态 = I静态 ⋅ Vs ⋅ T

图16

一个周期内的能耗 ETOT = EOFF/ON + E负载 + E折算 + EON/OFF + E静态 总功耗的计算中的变量符号含义: 功耗等于能除以周期时间 Tr表示 上升时间

Vin,Ven=L Vin,Ven=H

-0.3

0.8 V

2

7

V

-10 μA

30

μA

电气特性(续)

芯片控制逻辑时序

符号

参数

试验条件 最小

典型

最大

t1(Vi)

源电流关断延迟时间

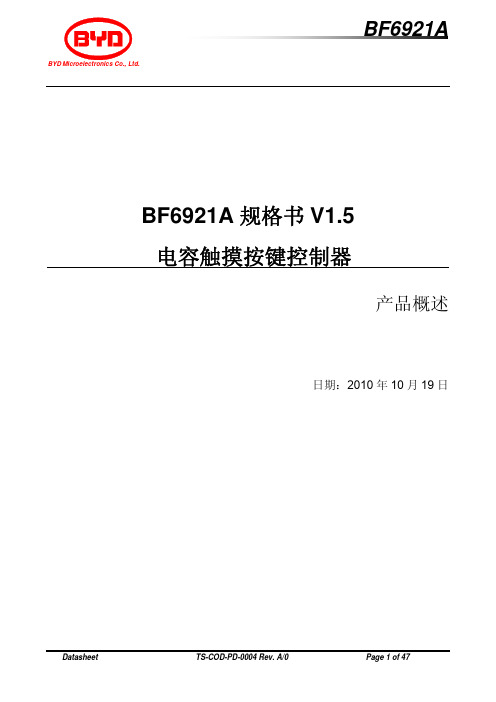

BF6921A中文规格书V1.5

rout1715连接电阻17电容触摸感应通道断开sensor1418电容触摸感应通道断开sensor1319电容触摸感应通道断开sensor1221电容触摸感应通道断开sensor1122电容触摸感应通道断开sensor1023电容触摸感应通道断开sensor924电容触摸感应通道断开sensor825电容触摸感应通道断开sensor71826电容触摸感应通道断开sensor61927电容触摸感应通道断开sensor52028电容触摸感应通道断开sensor42129电容触摸感应通道断开sensor32230电容触摸感应通道断开sensor22331电容触摸感应通道断开sensor12432电容触摸感应通道断开sensor033电容触摸感应通道断开scliic时钟端口断开sdaiic数据端口断开iovcc39模拟地20数字地iic模式中为add1断开add0iic模式中为add0断开shield13连接防水电极断开vssd40数字地16悬空断开nc34悬空断开nc35悬空断开nc36悬空断开nc37悬空断开nc38悬空断开注

电子管代换及说明资料

电子管代换及说明常用电压放大级即前级放大胆管代换表6N1ECC85,6AQ8,6H1л6N412AX7,ECC83,E83CC,7729,CV4004,B759,CV4926N10 12AU7,ECC82,E82CC,7316,CV4003,5814,B749,61896N11 6DJ8,E88CC,ECC88,6922,ECC189,6J5,6H11N,7308,El88CC6N8P 6SN7,B65,5692,33S30,CV1988,6H8C,6HM,6F8G,16336H8C 6HM,6F8G,1633,9002,6C8G6J8P 6SJ7,6267,EF86,12AT7ECC81,CV4024,6201,B739,A2900,2025,ECC80156N9P 6SL7,5691,33S29,VT2296F2ECF82,6U86N26H2л电子管代换及说明可以直接代用12AU7的型号有:ECC82,E82CC,ECC802S,B329,CV491,CV4003,CV8155,M8136,5814,6189,7730,6067,7730。

可以直接代用12AX7的管子有:ECC83,ECC803S,B339,E283CC,M8137,CV492,CV4004,CV8156,6057,7729。

7025,5751,7058,6N4。

前级管的选择:12AX7:品牌一:AMPEREX 『橙字』『地球嘜』品牌二:RCA 5751 『红字』『黑屏』『方环胆』『三云母』三:『黃字』『三雲母』『黑屏』『方環』『閃電嘜』SYLVANIA 5157。

12AU7:品牌一:AMPEREX『地球嘜』品牌二:MULLARD ecc826922:品牌一:西门子 CCA品牌二:AMPEREX 7308PHILIPS电子管大家族“买Philips电子管?不是真的吧,他们好像只是生产灯泡和光管,其音响用电子管的质素想必好不到哪里吧!”,“Philips电子管?他们根本没有生产音响用电子管,全部都是买别人家的出品回来印牌发售,又谈何Philips电子管的音色呢?”“Amperex电子管?Amperex只是一个商标,并无自己的出品,好像其吹喇叭系列电子管,都是买Philips电子管来印牌发售的”。

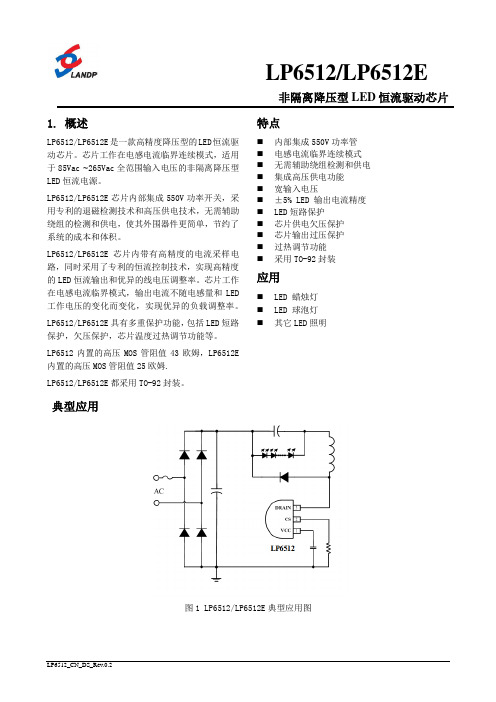

LP6512-LP6512E规格书_0.2

非隔离降压型 LED 恒流驱动芯片

储能电感

LP6512/LP6512E 工作在电感电流临界模式,当功 率管导通时,流过储能电感的电流从零开始上升, 导通时间为:

LP6512/LP6512E 内置多种保护功能,包括 LED 短 路保护,V CC 欠压保护,芯片温度过热调节等。

当 LED 短路时,系统工作在 3KHz 低频,所以功耗 很低。

管脚封装

LP6512/LP6512E

非隔离降压型 LED 恒流驱动芯片

封装 TO-92 TO-92

温度范围 -40 ℃到 105 ℃ -40 ℃到 105 ℃

包装形式 编带

2,000 颗/盒 编带

2,000 颗/盒

打印

LP6512 XXXXXY

LP6512E XXXXXY

XXXXXY: lot code

减小功率环路的面积,如功率电感、功率管、母 线电容的环路面积,以及功率电感、续流二极管、 输出电容的环路面积,以减小 EMI 辐射。

DRAIN 引脚

增加 DRAIN 引脚的铺铜面积以提高芯片散热。

保护功能

LP6512_CN_DS_Rev.0.2

封装信息

LP6512/LP6512E

非隔离降压型 LED 恒流驱动芯片

LP6512 内置的高压 MOS 管阻值 43 欧姆,LP6512E 内置的高压 MOS 管阻值 25 欧姆.

LP6512/LP6512E 都采用 TO-92 封装。

典型应用

LP6512_CN_DS_Rev.0.2

图 1 LP6512/LP6512E 典型应用图

定购信息

定购型号 LP6512 LP6512E

储能电感的计算公式为: L = VLED × (VIN − VLED ) f × IPK × VIN

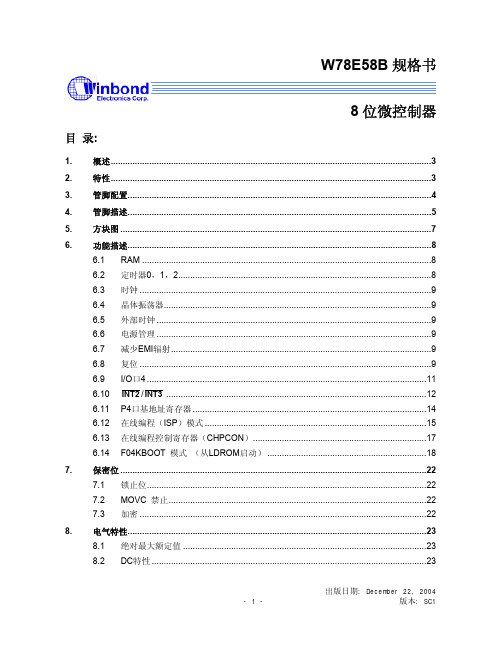

W78E58中文

W78E58B规格书8位微控制器目录:1.概述 (3)2.特性 (3)3.管脚配置 (4)4.管脚描述 (5)5.方块图 (7)6.功能描述 (8)6.1 RAM (8)6.2 定时器0,1,2 (8)6.3 时钟 (9)6.4 晶体振荡器 (9)6.5 外部时钟 (9)6.6 电源管理 (9)6.7 减少EMI辐射 (9)6.8 复位 (9)6.9 I/O口4 (11)6.10 INT2/INT3 (12)6.11 P4口基地址寄存器 (14)6.12 在线编程(ISP)模式 (15)6.13 在线编程控制寄存器(CHPCON) (17)6.14 F04KBOOT 模式(从LDROM启动) (18)7.保密位 (22)7.1 锁止位 (22)禁止 (22)7.2 MOVC7.3 加密 (22)8.电气特性 (23)8.1 绝对最大额定值 (23)8.2 DC特性 (23)出版日期: December 22, 20048.3 AC特性 (25)8.3.1时钟输入波形 (25)8.3.2程序读取周期 (26)8.3.3数据读取周期 (26)8.3.4数据写周期 (27)8.3.5端口访问周期 (27)9.时序波形图 (28)9.1 程序读取周期 (28)9.2 数据读周期 (28)9.3 数据写周期 (29)9.4 端口访问周期 (29)10.典型应用电路 (30)10.1 扩展的外部程序存储器和石英晶体 (30)10.2 扩展的外部程序存储器和振荡器 (31)11.封装尺寸 (32)11.1 DIP40 (32)11.2 44 管脚PLCC (33)11.3 44 管脚PQFP (34)12.应用指南 (35)12.1 ISP 软件编程示例: (35)13.文件版本描述 (42)1. 概述W78E58B是具有带ISP功能的Flash EPROM的低功耗8位微控制器;ISP功能的Flash EPROM可用于固件升级。

IS62LV1024L-70QI中文资料

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.DESCRIPTIONThe 1+51 IS62LV1024L and IS62LV1024LL are low powerand low Vcc,131,072-word by 8-bit CMOS static RAMs. They are fabricated using 1+51's high-performance CMOS technol-ogy. This highly reliable process coupled with innovative circuit design techniques, yields higher performance and low power consumption devices.When CE1 is HIGH or CE2 is LOW (deselected), the device assumes a standby mode at which the power dissipation can be reduced by using CMOS input levels.Easy memory expansion is provided by using two Chip Enable inputs, CE1 and CE2. The active LOW Write Enable (WE )controls both writing and reading of the memory.The IS62LV1024L and IS62LV1024LL are available in 32-pin 8*20mm TSOP-1, 8*13.4mm TSOP-1, 450mil SOP and 48-pin 6*8mm T.-BGA.CMOS STATIC RAM.EATURESAccess times of 45, 55, and 70 ns Low active power: 60 mW (typical)Low standby power: 15 µW (typical) CMOS standbyLow data retention voltage: 2V (min.) Available in Low Power (-L) and Ultra Low Power (-LL)Output Enable (OE ) and two Chip Enable (CE1 and CE2) inputs for ease in applications TTL compatible inputs and outputs Single 2.7V to 3.6V power supplyIS62LV1024L/LL1234567891011121314151632313029282726252423222120191817NC A16A14A12A7A6A5A4A3A2A1A0I/O0I/O1I/O2GNDVCC A15CE2WE A13A8A9A11OE A10CE1I/O7I/O6I/O5I/O4I/O3PIN CON.IGURATION32-Pin SOPPIN DESCRIPTIONSA0-A16Address Inputs CE1Chip Enable 1 Input CE2Chip Enable 2 Input OE Output Enable Input WE Write Enable Input I/O0-I/O7Input/OutputC o C onnectionVcc Power GNDGroundPIN CON.IGURATION32-Pin 8x20mm TSOP-1 and 8x13.4mm TSOP-1OPERATING RANGERangeAmbient TemperatureV CCCommercial 0°C to +70°C 2.7V to 3.6V Industrial40°C to +85°C2.7V to3.6V48-Pin 6x8mm T.-BGAIS62LV1024L/LLABSOLUTE MAXIMUM RATINGS (1)Symbol ParameterValueUnit V TERM Terminal Voltage with Respect to GND 0.5 to Vcc + 0.5V V CC Vcc related to GND0.3 to +4.6V T BIAS Temperature Under Bias 40 to +85°C T STG Storage Temperature 65 to +150°C P TPower Dissipation0.7WNotes:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.CAPACITANCE (1,2)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 6p.C OUTOutput CapacitanceV OUT = 0V8p.Notes:1.Tested initially and after any design or process changes that may affect these parameters.2.Test conditions: T A = 25°C, f = 1 MHz, Vcc =3.0V.DC ELECTRICAL CHARACTERISTICS (Over Operating Range)Symbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V CC = Min., I OH = 1.0 mA 2.2 V V OL Output LOW Voltage V CC = Min., I OL = 2.1 mA0.4V V IH Input HIGH Voltage 2.2V CC + 0.3V V IL Input LOW Voltage 0.30.4V I LI Input Leakage GND ≤ V IN ≤ V CC 11µA I LOOutput LeakageGND ≤ V OUT ≤ V CC11µANotes:1.V IL = 3.0V for pulse width less than 10 ns.TRUTH TABLEModeWE CE1CE2OE I/O Operation Vcc Current Not Selected X H X X High-Z I SB , I SB (Power-down)X X L X High-Z I SB , I SB Output Disabled H L H H High-Z I CC Read H L H L D OUT I CC WriteLLHXD INI CCIS62LV1024L/LLIS62LV1024L POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)-45L ns-55L ns-70L ns Symbol Parameter Test Conditions Min.Max.Min.Max.Min.Max.Unit I CC Vcc Dynamic Operating V CC = Max., CE = V IL Com. 40 35 30mASupply Current I OUT = 0 mA, f = f MAX Ind. 45 40 35I SB TTL Standby Current V CC = Max.,Com. 0.3 0.3 0.3mA(TTL Inputs)V IN = V IH or V IL, CE1≥ V IH Ind. 0.4 0.4 0.4or CE2 ≤ V IL, f = 0I SB CMOS Standby V CC = Max., f = 0Com. 50 50 50µACurrent (CMOS Inputs)CE1≥ V CC 0.2V,Ind. 75 75 75CE2 ≤ 0.2V,or V IN≥ V CC 0.2V, V IN≤ 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.IS62LV1024LL POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)-45LL ns-55LL ns-70LL ns Symbol Parameter Test Conditions Min.Max.Min.Max.Min.Max.Unit I CC Vcc Dynamic Operating V CC = Max., CE = V IL Com. 40 35 30mASupply Current I OUT = 0 mA, f = f MAX Ind. 45 40 35I SB TTL Standby Current V CC = Max.,Com. 0.2 0.2 0.2mA(TTL Inputs)V IN = V IH or V IL, CE1≥ V IH Ind. 0.3 0.3 0.3or CE2 ≤ V IL, f = 0I SB CMOS Standby V CC = Max., f = 0Com. 5 5 5µACurrent (CMOS Inputs)CE1≥ V CC 0.2V,Ind. 10 10 10CE2 ≤ 0.2V,or V IN≥ V CC 0.2V, V IN≤ 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.IS62LV1024L/LLREAD CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)-45-55-70Symbol Parameter Min.Max.Min.Max.Min.Max.Unit t RC Read Cycle Time45 55 70 ns t AA Address Access Time 45 55 70ns t OHA Output Hold Time10 10 10 ns t ACE CE1 Access Time 45 55 70ns t ACE CE2 Access Time 45 55 70ns t DOE OE Access Time 20 25 35ns t LZOE OE to Low-Z Output0 5 5 ns t HZOE OE to High-Z Output015020025ns t LZCE CE1 to Low-Z Output5 7 10 ns t LZCE CE2 to Low-Z Output5 7 10 ns t HZCE CE1 or CE2 to High-Z Output015020025ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0.4V to2.2Vand output loading specified in .igure 1.2.Tested with the load in .igure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC TEST CONDITIONSParameter UnitInput Pulse Level0.4V to 2.2VInput Rise and .all Times 5 nsInput and Output Timing 1.5Vand Reference LevelOutput Load See .igures 1AC TEST LOADS.igure 1..igure 2.IS62LV1024L/LLNotes:1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE , CE1 = V IL , CE2 = V IH .3.Address is valid prior to or coincident with CE1 LOW and CE2 HIGH transitions.(1,3)AC WAVE.ORMS (1,2)IS62LV1024L/LLWRITE CYCLE SWITCHING CHARACTERISTICS (1,3) (Over Operating Range, Standard and LowPower)-45-55-70SymbolParameter Min.Max.Min.Max.Min.Max.Unit t WC Write Cycle Time 45 55 70 ns t SCE CE1 to Write End 35 50 60 ns t SCE CE2 to Write End35 50 60 ns t AW Address Setup Time to Write End 35 50 60 ns t HA Address Hold from Write End 0 0 0 ns t SA Address Setup Time 0 0 0 ns t PWE " WE Pulse Width 35 40 55 ns t SD Data Setup to Write End 25 25 30 ns t HDData Hold from Write End0 0 0 ns t HZWE WE LOW to High-Z Output 15 20025ns t LZWE WE HIGH to Low-Z Output555nsNotes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0.4V to2.2V and output loading specified in .igure 1.2.Tested with the load in .igure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.3.The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the Write.4.Tested with OE HIGH.AC WAVE.ORMSWRITE CYCLE NO. 1 (9- Controlled)(1,2)IS62LV1024L/LLWRITE CYCLE NO. 2 (+- , CE2 Controlled)(1,2)1.The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the Write.2.I/O will assume the High-Z state if OE = V IH .DATA RETENTION SWITCHING CHARACTERISTICSSymbolParameterTest ConditionMin.Max.Unit V DRVcc for Data Retention See Data Retention Waveform 2.0 3.6V I DRData Retention CurrentVcc = 2.0V, CE1 ≥ Vcc 0.2VCom. (-L) 30µA Com. (-LL) 5µA Ind. (-L)50µA Ind. (-LL)10µA t SDR Data Retention Setup Time See Data Retention Waveform 0ns t RDRRecovery TimeSee Data Retention Waveformt RCnsDATA RETENTION WAVE.ORM (+- Controlled)IS62LV1024L/LLDATA RETENTION WAVE.ORM (CE2 Controlled)IS62LV1024LORDERING IN.ORMATION Commercial Range: 0°C to +70°C Speed (ns)Order Part No.Package45IS62LV1024L-45Q450mil SOPIS62LV1024L-45T8*20mm TSOP-1IS62LV1024L-45H8*13.4mm TSOP-1IS62LV1024L-45B6*8mm T.-BGA 55IS62LV1024L-55Q450mil SOPIS62LV1024L-55T8*20mm TSOP-1IS62LV1024L-55H8*13.4mm TSOP-1IS62LV1024L-55B6*8mm T.-BGA 70IS62LV1024L-70Q450mil SOPIS62LV1024L-70T8*20mm TSOP-1IS62LV1024L-70H8*13.4mm TSOP-1IS62LV1024L-70B6*8mm T.-BGA IS62LV1024LORDERING IN.ORMATION Industrial Range: 40°C to +85°C Speed (ns)Order Part No.Package45IS62LV1024L-45QI450mil SOPIS62LV1024L-45TI8*20mm TSOP-1IS62LV1024L-45HI8*13.4mm TSOP-1IS62LV1024L-45BI6*8mm T.-BGA 55IS62LV1024L-55QI450mil SOPIS62LV1024L-55TI8*20mm TSOP-1IS62LV1024L-55HI8*13.4mm TSOP-1IS62LV1024L-55BI6*8mm T.-BGA 70IS62LV1024L-70QI450mil SOPIS62LV1024L-70TI8*20mm TSOP-1IS62LV1024L-70HI8*13.4mm TSOP-1IS62LV1024L-70BI6*8mm T.-BGAIS62LV1024L/LLIntegrated Circuit Solution Inc.HEADQUARTER:NO.2, TECHNOLOGY RD. V, SCIENCE-BASED INDUSTRIAL PARK,HSIN-CHU, TAIWAN, R.O.C.TEL: 886-3-5780333.ax: 886-3-5783000BRANCH O..ICE:7., NO. 106, SEC. 1, HSIN-TAI 5TH ROAD,HSICHIH TAIPEI COUNTY, TAIWAN, R.O.C.TEL: 886-2-26962140.AX: 886-2-26962252IS62LV1024LLORDERING IN.ORMATIONCommercial Range: 0°C to +70°CSpeed (ns) Order Part No.Package 45IS62LV1024LL-45Q 450mil SOPIS62LV1024LL-45T 8*20mm TSOP-1IS62LV1024LL-45H 8*13.4mm TSOP-1IS62LV1024LL-45B 6*8mm T.-BGA 55IS62LV1024LL-55Q 450mil SOPIS62LV1024LL-55T 8*20mm TSOP-1IS62LV1024LL-55H 8*13.4mm TSOP-1IS62LV1024LL-55B 6*8mm T.-BGA 70IS62LV1024LL-70Q 450mil SOPIS62LV1024LL-70T 8*20mm TSOP-1IS62LV1024LL-70H 8*13.4mm TSOP-1IS62LV1024LL-70B6*8mm T.-BGAIS62LV1024LLORDERING IN.ORMATIONIndustrial Range: 40°C to +85°CSpeed (ns) Order Part No.Package 45IS62LV1024LL-45QI 450mil SOPIS62LV1024LL-45TI 8*20mm TSOP-1IS62LV1024LL-45HI 8*13.4mm TSOP-1IS62LV1024LL-45BI 6*8mm T.-BGA 55IS62LV1024LL-55QI 450mil SOPIS62LV1024LL-55TI 8*20mm TSOP-1IS62LV1024LL-55HI 8*13.4mm TSOP-1IS62LV1024LL-55BI 6*8mm T.-BGA 70IS62LV1024LL-70QI 450mil SOPIS62LV1024LL-70TI 8*20mm TSOP-1IS62LV1024LL-70HI 8*13.4mm TSOP-1IS62LV1024LL-70BI6*8mm T.-BGA。

L6562简介..

2009/8/5

20

Disable function线路架构及工作原理

图9 ZCD内部实际工作电路

21

Disable function线路架构及工作原理

图10 零电流检测电路

22

THD optimizer circuit

针对导致THD恶化的原因,L6562在其内部乘法器 单元中,嵌入了THD最优化专门电路。该电路能处理AC线 路电压过零附近积聚的能量,从而使桥式整流器之后的高频滤 波器电容得以充分放电,以减小交越失真,降低THD。

这种工作在过渡模式的电流型pfc控制器与l6561的引脚相兼容其主要不同点是在高线性乘法器中嵌入了ac输入电流总谐波失真thd最优化电路从而能在宽范围的ac线路输入电压和一个大的负载范围内提供非常低的thd及高次谐具有低于70ua的启动电流和低于4ma的工作电流并且含有截止功能因而特别适用于遥控开关控制并且能满足蓝天使能源之星和energy2000等标准

Typical application circuit (250W, Wide-range mains)

31

BCD AC-DC重要规格与典型应用

32

25

STARTER模块线路架构及工作原理

自启动电路实现的功能是在功率因数校正芯片刚开始工作 时,周期性输出一个脉冲信号开启功率管。输出周期性的脉冲 信号实际上就是一个振荡器。在集成电路中,实现振荡器的方 式很多,有LC振荡器、有环形振荡器、双比较器振荡器等等。 双比较器振荡器构成的自启动电路如图12:

7

VOLTAGE REGULATOR线路架构及工作原理

图2 电压基准实际电路图

8

VOLTAGE REGULATOR线路架构及工作原理

液晶常用电源管理芯片

1200AP40 1200AP60、1203P60 200D6、203D6 DAP8A 可互代203D6/1203P6 DAP8A 2S0680 2S0880 3S0680 3S0880 5S0765 DP104、DP704 8S0765C DP704加24V的稳压二极管ACT4060 ZA3020LV/MP1410/MP9141 ACT4065 ZA3020/MP1580 ACT4070 ZA3030/MP1583/MP1591MP1593/MP1430 ACT6311 LT1937 ACT6906 LTC3406/AT1366/MP2104 AMC2576 LM2576 AMC2596 LM2596 AMC3100 LTC3406/AT1366/MP2104 AMC34063A AMC34063 AMC7660 AJC1564 AP8012 VIPer12A AP8022 VIPer22A DAP02 可用SG5841 /SG6841代换DAP02ALSZ SG6841 DAP02ALSZ SG6841 DAP7A、DP8A 203D6、1203P6 DH321、DL321 Q100、DM0265R DM0465R DM/CM0565R DM0465R/DM0565R 用cm0565r代换〔取掉4脚的稳压二极管〕DP104 5S0765 DP704 5S0765 DP706 5S0765 DP804 DP904 FAN7601 LAF0001 LD7552 可用SG6841代〔改4脚电阻〕LD7575PS 203D6改1脚100K电阻为24K OB2268CP OB2269CP OB2268CP SG6841改4脚100K电阻为20-47K OCP1451 TL1451/BA9741/SP9741/AP200 OCP2150 LTC3406/AT1366/MP2104 OCP2160 LTC3407 OCP2576 LM2576 OCP3601 MB3800 OCP5001 TL5001 OMC2596 LM2596/AP1501 PT1301 RJ9266 PT4101 AJC1648/MP3202 PT4102 LT1937/AJC1896/AP1522/RJ9271/MP1540 SG5841SZ SG6841DZ/SG6841D SM9621 RJ9621/AJC1642 SP1937 LT1937/AJC1896/AP1522/RJ9271/MP1540 STR-G5643D STR-G5653D、STR-G8653D TEA1507 TEA1533 TEA1530 TEA1532对应引脚功能接入THX202H TFC719 THX203H TFC718S TOP246Y TOP247Y VA7910 MAX1674/75 L6920 AJC1610 VIPer12AVIPer22A [audio01]ICE2A165(1A/650V.31W);ICE2A265(2A/650V.52W);ICE2B0565(0.5A/6 50V.23W):ICE2B165(1A/650V.31W);ICE2B265(2A/650V.52W);ICE2A180(1A/800V.29W);ICE2 A280(2A/800.50W).KA5H0365R, KA5M0365R, KA5L0365R, KA5M0365RN# u) t! u1 W1 B) R, PKA5L0365RN, KA5H0380R, KA5M0380R, KA5L0380R1、KA5Q1265RF/RT〔大小两种体积〕、KA5Q0765、FSCQ1265RT、KACQ1265RF、FSCQ0765RT、FSCQ1565Q这是一类的,这些型号的引脚功能全都一样,只是输出功率不一样。

L6562D中英文

1 Features产品特点,特征;Realised in bcd technology在BCD技术变现BCD 二进制■transition-mode control of PFC pre-regulators过渡模式PFC预调节器的控制■proprietary multiplier design for minimum THD of AC input current Proprietary所有的;专利的;私人拥有的AC输入电流的最小总谐波失真专有乘法器设计■very precise adjustable output overvoltage protection■ultra-low (≤70μa) start-up currentULTRA 极端的;过分的超低(≤70μA)启动电流■low (≤4 ma) quiescent current低(≤4 mA时)的静态电流■extended IC supply voltage range■on-chip filter on current sense■disable function禁用功能■1% (@TJ = 25 °c) internal reference voltage1%(TJ= 25°C)内部参考电压■-600/+800mA totem pole gate driver with UVLO pull-down and voltage clamp-600/+800mA图腾柱栅极驱动器通过欠压锁定下拉和电压钳定totem pole 图腾柱UVLO 欠压锁定就是让输入电压低于某一个值的时候,电源芯片不工作,出于保护状态。

■dip-8/so-8 packages ecopack®8孔插/8脚(贴片)封装生态包装1.1 applications 应用■PFC pre-regulators for:– IEC61000-3-2 compliant smps (TV, Desktop pc, monitor) up to 300w– hi-end ac-dc adapter/charger– entry level server & web serverSmps switched-mode power supply 开关式电源compliant smps 兼容式开关式电源高级的AC-DC适配器/充电器入门级服务与Web服务2 .2.1 Description 描述The L6562 is a current-mode PFC controller operating in Transition Mode (TM). Pin-to-pin compatible with the predecessor L6561, it offers improved performance.6562是电流模式PFC控制器操作在过渡模式(TM)。

isis元件符号对照表

isis元件符号对照表Proteus 元件名称对照1元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG[size=+0]转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

没背光,和常用的1602B功能和引脚一样(除了调背光的二个线脚)LOGIC ANALYSER 逻辑分析器LOGICPROBE 逻辑探针LOGICPROBE[BIG] 逻辑探针用来显示连接位置的逻辑状态LOGICSTATE 逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态LOGICTOGGLE 逻辑触发MASTERSWITCH 按钮手动闭合,立即自动打开MOTOR 马达OR 或门POT-LIN 三引线可变电阻器POWER 电源RES 电阻RESISTOR 电阻器SWITCH 按钮手动按一下一个状态SWITCH-SPDT 二选通一按钮VOLTMETER 伏特计VOLTMETER-MILLI mV伏特计VTERM 串行口终端Electromechanical 电机Inductors 变压器Laplace Primitives 拉普拉斯变换Memory IcsMicroprocessor IcsMiscellaneous 各种器件 AERIAL-天线;ATAHDD;ATMEGA64;BATTERY;CELL;CRYSTAL-晶振;FUSE;METER-仪表;Modelling Primitives 各种仿真器件是典型的基本元器模拟,不表示具体型号,只用于仿真,没有PCBOptoelectronics 各种发光器件发光二极管,LED,液晶等等PLDs & FPGAsResistors 各种电阻Simulator Primitives 常用的器件Speakers & SoundersSwitches & Relays 开关,继电器,键盘Switching Devices 晶阊管Transistors 晶体管(三极管,场效应管)TTL 74 seriesTTL 74ALS seriesTTL 74AS seriesTTL 74F seriesTTL 74HC seriesTTL 74HCT seriesTTL 74LS seriesTTL 74S seriesAnalog Ics 模拟电路集成芯片Capacitors 电容集合CMOS 4000 seriesConnectors 排座,排插Data Converters ADC,DACDebugging Tools 调试工具ECL 10000 SeriesPROTEUS 元件库元件名称及中英对照AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管)BRIDEG 2 整流桥(集成块)BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPVAR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE ? 三极真空管VARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关PROTEUS原理图元器件库详细说明Device.lib 包括电阻、电容、二极管、三极管和PCB的连接器符号ACTIVE.LIB 包括虚拟仪器和有源器件DIODE.LIB 包括二极管和整流桥DISPLAY.LIB 包括LCD、LEDBIPOLAR.LIB 包括三极管FET.LIB 包括场效应管ASIMMDLS.LIB 包括模拟元器件VALVES .LIB 包括电子管ANALOG.LIB 包括电源调节器、运放和数据采样IC CAPACITORS.LIB 包括电容COMS.LIB 包括 4000系列ECL.LIB 包括ECL10000系列MICRO.LIB 包括通用微处理器OPAMP.LIB 包括运算放大器RESISTORS.LIB 包括电阻FAIRCHLD .LIB 包括FAIRCHLD 半导体公司的分立器件LINTEC.LIB 包括 LINTEC公司的运算放大器NATDAC.LIB 包括国家半导体公司的数字采样器件NATOA.LIB 包括国家半导体公司的运算放大器TECOOR.LIB 包括TECOOR公司的 SCR 和TRIAC TEXOAC.LIB 包括德州仪器公司的运算放大器和比较器ZETEX .LIB 包括ZETEX 公司的分立器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。