EDA示例汇集

EDA例子

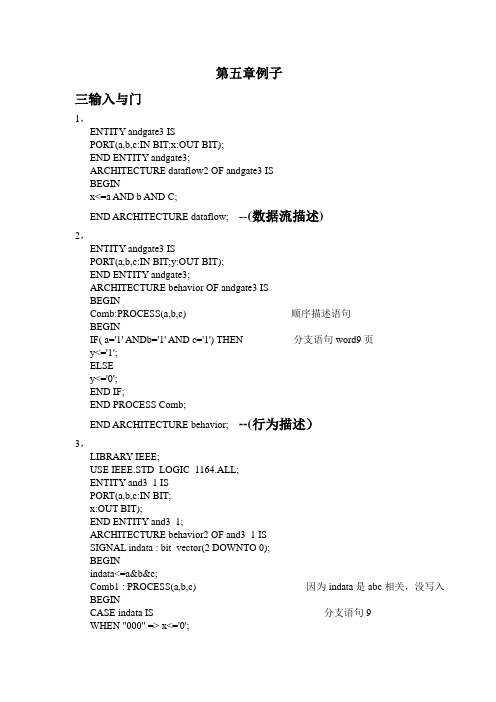

第五章例子三输入与门1,ENTITY andgate3 ISPORT(a,b,c:IN BIT;x:OUT BIT);END ENTITY andgate3;ARCHITECTURE dataflow2 OF andgate3 ISBEGINx<=a AND b AND C;END ARCHITECTURE dataflow; --(数据流描述)2,ENTITY andgate3 ISPORT(a,b,c:IN BIT;y:OUT BIT);END ENTITY andgate3;ARCHITECTURE behavior OF andgate3 ISBEGINComb:PROCESS(a,b,c) 顺序描述语句BEGINIF( a='1' ANDb='1' AND c='1') THEN 分支语句word9页y<='1';ELSEy<='0';END IF;END PROCESS Comb;END ARCHITECTURE behavior; --(行为描述)3,LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY and3_1 ISPORT(a,b,c:IN BIT;x:OUT BIT);END ENTITY and3_1;ARCHITECTURE behavior2 OF and3_1 ISSIGNAL indata : bit_vector(2 DOWNTO 0);BEGINindata<=a&b&c;Comb1 : PROCESS(a,b,c) 因为indata是abc相关,没写入BEGINCASE indata IS 分支语句9WHEN "000" => x<='0';WHEN "001" => x<='0';WHEN "010" => x<='0';WHEN "011" => x<='0';WHEN "100" => x<='0';WHEN "101" => x<='0';WHEN "110" => x<='0';WHEN "111" => x<='1';END CASE;END PROCESS Comb1;END ARCHITECTURE behavior2; --行为描述2输入与非门的VHDL描述ENTITYnand2 IS --实体描述PORT (i1,i2:IN BIT; --输入信号名o1:OUT BIT); --输出信号名END nand2;ARCHITECTUREdelayed OFnand2 IS--结构体描述BEGINo1<=i1 NAND i2 AFTER 5NS; --电路描述END delayed二输入与非门的另一种描述。

EDA-常见实例源程序代码vhdl

EDA-常见实例源程序代码vhdl第4章用VHDL程序实现常用逻辑电路4.1 组合逻辑电路设计4.1.1 基本逻辑门library ieee;use iee.std_logic_1164.all;entity jbm isport(a,b: in bit;f1,f2,f3,f4,f5,f: out bit);end jbm;architecture a of jbm isbeginf1<=a and b; --构成与门f2<=a or b; --构成或门f<=not a; --构成非门f3<=a nand b; --构成与非门f4<=a nor b; --构成异或门f5<=not(a xor b); --构成异或非门即同门end;4.1.2 三态门library ieee;use ieee.std_logic_1164.all;entity tri_s isport(enable: in std_logic;datain: in std_logic_vector(7 downto 0);dataout: out std_logic_vector(7 downto0));end tri_s;architecture bhv of tri_s isbeginprocess(enable,datain)beginif enable='1' thendataout<=datain;elsedataout<="ZZZZZZZZ";end if;end process;end bhv;4.1.3 3-8译码器library ieee;use ieee.std_logic_1164.all;entity decoder3_8 isport(a,b,c,g1,g2a,g2b: in std_logic;y: out std_logic_vector(7 downto 0));end decoder3_8;architecture a of decoder3_8 issignal dz:std_logic_vector(2 downto 0);begindz<=c&b&a;process (dz,g1,g2a,g2b)beginif(g1='1'and g2a='0'and g2b='0')thencase dz iswhen "000"=> y<="11111110";when "001"=> y<="11111101";when "010"=> y<="11111011";when "011"=> y<="11110111";when "100"=> y<="11101111";when "101"=> y<="11011111";when "110"=> y<="10111111";when "111"=> y<="01111111";when others=>y<="XXXXXXXX";end case;elsey<="11111111";end if;end process;4.1.4 优先编码器library ieee;use ieee.std_logic_1164.allentity coder isport(din: in std_logic_vector(0 to 7);output: out std_logic_vector(0 to 2));end coder;architecture behave of coder issignal sint: std_logic_vevtor(4 downto 0);beginprocess(din)beginif (din(7)='0') thenoutput <= "000" ;elsif (din(6)='0') thenoutput <= "100" ;elsif (din(5)='0') thenoutput <= "010" ;elsif (din(4)='0') thenoutput <= "110" ;elsif (din(3)='0') thenoutput <= "001" ;elsif (din(2)='0') thenoutput <= "101" ;elsif (din(1)='0') thenoutput <= "011" ;a< =din;b< =0;elsea< =din-10;b< =1;end if;end process p1;end;4.1.7 多位加(减)法器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity jianfaqi isport(a,b : in std_logic_vector(0 to 3);c0: in std_logic;c1: out std_logic;d : out std_logic_vector(0 to 3));end;architecture a of jianfaqi isbeginprocessbeginif a>b+c0 thend<=a-(b+c0);c1<='0';elsec1<='1';d<=("10000")-(b+c0-a);end if;end process ;end ;4.2 时序逻辑电路设计4.2.1 触发器RS触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity rsff isport(r,s,clk:in std_logic;q,qb:buffer std_logic);end rsff;architecture rsff_art of rsff issignal q_s,qb_s:std_logic;beginprocess(clk,r,s)beginif (clk'event and clk='1') thenif (s='1' and r='0') thenqb_s<='1' ;elsif (s='0' and r='1') thenq_s <= '1' ;qb_s <= '0' ;elsif (s='0' and r='0') thenq_s <= q_s;qb_s <= qb_s;end if;end if;q_s <= q_s;qb_s <= qb_s;end process;end rsff_art;同步复位D触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity syndff isport(d,clk,reset:in std_logic;q,qb:out std_logic);end syndff;architecture dff_art of syndff isbeginprocess(clk)beginif (clk'event and clk='1') thenif (reset='0') thenq<='0';qb<='1';elseq<=d;qb<=not q;end if;end if;end process;end dff_art;JK触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity asynjkff isport(j,k,clk,set.reset:in std_logic;q,qb:out std_logic);end asynjkff;architecture jkff_art of asynjkff issingal q_s,qb_s:std_logic;beginprocess(clk,set,reset)beginif (set='0' and reset='1' ) thenq_s<='1';qb_s<='0';elsif (set='1' and reset='0' ) thenq_s<='0';qb_s<='1';elsif (clk'event and clk='1') thenif (j='0' and k='1' ) thenq_s<='0';qb_s<='1';elsif (j='1' and k='0' ) thenq_s<='1';qb_s<='0';elsif (j='1' and k='1' ) thenq_s<=not q_s;qb_s<=not qb_s;end if;end if;q<= q_s;qb<= qb_s;end process;end jkff_art;T触发器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity tff isport(t,clk: in std_logic;q: out std_logic);end;architecture tff_art of tff issignal q_temp: std_logic;beginp1:process(clk)beginif rising_edge(clk) thenif t='1' then --当T=1时T触发器具有2分频的功能q_temp<=not q_temp;elseq_temp<=q_temp;end if;end if;q<=q_temp;end process;q<=q_temp;end tff_art;4.2.2计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4 ISport( clk: in std_logic;q: out std_logic_vector(3 downto 0));end cnt4;architecture behave of cnt4 issignal q1: std_logic_vector(3 downto 0);beginprocess(clk)beginif (clk'event and clk = '1') thenq1<=q1+1;end if;end process;q<=q1;end behave;一般计数器设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport( clk,rst,en,updown: in std_logic;cq: out std_logic_vector(3 downto 0));end cnt10;architecture behave of cnt10 isbeginprocess(clk,rst,en,updown)variable cqi:std_logic_vector(3 downto 0);beginif rst='1' thencqi:=(others=>'0'); --计数器异步复位elsif (clk'event and clk = '1') then --检测时钟上升沿if en='1'then --检测是否允许计数(同步使能)if updown='0'thenif cqi<9 thencqi:=cqi+1; --允许计数,检测是否小于9 elsecqi:=(others=>'0'); --大于9,计数值清零end if;elseif cqi>0 thencqi:=cqi-1; --检测是否大于0elsecqi:=(others=>'1'); ---否则,计数值置1end if;end if;end if;end if;cq<=cqi; --将计数值向端口输出end process;end behave;4.2.3 分频器library ieee;use std_logic_1164.all;use std_logic_unsigned.all;entity freq1 isport(clk: in std_logic;d: in std_logic_vector(7 downto 0);fout: out std_logic);end;architecture one of dvf issignal full: std_logic;beginp_reg:process(clk)variable cnt8: std_logic_vector(7 downto 0);beginif clk'event and clk='1'then --检测时钟上升沿if cnt8=''11111111'' thencnt8:=d; --当CNT8计数计满时,输入数据D被同步预置给计数器CNT8full<='1';--同时使溢出标志信号FULL输出为高电平elsecnt8:=cnt8+1;--否则继续作加1计数full<='0'; --且输出溢出标志信号FULL为低电平end if;end if;end process p_reg;p_div:process(full)variable cnt2: std_logic;beginif full'event and full='1' thencnt2:=not cnt2; --如果溢出标志信号FULL为高电平,T触发器输出取反if cnt2='1'thenfout<='1';elsefout<='0';end if;end if;end process p_div;end;4.2.4 移位寄存器library ieee;use ieee.std_logic_1164.all;entity shift isport(clk,c0: in std_logic;--时钟和进位输入md: in std_logic_vector(2 downto 0);--移位模式控制字d: in std_logic_vector(7 downto 0);--待加载移位的数据qb: out std_logic_vector(7 downto 0);--移位数据输出cn: out std_logic);--进位输出end;architecture behave of shift issignal reg: std_logic_vector(7 downto 0);signal cy: std_logic;beginprocess(clk,md,c0)beginif clk'event and clk='1' thencase md iswhen "001" => reg (0) <= c0 ;reg (7 downto 1) <= reg (6 downto 0);cy <= reg (7); --带进位循环左移when "010" => reg (0) <= reg (7);reg (7 downto 1) <= reg (6 downto 0); --自循环左移when "011" => reg (7) <= reg (0);reg (6 downto 0) <= reg (7 downto 1); --自循环右移when "100" => reg (7) <= C0 ;reg (6 downto 0) <= reg (7 downto 1);cy <= reg (0); --带进位循环右移when "101" => reg (7 downto 0) <= d(7 downto 0); --加载待移数when others => reg<= reg ; cy<= cy ; --保持end case;end if;end process;qb(7 downto 0) <= reg (7 downto 0); cn <= cy; --移位后输出end behav;4.3 状态机逻辑电路设计4.3.1 一般状态机设计library ieee;use ieee.std_logic_1164.all;entity s_machine isport ( clk,reset : in std_logic;state_inputs : in std_logic_vector(0 to1);comb_outputs : out integer range 0 to 15 );end s_machine;architecture behv of s_machine istype fsm_st is (s0, s1, s2, s3); --数据类型定义,状态符号化signal current_state, next_state: fsm_st; --将现态和次态定义为新的数据类型beginreg: process(reset,clk) --主控时序进程beginif reset = '1' thencurrent_state <= s0; --检测异步复位信号elsif clk='1' and clk'event thencurrent_state <= next_state;end if;end process;com:process(current_state, state_inputs) --主控组合进程begincase current_state iswhen s0 => comb_outputs<= 5;if state_inputs = "00" thennext_state<=s0;elsenext_state<=s1;end if;when s1 => comb_outputs<= 8;if state_inputs = "00" thennext_state<=s1;elsenext_state<=s2;end if;when s2 => comb_outputs<= 12;if state_inputs = "11" thennext_state <= s0;elsenext_state <= s3;end if;when s3 => comb_outputs <= 14;if state_inputs = "11" thennext_state <= s3;elsenext_state <= s0;end if;end case;end process;end behv;4.3.2状态机的应用library ieee;use ieee.std_logic_1164.all;entity asm_led isport(clk,clr : in std_logic;led1,led2,led3:out std_logic);end;architecture a of asm_led istype states is (s0,s1,s2,s3,s4,s5); --对状态机的状态声明signal q: std_logic_vector( 0 to 2);signal state : states;beginp1: process(clk,clr)beginif(clr='0')thenstate<=s0;elsif (clk'event and clk='1') thencase state iswhen s0=> state <=s1;when s1=> state <=s2;when s2=> state <=s3;when s3=> state <=s4;when s4=> state <=s5;when s5=> state <=s0;when others => state<=s0;end case;end if;end process p1;p2: process (clr,state)beginif(clr='0') thenled1<='0';led2<='0';led3<='0';elsecase state iswhen s0=> led1<='1';led2<='0';led3<='0';when s1=> led1<='0';led2<='1';led3<='0';when s2=> led1<='0';led2<='1';led3<='0';when s3=> led1<='0';led2<='0';led3<='1';when s4=> led1<='0';led2<='0';led3<='1';when s5=> led1<='0';led2<='0';led3<='1';when others => null;end case;end if;end process p2;end ;第6章EDA仿真技术应用实例6.1带使能和片选端的16:4线优先编码器设计子模块设计源代码:library ieee;use ieee.std_logic_1164.all;entity pencoder isport(d:in std_logic_vector(7 downto 0);ei:in std_logic; --ei:enable inputgs,eo:out bit; --gs:chip select output;eo:enable outputq2,q1,q0:out std_logic);end pencoder;architecture encoder of pencoder isbeginprocess(d)beginif(d(0)='0' and ei='0')thenq2<='1';q1<='1';q0<='1';gs<='0';eo<='1';elsif(d(1)='0' and ei='0')thenq2<='1';q1<='1';q0<='0';gs<='0';eo<='1';elsif(d(2)='0' and ei='0')thenq2<='1';q1<='0';q0<='1';gs<='0';eo<='1';elsif(d(3)='0' and ei='0')thenq2<='1';q1<='0';q0<='0';gs<='0';eo<='1';elsif(d(4)='0' and ei='0')thenq2<='0';q1<='1';q0<='1';gs<='0';eo<='1';elsif(d(5)='0' and ei='0')thenq2<='0';q1<='1';q0<='0';gs<='0';eo<='1';elsif(d(6)='0' and ei='0')thenq2<='0';q1<='0';q0<='1';gs<='0';eo<='1';elsif(d(7)='0' and ei='0')then --d7 prioty encoderq2<='0';q1<='0';q0<='0';gs<='0';eo<='1';elsif(ei='1')thenq2<='1';q1<='0';q0<='1';gs<='1';eo<='1';elsif(d="11111111" and ei='0')thenq2<='1';q1<='1';q0<='1';gs<='1';eo<='0';end if;end process;end encoder;6.27段显示译码器设计译码器设计源代码:library ieee;use ieee.std_logic_1164.all;entity decoder47 isport(lt,ibr,ib_ybr:in bit;a: in std_logic_vector(3 downto 0);y:out std_logic_vector(6 downto 0));end decoder47;architecture art of decoder47 isbeginprocess(lt,ibr,ib_ybr,a)variable s: std_logic_vector(3 downto 0);begins:=a(3)&a(2)&a(1)&a(0);if lt='0' and ib_ybr='1' theny<="1111111"; --检查七段显示管是否正常elsif ibr='0' and a="0000" theny<="0000000";elsecase s iswhen"0000"=>y<="1111110"; --7Ewhen"0001"=>y<="0110000"; --30when"0010"=>y<="1101101"; --6Dwhen"0011"=>y<="1111001"; --79when"0100"=>y<="0110011"; --33when"0101"=>y<="1011011"; --5Bwhen"0110"=>y<="0011111"; --5Fwhen"0111"=>y<="1110000"; --70when"1000"=>y<="1111111"; --7Ewhen"1001"=>y<="1110011"; --7Bwhen"1010"=>y<="0001101"; --0Dwhen"1011"=>y<="0011001"; --19when"1100"=>y<="0100011"; --23when"1101"=>y<="1001011"; --4Bwhen"1110"=>y<="0001111"; --0Fwhen"1111"=>y<="0000000";end case;end if;end process;end art;6.3带异步清零端的12位二进制全加器设计子模块源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport(clr,cin: in std_logic;a,b: in std_logic_vector(3 downto 0);s: out std_logic_vector(3 downto 0);cout:out std_logic);end adder4b;architecture art of adder4b issignal sint:std_logic_vector(4 downto 0);signal aa,bb:std_logic_vector(4 downto 0);beginprocess(clr)beginif clr='1'thensint<="00000";elseaa<='0'&a;bb<='0'&b;sint<=aa+bb+cin;end if;s<=sint(3 downto 0);cout<=sint(4);end process;end art;顶层模块设计源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder12b isport(clr,cin: in std_logic;a,b: in std_logic_vector(11 downto 0);s: out std_logic_vector(11 downto 0);cout:out std_logic);end adder12b;architecture art of adder12b iscomponent adder4b isport(clr,cin: in std_logic;a,b: in std_logic_vector(3 downto 0);s: out std_logic_vector(3 downto 0);cout:out std_logic);end component;signal carry_out1:std_logic;signal carry_out2:std_logic;beginu1:adder4b port map(clr=>clr,cin=>cin,a=>a(3 downto 0),b=>b(3 downto 0),s=>s(3 downto 0),cout=>carry_out1);u2:adder4b port map(clr=>clr,cin=>carry_out1,a=>a(7 downto 4),b=>b(7 downto 4),s=>s(7 downto 4),cout=>carry_out2);u3:adder4b port map(clr=>clr,cin=>carry_out2,a=>a(11 downto 8),b=>b(11 downto 8),s=>s(11 downto 8),cout=>cout);end art;6.4 带异步清零/置位端的JK触发器设计带异步清零/置位端的JK触发器源程序如下:library ieee;use ieee.std_logic_1164.all;entity jkff_logic isport(j,k,clk,clr,set:in std_logic;q:out std_logic);end jkff_logic;architecture art of jkff_logic issignal q_s:std_logic;beginprocess(clk,clr,set,j,k)beginif set='0' thenq_s<='1'; --异步置位elsif clr='1' thenq<='0'; --异步复位elsif clk'event and clk='1' thenif (j='0') and (k='1') thenq_s<='0';elsif(j='1') and (k='0') thenq_s<='1';elsif(j='1') and (k='1') thenq_s<=not q_s;end if;end if;q<=q_s;end process;end art;6.5 4位锁存器设计子模块设计源代码:library ieee;use ieee.std_logic_1164.all;entity latch1b isport(d: in std_logic;ena: in std_logic; --使能端q: out std_logic);end latch1b;architecture art of latch1b isbeginprocess(d,ena)beginif ena='1' thenq<=d;end if;end process;end art;元件声明程序包设计源代码:library ieee;use ieee.std_logic_1164.all;package my_package iscomponent latch1port(d:in std_logic;ena:in std_logic;q: out std_logic);end component;end;顶层模块设计源代码:library ieee;use ieee.std_logic_1164.all;use work.my_package.all; --使用用户自定义的程序包entity latch4d isport(d: in std_logic_vector(3 downto 0);oen: in bit;q:out std_logic_vector(3 downto 0));end latch4d;architecture one of latch4d issignal sig_save:std_logic_vector(3 downto 0);begingetlatch:for n in 0 to 3 generate --用for_generate语句循环例化4个1位锁存器latchx:latch1 port map(d(n),g,sig_save(n)); --关联end generate;q<=sig_save when oen='0'else"ZZZZ";end one;6.6 32进制多样型计数器设计(1)32进制同步加法计数器源程序32进制同步加法计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_plus isport(clk,clr:in std_logic;dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_plus issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr,)beginif clr='1'thend1<=(others=>'0');d0<="0000"; --同步清零elsif clk'event and clk='1' thenif(d1=3 and d0=1)thend1<="0000";d0<="0000"; --计数到32时清零elsif(d0=1) thend0<="0000";d1<=d1+1;elsed0<=d0+1;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(2)32进制同步减法计数器源程序32进制同步减法计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_sub isport(clk,clr:in std_logic;dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_sub issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr)beginif clr='1' thend1<="0000";d0<="0000"; --异步清零elsif clk'event and clk='1' thenif(d1=0 and d0=0) thend1<="0011";d0<="0001"; --设定容量31elsif(d0=0) thend0<="0001";d1<=d1-1;elsed0<=d0-1;d1<=d1;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(3)32进制同步可逆计数器源程序32进制同步可逆计数器源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter_reversible isport(clk,clr,s:in std_logic; --s=1加法计数,s=0减法计数dout0,dout1: out std_logic_vector(3 downto 0));end;architecture art of counter_reversible issignal d0,d1:std_logic_vector(3 downto 0); --d0代表个位,d1代表十位beginprocess(clk,clr,s)beginif clr='1'thend1<="0000";d0<="0000"; --异步清零elsif (clk'event and clk='1' )thenif s='1' thenif(d1=3 and d0=1) thend1<="0000";d0<="0000"; --计数到31时清零elsif(d0=1) thend0<="0000";d1<=d1+1;else d0<=d0+1;end if;elsif s='0' thenif(d1=0 and d0=0)thend1<="0011";d0<="0001"; --设定容量31elsif(d0=0) thend0<="0001";d1<=d1-1;elsed0<=d0-1;d1<=d1;end if;end if;end if;dout1<=d1;dout0<=d0;end process;end art;(4)32进制异步加法计数器源程序32进制异步加法计数器源程序如下:①子模块D触发器源程序设计。

EDA示例汇集

方法二:用键盘直接 输入所需元件名,再 单击“OK”按钮即可将 元件调入原理图编辑 窗中。

2018/12/10

湖北众友科技EDA工作室

11

步骤2:输入设计项目和存盘 (5)排列好调入的元件,连接好原理图。

A

B

连线方法:把鼠标放在 A 处变成十字形, 按处左键保持十字形移至 B 处松开即完成 连接。

输入设计项目和存盘用户工作库末存盘时为默认文件夹此处已存盘到自己建立的文件夹元件符号名输入区可直接输入所需元件的符号名库选择区软件安装在d盘maxplus2文件夹下除了用户工作库外件夹下除了用户工作库外还有四种元件库包含了基本逻辑元件库prim如门触发器等

EDA技术教学系列

EDA 示 例 汇 集

基于EDA-E的实验例程

2018/12/10

湖北众友科技EDA工作室

12

步骤2:输入设计项目和存盘 (6)分别在input和output的PIN_NAME上双击使其变黑色, 再用键盘分别输入各引脚名:a、b、co、so。

半加器表达式:

进位:co=a and b

和: so=a xnor (not b)

注意:半加器用原理图的实现方法很多,此处用同或的方 法来实现。有兴趣的同学可以用其它的方法来实现。

2018/12/10 湖北众友科技EDA工作室 24

步骤5:时序仿真 (3) 设 置 波 形 参 量 。 在 “ Option” 菜 单 中 消 去 网 格 对 齐 项 “Snap to Grid”的对勾,以便能够任意设置输入电平位置, 或设置输入时钟信号的周期。

2018/12/10

湖北众友科技EDA工作室

设置后

步骤4:选择目标器件并编译 (1)选择“Assign”菜单中“Device”项,弹出Device对话框 。

EDA实验报告范例

EDA技术的相关网址:

• END F_ADDER_1;

• ARCHITECTURE a OF F_ADDER_1 IS • COMPONENT XOR_1 • PORT (A1,B1:IN std_logic; • C1: OUT std_logic); • END COMPONENT; • COMPONENT NAND_2 • PORT (A1,B1:IN std_logic; • C1: OUT std_logic); • END COMPONENT; • SIGNAL S1,S2,S3: std_logic ; • BEGIN

• 三、 实验条件

• (1) 电脑。 • (2) 开发软件: QuartusII 。 • (3) 实验设备: EL- EDA-V型 • EDA 实 验 开 发 系 统。 • (3) 拟用芯片: ACEX1K: • EP1K100QC2083。

•

四、 实验设计

1)全加器的逻辑图

由异或门和二输入端与非门构 成的1位二进制全加器如图所示。

实验教学目的:

了解一类可编程逻辑器件,掌握一门硬件描述 语言,熟悉使用一种EDA设计工具,设计自己的芯片。

教材及参考资料

教材:

《EDA技术及应用》谭会生、张昌凡 编著 西安电子科技大学出版社

参考资料:

《CPLD技术及其应用》宋万杰 等编著 西安电子科大出版社出版 《VHDL硬件描述语言与数字逻辑电路设计》 侯伯亨 顾新 等编著 西安电子科技大学出版社 《CPLD/FPGA的开发和应用》徐光辉 等编著 电子工业出版社出版

• --与非门的VHDL描述

• • • • • • • • • • LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY NAND_2 IS PORT( A1,B1: IN std_logic; C1: OUT std_logic); END NAND_2; ARCHITECTURE c OF NAND_2 IS BEGIN C1<=A1 NAND B1; END c;

基于EDA的示例程序

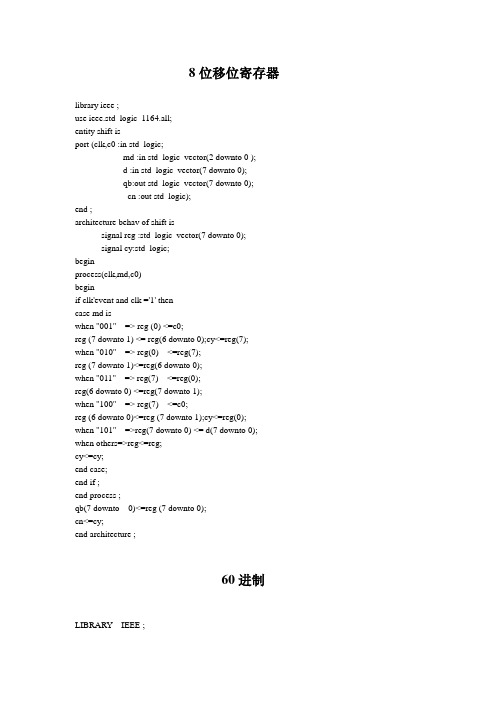

8位移位寄存器library ieee ;use ieee.std_logic_1164.all;entity shift isport (clk,c0 :in std_logic;md :in std_logic_vector(2 downto 0 );d :in std_logic_vector(7 downto 0);qb:out std_logic_vector(7 downto 0);cn :out std_logic);end ;architecture behav of shift issignal reg :std_logic_vector(7 downto 0);signal cy:std_logic;beginprocess(clk,md,c0)beginif clk'event and clk ='1' thencase md iswhen "001" => reg (0) <=c0;reg (7 downto 1) <= reg(6 downto 0);cy<=reg(7);when "010" => reg(0) <=reg(7);reg (7 downto 1)<=reg(6 downto 0);when "011" => reg(7) <=reg(0);reg(6 downto 0) <=reg(7 downto 1);when "100" => reg(7) <=c0;reg (6 downto 0)<=reg (7 downto 1);cy<=reg(0);when "101" =>reg(7 downto 0) <= d(7 downto 0); when others=>reg<=reg;cy<=cy;end case;end if ;end process ;qb(7 downto 0)<=reg (7 downto 0);cn<=cy;end architecture ;60进制LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY CNT60 ISPORT (CLK , RESET: IN STD_LOGIC ;C : OUT STD_LOGIC_VECTOR (6 DOWNTO 0)) ; END CNT60 ;ARCHITECTURE BY OF CNT60 ISSIGNAL A1 : STD_LOGIC_VECTOR (6 DOWNTO 0) ; BEGINPROCESS (CLK , RESET )BEGINIF RESET ='1' THEN A1 <= "0000000" ;ELSIF CLK'EVENT AND CLK ='1' THENIF A1 < 16#60# THENIF A1 = "1011001" THENA1 <= "0000000" ;ELSE A1 <=A1 + 1 ;IF A1(3 DOWNTO 0) ="1001" THENA1 <= A1 + 7 ;END IF ;END IF ;END IF ;END IF ;END PROCESS ;C<=A1;END ARCHITECTURE BY ;移动小车LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY CNT60 ISPORT (CLK , RESET: IN STD_LOGIC ;C : OUT STD_LOGIC_VECTOR (6 DOWNTO 0)) ; END CNT60 ;ARCHITECTURE BY OF CNT60 ISSIGNAL A1 : STD_LOGIC_VECTOR (6 DOWNTO 0) ; BEGINPROCESS (CLK , RESET )BEGINIF RESET ='1' THEN A1 <= "0000000" ;ELSIF CLK'EVENT AND CLK ='1' THENIF A1 < 16#60# THENIF A1 = "1011001" THENA1 <= "0000000" ;ELSE A1 <=A1 + 1 ;IF A1(3 DOWNTO 0) ="1001" THENA1 <= A1 + 7 ;END IF ;END IF ;END IF ;END IF ;END PROCESS ;C<=A1;END ARCHITECTURE BY ;数据选择器library ieee ;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shujuxuanzhe isport(clk3,ret:in std_logic;sec:in std_logic_vector(6 downto 0);min:in std_logic_vector(6 downto 0);hour:in std_logic_vector(6 downto 0);daout:out std_logic_vector(3 downto 0);sel:out std_logic_vector(2 downto 0));end shujuxuanzhe;architecture bev of shujuxuanzhe issignal q: std_logic_vector (2 downto 0);beginprocess(clk3,ret)beginif ret='1' then q<="000";elsif clk3'event and clk3='1'then q<=q+1;case q iswhen "101"=>daout<=sec(3 downto 0);when "100"=>daout(2 downto 0)<=sec(6 downto 4); daout(3)<='0';when "011"=>daout<=min(3 downto 0);when "010"=>daout(2 downto 0)<=min(6 downto 4); daout(3)<='0';when "001"=>daout<=hour(3 downto 0);when "000"=>daout(1 downto 0)<=hour(5 downto 4);daout(3 downto 2)<="00";when others=>daout<="0000";end case ;end if;end process;sel<=q;end bev;半加器LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY H_ADDER ISPORT (A, B :IN STD_LOGIC ;CO, SO :OUT STD_LOGIC);END ENTITY H_ADDER;ARCHITECTURE FH1 OF H_ADDER ISSIGNAL ABC :STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINABC <= A&B;PROCESS (ABC) BEGINCASE ABC ISWHEN " 00 " => SO <= '0'; CO <= '0' ;WHEN "01" =>SO <='1'; CO <= '0 ';WHEN "10" =>so <= '1'; co <= '0';WHEN "11" =>so <='0'; co <='1';WHEN OTHERS =>NULL ;END CASE ;END PROCESS ;END ARCHITECTURE FH1;数码显示器library ieee ;use ieee.std_logic_1164.all;entity led isport (a :in std_logic_vector (3 downto 0);y :out std_logic_vector (7 downto 0));end entity led;architecture one of led isbeginprocess (a )begincase a iswhen "0000" => y <="00111111";when "0001" => y <="00000110";when "0010" => y <="01011011";when "0011" => y <="01001111";when "0100" => y <="01100110";when "0101" => y <="01101101";when "0110" => y <="01111101";when "0111" => y <="00000111";when "1000" => y <="01111111";when "1001" => y <="01101111";when "1010" => y <="01110111";when "1011" => y <="01111100";when "1100" => y <="00111001";when "1101" => y <="01011110";when "1110" => y <="01111001";when "1111" => y <="01110001";when others => y <="00000000"; end case ;end process;end architecture one;。

EDA含有(程序-示例图全套)实验报告(吐血推荐)

实验报告(2012----2013学年第一学期)课程名称:EDA技术专业班级:学号:姓名:实验一:原理图输入法设计与仿真实验时间:2012年10月19日(第七周)六、实验心得实验二七人表决器的设计3、引脚匹配实验三 显示电路设计一、实验目的1、学习7段数码显示译码器设计;2、学习VHDL 的多层设计方法。

二、实验仪器设备1、PC 机一台2、GW48-PK2系列SOPC/EDA 实验开发系统 三、实验原理1、七段数码显示工作原理(共阴极接法)7 段数码是纯组合电路,通常的小规模专用IC ,如74 或4000系列的器件只能作十进制BCD 码译码,然而数字系统中的数据处理和运算都是2 进制的,所以输出表达都是16 进制的,为了满足16 进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD 中来实现。

作为7 段译码器,输出信号LED7S 的7 位分别接数码管的7 个段,高位在左,低位在右。

例如当LED7S 输出为“1101101”时,数码管的7 个段:g 、f 、e 、d 、c 、b 、a 分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h 。

2、显示代码概念 显示代码a b cdefg四、实验内容1、编写7段译码器VHDL 源程序。

2、在Quartus Ⅱ软件上编译和仿真。

3、锁定管脚,建议选择实验电路模式6,显示译码输出用数码8 显示译码输出(PIO46-PIO40),键8、键7、键6 和键5 四位控制输入。

4编程下载与硬件验证。

5、记录系统仿真和硬件验证结果。

五、实验结果:2、波形仿真图:4、 引脚锁定:六、实验心得: 其实本实验的显示我们在模电里面就学习过了,也用集成块进行过实验,本实验用程序加硬件完成。

真所谓条条道路通罗马!实验四 四位全加器一、实验目的通过实验让学生熟悉Quartus Ⅱ的VHDL 文本设计流程全过程,掌握组合逻辑电路的文本输入设计法,通过对设计电路的仿真和硬件验证,让学生进一步了解加法器的功能。

EDA(电子设计自动化)模板

EDA(电子设计自动化)模板项目名称:EDA(电子设计自动化)模板1. 项目简介:本项目是一个用于电子设计自动化的模板,旨在提供一个可靠、高效的电子设计自动化框架,以帮助电子工程师快速完成电路设计、仿真和验证工作。

2. 功能特点:- 电路设计:提供基本的电路元件库,支持通过拖拽方式构建电路图,并自动生成对应的电路连接。

- 电路仿真:集成常用的电路仿真工具,例如SPICE仿真,以验证电路的性能和功能。

- 电路布局与布线:提供丰富的布局和布线工具,支持生成PCB (印制电路板)的设计文件。

- 线束与信号完整性分析:集成线束设计与信号完整性分析工具,帮助工程师解决电路布线时可能遇到的问题。

- 可扩展性:支持自定义电路元件库、仿真模型和布局规则,以满足不同项目的需求。

3. 技术实现:- 前端框架:使用HTML、CSS和JavaScript实现界面的搭建和交互功能。

- 后端开发:使用Python或Java等编程语言构建后端逻辑,处理用户请求和数据存储。

- 数据库:使用MySQL或MongoDB等数据库管理电路设计的相关信息。

- 仿真工具集成:集成常用的电路仿真工具,例如PSPICE、LTspice等。

- 布局与布线工具:集成AutoCAD、Altium Designer等工具,实现电路布局和布线功能。

4. 使用步骤:1) 登录系统或注册新用户。

2) 创建项目并命名。

3) 在项目中添加电路元件,连接电路图。

4) 进行电路仿真,验证电路性能。

5) 根据仿真结果进行电路布局和布线。

6) 分析电路线束与信号完整性,解决布线中的问题。

7) 导出PCB设计文件或打印电路图。

5. 预期成果:本项目的目标是提供一个完整的电子设计自动化框架,简化电子工程师的设计流程,提高工作效率。

预期成果包括:- 一个稳定可靠的EDA模板,满足基本的电子设计需求。

- 提供可扩展性,允许用户根据具体项目需求进行定制。

- 提供详细的文档和示例,帮助用户快速上手使用和定制模板。

EDA示例汇集讲解

EDA 示 例 汇 集

基于EDA-E的实验例程

示例课件目录

1、原理图输入设计方法示例

1、原理图输入设计方法示例

1.1(组合逻辑)1位全加器设计 1.2(时序逻辑)2位十进制数字频率计设计

1.3参数可设置LPM兆功能块设计

1.4波形输入设计方法

1.1:1位全加器设计向导

1.11实验目的 熟悉利用MAX+plusII的原理图输入方法设计 简单组合电路,掌握层次化设计的方法。

锁存器

7 段 码 输 出 数 码 管 片 选

位选

1.22设计分析与实现

(3)测频时序控制模块:设计3个控制信号:计数器计数信号 en、清零信号clr、锁存信 号lock。完成频率计自动测频功能。

1.22设计分析与实现

(4)频率计顶层文件设计:

(5)功能概述:对照频率计设计的顶层文件与总框图,可以了解到我们成功的用原理 图的方式设计出了 2位十进制频率计, 8Hz 是基准时钟,通过 ctrol 模块产生 1Hz的en 计数有效信号,及计数锁存信号lock,计数清零信号clr。32768Hz是数码管显示扫描 信号,可完成多位数码显示。 fry是待测频率, cout满一百时的进位显示,可通过发 光二极管显示。在二位频率范围内,输入不同的待测频率可以马上在数码管显示出 测量值。有兴趣的同学不妨按总框图的结构试用原理图设计出多位频率计的设计。

步骤5:时序仿真

(7)运行仿真器。

步骤5:时序仿真

步骤5:时序仿真

单击 Simulator 对话框中的“ Start” 按钮 ,仿真提示无错。

步骤5:时序仿真

(8)观察半加器的仿真波形。

结果正确, 但有延迟

步骤5:时序仿真

EDA 第6章 VHDL设计应用实例

6.1 数字频率计的设计 6.2 数字钟的设计 6.3 函数发生器的设计 6.4 交通灯信号控制器的设计 6.5 乐曲演奏电路的设计 VGA显示控制器的设计 6.6 VGA显示控制器的设计

6.1 数字频率计的设计

数字频率计是直接用十进制数字显示被 测信号频率的一种测量装置, 测信号频率的一种测量装置,是一种应用很 广泛的仪器。 广泛的仪器。

图6.4 频率计的仿真波形

6.2 数字钟的设计

图6.5 数字钟的电路原理图

6.3 函数发生器的设计

图6.6 函数发生器总体框图

6.4 交通灯信号控制器的设计

图6.7 交通灯信号控制器仿真波形图

图6.8 七段码显示动态扫描仿真波形图

6.5 乐曲演奏电路的设计

图6.9 硬件乐曲演奏电路结构

6.6 VGA显示控制器的设计 VGA显示控制器的设计

图6.10 CRT显示器扫描过程示意图 CRT显示器扫描过程示意图

图6.11 15针VGA接口 15针VGA接口

表6.1

引脚 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

15针VGA接口引脚定义 15针VGA接口引脚定义

名 RED GREEN BLUE ID2 GND RGND GGND BGND KEY SGND ID0 ID1 or SDA HSYNC or CSYNC VSYNC ID3 or SCL 称 定 义 红基色 red 绿基色 green 蓝基色 blue 地址码 ID bit 自测试(各家定义不同) 红地 绿地 蓝地 保留(各家定义不同) 数字地 地址码 地址码 行同步 场同步 地址码(各家定义不同)

图6.1 测频原理框图和时间波形

(EDA技术及应用)第6章VerilogHDL设计应用实例

第6章 Verilog HDL设计应用实例

6.1 8位加法器的设计

1.系统设计思路 加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器 都可由加法器来构成。多位加法器的构成有两种方式:并行进位和 串行进位。并行进位加法器设有进位产生逻辑,运算速度较快;串 行进位方式是将全加器级联构成多位加法器。并行进位加法器通常 比串行级联加法器占用更多的资源。随着位数的增加,相同位数的 并行加法器与串行加法器的资源占用差距也越来越大。因此,在工 程中使用加法器时,要在速度和容量之间寻找平衡点。 实践证明, 4位二进制并行加法器和串行级联加法器占用几乎相 同的资源。这样,多位加法器由 4位二进制并行加法器级联构成是 较好的折中选择。本设计中的8位二进制并行加法器即是由两个4位 二进制并行加法器级联而成的,其电路原理图如图6.1所示。

在掌握了EDA技术的基础知识和基本操作后,学习 EDA技术最有效地方法就是进行EDA技术的综合应用设计 。本章阐述了12个非常实用的Verilog HDL综合应用设计实 例的系统设计思路,主要Verilog HDL源程序,部分时序仿 真和逻辑综合结果及分析,以及硬件的逻辑验证方法。这些 综合应用设计实例包括8位加法器、8位乘法器、8位除法器 等基本运算电路,数字频率计、数字秒表、交通灯信号控制 器、可调信号发生电路、闹钟系统等常用应用电路,PWM 信号发生器、高速PID控制器,FIR滤波器,CORDIC算法 的应用等电机控制、数字信号处理、模糊控制、神经网络中 经常用到的基本电路。

立创eda 复用模块器件编号

立创eda 复用模块器件编号English Answer:Introduction.Altium Designer is a powerful and versatile PCB design software that allows users to create complex and high-quality PCBs. One of the most useful features of Altium Designer is its ability to reuse modules. Modules are essentially pre-designed blocks of circuitry that can be easily inserted into a new design. This can save a significant amount of time and effort, especially when designing complex PCBs.Module Reuse in Altium Designer.To reuse a module in Altium Designer, simply select the module from the library and place it on the schematic. The module can then be connected to other components on the schematic just like any other component.Module Parameters.Modules can have parameters that can be set to customize the module's behavior. For example, a module might have a parameter that sets the output voltage or the operating frequency. To set the parameters of a module, simply right-click on the module and select "Edit Module Parameters".Module Reuse Benefits.There are many benefits to reusing modules in Altium Designer. Some of the benefits include:Reduced design time: Reusing modules can save a significant amount of time by eliminating the need to design the same circuitry from scratch.Improved quality: Modules are typically designed and tested by experienced engineers, so they are more likely to be reliable and accurate.Reduced errors: Reusing modules can help to reduce errors by eliminating the need to manually enter component information.Greater flexibility: Modules can be easily customized to meet the specific needs of a design.Module Reuse Examples.Modules can be used to reuse a variety of different types of circuitry. Some common examples include:Power supplies: Modules can be used to create custom power supplies that meet the specific needs of a design.Signal conditioning: Modules can be used to amplify, filter, and otherwise condition signals.Microcontrollers: Modules can be used to add microcontrollers to a design.Sensors: Modules can be used to add sensors to a design.Communication interfaces: Modules can be used to add communication interfaces such as RS-232, USB, and Ethernet.Conclusion.Module reuse is a powerful feature of Altium Designer that can save time, improve quality, and reduce errors. By reusing modules, designers can create complex and high-quality PCBs quickly and easily.Chinese Answer:简介。

立创eda 内电层与焊盘连接方式

立创eda 内电层与焊盘连接方式全文共四篇示例,供读者参考第一篇示例:在PCB设计中,内电层与焊盘的连接方式是非常重要的一环。

正确的连接方式可以确保电路板的稳定性和可靠性。

在实际的设计中,有多种连接方式可供选择,每种方式都有其适用的场景和特点。

今天我们就来探讨一下关于【立创eda 内电层与焊盘连接方式】的相关知识。

在PCB设计中,内电层是指板材内部的电气连接层,用于传输信号和供电。

而焊盘则是指电子元件连接的金属圆盘。

内电层与焊盘的连接方式可以分为以下几种:1. 通过通孔连接:通孔是一种贯穿整个PCB板的孔洞。

内电层与焊盘之间可以通过通孔来连接。

通孔连接方式简单可靠,适用于信号传输要求较高的场景。

但通孔连接方式会消耗较多的板材空间,且可能导致电路板钻孔难度增加。

2. 通过过孔连接:过孔是一种连接内电层与焊盘的孔洞。

过孔连接方式在通孔连接的基础上做了改进,它可以有效减小板材空间占用,提高电路板的布线密度。

但是过孔连接方式容易受到焊盘装配过程中的热影响,可能导致焊盘与内电层的连接出现问题。

在选择内电层与焊盘连接方式时,需要根据实际的设计需求和制造工艺来进行综合考虑。

正确的连接方式可以提高电路板的性能和可靠性,降低设计和制造成本。

希望上述内容能帮助您更加深入理解【立创eda 内电层与焊盘连接方式】的相关知识。

第二篇示例:一、常见的内电层与焊盘连接方式在PCB设计中,内电层与焊盘的连接方式主要有以下几种:1. 通过通孔连接:这是最常见的一种连接方式。

设计师可以在内电层和焊盘之间布置通孔,并通过焊盘内的铜箔与内电层相连接。

这种方式连接简单可靠,适用于大多数情况。

2. 通过盲孔连接:盲孔是一种只在一面板上的孔,不通穿整个板厚。

设计师可以通过盲孔连接内电层和焊盘,但盲孔的制造和成本较高,使用较少。

4. 通过金属化孔连接:金属化孔是一种带有金属涂层的盲孔或盲孔的变种。

金属化孔连接内电层和焊盘可以提高连接的可靠性和导电性能。

eda中的always语句 -回复

eda中的always语句-回复什么是EDA中的Always语句?在EDA(Electronic Design Automation,电子设计自动化)中,Always语句是一种常用的硬件描述语言(HDL)构造。

它在多种HDL,如Verilog和VHDL中都有应用。

Always语句的主要作用是定义系统的行为和状态转换。

Always语句的基本语法如下:always (posedge signal_A or negedge signal_B) begin sequential statementsend在上述语法中,posedge和negedge关键字分别表示上升沿和下降沿触发器。

signal_A和signal_B代表输入信号。

当信号A产生上升沿(或下降沿),或者信号B产生上升沿(或下降沿)时,被定义在begin和end之间的顺序语句将会被执行。

Always语句的执行机制如下:1. Always语句块中的顺序语句会按照从上到下的顺序执行。

2. Once执行完成后,Always语句会等待信号的变化,然后重新执行该代码块。

Always语句的特点:1. Always语句用于描述时序逻辑和数据流行为,因此它主要用于描述触发和状态转换。

2. Always语句中的信号可以是单个信号或多个信号的组合。

3. Always语句中的信号变化会导致代码块被重复执行,保证了逻辑处理过程的连续性。

4. Always语句中可以使用敏感信号列表,以便控制代码块的执行方式。

5. Always语句可用于组合逻辑(Combinational Logic)和时序逻辑(Sequential Logic)。

Always语句的实例示意:为了更好地理解Always语句的应用,下面将通过一个简单的例子来展示其用法。

假设有一个时钟(Clock)信号,周期为10个时钟周期。

我们想要检测时钟信号的上升沿,并通过一个计数器(Counter)记录触发的次数。

eda中的always语句 -回复

eda中的always语句-回复什么是EDA中的always语句?在硬件描述语言(HDL)中,特别是在Verilog HDL中,always语句用于定义一个始终执行的块。

这个块中的代码会在满足指定的敏感列表条件时一直运行。

always块可以用于创建组合逻辑或时序逻辑。

always语句的主要用途是创建时序逻辑,这些逻辑在特定的时钟信号驱动下执行。

always语句可以定义在时钟上升沿、下降沿或者任意边沿触发的条件下执行。

此外,always语句也可以用于描述组合逻辑,即不受时钟信号驱动的逻辑。

在Verilog HDL中,always语句的基本语法如下:always @ (敏感列表)begin执行的代码块end敏感列表(sensitivity list)是指触发always语句执行的条件。

这些条件可以是时钟信号的边沿触发,也可以是特定信号值的变化触发。

敏感列表用于告诉HDL编译器何时执行always语句中的代码块。

现在让我们分步骤回答与EDA中的always语句相关的问题。

第一步:always语句的基本语法always语句的基本语法在上面已经给出。

它由关键字"always"开始,后面是@符号和敏感列表。

在begin和end之间是具体执行的代码块。

敏感列表可以是一个或多个信号或时钟信号的边沿。

第二步:时钟触发的always语句在时序逻辑中,always语句通常与时钟信号相关联,以实现特定的逻辑功能。

在时钟边沿上触发的always语句最常见,它用来定义在时钟上升沿(posedge)或下降沿(negedge)时执行的逻辑。

这样的语句可以用于实现触发器(flip-flop)和寄存器(register)等时序逻辑。

例如,下面是一个在时钟上升沿触发的always语句的示例:always @(posedge clk)begin在时钟上升沿执行的代码块end在这个示例中,always语句指定当时钟信号(clk)上升沿触发时执行代码块中的逻辑。

EDA例子

1.门电路的设计基本门电路:与门、或门、非门(反相器)复合门电路:与非门、或非门、与或非门两种特殊的门电路:异或门、同或门(1)module(a,b,c,y1,y2,y3,y4,y5,y6,y7,y8);input a,b,c;output y1,y2,y3,y4,y5,y6,y7,y8;assign y1= a & b;assign y2= a | b;assign y3= ~a;assign y4= ~(a & b);assign y5=~(a | b);assign y6= ~( a&b | c);assign y7= a ^ b;assign y8=~(a ^ b);endmodule(2)//-------------------------------------------// BasicGate Modeling (Gate-Level)// Filename: Basic_Gates.v//------------------------------------------module Basic_Gates (a,b,yand,yor,ynot,ynand,ynor,yxor,yxnor);// Port Declarationsinput a,b;output yand,yor,ynot,ynand,ynor,yxor,yxnor;// Gate instantiationsand (yand,a,b);or (yor,a,b);not (ynot,a);nand (ynand,a,b);nor (ynor,a,b);xor (yxor,a,b);xnor (yxnor,a,b);endmodule2.编码器的设计在数字系统中,经常需要将特定意义的信息编成若干位二值代码,实现编码操作的数字电路称为编码器。

编码器分优先编码器和普通编码器两种,有4线-2线、8线-3线、16线-4线等多种类型,其中优先编码器应用最为普遍。

EDA技术5_并发代码例子

四位串行加法器仿真波形

深圳大学信息工程学院

Ci1 Ai Bi Ci ( Ai Bi )

Ai Bi Gi Ai Bi Pi C0 A0 B0 ( A0 B0 ) C IN G0 P0 CIN C1 G1 P 1 C0 C2 G2 P2 (G1 P 1 C0 ) C3 G3 P3 (G2 P2 (G1 P 1 C0 )) Si Ai Bi Ci

加法器

例:四位超前进位加法器

S3

各位的进位输出信号只 与两个相加数有关,而与 低位进位信号无关。

S1

S0

S2

C

si c i c i 1

进位 电路

si c i c i 1

进位 电路

si c i c i 1

si c i c i 1

cin

进位 电路

A3

B3

A 2 B2

A1

B1

A 0 B0

超前进位全加器

深圳大学信息工程学院

architecture behavioral of sync_DFF is begin process(clk) begin if (clk 'event and clk='1')then if(reset='1') then q <= '0'; else q <= d;

嘉立创 eda 例程

嘉立创 eda 例程嘉立创EDA例程在当前的电子设计自动化(EDA)领域中,嘉立创(JLC)是一家备受推崇的公司,致力于提供高效、可靠和创新的解决方案。

作为全球领先的PCB原型解决方案提供商,嘉立创不仅仅提供优质的PCB制造服务,还提供一系列EDA工具和例程,以帮助工程师们轻松完成设计任务。

一、嘉立创EDA的概述与特点嘉立创EDA旨在满足不同领域、不同规模的电子设计需求。

他们提供的EDA工具以其便捷性、灵活性和高效性而在行业内脱颖而出。

1. 电路原理图设计嘉立创通过其专业的原理图设计工具,使工程师们能够以直观的方式创建和修改电路原理图。

该工具支持多种元件和符号库,包括常用的IC、传感器和排线等。

此外,嘉立创的原理图设计工具还具备云端协作功能,工程师们可以方便地共享和合作编辑设计。

2. PCB布局设计对于PCB布局设计,嘉立创提供了一流的设计软件,以帮助工程师们快速创建高质量的PCB布局。

该软件具备丰富的特性,包括自动布线、信号完整性分析和差分信号设计等。

此外,嘉立创还支持所有常见的文件格式,以便与其他EDA工具和制造商进行兼容。

3.仿真和验证嘉立创的EDA工具还可以在设计过程中进行仿真和验证,以确保设计的可靠性和稳定性。

他们提供了完备的仿真工具和库,可用于电气特性仿真、时序仿真和噪声分析等。

通过这些工具,工程师们能够提前发现和解决设计中的问题,从而节约时间和资源。

4.嵌入式软件开发对于嵌入式系统的开发,《嘉立创》也提供了一系列的EDA工具和例程。

他们的工具可以帮助工程师们轻松进行嵌入式软件的编写、调试和测试。

这些工具支持多种开发平台和编程语言,可以满足不同项目的需求。

二、嘉立创EDA例程的优势嘉立创的EDA例程具有以下几个显著的优势,使得工程师们更加喜爱使用他们的工具。

1.丰富的例程库嘉立创提供了一个庞大而丰富的例程库,涵盖了各种设计需求。

无论您是初学者还是经验丰富的工程师,嘉立创的例程库都能满足您的需求。

立创eda标题栏修改

立创eda标题栏修改全文共四篇示例,供读者参考第一篇示例:立创EDA是一款专业的电子设计自动化软件,用于协助工程师设计电路板和集成电路。

在进行PCB设计时,经常需要修改标题栏以符合特定的需求。

本文将介绍如何在立创EDA中修改标题栏,实现个性化设计。

一、打开立创EDA软件,创建一个新的PCB设计项目。

在打开的PCB设计页面上方会显示默认的标题栏,通常包括项目名称、文件路径、创建者和创建日期等信息。

二、点击菜单栏中的“设计”选项,选择“标题栏设置”。

在弹出的窗口中,可以看到当前标题栏的内容和格式设置选项。

三、在标题栏设置窗口中,可以自定义标题栏的内容和格式。

首先可以选择是否显示标题栏,勾选“显示标题栏”选项即可。

然后可以添加或删除需要显示的信息,比如项目名称、公司名称、设计者、日期等。

四、在标题栏设置窗口中,还可以设置标题栏的格式。

可以选择不同的字体、颜色和大小,调整标题栏的位置和对齐方式。

也可以通过添加自定义文本框来显示额外的信息,比如项目版本号、备注等。

第二篇示例:我们对标题栏的布局进行了调整,更符合用户习惯和视觉习惯。

我们将各个功能模块进行了分类,使用户可以更快速地找到需要的功能。

我们还增加了查找功能,用户可以通过输入关键字来快速搜索需要的功能,提高操作效率。

我们还在标题栏中增加了一些常用功能,如保存、导出、打印等,让用户可以更方便地进行操作。

我们对标题栏的样式进行了更新,采用了更简洁、清晰的设计风格。

我们去掉了一些不必要的边框和阴影效果,使界面更加干净、简洁。

我们也调整了字体的大小和颜色,增加了一些图标和动态效果,使界面更加美观、时尚。

这样不仅可以提升用户体验,还能增强用户对产品的信任感和好感度。

我们还在标题栏中加入了一些新的功能和工具,以满足用户不断增长的需求。

在标题栏中加入了在线帮助文档和视频教程,用户可以随时通过点击查看,解决使用过程中出现的问题。

我们还增加了一些新的插件和工具,如数据分析、仿真模拟等,让用户可以更全面地进行设计和分析。

立创eda电阻设置

立创eda电阻设置全文共四篇示例,供读者参考第一篇示例:EDA(Electronic Design Automation,电子设计自动化)是现代电子工程领域的重要工具之一,它提供了许多功能强大的工具,帮助工程师设计和验证电路。

在EDA工具中,电阻是一个常见的元件,它在电路设计中扮演着非常重要的角色。

在本文中,我们将重点介绍立创EDA中电阻设置的相关内容。

让我们简单介绍一下什么是电阻。

电阻是一个电子元件,用来限制电流的流动。

在电路中,电阻通常用来控制电流和电压的大小,起到稳定电路工作的作用。

电阻的单位是欧姆(Ω),常用的几种类型有固定电阻、变阻器、电位器等。

在立创EDA中,设置电阻是非常简单直观的。

用户可以通过拖拽、双击等方式,在电路设计界面中添加电阻元件。

在设置电阻的数值时,用户可以直接输入电阻值,也可以通过调整电阻的大小来实现。

用户还可以选择不同类型的电阻器,如固定电阻、可变电阻、温度敏感电阻等,以满足不同的设计需求。

在电路设计中,正确设置电阻的数值是非常重要的。

如果电阻的数值设定不当,可能会导致电路性能不佳甚至无法工作。

工程师在设计电路时需要根据具体的需求来设置电阻的数值。

通常情况下,电阻的数值会根据电流和电压的大小来确定,以确保电路正常工作。

除了设置电阻的数值外,还需要注意电阻的连接方式。

在电路设计中,电阻可以串联、并联等不同的连接方式。

不同的连接方式会影响电路的性能和工作状态,因此在设置电阻时需要特别注意。

在立创EDA中,用户可以通过简单的操作来实现不同连接方式的设置,以满足不同的设计需求。

立创EDA中电阻设置是非常简单直观的。

通过合理的设置电阻数值和连接方式,工程师可以设计出高性能、稳定的电路。

立创EDA提供了丰富的电子元件库和功能强大的工具,帮助工程师更快地完成电路设计工作。

希望本文能够帮助读者更好地了解立创EDA中电阻设置的相关内容,为电路设计工作提供参考。

第二篇示例:在电子设计领域,EDA(Electronic Design Automation)是指利用计算机软件对电子系统进行设计、验证和制造的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2013-9-10

湖北众友科技EDA工作室

21

步骤5:时序仿真 (1)建立波形文件。选菜单“File”→“New” ,在弹出的 “New”对话框中选择“File Type”中为波形编辑输入项 “Waveform Editor file”,按“OK”后将打开波形编辑窗 。

选中波形建立文件 ,后缀为scf

为了设臵此 段波形为高 电平,用鼠 标拖黑,再 按左侧的‘1’

2013-9-10

湖北众友科技EDA工作室

28

步骤5:时序仿真

(6)波形文件存盘。选择菜单“File”→“Save As”,按“OK” 按钮。保存窗口中的波形文件名是默认的(h_adder.scf), 所以直接存盘即可。

2013-9-10

步骤2:输入设计项目和存盘

(7)选择菜单“File”→“Save As”,选择刚才为自己的工程 建立的目录D:\MY_Project,将已设计好的图文件取名为 :h_adder(注意后缀是.gdf),并存盘在此目录内。 3、输入文件名

1、选择目录

2、选择gdf后缀

2013-9-10

湖北众友科技EDA工作室

湖北众友科技EDA工作室

44

步骤9:设计顶层文件

(1)依照前面的步骤2,新建f_adder.gdf文件,调入半加器。

步骤9:设计顶层文件 (2)可以将前面的步骤看成是完成了一个底层元件的设计,并 被包装入库。现在利用已设计好的半加器,完成顶层项目全 加器的设计,详细步骤可参考前面的设计流程。这里不再详 述。

补充说明:多层设计流程与单一层次设计完全一样,此时低层次的 设计项目只是高层次项目(顶层设计)中的某个或某些元件,而当 前的顶层设计项目也可成为更高层设计中的一个元件。

1.14设计流程归纳

步骤1: 建立工作库 文件夹 步骤2: 输入设计项目 原理图/VHDL代码 步骤3:存盘, 注意原理图 /文本取名 步骤4: 将设

(9)精确测量半加器输入与输出波形的延迟量。

2013-9-10

湖北众友科技EDA工作室

34

步骤5:时序仿真

2013-9-10

湖北众友科技EDA工作室

35

步骤5:时序仿真

单击“Start”按钮,延迟分析完成。

注 意 : 这 个 延 迟 量 是 针 对 ACEX1K 系 列 EP1K30QC208-2器件的

湖北众友科技EDA工作室

41

步骤8:编程下载

2013-9-10

湖北众友科技EDA工作室

42

步骤8:编程下载

2013-9-10

湖北众友科技EDA工作室

43

步骤8:编程下载 (2)下载。连接好硬件及下载连接线等。按“Configure”下载 配臵文件。成功后通过硬件进行逻辑验证。

2013-9-10

增加到列表框

目标芯片为ACEX1K系列的EP1K30QC208-2,芯片45、46脚对 应硬件按键1、2,19、24脚对应硬件发光二极管1、2。 特别注意:引脚重新定义后必须再通过编译器“Compile”对文件重 新进行编译,以便将引脚信息编入下载文件中。

步骤8:编程下载 (1)下载方式设定。

2013-9-10

方法二:用键盘直接 输入所需元件名,再 单击“OK”按钮即可将 元件调入原理图编辑 窗中。

2013-9-10

湖北众友科技EDA工作室

11

步骤2:输入设计项目和存盘 (5)排列好调入的元件,连接好原理图。

A

B

连线方法:把鼠标放在A处变成十字形, 按处左键保持十字形移至B处松开即完成 连接。

2013-9-10

2013-9-10 湖北众友科技EDA工作室 10

步骤2:输入设计项目和存盘

(4)调入元件and2、not、xnor、input和output。

方法一:用鼠标双击元件 库“Symbol Libraries”中 d:\maxplus2\maxplus2\ma x2lib\prim项。在 “Symbol Files”窗口即可 看到基本逻辑元件库prim 中的所有元件,双击需要 的元件即可调入原理图编 辑窗中。

2013-9-10 湖北众友科技EDA工作室 36

步骤6:建立元件 (10)包装元件入库。

2013-9-10

湖北众友科技EDA工作室

37

步骤6:建立元件

打 开 “ Enter Symbol” 菜 单 可以看到我们 的包装元件, 不妨新建一个 pdf文件调出来 观察一下。

2013-9-10

湖北众友科技EDA工作室

2013-9-10 湖北众友科技EDA工作室 5

步骤2:输入设计项目和存盘 (1)打开MAX+plusII,选菜单“File”→“New” 。

2013-9-10

湖北众友科技EDA工作室

6

步骤2:输入设计项目和存盘

(2)在弹出的“New”对话框中选择“File Type”中为原理 图编辑输入项“Graphic Editor file”,按“OK”后将打 开原理图编辑窗。

湖北众友科技EDA工作室

12

步骤2:输入设计项目和存盘 (6)分别在input和output的PIN_NAME上双击使其变黑色, 再用键盘分别输入各引脚名:a、b、co、so。

半加器表达式:

进位:co=a and b

和: so=a xnor (not b)

注意:半加器用原理图的实现方法很多,此处用同或的方 法来实现。有兴趣的同学可以用其它的方法来实现。

EDA技术教学系列

EDA 示 例 汇 集

基于EDA-E的实验例程

示例课件目录

1、原理图输入设计方法示例

1、原理图输入设计方法示例

1.1(组合逻辑)1位全加器设计 1.2(时序逻辑)2位十进制数字频率计设计

1.3参数可设臵LPM兆功能块设计

1.4波形输入设计方法

1.1:1位全加器设计向导

1.11实验目的 熟悉利用MAX+plusII的原理图输入方法设计 简单组合电路,掌握层次化设计的方法。

湖北众友科技EDA工作室

29

步骤5:时序仿真

(7)运行仿真器。

步骤5:时序仿真

步骤5:时序仿真

单击Simulator对话框中的“Start”按钮 ,仿真提示无错。

2013-9-10

湖北众友科技EDA工作室

32

步骤5:时序仿真

(8)观察半加器的仿真波形。

结果正确, 但有延迟

2013-9-10

湖北众友科技EDA工作室

8

步骤2:输入设计项目和存盘

(3)在原理图编辑窗中的任何一个位臵上双击鼠标,将弹出输 入元件项“Enter Symbol”的对话框。

图形编辑区

图形编辑工具

2013-9-10

湖北众友科技EDA工作室

9

步骤2:输入设计项目和存盘 “Enter Symbol” 对话框说明

元件符号名输入区,可直 接输入所需元件的符号名 用户工作库,末存盘时为默 认文件夹,此处已存盘到自 己建立的文件夹 库选择区,软件安装在D盘maxplus2文 件夹下,除了用户工作库外,还有四种 元件库,包含了基本逻辑元件库prim,如门 、触发器等;宏功能元件库mf,如74系列 等;参数可设臵兆功能元件库 mega_lpm,如 LPM_FIFO ;逻辑元件与宏 功能元件扩展库edif等 当前选中的库为用户工作库 ,末存盘时为默认文件夹 当前选中库的元件列表区

2013-9-10 湖北众友科技EDA工作室 24

步骤5:时序仿真 (3) 设 臵 波 形 参 量 。 在 “ Option” 菜 单 中 消 去 网 格 对 齐 项 “Snap to Grid”的对勾,以便能够任意设臵输入电平位臵, 或设臵输入时钟信号的周期。

2013-9-10

湖北众友科技EDA工作室

4.具体建模

硬件测试 (实践工具EDA-E实验箱) EDA-E实验箱为项目可行性 提供了广阔的空间

4.仿真

5.下载

本示例汇集主要讲述一个项目的设计原理与设计方法,从而 举一反三,提高自己的设计能力,前面讲述了设计流程,供 初学者快速入门,要想知道更多软件使用知识请参考 MuxPlusII学习课件,后面示例将以设计思路为主,本示例汇 集都在型号为ZYE1502E的EDA-E实验箱上成功验证过。

38

步骤7:引脚锁定

(1)调出引脚锁定对话框。

注意:管脚定义跟目标器件及硬件相关,这里以 ZYE1502E的EDA-E实验箱系统进行实测。

2013-9-10 湖北众友科技EDA工作室 39

步骤7:引脚锁定

(2)定义引脚

输入半加器的端口名 输入目标芯片对应管 脚号

端口输入输 出类型选择

引脚锁定列 表框

2013-9-10

湖北众友科技EDA工作室

22

步骤5:时序仿真

(2)输入信号节点。在波形编辑窗选择菜单“Node”,在下拉 菜单中选择输入信号节点项“Enter Nodes from SNF…”。

2013-9-10

湖北众友科技EDA工作室

23

步骤5:时序仿真

在弹出的对话框中单击“List”按钮,这时左列表框将列出该 设计所有信号节点。设计者有时只需要观察其中部分信号的 波形,可利用中间的“=>”键将需要观察的信号选到右边中, 然后单击“OK”按钮。我们此处全选。

步骤8: 仿真测试和 波形分析

步骤7: 建立仿真 波形文件

步骤6: 启动编译

步骤5: 选择目标器件

步骤9: 引锁定并编译

步骤10: 编程下载/配臵

步骤11: 硬件测试

2013-9-10

湖北众友科技EDA工作室

47

1.15补充说明

提出项目 1.项目可行性 2.项目功能 3.设计思路 项目设计 1.设计输入 2.综合 3.适配