61060-102中文资料

61010中文资料

61010PHOTODARLINGTON “PIGTAIL” (TYPE GS3030)Mii OPTOELECTRONIC PRODUCTSDIVISIONFeatures:• Hermetically sealed• High Sensitivity• Small Package• Suitable for High-Density PC Board Mounting • Spectrally Matched to the 62017 Series LED. Applications:• Incremental Encoding • Reflective Sensors • Position Sensors• Level SensorsDESCRIPTIONThe 61010 is an N-P-N Planar Silicon Photodarlington Transistor in a package designed to be mounted in a single-clad printed circuit board. Its large effective aperture and narrow angular response make this a highly sensitive device with minimum response to off-axis or stray light. This sensor is also available with a lead attached to the case so that it may be connected without the use of a printed circuit board. Available in custom binned to customer specifications and/or screened to MIL-PRF-19500.ABSOLUTE MAXIMUM RATINGSStorage Temperature...........................................................................................................................................-65°C to +150°C Operating Temperature (See part selection guide for actual operating temperature) .......................................-65°C to +125°C Collector-Emitter Voltage. (50V)Emitter-Collector Voltage (7V)Power Dissipation (Derate at the rate of 0.5 mW/°C above 25°C) .....................................................................................50mW Lead Soldering Temperature (3 minutes) ...........................................................................................................................240°C61010 SILICON PHOTODARLINGTON “PIGTAIL” (TYPE GS3030) ELECTRICAL CHARACTERISTICSRECOMMENDED OPERATING CONDITIONS:UNITSMAXPARAMETER SYMBOLMINBias Voltage-Collector/Emitter V CE 5 10 mAIrradiance (H) H 0.2 1 mW/cm2SELECTION GUIDEPART NUMBER PART DESCRIPTION IL Range 61010-001 Silicon Photodarlington in pigtail package, commercial version 1 to 4mA61010-101 Silicon Photodarlington in pigtail package (-55° to +125°C) with 100% screening 1 to 4mA61010-002 Silicon Photodarlington in pigtail package, commercial version 3 to 7mA61010-102 Silicon Photodarlington in pigtail package (-55° to +125°C) with 100% screening 3 to 7mA61010-003 Silicon Photodarlington in pigtail package, commercial version +6mA61010-103 Silicon Photodarlington in pigtail package (-55° to +125°C) with 100% screening +6mA。

UL 1026-中文版

UL 1026前言A.此標準包括目錄範圍內覆蓋UL公司產品后續服務的基本要求, 這些要求是基于成熟的工程原理, 研究, 測試記錄現場試驗及生產安裝問題的認識, 從廠家, 用戶, 檢驗機構其它專業經驗咨詢時所獲取的信息, 如有必要他們可以進一步實驗調查后改正.B.此標準的觀察要求是持續保證生產廠家產品的條件之一.C.按這些要求在檢查或測試產品時, 只要產品符合此標準, 即使發現預料的其它安全損害, 也可視為符合標準.D.產品采用的材料或者其結構形式與此標準中的要求有些區別, 那么可以按照設計要求測試, 如果大部份材料相同, 那么就可以按照標準進行判斷.E.UL在按照目標進行功能演示時, 不能下放廠家或其它任何部門的責任, 標準在制定時, UL的意見和調查研究結果, 已經代表了專業評判標準, UL對任何使用或依賴下標準不負任何責任, UL不會發生任何責任義務損害, 包括由于使用, 解釋或依賴此標準產生的重大損壞.F.按照UL要求進行測試時有一些不可避免的損害, 因此在進行測試時采取足夠的安全措施和足夠的防護工具是必要的.1.範圍1.1.這些要求覆蓋了在普通情況下使用的250V或以下的家用廚具電器(除了1.2里有說明外),包括臨時或永久地在戶外使用的家用廚具電器應符合國際電器條例規定.1.2.這些要求不包括家用電器系列, 電極型, 長柄鍋及電炸鍋, 乳酪機鍋, 面拖油炸機, 爆谷機, 咖啡壺, 電飯鍋, 微波爐, 以及按個人要求制作的電器不包括在此標準內.1.3.以下內容中, 確定是否符合此範圍內的一種裝置的要求(如多士爐和類似的)應通過具體參考此型號要求, 在沒有具體參考資料時,如果采用"符合"條款, 那么條款應為公認符合標準所有型號的要求.1.4.產品包括外形特點, 零件, 系統更新及與此標準要求有區別的產品,而涉及到火險, 電擊, 傷人應該使用適當的附加零件進行測試, 其安全水平的最后結果應保留在標預期的範圍內, 產品外型, 特性, 零件, 材料, 系統與具體要求相衝突, 不能視為符合此標準, 如果考慮提出修改要求, 應采用一致的方法, 開發, 修正, 執行此標準.2.組合件.2.1.除2.2說明外, 此標準中產品組合件應符合組合件的要求, 如產品一般使用標準組合件清單索引A所示.2.2.組合件不需要與具體相符是:a.此標準包括的產品應用中不必涉及到外形或特性.b.由此標準要求代替.2.3.組合件應在認可的設計環境下使用.2.4.結構中的些特殊組合件不全面或限制其性能發揮, 這些組合件只能在限定環境下使用, 例如不超過一定限定溫度下使用且只有在認可的選定環境下限制使用.3.裝置的測量:3.1.指數必須說明, 括號里的指數為解釋或相近信息.4.參考材料4.1.此標準要求的條例或標準的任何要求更新應被解釋為最新的條例和標準.結構5.總則.5.1 如果電器在運行時會產生或在有氣體或其它氣體壓力下運行, 考慮到爆炸事故的可能性, 因此電器不能算合格, 除非電器有足夠強度抵禦爆炸危險.6.框架與外殼.6.1.電器的框架和外殼應該足夠的張度和鋼度抗拒正常使用中可能的濫用, 但不要因電器固有的抵抗強度而減少電器的空間, 產生松動, 零件錯位而導致部分或全部失效或者結構組合時而增加火險, 電擊或傷害的危險.6.2.電器外殼材料應該能夠隨特殊用途, 能夠容納所有電器零件, 除電源線和14.3,14.4中在任意環境下使用時可能會引起火險, 電擊或傷害的裸線元件外, 如果電器要與電源永久聯接時, 電器外殼應提供用于安裝所必需的裝置, 如: 托架, 挂鉤或類似物.6.3.在正常工作狀態中需要加油的電器, 應特別考慮在烹調腔上加一個外殼, 外殼的材料也應適合此目的.6.4.電器外殼采用通風開口或在外殼上安裝永久電源聯接元件的電器,其位置不能讓排氣進入封閉結構的空間, 如活動頂的空間, 壁洞空間或類似空間.6.5.判斷電器外殼性能時應考慮的因素是:a.物理強度.b.抗衝擊強度.c.吸水汽性.d.可燃性.e.防腐蝕性.f.在高溫下抗變形能力, 外殼在正常和非正常情況下使用的承受能力.對于非金屬材料外殼要求可參考<<電氣設備評估>>UL746C的聚合物標準, 金屬外殼零件或外殼應按照<<金屬外殼衝擊測試>>42節進行抗衝擊能力測試.例外情況1. 考慮按UL746C進行濫用和惡劣條件測試時, 電器外殼應按此標準中濫用運作測試的第44節進行判斷.例外情況2. 因加硬化材料要按43.1要求在高溫下連續1000小時老化測試, 所以加熱硬化材料不需要符合UL746C要求..06.6.采用過熱保護的熱塑外殼電器, 如果采用94HB材料, 具有至少60弧抵抗高電流弧光點火, 至少7秒鐘抗熱點火, 及外殼所有零件包括, 肋骨, 煎件或類似零件相距至少1/2" (12.7mm)那么可燃性要求可不一定要符合UL746C.6.7.除非電器外殼如6.5和6.8判斷認為合格, 否則電器外殼的鑄造和鐵片部分厚度不能小于表格6.1所示.6.8.除了考慮6.5中所提及的因素外, 考慮到電器的設計用途, 外殼金屬片也要考慮其尺寸, 形狀, 厚度和特殊應用能力.6.9.為防止發生無意識與導電零件接觸, 電器上的導電零件, 除自動焗燼裸線元件的發光部分以外, 其位置或包起來保護, 絕緣馬達刷帽不要求額外附件.表6.1金屬外殼的最小厚度6.10外殼構造應該讓熔化金屬, 防火物, 或類似物不會落在支撐面上6.11在6.10必須要求中, 外殼底部開口處的上面或下面必須有隔板, 如果開口為:a.在馬達下面時應:1).馬達的結構零件或電器提供類似的隔板.2).馬達在以下缺陷條件下通電時, 馬達這種保護措施是為了防止燃燒絕緣物或熔化物落在電器的支撐面上.i) 開主線圈.ii)打開起動線圈.iii)啟動短路關.iv)永久分開電容器的馬達為短路電容器, 在馬達通電前和回轉輪被堵時進行短路通電.3).采用熱發動機保護器(同時感應溫度和電流的保護裝置)的發動機是防止發動機線圈在最大負荷的內溫度不超過125℃(302ºF).4). 采用的馬達符合阻抗馬達要求.b.在電線下, 除非電線符合電線, 電纜, 伸縮線UL1581參考標準VW-1燃燒測試或者垂直燃燒測試.c.在無蓋開關, 變壓器, 螺線管或類似物下面, 除非馬達零件不會因為著火而引起故障.d.在電場和工廠制造的拼接過載, 過載電流保護裝置.例如: 如圖6.1D線所示, 如果開口不在組合件下面範圍內, 可以不用隔板.圖6.1隔板呎吋與位置A-隔板遮蓋的範圍,如果組合件沒有被遮蓋,則由整個組合件組成和一個組合件未遮蓋部份(被組合件外殼遮蓋的部份)組成.B-投影在水平板上組合件的輪廓C-隔板傾斜線軸軌跡最小範圍,傾斜線總是1)與零件的切線2)與垂直線5度,和3)水平面的定向軌跡是最大的D- 為隔板最小範圍和位置(水平位),範圍包括傾斜線C和隔板水平面軌跡交叉線6.12於6.11中所提及的擋板應是a)金屬,陶瓷,或作為外殼符合6.5可以接受的原料.b)水平的c)位於圖6.1指示的位置,不應小於圖6.1所描述的位置.6.13 如果在圖6.2中說明的探針通過開口插入不能接觸能引起水險或電擊的任何非常絕緣帶電部件,則在外殼中的開口有小於1英吋(25.4mm)的較小呎吋是可以接受的.探針在插入前、後及過程中適用於所有可能連接的位置.6.14如果在外殼內部沒有非絕緣體或用膠膜包裹的電線,則如圖6.3說明的外殼開口最小呎吋為1英吋或更長一點是可以接受的.R表示至開口周圍里邊的距離,X表示至開口平面的距離,T等於外殼的厚度,R等於X 加T,X等於能插入開口圓桿最大直徑的5倍,但不小於6-1/16英吋(154毫米).在測定開口的過程中,任何在容積範圍內的擋板是可以被忽略的,除非它持續橫切容積邊緣.6.15為了恆溫器的調整或類似的行動,如果在外殼上作一個引起用戶註意的任意大小的孔,不能破壞絕緣體或用直徑為1/16英吋(1.6毫米)插通過孔接觸非絕緣體.6.16關於在6.9和6.13-6.15中的要求,在電器的檢查過程中,外殼的任何部份可被忽視(打開或移動)那是受到的保護能防止電擊或傷人的部份.或如果a)外殼用或不用工具打開或拆卸以執行制造商推薦的用戶服務、維修、操作調整.配件連接或其它操作.b)不用工具能打開或拆卸,見6.16.1例外:如果電器標記與54.9一致,外殼的一部分要求用工具打開或拆卸以執行制造商推薦的用戶服務、維修、操作調整、配件連接或其它操作以保持保持其位置.6.16.1關於6.16(b),為确定外殼或外殼的一部份要求使用工具打開或移動,依靠非金屬部件機械穩固的外殼或外殼的一部份,如塑膠挂耳或快速連軸節插人物或插桿應遵照42A節非金屬外殼緊固器測試.例外:完全通過金屬緊固器(如鏍絲或鉚釘)穩固外殼或外殼的一部份到其它外殼部份,則不需經受此測試.6.17任何活動零件, 例如馬達回轉輪, 鏈條, 滑輪, 帶子和齒輪應褢起來或監視以減少對人的傷害.6.18參照6.17要求, 外殼的保護程度取決于總結構和電器的用途, 以下為判斷裸露活動零件能力應考慮的因素.a.外殼強度b.活動零件的銳利程度.c.無意識與導電零件接觸可能性.d.這些零件移動的速度.e.手指, 手臂或衣服被卷入活動零件的可能性.6.19外殼上的門或蓋上應有手柄以確保進入關閉位置6.20為方便更換過蠛保護裝置或當有需要開蓋操作保護裝置, 外殼上的門或蓋應用絞鏈連接.這些門或蓋應有插銷, 配合緊湊或與外殼表面開口有重壘.6.21電器零件無需用特別工具(不是服務人員就難得到的工具)如果是由人工操作, 調節或定期維護的電器.6.22如果試管或燈泡壞了會嗇火險, 那熱偶的燈泡或毛細管應可以保護電器不被破壞.7組裝7.1 如果電器上有開關, 可連接插頭型插座或插頭型連接器安裝要可靠防止因表面摩擦而使零件產生反轉(動).7.2 為防止裝柄開關轉動可采用鎖墊圈.7.3如果導電零件因附重壓而轉動或轉移而減少零件之間空間低于26.1.1.1-26.1.1.4的要求, 那么導電零件應固定在基面上.7.4 防止導電零件轉動或轉移, 導電零件之間的表面不能產生摩擦可使用鎖墊圈.8. 穩定:8.1 電器的穩定性, 不能因正常使用情況電器很容易傾倒.8.2 家用烹調或熱電器可以輕易用手提或搬運(如矮電器, 食品加熱器或類似的)電器裝上至少50盎司(148ml)水, 加熱到115ºF(46ºC)溫度, 放在與水平面15º的傾斜面上, 無論裝上全部的拆分件, 液體或其它材料, 電器應符合設計使用的最大傾斜角傾倒要求, 電器不會產生滑動, 不能因測試而傾倒.9. 防腐蝕保護9.1 如果因未保護零件的故障增加著火或電擊危險的鐵和鋼片應以瓷釉法, 鍍鋅,電鍍或其它的方法以保護.例外: 某些設備中的氧化鋼不會因為金屬暴露在空氣, 水汽或其它氧化而影響使其加快氧化的金屬其厚度和溫度也是考慮因素, 無需保護, 外殼內金屬片表面要求防腐蝕保護. 鑄壓零件不要求防腐蝕保護, 采用保護套的加熱件和直接連接加熱件的終端零件不需防腐蝕保護.9.2 電器里電鍍或其它處理具有老化性質的零件不能在最后壞至電器不能使用的程度.10. 電源聯接10.1 永久性連接電器10.1.1總則10.1.1.1除10.1.1.2中注明外, 電器采用永久電源聯接設計, 應符合國際電器條例ANSI/NFPA No.7-1993要求.10.1.1.2如果采用活動短電線和可連接插頭作為電源聯接的電器, 可以固定在特點空間. 這種特征的電器還應考慮到電器的應用性, 和電器可連接電源插頭應容易拆開.10.1.1.3 電器按設計要求安裝以后, 終端的位置或永久聯接電器與電源隔板的這些聯接應檢查方便.10.1.1.4 聯接電源保護管的終端間隔與電器的聯接不會產生轉動. 10.1.2 電場電線終端.10.1.2.1 永久聯接電源電器應該采用電線終端或當電流量不低于電器電流量, 連接導體的安載流量不少于電器電流的125%時, 負載邊3小時或以上時這時負載將時斷時續.10.1.2.2 為符合這些要求, 電路終端應為電源接頭或當電器安裝時現場聯接控制.10.1.2.3 電線終端應采用焊接接合, 或可以將電線聯接器牢固地壓入合適位置(如用插銷或螺釘穩固)如果向上接合或類似方法使電線固定, 電線終端容納10AWG(5.3mm2)或更小的導體可以采用線綁螺釘固定.10.1.2.4 電線終端應防止轉動或旋轉, 除表面摩擦外, 可以用兩個螺絲,鉚釘或其它類似方法固定.10.1.2.5 電線終端上的線綁螺釘不能小于10號, 除8號螺釘可以使用在14AWG(2.1mm2)或更小導體的終端聯接中, 6號螺釘可以使用在16AWG(13mm2)或更小的控制電路導體中.10.1.2.6 叩入綁線螺釘的終端金屬片不能小于0.050”(1.3mm)除叩擊螺紋線有相同的機械強度可用于小于0.030”(0.8mm)厚度的金屬上. 如果需要螺紋線伸出金屬上可用雙根螺紋線.10.1.2.7 突出接合處或杯形墊圈可保持導體的能力如果其尺寸為10.1.2.1在螺帽或墊圈下的導體不能小于14AWG(2.1 mm2)10.1.2.8 線綁螺釘應穿入金屬中.10.1.2.9 接地電源導體聯接的電器應:a.Edison螺帽型的燈頭或元件容器.b.單柱開關, 或c.單柱自動控制應有一個終端或頭以確認電源電路接地導體. 除在24.2中說明外, 終端或頭到燈頭或元件容器的螺帽殼視為一個整體, 不是聯接到單柱開關或單柱自動控制器.10.1.2.10 接地聯接電路導體的終端應用白色金屬制成或鍍成白色, 使之非常容易與其它終端與辨出來, 或以其它方法使之容易分辨,如在線路圖上標注, 接地電路導體的頭也要用白色或灰色, 使之與其它頭容易分辨.10.1.2.11 除10.1.2.12說明外, 內部的插座盒或電線間隔長度應為6"(152mm)或以上, 如果頭聯接電場與電路外圍.10.1.2.12 如果有跡象顯示, 使用長頭可能導致火險或電擊, 頭的長度可以少于6"(152mm).10.1.2.13 只聯接設備接地導體的絕緣頭的表面, 應用涂上綠色或黃綠相間的斜帶, 其它頭不必如此.10.1.2.14 聯接設備接地導體的六角形, 溝槽形或都是的綁線螺如應為綠色, 聯接這種導體的壓力電線聯接器應標記"G" "GR""GROUNDING"或類似的或標記在加熱電器上的線路圖里, 以便于區分, 綁線螺絲或壓力電線聯接器位置在電器維護時不會被移動.10.1.2.15 只聯接接地設備導體的終端應能確保特殊電器導體的適當尺寸.10.2 線聯接電器10.2.1 總則10.2.1.1線路聯接電器(用伸縮線路聯接電源電路的一種電器)應有一根電源線聯接電源電路或應有容納可拆或電源線的雄針終端,連接線或分拆線的長度按10.1所示.10.2.1.2線路聯接電器的線路電流量和電壓, 配件不能小于電器的標準, 當電器負載續運行3小時或以上時, 聯接插頭電流量不能小于125%電器電流量.10.2.1.3 電器中的可連接伸縮線和在可拆開電源線的型號應按10.2表格所示, 或其特性至少應能適應特定用途.10.2.1.4 當燒烤器使用在焗爐里時, 焗爐應采用可拆式或電源線, 焗爐和燒烤器都應采用無附件可拆式電源線.10.2.1.5 加強絕緣, 如果采用伸縮線長度不能超出電器外1/2"(13mm)如超出此長度, 應采取機械保護, 防止磨損或松脫, 減少拉緊力產生的不利影響.10.2.1.6 電器不能采用A3-2線制, 接地型接頭.10.2.1.7 15-20A電源線連接插頭的電器一般用3線接地型插座, 開合電器采用的電源線可聯接插頭應該可手工操作, 線聯單柱開關,或是極化或接地型螺口燈座燈柱.10.2.1.8 采用線接地型聯接插頭或2線型極化聯接插頭應符合圖10.1,伸縮極化確認應符合表格10.3要求.10.2.1.9 接地電源導體以下因素也要考慮在里面.a.螺口燈座柱的螺絲殼.b.插座接地終端或頭.10.1為接地電源線確認表.10.2.2 緩解拉力10.2.2.1 緩解拉力應防止聯接伸縮電源線上的機械力傳至終端, 絞接處, 或內線上.10.2.2.2 如果使用材料, 壓力板或其它纖維確保拉力緩解裝配, 纖維材料應用別針, 固定螺釘或其它有效方法予以固定.10.2.2.3 應采用一些措施防止聯接伸縮線通過線入口被壓入電器外殼里面, 確認是否符合此要求, 電源線或頭應按照Push-BackRelief40節A進行測試.10.2.2.4 用電線夾綁緊軟皮線,任何表面可以自由從,邊緣,批鋒,以便導致絕緣導電體擦損.10.2.2.5 當測量結果與10.2.2.6相符時, 伸縮線上的壓力緩解結在斷開電源狀態下以35Lbf(156N)拉線, 應能支撐1分鐘, 無錯位.10.2.2.6 電器結構的電線允許特定力量和從不同角度的拉線. 導體的斷開點, 結果顯示電線移動有足夠連接力.10.2.3 終端針10.2.3.1 如果電器采用終端針, 電器把插頭插在針上時或插上后, 不能使導電零件產生無意識的接觸.10.2.3.2 針護套要求如a.直線邊緣放在任何位置,交叉,與連接插頭開口(插頭沒有插在里面)邊接觸時, 不能與通電的終端針接觸.b.插頭與指針在同一條直線, 板上的插頭與未端或與通電指針成直角,當管道插入任何位電器的開口時, 管道(如圖6.2)不能接觸任何通電指針.10.2.3.3 符合10.2.3.2(b)要求的插頭可以隨附電器.10.2.3.4 采用3個以上的針終端, 并覆蓋所有的指針的電器插頭, 終端的空間不能容納一個熨斗插頭或線聯插頭或導體主體, 這些插頭針應適應于特定電器.10.2.3.5 如果電器采用用戶可拆加熱元件, 這些加熱元件應有如下保證:a.安裝可靠安全耐磨和b.加熱針防止被破壞, 縮短, 當在插入或拆出和彼此更換位置時.10.2.3.6 針終端應安全, 嚴格安裝防止摩擦而產生位置更換.10.2.3.7 10.2.3.6的要求主要是提供空間維護, 說明如26.1.1.1表格26.1和26.2里, 針終端之間保持適當空間. 在此要求中, 還要考慮保持鎖住終端的緊密性方法.10.2.3.8 針的尺寸, 中點與中點之間的距離, 包括一般使用插頭的接觸片之間的相應空間, 采用這些針的規格如10.4所示.10.2.3.9 采用兩針終端的電器不能使用可拆三導體或電源線作為接地導體.10.2.4 杯士10.2.4.1 軟皮線在通過牆隔板或密封盒的任一點時,將有一個杯士或相等同的固定,應光滑,圓渾的表面,如果SP-2, SPT-2型或采用其它比HSJ型輕的伸軟皮線, 如果牆或隔板為金屬, 軟皮線可能要承受拉力或移動時, 絕緣的杯士, 特殊用途的電器套管采用的材料應能隔熱, 抗水汽的特性.10.2.4.2 如果線孔是木材,陶瓷,電木粉成份或其它不導電材料構成,套管的表面應光滑, 圓渾相等同的杯士.10.2.4.3 絕緣套管通常可采用陶瓷材料和一些鑄模結構, 但不能采用,木材, 熱模紫膠, 瀝青, 橡膠等材料的單套管. 如果套管厚度不小于3/64"(1.2mm)在一般水汽條件下不會產生不利影響可采用硬化纖維材料.10.2.4.4 單個的軟橡膠, 氯丁橡膠管套可采用在馬達框架上或邊接馬達的容器外殼(除10.2.4.5說明外不能使用在電器其它地方)且:a.套管厚度不能少于3/64"(1.2mm)b.套管位置不能暴露在油, 油脂, 油性氣體或其它對化合物有破壞影響的物質中.10.2.4.5 如果絕緣連接導管伸縮線無型號要求, 10.2.4.4中所提及的套管的任何材料可以使用在電器中任何部位, 安套管洞口邊光滑無毛邊, 鰭或類似物時.10.2.4.6 如果使用的絕緣材料厚度少于1/32"(0.8mm), 能完全填住安裝金屬的孔眼, 絕緣套管里可以采用絕緣金屬墊圈.11. 通電零件.11.1每一個通電零件所采用的材料應適合特殊用途.11.2通電零件可用抗腐蝕合金做成(如不鏽鋼)不能用普通鐵和鋼做成, 除非這些材料經過表面處理及產生抗腐蝕能力, 即使這樣也適用于:a.針終端b.終端零件, 馬達的其它零件, 馬達控制器.c.正常溫度下操作時超過100°C(212°F)的零件.d.鍍膜鐵和鋼件局部的部件要求參照2.1節所示.11.3 帶水槽的電器, 所有的活動零件其位置或要保護起來而不會因為水槽壞了而掉下來, 除非:a.水槽能抗使用液體腐蝕, 和b.水槽不會因老化而破裂.12. 內線12.1 總則12.1.1電器的內線尺寸, 型號應適用于特殊用途, 并考慮以下特性:a.電線可能承受的溫度和電壓.b.暴露在油或油脂中, 和c.可承受的其他環境.12.1.2玻璃纖維, 無機材料或類似材料作為導體絕緣材料無溫度限制.12.1.3電器內部采用的熱塑絕緣電線應為標準的建築電線, 混合電線或適用于特殊用途的電器電線材料.12.2 電線保護12.2.1線路和零件之間的聯接應予以保護或封閉, 除外部聯接的伸縮線外, 或因為電器使用時可能暴露內部聯接, 線路必須是活動的除外, 絕緣的裸導體或帶珠導體不能在外殼外使用.12.2.2穿過電器外殼開口處而露出的內部線路的保護要求如122.1當認為有鍍膜需要的線路應符合6.9-6.13要求. 內部線路在外殼內不會承受壓力或機械損壞可不需要保護.12.2.3如果電器線路的位置可能靠近可燃材料或機械傷害的線路要用彩盔甲電線或在鋼管, 電子金屬管, 金屬保護里, 或其它保護..12.2.4外殼, 零件, 保護管或類似物內的線路其位置或被保護, 而不會因為接觸任何粗糙, 尖銳或活動零件而損壞導體的絕緣體. 12.2.5絕緣電線通過電器外殼內金屬牆洞口時, 應用一根光滑的導管,或電線通過的表面應光滑圓渾, 以防止絕緣體被擦壞. 如12.2.1用伸縮線作內, 外聯接應按照10.2.2.1-10.2.2.6和10.2.4.1-10.2.4.6進行拉力解緩和采用套管, 除非伸縮線的結構可抗拒拉力和移動, 例外10.2.6 絕緣電線可以扎成束穿過電器外殼內金屬牆洞口.12.3 絞接(疊接)12.3.1所有的絞接和聯接機械性能應可靠, 電子件接觸應應適應, 如果由于聯接的破裂或松動可能引火險或火擊時, 在確保可靠機械性能下可進行死聯接.12.3.2如果絞接處與其它金屬零件之間的距離不能永久保持, 那么絞接處也要采用與電線一樣的絕緣.12.3.3絞接處的絕緣由兩層摩擦帶, 兩層熱塑帶或一層摩擦帶在一層橡膠帶上組成, 考慮其絕緣性, 抗熱性, 抗水汽性, 絞接處絕緣材料可由纖維, 熱塑片或其它型號管子構成. 但熱塑帶不能包尖銳邊.12.3.4連接綁線螺絲和內部線路, 應絕對防止與其它任何同樣極化的導電是線接觸, 與任何死區金屬零件接觸. 可使用壓力終端連接器, 焊接接合, 折皺視孔, 氫所有的電線焊接在一塊或其它類似方法達到目的.12.4分開電路.12.4.1 總則12.4.1.1除非絕緣導體提供最高電壓絕緣, 否則電路絕緣導體分開聯接電源應用隔板隔開, 或單獨聯接電源, 除12.4.1.3說明外,電路上的絕緣導體應為單獨的或與其它不同線路導電零件和絕緣零件分開.12.4.1.2絕緣導體的分開可采用夾, 路線, 或類似能與不同電路的絕緣和導電零件永久分開的方法.12.4.1.3 任何電路的現場安裝導體應隔與….分開.a.現場安裝導體和工廠導體與其它任何電路的聯接, 除非兩個電路導體與每個電路最大電壓絕緣. 和b.電器中任何其它電路的導電零件與任何導電零件的短路將會導致火險, 和電擊, 除…1). 電場安裝導體的結構型或為T, TF型時或安裝的相似導體可。

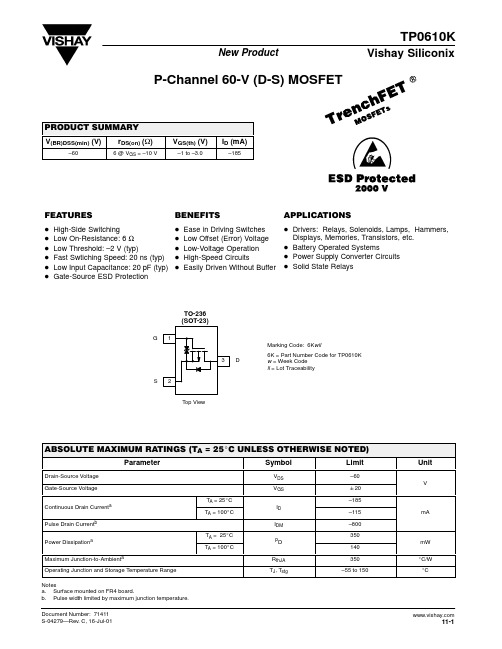

TP0610K中文资料

0.4 ID = 250 mA

0.3

0.2

0.1

–0.0

–0.1

–0.2

–0.3 –50 –25 0

25 50 75 100 125 150

TJ – Junction Temperature (_C)

Power (W)

Single Pulse Power, Junction-to-Ambient 3 2.5

0.2 0.1 0.1 0.05 0.02

0.01 10–4

11-4

Single Pulse 10–3

10–2

10–1

1

Square Wave Pulse Duration (sec)

Notes:

PDM

t1

t2 1. Duty Cycle, D =

t1 t2

2. Per Unit Base = RthJA = 350_C/W

On-Resistance vs. Drain Current 20

16

VGS = 4.5 V

Capacitance 40

VGS = 0 V 32

C – Capacitance (pF)

12 VGS = 5 V

Ciss 24

8 VGS = 10 V

4

16 Coss

8

Crss

0

0

200

400

600

800

Unit

V

mA

mW _C/W

_C

11-1

元器件交易网

TP0610K

Vishay Siliconix

New Product

SPECIFICATIONS (TA = 25_C UNLESS OTHERWISE NOTED)

610NM中文资料

5

5

5

5

5

5

5

V

Forward Current

30

30

25

30

25

30

25

mA

Forward Current (Peak)

t ≤10us

100

100

150

100

150

150

150

mA

Power Dissipation

105

120

105

120

105

105

105

mW

Operating Temperature

91

元器件交易网

LED TECHNICAL DATA

Lead Forming Guidelines

Custom Lead Options

Contact us with your requirements and specifications.

Custom lead forming

2.6

2.5

2.5

2.5

2.5

1.7

1.5

V

Reverse Current

VR=5V

10

10

10

10

10

10

10

uA

Wavelength at Peak Emmission

IF=20mA

610

620

625

660

700

880

940

nm

Spectral line half-width

IF=20mA

35

15

LED TECHNICAL DATA

Absolute Maximum Ratings

改良麦康凯肉汤基础产品说明书

化学品安全技术说明书第一部分化学品及企业标识产品中文名称:改良麦康凯肉汤基础产品英文名称:CT-MacConkey Broth Base产品编号:025180企业名称:广东环凯微生物科技有限公司地址:广东省广州市黄埔区广州开发区科学城神舟路788号邮编:510663公司网址电子邮件地址:*********************传真号码:************销售热线:************-8602技术热线:************-8877/8876推荐用途和限制用途:生化研究/分析第二部分危险性概述GSH危害性类别非危险物质或混合物GSH标签要素非危险物质或混合物其它危害(健康危害、环境危害)未见报道第三部分成分/组成信息混合物化学品成分:参考培养基使用说明。

有害物质成分:无第四部分急救措施一般信息:无特殊的措施要求。

皮肤接触:立即用清水彻底清洗。

眼睛接触:立即提起眼睑,用大量流动清水冲洗15min。

如不适就医。

吸入:如果吸入,将人员移动到新鲜空气处,如果没有呼吸,进行人工呼吸操作,并联系医生。

食入:如误食,用水冲洗口腔,如不适就医。

就医信息:出示产品使用说明或者此SDS。

第六部分 泄露应急处理个人防护:穿个人实验服,佩戴手套和口罩,避免吸入干粉。

环境保护措施:用湿布和地拖擦拭干净。

清洁/收集措施:保持干燥。

迅速清洗弄脏的区域。

第七部分 操作处置与储存安全操作注意事项:防止粉尘扬起,应提供通风设备。

储存注意事项:贮存于避光、干燥处,用后立即旋紧瓶盖。

第八部分 接触控制/个人防护职业接触限值没有已知的国家规定的暴露极限。

工程控制:提供安全淋浴和洗眼设备个人保护措施呼吸系统防护:在通风橱里称取产品,佩戴口罩。

眼睛防护:佩戴安全眼镜。

身体防护:穿实验室服。

手防护:戴防化学品手套。

其他防护:常规的工业卫生操作,工作后及时清洗双手。

第九部分 理化特性外观:粉末 pH 值: 7.2±0.2 颜色:淡紫红色 气味: 特征性 熔点:无数据资料 沸点: 无数据资料 燃点:无数据资料 闪点: 无数据资料 爆炸限度下限:无数据资料 上限: 无数据资料 热分解:无数据资料溶解性: 按产品使用说明上的用量比例加蒸馏水,加热煮沸至完全溶解,溶液呈淡紫色澄清无沉淀。

LECO 氧氮分析仪TC400耗材配件参照表中文

300–600

25-75

502-328

300–600

—

校正标样(续)

(1克/粒,454克/瓶)

部件号 ppm 氮 ppm 氧

501-643-100

15–45

15–45

钛柱标样(0.1克/粒,100克/瓶)

部件号 %氮 %氧

校正标样

钢柱标样(0.5克/粒,100克/瓶)

部件号 ppm 氮 ppm 氧

501-550

15–45

15–45

501-644 502-102

25–85 200–250

100–225 25–55

502-494

300–600

30–80

(1克/粒,100克/瓶)

represented by:

®

是力可公司的注册商标

其他国家及地区: 电话:269-983-5531 传真:269-983-3850

1/6/10

768-980 巴斯通过滤器

617-228 螺栓 需2根

772-520 O型圈 (需2片) 618-833

螺母 需2只

782-720 782-720S 782-720SHD 782-719

高温石墨坩埚

617-140 调温装置组件

775-622 接头

603-442 O 型圈

617-850 接头

(改进型)

石英 试剂管

1英寸

501-608

石英棉

501-170

稀土 氧化铜

617-083

O型圈

617-171

管子

502-304

铜棒

501-621

铜屑

772-520

O型圈

617-173

WSH610中文资料

WSH610Winson reserves the right tomake changesto improve reliability or manufacturability.Hall Effect IC with Two-Step Lock Protection andAuto-Restart FunctionFeatures:Operate from 2.8V to 20V supply voltage.On-chip Hall sensor.Internal bandgap regulator allows temperature compensated operations and a wide operating voltage range.High output sinking capability up to 600mA for driving large load. Available in rugged low profile SOT-25 , SIP-4L packages. Built-in protection diode for reverse power supply fault. Built-in 2-Step Lock protection and auto-restart function.General Description:WSH610 is designed to integrate Hall sensor with complementary output drivers and 2-Step thermal protection circuit together on the same chip. It is carefully designed to protect DC brushless motors to operate on different fault operating condition. WSH610 can detect whether motor is in locked or operating condition then trigger the low or high temperature protection to protect motor under safety operating zone. This technique allows motors to operate as high temperature as 125°C and keep motor under 80°C low temperature when motor is locked.And all above protection will be disabled when fault condition is removed and motor will be auto-restarted. WSH610 includes two open collector output drivers, each capable of sinking 600mA current load. An on-chip protection diode is implemented to prevent reverse power fault. Its 2-step protection can replace traditional lock protection and auto restart function but without EMI noise and any external components with much lower cost. The temperature-dependent bias increases the supply voltage of the hall plates and adjusts the switching points to the balance the influence of magnets at highertemperatures.WSH610 are rated for operation on wide temperature range from –20˚C to 125˚C and voltage ranges from 2.8V to 20V .WSH610Vcc=12VWSH610WSH610Operating CurrentSIP- 4L: WSH610-XPA N Elec.Grade1:A Grade (50 Gauss) NWSH610WSH610WSH610Winson reserves the right to make changesto improve reliability or manufacturability. SIP-4LWSH610。

TPS61026中文资料

(3,25 mm x 3,25 mm)FEATURES DESCRIPTIONAPPLICATIONSV O3.3 V Up To200 mALow BatteryOutputTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER2003–REVISED FEBRUARY2006 96%EFFICIENT SYNCHRONOUS BOOST CONVERTER•96%Efficient Synchronous Boost Converter The TPS6102x devices provide a power supplysolution for products powered by either a one-cell,•Output Voltage Remains Regulated Whentwo-cell,or three-cell alkaline,NiCd or NiMH,or Input Voltage Exceeds Nominal Outputone-cell Li-Ion or Li-polymer battery.Output currents Voltagecan go as high as200mA while using a single-cell •Device Quiescent Current:25µA(Typ)alkaline,and discharge it down to0.9V.It can also•Input Voltage Range:0.9V to6.5V be used for generating5V at500mA from a3.3-Vrail or a Li-Ion battery.The boost converter is based •Fixed and Adjustable Output Voltage Optionson a fixed frequency,pulse-width-modulation(PWM) Up to5.5Vcontroller using a synchronous rectifier to obtain •Power Save Mode for Improved Efficiency at maximum efficiency.At low load currents the Low Output Power converter enters the Power Save mode to maintain a •Low Battery Comparator high efficiency over a wide load current range.ThePower Save mode can be disabled,forcing the •Low EMI-Converter(Integrated Antiringingconverter to operate at a fixed switching frequency.Switch)The maximum peak current in the boost switch is •Load Disconnect During Shutdown limited to a value of800mA,1500mA or1800mA •Over-Temperature Protection depending on the device version.•Small3mm×3mm QFN-10Package The TPS6102x devices keep the output voltageregulated even when the input voltage exceeds thenominal output voltage.The output voltage can beprogrammed by an external resistor divider,or is •All One-Cell,Two-Cell and Three-Cell Alkaline,fixed internally on the chip.The converter can be NiCd or NiMH or Single-Cell Li Batterydisabled to minimize battery drain.During shutdown, Powered Productsthe load is completely disconnected from the battery.•Portable Audio PlayersA low-EMI mode is implemented to reduce ringing •PDAs and,in effect,lower radiated electromagnetic energy•Cellular Phones when the converter enters the discontinuousconduction mode.The device is packaged in a •Personal Medical Products10-pin QFN PowerPAD™package measuring3mm •Camera White LED Flash Lightx3mm(DRC).Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PowerPAD is a trademark of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2003–2006,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.ABSOLUTE MAXIMUM RATINGSDISSIPATION RATINGS TABLERECOMMENDED OPERATING CONDITIONSTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.AVAILABLE OUTPUT VOLTAGE OPTIONS (1)OUTPUT NOMINAL SWITCH PACKAGE T AVOLTAGE PACKAGEPART NUMBER (2)CURRENT LIMITMARKING DC/DC Adjustable 1500mA BDR TPS61020DRC Adjustable 800mA BNE TPS61028DRC Adjustable1800mA BRF TPS61029DRC –40°C to 85°C3.0V 1500mA BDS 10-Pin QFN TPS61024DRC 3.3V 1500mA BDT TPS61025DRC 5V 1800mA BRD TPS61026DRC 5V1500mABDUTPS61027DRC(1)Contact the factory to check availability of other fixed output voltage versions.(2)The DRC package is available taped and reeled.Add R suffix to device type (e.g.,TPS61020DRCR)to order quantities of 3000devices per reel.Add a T suffix to the device type (i.e.,TPS61020DRCT)to order quantities of 250devices per reel.over operating free-air temperature range (unless otherwise noted)(1)TPS6102xInput voltage range on SW,VOUT,LBO,VBAT,PS,EN,FB,LBI –0.3V to 7V Operating virtual junction temperature range,T J –40°C to 150°C Storage temperature range,T stg –65°C to 150°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliabilitiy.THERMAL RESISTANCEPOWER RATINGDERATING FACTOR ABOVEPACKAGE ΘJAT A ≤25°CT A =25°CDRC48.7°C/W2054mW21mW/°CMINNOMMAX UNIT Supply voltage at VBAT,V I (TPS61020,TPS61024,TPS61025,TPS61028)0.9 6.5V Supply voltage at VBAT,V I (TPS61026,TPS61029)0.9 5.5V Operating free air temperature range,T A–4085°C Operating virtual junction temperature range,T J–40125°C2Submit Documentation FeedbackELECTRICAL CHARACTERISTICSTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029 SLVS451D–SEPTEMBER2003–REVISED FEBRUARY2006over recommended free-air temperature range and over recommended input voltage range(typical at an ambient temperature range of25°C)(unless otherwise noted)DC/DC STAGEPARAMETER TEST CONDITIONS MIN TYP MAX UNITMinimum input voltage for start-up R L=120Ω0.9 1.2VInput voltage range,after start-up(TPS61020,0.9 6.5VV I TPS61024,TPS61025,TPS61027,TPS61028)Input voltage range,after start-up(TPS61026,0.9 5.5VTPS61029)TPS61020,TPS61028and TPS61029outputV O 1.8 5.5V voltage rangeTPS61020,TPS61028and TPS61029feedbackV FB490500510mV voltagef Oscillator frequency480600720kHzSwitch current limit(TPS61020,TPS61024,I SW VOUT=3.3V120015001800mATPS61025,TPS61027)I SW Switch current limit(TPS61028)VOUT=3.3V800mAI SW Switch current limit(TPS61026,TPS61029)VOUT=3.3V150018002100mAStart-up current limit0.4x I SW mASWN switch on resistance VOUT=3.3V260mΩSWP switch on resistance VOUT=3.3V290mΩTotal accuracy(including line and load regulation)±3%Line regulation0.6%Load regulation0.6%VBAT13µAI O=0mA,V EN=VBAT=1.2V,Quiescent currentVOUT=3.3V,T A=25°CVOUT2545µAV EN=0V,VBAT=1.2V,Shutdown current0.11µAT A=25°CCONTROL STAGEPARAMETER TEST CONDITIONS MIN TYP MAX UNITV UVLO Under voltage lockout threshold V LBI voltage decreasing0.8VV IL LBI voltage threshold V LBI voltage decreasing490500510mVLBI input hysteresis10mVLBI input current EN=VBAT or GND0.010.1µAV OL LBO output low voltage V O=3.3V,I OI=100µA0.040.4VV lkg LBO output leakage current V LBO=7V0.010.1µAV IL EN,PS input low voltage0.2×VBAT VV IH EN,PS input high voltage0.8×VBAT VEN,PS input current Clamped on GND or VBAT0.010.1µAOvertemperature protection140°COvertemperature hysteresis20°C3Submit Documentation FeedbackPIN ASSIGNMENTSDRC PACKAGE (TOP VIEW)TPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006Terminal FunctionsTERMINAL I/O DESCRIPTIONNAME NO.EN 1I Enable input.(1/VBAT enabled,0/GND disabled)FB 3IVoltage feedback of adjustable versions GND 5Control /logic groundLBI 7I Low battery comparator input (comparator enabled with EN),may not be left floating,should be connected to GND or VBAT if comparator is not used LBO 4O Low battery comparator output (open drain)PS 8I Enable/disable power save mode (1/VBAT disabled,0/GND enabled)SW 9I Boost and rectifying switch input PGND 10Power ground VBAT 6I Supply voltage VOUT 2O Boost converter outputPowerPAD™Must be soldered to achieve appropriate power dissipation.Should be connected to PGND.4Submit Documentation FeedbackVOUTPGNDFBLBOTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006FUNCTIONAL BLOCK DIAGRAM (TPS61020,TPS61028,TPS61029)5Submit Documentation Feedback PARAMETER MEASUREMENT INFORMATIONPowerSupplyC3 = Low ESR TantalumV CCBoost OutputControl Output TYPICAL CHARACTERISTICSTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER2003–REVISED FEBRUARY2006Table of GraphsFIGURE Maximum output current vs Input voltage1vs Output current(TPS61020)2vs Output current(TPS61025)3 Efficiency vs Output current(TPS61027)4vs Input voltage(TPS61025)5vs Input voltage(TPS61027)6vs Output current(TPS61025)7 Output voltagevs Output current(TPS61027)8 No load supply current into VBAT vs Input voltage9 No load supply current into VOUT vs Input voltage10Output voltage in continuous mode(TPS61025)11Output voltage in continuous mode(TPS61027)12Output voltage in power save mode(TPS61025)13Output voltage in power save mode(TPS61027)14Load transient response(TPS61025)15 WaveformsLoad transient response(TPS61027)16Line transient response(TPS61025)17Line transient response(TPS61027)18Start-up after enable(TPS61025)19Start-up after enable(TPS61027)206Submit Documentation Feedback0.91.72.53.34.1M a x i m u m O u t p u t C u r r e n t - m A4.9 6.55.7V I - Input Voltage - V01020304050607080901001101001000E f f i c i e n c y - %I O- Output Current - mA01020304050607080901001101001000E f f i c i e n c y - %I O - Output Current - mA01020304050607080901001101001000E f f i c i e n c y - %I O - Output Current - mATPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006TPS61020MAXIMUM OUTPUT CURRENTEFFICIENCYvsvsINPUT VOLTAGEOUTPUT CURRENTFigure 1.Figure 2.TPS61025TPS61027EFFICIENCYEFFICIENCYvsvsOUTPUT CURRENTOUTPUT CURRENTFigure 3.Figure 4.7Submit Documentation Feedback50556065707580859095100E f f i c i e n c y - %V I - Input Voltage - VE f f i c i e n c y - %V I - Input Voltage - V3.203.253.303.351101001000- O u t p u t V o l t a g e - VV O I O - Output Current - mA- O u t p u t V o l t a g e - VV O I O - Output Current - mA4.804.854.904.9555.055.101101001000TPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006TPS61025TPS61027EFFICIENCYEFFICIENCYvsvsINPUT VOLTAGEINPUT VOLTAGEFigure 5.Figure 6.TPS61025TPS61027OUTPUT VOLTAGEOUTPUT VOLTAGEvsvsOUTPUT CURRENTOUTPUT CURRENTFigure 7.Figure 8.8Submit Documentation Feedback0.9 1.522.533.54N o L o a d S u p p l y C u r r e n t I n t o V O U T -4.556 6.55.5V I - Input Voltage - VAµ-0.24.89.814.819.824.829.834.80.20.40.60.81.21.60.9 1.522.533.54N o L o a d S u p p l y C u r r e n t I n t o V B A T -4.5566.55.5V I - Input Voltage - VAµ11.4t - Time - 1 µs/divV I = 3.6 V,R L = 25 Ω,V O = 5 VO u t p u t V o l t a g e 20 m V /d i vI n d u c t o r C u r r e n t 200 m A /d i vt - Time - 1 µs/divV I = 1.2 V,R L = 33 Ω,V O = 3.3 VO u t p u t V o l t a g e 20 m V /d i v I n d u c t o r C u r r e n t 200 m A /d i vTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006NO LOAD SUPPLY CURRENT INTO VBATNO LOAD SUPPLY CURRENT INTO VOUTvsvsINPUT VOLTAGEINPUT VOLTAGEFigure 9.Figure 10.TPS61025TPS61027OUTPUT VOLTAGE IN CONTINUOUS MODEOUTPUT VOLTAGE IN CONTINUOUS MODEFigure 11.Figure 12.9Submit Documentation Feedbackt - Time - 50 µs/divV I = 1.2 V,R L = 330 Ω,V O = 3.3 VO u t p u t V o l t a g e 20 m V /d i v , A C I n d u c t o r C u r r e n t 100 m A /d i v , D Ct - Time - 50 µs/divV I = 3.6 V,R L = 250 Ω,V O = 5 VO u t p u t V o l t a g e 50 m V /d i v , A CI n d u c t o r C u r r e n t 200 m A /d i v , D C t - Time - 2 ms/divO u t p u t C u r r e n t 100 m A /d i v , D C O u t p u t V o l t a g e 20 m V /d i v , A CV I = 3.6 V,I L = 100 mA to 200 mA,V O = 5 Vt - Time - 2 ms/divV I = 1.2 V,I L = 100 mA to 200 mA,V O = 3.3 VO u t p u t C u r r e n t 100 m A /d i v , D CO u t p u t V o l t a g e 20 m V /d i v , A CTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006TPS61025TPS61027OUTPUT VOLTAGE IN POWER SAVE MODEOUTPUT VOLTAGE IN POWER SAVE MODEFigure 13.Figure 14.TPS61025TPS61027LOAD TRANSIENT RESPONSELOAD TRANSIENT RESPONSEFigure 15.Figure 16.10Submit Documentation Feedbackt - Time - 2 ms/divV I = 1.8 V to 2.4 V,R L = 33 Ω,V O = 3.3 VI n p u t V o l t a g e 500 m V /d i v , A C O u t p u t V o l t a g e 20 m V /d i v , A Ct - Time - 2 ms/divV I = 3 V to 3.6 V,R L = 25 Ω,V O = 5 VI n p u t V o l t a g e 500 m V /d i v , A CO u t p u t V o l t a g e 20 m V /d i v , A C t - Time - 1 ms/divO u t p u t V o l t a g e 1 V /d i v , D CI n d u c t o r C u r r e n t 200 m A /d i v , D CV o l t a g e A t S W 2 V /d i v , D CE n a b l e 5 V /d i v , D CV I = 2.4V,R L = 33 Ω,V O = 3.3 Vt - Time - 500s/divm V I = 3.6 V ,R L = 50W ,V O = 5 VO u t p u t V o l t a g e 2 V /d i v , D CI n d u c t o r C u r r e n t 200 m A /d i v , D CV o l t a g e A t S W 2 V /d i v , D C E n a b l e 5 V /d i v , D CTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006TPS61025TPS61027LINE TRANSIENT RESPONSELINE TRANSIENT RESPONSEFigure 17.Figure 18.TPS61025TPS61027START-UP AFTER ENABLESTART-UP AFTER ENABLEFigure 19.Figure 20.11Submit Documentation FeedbackDETAILED DESCRIPTIONCONTROLLER CIRCUITSynchronous RectifierDown RegulationDevice EnableTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006The controller circuit of the device is based on a fixed frequency multiple feedforward controller topology.Input voltage,output voltage,and voltage drop on the NMOS switch are monitored and forwarded to the regulator.So changes in the operating conditions of the converter directly affect the duty cycle and must not take the indirect and slow way through the control loop and the error amplifier.The control loop,determined by the error amplifier,only has to handle small signal errors.The input for it is the feedback voltage on the FB pin or,at fixed output voltage versions,the voltage on the internal resistor divider.It is compared with the internal reference voltage to generate an accurate and stable output voltage.The peak current of the NMOS switch is also sensed to limit the maximum current flowing through the switch and the inductor.The typical peak current limit is set to 1500mA.An internal temperature sensor prevents the device from getting overheated in case of excessive power dissipation.The device integrates an N-channel and a P-channel MOSFET transistor to realize a synchronous rectifier.Because the commonly used discrete Schottky rectifier is replaced with a low RDS(ON)PMOS switch,the power conversion efficiency reaches 96%.To avoid ground shift due to the high currents in the NMOS switch,two separate ground pins are used.The reference for all control functions is the GND pin.The source of the NMOS switch is connected to PGND.Both grounds must be connected on the PCB at only one point close to the GND pin.A special circuit is applied to disconnect the load from the input during shutdown of the converter.In conventional synchronous rectifier circuits,the backgate diode of the high-side PMOS is forward biased in shutdown and allows current flowing from the battery to the output.This device however uses a special circuit which takes the cathode of the backgate diode of the high-side PMOS and disconnects it from the source when the regulator is not enabled (EN =low).The benefit of this feature for the system design engineer is that the battery is not depleted during shutdown of the converter.No additional components have to be added to the design to make sure that the battery is disconnected from the output of the converter.In general,a boost converter only regulates output voltages which are higher than the input voltage.This device operates differently.For example,it is able to regulate 3.0V at the output with two fresh alkaline cells at the input having a total cell voltage of 3.2V.Another example is powering white LEDs with a forward voltage of 3.6V from a fully charged Li-Ion cell with an output voltage of 4.2V.To control these applications properly,a down conversion mode is implemented.If the input voltage reaches or exceeds the output voltage,the converter changes to the conversion mode.In this mode,the control circuit changes the behavior of the rectifying PMOS.It sets the voltage drop across the PMOS as high as needed to regulate the output voltage.This means the power losses in the converter increase.This has to be taken into account for thermal consideration.The down conversion mode is automatically turned off as soon as the input voltage falls about 50mV below the output voltage.For proper operation in down conversion mode the output voltage should not be programmed below 50%of the maximum input voltage which can be applied.The device is put into operation when EN is set high.It is put into a shutdown mode when EN is set to GND.In shutdown mode,the regulator stops switching,all internal control circuitry including the low-battery comparator is switched off,and the load is isolated from the input (as described in the Synchronous Rectifier Section).This also means that the output voltage can drop below the input voltage during shutdown.During start-up of the converter,the duty cycle and the peak current are limited in order to avoid high peak currents drawn from the battery.12Submit Documentation FeedbackUndervoltage LockoutSoftstart and Short Circuit ProtectionV O − Output Voltage − VP r e c h a r g e C u r r e n t − APower Save ModeTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006DETAILED DESCRIPTION (continued)An undervoltage lockout function prevents device start-up if the supply voltage on VBAT is lower than approximately 0.8V.When in operation and the battery is being discharged,the device automatically enters the shutdown mode if the voltage on VBAT drops below approximately 0.8V.This undervoltage lockout function is implemented in order to prevent the malfunctioning of the converter.When the device enables,the internal startup cycle starts with the first step,the precharge phase.During precharge,the rectifying switch is turned on until the output capacitor is charged to a value close to the input voltage.The rectifying switch is current limited during that phase.The current limit increases with the output voltage.This circuit also limits the output current under short circuit conditions at the output.Figure 21shows the typical precharge current vs output voltage for specific input voltages:Figure 21.Precharge and Short Circuit CurrentAfter charging the output capacitor to the input voltage,the device starts switching.If the input voltage is below 1.4V the device works with a fixed duty cycle of 50%until the output voltage reaches 1.4V.After that the duty cycle is set depending on the input output voltage ratio.Until the output voltage reaches its nominal value,the boost switch current limit is set to 40%of its nominal value to avoid high peak currents at the battery during startup.As soon as the output voltage is reached,the regulator takes control and the switch current limit is set back to 100%.The PS pin can be used to select different operation modes.To enable power save,PS must be set low.Power save mode is used to improve efficiency at light load.In power save mode the converter only operates when the output voltage trips below a set threshold voltage.It ramps up the output voltage with one or several pulses and goes again into power save mode once the output voltage exceeds the set threshold voltage.This power save mode can be disabled by setting the PS to VBAT.In down conversion mode,power save mode is always active and the device cannot be forced into fixed frequency operation at light loads.13Submit Documentation FeedbackLow Battery Detector Circuit—LBI/LBOLow-EMI SwitchTPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006DETAILED DESCRIPTION (continued)The low-battery detector circuit is typically used to supervise the battery voltage and to generate an error flag when the battery voltage drops below a user-set threshold voltage.The function is active only when the device is enabled.When the device is disabled,the LBO pin is high-impedance.The switching threshold is 500mV at LBI.During normal operation,LBO stays at high impedance when the voltage,applied at LBI,is above the threshold.It is active low when the voltage at LBI goes below 500mV.The battery voltage,at which the detection circuit switches,can be programmed with a resistive divider connected to the LBI pin.The resistive divider scales down the battery voltage to a voltage level of 500mV,which is then compared to the LBI threshold voltage.The LBI pin has a built-in hysteresis of 10mV.See the application section for more details about the programming of the LBI threshold.If the low-battery detection circuit is not used,the LBI pin should be connected to GND (or to VBAT)and the LBO pin can be left unconnected.Do not let the LBI pin float.The device integrates a circuit that removes the ringing that typically appears on the SW node when the converter enters discontinuous current mode.In this case,the current through the inductor ramps to zero and the rectifying PMOS switch is turned off to prevent a reverse current flowing from the output capacitors back to the battery.Due to the remaining energy that is stored in parasitic components of the semiconductor and the inductor,a ringing on the SW pin is induced.The integrated antiringing switch clamps this voltage to VBAT and therefore dampens ringing.14Submit Documentation FeedbackAPPLICATION INFORMATIONDESIGN PROCEDUREPROGRAMMING THE OUTPUT VOLTAGER3+R4ǒVO V FB*1Ǔ+180k WǒVO 500mV*1Ǔ(1)C parR3+20pF ǒ200k W R4*1Ǔ(2)Power SupplyV CCBoost OutputControl OutputPROGRAMMING THE LBI/LBO THRESHOLD VOLTAGETPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER 2003–REVISED FEBRUARY 2006The TPS6102x dc/dc converters are intended for systems powered by a single up to triple cell Alkaline,NiCd,NiMH battery with a typical terminal voltage between 0.9V and 6.5V.They can also be used in systems powered by one-cell Li-Ion or Li-Polymer with a typical voltage between 2.5V and 4.2V.Additionally,any other voltage source with a typical output voltage between 0.9V and 6.5V can power systems where the TPS6102x is used.The output voltage of the TPS61020dc/dc converter can be adjusted with an external resistor divider.The typical value of the voltage at the FB pin is 500mV.The maximum recommended value for the output voltage is 5.5V.The current through the resistive divider should be about 100times greater than the current into the FB pin.The typical current into the FB pin is 0.01µA,and the voltage across R4is typically 500mV.Based on those two values,the recommended value for R4should be lower than 500k Ω,in order to set the divider current at 1µA or higher.Because of internal compensation circuitry the value for this resistor should be in the range of 200k Ω.From that,the value of resistor R3,depending on the needed output voltage (V O ),can be calculated using Equation 1:If as an example,an output voltage of 3.3V is needed,a 1.0-M Ωresistor should be chosen for R3.If for any reason the value for R4is chosen significantly lower than 200k Ωadditional capacitance in parallel to R3is recommended,in case the device shows instable regulation of the output voltage.The required capacitance value can be easily calculated using Equation 2:Figure 22.Typical Application Circuit for Adjustable Output Voltage OptionThe current through the resistive divider should be about 100times greater than the current into the LBI pin.The typical current into the LBI pin is 0.01µA,and the voltage across R2is equal to the LBI voltage threshold that is generated on-chip,which has a value of 500mV.The recommended value for R2is therefore in the range of 500k Ω.From that,the value of resistor R1,depending on the desired minimum battery voltage V BAT,can be calculated using Equation 3.15Submit Documentation Feedback R1+R2ǒV BATV LBI*threshold*1Ǔ+390k WǒV BAT500mV*1Ǔ(3) INDUCTOR SELECTIONI L+I OUTV OUTV BAT0.8(4)L+V BATǒV OUT–V BATǓD I LƒV OUT(5)TPS61020,TPS61024,TPS61025TPS61026,TPS61027,TPS61028TPS61029SLVS451D–SEPTEMBER2003–REVISED FEBRUARY2006The output of the low battery supervisor is a simple open-drain output that goes active low if the dedicated battery voltage drops below the programmed threshold voltage on LBI.The output requires a pullup resistor with a recommended value of1MΩ.If not used,the LBO pin can be left floating or tied to GND.A boost converter normally requires two main passive components for storing energy during the conversion.A boost inductor and a storage capacitor at the output are required.To select the boost inductor,it is recommended to keep the possible peak inductor current below the current limit threshold of the power switch in the chosen configuration.For example,the current limit threshold of the TPS6102xs switch is1800mA at an output voltage of5V.The highest peak current through the inductor and the switch depends on the output load, the input(V BAT),and the output voltage(V OUT).Estimation of the maximum average inductor current can be done using Equation4:For example,for an output current of200mA at3.3V,at least920mA of average current flows through the inductor at a minimum input voltage of0.9V.The second parameter for choosing the inductor is the desired current ripple in the inductor.Normally,it is advisable to work with a ripple of less than20%of the average inductor current.A smaller ripple reduces the magnetic hysteresis losses in the inductor,as well as output voltage ripple and EMI.But in the same way, regulation time at load changes rises.In addition,a larger inductor increases the total system costs.With those parameters,it is possible to calculate the value for the inductor by using Equation5:Parameter f is the switching frequency and∆I L is the ripple current in the inductor,i.e.,20%×I L.In this example, the desired inductor has the value of5.5µH.With this calculated value and the calculated currents,it is possible to choose a suitable inductor.In typical applications a6.8µH inductance is recommended.The device has been optimized to operate with inductance values between2.2µH and22µH.Nevertheless operation with higher inductance values may be possible in some applications.Detailed stability analysis is then recommended.Care has to be taken that load transients and losses in the circuit can lead to higher currents as estimated in Equation5.Also,the losses in the inductor caused by magnetic hysteresis losses and copper losses are a major parameter for total circuit efficiency.The following inductor series from different suppliers have been used with the TPS6102x converters:Table1.List of InductorsVENDOR INDUCTOR SERIESCDRH4D28SumidaCDRH5D287447789Wurth Elektronik744042EPCOS B82462-G4SD25Cooper Electronics TechnologiesSD2016Submit Documentation Feedback。

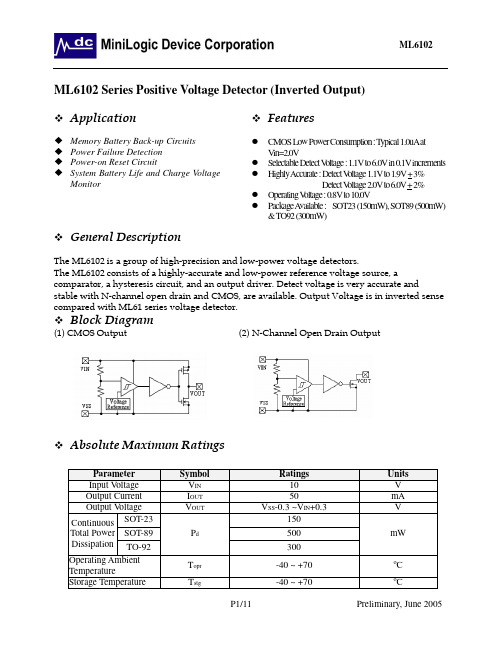

ML6102X113XX资料

ML6102 Series Positive Voltage Detector (Inverted Output)ApplicationMemory Battery Back-up Circuits Power Failure Detection Power-on Reset CircuitSystem Battery Life and Charge Voltage MonitorFeaturesCMOS Low Power Consumption : T ypical 1.0uA atV in=2.0VSelectable Detect V oltage : 1.1V to 6.0V in 0.1V increments Highly Accurate : Detect V oltage 1.1V to 1.9V + 3%Detect V oltage 2.0V to 6.0V + 2%Operating V oltage : 0.8V to 10.0VPackage A vailable : SOT23 (150mW), SOT89 (500mW)& TO92 (300mW)General DescriptionThe ML6102 is a group of high-precision and low-power voltage detectors.The ML6102 consists of a highly-accurate and low-power reference voltage source, acomparator, a hysteresis circuit, and an output driver. Detect voltage is very accurate andstable with N-channel open drain and CMOS, are available. Output Voltage is in inverted sense compared with ML61 series voltage detector. Block Diagram (1) CMOS Output (2) N-Channel Open Drain Output Absolute Maximum RatingsParameter SymbolRatingsUnits Input V oltage V IN 10 V Output Current I OUT 50mA Output V oltage V OUT V SS -0.3 ~V IN +0.3V SOT-23 150SOT-89500 Continuous Total Power Dissipation TO-92 P d 300 mW Operating Ambient TemperatureT opr -40 ~ +70 oC Storage Temperature T stg-40 ~ +70o CElectrical CharacteristicsParameter Symbol Conditions Min Typ Max UnitsV DF = 1.1V to 1.9V X0.97 V DF X1.03 V Detect Voltage V DFV DF = 2.0V to 7.0V X0.98 V DF X1.02 VV DF = 1.1V to 2.9V X0.04 V DF X0.05 X0.06 V Hysteresis Range V HYSV DF = 3.0V to 7.0V X0.015 V DF X0.025 X0.035 VV IN = 1.0V 0.8 2.0V IN = 2.0V 1.0 2.5V IN = 3.0V 1.3 3.0V IN = 4.0V 1.6 3.5 Supply Current I SSV IN = 5.0V 2.0 4.0uAOperating Voltage V IN V DF = 1.1~7.0V 0.8 10.0 VNch V DS = 0.5VV IN = 1.0V 1.0V IN = 2.0V 3.0V IN = 3.0V 5.0V IN = 4.0V 11.0V IN = 5.0V 13.0Pch V DS = 1.0VV IN = 5.0V -5.0 Output Current I OUT(CMOS Output)mATransient Delay Time (V DR -> V OUT Inversion) t DLYWhile V IN changes from0.6V to 10V0.2 msElectrical Characteristics By Detector ThresholdPackage Pin NumberSOT-23-3 SOT-89-3 TO-92Pin Name Function 1 1 1 VOUTSupply Voltage Output 3 2 2 VIN Supply Voltage Input2 3 3VSSGroundPin ConfigurationSOT-23-3SOT-89-3TO-92Functional Description (Refers to CMOS Output)Notes :1.Output cannot be specified for power supply voltage under V MIN (ie. 0.8V) because operation is notguaranteed for that range.2.V DF : Detect V oltage for drop in power supply voltage3.V DR : Detect Release V oltage for rise in power supply voltage4.V HYS = V DR – V DF5.t OL : Time lag between the time that the power supply voltage rises to the detect release voltage (V DR)and the time that the output pin (OUT) goes to “L” level.6.t OH : Time lag between the time that the power supply voltage falls to the detect voltage (V DF) and thetime that the output pin (OUT) goes to “H” level.7.These characteristics for the N-channel open drain output are when a load resistor is connectedbetween the OUT and IN pins.Ordering InformationMarkingDesignatorDescriptionaOutput ConfigurationC = CMOS Output N = N-Channel Output Detect Voltage eg. 30=3.0V b50=5.0VcDetect Voltage Accuracy 2 = +2.0% 3 = +3.0%dPackage Type M = SOT-23-3 P = SOT-89 T = TO-92eDevice Orientation R = Embossed Tape(Orientation of Device : Right) L = Embossed Tape(Orientation of Device : Left) B = Bag (TO-92)H = Paper Tape (TO-92) G G = Lead Free PartSOT-89-3 : Designator Description 1 TypeD = V oltage Detector (CMOS Output)E = V oltage Detector (N-channel Output) 2,3 Output Voltage eg. 30 = 3.0V 4 Internal CodeSOT-23-3 : DesignatorDescription1 TypeD = V oltage Detector (CMOS Output)E = V oltage Detector (N-channel Output) 2,3 Output Voltage eg. 30 = 3.0V 4 Internal CodeTO-92 : Designator Description 1 TypeD = V oltage Detector (CMOS Output)E = V oltage Detector (N-channel Output) 2,3 Output Voltage eg. 30 = 3.0V 4 Internal code 5, 6 Year Codeeg. 05 = Year 2005 7, 8 Week Codeeg. 30 = Week 30Packaging InformationRecommended Pattern LayoutTO-92 :Units : mm SOT-23-3 :Tape and Reel InformationSOT-23 Taping Specifications :“R” type [Orientation of Device: Right ]Standard Type“L” type [Orientation of Device: Left ]Reverse TypeSIZE (mm) A ∅ 178 ± 0.8 B 2 ± 0.2 C ∅ 13 ± 0.2 D ∅ 21 ± 0.8 G 8 ± 0.5 H ∅ 603,000 pcs / reel SOT-23 :SOT-89 Taping Specifications : “R” type [Orientation of Device: Right ]Standard TypeSOT-89 :SIZE (mm) A ∅ 178 ± 0.8 B 2 ± 0.2 C ∅ 13 ± 0.2 D ∅ 21 ± 0.8 G 12 ± 0.5 H ∅ 601,000 pcs / reelReverse TypeP11/11 Preliminary, June 2005 ML6102SIZE (mm) P12.7 ± 1.0 PO12.7 ± 0.3 P26.35 ± 0.4 F2.5 W18.0 ± 1.0 WO6.0 ± 0.3 W19.0 ± 0.5 W20.5 MAX H19.0 ± 0.5 H016.0 ± 0.5 H132.25 MAX D∅ 4.0 ± 0.2 t0.6 ± 0.2 L1 3.5 MIN+ 0.45 - 0.15 2,000 pcs / box TO-92 Taping Specifications :The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. 元器件交易网。

IXDP610资料

© 2001 IXYS/DEI All rights reserved1DescriptionThe IXDP610 Digital Pulse WidthModulator (DPWM) is a programmable CMOS LSI device which accepts digital pulse width data from a microprocessor and generates two complementary,non-overlapping, pulse width modula-ted signals for direct digital control of switching power bridge. The DPWM is designed to be operated under the direct control of a microprocessor and interfaces easily with most standard microprocessor and microcomputer buses. The IXDP610 is packaged in an 18-Pin slim DP .The PWM waveform generated by the IXDP610 results from comparing the output of the Pulse Width counter to the number stored in the Pulse Width Latch (see below). A programmable "dead-time" is incorporated into the PWM waveform. The Dead-Time Logic disables both outputs on eachtransition of the Comparator output for the required dead-time interval.The output stage provides complemen-tary PWM output signals capable ofBus Compatible Digital PWM Controller, IXDP 610sinking and sourcing 20 mA at TTL voltage levels. The Output Disable logic can be activated either bysoftware or hardware. This facilitates cycle-by-cycle current-limit, short-circuit, over-temperature, and desaturation protection schemes.The IXDP610 is capable of operating at PWM frequencies from zero to 390kHz;the dead-time is programmable from zero to 14 clock cycles (0 to 11 % of the PWM cycle), which allowsoperation with fast power MOSFETs,IGBTs, and bipolar power transistors. A trade-off between PWM frequency and resolution is provided by selecting the counter resolution to be 7-bit or 8-bit.The 20 mA output drive makes the IXDP610 capable of directly driving opto isolators and Smart Power devices. The fast response to pulse width commands is achieved byinstantaneous change of the outputs to correspond to the new command. This eliminates the one-cycle delay usually associated with other digital PWM implementations.FeaturesG Microcomputer bus compatible GTwo complementary outputs for direct control of a switching power bridgeGDynamically programmable pulse width ranges from 0 to 100 %GTwo modes of operation: 7-bit or 8-bit resolutionGSwitching frequency range up to 390 kHzGProgrammable Dead-time Counter prevents switching overlap GCycle-by-Cycle disable input to protect against over-current, over-temperature, etc.GOutputs may be disabled under software controlGSpecial locking bit prevents damage to the stage in the event of a software failureG18-pin slim DIP packageDimensions in inch and mm 18-Pin Slim DIPSymbol Definition Maximum Ratings V CC Supply voltage -0.3 ... 5.5V V IN Input voltage -0.3 ... V CC + 0.3V V out Output voltage-0.3 ... V CC + 0.3V P D Maximum power dissipation 500mW T stgStorage temperature range-40 (125)°C© 2001 IXYS/DEI All rights reserved2SymbolDefinitionOperating RangeV CC Supply voltageT AOperating free air temperatureSymbolDefinition/Condition V IH(CMOS)Input High Voltage ** T clk = 1/f clk© 2001 IXYS/DEI All rights reserved3Pin Description IXDP 610PINomenclature ofSym.Pin Description D01DATA BUS - the data bus on CS WR RST SEL ODIS CLK V OUT1OUT2D0D1D2D3D4D5D6D7GNDIXYS IXDP610PI© 2001 IXYS/DEI All rights reserved4DescriptionIntroductionThe IXDP610 is a digital PWM con-troller. It simplifies the interface between a microprocessor and aswitching power bridge by providing to a micro-processor the means to directly control the average voltage across a load (DC motor, etc.). Since the IXDP610 generates twocomplementary PWM control signals,there is no need for Digital to Analog Converters (DACs), SawtoothGenerators, and Analog Comparators.OUT1 and OUT2 can directly drive the buffers to the power e of the IXDP610 in a DC servo system is depicted in the system block diagram shown in Fig. 1. The IXDP610receives digital data from the micropro-cessor and converts the data to a pair of complementary PWM signals that can be used to control the average voltage across a DC servo motor. A Shaft Encoder Peripheral Interface (SEPI) IC converts incrementalencoder signals to a binary number so the micro-processor can monitor and co m plete the control of the DC servo motor.It is possible to generate PWM control signals in software with a dedicated microprocessor or microcontroller. This has the limitation, however, of very low switching frequencies (<5 kHz) and significant software overhead. By using the IXDP610 to handle the generation of the PWM control signals, a micro-processor can handle several PWM channels and the PWM control signals can switch at relatively high rates (up to 300 kHz). Servicing the IXDP610 is a simple as writing an 8-bit number to the Pulse Width latch whenever a change in duty cycle is desired. This is analo-gous to writing data to a DAC.Programmable dead-timeBecause the IXDP610 is a digital IC,and is programmable, it is possible to tailor the dead-time period (defined as t DT in Fig. 2). IXDP610’s programmable dead-time feature is difficult to duplicate in the equivalent analog system. The control of a switching bridge usually involves a process of alternating the “on-time” of two power switches connected in series between a high-voltage and a low-voltage. For example, the H-bridge of Fig. 3 can be operated by turning the upper left and lower right transistors on and leaving the two remaining transistors off, during the first half of the PWM cycle. In the second half of the cycle, the upper right and lower left transistors are on andFig. 1 Basic System ConfigurationFig. 3 IXDP610 to DC Servo Motor Full Bridge Block Diagramguaranteeing that both transistors in a leg are off for a minimum of time during a transition (the dead-time period).Since the dead-time is programmable,it can be tailored to the specific application. It can be short for high-speed MOSFET s and longer for IGBTs.Protection circuitryThe IXDP610 has several features thatfacilitate protection of the power devi-ces being controlled. The ODIS pin is an input that can be driven by external hardware under emergency shutdown conditions, such as over-current and over-temperature. The Stop bit, in the Control latch, provides a mechanism through which the software can indefi-nitely disable the complementary out-functions, they provide a means toprotect the power devices from measu-rable system hazards such as over-current, over-voltage, over-temperature etc.Software runaway is a system hazard that is difficult or impossible tomeasure. The Lock bit, in the Control latch, can be used to protect thesystem from software runaway and/or errors. Setting the Lock bit prevents subsequent writes to the Control latch from having any affect on theIXDP610’s operating para-meters.Setting the Lock bit does not prevent the Lock bit is set, it is impossible to modify critical parameters, such as the dead-time delay or the PWM wave-form resolution.Control latchThe Control latch is composed of eight bits that determine the IXDP610’sFig. 2 PWM Cycle Time and Dead-Time Definitionthe remaining two are off. During the transition, between the first half and the second half of the PWM cycle, there is a very short period of time when both the upper transistor and the lower transistor in a leg could be on. If both transistors are on, for this short period of time, they will effectively short the high voltage supply to ground-this is an undesirable situation.The IXDP610’s programmable dead-time feature prevents this situation by© 2001 IXYS/DEI All rights reserved5SEL CS WR Resulting Function X 1XNo Action 00Load D0-D7into PW latch 1Load D0-D7into Control LatchTable 1 Bus Transaction Truth Table time period overlaps the ontime of an output, therefore, it shortens the on-time without affecting the base PWM cycle time. A dead-time period is only inserted if an output changes from high to low (on to off). Thus, if a PWM duty cycle ischosen such that an output would be on for a period of time equal to or less than one dead-time period, the switchassociated with that output will not be turned on during the PWM cycle. In this special case, one will observe only dead-time period per PWM cycle time, rather than the two dead-time periods shown in Fig. 2.Lock bit - writing a one to this bit pre-vents further writes to all bits in thecontrol latch, except the Stop bit. Thus, a one should not be written to this bit until the IXDP610 has been program-med.Those writes that follow a one being written to the Lock bit have no effect on D0 through D6. The locking featureprovided by this bit prevents modification of the control latch due to a software error, thereby helping prevent damage to the bridge being controlled by the IXDP610. Asserting the RESET pin is the only method by which the lock bit can be cleared.Divide bit - this bit sets the frequency of the internal PWM clock. Writing a one to this bit causes the external CLOCK to be divided by two before being presented to the PW counter. Writing a zero to this bit results in no division of the external CLOCK before it is presented to the PW counter (“divide by one”). The Divide bit has no affect on the dead-time Counter.Resolution bit - writing a zero to this bit chooses 7-bit counter resolution, while writing a one chooses 8-bit PWM counter resolution. Choosing 7-bit resolution doubles the achieveablePWM base frequency at the expense of decreased duty cycle resolution. The combination of the Divide bit and the Resolution bit provides the user with three different PWM base periods for a given external CLOCK frequency. ARESET programs the IXDP610 to operate in the 8-bit resolution mode.When the IXDP610 is programmed in 8-bit mode, the PWM base period is equal to 256 PWM clock cycles. In 7-bit mode the PWM base period is equal to 128PWM clock cycles. A PWM clock cycle is equal to one external CLOCK period when the Divide bit in the control latch is a zero and is equal to two externalCLOCK periods when the Divide bit is a one.The following formula can be used to determine the PWM base period:If ((7/8 bit = 0) And (DIV bit = 0))PWM base period CLOCK period x 128else If ((7/8 bit = 0) And (DIV bit = 1))PWM base period = CLOCK period x 256else If ((7/8 bit = 1) And (DIV bit = 0))PWM base period = CLOCK period x 256else If ((7/8 bit = 1) And (DIV bit = 1))PWM base period = CLOCK period x 512The Pulse Width number that is written to the Pulse Width latch represents the high time of OUT1 (the low time of OUT2). The Dead-time Counterdecreases the on-time (output high) of an output by one dead-time period (t DT ).See Fig. 2 and the description of the dead-time bits in the Control latch to determine the duration of one dead-time period.Stop bit - writing a zero to this bit immediately disables the complemen-tary outputs (OUT1 and OUT2 are forced to zero). As long as this bit is a zero, the complementary outputs will be disabled.This bit is not affected by the Lock bit.This bit is equivalent in function to the OUTPUT DISABLE input. The outputs will not be re-enabled until the start of the PWM period which has both the Stop bit and the OUTPUT DISABLE input set to ones.PW latch - The binary number written to the PW latch represents the duty cycle of the complementary PWM outputs.Percent duty cycle is defined as follows:(assuming zero dead-time)For OUT1:time at 1% duty cycle =x 100PWM cycle time For OUT2:time at 0% duty cycle =x 100PWM cycle time“PWM cycle time” is t CYCLE in Fig. 2.operating parameters. Those bits are summarized in Table 2.Dead-time counter bits - these three bits determine the dead-time period, as defined by Fig. 2. Dead-time is that period of time when both OUT1 and OUT2 are low. Any binary number from 000 through 111 is valid. Thus, eight different dead-time periods can be programmed. DT0 is the least signifi-cant bit and DT2 is the most significant bit. A 000 binary means no dead-time and a 111 means maximum dead-time.Each dead-time count corresponds to two CLOCK periods. For instance, if a binary three (3) is programmed into the dead-time bits, the dead-time will be six external CLOCK cycles long.The dead-time is provided to aid in preventing switch overlap. The Dead-time Counter delays turning on the switch connected to OUT1 until the switch connected to OUT2 has had sufficient time to turn off; the comple-ment is also true, the dead-time counter delays turning on the switch connected to OUT2 until the switch connected to OUT1 has had sufficient time to turn off.Since the dead-time counter is pro-grammable, the user can optimize the dead-time delay to suit their specific application.In a typical PWM cycle (refer to Fig. 2)two dead-time periods will occur. One follows the turnoff of OUT2. The dead-time counter is triggered by an output turning off. During a dead-time period,both outputs are guaranteed to be off (no dead-time periods occur during 0 %and 100 % duty-cycle states). The dead-Control BitsName Descriptionbit 0DT0for setting the dead-time period, all combinations are valid,bit 1DT10 is no dead-time delay and 7 is maximum dead-time.bit 2DT2bit 3not used, reserved; always write a zero to this bitbit 4Lock setting this bit prevents further access to all bits in the Control latch, except the Stop bit.bit 5DIV determines frequency of the internal PWM clock.bit 67/8chooses between 7-bit and 8-bit resolution.bit 7Stopdisables (turns off) the complementary outputs.Table 2 Control Latch Bits© 2001 IXYS/DEI All rights reserved6The Resolution bit in the Control latch determines whether the number in the PW latch has 7 significant bits or 8significant bits. The following formulae can be used to determine the resulting PWM waveform’s duty cycle:For 7-bit mode operation:PW number% duty cycle =x 100128For 8-bit mode operation:PW number% duty cycle =x 100256The formulae are valid for all PWnum-bers except those at theFig. 5 8088 to IXDP610 InterfacePW Number Resulting (binary)Duty7-Bit8-Bit Cycle Resolution Resolution %00000000000000000.000000001000000010.0--000000100.78125--00000011 1.1718750000001000000100 1.5625--00000101 1.9531250000001100000110 2.34375--00000111 2.7343750000010000001000 3.125:::::::::010000001000000050.0:::::::::011111011111101097.65625--1111101198.046875011111101111110098.4375--1111110198.828125--1111111099.218750111111111111111100.01XXX XXXX--100.0Table 3: Duty Cycle as a Function of PW Numberextremes. The following tableillustrates the resulting percent duty cycle for seve-ral PW numbers. (The complete table would have 256entries, those entries that have been omitted can be calcu-lated using the above formulare.)The PWM duty cycle byte can be written to at any time. If the outputs are disabled by either the Stop bit in the Control latch or the OUTPUT DISABLE input, writing to the PWM duty cycle byte will have no effect on the outputs. When the outputs are re-enabled, the duty cycle will be deter-mined by the last byte written to the PWM duty cycle byte.Application InformationIntroductionThe IXDP610 is a digital PWM con-troller intended for use with general-purpose microprocessors and micro-controllers. Therefore, it is important to understand how the microproces-sor hardware and software interacts with and affects the operation of the IXDP610. On the following pages one will find discussions of some of the most important hardware and soft-ware interface issues. Among these issues are the hardware interface,how to choose the IXDP610's clock,initialization of the DPWM, the effect of the dead-time on the duty cycle,and the response of the IXDP610 to changes in the Pulse Width latch number. The following pages should be studied carefully by both thehardware and the software designer.The IXDP610 can be interfaced with virtually any microprocessor or micro-controller. Some interface examples are shown below.8051 to IXDP610 InterfaceFig. 4 is an example of how the IXDP610 can be interfaced with an Intel 8051 microcontroller. Theinterface is very simple and is ideally suited for servo motor control appli-cations. The 11.059 MHz clock allows one to use the 8051's built-in serial communication hardware at any standard baud rate. At this clock frequency, the IXDP610 can be configured for a 21.6 kHz switching frequency and a dead-time between zero and 1.26 µs, which is adjustable in 180 ns steps.8088 to IXDP610 InterfaceFig. 5 is just one example of how the IXDP610 can be interfaced with the Intel 8088 microprocessor. Using a 5 MHz clock (15 MHz crystal) the IXDP610 can be configured for a 19.53 kHz switching frequency. The deadtime can be adjusted between 0and 2.8 µs, in 400 ns steps. This confi-guration is ideally suited for driving DC servo motor amplifiers that useMOSFET, IGBT, or bipolar transistors.Frequency and dead-time considerationsTypical applications for the IXDP610include full and half bridge systems.Shown in Fig. 3 is a full bridge system.The programmable dead-time feature of the IXDP610 aids in preventing shorts in the power bridge and allows use of either fast MOSFETs or slower IGBTs and bipolar transistors. Table 4shows some of the PWM frequency and dead-time combinations that can be obtained with the IXDP610. The various options shown in the table are selected by varying the CLK frequency and the Divide and 7/8 bit in theFig. 4 8051 to IXDP610 Interface© 2001 IXYS/DEI All rights reserved7IXDP610's Control latch. The "%"columns express the dead-time as a percent of the PWM cycle time.If a zero is written to the 7/8 bit the IXDP610 is programmed for 7-bitresolution, writing a one programs the IXDP610 for 8-bit resolution. If a one is written to the Divide bit, the external clock (CLK) is divided by two before being presented to the Pulse Width counter; a zero in the Divide bit passes CLK directly to the Pulse Width Counter with no division of thefrequency. For a given CLK frequency one can select three different PWM frequencies: CLK/128, CLK/256, and CLK/512. (CLK/256 can be selected for either 7-bit or 8-bit resolution.Software ConsiderationsInitialization and the Lock Bit After power-up, the IXDP610 should be reset via the RST input. Doing so will guarantee the initial state of the DPWM and effectively write a01000111 binary to the Control latch.Thus, after asserting RST, theIXDP610 is set to the following state:G Stop is asserted, disabling OUT1and OUT2G 8-bit resolution is selected G CLK is divided by one (not divided by two)G Lock bit is “UNLOCKED”G Dead-time Counter is set for maximum dead-time.Asserting RST is the only means by which the Lock bit can be “unlocked".The lock bit must be cleared in order to write to all other bits in the Control latch, except the Stop bit.The IXDP610 does not undergo an internal reset on power-up; therefore,it is recommended that the system reset be connected to the DPWM, as in Fig. 5. If one wishes to allow soft-ware control over the RST input, they should “OR” the system reset and an I/O bit together, so the DPWM has a known state following system reset.Before initializing the Control latch,one should first write a valid number to the Pulse Width latch (i.e., a num-ber that results in 0 V applied to the load). Asserting RST clears the Pulse Width latch.During a write to the Control latch, all bits can be modified simultaneously,including the Lock bit. Thus, only one write is necessary to set the dead-time: 1) assert the Lock bit; 2) choose the Divide bit state; 3) choose the resolution. In most applications it is not necessary to change the dead-time bit, the Divide bit, or the 7/8 bit “on the fly”. Therefore, it is recom-mended that the Lock bit be asserted during initialization of the Control latch. Setting the Lock bit guarantees that a software runaway will notmodify the state of the dead-time bit,thereby preventing an accidentalshort of the bridge. If the RST input is accessible to the software (via an I/O bit, spare chip select, etc.), thehardware associated with asserting the RST input should be designed to minimize the possibility of resetting the IXDP610 in the event of a soft-ware runaway, since asserting the RST input clears the Lock bit, allo-wing modification of the DPWM's Control latch.Software Overflow Protection In many applications, the Pulse Width number written by the micro-processor to the IXDP610’s Pulse Width latch is the result of closed-loop numeric calculations. Depending on the algorithm used, the calculated PWM number may be susceptible to overflow, i.e. the calculated PWM PWM Dead-time OptionsFre- quency Min.Step Max.CLK 7/8DIV kHz %µs %µs %µs MHz bit bit 30000 1.560.05210.90.36338.40020000 1.560.07810.90.54725.600100000.780.078 5.50.54725.61010000 1.560.15610.9 1.09412.80050000.390.078 2.70.54725.61150000.780.156 5.5 1.09412.81050000.780.156 5.5 1.09412.8015000 1.560.31210.9 2.188 6.40020000.390.195 2.7 1.36710.241120000.780.391 5.5 2.734 5.121020000.780.391 5.5 2.734 5.12012000 1.560.78110.9 5.469 2.56005000.390.781 2.7 5.469 2.56115000.78 1.562 5.510.94 1.28105000.78 1.562 5.510.94 1.280151.563.12510.921.880.64Table 4. Sample PWM Frequency and Dead-time Optionsnumber could be larger than theavailable 8-bits (or 7-bits) provided in the Pulse Width latch. If this is the case, it is important that the software checks for overflow conditions before writing a number to the Pulse Width latch. Following is an example assuming 8-bit resolution:if (PWM__num < 0), check for underflow, PWM__num = 0, set to minimum limitelse if (PWM__num > 255), check for overflow, PWM__num = 255; set to maximum limitEffect of Dead-time on Duty Cycle The IXDP610 has been designed to generate PWM signals that range from 0 % to 100 %, inclusive. When zero dead-time has been selected (by writing 000 to the dead-time bits)the duty cycle of a PWM cycle can be determined by using the formulae shown on page 32/33. Fig. 6 illustra-tes the effect that a nonzero dead-time has on the PWM waveform.The dead-time feature built into the IXDP610 guarantees that both OUT1and OUT2 remain off for the duration of the dead-time period. A dead-time period occurs each time either OUT1or OUT2 turns off; the dead-time period overlaps the on-time of an output (see Fig. 6c). Thus, if the desired duty cycle is such that the© 2001 IXYS/DEI All rights reserved8have only one dead-time period in-serted in each PWM cycle. In Fig. 6b the desired ontime of OUT1 is less than the one dead-time period, there-fore OUT1 can never turn on. The same is true for OUT2 in Fig. 6d. Fig.6c is the normal situation, where both outputs turn on and off during one PWM cycle and, as a result, two dead-time periods are inserted.Response to a Change in the Pulse Width NumberOne can change the Pulse Width number at any time. It is notnecessary to synchronize writes to the Pulse Width latch with the CLK or the PWM cycle period. The IXDP610responds to the new Pulse Width number three clock cycles after the Pulse Width latch is loaded (1 CLK cycle after WR goes high). Thus,OUT1 and OUT2 will immediately reflect the new Pulse Width number.The IXDP610 does not wait until the next PWM cycle to implement a change in the Pulse Width number.(See Fig. 7).The resulting duty cycle is some-where between the old and the new duty cycle. The exact value of the resulting duty cycle depends on when the Width Latch is loaded (1 CLK cycle after WR goes high). Thus,OUT1 and OUT2 will immediately reflect the new Pulse Width number.The IXDP610 does not wait until the next PWM cycle to implement a change in the Pulse Width number.Fig. 7a shows what happens when the Pulse Width number is changed from 20 % to 80 % near the middle of the PWM cycle. Fig. 7b shows the reverse situation.The resulting duty cycle is somewhere between the old and the new duty cycle. The exact value of the resulting duty cycle depends when the Width latch is loaded (1 CLK cycle after WR goes high). Thus, OUT1 and OUT2 will immediately reflect the new Pulse Width number. The IXDP610 does not wait until the next PWM cycle toimplement a change in the Pulse Width number.Fig. 7 Effect of Changing the Duty Cycle during a PWM CycleFig. 6 Effect of Nonzero Dead-time on PWM Waveformon-time of an output is less than one dead-time period, the output will not turn on. This is shown in Fig. 6b and 6d. Therefore, the commanded duty cycle and the actual duty cycle may differ slightly, especially at extreme duty cycle values.Additionally, the dead-time can have an effect on the voltage applied to the load by the switching power bridge; the exact effect is a function of the direction of the current in the bridge and the architecture of the bridge. One should try and choose the smallest dead-time that will work with the given switch configuration.Fig. 6.a and 6.e illustrate the two duty cycle extremes, 0 % and 100 %.In these two instances there willnever by a dead-time period, regard-less of the value programmed in the dead-time bits, because neither output ever turns off. Fig. 6b and 6da)b)a)b)c)。

610-Q2R01资料