HY57V561620CLTP-7中文资料

hy57v561620接法

转SDRAM工作原理及S3C2410 SDRAM控制器4Banks x 4M x 16Bit配置方法(1)嵌入式系统 2011-01-18 20:49:05 阅读7 评论0 字号:大中小订阅SDRAM的工作原理、控制时序、及相关控制器的配置方法一直是嵌入式系统学习、开发过程中的一个难点。

掌握SDRAM的知识对硬件设计、编写系统启动代码、提高系统存取效率、电源管理都有一定的意义。

本文想通过:1.SDRAM的工作原理。

2.HY57V561620 SDRAM介绍。

3.S3C2410和HY57V561620的接线方法。

4.S3C2410 SDRAM控制器的配置方法。

5.SDRAM控制时序分析这5个方面来帮助初学者了解SDRAM。

文章分为2篇,第1篇讲解前3个知识点,第2篇讲解后2个。

一、SDRAM的工作原理SDRAM之所以成为DRARM就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM最重要的操作。

那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。

这样刷新速度就是:行数量/64ms。

我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个Bank的行数。

刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为15.625μs(微秒,1/1000毫秒),8192行时就为7.8125μs。

HY57V561620为8192 refresh cycles / 64ms。

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了,这也就大大提高了存储器的访问速度。

HY57V561620CT-H中文资料

元器件交易网

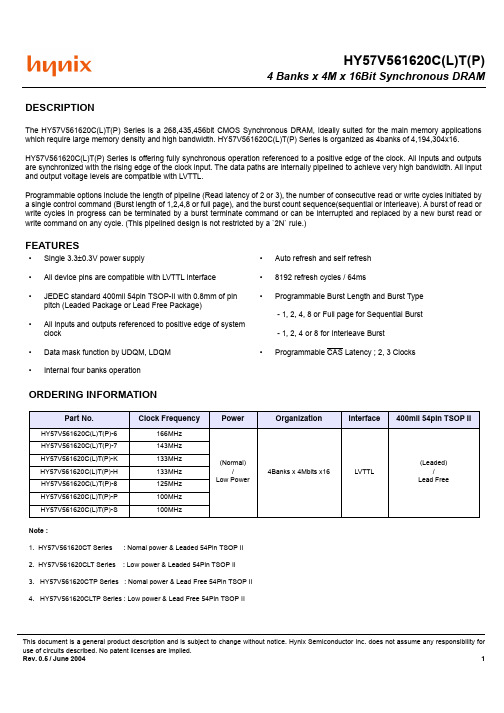

HY57V561620C(L)T(P)

4 Banks x 4M x 16Bit Synchronous DRAM

DESCRIPTION

The HY57V561620C(L)T(P) Series is a 268,435,456bit CMOS Synchronous DRAM, ideally suited for the main memory applications which require large memory density and high bandwidth. HY57V561620C(L)T(P) Series is organized as 4banks of 4,194,304x16.

ABSOLUTE MAXIMUM RATINGS

HY57V561620C(L)T(P)

Parameter Ambient Temperature Storage Temperature Voltage on Any Pin relative to VSS Voltage on VDD relative to VSS Short Circuit Output Current Power Dissipation Soldering Temperature ⋅ Time

(Leaded) /

Lead Free

Note : 1. HY57V561620CT Series : Nomal power & Leaded 54Pin TSOP II 2. HY57V561620CLT Series : Low power & Leaded 54Pin TSOP II 3. HY57V561620CTP Series : Nomal power & Lead Free 54Pin TSOP II 4. HY57V561620CLTP Series : Low power & Lead Free 54Pin TSOP II

HY57V561620(TSOP-54)HYNIX牌子

HY57V561620(L)T4Banks x 4M x 16Bit Synchronous DRAM This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any DESCRIPTIONThe HY57V561620T is a 268,435,456bit CMOS Synchronous DRAM, ideally suited for the main memory applications which require large memory density and high bandwidth. HY57V561620 is organized as 4 banks of 4,194,304x16. The HY57V561620T is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.Programmable options include the length of pipeline ( CAS latency of 2 or 3), the number of consecutive read or write cycles initiated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipelined design is not restricted by a `2N` rule.)FEATURES•Single 3.3V ± 0.3V power supply•All device pins are compatible with LVTTL interface•JEDEC standard 400mil 54pin TSOP-II with 0.8mmof pin pitch•All inputs and outputs referenced to positive edge ofsystem clock•Data mask function by UDQM and LDQM•Internal four banks operation•Auto refresh and self refresh•8192 refresh cycles / 64ms•Programmable Burst Length and Burst Type- 1, 2, 4, 8 and Full Page for Sequential Burst- 1, 2, 4 and 8 for Interleave Burst•Programmable CAS Latency ; 2, 3 Clocks ORDERING INFORMATIONPart No.Clock Frequency Power Organization Interface PackageHY57V561620T-HP133MHzNormal4Banks x 4Mbitsx16LVTTL400mil 54pin TSOP II HY57V561620T-H133MHzHY57V561620T-8125MHzHY57V561620T-P100MHzHY57V561620T-S100MHzHY57V561620LT-HP133MHzLowerPowerHY57V561620LT-H133MHzHY57V561620LT-8125MHzHY57V561620LT-P100MHzHY57V561620LT-S100MHzPIN DESCRIPTIONPIN PIN NAME DESCRIPTIONCLK Clock The system clock input. All other inputs are registered to the SDRAM on the rising edge of CLKCKE Clock Enable Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or self refreshCS Chip Select Enables or disables all inputs except CLK, CKE, UDQM and LDQMBA0, BA1Bank Address Selects bank to be activated during RAS activity Selects bank to be read/written during CAS activityA0 ~ A12Address Row Address : RA0 ~ RA12, Column Address : CA0 ~ CA8 Auto-precharge flag : A10RAS, CAS, WE Row Address Strobe, Col-umn Address Strobe, WriteEnableRAS, CAS and WE define the operationRefer function truth table for detailsUDQM, LDQM Data Input/Output Mask Controls output buffers in read mode and masks input data in write mode DQ0 ~ DQ15Data Input/Output Multiplexed data input / output pinV DD/V SS Power Supply/Ground Power supply for internal circuits and input buffersV DDQ/V SSQ Data Output Power/Ground Power supply for output buffersNC No Connection No connectionFUNCTIONAL BLOCK DIAGRAM4Mbit x 4banks x16 I/O Synchronous DRAMABSOLUTE MAXIMUM RATINGSParameter Symbol Rating Unit Ambient Temperature T A0 ~ 70°CStorage Temperature T STG-55 ~ 125°CVoltage on Any Pin relative to V SS V IN, V OUT-1.0 ~ 4.6VVoltage on V DD relative to V SS V DD, V DDQ-1.0 ~ 4.6VShort Circuit Output Current I OS50mAPower Dissipation P D1WSoldering Temperature ⋅ Time T SOLDER260 ⋅ 10°C⋅ SecNote : Operation at above absolute maximum rating can adversely affect device reliabilityDC OPERATING CONDITION (TA=0 to 70°C)Parameter Symbol Min Typ.Max Unit Note Power Supply Voltage V DD, V DDQ 3.0 3.3 3.6V1 Input High Voltage V IH 2.0 3.0V DDQ + 0.3V1,2 Input Low Voltage V IL VSSQ-2.000.8V1,3 Note :1. All voltages are referenced to V SS = 0V2. V IH (max) is acceptable 5.6V AC pulse width with ≤3ns of duration3. V IL (max) is acceptable -2.0V AC pulse width with ≤3ns of durationAC OPERATING CONDITION (TA=0 to 70°C, V DD=3.3 ± 0.3V, V SS=0V)Parameter Symbol Value Unit Note AC Input High / Low Level Voltage V IH / V IL 2.4/0.4VInput Timing Measurement Reference Level Voltage Vtrip 1.4VInput Rise / Fall Time tR / tF1nsOutput Timing Measurement Reference Level Voutref 1.4VOutput Load Capacitance for Access Time Measurement CL50pF1 Note :1. Output load to measure access time is equivalent to two TTL gates and one capacitor (50pF)For details, refer to AC/DC output circuitCAPACITANCE (TA=25°C , f=1MHz)OUTPUT LOAD CIRCUITDC CHARACTERISTICS I (TA=0 to 70°C , V DD =3.3±0.3V)Note :1. V IN = 0 to 3.6V, All other pins are not under test = 0V2. D OUT is disabled, V OUT =0 to3.6VParameterPinSymbol-H-8/P/SUnitMinMax Min Max Input capacitanceCLKC I1 2.5 3.5 2.5 4.0pF A0 ~ A12, BA0, BA1, CKE, CS, RAS, CAS, WE, UDQM, LDQMCI 2 2.5 3.8 2.5 5.0pF Data input / output capacitanceDQ0 ~ DQ15C I/O4.06.54.06.5pFParameterSymbolMin.Max Unit Note Input leakage current I LI -11uA 1Output leakage current I LO -11uA 2Output high voltage V OH 2.4-V I OH = -4mA Output low voltageV OL-0.4VI OL =+4mADC CHARACTERISTICS II (TA=0°C to 70°C , V DD =3.3V ± 0.3V, V SS =0V)Note :1. I DD1 and I DD4 depend on output loading and cycle rates. Specified values are measured with the output open.2. Min. of tRRC (Refresh RAS cycle time) is shown at AC CHARACTERISTICS II3. HY57V561620T-HP/H/8/P/S4. HY57V561620LT-HP/H/8/P/SParameterSymbolTest ConditionSpeedUnitNote-HP-H -8-P -S Operating CurrentIDD1Burst Length=1, One bank activetRAS ≥ tRAS(min),tRP ≥ tRP(min), IO=0mA 120120110100100mA1Precharge Standby Current in power down modeIDD2P CKE ≤ VIL(max), tCK = min.2mAIDD2PSCKE ≤ VIL(max), tCK = ∞2Precharge Standby Current in non power down modeIDD2NCKE ≥ VIH(min), CS ≥ VIH(min), tCK = minInput signals are changed one time during 2clks. All other pins ≥ VDD-0.2V or ≤ 0.2V 20mAIDD2NS CKE ≥ VIH(min), tCK = ∞Input signals are stable.10Active Standby Current in power down modeIDD3P CKE ≤ VIL(max), tCK = min 3mAIDD3PSCKE ≤ VIL(max), tCK = ∞3Active Standby Current in non power down modeIDD3NCKE ≥ VIH(min), CS ≥ VIH(min), tCK = minInput signals are changed one time during 2clks. All other pins ≥ VDD-0.2V or ≤ 0.2V 25mAIDD3NSCKE ≥ VIH(min), tCK = ∞Input signals are stable 15Burst Mode Operating CurrentIDD4tCK ≥ tCK(min),tRAS ≥ tRAS(min), IO=0mA All banks active150150*********mA 1Auto Refresh CurrentIDD5tRRC ≥ tRRC(min), All banks active260260260250250mA 2Self Refresh Current IDD6CKE ≤ 0.2V3mA 31.5mA4AC CHARACTERISTICS INote :1. Assume tR / tF (input rise and fall time ) is 1ns.2. Access times to be measured with input signals of 1v/ns slew rate, 0.8v to 2.0vParameterSymbol-HP-H-8-P-SUnitNoteMinMaxMin MaxMin MaxMin MaxMin MaxSystem clock cycle timeCAS Latency = 3tCK37.510007.5100081000101000101000nsCAS Latency = 2tCK21010101012ns Clock high pulse width tCHW 2.5- 2.5-3-3-3-ns 1Clock low pulse width tCLW 2.5- 2.5-3-3-3-ns 1Access time from clockCAS Latency = 3tAC3- 5.4- 5.4-666ns2CAS Latency = 2tAC2-6-6-666ns Data-out hold time tOH 2.7- 2.7-3-3-3-ns Data-Input setup time tDS 1.5- 1.5-2-2-2-ns 1Data-Input hold time tDH 0.8-0.8-1-1-1-ns 1Address setup time tAS 1.5- 1.5-2-2-2-ns 1Address hold time tAH 0.8-0.8-1-1-1-ns 1CKE setup time tCKS 1.5- 1.5-2-2-2-ns 1CKE hold time tCKH 0.8-0.8-1-1-1-ns 1Command setup time tCS 1.5- 1.5-2-2-2-ns 1Command hold timetCH 0.8-0.8-1-1-1-ns 1CLK to data output in low Z-time tOLZ 1-1-1-1-1-ns CLK to data output in high Z-timeCAS Latency = 3tOHZ3 2.7 5.4 2.7 5.4363636ns CAS Latency = 2tOHZ23636363636nsAC CHARACTERISTICS IINote :1. A new command can be given tRRC after self refresh exit.ParameterSymbol-HP-H-8-P-SUnitNoteMinMax Min Max Min Max Min Max Min Max RAS cycle timeOperationtRC65-65-68-70-70-nsAuto RefreshtRRC 65-65-68-70-70-ns RAS to CAS delay tRCD 20-20-20-20-20-ns RAS active time tRAS 45100K 45100K 48100K 50100K 50100K ns RAS precharge timetRP 20-20-20-20-20-ns RAS to RAS bank active delay tRRD 15-15-16-20-20-ns CAS to CAS delaytCCD 1-1-1-1-1-CLK Write command to data-in delay tWTL 0-0-0-0-0-CLK Data-in to precharge command tDPL 2-2-2-2-2-CLK Data-in to active command tDAL 5-5-5-4-4-CLK DQM to data-out Hi-Z tDQZ 2-2-2-2-2-CLK DQM to data-in mask tDQM 0-0-0-0-0-CLK MRS to new command tMRD 2-2-2-2-2-CLK Precharge to data output Hi-ZCAS Latency = 3tPROZ33-3-3-3-3-CLK CAS Latency = 2tPROZ2------2-2-CLK Power down exit time tPDE 1-1-1-1-1-CLK Self refresh exit time tSRE 1-1-1-1-1-CLK 1Refresh TimetREF-64-64-64-64-64msIBIS SPECIFICATION** IBIS spec. is also applied to 133MHz device.I OH Characteristics (Pull-up) 66MHz and 100MHz Pull-upVoltage 100MHz Min 100MHz Max 66MHz Min(V)I (mA)I (mA)I (mA)3.45-2.43.3-27.33.00.0-74.1-0.72.6-21.1-129.2-7.52.4-34.1-153.3-13.32.0-58.7-197.0-27.51.8-67.3-226.2-35.51.65-73.0-248.0-41.11.5-77.9-269.7-47.91.4-80.8-284.3-52.41.0-88.6-344.5-72.50.0-93.0-502.4-93.0I OL Characteristics (Pull-down) 66MHz and 100MHz Pull-downVoltage 100MHz Min 100MHz Max 66MHz Min (V)I (mA)I (mA)I (mA)0.00.00.00.00.427.570.217.70.6541.8107.526.90.8551.6133.833.31.058.0151.237.61.470.7187.746.61.572.9194.448.01.6575.4202.549.51.877.0208.650.71.9577.6212.051.53.080.3219.654.23.4581.4222.654.9V DD Clamp @ CLK, CKE, CS, DQM & DQV DD (V)I(mA)0.00.00.20.00.40.00.60.00.70.00.80.00.90.01.00.231.2 1.341.4 3.021.6 5.061.87.352.09.832.212.482.415.302.618.31V SS Clamp @ CLK, CKE, CS, DQM & DQ V SS (V)I (mA)-2.6-57.23-2.4-45.77-2.2-38.26-2.0-31.22-1.8-24.58-1.6-18.37-1.4-12.56-1.2-7.57-1.0-3.37-0.9-1.75-0.8-0.58-0.7-0.05-0.60.0-0.40.0-0.20.00.00.0 Minimum V DD clamp current (Referenced to V DD) Minimum V SS clamp currentDEVICE OPERATING OPTION TABLEHY57V561620(L)T-HPCAS Latency tRCD tRAS tRC tRP tAC tOH 133MHz(7.5ns)3CLKs3CLKs6CLKs9CLKs3CLKs 5.4ns 2.7ns 125MHz(8ns)3CLKs3CLKs6CLKs9CLKs3CLKs6ns3ns 100MHz(10ns)2CLKs2CLKs5CLKs7CLKs2CLKs6ns3nsHY57V561620(L)T-HCAS Latency tRCD tRAS tRC tRP tAC tOH 133MHz(7.5ns)3CLKs3CLKs6CLKs9CLKs3CLKs 5.4ns 2.7ns 125MHz(8ns)3CLKs3CLKs6CLKs9CLKs3CLKs6ns3ns 100MHz(10ns)3CLKs3CLKs6CLKs9CLKs3CLKs6ns3nsHY57V561620(L)T-8CAS Latency tRCD tRAS tRC tRP tAC tOH 125MHz(8ns)3CLKs3CLKs6CLKs9CLKs3CLKs6ns3ns 100MHz(10ns)3CLKs3CLKs6CLKs9CLKs3CLKs6ns3ns 83MHz(12ns)2CLKs2CLKs4CLKs6CLKs2CLKs6ns3nsHY57V561620(L)T-PCAS Latency tRCD tRAS tRC tRP tAC tOH 100MHz(10ns)2CLKs2CLKs5CLKs7CLKs2CLKs6ns3ns 83MHz(12ns)2CLKs2CLKs5CLKs7CLKs2CLKs6ns3ns 66MHz(15ns)2CLKs2CLKs4CLKs6CLKs2CLKs6ns3nsHY57V561620(L)T-SCAS Latency tRCD tRAS tRC tRP tAC tOH 100MHz(10.0ns)3CLKs2CLKs5CLKs7CLKs2CLKs6ns3ns 83MHz(12.0ns)2CLKs2CLKs5CLKs7CLKs2CLKs6ns3ns 66MHz(15.0ns)2CLKs2CLKs4CLKs6CLKs2CLKs6ns3nsCOMMAND TRUTH TABLENote :1. OP Code : Operand Code2. V = Valid, X = Don’t care, H = Logic High, L= Logic Low, RA = Row Address, CA = Column Address.CommandCKEn-1CKEn CS RAS CAS WE DQM ADDRA10/AP BA Note Mode Register Set H X L L L L XOP code1No Operation H XHXXXXXLH H H Bank Active HXLLHHXRAVReadHXLHLHXCALV Read with Autoprecharge H WriteHXLHLLXCALVWrite with Autoprecharge H Precharge All BanksHXLLHLXXHXPrecharge selected Bank L VBurst Stop H XLH HLX X UDQM, LDQM H X V X Auto RefreshH H L L L H X XSelf RefreshEntryHLL L L H XXExitLHHXXXXL H H H Precharge power downEntryHLHXXXXXL H H HExitLHHXXXXL H H H Clock SuspendEntry H LHXXXXXLVVVExitLHXXPACKAGE INFORMATION400mil 54pin Thin Small Outline Package。

2012培训教材-轻中卡操纵部分解析

3

2012年培训教材

2012年培训教材

轻卡变速器操纵部分大致相同(见图1),不同的地 方在于使用不同变速器时所用的软轴固定支架、软轴及挡 位标牌不同,见表1。

4

2012年培训教材

2012年培训教材

图1

5

2012年培训教材

变速器型号 HW20505TCL HW24505TCL 布置型式 变速器左操纵 变速器左操纵 变速器左操纵 HW25505TCL 变速器右操纵 软轴 选LG9704240010(2400) 手柄 LG9704240026 LG9704240003 LG9704240003 LG9704240002 软轴支架 LG9704240032 LG9704240032 LG9704240011 LG9704240019

2012年培训教材

2012年培训教材

轻型卡车变速器操纵部分结构简介

技术中心 2012年2月

2012年培训教材

2012年培训教材

2012年培训教材

2012年培训教材

目前我公司轻卡系列车型变速器操纵采用双软轴操纵, 该结构布置方便,结构简单,便于模块化装配。 通过优化设计,合理布置软轴走向,支架结构简单,重 量轻。 挡位清晰,换选挡力度适中。

2012年培训教材

26

2012年培训教材

2012年培训教材

图7

27

2012年培训教材

(6)软轴及气管走向与固定

2012年培训教材

轻卡系列车型使用的软轴最小转弯半径为200mm,因此

在固定软轴时要避免软轴直径小于200mm。软轴使用扎带固 定,避免和其他运动部件磨碰、干涉,尽可能远离排气管。 装HW50508C变速器时气管顺着软轴进入驾驶室,和软轴捆绑 在一起。

威盛WM8650中文说明书V0.3(7寸)

资料来源:爱购机目录................................................................................................... 错误!未定义书签。

1 外观描述 (2)2 电源键的用法 (3)3 触摸屏 (4)4转接盒 (4)5 SD卡的使用 (5)6开始使用 (5)给设备充电 (5)启动设备 (5)Wi-Fi 网络设置 (5)7桌面 (5)8锁屏界面 (6)9预装程序 (7)10桌面菜单功能 (8)11 程序管理 (10)安装程序 (10)直接从网络上下载程序 (10)卸载程序 (10)12 天气 (10)13 时钟 (11)闹钟 (11)14在线软件安装 (12)菜单功能 (12)15浏览器 (13)16 日历 (13)新建活动 (13)17 相机 (13)拍摄图片 (13)录制视频 (14)18 计算器 (14)19 电子邮件 (14)添加邮件账户 (14)收件箱 (15)编辑邮件账户 (15)删除邮件账户 (16)20 文件浏览器 (16)在电脑和设备之间拷贝文件 (17)删除文件 (17)21 我的音乐 (17)播放音乐 (17)对音乐盒播放列表进行操作 (18)22 我的视频 (18)播放视频 (18)对视频和播放列表进行操作 (19)23 我的相册 (19)涂鸦 (20)24 通讯录 (20)添加新的联系人 (20)添加联系人到收藏 (20)编辑联系人 (20)删除联系人 (20)25 图片截取 (21)26 程序管理器 (21)停止程序 (21)卸载程序 (21)27 YouTube (21)28 土豆视频 (22)29 Wi-Fi设置 (22)30 3G Settings (22)31 连接ADSL上网 (23)32 有线网络 (23)33 设置 (23)常见问题 (25)电池管理 (26)电池充电 (26)重要安全提示 (26)附录.建议可选配件及型号 (27)1 外观描述前视图:右视图:左视图:顶视图:2 电源键的用法开机: 长按电源键2秒。

V5系列可编程逻辑控制器简易手册说明书

目录目录前言 (1)1 产品信息 (3)1.1产品解析图 (3)1.2产品尺寸 (3)2 安装指导 (4)2.1 环境要求 (4)2.2 安装位置与空间 (4)2.3安装方法 (4)3 接线与规格 (5)3.1 接线要求 (5)3.2 规格要求 (5)3.3 输入输出端子介绍 (6)3.4输入接线 (7)3.4.1普通输入接线说明 (7)3.4.2 差分输入接线说明 (7)3.4.3 故障输入接线说明 (8)3.5 输出接线 (8)3.5.1 普通/高速晶体管输出接线说明 (8)3.5.2 高速差分输出接线说明 (9)3.5.3 使能输出接线说明 (9)3.6 模拟量输入电路 (9)4 通信指导 (10)5 附录 (11)前言首先感谢您购买使用V5系列可编程控制器!V5系列可编程控制器是结合全球领先的控制算法开发的一款全新产品。

本产品支持点动运动、直线插补、圆弧、3D 圆弧、电子齿轮/凸轮等功能;内嵌大量方便行业功能块,如追剪、飞剪、防空等功能块,使应用变得非常简单;集成同步跟随、全闭环控[2] 定义为4轴输入,作为手摇轮输入或者反馈输入,可接收差分信号输入。

[3] 定义为4轴输出,每个轴包括2组差分输出,可作为AB 相输出,CW/CCW 输出方式或者脉冲加方向方式。

[4]CAN 支持CANopen DS301以及CANopen DS402主站以及从站协议。

安全注意事项:请由专业的操作人员按照正常步骤使用本产品,使用过程中注意以下安全相关的注意事项,否则可能导致对人体的伤害或财产损失。

其中安全注意事项定义如下。

危险:如果操作错误,极有可能会导致死亡或重伤; 警告:如果操作错误,可能会导致死亡或重伤;1 产品信息1.1产品解析图91087654321WHDD11211131.2产品尺寸2 安装指导2.1 环境要求2.2 安装位置与空间1 安装时请注意安装位置,务必水平安装。

2 安装时请务必考虑散热情况,务必保证控制器及其模块距离A>50mm:2.3安装方法本产品V5系列可以采用DIN轨道(DIN46277,宽35mm)安装。

CL57 使用手册说明书

目录1.产品概述 (1)2.应用环境及安装 (2)2.1应用环境要求 (2)2.2驱动器安装尺寸 (3)3.驱动器端口和接线 (4)3.1端口功能说明 (4)3.2电源输入 (4)3.3编码器连线 (4)3.3电机连线 (5)3.5控制信号连线 (5)3.5.1PUL、DIR端口 (5)3.5.2ENA端口 (5)3.5.3ALM端口 (5)3.5.4控制信号接线实例 (6)3.6RS232串口 (7)4.拨码及运行参数设置 (7)4.1每转脉冲设置 (7)4.2电机方向选择 (8)4.3脉冲滤波功能选择 (8)4.4脉冲模式选择 (8)4.5带宽选择 (8)5.驱动器工作状态LED指示 (8)6.常见问题及对策 (9)附录A.保修条款 (9)1.产品概述感谢您选择CL系列数字式步进伺服驱动器。

步进伺服,是在普通开环步进电机的基础上,结合位置反馈和伺服算法形成的高速、高扭矩、高精度、低振动、低发热、不丢步的步进伺服方案。

CL系列步进伺服驱动器,基于TI公司全新32位DSP处理芯片的平台,利用伺服驱动器中磁场定向(FOC)和矢量弱磁控制算法设计,具有全方位超越普通步进的性能表现。

内置PID参数调节功能,使电机更好的满足不同种类负载的应用;内置弱磁控制算法,使电机高速时磁场特性减弱,保持动力;内置电流矢量控制功能,使电机具有伺服的电流特性,发热低;内置微步指令算法,使电机运行各速度段时保持平稳、低振动;内置4000pulse分辨率的编码器反馈,使定位精度提高,绝不丢步。

总之,结合步进电机特性的伺服控制方案使得CL系列步进伺服驱动器能更好的发挥步进电机的性能,可替代相同功率的伺服应用,是自动化设备最优性价比的新选择。

CL57驱动器可通过拨码开关和调试软件设置细分及其他参数,具有电压、电流、位置等保护功能,增添报警输出接口,其输入输出信号均采用光电隔离。

供电电源24–60VDC控制精度4000Pulse/r脉冲模式方向&脉冲、CW/CCW双脉冲电流控制伺服矢量控制算法细分设置拨码开关设定,16种选择(或调试软件设定)速度范围常规1200~1500rpm,最高4000rpm共振抑制自动计算共振点,抑制中频振动PID参数调节调试软件调整电机PID特性脉冲滤波2MHz数字信号滤波器报警输出过流、过压、位置错误等报警输出希望我们优异性能的产品,可以帮您出色的完成运动控制项目。

长虹电视超级芯片与高频头代换大全

For personal use only in study and research; not forcommercial use长虹电视超级芯片与高频头代换大全CH-16机芯微处理器的代换1.CH05T1602、CH05T1604、CH05T1607三者间可以相互直接代换,代换后若机器出现TV无伴音,则将总线数据中OP2项置于64。

2.CH05T1609、CH05T1623,1631三者间可以相互代换,但代换时,应注意:使用CH05T1609芯片时,主板上C171容量应为1200PF;使用CH05T1623芯片时,主板上C171容量应为3900PF。

3.CH05T1609、CH05T1623与CH05T1602、CH05T1604、CH05T1607不能互换,因为两者间软件截然不同,前者为飞利浦软件,后者为四川长虹统一软件。

4.CH05T1601与CH05T1603可以相互代换,但要注意以下几点:①CH05T1601应对应TDA9383“N2H”版本(IC表面最下面中间有“N2H”字样),同时相关元件位号、型号对应如下:R171-0.166W/2.7KΩ;C171-63V/4700PF;C171A-63V/820PF;②CH05T1603对应TDA9383“N2I”版本(IC表面最下面中间有“N2H”字样),同时相关元件位号、型号对应如下:R171-0.166W/3.9KΩ;C171-63V/1200PF;C171A-63V/330PF。

③CH05T1601与CH05T1603互换,需更换外围元件;④用CH05T1601或CH05T1603代换TDA9383PS时,应注意TDA9383PS的版本及与CH05T1601、CH05T1603的对应关系,并更改相应的外围元件;5.CH05T1606与CH05T1608可以互换,但OSD显示风格及EEPROM数据不同,代换时需征得用户同意。

6.CH05T1619可以代换CH05T1608,但EEPROM数据不同,总线数据中增加一调节项“PWL”,该数据设置为“14”,CH05T1619与CH05T1608 OSD显示风格相同。

HY57V161610ETP-7I中文资料

This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any responsibility for use of circuits described. No patent licenses are impliedRev. 0.1 / Nov. 2003 12 Banks x 512K x 16 Bit Synchronous DRAMDESCRIPTIONTHE Hynix HY57V161610E is a 16,777,216-bits CMOS Synchronous DRAM, ideally suited for the main memory and graphic appli-cations which require large memory density and high bandwidth. HY57V161610E is organized as 2banks of 524,288x16.HY57V161610E is offering fully synchronous operation referenced to a positive edge clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.Programmable options include the length of pipeline (Read latency of 1,2 or 3), the number of consecutive read or write cycles initi-ated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipeline design is not restricted by a `2N` rule.)FEATURES•Single 3.0V to 3.6V power supply•All device pins are compatible with LVTTL interface •JEDEC standard 400mil 50pin TSOP-II with 0.8mm of pin pitch•All inputs and outputs referenced to positive edge of system clock•Data mask function by UDQM/LDQM •Internal two banks operation•Auto refresh and self refresh •4096 refresh cycles / 64ms•Programmable Burst Length and Burst Type - 1, 2, 4, 8 and Full Page for Sequence Burst - 1, 2, 4 and 8 for Interleave Burst•Programmable CAS Latency ; 1, 2, 3 Clocks •Pb-free PackageORDERING INFORMATIONPart No.Clock FrequencyOrganization Interface PackageHY57V161610ETP-5I 200MHz 2Banks x 512Kbits x 16LVTTL400mil 50pin TSOP II (Pb free)HY57V161610ETP-55I 183MHz HY57V161610ETP-6I 166MHz HY57V161610ETP-7I 143MHz HY57V161610ETP-8I 125MHz HY57V161610ETP-10I 100MHz HY57V161610ETP-15I66MHzNote :1. VDD(min) of HY57V161610ETP-5I/55I is 3.15V2. Hynix supports lead free part for each speed grade with same specification.Rev. 0.1 / Nov. 2003 2PIN CONFIGURATIONPIN DESCRIPTIONPINPIN NAMEDESCRIPTIONCLK Clock The system clock input. All other inputs are referenced to the SDRAM on the rising edge of CLK.CKE Clock Enable Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or self refresh.CS Chip Select Command input enable or mask except CLK, CKE and DQM BA Bank Address Select either one of banks during both RAS and CAS activity.A0 ~ A10AddressRow Address : RA0 ~ RA10, Column Address : CA0 ~ CA7Auto-precharge flag : A10RAS, CAS, WE Row Address Strobe,Column Address Strobe, Write EnableRAS, CAS and WE define the operation.Refer function truth table for detailsLDQM, UDQM Data Input/Output Mask DQM control output buffer in read mode and mask input data in write mode DQ0 ~ DQ15Data Input/Output Multiplexed data input / output pinV DD /V SS Power Supply/Ground Power supply for internal circuit and input buffer V DDQ /V SSQ Data Output Power/Ground Power supply for DQ NCNo ConnectionNo connectionRev. 0.1 / Nov. 2003 3FUNCTIONAL BLOCK DIAGRAM1Mx16 Synchronous DRAMRev. 0.1 / Nov. 2003 4ABSOLUTE MAXIMUM RATINGSNote : Operation at above absolute maximum rating can adversely affect device reliability.DC OPERATING CONDITION (TA=0°C to 70°C )Note :1.All voltages are referenced to V SS = 0V.2.V DD (min) is3.15V when HY57V161610ETP-7I operates at CAS latency=23.V DD (min) of HY57V161610ETP-5I/55I is 3.15V4.Vih(Max) : 4.6V AC pulse width with < 3ns of duration.5.Vil(min) : -1.5V AC pulse width with < 3ns of duration.AC OPERATING CONDITION (TA=-40°C to 85°C , V DD =3.0V to 3.6V, V SS =0V)Note :1. Output load to measure access times is equivalent to two TTL gates and one capacitance(30pF). For details, refer to AC/DC output load circuit.2. V DD (min) is3.15V when HY57V161610ETP-7I operates at CAS latency=2 and tCK2=8.9ns 3. V DD (min) of HY57V161610ETP-5I/55I is 3.15V‘ParameterSymbolRatingUnitAmbient Temperature T A -40 ~ 85°C Storage TemperatureT STG -55 ~ 125°C Voltage on Any Pin relative to V SS V IN , V OUT -1.0 ~ 4.6V Voltage on V DD relative to V SS V DD -1.0 ~ 4.6V Short Circuit Output Current I OS 50mA Power DissipationP D 1W Soldering Temperature ·TimeT SOLDER260·10°C ·SecParameterSymbol Min Typ.Max Unit Note Power Supply Voltage V DD , V DDQ 3.0 3.3 3.6V 1, 2, 3Input high voltage V IH 2.0 3.0V DD + 0.3V 1, 4Input low voltageV IL-0.30.8V1, 5ParameterSymbol Value Unit NoteAC input high / low level voltageV IH / V IL 2.4/0.4V Input timing measurement reference level voltage Vtrip 1.4V Input rise / fall timetR / tF 1ns Output timing measurement reference levelVoutref 1.4V Output load capacitance for access time measurementCL30pF1Rev. 0.1 / Nov. 20035CAPACITANCE (TA=25°C , f=1MHz)DC CHARACTERISTICS I (TA=-40°C to 85°C )Note :1.V DD (min) is 3.15V when HY57V161610ETP-7I operates at CAS latency=2 and tCK2=8.9ns.2.V DD (min) of HY57V161610ETP-5I/55I is3.15V3.V IN = 0 to 3.6V, All other pins are not under test = 0V4.D OUT is disabled, V OUT =0 to 3.6VParameterPinSymbol Min Max Unit Input capacitanceCLKC I1 2.54pF A0 ~ A10, BACKE, CS, RAS, CAS, WE, UDQM, LDQM C I2 2.55pF Data input / output capacitanceDQ0 ~ DQ15C I/O46.5pFParameterSymbolMin.Max Unit Note Power Supply Voltage V DD 3.0 3.6V 1, 2Input leakage current IL -11uA 3Output leakage current IO -11uA 4Output high voltage V OH 2.4-V I OH = -4mA Output low voltageV OL-0.4VI OL =+4mARev. 0.1 / Nov. 20036DC CHARACTERISTICS II (TA= -40°C to 85°C , V DD =3.0V to 3.6V, V SS =0V Note1,2)Note :1.V DD (min) is 3.15V when HY57V161610ETP-7I operates at CAS latency=2 and tCK2=8.9ns.2.V DD (min) of HY57V161610ETP-5I/55I is3.15V3.I DD1 and I DD4 depend on output loading and cycle rates. Specified values are measured with the output open.ParameterSymbolTest ConditionSpeedUnitNote-5-55-6-7-8-10-15Operating Current IDD1Burst Length=1, One bank active tRAS ≥ tRAS(min),tRP ≥ tRP(min), IO=0mA130130120110110110100mA 2Precharge Standby Currentin power down modeIDD2P CKE ≤ VIL(max), tCK = 15ns 2mAIDD2PSCKE ≤ VIL(max), tCK = ∞1Precharge Standby Currentin non power down modeIDD2N CKE ≥ VIH(min), CS ≥ VIH(min), tCK = 15nsInput signals are changed one time during 2Clks. All other pins ≥ VDD-0.2V or ≤ 0.2V25mAIDD2NS CKE ≥ VIH(min), tCK = ∞Input signals are stable.15Active Standby Current in power down modeIDD3P CKE ≤ VIL(max), tCK = min 3.0mAIDD3PSCKE ≤ VIL(max), tCK = ∞3.0Active Standby Current in non power down modeIDD3N CKE ≥ VIH(min), CS ≥ VIH(min), tCK = minInput signals are changed one time during 2CLKs. All other pins ≥ VDD-0.2V or ≤ 0.2V50mAIDD3NS CKE ≥ VIH(min), tCK = ∞Input signals are stable30Burst Mode Operating CurrentIDD4tCK ≥ tCK(min), tRAS ≥ tRAS(min), IO=0mAAll banks activeCL=31301301201101109080mA3CL=2--110110---CL=1------70Auto Refresh Current IDD5tRRC ≥ tRRC(min), All banks active 130130110110110110100mA Self Refresh CurrentIDD6CKE ≤ 0.2V2mARev. 0.1 / Nov. 20037AC CHARACTERISTICS (TA=-40°C to 85°C , V DD =3.0V to 3.6V, V SS =0V Note1,2)ParameterSymbol-5-55-6-7UnitNoteMinMaxMin MaxMin Max Min Max System clock cycle timeCL=3tCK35 5.56-7-nsCL=2tCK2--10-10-3CL=1tCK1------Clock high pulse width tCHW 222- 2.5-ns 4Clock low pulse widthtCLW 222- 2.5-ns4Access time from clockCL=3tAC3 4.55- 5.5-6nsCL=2tAC2-6-63CL=1tAC1----Data-out hold time tOH 1.522- 2.5-ns Data-Input setup time tDS 1.5 1.5 1.5- 1.75-ns 4Data-Input hold time tDH 111-1-ns 4Address setup time tAS 1.5 1.5 1.5- 1.75-ns 4Address hold time tAH 111-1-ns 4CKE setup time tCKS 1.5 1.5 1.5- 1.75-ns 4CKE hold time tCKH 111-1-ns 4Command setup time tCS 1.5 1.5 1.5- 1.75-ns 4Command hold time tCH111-1-ns4CLK to data output in low Z-timetOLZ 222-2-nsCLK to data output in high Z-timetOHZ 252 5.52627nsRev. 0.1 / Nov. 20038AC CHARACTERISTICS (TA=-40°C to 85°C , V DD =3.0V to 3.6V, V SS =0V Note1,2) - continued -Note :1.V DD (min) is 3.15V when HY57V161610ETP-7I operates at CAS latency=2 and tCK2=8.9ns.2.V DD (min) of HY57V161610ETP-5I/55I is3.15V3.tCK2 is 8.9ns only when tAC2 is 7.9ns in HY57V161610ETP-6I and HY57V161610ETP-7I.4.Assume tR / tF (input rise and fall time ) is 1ns.ParameterSymbol-8-10-15UnitNoteMinMax Min Max Min Max System clock cycle timeCL=3tCK38-10-15-nsCL=2tCK212-12-15-3CL=1tCK1----15-Clock high pulse width tCHW 3-3-3-ns 4Clock low pulse widthtCLW 3-3-3-ns4Access time from clockCL=3tAC3-6-7-7nsCL=2tAC2-6-7-73CL=1tAC1-----14Data-out hold time tOH 2.5- 2.5- 2.5-ns Data-Input setup time tDS 2- 2.5- 2.5-ns 4Data-Input hold time tDH 1-1-1-ns 4Address setup time tAS 2- 2.5- 2.5-ns 4Address hold time tAH 1-1-1-ns 4CKE setup time tCKS 2- 2.5- 2.5-ns 4CKE holdtime tCKH 1-1-1-ns 4Command setup time tCS 2- 2.5- 2.5-ns 4Command hold timetCH 1-1-1-ns 4CLK to data output in low Z-time tOLZ 2-2-2-ns CLK to data output in high Z-timetOHZ28310315nsRev. 0.1 / Nov. 2003 9AC CHARACTERISTICS (TA=-40°C to 85°C , V DD =3.0V to 3.6V, V SS =0V Note1,2))ParamterSymbol-5-55-6-7UnitNoteMinMaxMin MaxMin Max Min Max RAS cycle timeOperationtRC555560-70-nsAuto RefreshtRRC 555560-70-ns RAS to CAS delay tRCD 1516.518-20-ns RAS active time tRAS 40100K38.5100K40100K 45100K ns RAS precharge timetRP 333-3-CLK RAS to RAS bank active delay tRRD 222-2-CLK CAS to CAS bank active delay tCCD 111-1-CLK Write command to data-in delay tWTL 000-0-CLK Data-in to precharge command tDPL 111-1-CLK Data-in to active command tDAL 544-4-CLK DQM to data-in Hi-Z tDQZ 222-2-CLK DQM to data mask tDQM 000-0-CLK MRS to new command tMRD 222-2-CLK Precharge to data output Hi-Z tPROZ 333-3-CLK Power down exit time tPDE 111-1-CLK Self refresh exit time tSRE 111-1-CLK 3Refresh TimetREF6464-64-64msRev. 0.1 / Nov. 200310AC CHARACTERISTICS (TA=-40°C to 85°C , V DD =3.0V to 3.6V, V SS =0V Note1,2) - continued -Note :1. V DD (min) is 3.15V when HY57V161610ETP-7I operates at CAS latency=2 and tCK2=8.9ns.2.V DD (min) of HY57V161610ETP-5I/55I is3.15V3. A new command can be given tRRC after self refresh exit.DEVICE OPERATING OPTION TABLEHY57V161610ETP-5IParamterSymbol-8I-10I-15IUnitNoteMinMax Min Max Min Max RAS cycle timeOperationtRC70-70-70-nsAuto RefreshtRRC 70-80-80-ns RAS to CAS delay tRCD 20-20-20-ns RAS active time tRAS 45100K 45100K 45100K ns RAS precharge timetRP 3-2-2-CLK RAS to RAS bank active delay tRRD 2-2-2-CLK CAS to CAS bank active delay tCCD 1-1-1-CLK Write command to data-in delay tWTL 0-0-0-CLK Data-in to precharge command tDPL 1-1-1-CLK Data-in to active command tDAL 4-3-3-CLK DQM to data-in Hi-Z tDQZ 2-2-2-CLK DQM to data mask tDQM 0-0-0-CLK MRS to new command tMRD 2-2-2-CLK Precharge to data output Hi-Z tPROZ 3-3-3-CLK Power down exit time tPDE 1-1-1-CLK Self refresh exit time tSRE 1-1-1-CLK 3Refresh TimetREF-64-64-64msCAS LatencytRCD tRAS tRC tRP tAC tOH 200MHz 3CLKs 3CLKs 8CLKs 11CLKs 3CLKs 4.5ns 1.5ns 183MHz 3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5ns 2ns 166MHz3CLKs3CLKs7CLKs10CLKs3CLKs5.5ns2nsRev. 0.1 / Nov. 2003 11HY57V161610ETP-55IHY57V161610ETP-6IHY57V161610ETP-7IHY57V161610ETP-8IHY57V161610ETP-10IHY57V161610ETP-15ICAS LatencytRCD tRAS tRC tRP tAC tOH 183MHz 3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5ns 2ns 166MHz 3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5.5ns 2ns 143MHz3CLKs3CLKs7CLKs10CLKs3CLKs5.5ns2.5nsCAS LatencytRCD tRAS tRC tRP tAC tOH 166MHz 3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5.5ns 2ns 143MHz 3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5.5ns 2.5ns 125MHz3CLKs2CLKs6CLKs9CLKs3CLKs6ns2.5nsCAS LatencytRCD tRAS tRC tRP tAC tOH 143MHz 3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5.5ns 2.5ns 125MHz 3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 6ns 2.5ns 100MHz2CLKs2CLKs5CLKs7CLKs2CLKs7ns2.5nsCAS LatencytRCD tRAS tRC tRP tAC tOH 125MHz 3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 6ns 2.5ns 100MHz 3CLKs 2CLKs 5CLKs 7CLKs 2CLKs 7ns 2.5ns 83MHz2CLKs2CLKs4CLKs6CLKs2CLKs7ns2.5nsCAS LatencytRCD tRAS tRC tRP tAC tOH 100MHz 3CLKs 2CLKs 5CLKs 7CLKs 2CLKs 7ns 2.5ns 83MHz2CLKs2CLKs4CLKs6CLKs2CLKs7ns2.5nsCAS LatencytRCD tRAS tRC tRP tAC tOH 66MHz1CLKs2CLKs4CLKs6CLKs2CLKs14ns2.5nsRev. 0.1 / Nov. 200312COMMAND TRUTH TABLENote :1. Exiting Self Refresh occurs by asynchronously bringing CKE from low to high.2. X=Do not care, L=Low, H=High, BA=Bank Address, RA= Row Address, CA=Column Address, Opcode=Operand Code, NOP=No Operation.CommandCKEn-1CKEn CS RAS CAS WE DQM A0~A9A10/AP BANoteMode RegisterSetHXL L L L XOPcodeNo OperationHXHXXXXXLH H H Bank Active HXLLHHXRow Address VReadHXLHLHXColumn AddressLVRead with Auto precharge H WriteHXLHLLXColumn AddressLVWrite with Auto precharge H Precharge All BankHXLLHLXXHX Precharge selected Bank L VBurst Stop H XLH HLX X U/LDQM H X V X Auto RefreshH H L L L H X XBurst-READ-Single-WRITEH X L L L L X A9 Pin High (Other Pins OP code)Self Refresh 1EntryHLL L L H XXExitLHHXXXXL H H H Precharge power downEntryHLHXXXXXL H H HExitLHHXXXXL H H H Clock SuspendEntryHLHXXXXXLVVVExitLHXXRev. 0.1 / Nov. 2003 13PACKAGE INFORMATION400mil 50pin Thin Small Outline Package (TC)1Mx16 Synchronous DRAM UNIT : mm(inch)。

SN75107BD 数据手册说明书

SN75107AJ SN75107BJ SN75108AJ SN75108BD SN75108BJ SN75108BN SN75109AJ

SN75109J

SN75109N

SN7510FA SN7510FA SN7510FA SN7510FA SN7510L SN7510L SN7510L SN7510P SN7510P SN7510P SN7511FA

N/A

IC Datasheets -

/SN7510L-datasheet.html

Shortform

Texas Instruments

Differential Video Amplifier

/SN7510L-datasheet.html

Advanced Micro Devices

Differential DriverTransmitter - ConstantCurrent Output

/SN75109N-datasheet.html

Texas Instruments

General Purpose Video Amplifier

Shortform

Texas Instruments

Differential Video Amplifier

/SN7510P-datasheet.html

Texas Instruments

General Purpose Video Amplifier

Differential Video Amplifier

/SN7510FA-datasheet.html

Texas Instruments

General Purpose Video Amplifier

PLC工业智能液晶显示器

本说明书中所提及的商标属下述公司拥有: 为友利华(河南)高科技开发有限公司产品的注册商标。 “KingView”组态王为北京亚控科技发展有限公司注册商标。 “Windows CE”为 Microsoft Corporation 嵌入式操作系统。

地 址:郑州市高新区翠竹街 1 号 10 号楼 电 话: 0371-67391605/67391606

河南友利华系统工程有限公司

800× RGB×480, TFT LCD

河南友利华系统工程有限公司

Version1.0

YD-711E _P 彩色液晶显示器

使用说明书

终端尺寸:7 英寸 图形点阵:800×480

版本

描述

修改日期

地 址:郑州市高新区翠竹街 1 号 10 号楼 电 话: 0371-67391605/67391606

网 址: http:// 传 真:0371- 67391622/67090320

第 2 页 共 73 页

河南友利华系统工程有限公司

800× RGB×480, TFT LCD

目 录

开箱检查............................................................................................................................................................................ 4 第一章 概述 .............................................................................................................................

HM62V16256CLTT-5中文资料

Features

• • • Single 2.5 V and 3.0 V supply: 2.2 V to 3.6 V Fast access time: 55 ns/70 ns (max) Power dissipation: Active: 5.0 mW/MHz (typ)(VCC = 2.5 V) : 6.0 mW/MHz (typ) (VCC = 3.0 V) Standby: 2 µW (typ) (VCC = 2.5 V) : 2.4 µW (typ) (V CC = 3.0 V) Completely static memory. No clock or timing strobe required Equal access and cycle times Common data input and output. Three state output Battery backup operation. 2 chip selection for battery backup

1. This parameter is sampled and not 100% tested.

7

HM62V16256C Series

AC Characteristics (Ta = –20 to +70°C, VCC = 2.2 V to 3.6 V, unless otherwise noted.)

Operating current Average operating current

I CC

— —

5 18

20 35

mA mA

HM62V16256C-5 I CC1

HM62V16256C-7 I CC1 I CC2

— —

M57962CL-01;中文规格书,Datasheet资料

1Gate DriverM57962CL-01Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272Hybrid Integrated Circuit For Driving IGBT ModulesDescription:M57962CL-01 is a hybridintegrated circuit designed for driving n-channel IGBT modules in any gate amplifier application. This device operates as an isolation amplifier for these modules and provides the required electrical isolation between the input and output with an opto-coupler. Short circuit protection is provided by a built in desaturation detector. A fault signal is provided if the short circuit protection is activated.Features:□Electrical Isolation betweeninput and output with opto-couplers.(V iso = 2500V RMS for 1 min.)□Two supply drive topology □Built in short circuit protectioncircuit with a pin for fault output □Variable fall time on activity ofshort circuit protection□TTL compatible input interface Application:To drive IGBT modules for inverter,AC Servo systems, UPS, CVCF inverter, and welding applications.Recommended Modules:V CES = 600V Series(up to 800A Class)V CES = 1200V Series(up to 400A Class)/Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272M57962CL-01Hybrid IC for IGBT Gate DriverAbsolute Maximum Ratings, T a =25°C unless otherwise specifiedItem Symbol Test Conditions Limit Units Supply Voltage V CC DC 18VoltsV EE DC-15Volts Input Voltage V I Applied between: 13 – 14-1 ~ 7Volts Output Voltage V O Output Voltage “H”V CC Volts Output Current I OHP Pulse Width 2µs, f ≤ 20kHz -5AmperesI OLP Pulse Width 2µs, f ≤ 20kHz5Amperes Isolation Voltage V RMS Sinewave Voltage 60Hz, 1 min.2500Volts Case T emperature T c85°C Operating Temperature T opg-20 ~ 60°C Storage Temperature t stg-25 ~ 100°C Fault Output Current I FO Applied 8 pin20mA Input Voltage V R1Applied 1 pin50Volts2/Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272M57962CL-01Hybrid IC for IGBT Gate DriverElectrical Characteristics, T a = 25°C, V CC = 15V, V EE = -10V unless otherwise specifiedCharacteristics Symbol Test Conditions Min.Typ.Max.UnitsSupply Voltage V CC Recommended Range14 15—VoltsV EE Recommended Range -7—-10Volts Pull-up Voltage on Input Side V IN Recommended Range 4.75 5.00 5.25Volts“H” Input Current I IH Recommended Range15.21619mASwitching Frequency f Recommended Range——20kHzGate Resistor R G Recommended Range2——Ω“H” Input Current I IH V IN = 5V—16—mA“H” Output Voltage V OH1314—Volts“L” Output Voltage V OL-8-9—Volts“L-H” Propagation Time t PLH I IH = 16mA—0.5 1.0µs“L-H” Rise Time t r I IH = 16mA—0.6 1.0µs“H-L” Propagation Time t PHL I IH = 16mA—0.8 1.3µs“H-L” Fall Time t f I IH = 16mA—0.4 1.0µsTimer t timer Between start and cancel 1.0— 2.0ms(under input sign “L”)Fault Output Current I FO Applied 8 pin, R = 4.7kΩ— 5.0—mAControlled Time Detect Short Circuit 1t trip1Pin1: 15V and more, Pin 2 : Open— 2.6—µsControlled Time Detect Short Circuit 2*t trip2Pin1: 15V and more,— 3.0—µsPin 2 – 4 : 1000pF (Connective Capacitance)SC Voltage V SC SC Detect Voltage15——Volts*Length of wiring of condenser controlled time detect short circuit is within 5cm from 2 and 4 pin coming and going.3/4M57962CL-01Hybrid IC for IGBT Gate DriverPowerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272AMBIENT TEMPERATURE, T a , (°C) P R O P A G A T I O N D E L A Y T I M E "L -H ", t P L H , (µs ) P R O P A G A T I O N D E L A Y T I M E "H -L ", t P H L , (µs )PROPAGATION DELAY TIME VS. AMBIENT TEMPERATURE CHARACTERISTICS (TYPICAL)1.62040601.21.41.00.60.80.20.4080INPUT SIGNAL VOLTAGE, V I , (VOLTS) P R O P A G A T I O N D E L A Y T I M E "L -H ", t P L H , (µs ) P R O P A G A T I O N D E L A Y T I M E "H -L ", t P H L , (µs )PROPAGATION DELAY TIME VS. SIGNAL VOLTAGE CHARACTERISTICS (TYPICAL)1.634561.21.41.00.60.80.20.407AMBIENT TEMPERATURE, T a , (°C)C O N T R O L L ED T I ME D E T E C T S H O R T C I R C U I T , t t r i p 1, t t r i p 2, (µs )CONTROLLED TIME DETECT VS. AMBIENT TEMPERATURE CHARACTERISTICS (TYPICAL)802040606753412080CONNECTIVE CAPACITANCE, C trip , (pF)PIN: 2 4C O N T R O L L ED T I ME D E T E C T S H O R T C I R C U I T , t t r i p , (µs )CONTROLLED TIME DETECT VS. CONNECTIVE CAPACITANCECHARACTERISTICS (TYPICAL)80200040006000675341208000AMBIENT TEMPERATURE, T a , (°C)P O W E R D I S S I P A T I O N , P D , (W A T T S )POWER DISSIPATION VS. AMBIENT TEMPERATURE(MAXIMUM RATING)020*******3412010000.020.040.080.06503040102000.1SUPPLY VOLTAGE, V CC , (VOLTS)APPLIED BETWEEN: 4 6D I S S I P A T IO N C U R R E N T , (m A )DISSIPATION CURRENT VS. SUPPLY VOLTAGE INPUT SIGNAL "L" (TYPICAL)FA L L T I M E O F S H O R T C I R C U I T , t 1, t 2, (µs )SLOW SHUTDOWN SPEED (t 1, t2) VS. C S01020C S (µF)304025205101550V pin 1V GE/分销商库存信息: POWEREXM57962CL-01。

热敏电阻器资料

匀,NTC半导体瓷的微观结构由晶粒和晶界组成,其宏观电阻由

无数个晶粒电阻和晶界电阻串联而成,存在局部“高阻区”,瞬 间大电流冲击,引起局部温度迅速上升,致使高阻处发生熔融碎 裂造成炸裂或击穿。 电极与瓷体之间的留边量不够。由于加工原因,瓷体边缘总是缺 陷较多的区域,如气孔率高、致密度不够、边缘破损等,若电极 离瓷体边缘很近,瞬间大电流冲击,则会因边缘击穿引起打火。

失效机理

对策: 选择含银量及玻璃相较高的电极,合适的印刷电极工艺,增加银层厚度 及与瓷体之间的结合力;防止焊接温度偏高出现飞银,保证导线与电极的 接触良好。 客户选型时,正常工作时的稳态电流要低于厂商提供的最大稳态电流, 一般选择不超过0.5Imax

选型

在包含有电容,电灯泡灯丝,荧光灯换流器和加热器等的电子电路中,在开关 闭合的瞬间会产生一个比正常工作电流高出百倍的突波电流,利用 NTC 热敏

术指标。B=2.303(lgR2-lgR1)/(1/T2-1/T1). ③耗散系数 它是指热敏电阻器功率耗散的变化Δ P与电阻嚣温度变化Δ T的比 值,即:H=Δ P/Δ T (mw/℃)它是描热敏电阻器工作时,阻体与外 界环境进行热量交换的一个量。

名词术语

④时间常数

在不加功率的状态下,当环境温度从一个特定温度向另一个温度

设备:数字表、温度计、 铜盘、复测机、电阻箱。

完工品:复测后电阻器

生产工序

13、包装

目的:以便于入库保存及运输。 材料:电阻器、浆糊、塑料袋、 标签、包装盒

设备:托盘天平、热合机 完工品:包装后电阻器

MF71技术参数

零功率电阻 值 (Ω) ±20% 5 5 最大稳态 电流 Imax(A) 240V载 电容 (uF) 耗散系数H (mW/℃) 热时间 工作温度 常数(s) (℃) B值 ±10%

5-7槽电脑机箱背板参考手册说明书

PCE-7B13-64B1E

13-slot BP for 14-slot chassis Segment: 1 One CPU card slot PCIe slot: Two x8 PCI-X slot: Two 64/100; Four 64/66 PCI slot: Four 32/33 Compatible with IPC chassis: IPC-610, IPC-611, IPC-630, ACP-4000, ACP-4320

ACP-1010

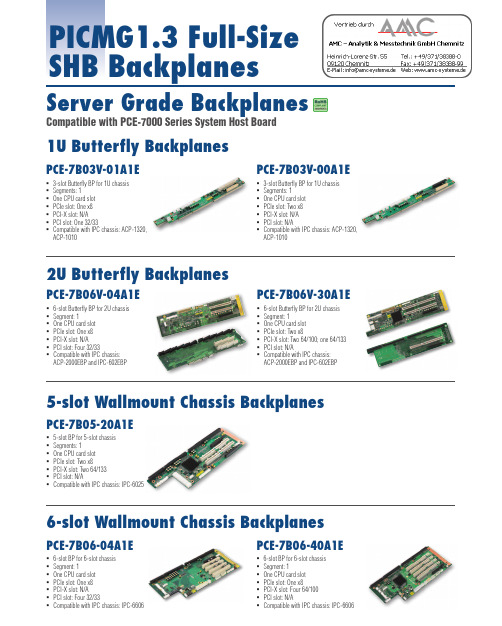

2U Butterfly Backplanes

PCE-7B06V-04A1E

6-slot Butterfly BP for 2U chassis Segment: 1 One CPU card slot PCIe slot: One x8 PCI-X slot: N/A PCI slot: Four 32/33 Compatible with IPC chassis:

PICMG1.3 Full-Size SHB Backplanes

Server Grade Backplanes

Compatible with PCE-7000 Series System Host Board

1U Butterfly Backplanes

PCE-7B03V-01A1E

3-slot Butterfly BP for 1U chassis Segments: 1 One CPU card slot PCIe slot: One x8 PCI-X slot: N/A PCI slot: One 32/33 Compatible with IPC chassis: ACP-1320,

VAMP 57多功能保护说明书

5.1 通信端口 ………………………………………………………………………………………… 53

5.1.1 远方端口………………………………………………………………………………………………………………… 53 5.1.2 以太网接口……………………………………………………………………………………………………………… 53

2 控制功能 …………………………………………………………………… 6

2.1 开关量输出 …………………………………………………………………………………………6 2.2 开关量输入 ………………………………………………………………………………………… 7 2.3 虚拟的输入与输出 …………………………………………………………………………………9 2.4 LED 的名称 …………………………………………………………………………………………9 2.5 矩阵 ……………………………………………………………………………………………… 10

能效管理平台,为企业客户节省高达30%的投资成本和运营成本。

目录

1 简介 ………………………………………………………………………… 2

1.1 本地人机界面 ……………………………………………………………………………………… 2 1.2 VAMPSET 设置和配置工具 …………………………………………………………………………4 1.3 用 VAMPSET 配置系统 ………………………………………………………………………………4

3. 3.1 远端控制过流缩放……………………………………………………………………………………………………… 24

3.4 方向过流 Iφ> (67) ……………………………………………………………………………… 24 3. 5 馈线模式电流不平衡保护 I2 /I1> (46) …………………………………………………………… 27 3.6 电动机模式电流不平衡保护 I2> (46) …………………………………………………………… 27 3.7 反相 / 不正确相序保护 I2>> (47) ………………………………………………………………… 28 3.8 堵转保护 IST> (48) ……………………………………………………………………………… 28

最新集中器使用手册

集中器使用手册集中器使用说明书一、概述 (3)二、执行标准 (3)三、系统特点 (3)四、主要技术指标 (4)4.1 基本参数 (4)4.2 硬件组成表 (5)4.3 软件构成表 (5)五、功能配置表 (6)六、工作原理 (7)6.1 工作原理简述 (7)6.2 硬件原理图 (8)6.3 软件流程图 (9)6.4现场拓扑图 (10)6.5系统架构图 (11)七、外观及端子说明 (12)7.1 安装尺寸图 (12)7.2 外观结构示意图 (13)7.3 接线图 (13)八、操作说明 (14)8.1 操作流程 (14)8.2 安装说明 (16)8.3 指示灯 (16)8.4 主站操作说明 (17)8.5 界面操作说明 (18)8.6 短信控制说明 (18)8.7 级联操作说明 (19)8.8 升级操作说明 (20)九、初始化 (21)9.1 集中器核心板程序烧写流程 (21)9.2 集中器功能测试流程 (43)9.3集中器常见故障处理 (47)十、维护 (49)十一、注意事项 (49)一、概述集中器是集抄系统中心管理设备负责主站命令的传送,抄表数据的存储,自动抄表任务的执行与事件的记录等功能。

二、执行标准《Q/GDW 374.2-2009电力用户用电信息采集系统技术规范:集中抄表终端技术规范》《Q/GDW 375.2-2009电力用户用电信息采集系统技术规范:集中器型式规范》《Q/GDW 376.1-2009电力用户用电信息采集系统技术规范:主站与采集终端通信协议》《Q/GDW 376.2-2009电力用户用电信息采集系统技术规范:集中器本地通信模块接口协议》三、系统特点◆工业级32位ARM9处理器和Linux嵌入式系统与嵌入式数据库技术。

◆同时支持无线、晓程、东软等本地模块的模块路由模式或集中器路由模式。

◆智能的集中器中继路由抄表算法(基于嵌入式数据库数据挖掘统计分析能力与速度),配主流厂家的芯片现场平均每户3到4秒的实时表码抄表速度与100%的实时抄到率。

hy57v561620接法

转SDRAM工作原理及S3C2410 SDRAM控制器4Banks x 4M x 16Bit配置方法(1)嵌入式系统2011-01-18 20:49:05 阅读7 评论0 字号:大中小订阅SDRAM的工作原理、控制时序、及相关控制器的配置方法一直是嵌入式系统学习、开发过程中的一个难点。

掌握SDRAM的知识对硬件设计、编写系统启动代码、提高系统存取效率、电源管理都有一定的意义。

本文想通过:1.SDRAM的工作原理。

2.HY57V561620 SDRAM介绍。

3.S3C2410和HY57V561620的接线方法。

4.S3C2410 SDRAM控制器的配置方法。

5.SDRAM控制时序分析这5个方面来帮助初学者了解SDRAM。

文章分为2篇,第1篇讲解前3个知识点,第2篇讲解后2个。

一、SDRAM的工作原理SDRAM之所以成为DRARM就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM最重要的操作。

那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。

这样刷新速度就是:行数量/64ms。

我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个Bank的行数。

刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为15.625μs(微秒,1/1000毫秒),8192行时就为7.8125μs。

HY57V561620为8192 refresh cycles / 64ms。

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了,这也就大大提高了存储器的访问速度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4 Banks x 4M x 16Bit Synchronous DRAMThis document is a general product description and is subject to change without notice. Hynix Semiconductor Inc. does not assume any responsibility forDESCRIPTIONThe HY57V561620C(L)T(P) Series is a 268,435,456bit CMOS Synchronous DRAM, ideally suited for the main memory applications which require large memory density and high bandwidth. HY57V561620C(L)T(P) Series is organized as 4banks of 4,194,304x16. HY57V561620C(L)T(P) Series is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.Programmable options include the length of pipeline (Read latency of 2 or 3), the number of consecutive read or write cycles initiated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipelined design is not restricted by a `2N` rule.)FEATURES•Single 3.3±0.3V power supply•All device pins are compatible with LVTTL interface •JEDEC standard 400mil 54pin TSOP-II with 0.8mm of pin pitch (Leaded Package or Lead Free Package)•All inputs and outputs referenced to positive edge of system clock•Data mask function by UDQM, LDQM •Internal four banks operation•Auto refresh and self refresh •8192 refresh cycles / 64ms•Programmable Burst Length and Burst Type - 1, 2, 4, 8 or Full page for Sequential Burst- 1, 2, 4 or 8 for Interleave Burst•Programmable CAS Latency ; 2, 3 ClocksORDERING INFORMATIONNote :1. HY57V561620CT Series : Nomal power & Leaded 54Pin TSOP II2. HY57V561620CLT Series : Low power & Leaded 54Pin TSOP II3. HY57V561620CTP Series : Nomal power & Lead Free 54Pin TSOP II4. HY57V561620CLTP Series : Low power & Lead Free 54Pin TSOP IIPart No.Clock FrequencyPower Organization Interface 400mil 54pin TSOP IIHY57V561620C(L)T(P)-6166MHz (Normal)/Low Power4Banks x 4Mbits x16LVTTL(Leaded)/Lead FreeHY57V561620C(L)T(P)-7143MHz HY57V561620C(L)T(P)-K 133MHz HY57V561620C(L)T(P)-H 133MHz HY57V561620C(L)T(P)-8125MHz HY57V561620C(L)T(P)-P 100MHz HY57V561620C(L)T(P)-S 100MHzPIN CONFIGURATIONPIN DESCRIPTIONPIN PIN NAME DESCRIPTIONCLK Clock The system clock input. All other inputs are registered to the SDRAM on the rising edge of CLKCKE Clock Enable Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or self refreshCS Chip Select Enables or disables all inputs except CLK, CKE, UDQM and LDQMBA0, BA1Bank Address Selects bank to be activated during RAS activity Selects bank to be read/written during CAS activityA0 ~ A12Address Row Address : RA0 ~ RA12, Column Address : CA0 ~ CA8 Auto-precharge flag : A10RAS, CAS, WE Row Address Strobe,Column Address Strobe,Write EnableRAS, CAS and WE define the operationRefer function truth table for detailsUDQM, LDQM Data Input/Output Mask Controls output buffers in read mode and masks input data in write mode DQ0 ~ DQ15Data Input/Output Multiplexed data input / output pinV DD/V SS Power Supply/Ground Power supply for internal circuits and input buffersV DDQ/V SSQ Data Output Power/Ground Power supply for output buffersNC No Connection No connectionFUNCTIONAL BLOCK DIAGRAM4Mbit x 4banks x 16 I/O Synchronous DRAMABSOLUTE MAXIMUM RATINGSNote : Operation at above absolute maximum rating can adversely affect device reliabilityDC OPERATING CONDITION (TA=0 to 70°C )Note :1.All voltages are referenced to V SS = 0V2.V IH (max) is acceptable 5.6V AC pulse width with ≤3ns of duration3.V IL (min) is acceptable -2.0V AC pulse width with ≤3ns of durationAC OPERATING CONDITION (TA=0 to 70°C , V DD =3.3 ± 0.3V, V SS =0V)Note :1. Output load to measure access time is equivalent to two TTL gates and one capacitor (50pF) For details, refer to AC/DC output circuitParameterSymbolRatingUnitAmbient Temperature T A 0 ~ 70°C Storage TemperatureT STG -55 ~ 125°C Voltage on Any Pin relative to V SS V IN , V OUT -1.0 ~ 4.6V Voltage on V DD relative to V SS V DD, V DDQ -1.0 ~ 4.6V Short Circuit Output Current I OS 50mA Power DissipationP D 1W Soldering Temperature ⋅ TimeT SOLDER260 ⋅ 10°C ⋅ SecParameterSymbol Min Typ.Max Unit Note Power Supply Voltage V DD , V DDQ 3.0 3.3 3.6V 1Input High Voltage V IH 2.0 3.0VDDQ + 0.3V 1,2Input Low VoltageV IL- 0.30.8V1,3ParameterSymbol Value Unit NoteAC Input High / Low Level VoltageV IH / V IL 2.4/0.4V Input Timing Measurement Reference Level Voltage Vtrip 1.4V Input Rise / Fall TimetR / tF 1ns Output Timing Measurement Reference LevelVoutref 1.4V Output Load Capacitance for Access Time MeasurementCL50pF1CAPACITANCE (TA=25°C , f=1MHz)OUTPUT LOAD CIRCUITDC CHARACTERISTICS I (TA=0 to 70°C , V DD =3.3±0.3V)Note :1.V IN = 0 to 3.6V, All other pins are not tested under V IN =0V2.D OUT is disabled, V OUT =0 to3.6VParameterPinSymbol-6/7/K/H-8/P/SUnitMinMax Min Max Input capacitanceCLKC I1 2.5 3.5 2.5 4.0pF A0 ~ A12, BA0, BA1, CKE, CS, RAS, CAS, WE, UDQM, LDQMCI 2 2.5 3.8 2.5 5.0pF Data input / output capacitanceDQ0 ~ DQ15C I/O4.06.54.06.5pFParameterSymbolMin.Max Unit Note Input Leakage Current I LI -11uA 1Output Leakage Current I LO -11uA 2Output High Voltage V OH 2.4-V I OH = -4mA Output Low VoltageV OL-0.4VI OL = +4mADC CHARACTERISTICS II (TA=0 to 70°C , V DD =3.3±0.3V, V SS =0V)Note :1.I DD1 and I DD4 depend on output loading and cycle rates. Specified values are measured with the output open2.Min. of tRRC (Refresh RAS cycle time) is shown at AC CHARACTERISTICS II3.HY57V561620CT(P)-6/7/K/H/8/P/S4.HY57V561620CLT(P)-6/7/K/H/8/P/SParameterSymbolTest ConditionSpeedUnitNote-6-7-K -H -8-P -S Operating CurrentI DD1Burst length=1, One bank active t RC ≥ t RC (min), I OL =0mA 130110110110100100100mA1Precharge Standby Current in Power Down ModeI DD2P CKE ≤ V IL (max), t CK = 15ns 2mAI DD2PSCKE ≤ V IL (max), t CK = ∞1Precharge Standby Current in Non Power Down ModeI DD2NCKE ≥ V IH (min), CS ≥ V IH (min), t CK = 15ns Input signals are changed one time during 30ns. All other pins ≥ V DD -0.2V or ≤ 0.2V 20mAI DD2NSCKE ≥ V IH (min), t CK = ∞Input signals are stable.10Active Standby Current in Power Down ModeI DD3P CKE ≤ V IL (max), t CK = 15ns 3mAI DD3PSCKE ≤ V IL (max), t CK = ∞3Active Standby Current in Non Power Down ModeI DD3NCKE ≥ V IH (min), CS ≥ V IH (min), t CK = 15ns Input signals are changed one time during 30ns. All other pins ≥ V DD -0.2V or ≤ 0.2V 30mAI DD3NSCKE ≥ V IH (min), t CK = ∞Input signals are stable.25Burst Mode Operating CurrentI DD4t CK ≥ t CK (min), I OL =0mA All banks active150130130130130110110mA 1Auto Refresh Current I DD5t RRC ≥ t RRC (min), All banks active 220220220220200200200mA 2Self Refresh CurrentI DD6CKE ≤ 0.2V3mA31.5mA4AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)Note :1.Assume tR / tF (input rise and fall time ) is 1ns2.Access times to be measured with input signals of 1v/ns edge rateParameterSymbol-6-7-K-H-8-P-SUnit NoteMinMaxMin MaxMin MaxMin MaxMin MaxMin MaxMin MaxSystem ClockCycle TimeCAS Latency = 3tCK361000710007.510007.5100081000101000101000nsCAS Latency = 2tCK27.5107.510101012ns Clock High Pulse Width tCHW 2.5- 2.5- 2.5- 2.5-3-3-3-ns 1Clock Low Pulse WidthtCLW 2.5- 2.5- 2.5- 2.5-3-3-3-ns 1Access Time From ClockCAS Latency = 3tAC3- 5.4- 5.4- 5.4- 5.4-6-6-6ns2CAS Latency = 2tAC2-6-6- 5.4-6-6-6-6ns Data-Out Hold Time tOH 2.7- 2.7- 2.7- 2.7-3-3-3-ns Data-Input Setup Time tDS 1.5- 1.5- 1.5- 1.5-2-2-2-ns 1Data-Input Hold Time tDH 0.8-0.8-0.8-0.8-1-1-1-ns 1Address Setup Time tAS 1.5- 1.5- 1.5- 1.5-2-2-2-ns 1Address Hold Time tAH 0.8-0.8-0.8-0.8-1-1-1-ns 1CKE Setup Time tCKS 1.5- 1.5- 1.5- 1.5-2-2-2-ns 1CKE Hold Time tCKH 0.8-0.8-0.8-0.8-1-1-1-ns 1Command Setup Time tCS 1.5- 1.5- 1.5- 1.5-2-2-2-ns 1Command Hold TimetCH 0.8-0.8-0.8-0.8-1-1-1-ns 1CLK to Data Output in Low-Z Time tOLZ1-1-1-1-1-1-1-ns CLK to Data Output in High-Z TimeCASLatency =3tOHZ3 2.7 5.4 2.7 5.4 2.7 5.4 2.7 5.4363636ns CAS Latency =2tOHZ22.75.42.75.42.75.436363636nsAC CHARACTERISTICS IINote :1. A new command can be given tRRC after self refresh exitParameterSymbol-6-7-K-H-8-P-SUnitNoteMinMax Min Max Min Max Min Max Min Max Min Max Min Max RAS Cycle TimeOperationtRC60-60-60-65-68-70-70-nsAuto RefreshtRRC 60-60-60-65-68-70-70-ns RAS to CAS Delay tRCD 18-18-15-20-20-20-20-ns RAS Active Time tRAS 42100K 42100K 45100K 45100K 48100K 50100K 50100K ns RAS Precharge Time tRP 18-18-15-20-20-20-20-ns RAS to RAS Bank Active Delay tRRD 12-14-15-15-16-20-20-ns CAS to CAS Delay tCCD 1-1-1-1-1-1-1-CLK Write Command to Data-In Delay tWTL 0-0-0-0-0-0-0-CLK Write Recovery TimetWR 2-2-2-2-2-2-2-CLK Data-In to ActiveCommand tDAL 5-5-5-5-5-5-5-CLK DQM to Data-Out Hi-Z tDQZ 2-2-2-2-2-2-2-CLK DQM to Data-In Mask tDQM 0-0-0-0-0-0-0-CLK MRS to NewCommandtMRD 2-2-2-2-2-2-2-CLK Precharge to Data Output Hi-ZCAS Latency = 3tPROZ33-3-3-3-3-3-3-CLK CAS Latency = 2tPROZ22-2-2-2-2-2-2-CLK Power Down Exit Time tPDE 1-1-1-1-1-1-1-CLK Self Refresh Exit Time tSRE 1-1-1-1-1-1-1-CLK 1Refresh TimetREF-64-64-64-64-64-64-64msIBIS SPECIFICATIONI OH Characteristics (Pull-up)I OL Characteristics (Pull-down)Voltage 100MHz (Min)100MHz (Max)66MHz (Min)(V)I(mA)I(mA)I(mA)3.45-2.43.3-27.33.00-74.1-0.72.6-21.1-129.2-7.52.4-34.1-153.3-13.32.0-58.7-197-27.51.8-67.3-226.2-35.51.65-73-248-41.11.5-77.9-269.7-47.91.4-80.8-284.3-52.41.0-88.6-344.5-72.50-93-502.4-93Voltage 100MHz (Min)100MHz (Max)66MHz (Min)(V)I(mA)I(mA)I(mA)00000.427.570.217.70.6541.8107.526.90.8551.6133.833.31.058.0151.237.61.470.7187.746.61.572.9194.448.01.6575.4202.549.51.877.0208.650.71.9577.6212.051.53.080.3219.654.23.4581.4222.654.9DEVICE OPERATING OPTION TABLEHY57V561620C(L)T(P)-6HY57V561620C(L)T(P)-7HY57V561620C(L)T(P)-KHY57V561620C(L)T(P)-HHY57V561620C(L)T-8HY57V561620C(L)T(P)-PHY57V561620C(L)T(P)-SCAS LatencytRCD tRAS tRC tRP tAC tOH 166MHz(6ns)3CLKs 3CLKs 7CLKs 10CLKs 3CLKs 5.4ns 2.7ns 143MHz(7ns)3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 5.4ns 2.7ns 133MHz(7.5ns)2CLKs3CLKs6CLKs9CLKs3CLKs5.4ns2.7nsCAS LatencytRCD tRAS tRC tRP tAC tOH 143MHz(7ns)3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 5.4ns 2.7ns 133MHz(7.5ns)2CLKs 3CLKs 6CLKs 9CLKs 3CLKs 5.4ns 2.7ns 125MHz(8ns)3CLKs3CLKs6CLKs9CLKs3CLKs6ns3nsCAS LatencytRCD tRAS tRC tRP tAC tOH 133MHz(7.5ns)2CLKs 2CLKs 6CLKs 8CLKs 2CLKs 5.4ns 2.7ns 125MHz(8ns)3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 6ns 3ns 100MHz(10ns)2CLKs2CLKs5CLKs7CLKs2CLKs6ns3nsCAS LatencytRCD tRAS tRC tRP tAC tOH 133MHz(7.5ns)3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 5.4ns 2.7ns 125MHz(8ns)3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 6ns 3ns 100MHz(10ns)2CLKs2CLKs5CLKs7CLKs2CLKs6ns3nsCAS LatencytRCD tRAS tRC tRP tAC tOH 125MHz(8ns)3CLKs 3CLKs 6CLKs 9CLKs 3CLKs 6ns 3ns 100MHz(10ns)2CLKs 2CLKs 5CLKs 7CLKs 2CLKs 6ns 3ns 83MHz(12ns)2CLKs2CLKs4CLKs6CLKs2CLKs6ns3nsCAS LatencytRCD tRAS tRC tRP tAC tOH 100MHz(10ns)2CLKs 2CLKs 5CLKs 7CLKs 2CLKs 6ns 3ns 83MHz(12ns)2CLKs 2CLKs 5CLKs 7CLKs 2CLKs 6ns 3ns 66MHz(15ns)2CLKs2CLKs4CLKs6CLKs2CLKs6ns3nsCAS LatencytRCD tRAS tRC tRP tAC tOH 100MHz(10ns)3CLKs 2CLKs 5CLKs 7CLKs 2CLKs 6ns 3ns 83MHz(12ns)2CLKs 2CLKs 5CLKs 7CLKs 2CLKs 6ns 3ns 66MHz(15ns)2CLKs2CLKs4CLKs6CLKs2CLKs6ns3nsCOMMAND TRUTH TABLENote :1. Exiting Self Refresh occurs by asynchronously bringing CKE from low to high2. X = Don ′t care, H = Logic High, L = Logic Low. BA =Bank Address, RA = Row Address, CA = Column Address, Opcode = Operand Code, NOP = No OperationCommandCKEn-1CKEn CS RAS CAS WE DQM ADDRA10/AP BA NoteMode Register Set H X L L L L XOP codeNo Operation H XHXXXXXLH H H Bank Active HXLLHHXRAVReadHXLHLHXCALV Read with Autoprecharge H WriteHXLHLLXCALVWrite with Autoprecharge H Precharge All BanksHXLLHLXXHXPrecharge selected Bank L VBurst Stop H XLH HLX X DQM H X V X Auto RefreshH H L L L H X XBurst-Read-Single-WRITEH X L L L H X A9 Pin High(Other Pins OP code)Self Refresh 1EntryH L L L L H XXExitLHHXXXXL H H H Precharge power downEntryHLHXXXXXL H H HExitLHHXXXXL H H H Clock SuspendEntry H LHXXXXXLVVVExitLHXXPACKAGE INFORMATION400mil 54pin Thin Small Outline Package。