NIOSII添加SRAM方法

nios ii 入门手册

一、建立quartus ii工程首先,双击quartus ii 9.1图标打开软件,界面如下图1.1所示图1.11.1新建工程(1)点击file –>New Project Wizard 出现图1.2所示的对话框。

图1.2(2)点击Next。

如图1.3所示:第一行是工程的路径,二、三行为实体名。

填好后点击Next。

图1.3(3)此处可选择加入已设计好的文件到工程,点击Next。

图1.4(4)选择设计器件如图1.5所示。

接着点击Next。

图1.5(5)接着点击Next。

无需改动,点击finish,显示如下图所示。

图1.6(6)此时,工程已经建立完成,接下来需要建立一个原理图输入文件,点击file –>New ->Block Diagram/Schematic File 后如图1.7所示。

图1.7二、构建一个nios ii 软核(1)首先点击Tools ->Sopc Builder图2.1在System Name中输入软核的名称,注意:软核的名称不能和quartus工程的实体名相同,否则编译会出现错误,接着点击ok。

图2.2图中clk_0为时钟名称,100.0为时钟值双击可修改其值。

即软核的时钟就是100MHZ。

(2)建立nios ii处理器点击Processors -> Nios ii Processor 如图2.3所示图2.3点击后,将出现下图,在下图中选择软核的类型。

这里提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。

Nios II/s占资源比,前者多一些,功能也多了,速度也忚一些Nios II/f 占资源最多,功能也最多,速度就最快,用户可根据实际的需要选择不同的类型。

此处选择Nios II/f型,速度和功能都能满足。

下方Reset Vector是复位后启动的Memory类型和偏移量。

待SDRAM设置号以后再来设置此处。

nios ii处理器功能说明

NIOS II功能模块说明(一)结合前面的NIOS II处理器架构简介,后面对各功能模块进行简要说明。

NIOS II功能模块说明(一)l 通用寄存器NIOS II架构包含32个32位通用寄存器,还包含32个32位的控制寄存器。

处理器架构能支持超级用户模式和普通用户模式,以便系统软件保护不同应用的控制寄存器。

这可以通过设置控制寄存器来实现。

NIOS II架构还能兼容未来增加的浮点寄存器。

算术逻辑单元(ALU)NIOS II的算术逻辑操作是基于通用寄存器来完成的,整个操作需要将一个或两个输入操作数进行运算,然后将计算结果输出并存储到寄存器中。

NIOS II支持的数据运算包括:1.算术运算:包括对有符号和无符号操作数进行的加、减、乘和除运算。

2.关系运算:包括对有符号和无符号操作数进行的等于、不等于、大于等于和小于运算。

EDA中国门户网站2e#t;jF"{1S3.逻辑运算:包括对逻辑操作数进行的与、或、或非和异或操作4.移位和循环移位操作:可以在单指令对操作数进行0至31位的移位和循环移位操作,并且能支持左移和右移、左循环和右循环移位。

NIOS II核并没有采用硬件来实现全部的NIOS II指令集,对没有用硬件实现的指令又称为未实现指令(Unimplemented Instructions)。

NIOS II核支持IEEE标准754‐1985规定的单精度浮点指令,这些单精度定制指令包括浮点加、减和乘运算,浮点除运算作为扩展的简单指令集有效。

这些指令均作为定制指令在NIOS II中实现,通过NIOS II Processor MegaWizard接口可以很容易的设计这些浮点指令。

需要注意的是,浮点除指令若采用硬件来实现,或占用比其他指令多的多的资源,若在设计中不使用硬件实现,则处理器会使用软件来实现浮点除运算。

另外,由于指令集仿真器不支持定制指令,若需要在指令集仿真器上运行软件,可以使用如下的#pragma描述在软件中禁止浮点定制指令,而是用软件实现浮点指令。

Nios II 快速入门

Nios II快速入门Nios II的开发涉及到多个软件工具,由于文档需要面向最广泛的开发者,在这一篇中以一般的开发流程,图文并列的方式进行探讨,假设读者已经正确安装Altera公司的Quartus II5.1或更高版本、Nios II Development Kit 5.1或更高版本的软件,对软件安装不再赘述。

1软件工具介绍Nios II的开发包括了以32位Nios II软核处理器为核心的硬件配置、硬件设计、软件仿真、软件设计、软件调试等,基本的软件工具有:1.1Quartus II,用于完成Nios II系统的综合、硬件优化、适配、编程下载和硬件测试1.2SOPC Builder是Altera Nios II嵌入式处理器开发软件包,用于实现Nios II系统的配置、生成、Nios II系统相关的软件的生成1.3ModelSim用于对SOPC Builder生成的Nios II的HDL描述进行系统功能仿真1.4Matlab/DSP Builder,生成Nios II系统硬件加速器,并为定制新指令提供支持。

1.5Nios II IDE,软件开发调试环境。

我们主要使用上述工具1、2、5,对3、4工具的开发使用可以根据大家的具体需求另行探讨。

2Nios II应用系统开发设计流程介绍II开发分硬件开发和软件开发两个流程,硬件开发过程主要由用户定制系统硬件, Nios然后由SOPC Builder等工具完成系统硬件和对应的开发软件生成;软件设计和传统方式类似,接近于unix/linux系统开发,软件开发又可以细分为HAL驱动程序开发和应用系统开发。

在以后的实践中我们会体会到Nios II的开发是一个灵活的软硬件融合的开发过程。

3Nios II系统硬件设计实例导航我们以一个简单的基于Nios II的系统开发过程来介绍Nios II系统的开发过程,该系统具有四个按钮,8个LED输出,SDRAM,FLASH硬件,实现简单的流水灯。

NIOSII SOPC实例1

一.关于SOPC1)SOPC英文全名为:System-On-a-Programmable-Chip,即可编程片上系统。

SOPC 用可编程逻辑技术把整个系统放到一块硅片上,来用于嵌入式系统研究和电子信息处理。

SOPC是一种特殊的嵌入式系统,它是片上系统(System-On-a -Chip,SOC),即由单个芯片完成整个系统的主要逻辑功能但它不是简单的SOC,它也是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC设计包括以32位NIOSII软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、软件设计以及软件调试等。

SOPC系统设计的基本软件工具有:1)QuartusII:用于完成NIOSII系统的综合、硬件优化、适配、编程下载以及硬件系统调试等;2)SOPC Builder:Altera NiosII嵌入式处理器开发软件包,用于实现NiosII 系统的配置、生成,内嵌于QuartusII软件中;3)ModelSim: 用于对SOPC生成的NiosII系统的HDL描述进行系统的功能仿真;4)NiosII IDE:用于进行软件的开发、调试,以及向目标开发板进行Flash下载;二.关于NIOSII处理器NIOSII 是一个可配置的软核处理器。

“可配置”的意思是设计者可以根据性能和成本的要求来增加或删减处理器的功能。

ALTERA公司并不销售NIOSII处理器芯片,而是销售空的FPGA,并提供NIOSII 系统相应的IP核来组成NIOSII系统,然后将这个系统下载到FPGA中实现。

1)关于AVALONAvalon总线是SOPC硬件系统的重要组成部分,Avalon总线规范是为了开发SOPC 环境下外设而设计的。

图1-1 一个SOPC的示例二. SOPC简单实例:软核控制LCD液晶字母显示器1.系统构成规划1)系统功能:在character LCD上显示”Hello LCD from NiosII!”2)本系统中需要的外围器件:(1)L CD:输出显示(2)S RAM存储器:程序运行时将其导入SRAM3)SOPC中建立系统需要添加的模块包括:(1)N ios II 32bit CPU(2)L CD display(3)外部RAM总线(4)外部RAM接口(5)J TAG UART Interface(6)定时器2.硬件系统的建立1)首先打开Quartus II 建立工程文件:将工程文件命名为hello_lcd,顶层文件与工程文件同名。

NIOS教程4---使用起SRAM

NIOS教程(4) --------使用板载的SRAM存储器在此实验中我们将建立一个NIOS工程,实验点亮LED的演示使用板载的SRAM并且烧代码烧录到板载的EPCS4存储配置芯片中运行。

1.先打开QuartusII 9.0SP2软件点击菜单栏FileÆ New Project Wizard,弹出如下对话框点击Next>按钮继续,在此步中,What is the working directory for this project? 是询问你的这个项目工程打算放在哪里?我们改为D:\ask2cb_nios\nios4 (表示整个工程建立在D盘的ask2cb_nios目录下的NIOS4目录下面)What is the name of this project? 是询问你这个工程项目名是什么?我们改为nios4(表示这是第四个nios示例工程)What is the name of the top-level design entity for this project? 是询问这个工程项目的顶层设计入门名我们改为nios4,表示顶层模块名为nios4改成如下图所示:点击Next>继续提示D盘ask2cb_nios目录下下面没有nios4这个目录,询问是否要创建它,选择是(y),让QuartusII创建这个目录。

向导开始询问是否有现成的文件需要加到当前新建的工程中?这步不用管它,点击Next>继续,在此步中,向导询问你使用的是何种器件,我们在Device family组合框中,Family下拉列表中选择CycloneII,在Available devices:下面的列表框中选择EP2C5Q208C8,这是我们ASK2CB-5开发板所使用的FPGA主芯片(EP2C5Q208C8),如果您购买的是ASK2CB-8开发板,请选择EP2C8Q208C8。

在本教程中,默认采用的是EP2C5Q208C8,如果你的开发板上的FPGA主芯片为EP2C8Q208,请修改相应的器件为EP2C8Q208C8点击Next按钮继续在此步中询问你要使用何种综合工具,仿真工作,时序分析工具,不用管它,点Next>继续,最后显示一个整个新建的Project的摘要。

NIOSII实验手册V1

NIOSII程序设计--FPGA开发板配套教程(二)广西师范大学目录第二节 SOPC概述 (1)2.1NIOSII开发流程 (1)2.2NIOSII IDE功能说明 (2)2.3软件版本与开发平台 (4)第三节 NIOSII程序设计 (5)实验一点亮LED灯 (5)实验二NIOSII系统设计 (36)实验三PIO外部中断-接键开关 (46)实验四数码管显示驱动 (56)实验五T IMER定时器 (59)实验六串口通信实验 (69)实验七LCD显示操作 (78)第二节 SOPC概述SOPC是system on a programmable chip的缩写,顾名思义就是把一个系统集成在单片可编程芯片中。

一个最小系统应该包括中央处理单元(CPU)、随机存储器(RAM)和Flash ROM(存储代码、数据等),稍微复杂点的系统至少应该包括UART、DMA、Timer、中断管理模块以及GPIO等。

早在2002年的时候,Altera公司就基于SOC的设计思想,推出了其第一款32位RISC CPU软核——Nios,那时的Nios CPU功能简单,执行效率低下且不支持在线调试,所以并未得到很大的推广。

在Nios CPU基础上,Altera公司又于2005年推出了其第二代32位RISC CPU——Nios II。

与Nios CPU相比,Nios II CPU在性能方面得到了质的提升,指令执行速度快,执行效率高,且支持JTAG在线调试。

2.1NIOSII开发流程Nios II CPU的开发流程与Nios CPU基本一致,唯一不同的就是Nios CPU的软件开发是在Nios SDK Shell下进行,而Nios II CPU则是在Nios II IDE集成环境下开发。

其基本开发流程依旧为:(1)在Quartus II中新建一个工程(硬件)。

(2)在SOPC Builder中根据自己的需要加入各种IP核。

(3)利用SOPC Builder产生Quartus II能够识别的文件。

Nios II嵌入式系统软件开发平台安装与使用说明

命名好后点击"finish",就创建好了一个虚拟硬盘了。 注解:

XuX NiosII嵌入式系统开发平台 - mercury

XuX NiosII嵌入式系统开发平台 - mercury

点击”Enter License Key …”输入获得的 License Key。

XuX NiosII嵌入式系统开发平台 - mercury

安装完成 选择”Restart Now”立刻重启;选择”Restart Later”稍后重启。

完成安装后运行 VMware Workstation 的界面。

XuX NiosII嵌入式系统开发平台 - mercury

驱: 如下图所示:

双击上图所示的图标,再从”Device status”选择” Connected”复选框,就可以讲光驱添加到虚拟机中了。

XuX NiosII嵌入式系统开发平台 - mercury

o 2. 连接

连接有两种选择:一种是将主机上的光驱连接到虚拟 机中,另外一种是选择 image 映像文件(*.iso) 2.2.5. 其他的可以保持不变。

2.2.2. 处理器的设置 如下图所示:

XuX NiosII嵌入式系统开发平台 - mercury

左侧选择”processors”。 图中右侧 2 所示的位置可以设置 你 PC 处理器参数,以达到虚拟机的最优化设置。

第12章 NIOS II常用外设使用

12.4.3 软件编程

使用Avalon总线访问SDRAM控制器就像访问一般的存储器一样, 不需要软件驱动程序,可以直接通过函数IORD和IOWR进行读写。

读函数IORD的格式为:IORD(BASE,REGNUM)。BASE是寄 存器的基地址,REGNUM是寄存器的偏移量,函数功能是从基地 址为BASE的设备中读取偏移量为REGNUM的单元里的值。 写函数IOWR的格式为:IOWR(BASE,REGNUM,DATA)。 BASE是寄存器的基地址,REGNUM是寄存器的偏移量,DATA是 要写入的数据。函数功能是向基地址为BASE的寄存器的偏移量为 REGNUM的单元里写入数值DATA。

12.5 UART的使用

UART(通用异步接收器/发送器)是一个常用的字符型外围设备。 在NiosII系统中可以集成了两种UART内核,一种是JTAG UART, 使用它可以通过JTAG通讯端口与PC机进行数据交换,一般用于程 序调试;另一种是通用的UART,它以RS—232协议的形式与外界 进行数据交换。本节介绍UART。

12.2 定时器的使用

在NiosⅡ处理器系统中含有一个内核定时器,它能够作为系统的 周期性时钟源,也可以作为一个计时器,测定事件发生的时间; 它既能对外输出周期性脉冲,也可作为一条“看门狗”以监管系 统正常运行。

12.2.1 内核定时器简介

1.状态寄存器(Status)

2.控制寄存器(Congtrol) 3.初值寄存器(Period) 4.快照寄存器(snap)

与片上逻辑 相连的 Avalon信号 Address Data IRQ Endofpacket Dataavailable Readyfordata

Endofpacket

第4讲NIOSII外围设备标准系统搭建

第4讲NIOSII外围设备标准系统搭建

4.1 并行输入/输出内核

PI O 内 核 配 置 选 项

边沿捕获寄存器 中断寄存器

Input Options 选项卡

Rising Edge:上升沿 Falling Edge:下降沿 Either Edge: 上升或下降沿

说明:当指定类型的边沿在输入端口出现时, 边沿捕获寄存器对应位置1。

件。

Nios II 系统

PIO 内核

寄存器

CPU 内核

PIO 内核

PIO 内核

PIO内核结构框图

CPU通过寄存 器控制I/O端 口行为

Pio[7] Pio[6] Pio[5] Pio[4] Pio[3] Pio[2] Pio[1] Pio[0] Pio[31] Pio[30] Pio[29]

Pio[3] Pio[2] Pio[1] Pio[0]

第4讲NIOSII外围设备标准系统搭建

4.1 并行输入/输出内核

• PIO内核简介

每个Avalon接口的PIO内核 可提供32个I/O端口且端口数可 设置,用户可以添加一个或多个

PIO内核。CPU通过I/O寄存器 控制I/O端口的行为。I/O口可 以配置为输入、输出和三态,还

可以用来检测电平事件和边沿事

添加1个按钮 在此选Input ports only。在Input Options选

项单我们配置了上升沿触发,生成中断请求 的模式

第4讲NIOSII外围设备标准系统搭建

第4讲 主要内容

• 4.1 并行输入/输出(PIO)内核 • 4.2 SDRAM控制器内核 • 4.3 ram/rom片上存储 • 4.4 EPCS控制器内核 • 4.5 定时器内核 • 4.6 UART内核 • 4.7 JTAG_UART内核 • 4.8 lcd控制器 • 4.9 System ID内核 • 4.10 课程实验

nios2+c语言编程方法Nios2系列教程

nios2+c语言编程方法Nios2系列教程最小的Nios2系统前言2003年Altera推出了第一代32位Nios系统,开创了FPGA内构建高性能单片机的先河。

随之2004年,Nios系统升级为Nios2系统,解决了软硬件开发中一些不方便的问题,软件开发环境从命令行编译转移到Eclips的IDE集成开放环境。

Nios2开发环境从1.0、1.1到 1.2逐步升级。

后来为了和QuartusII软件升级同步,从QuartusII5.0版本开始Nios2的版本号正式和QuartusII统一。

作者我亲身经历过整个Nios2发展历程,深知Nios2的不同版本发生的巨大变化。

目前网上流行的Nios2教程针对的版本相对较老,已经对初学者学习Nios2起不到指导作用,并且应广大爱好者的强烈要求,我在此使用QuartusII和Nios2的8.0版本详细叙述Nios2的开发流程。

构建一个Nios2最小系统需要什么构建一个Nios2最小系统需要具备以下资源:★Nios2软核处理器★内存★Jtag_uart调试接口1. Nios2软核处理器:这就是Nios2处理器的核心CPU,所有的外设都是和这个CPU通过Avalon总线连接到一起的。

2. 内存:编译后的程序代码需要通过下载线下载到该内存中,然后CPU的程序指针跳转到内存的首地址开始执行程序。

3. Jtag_uart调试接口:想要用单步调试等调试功能控制程序执行和查看程序变量,那么就需要这个调试接口。

开始构建一个再简单不过的Nios2工程整个步骤由2部分组成,第一部分建立Nios2硬件SOPC工程,第二部分建立Nios2软件工程。

1.建立Nios2硬件SOPC工程建立Nios2硬件SOPC工程就是设计一个软核CPU和它的外设,编译成硬件电路放到FPGA芯片里面。

这时候可以认为FPGA就是一个32位的单片机了,下面的软件开发都是针对这个单片机的。

打开QuartusII软件,新建一个工程选择EP2C8Q208C8芯片。

NIOS II 常见问题总结

NIOS II 常见问题总结1. 怎样在TCL脚本分配管脚source .tcl 有点问题:# source stratix_pin_assign.tclcouldn't read file "stratix_pin_assign.tcl": no such file or directory答:From the Tools menu select Tcl Scripts, and then from the project folder choose the setup script for your particular development board, and click Run.2.D:\TEST\nios_sst60下载时出现错误:Error: Can't configure device. Expected JTAG ID code 0x020010DD for device 1, but found JTAG ID code 0x020B40DD.答:SOPC所选器件和开发板上的不一致。

3.在NOIS II中Bulid例程hello_world都出现了错误,错误提示为:gdrive/c/altera/kits/nios2/components/altera_nios2/HAL/src/alt_busy_sleep.c:68: error: parse error before '/' token等错误全部由alt_busy_sleep.c引起,都是关于括号不匹配的问题,而alt_busy_sleep.c是IDE中的一个默认程序。

这个错误同样出现在D:\TEST\DE2Project\software\nios2 ,培训用的一个简单实验。

答:找到system.h文件,里面有个关于系统时钟频率的设置项,应该是没有赋值,你手动赋值。

1IntroductionDemo在nios2上使用sdhc(DE2-70 + NIOS2 + Quartus 9)

此錯誤代表 tri_state_bridge 沒有連上 ssram(空心代表未連接) 已連接如下

14

nios Nios

現在使用 de2-70 因此可將自定義的 sram disable

再來需將剛產生的 SOPC 加入到專案的 TOP MODULE 中,以便專案可以使用 DE2_70_SOPC DE2_70_SOPC_inst(

由於 simulation 時無法確認 de2-70 上 switch 的輸入狀況,因此 simulation 時會出 現錯誤,可給定預設的初值十六進位 0x00(只要利用 pio 作輸入都會遇到此問題)

6

nios Nios

新增 timer

新增 lcd 目前系統圖

7

nios Nios

新增 UART

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00 Pausing target processor: not responding. Resetting and trying again: FAILED Leaving target processor paused

nios Nios

Introduction

Demo 在 nios2 上使用 sdhc(DE2-70 + NIOS2 + Quartus 9) 建立完新專案後選擇 Assignments->Settings

設定 device 定 Device and Pin Options 設定 release 路徑

因此若在 de2-70 上想要使用 sw7 便需進行下列設定(use as regular i/o)

NiosII中DRAM的使用

NiosII中DRAM的使用NiosII处理器可以方便得使用DRAM,从而获得大容量的内存。

这比较起许多单片机,实在是一个非常方便的地方。

在这里,我粗略得介绍一下nios 中DRAM的使用;更加详细的帮助信息请您参考Altera公司提供的文档。

如果本文能对您有一点点帮助,我都会感到非常高兴。

我只挑要点讲一下,关于DRAM的详细使用指南,请您参考Altera提供的随机help文档。

1。

准备工作:1。

关于创建并使用NiosII系统,请参考我之前写的文章“FPGA也疯狂(五)--Step By Step 创建标准(Standard)niosII系统”。

2。

开发板上至少要有一片DRAM。

2。

使用DRAM:1)在sopc_builder中,双击MEMORY下的SDRAM Controller,可以创建SDRAM 控制器。

Data Width:数据位宽,ezNiosDK的用户请选择16 BitsChip Selects:芯片的片选信号,ezNiosDK的用户请选择1。

Banks:设定DRAM芯片的Bank数目。

ezNiosDK的用户请选择4。

Row : 设定行地址线的数量。

ezNiosDK的用户请选择12。

Column : 设定列地址线的数量。

ezNiosDK的用户请选择8。

其余的请按照上图中设置。

2)设定DRAM的时序参数CAS latency cycles:在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS潜伏期)。

由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read Latency)。

CL的单位一般为时钟周期数,具体耗时由时钟频率决定。

ezNiosDK的用户可以选择2Initialization refresh cycles:初始化过程中所需的刷新周期,ezNiosDK的用户可以选择2 Isssue one refresh command every:刷新周期。

NiosII软件调试技巧

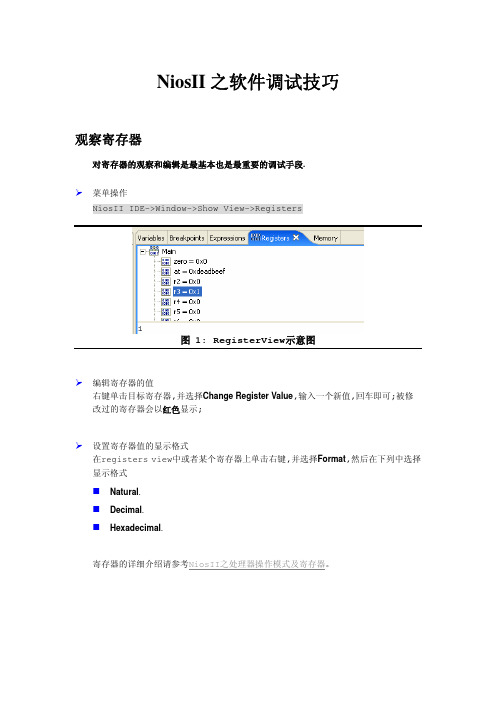

NiosII 之软件调试技巧观察寄存器对寄存器的观察和编辑是最基本也是最重要的调试手段.¾ 菜单操作NiosII IDE->Window->Show View->Registers图示意图 1: RegisterView编辑寄存器的值右键单击目标寄存器,并选择Ch ¾ ange Register Value ,输入一个新值,回车即可;被修红色显示;¾ rs view 中或者某个寄存器上单击右键,并选择Format ,然后在下列中选择显示格式 Hexadecimal .寄存器的详细介绍请参考NiosII 之处理器操作模式及寄存器改过的寄存器会以设置寄存器值的显示格式在registeNatural .Decimal .。

观察变量Variables View 默认显示当前函数中的所有局部变量,用户也可以在Variables View 中通过鼠标右键选择Add Global Variables,添加任何感兴趣的全局变量.¾ 菜单操作NiosII IDE->Window->Show View->Variables图示意图 2: VariablesView编辑变量的值¾ 右键单击目标变量,并选择Change Variable Value,输入一个新值,回车即可;被修红色显示;¾ 改过的变量会以设置变量值的显示格式在Variables View 中或者某个变量上单击右键,并选择Format,然后在下列中选择显示格式 Hexadecimal .¾ :Natural .Decimal .查看变量的类型属性在Variables View 中的某个变量上单击右键,并选择Cast to Type;观察内存¾ 菜单操作NiosII IDE->Window->Show View-> Memory图 3: MemoryView 示意图Memo ¾ ry View 支持与C 语言一样的寻址方式,用户可以在地址栏中使用下面几种表达式 0x0847d3c (&y)24*ptr¾ 图:+10编辑memory 的值在地址栏中输入感兴趣的地址, 然后在其下方的Memory View 中,鼠标左键单击(不能双击)感兴趣的地址单元(参考图 3: MemoryView 示意),然后输入新值即可;可以通过键盘的Arrow Key,来定位新的要修改的单元;对Memory 的编辑是NiosII IDE 中最不人性化的一点/观察表达式¾菜单操作NiosII IDE->Window->Show View->Expressions图 4: ExpressionView示意图¾添加Expression在Expression View中,单击鼠标右键选择Add Watch Expression,然后在弹出的对话框中输入想要观察的表达式(例如: (x-5)*3), 单击OK即可;设置断点¾ 断点的作用: 使程序运行到满足断点条件时自动停止运行;用户可以直接在源程序的代码上添加断点,取消断点或者暂时禁止断点;¾ 设置断点: 双击代码左侧边缘处即可设置断点,如下图所示;图断点设置示意图 5:¾ 编辑断点菜单操作NiosII IDE->Window->Show View->Breakpoints所有的断点都会在Breakpoint View 中显示,并可以使能/禁止/删除断点;图 6: BreakpointView 示意图NiosII IDE 的支持断点的动态设置,用户可以在程序运行时在源码中动态设置 断点.WatchpointWatchpoint是一种特殊的断点,一般的断点是当程序执行到源代码的某个位置时强制程序停下来; Watchpoint则可以根据给定条件控制程序.NiosII IDE对Watchpoint的支持还存在很大缺陷,这里只作简单介绍.¾在全局变量上设置watchpoint在源文件中双击选中一个全局变量(目前只支持32位的变量,例如int);选择菜单 Run > Toggle Watchpoint;在Add Watchpoint 的对话框中选择z如果要让程序在读该全局变量的时候停止的话,就在Read选项上打勾;z如果要让程序在写该全局变量的时候停止的话,就在Write选项上打勾;单击OK.可以在Breakpoints view(见P5)中观察和控制所有的断点,包括Watchpoint;注:重复1-2步可以取消Watchpoint;¾在表达式上设置watchpoint打开Breakpoints view(见P5);右键单击窗口内任何位置,然后选择Add Watchpoint;在Add Watchpoint (C/C++) 对话框的Expression to watch 域输入目标表达式(目标表达式通常用来表示某个地址);在Add Watchpoint 的对话框中选择z如果要让程序在读表达式所指向的地址时停止的话,就在Read选项上打勾.z如果要让程序在写表达式所指向的地址时停止的话,就在Write选项上打勾.单击OK.图 7: Watchpoint示意图在HAL源文件中设置断点NiosII IDE 6.0支持Linked Folder这样的特性,在每个系统库项目中你都可以看到两个Linked Folder,如下图所示:图 8: LinkerFolder示意图借由这两个linked folder,用户可以找到HAL的所有源文件,并直接在源文件上设置断点.用户在调试程序时,通常IDE会自动在应用程序的main函数入口处设置一个断点,使得程序看起来好像都是从main开始执行的.实际上程序的真正入口是复位子程序,读者可以思考下面两个问题:¾如何让程序从复位地址开始调试?¾如何在中断入口设置断点?指令单步调试模式在NiosII IDE的Debug Perspective界面工具栏中, 用户可以看见一个Instruction Stepping Mode按钮(如下图所示), 只要单击该按钮, 就可以进入单个指令的调试模式;图 9: 指令单步调试工具示意图指令单步调试在Disassembly窗口中进行,如下图所示;图 10: Disassembly窗口示意图用户无法在汇编源文件*.S中直接进行单步调试,此时就需要借助指令单步调试模式在Disassembly窗口中调试汇编程序.观察复杂的结构变量很多时候,特别是用C++进行软件开发的时候,用户可能需要观察一些比较复杂的变量,比如类,结构体,联合体以及多维数组等;NiosII IDE默认的调试级别并不支持复杂变量的观察和编辑.用户可以通过修改调试器的调试等级来实现复杂变量的观察和编辑,右键单击目标项目并进行下面的菜单操作:->Properties->C/C++Build->ToolSettings->NiosIICompiler->General->DebugLevel选择最高调试级别: Maximum(-g3), 就可以观察很多高级变量了;图 11: 调试级别设置示意图观察.objdump文件*.objdump有点象快速查看之流的工具,就是以一种可阅读的格式让你更多地了解二进制文件可能带有的附加信息。

一、基于FPGA内部RAM的简单Nios II系统

第1章SOPC硬件系统基础实验本章的目的是让读者熟悉SOPC硬件系统的构建流程及SOPC Builder和Nios II IDE的基本操作。

这是SOPC系统开发的基础,读者务必熟练掌握。

图1.1 一般核心板构造图1.1展示的是一般核心板的组成。

JTAG口用于配置和调试用,EPCS口用于AS配置模式。

EPCS是一种串行配置芯片,实际上是一种串行Flash,存储完配置文件后的剩余空间可用于存储程序。

目前市面上的很多核心都只配一个容量稍为大一些的EPCS而不使用并行Flash,这样可以节省大约40个I/O口。

图中的FLASH和SDRAM并不是核心本身所必需的,只是为了方便开发Nios II系统而增加的,因为FPGA内部的RAM比较小,不适合开发大的程序。

1.1 基于FPGA内部RAM的简单Nios II系统1.实验目的(1)熟悉Nios II系统的构成及开发流程;(2)熟悉SOPC Builder和Nios II IDE的使用;(3)本节内容是后面内容的基础,在后面的实验里对本节的一些基本操作将不再详细阐述,读者若有疑问可返回本节查阅。

2.实验现象两个LED灯交替闪烁。

3.实验原理控制两个LED灯交替闪烁的程序代码比较小,因此可以将其固化在内部ROM内,系统复位时把其读入内部RAM运行。

说到这,读者是否有似曾相识的感觉呢?其实我们天天用的计算机也是这么操作的。

ROM相当于硬盘,RAM相当于内存,之后的实验将用到的FLASH和SDRAM 也一样,FLASH相当于硬盘,SDRAM相当于内存。

各自的作用大家也应该很熟悉了吧,FLASH 属于非易失性的存储器,可以存储程序及其他一些数据文件等,但访问比较慢;SDRAM属于易失性存储器,但访问的速度比较快,系统复位时会把程序复制到SDRAM可以提高程序的运行速度(需要说明一点,系统复位时从哪复制程序取决于在定制Nios II处理器时复位地址设置为在哪,复制到哪取决于把程序代码空间设置为在哪,在后面的实验将详细说明)。

nios2系统添加外部接口读写总线实例

NIOS ii系统添加外部接口读写总线实例软件环境:quartus ii 11.0本实例使用quartus ii 的Qsys工具建立NIOS ii系统。

Qsys工具只提供部分标准外部存储器件的读写控制模块,如下图示:对于一般外部地址空间的访问,需要用户自定义接口控制模块,然后挂接在NIOS ii Avalon总线上,实现外部空间的读写功能。

下面通过实例演示总线的添加及使用过程。

首先建立所需的外部接口总线控制模块(verilog module),本例建立ADV212_interface模块,对应的文件名称为ADV212_interface.v,端口描述如下:定义avalon 总线和外设的互联关系,需要关注外设的总线宽度和地址空间大小,如下图:下面生成外设控制模块,首先打开component Editor窗口,如下图:弹出对话框如下,点击Add添加ADV212_interface.v,点击NextSignals选项卡定义信号接口关系。

首次定义avalon总线Interface 选择new Avalon Memory Mapped Slave…,生成avalon-slave接口,此处为s0,如下图:首次定义外部接口信号Interface选择new Conduit将产生conduit_end,然后依次选择,Signal Type选择export依次选择其他选项,最终结果如下,点击Next进入Interface选项。

如果Remove Interfaces With No Signals有效(见下图红色方框内),点击一下。

设置其他选项,关注红色区域,如下图:下拉右侧滚动条,设置总线Timing 参数:下拉右侧滚动条,设置clock,reset:下拉右侧滚动条,设置conduit_end,点击Next进入HDL Parameters选项卡,点击Next进入Library Info选项卡,设置模块名称,点击Finish此时,在左侧component library窗口将出现刚生成的user_bus1模块,将其添加进右侧System contents窗口,然后重新分配地址和中断向量,最后在点击generation,生成NIOS ii。