9N90中文资料

FQA9N90C中文资料

BVDSS ∆BVDSS / ∆TJ

Drain-Source Breakdown Voltage

Breakdown Voltage Temperature Coefficient

VGS = 0 V, ID = 250 µA

900 --

ID = 250 µA, Referenced to 25°C -- 0.99

-55 to +150

300

Typ

Max

--

0.45

0.24

--

--

40

©2003 Fairchild Semiconductor Corporation

Units V A A A V mJ A mJ

V/ns W

W/°C °C °C

Units °C/W °C/W °C/W

Rev. A, March 2003

Output Capacitance

Crss

Reverse Transfer Capacitance

VDS = 25 V, VGS = 0 V, f = 1.0 MHz

-- 2100 2730 pF

-- 175 230

pF

-- 14

18

pF

Switching Characteristics

td(on)

FQA9N90C

元器件交易网

Electrical Characteristics

Symbol

Parameter

TC = 25°C unless otherwise noted

Test Conditions

Min Typ Max Units

Off Characteristics

--

fqpf9n90场效应管参数

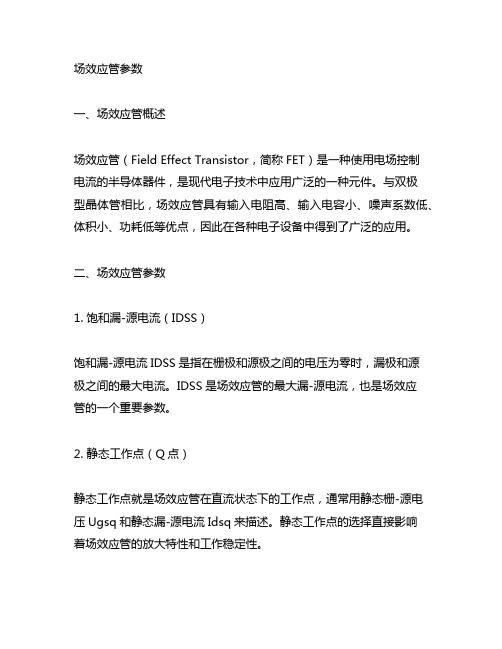

场效应管参数一、场效应管概述场效应管(Field Effect Transistor,简称FET)是一种使用电场控制电流的半导体器件,是现代电子技术中应用广泛的一种元件。

与双极型晶体管相比,场效应管具有输入电阻高、输入电容小、噪声系数低、体积小、功耗低等优点,因此在各种电子设备中得到了广泛的应用。

二、场效应管参数1. 饱和漏-源电流(IDSS)饱和漏-源电流IDSS是指在栅极和源极之间的电压为零时,漏极和源极之间的最大电流。

IDSS是场效应管的最大漏-源电流,也是场效应管的一个重要参数。

2. 静态工作点(Q点)静态工作点就是场效应管在直流状态下的工作点,通常用静态栅-源电压Ugsq和静态漏-源电流Idsq来描述。

静态工作点的选择直接影响着场效应管的放大特性和工作稳定性。

3. 灵敏度场效应管的灵敏度是指当栅-源电压变化时,漏-源电流的变化量与栅-源电压的变化量之比。

灵敏度越大,表示场效应管对栅-源电压的变化更为敏感。

4. 饱和电流饱和电流是指当场效应管的栅-源电压足够大时,漏-源电流达到最大值。

饱和电流的大小决定了场效应管的输出功率。

5. 输入电容(Ciss)输入电容是指场效应管的栅-源电容和栅-漏电容之和。

输入电容的大小直接影响了场效应管的输入电阻。

6. 输、输出电阻输、输出电阻分别是指场效应管的输入电阻和输出电阻。

输、输出电阻的大小直接影响了场效应管的放大特性和匹配特性。

7. 开启电压(VGS(th))开启电压是指当场效应管的栅-源电压大于一定值时,场效应管开始导通。

开启电压的大小直接影响了场效应管的饱和电流和输出功率。

8. 最大耗散功率(Pd)最大耗散功率是指场效应管在允许工作条件下所能承受的最大功率。

超过最大耗散功率会导致场效应管损坏。

三、场效应管参数的选取原则1. 静态工作点的选择原则静态工作点的选择应根据具体应用来确定,一般应使得静态漏-源电流较大,但不能太大。

2. 灵敏度的选择原则灵敏度的大小直接影响了场效应管在信号放大时的放大倍数,应根据具体应用需求来确定。

39100-0903中文资料

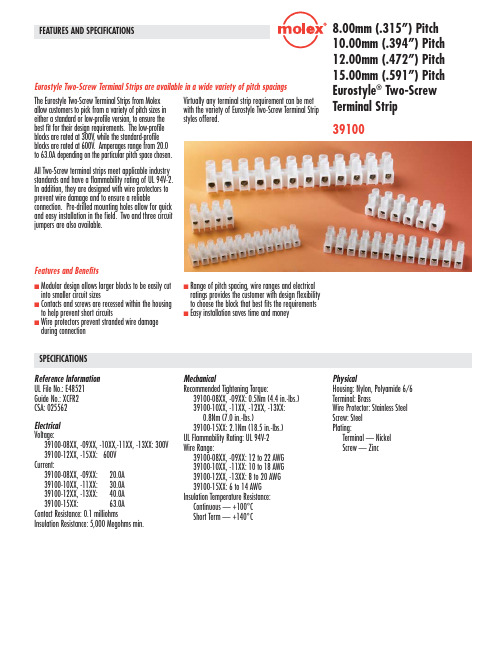

FEATURES AND SPECIFICATIONSSPECIFICATIONS8.00mm (.315”) Pitch 10.00mm (.394”) Pitch 12.00mm (.472”) Pitch 15.00mm (.591”) Pitch Eurostyle ®Two-Screw Terminal Strip 39100The Eurostyle Two-Screw Terminal Strips from Molex allow customers to pick from a variety of pitch sizes in either a standard or low-profile version, to ensure the best fit for their design requirements. The low-profile blocks are rated at 300V, while the standard-profile blocks are rated at 600V. Amperages range from 20.0to 63.0A depending on the particular pitch space chosen.All Two-Screw terminal strips meet applicable industry standards and have a flammability rating of UL 94V-2.In addition, they are designed with wire protectors to prevent wire damage and to ensure a reliableconnection. Pre-drilled mounting holes allow for quick and easy installation in the field.Two and three circuit jumpers are also available.Virtually any terminal strip requirement can be met with the variety of Eurostyle Two-Screw Terminal Strip styles offered.Reference Information UL File No.: E48521Guide No.: XCFR2CSA: 025562Electrical Voltage:39100-08XX, -09XX, -10XX,-11XX, -13XX: 300V 39100-12XX, -15XX: 600V Current:39100-08XX, -09XX:20.0A 39100-10XX, -11XX:30.0A 39100-12XX, -13XX:40.0A 39100-15XX: 63.0A Contact Resistance: 0.1 milliohmsInsulation Resistance: 5,000 Megohms min.MechanicalRecommended Tightening Torque:39100-08XX, -09XX: 0.5Nm (4.4 in.-lbs.)39100-10XX, -11XX, -12XX, -13XX: 0.8Nm (7.0 in.-lbs.)39100-15XX: 2.1Nm (18.5 in.-lbs.)UL Flammability Rating: UL 94V-2Wire Range:39100-08XX, -09XX: 12 to 22 AWG 39100-10XX, -11XX: 10 to 18 AWG 39100-12XX, -13XX: 8 to 20 AWG 39100-15XX: 6 to 14 AWG Insulation Temperature Resistance: Continuous — +100°C Short Term — +140°CPhysicalHousing: Nylon, Polyamide 6/6Terminal: BrassWire Protector: Stainless Steel Screw: Steel Plating:Terminal — Nickel Screw — ZincFeatures and BenefitsI Modular design allows larger blocks to be easily cutinto smaller circuit sizesI Contacts and screws are recessed within the housing to help prevent short circuitsI Wire protectors prevent stranded wire damage during connection I Range of pitch spacing, wire ranges and electricalratings provides the customer with design flexibility to choose the block that best fits the requirements I Easy installation saves time and moneyEurostyle Two-Screw Terminal Strips are available in a wide variety of pitch spacingsAPPLICATIONS8.00mm (.315”) Pitch10.00mm (.394”) Pitch12.00mm (.472”) Pitch15.00mm (.591”) PitchEurostyle®Two-ScrewTerminal Strip39100I Power suppliesI Spa controllersI HVAC equipmentI Motor controlsI Lighting controlsAmericas HeadquartersLisle, Illinois 60532 U.S.A.1-800-78MOLEXamerinfo@Far East North HeadquartersYamato, Kanagawa, Japan81-462-65-2324feninfo@Far East South HeadquartersJurong, Singapore65-6-268-6868fesinfo@European HeadquartersMunich, Germany49-89-413092-0eurinfo@Corporate Headquarters2222 Wellington Ct.Lisle, IL 60532 U.S.A.630-969-4550Fax:630-969-1352Visit our Web site at /product/tblocks.htmlOrder No. USA-303 Rev. 2Printed in USA/JI/2005.11©2005 Molex ORDERING INFORMATIONLow-Profile Terminal Strip Standard-Profile Terminal StripJunction BoxCircuitsOrder No.8.00mm (.315") Pitch10.00mm (.394") Pitch12.00mm (.472") Pitch15.00mm (.591") PitchLow-Profile withoutStandoffsStandard-Profilewith StandoffsLow-Profile withoutStandoffsStandard-Profilewith StandoffsLow-Profile withoutStandoffsStandard-Profilewith StandoffsStandard-Profile withStandoffs 239100-090239100-080239100-110239100-100239100-130239100-120239100-1502339100-090339100-080339100-110339100-100339100-130339100-120339100-1503439100-090439100-080439100-110439100-100439100-130439100-120439100-1504539100-090539100-080539100-110539100-100539100-130539100-120539100-1505639100-090639100-080639100-110639100-100639100-130639100-120639100-1506739100-090739100-080739100-110739100-100739100-130739100-120739100-1507839100-090839100-080839100-110839100-100839100-130839100-120839100-1508939100-090939100-080939100-110939100-100939100-130939100-120939100-15091039100-091039100-081039100-111039100-101039100-131039100-121039100-15101139100-091139100-081139100-111139100-101139100-131139100-121139100-15111239100-091239100-081239100-111239100-101239100-131239100-121239100-1512 Jumper CircuitsCircuits8.00mm (.315") Pitch10.00mm (.394") Pitch12.00mm (.472") Pitch15.00mm (.591") Pitch 238002-173038002-173238002-173438002-1736338002-173138002-173338002-1735N/A。

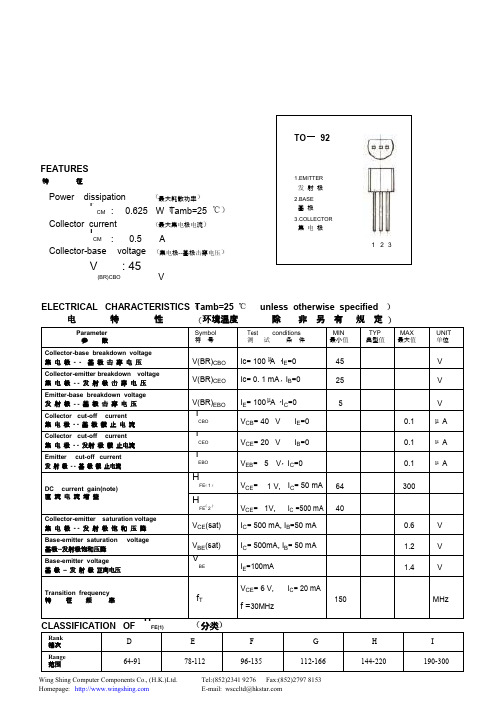

9013中文资料

Tel:(852)2341 9276 Fax:(852)2797 8153 E-mail: wsccltd@

V(BR)CBO V(BR)CEO V(BR)EBO

Ic= 100 A IE=0 Ic= 0. 1 mA IB=0 IE= 100 A IC=0 VCB= 40 V VCE= 20 V IE=0 IB=0

45 25 5 0.1 0.1 0.1 64 40 0.6 1.2 1.4 300

V V V A A A

A

集电极--基极击穿电压

V

(BR)CBO

: 45

V unless otherwise specified 除 非 另 有 规 定

Test conditions 测 试 条 件 MIN 最小值 TYP 典型值 MAX 最大值 UNIT 单位

ELECTRICAL CHARACTERISTICS Tamb=25 电 特 性 环境温度

TO

92

FEATURES

特 征

1.EMITTER

发 射 极

Power

dissipation

P

最大耗散功率

2.BASE

: 0.625 W Tamb=25 Collector current 最大集电极电流

CM

基 极

3.COLLECTOR

I

集 电 极 1 2 3

CM

:

Collector-base

0.5 voltage

Parameter 参 数 Collector-base breakdown voltage 集 电 极 - - 基 极 击 穿 电 压 Collector-emitter breakdown voltage 集 电 极 -- 发 射 极 击 穿 电 压 Emitter-base breakdown voltage 发 射 极 -- 基 极 击 穿 电 压 Collector cut-off current 集 电 极 -- 基 极 截 止 电 流 Collector cut-off current 集 电 极 - - 发射 极 截 止电流 Emitter cut-off current 发 射 极 - - 基 极 截 止电流 Symbol 符 号

Z0109NN0,135;中文规格书,Datasheet资料

1.Product profile1.1General descriptionPlanar passivated sensitive gate four quadrant triac in a SOT223 (SC-73)surface-mountable plastic package intended for applications requiring enhanced immunity to noise and direct interfacing to logic level ICs and low power gate drivers.1.2Features and benefitsDirect interfacing to logic level ICs Enhanced current surge capability Enhanced noise immunity High blocking voltage capabilityPlanar passivated for voltage ruggedness and reliability Sensitive gate in four quadrants Surface-mountable package Triggering in all four quadrants1.3ApplicationsGeneral purpose low power motor control Home appliancesIndustrial process control Low power AC Fan controllers1.4Quick reference dataZ0109NN04Q TriacRev. 3 — 10 May 2011Product data sheetTable 1.Quick reference data Symbol ParameterConditionsMin Typ Max Unit V DRM repetitive peak off-state voltage--800VI TSMnon-repetitive peak on-state current full sine wave; T j(init)=25°C; t p =20ms; see Figure 4; see Figure 5--12.5AI T(RMS)RMS on-state currentfull sine wave; T sp ≤105°C; see Figure 3; see Figure 1; see Figure 2--1A2.Pinning information3.Ordering information4.Marking[1]% = placeholder for manufacturing site codeStatic characteristicsI GTgate trigger currentV D =12V; I T =0.1A; T2+ G+; T j =25°C; see Figure 90.4-10mA V D =12V;I T =0.1A; T2+ G-; T j =25°C; see Figure 90.4-10mA V D =12V; I T =0.1A; T2- G-; T j =25°C; see Figure 90.4-10mA V D =12V;I T =0.1A; T2- G+; T j =25°C; see Figure 90.4-10mATable 1.Quick reference data …continued Symbol Parameter ConditionsMin Typ Max Unit Table 2.Pinning information Pin Symbol Description Simplified outline Graphic symbol1T1main terminal 1SOT223 (SOT223)2T2main terminal 23G gate4T2main terminal 21324sym051T1GT2Table 3.Ordering informationType numberPackage NameDescriptionVersion Z0109NN0SOT223plastic surface-mounted package with increased heatsink; 4 leadsSOT223Table 4.Marking codesType numberMarking code [1]Z0109NN0109NN05.Limiting valuesTable 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditionsMin Max Unit V DRM repetitive peak off-state voltage -800V I T(RMS)RMS on-state current full sine wave; T sp ≤105°C; see Figure 3; see Figure 1; see Figure 2-1A I TSMnon-repetitive peak on-state currentfull sine wave; T j(init)=25°C; t p =20ms; see Figure 4; see Figure 5-12.5A full sine wave; T j(init)=25°C; t p =16.7ms-13.8A I 2t I 2t for fusing t p =10ms; sine-wave pulse-0.78A 2s dI T /dtrate of rise of on-state currentI T =1A;I G =20mA;dI G /dt =100mA/µs; T2+ G+-50A/µs I T =1A;I G =20mA;dI G /dt =100mA/µs; T2+ G--50A/µs I T =1A;I G =20mA;dI G /dt =100mA/µs; T2- G--50A/µs I T =1A;I G =20mA;dI G /dt =100mA/µs; T2- G+-20A/µs I GM peak gate current -1A P GM peak gate power -2W P G(AV)average gate power over any 20 ms period-0.1W T stg storage temperature -40150°C T jjunction temperature-125°CNon-repetitive peak on-state current as a function of pulse width; maximum values6.Thermal characteristicsTable 6.Thermal characteristics Symbol ParameterConditionsMin Typ Max Unit R th(j-sp)thermal resistance from junction to solder point full cycle; see Figure 8--15K/W R th(j-a)thermal resistance from junction to ambientin free air; printed-circuit board mounted: minimum footprint; full cycle; see Figure 6-156-K/W in free air; printed-circuit board mounted: pad area; full cycle; see Figure 7-70-K/W7.CharacteristicsTable 7.CharacteristicsSymbol Parameter Conditions Min Typ Max Unit Static characteristicsI GT gate trigger current V D=12V; I T=0.1A; T2+ G+;T j=25°C; see Figure 90.4-10mAV D=12V; I T=0.1A; T2+ G-;T j=25°C; see Figure 90.4-10mAV D=12V; I T=0.1A; T2- G-;T j=25°C; see Figure 90.4-10mAV D=12V; I T=0.1A; T2- G+;T j=25°C; see Figure 90.4-10mAI L latching current V D=12V; I G=0.1A; T2+ G+;T j=25°C; see Figure 10--15mAV D=12V; I G=0.1A; T2+ G-;T j=25°C; see Figure 10--30mAV D=12V; I G=0.1A; T2- G-;T j=25°C; see Figure 10--15mAV D=12V; I G=0.1A; T2- G+;T j=25°C; see Figure 10--15mA I H holding current V D=12V; T j=25°C; see Figure 11--10mA V T on-state voltage I T=1.4A; T j=25°C;see Figure 12- 1.3 1.6VV GT gate trigger voltage V D=12V; I T=0.1A; T j=25°C;see Figure 13-- 1.3VV D=800V;I T=0.1A; T j=125°C;see Figure 130.2--VI D off-state current V D=800V;T j=125°C--0.5mA Dynamic characteristicsdV D/dt rate of rise of off-state voltage V DM=536V; T j=110°C; gate opencircuit; exponential waveform;see Figure 14120--V/µsdV com/dt rate of change of commutatingvoltage V D=400V;T j=110°C;dI com/dt=0.44A/ms; gate open circuit2--V/µs分销商库存信息: NXPZ0109NN0,135。

SVF9N90F(PN)说明书_1.0-L

漏源击穿电压(标准化)– BVDSS(V)

1.1 1.0

0.9

0.8 -100 -50

注:

1. VGS=0V 2. ID=250µA

0

50 100 150 200

结温 – TJ(°C)

漏极电流 - ID(A)

图9-1. 最大安全工作区域(SVF9N90F) 102

100µs 101

1ms

10ms

单位: mm

3.30±0.25

15.75±0.50 6.70±0.30

15.80±0.50

TO-3PN

9.80±0.50

1.47MAX 0.80±0.15 2.54 TYPE

2.80±0.30

0.50±0.15

单位:mm

杭州士兰微电子股份有限公司

版本号:1.0

该产品可广泛应用于 AC-DC 开关电源,DC-DC 电源转换 器,高压 H 桥 PWM 马达驱动。

1. 栅极

2. 漏极 3. 源极

特点

∗ 9A,900V,RDS(on)(典型值)=1.10Ω@VGS=10V ∗ 低栅极电荷量 ∗ 低反向传输电容 ∗ 开关速度快 ∗ 提升了 dv/dt 能力

1 23 TO-3PN

VGS=10V

VGS=20V

1.4

1.3

1.2

1.1

注:TJ=25°C

1.0

0

2

4

6

8

10

漏极电流 – ID(A)

漏源导通电阻 – RDS(ON)(Ω)

电容(pF)

3500 3000 2500 2000 1500 1000

500 0 0.1

图5. 电容特性

Ciss=Cgs+Cgd(Cds=shorted) Coss=Cds+Cgd Crss=Cgd

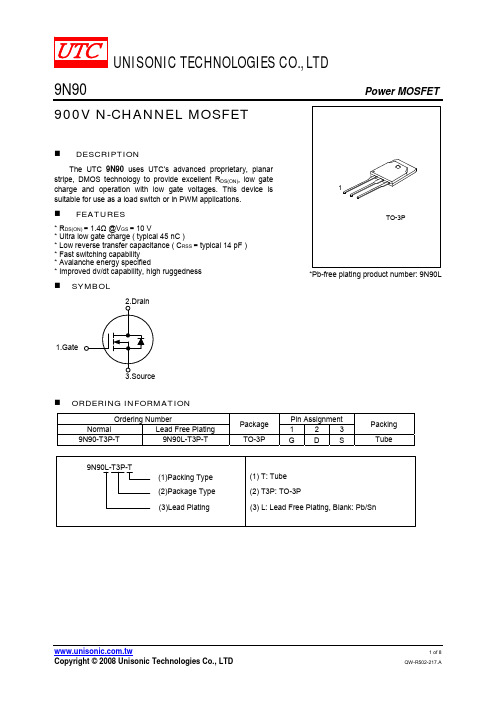

9N90L-T3P-T中文资料

UNISONIC TECHNOLOGIES CO., LTD9N90 Power MOSFET900V N-CHANNEL MOSFETDESCRIPTIONThe UTC 9N90 uses UTC’s advanced proprietary, planar stripe, DMOS technology to provide excellent R DS(ON), low gate charge and operation with low gate voltages. This device is suitable for use as a load switch or in PWM applications.FEATURES* R DS(ON) = 1.4Ω @V GS = 10 V* Ultra low gate charge ( typical 45 nC )* Low reverse transfer capacitance ( C RSS = typical 14 pF ) * Fast switching capability * Avalanche energy specified* Improved dv/dt capability, high ruggednessSYMBOL1.Gate*Pb-free plating product number: 9N90LORDERING INFORMATIONOrdering Number Pin AssignmentNormal Lead Free Plating Package 1 2 3Packing9N90-T3P-T 9N90L-T3P-T TO-3P G D STubeABSOLUTE MAXIMUM RATING (T C =25℃, unless otherwise specified)PARAMETER SYMBOL RATINGS UNITDrain-Source Voltage V DSS 900 V Gate-Source Voltage V GSS ±30 VContinuous Drain Current(T C = 25℃) I D 9.0 A Pulsed Drain Current (Note 1) I DM 36 A Avalanche Current (Note 1) I AR 9.0 ASingle Pulsed(Note 2)E AS 900Avalanche Energy Repetitive(Note 1) E AR 28mJPeak Diode Recovery dv/dt (Note 3) dv/dt 4.0 V/ns 280 WPower Dissipation Derate above 25℃ P D2.22 W/℃ Junction Temperature T J 125 ℃ Operating Temperature T OPR -20 ~ +85 ℃ Storage Temperature T STG -40 ~ +150 ℃ Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.THERMAL CHARACTERISTICSPARAMETER SYMBOL MIN TYP MAX UNITJunction-to- Ambient θJA 40 ℃/W Junction-to-Case θJC 0.45 ℃/WELECTRICAL CHARACTERISTICS (T J =25℃, unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT OFF CHARACTERISTICSDrain-Source Breakdown Voltage BV DSS V GS = 0 V, I D = 250 μA 900 V Drain-Source Leakage Current I DSS V DS = 900 V, V GS = 0 V 10 μAForward I GSSF V GS = 30 V, V DS = 0 V 100Gate-Body Leakage CurrentReverse I GSSRV GS = -30 V, V DS = 0 V -100nA Breakdown Voltage TemperatureCoefficientBV △DSS /△T J I D = 250 μA, Referenced to 25℃ 0.99 V/℃ON CHARACTERISTICS Gate Threshold Voltage V GS(TH) V DS = V GS , I D = 250 μA 3.0 5.0V Static Drain-Source On-Resistance R DS(ON) V GS = 10 V, I D = 4.5 A 1.12 1.4Ω DYNAMIC PARAMETERS Input Capacitance C ISS 2100 2730pFOutput Capacitance C OSS 175 230pFReverse Transfer Capacitance C RSSV DS = 25 V, V GS = 0 V,f = 1.0 MHz14 18 pF SWITCHING CHARACTERISTICS Turn-On Delay Time t D(ON) 50 110nsTurn-On Rise Time t R 120 250ns Turn-Off Delay Time t D(OFF) 100 210nsTurn-Off Fall Time t F V DD = 4500V, I D =11.0 A, R G = 25Ω (Note 4, 5) 75 160ns Total Gate Charge Q G 45 58 nCGate-Source Charge Q GS 13 nCGate-Drain Charge Q GDV DS = 720V, I D = 11.0A,V GS = 10 V (Note 4, 5)18 nCELECTRICAL CHARACTERISTICS(Cont.)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITDRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS Drain-Source Diode Forward Voltage V SD V GS = 0 V, I S = 9.0 A 1.4VMaximum Continuous Drain-SourceDiode Forward CurrentI S 9.0 AMaximum Pulsed Drain-Source DiodeForward CurrentI SM 36 AReverse Recovery Time t RR 550 ns Reverse Recovery Charge Q RR V GS = 0 V, I S = 9.0 A,d IF / dt = 100 A/μs (Note 4) 6.5 μCNote 1. Repetitive Rating : Pulse width limited by maximum junction temperature2. L = 21mH, I AS = 9.0A, V DD = 50V, R G = 25 Ω, Starting T J = 25℃3. I SD ≤ 9.0A, di/dt ≤ 200A/μs, V DD ≤ BV DSS , Starting T J = 25℃4. Pulse Test : Pulse width ≤ 300μs, Duty cycle ≤ 2%5. Essentially independent of operating temperatureTEST CIRCUITFig. 2A Switching Test Circuit Fig. 2B Switching WaveformsFig. 3A Gate Charge Test Circuit Fig. 3B Gate Charge WaveformFig. 4A Unclamped Inductive Switching Test Circuit Fig. 4B Unclamped Inductive Switching WaveformsTEST CIRCUIT(Cont.)TYPICAL CHARACTERISTICSTYPICAL CHARACTERISTICS(Cont.)D r a i n -S o u r c e B r e a k d o w n V o l t a g e , B V D S S (N o r m a l i z e d )D r a i n -S o u r c e O n -R e s i s t a n c e , R D S (O N ) (N o r m a l i z e d )D r a i n C u r r e n t , I D (A )D r a i n C u r r e n t , I D (A )。

NT90TNLASDC110VC中文资料

27.6max. 1.087max.

0.882

0.787

Open type

0.724 1.279max.

Dimensions

0.150 0.150 0.606 0.303 0.303 0.551 0.350 0.606 0.303 0.303

0.551

0.701

0.043

0.043

0.1

0.606

0.1

Wiring diagram(Bottom view) NOTES 1).Dimensions are in millimeters. 2).Inch equivalents are given for general information only.

Mounting (Bottom view)

Reference Data

2.Pickup and release voltage are for test purposes only and are not to be used as design criteria.

Operation condition

Insulation Resistance Dielectric Strength Between contacts Between contact and coil Shock resistance Vibration resistance Terminals strength Solderability Ambient Temperature Relative Humidity Mass 1000M min (at 500VDC) Item 7 of IEC255-5 Item 6 of IEC255-5 Item 6 of IEC255-5 IEC68-2-27 T Ea est IEC68-2-6 Test Fc IEC68-2-21 Test Ua1&Ua2 IEC68-2-20 Test Ta method 1 IEC68-2-3 Test Ca 50Hz 1500V 50Hz 2500V 200m/s2 11ms 10~55Hz double amplitude 1.5mm 10N 235 2 3 0.5s -55~100 -55~125 85% (at 40 ) 31g Low profile type 35g

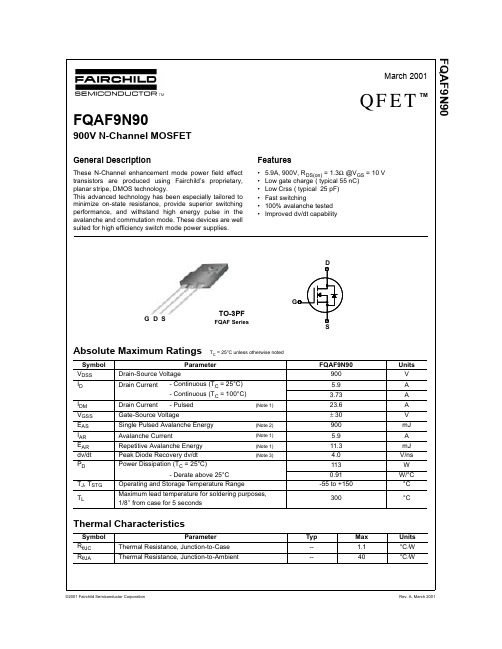

FQAF9N90中文资料

V

V/°C

µA µA nA nA

On Characteristics

VGS(th) RDS(on)

Gate Threshold Voltage

Static Drain-Source On-Resistance

gFS

Forward Transconductance

VDS = VGS, ID = 250 µA

IS

Maximum Continuous Drain-Source Diode Forward Current

--

--

5.9

A

ISM

Maximum Pulsed Drain-Source Diode Forward Current

--

-- 23.6

A

VSD

Drain-Source Diode Forward Voltage VGS = 0 V, IS = 5.9 A

Parameter Thermal Resistance, Junction-to-Case Thermal Resistance, Junction-to-Ambient

FQAF9N90 900 5.9 3.73 23.6 ± 30 900 5.9 11.3 4.0 113 0.91

-55 to +150

--

45 100

ns

-- 100 210

ns

-- 135 280

ns

(Note 4, 5)

--

80 170

ns

VDS = 720 V, ID = 8.6 A,

-- 55

72

nC

VGS = 10 V

-- 12

--

nC

ad9850中文资料

海纳电子资讯网:www.fpga-arm.com目录摘要 —————————————————————————2 创新之处 ———————————————————————2 关键词 ————————————————————————2 引言 —————————————————————————2 系统工作原理 —————————————————————3 直接数字频率合成 ———————————————————4 DDS 基本原理及性能特点 —————————————————5 采用 DDS 的 AD9851 ———————————————————6 AD9851 的原理 —————————————————————7 AD9851 在信号源中的应用 ————————————————8 AD9851 在本系统的应用电路 ———————————————9 低通滤波器(LPF) ——————————————————10 锁相环频率合成 ———————————————————11 锁相环频率合成 MC145151 在本电路中的应用 ————————12 压控振荡器(VCO) ———————————————————12 缓冲放大器 ——————————————————————13 单片机控制的整体电路 —————————————————14 功率放大 ———————————————————————15 本系统的软件设计 ———————————————————15 总调试 ————————————————————————25 结束语 ————————————————————————25 DDS 短波信号发生器技术指标 ——————————————26 所采用的仪器设备 ———————————————————26 所用软件 ———————————————————————26 参考文献 ———————————————————————26 参考网站 ———————————————————————27www.fpga-ar m1.海纳电子资讯网:www.fpga-arm.comDDS 短波信号发生器摘要: 本文主要介绍的是采用直接数字频率合成的短波信号发生器, 它 主要以微电脑控制部分、直接数字频率合成(DDS)部分、数字锁相 环频率合成部分、背光液晶显示部分、功率放大部分等组成。

BL8509-290资料

Low Voltage Detector with Built-in Delay CircuitBL8509 Outline:BL8509 is a series of high precision voltage detector with ultra low current consumption (500nA typ. at Vdd=3.0V) and a built-in delay circuit. It can work at very low voltage, which makes it perfect for system reset.BL8509 is composed of high precision voltage reference, comparator, delay circuit, output driver and resistor array. Internally preset detect voltage has a low temperature drift and requires no external trimming.Two type of output, CMOS and N-channel open-drain are available.BL8509 is available in SOT-23 which is Pb free.High-precision detection Voltage2% Detection Voltage0.9V~6.0V (in 0.1V steps) Built-in Power on Reset Delay Time circuit::Refer to Selection GuideOperating Voltage range0.7V~10VUltra-low current consumption500nA typ. (at V DD 3.0V)Two Output forms CMOS and N-channel open-drain (Active Low)Power monitor for portable equipment such as PDA,DSC,Mobile phone,Notebook,MP3CPU and Logic Circuit ResetBattery CheckerBattery Back-up CircuitPower Failure DetectorSelection Guide Pin Alignment8509-XXX X X XXPin Description :PIN NumberPIN NameFunction1 V SS GND Pin2 V OUT Voltage detection output Pin3V DDVoltage input PinOutput type N Nch C CMOS Detector voltage 0900.9V 100 1.0V 263 2.63V 300 3.0V 465 4.65V 600 6.0V (In 0.1V step)Package type RM SOT-23-3 Delay time A 50mS B 100mS C 150mS D 200mS E 250mS F 300mS G 400mSBlock diagram:Input Voltage range-------------------------------------------------------------------------------------0.3V~12V Output Voltage range-----------------------------------------------------------------------------------0.3V~12V Maximum Output current-----------------------------------------------------------------------------70mA Maximum power dissipation-------------------------------------------------------------------------150mW Ambient temperature---------------------------------------------------------------------------------- -40~+70C Storage temperature----------------------------------------------------------------------------------- -40~125C Lead temperature and time--------------------------------------------------------------------------260C,10SRecommended Work ConditionsItem Min Recommended Max unitInput Voltage range 0.7 10 V Ambient temperature -40 25 70Electrical CharacteristicsBL8509-090DNRM0.9V(Topt25,Unless otherwise specified.)Reference dataSymbol Parameter ConditionsMin. Typ. Max.Unit -V DET Detector Threshold 0.882 0.9 0.918 VI SS Current consumption V DD=2.9V 1 1.5 uAV DDH Maximum operatingvoltage10 VV DDL Minimum Operatingvoltage0.5 VNchV DS=0.05V V DD=0.7VV DS=0.50V V DD=0.8V0.010.050.050.50mAI OUT Output currentPchV DS=-2.1V V DD=4.50V 1.0 2.0 mAN channel open-drain CMOS outputBL8509-270DNRM 2.7V(Topt25,Unless otherwise specified.)Reference dataSymbol Parameter ConditionsMin. Typ. Max.Unit -V DET Detector Threshold 2.646 2.7 2.754 VI SS Current consumption V DD=4.7V 0.5 1 uAV DDH Maximum operatingvoltage10 VV DDL Minimum Operatingvoltage0.5 VNchV DS=0.05VV DD=0.70V 0.01 0.05mAI OUT Output currentPchV DS=-2.1VV DD=4.50V 1.0 2.0mA BL8509-300DNRM 3.0V(Topt25,Unless otherwise specified.)Reference dataSymbol Parameter ConditionsMin. Typ. Max.Unit -V DET Detector Threshold 2.94 3.0 3.06 VI SS Current consumption V DD=5.0V 0.5 1 uAV DDH Maximum operatingvoltage10 VV DDL Minimum Operatingvoltage0.5 VNchV DS=0.05V V DD=0.7V0.01 0.05mAI OUT Output currentPchV DS=-2.1V V DD=4.50V 1.0 2.0mA BL8509-340DNRM 3.4V(Topt25,Unless otherwise specified.)Reference dataSymbol Parameter ConditionsMin. Typ. Max.Unit -V DET Detector Threshold 3.332 3.4 3.468 VI SS Current consumption V DD=5.0V 0.5 1 uAV DDH Maximum operatingvoltage10 VV DDL Minimum Operatingvoltage0.5 VNchV DS=0.05V V DD=0.7V0.01 0.05mAI OUT Output currentPchV DS=-2.1V V DD=4.50V 1.0 2.0mABL8509-440DNRM 4.4V(Topt25,Unless otherwise specified.)Reference dataSymbol Parameter ConditionsMin. Typ. Max.Unit -V DET Detector Threshold 4.312 4.4 4.488 VI SS Current consumption V DD=6.4V 0.5 1 uAV DDH Maximum operatingvoltage10 VV DDL Minimum Operatingvoltage0.5 VNchV DS=0.05V V DD=0.7V0.01 0.05mAI OUT Output currentPchV DS=-2.1V V DD=8.0V 1.5 3.0mAElectrical Characteristics By Detector ThresholdDetector Threshold Supply Current1 Supply Current2-Vdet[V] Iss1[uA] Iss2[uA] Part NumberMin. Typ. Max. Condition Typ. Max. Condition Typ. Max.BL8509-0900XXXXX 0.882 0.900 0.918BL8509-1000XXXXX 0.980 1.000 1.020BL8509-1100XXXXX 1.078 1.100 1.122BL8509-1200XXXXX 1.176 1.200 1.224BL8509-1300XXXXX 1.274 1.300 1.326BL8509-1400XXXXX 1.372 1.400 1.428BL8509-1500XXXXX 1.470 1.500 1.530BL8509-1600XXXXX 1.568 1.600 1.632BL8509-170XXXX 1.666 1.700 1.734BL8509-180XXXX 1.764 1.800 1.836BL8509-190XXXX 1.862 1.900 1.9381.0 1.5BL8509-200XXXX 1.960 2.000 2.040BL8509-210XXXX 2.058 2.100 2.142BL8509-220XXXX 2.156 2.200 2.244BL8509-230XXXX 2.254 2.300 2.346BL8509-240XXXX 2.352 2.400 2.448BL8509-250XXXX 2.450 2.500 2.550BL8509-260XXXX 2.548 2.600 2.652BL8509-270XXXX 2.646 2.700 2.754BL8509-280XXXX 2.744 2.800 2.856BL8509-290XXXX 2.842 2.900 2.958BL8509-300XXXX 2.940 3.000 3.060BL8509-310XXXX 3.038 3.100 3.162BL8509-320XXXX 3.136 3.200 3.264BL8509-330XXXX 3.234 3.300 3.366BL8509-340XXXX 3.332 3.400 3.468 BL8509-350XXXX 3.430 3.500 3.570 BL8509-360XXXX 3.528 3.600 3.672 BL8509-370XXXX 3.626 3.700 3.774 BL8509-380XXXX 3.724 3.800 3.876 BL8509-390XXXX 3.822 3.900 3.978 BL8509-400XXXX 3.920 4.000 4.080 BL8509-410XXXX 4.018 4.100 4.182 BL8509-420XXXX 4.116 4.200 4.284 BL8509-430XXXX 4.214 4.300 4.386 BL8509-440XXXX 4.312 4.400 4.488 BL8509-450XXXX 4.410 4.500 4.590 BL8509-460XXXX 4.508 4.600 4.692 BL8509-470XXXX 4.606 4.700 4.794 BL8509-480XXXX 4.704 4.800 4.896 BL8509-490XXXX 4.802 4.900 4.998 BL8509-500XXXX 4.900 5.000 5.100 BL8509-510XXXX 4.998 5.100 5.202 BL8509-520XXXX 5.096 5.200 5.304 BL8509-530XXXX 5.194 5.300 5.406 BL8509-540XXXX 5.292 5.400 5.508 BL8509-550XXXX 5.390 5.500 5.610 BL8509-560XXXX 5.488 5.600 5.712 BL8509-570XXXX 5.586 5.700 5.814 BL8509-580XXXX 5.684 5.800 5.916 BL8509-590XXXX 5.782 5.900 6.018 BL8509-600XXXX 5.880 6.000 6.120Vdd=(-Vdet)+0.1V0.5 1.0Vdd=(-Vdet)+2V0.5 1.0Output Current1Output Current2 Minimum Operating Voltage Detector Threshold Temperature CoefficientIout1[mA]Iout2[mA]V DDL [V] -V DET /Tppm/°CCondition Min. Typ.ConditionMin. Typ. Typ. Max. Condition Typ. Vdd=0.85V0.10.5Vdd=1.0V 0.2 1.0NCH,V DS =0.05V , V DD =0.7V 0.01 0.05NCH,V DS =0.5V V DD =1.5V1.02.00.5 0.7-40CTopt 85C100Electrical Characteristics by Output Delay TimeOutput Delay Time UnitPart NumberTest ConditionMin. Typ. Max.8509-xxxAxxx 45 50 55 8509-xxxBxxx 90 100 110 8509-xxxCxxx 135 150 165 8509-xxxDxxx 180 200 220 8509-xxxExxx 225 250 275 8509-xxxFxxx 270 300 330 8509-xxxGxxxVDD=1.0V to Vdet+1.0V 360400440msFunction description:DelayComparatorHigh precision low temperature co-efficiency reference voltage is applied to the negative input of a comparator. Input voltage, divided by resistor array of Ra and Rb, is applied to the positive input of the comparator. Output of the comparator passes a delay circuit and a series of buffer to drive the output CMOS pair.V DET =V REF*(1+Ra/Rb)Supply VoltageDetector Treshold(Vdet) =Release VoltageMinimumOperating VoltageOutput Voltage (OUT)TdelayNo.Operation statusOutput statusI V DD >V detOutput voltage is equal to the supply voltageII V DD drops below V det Output voltage equals to GND levelIII V DD drops further belowV DDLOutput voltage is undefined IV V DD rises above V DDL Output voltage equals to GND levelVV DD rises above V detOutput voltage equals to supply voltage after TdelayTest circuits1Supply current test circuit2Detector threshold test circuitBL8509BL85093NCH Drive Output Current Test Circuit 4PCH Drive Output Current Test CircuitBL8509BL8509Typical Performance Characteristics1) Supply current VS. Input voltageDetector threshold= 0.9V1.E -081.E -071.E -061.E -05Input voltage (V)S u p p l y c u r r e n t (A )-40ºC25ºC 70ºCDetector threshold=2.7V123456Input voltage (V)S u p p l y c u r r e n t (A )-40ºC 25ºC 70ºCDetector threshold=3.0V1.E -081.E -071.E -061.E -05123456Input voltage (V)S u p p l y c u r r e n t (A )-40ºC 25ºC 70ºCDetector threshold=4.4V123456Input voltage (V)S u p p l y c u r r e n t (A )-40ºC 25ºC 70ºC2) Detector Threshold VS. TemperatureDetector threshold=3.0V2.902.922.942.962.983.003.023.04-50-30-101030507090Temperature(°C)D e t e c t o r t h r e s h o l d (V )Detector threshold= 0.9V0.850.860.870.880.890.900.910.920.930.940.95-50-30-101030507090Temperature (°C)D e t e c t o r t h r e s h o l d (V )Detector threshold=4.4V4.304.324.344.364.384.404.424.444.464.484.50-50-30-101030507090Temperature(°C)D e t e c t o r t h r e s h o l d (V )Detector threshold=2.7V2.542.582.622.662.702.742.78-50-30-101030507090Temperature(°C)D e t e c t o r t h r e s h o l d (V )3Nch Driver Output Current VS. V DSBL8509-090xxx0.00E+001.00E-042.00E-043.00E-044.00E-045.00E-046.00E-047.00E-048.00E-040.000.200.400.600.80VDS (V)O u t p u t c u r r e n t A )VDD=0.7V VDD=0.8VBL8509-270xxx0.00E+002.00E-034.00E-036.00E-038.00E-031.00E-021.20E-020.000.501.001.502.002.50VDS (V)O u t p u t c u r r e n t A )VDD=1.0V VDD=2.0VBL8509-300xxx0.00E+002.00E-034.00E-036.00E-038.00E-031.00E-021.20E-020.000.501.001.502.002.50VDS (V)O u t p u t c u r r e n t A )VDD=1.0V VDD=2.0VBL8509-440xxx0.00E+005.00E-031.00E-021.50E-022.00E-022.50E-020.001.002.003.004.00VDS (V)O u t p u t c u r r e n t A )VDD=1.0V VDD=2.0V VDD=3.0V4NCH Driver Output Current vs. Input VoltageDetector threshold=2.7V0.E+004.E-038.E-031.E-02Input Voltage Vin (V)O u t p u t C u r r e n t I o u t (A )-40ºC 25ºC75ºCDetector threshold=3.0V0.E+004.E-038.E-031.E-02Input Voltage Vin (V)O u t p u t C u r r e n t I o u t (A )-40ºC 25ºC75ºC5PCH Driver Output Current vs. Input CurrentDetector threshold=0.9V0.02.04.06.08.002468Input Voltage VinVO u t p u t C u r r e n t I o u t (m A )VDS=0.5V VDS=0.7VDetector threshold=2.7V0.05.010.015.020.001234567Input Voltage Vin V O u t p u t C u r r e n t I o u t m AVDS=0.5V VDS=1.0V VDS=1.5V VDS=2.0VDetector threshold=4.4V0.05.010.015.020.025.00246810Input Voltage Vin VO u t p u t C u r r e n t I o u t m AVDS=0.5V VDS=1.0V VDS=1.5V VDS=2.0VTypical applicationsNote1. R0 is unnecessary for CMOS outputproducts.2. The value of R0 need to be selected indifferent application, Typical value is470kPackage OutlineSOT-23-3:3000 Unit mm Package SOT-23-3 Devices perreelPackage dimensionTaping SpecificationTaping reel dimension。

N80930AD4资料

ADVANCE INFORMATIONCOPYRIGHT © INTEL CORPORATION, 1997February 1997Order Number: 272917-0038x 930A xUNIVERSAL SERIAL BUS MICROCONTROLLERThe 8x 930A x USB microcontroller is based on an 8x C251S x microcontroller core. It consists of standard 8x C251Sx peripherals plus an added USB function. The 8x 930A x uses the standard instruction set of the MCS 251 architecture, which is binary code compatible with the MCS 51 architecture. The USB function integrates the USB transceiver, serial bus interface engine (SIE), function interface unit (FIU) and transmit/receive FIFOs. The USB function also supports full-speed/low-speed data rates, suspend/resume modes, isochronous/non-isochronous transfers, and is fully compliant with the USB rev 1.0 specification.s Complete Universal Serial Bus Specification 1.0 Compatibility —Supports Isochronous and Non-isochronous Data —Bidirectional Half-duplex Link s On-chip USB Transceiver s Serial Bus Interface Engine (SIE)—Packet Decoding/Generation —CRC Generation and Checking —NRZI Encoding/Decoding and Bit-stuffing s USB Reset Interrupt s Four Transmit FIFOs —Three 16-byte FIFOs—One Configurable FIFO (up to 1 Kbyte) s Four Receive FIFOs —Three 16-byte FIFOs—One Configurable FIFO (up to 1 Kbyte)s Automatic Transmit/Receive FIFO Management s Suspend/Resume Operation s Three New USB Interrupt Vectors —USB Function Interrupt —Start of Frame —Suspend/Resumes Phase-locked Loop—12 Mbps or 1.5 Mbps Data Rates Low Clock Modes User-selectable Configurations —External Wait State —Address Range —Page Modes Real-time Wait Functions 256-Kbyte External Code/Data Memory Space s On-chip ROM Options —0, 8, or 16 Kbytes s 1 Kbyte On-chip Data RAM s Four Input/Output Ports —1 Open-drain port —3 Quasi-bidirectional Ports s Programmable Counter Array (PCA)—5 Capture/Compare Modules s Serial I/O Port (UART)s Hardware Watchdog Timers Three Flexible 16-bit Timer/Counters s Power-saving Idle and Powerdown Modes s Register-based MCS ® 251 Architecture —40-byte Register File —Registers Accessible as Bytes, Words, or Doublewords s Code Compatible with MCS 51 and MCS 251 Microcontrollers s 6 or 12 MHz Crystal OperationInformation in this document is provided in connection with Intel products. No license, express or implied, by estoppel or oth-erwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.Intel retains the right to make changes to specifications and product descriptions at any time, without notice.The product may contain design defects or errors known as errata. Current characterized errata are available on request.*Third-party brands and names are the property of their respective owners.Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:Intel CorporationLiterature SalesP.O. Box 7641Mt. Prospect, IL 60056-7641or call 1-800-548-4725COPYRIGHT © INTEL CORPORATION, 1997iii8x930Ax UNIVERSAL SERIAL BUS MICROCONTROLLER iv8x930Ax UNIVERSAL SERIAL BUS (USB) MICROCONTROLLERFigure 1. 8x930A x Internal Block DiagramADVANCE INFORMATION18x930Ax UNIVERSAL SERIAL BUS (USB) MICROCONTROLLERFigure 2. USB Module Block Diagram2ADVANCE INFORMATION8x930Ax UNIVERSAL SERIAL BUS (USB) MICROCONTROLLER 1.0NOMENCLATURE OVERVIEWFigure 3. Product NomenclatureTable 1. Description of Product NomenclatureParameter Options DescriptionTemperature and Burn-in no mark Commercial operating temperature range (0o C to 70o C) withIntel standard burn-in.Packaging Options N Plastic Leaded Chip Carrier (PLCC)Program Memory Options0Without ROM3With ROMProcess and Voltage Information no mark CHMOSProduct Family930Advanced 8-bit microcontroller architecture with on-chip Uni-versal Serial Bus (USB) function peripheralsDevice Speed no mark 6 or 12 MHz crystalTable 2. Proliferation OptionsProduct Name ROM Size RAM Size80930AD0 1 Kbyte83930AD8 Kbytes 1 Kbyte83930AE16 Kbytes 1 KbyteADVANCE INFORMATION34ADVANCE INFORMATION8x930Ax UNIVERSAL SERIAL BUS (USB) MICROCONTROLLER2.0PINOUTFigure 4. 8x 930A x 68-pin PLCC PackageFigure 4 illustrates the 8x 930A x PLCC package.Table 3 lists the pin assignments by pin number,and Table 4 lists the pin assignments by functional categories. Table 5 describes the signals.8x930Ax UNIVERSAL SERIAL BUS (USB) MICROCONTROLLERTable 3. 68-pin PLCC Pin AssignmentPin Name Pin Name Pin Name24P3.4/T047Reserved1VSS2A15/P2.725P3.5/T148Reserved3A14/P2.626P3.6/WR#49Reserved4A13/P2.527P3.7/RD#/A1650SOF#5A12/P2.428P1.0/T251VCCP6A11/P2.329P1.1/T2EX52VSSP7A10/P2.230P1.2/ECI53ECAP8A9/P2.131P1.3/CEX054DM09A8/P2.032P1.4/CEX155DP010AD7/P0.733P1.5/CEX256Reserved11AD6/P0.634P1.6/CEX3/WAIT#57Reserved12AD5/P0.535P1.7/CEX4/A17/WCLK58Reserved59Reserved13AD4/P0.436VCC60Reserved14AD3/P0.337VSS15AD2/P0.238XTAL161Reserved16AD1/P0.139XTAL262Reserved63Reserved17AD0/P0.040AVCC41RST64Reserved18VSSP42PLLSEL165PSEN#19VCCP20P3.0/RXD43PLLSEL266ALE21P3.1/TXD44PLLSEL067EA#22P3.2/INT0#45Reserved68VCC23P3.3/INT1#46ReservedADVANCE INFORMATION58x930Ax UNIVERSAL SERIAL BUS (USB) MICROCONTROLLERTable 4. 68-pin PLCC Signal Assignments Arranged by Functional Category Address & Data Input/Output USBName Pin Name Pin Name Pin AD0/P0.017P1.0/T228PLLSEL044 AD1/P0.116P1.1/T2EX29PLLSEL142 AD2/P0.215P1.2/ECI30PLLSEL243 AD3/P0.314P1.3/CEX031SOF#50 AD4/P0.413P1.4/CEX132ECAP5354 AD5/P0.512P1.5/CEX233DM055 AD6/P0.611P1.6/CEX3/WAIT#34DP0AD7/P0.710P1.7/CEX4/A17/WCLK35A8/P2.09P3.0/RXD20Processor Control A9/P2.18P3.1/TXD21Name Pin A10/P2.27P3.4/T024P3.2/INT0#22 A11/P2.36P3.5/T125P3.3/INT1#23 A12/P2.45EA#67 A13/P2.54Bus Control & Status RST41 A14/P2.63Name Pin XTAL138 A15/P2.72P3.6/WR#26XTAL239 P3.7/RD#/A1627P3.7/RD#/A1627P1.7/CEX4/A17/WCLK35ALE66PSEN#65Power & GroundName Pin36, 68VCC19, 51VCCP40AVCCEA#671, 37VSS18, 52VSSP6ADVANCE INFORMATION3.0SIGNALSTable 5. Signal DescriptionsSignal NameType DescriptionAlternate FunctionA17O18th Address Bit (A17). Output to memory as 18th exter-nal address bit (A17) in extended bus applications, depend-ing on the values of bits RD0 and RD1 in configuration byte UCONFIG0. See also RD#, PSEN#.P1.7/CEX4/WCLKA16O Address Line 16. See RD#.RD#A15:8†O Address Lines . Upper address lines for the external bus.P2.7:0AD7:0†I/O Address/Data Lines . Multiplexed lower address lines and data lines for external memory.P0.7:0ALEOAddress Latch Enable (ALE). ALE signals the start of an external bus cycle and indicates that valid address informa-tion is available on lines A15:8 and AD7:0. An external latch can use ALE to demultiplex the address from the address/data bus.PROG#AV CC PWR Analog V CC . A separate V CC input for the phase-locked loop circuitry.CEX2:0CEX3CEX4I/OProgrammable Counter Array (PCA) Input/Output Pins . These are input signals for the PCA capture mode and out-put signals for the PCA compare mode and PCA PWM mode.P1.5:3P1.6/WAIT#P1.7/A17/WCLK D M 0I/O Data Minus . USB minus data line interface.—D P 0I/O Data Plus . USB plus data line interface.—EA#IExternal Access . Directs program memory accesses to on-chip or off-chip code memory. For EA# strapped toground, all program memory accesses are off-chip. For EA# strapped to V CC , program accesses on-chip ROM if the address is within the range of the on-chip ROM; otherwise, the access is off-chip. The value of EA# is latched at reset. For devices without on-chip ROM, EA# must be strapped to ground.ECAP IExternal Capacitor . Must be connected to a 1 µF capacitor (or larger) to ensure proper operation of the differential line driver. The other lead of the capacitor must be connected to V SS .ECI I PCA External Clock Input . External clock input to the 16-bit PCA timer.P1.2INT1:0#IExternal Interrupts 0 and 1. These inputs set bits IE1:0 in the TCON register. If bits IT1:0 in the TCON register are set, bits IE1:0 are set by a falling edge on INT1#/INT0#. If bits INT1:0 are clear, bits IE1:0 are set by a low level on INT1:0#.P3.3:2P0.7:0I/O Port 0. This is an 8-bit, open-drain, bidirectional I/O port.AD7:0†The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration. If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 car-ries the upper address bits (A15:8) and the data (D7:0).P1.0 P1.1 P1.2 P1.5:3 P1.6 P1.7I/O Port 1. This is an 8-bit, bidirectional I/O port with internalpullups.T2T2EXECICEX2:0CEX3/WAIT#CEX4/A17/WCLKP2.7:0I/O Port 2. This is an 8-bit, bidirectional I/O port with internalpullups.A15:8P3.0 P3.1 P3.3:2 P3.5:4 P3.6 P3.7I/O Port 3. This is an 8-bit, bidirectional I/O port with internalpullups.RXDTXDINT1:0#T1:0WR#RD#/A16PLLSEL2:0I Phase-locked Loop Select. Three-bit code selects USBdata rate (see Table 8 on page 12).—PSEN#O Program Store Enable. Read signal output. This output isasserted for a memory address range that depends on bitsRD0 and RD1 in configuration byte UCONFIG0 (see RD#).—RD#O Read or 17th Address Bit (A16). Read signal output toexternal data memory or 17th external address bit (A16),depending on the values of bits RD0 and RD1 in configura-tion byte UCONFIG0 (See PSEN#).P3.7/A16RST I Reset. Reset input to the chip. Holding this pin high for 64oscillator periods while the oscillator is running resets thedevice. The port pins are driven to their reset conditionswhen a voltage greater than V IH1 is applied, whether or notthe oscillator is running. This pin has an internal pulldownresistor which allows the device to be reset by connecting acapacitor between this pin and VCC.Asserting RST when the chip is in idle mode or powerdownmode returns the chip to normal operation.—RXD I/O Receive Serial Data. RXD sends and receives data inserial I/O mode 0 and receives data in serial I/O modes 1, 2,and 3.P3.0SOF#O Start of Frame. Start of Frame pulse. Active low, assertedfor 8 states (see Table 8 on page 12 for state versus XTALclock) when Frame Timer is locked to USB frame timingand SOF token or artificial SOF is detected.—T1:0I Timer 1:0 External Clock Inputs. When timer 1:0 operatesas a counter, a falling edge on the T1:0 pin increments thecount.P3.5:4T2I/O Timer 2 Clock Input/Output. For the timer 2 capture mode,this signal is the external clock input. For the clock-outmode, it is the timer 2 clock output.P1.0Table 5. Signal Descriptions (Continued)SignalName Type Description Alternate Function†The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration. If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 car-ries the upper address bits (A15:8) and the data (D7:0).T2EX I Timer 2 External Input. In timer 2 capture mode, a fallingedge initiates a capture of the timer 2 registers. In auto-reload mode, a falling edge causes the timer 2 registers tobe reloaded. In the up-down counter mode, this signaldetermines the count direction: 1 = up, 0 = down.P1.1TXD O Transmit Serial Data. TXD outputs the shift clock in serialI/O mode 0 and transmits serial data in serial I/O modes 1,2, and 3.P3.1VCC PWR Supply Voltage. Connect this pin to the +5V supply volt-age.—VCCP PWR Supply Voltage for I/O buffers. Connect this pin to the +5V supply voltage.—VSSGND Circuit Ground. Connect this pin to ground.—VSSPGND Circuit Ground for I/O buffers. Connect this pin to ground.—WAIT#I Real-time Wait State Input. The real-time WAIT# input isenabled by writing a logical ‘1’ to the WCON.0 (RTWE) bitat S:A7H. During bus cycles, the external memory systemcan signal ‘system ready’ to the microcontroller in real timeby controlling the WAIT# input signal on the port 1.6 input.P1.6/CEX3WCLK O Wait Clock Output. The real-time WCLK output is driven atport 1.7 (WCLK) by writing a logical ‘1’ to the WCON.1(RTWCE) bit at S:A7H. When enabled, the WCLK outputproduces a square wave signal with a period of TCLK .P1.7/CEX4/A17WR#O Write. Write signal output to external memory. P3.6 XTAL1I Input to the On-chip, Inverting, Oscillator Amplifier. Touse the internal oscillator, a crystal/resonator circuit is con-nected to this pin. If an external oscillator is used, its outputis connected to this pin. XTAL1 is the clock source for inter-nal timing.—XTAL2O Output of the On-chip, Inverting, Oscillator Amplifier. Touse the internal oscillator, a crystal/resonator circuit is con-nected to this pin. If an external oscillator is used, leaveXTAL2 unconnected.—Table 5. Signal Descriptions (Continued)SignalName Type Description Alternate Function†The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage-mode chip configuration. If the chip is configured for page-mode operation, port 0 carries the lower address bits (A7:0), and port 2 car-ries the upper address bits (A15:8) and the data (D7:0).†RD1:0 are bits 3:2 of configuration byte UCONFIG0. Refer to figure 4-3 on page 4-5 in the 8x930Ax Uni-versal Serial Bus Microcontroller User’s Manual .4.0ADDRESS MAPTable 6. Memory Signal Selections (RD1:0)RD1:0†A17/P1.7/CEX4/WCLK A16/P3.7/RD#PSEN#WR#Features 0 0A17A16Asserted forall addresses Asserted for writes to all memory locations 256-Kbyte external memory0 1P1.7/CEX4/WCLK A16Asserted for all addresses Asserted for writes to all memory locations 128-Kbyte external memory1 0P1.7/CEX4/WCLKP3.7 onlyAsserted for all addressesAsserted for writes to all memory locations64-Kbyte external memoryOne additional port pin1 1P1.7/CEX4/WCLKRD# Asserted for addresses ≤ 7F:FFFFH Asserted for addresses ≥ 80:0000H Asserted for all com-patible MCS 51 mem-ory locationsCompatible with MCS 51 microcon-trollersTable 7. 8x 930A x Address MapInternal Address DescriptionNotes FF:FFFFH FF:0000H External Memory: The last eight bytes of the external address range FF:XFF8H–FF:XFFFH contain configuration byte information.1, 2, 3FE:FFFFH FE:0000H External Memory 2FD:FFFFH 02:0000H Reserved Addresses 401:FFFFH 01:0000H External Memory 200:FFFFH 00:0420H External Memory 500:041FH 00:0080H On-chip RAM 500:007FH 00:0020H On-chip RAM600:001FH 00:0000HStorage for R0–R7 of Register File7, 8NOTES:1.Eighteen address lines are bonded out (A15:0, A16:0, or A17:0 selected during chip configuration).2.Data in this area is accessible by indirect addressing only.3.Eight addresses at the top of all external memory maps are reserved for current and future deviceconfiguration byte information.4.This reserved area returns unspecified values and writes no data.5.Data is accessible by direct and indirect addressing.6.Data is accessible by direct, indirect, and bit addressing.7.The special function registers (SFRs) and the register file have separate internal address spaces.8.Data is accessible by direct, indirect, and register addressing.5.0ELECTRICAL CHARACTERISTICSABSOLUTE MAXIMUM RATINGSAmbient Temperature Under Bias....................-40°C to +85°C Storage Temperature ................................... -65°C to +150°C Voltage on Any Pins to VSS............................. -0.5 V to +6.5 VIOLper I/O Pin.................................................................15 mA Power Dissipation.......................................................... 1.5 W OPERATING CONDITIONS†TA(Ambient Temperature Under Bias): Commercial........................................................-0°C to +70°CV CC /VCCP(Digital Supply Voltage) .................. 4.00 V to 5.25 VV SS / VSSP............................................................................ 0 VAVCC(Analog Supply Voltage) ...................... 4.00 V to 5.25 VFOSC.............................................................. 6 MHz or 12 MHz NOTE:Maximum power dissipation is based onpackage heat-transfer limitations, not devicepower consumption.NOTICE: This document contains information on products in the sampling and initial production phases of development. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.†WARNING: Stressing the device beyond the “Absolute Maximum Ratings” may cause perma-nent damage. These are stress ratings only. Oper-ation beyond the “Operating Conditions” is not recommended and extended exposure beyond the “Operating Conditions” may affect device reliability.5.1Operating FrequenciesFigure 5. Clock CircuitTable 8. Frequency Selection and Operating FrequencyPLLSEL2Pin 43PLLSEL1Pin 42PLLSEL0Pin 44USB Rate (Low Speed or Full Speed)8x 930A x Internal Frequency for CPU and Peripherals (F CLK ) (5)XTAL1External Frequency (F OSC )Number of XTAL1 Clocks (T OSC )in One StateTime(4)Comments001 1.5 Mbps (LS) 3 MHz 6 MHz 2 T OSC /statePLL Off100 1.5 Mbps (LS) 6 MHz (3)12 MHz 2 T OSC /state PLL Off 1112 Mbps (FS)12 MHz (3)12 MHz1 T OSC /state PLL OnNOTES:1.Other PLLSEL x combinations are not valid.2.The sampling rate is 4X the USB rate.3.The 8x 930A x CPU and peripherals frequency is 3 MHz (low clock mode) until firmware disables thelow clock mode.4.The number of XTAL clocks in one state depends on the PLLSELx selections. When the CPU is oper-ating at low clock mode (3 MHz), there are four T OSC per state for the PLLSEL2:1:0 = 100 and 110.5.The AC timing specification (Table 11) defines the following symbol: CPU frequency = F CLK = 1/T CLK.5.2DC CharacteristicsTable 9. DC Characteristics at Operating ConditionsSymbol Parameter Min Typical (1)Max Units Test ConditionsV IL Input Low Voltage(Except EA#)-0.50.2 VCC– 0.1VV IL1Input Low Voltage(EA#)00.2VCC– 0.3VV IH InputHighVoltage(Except XTAL1, RST)0.2 VCC+ 0.9VCC+ 0.5VVIH1Input High Voltage(XTAL1, RST)0.7 VCCVCC+ 0.5VV OL Output Low Voltage(Port 1, 2, 3)0.30.451.0VIOL= 100 µA (2, 3)IOL= 1.6 mAIOL= 3.5 mAV OL1Output Low Voltage(Port 0, ALE, PSEN#,SOF#)0.30.451.0VIOL= 200 µA (2, 3)IOL= 3.2 mAIOL= 7.0 mAV OH Output High Voltage(Port 1, 2, 3,ALE,PSEN#, SOF#)VCC– 0.3VCC– 0.7VCC– 1.5VIOH= -10 µA (4)IOH= -30 µAIOH= -60 µAV OH1Output High Voltage(Port 0 in ExternalAddress)VCC– 0.3VCC– 0.7VCC– 1.5VIOH= -200 µA (4)IOH= -3.2 mAIOH= -7.0 mAI IL Logical 0 InputCurrent (Port 1,2,3)–150µA VIN= 0.45 VI LI Input Leakage Current(Port 0)±10µA0.45 < V IN< V CCNOTE:1.Typical values are obtained using VCC = 5.0V, TA= 25°C and are not guaranteed.2.Under steady state (non-transient) conditions, IOL must be externally limited as follows:Maximum IOH per port pin:10 mAMaximum IOL per 8-bit port:Port 0: 26 mA Ports 1-3: 15 mAMaximum Total IOL for all output pins: 71 mAIf IOL exceeds the test conditions, VOLmay exceed the related specification. Pins are not guaranteedto sink current greater than the listed test conditions.3.Capacitive loading on Ports 0 and 2 may cause spurious noise pulses above 0.4 V on the low-leveloutputs of ALE and Ports 1, 2 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins change from 1 to 0. In applications where capacitive loading exceeds 100pF, the noise pulses on these signals may exceed 0.8 V. It may be desirable to qualify ALE or other signals with a Schmitt Trigger or CMOS-level input logic.4.Capacitive loading on Ports 0 and 2 cause the VOH on ALE and PSEN to drop below the VCCspecifica-tion when the address lines are stabilizing.5.The abbreviations “LS” and “FS” indicate “Low Speed” and “Full Speed,” respectively.I TLLogical 1-to-0 Transition Current (Port 1, 2,3) -650µA V IN = 2.0 VR RST RST Pulldown Resistor40225K ΩC IO 10pFF OSC = 12 MHz T A = 25°CI PDPowerdown Current — Normal powerdown — USB suspend2514550175µAI DL (5)Idle Mode I CC 40mAPLLSEL = 110 3MHz – FS(in low clock mode)100PLLSEL = 11012MHz – FS (not in low clock mode)30PLLSEL = 0013MHz – LS 55PLLSEL = 1006 MHz – LSTable 9. DC Characteristics at Operating Conditions (Continued)SymbolParameterMinTypical (1)MaxUnitsTest ConditionsNOTE:1.Typical values are obtained using V CC = 5.0V, T A = 25°C and are not guaranteed.2.Under steady state (non-transient) conditions, I OL must be externally limited as follows:Maximum I OH per port pin:10 mA Maximum I OL per 8-bit port:Port 0: 26 mA Ports 1-3: 15 mA Maximum Total I OL for all output pins: 71 mAIf I OL exceeds the test conditions, V OL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.3.Capacitive loading on Ports 0 and 2 may cause spurious noise pulses above 0.4 V on the low-leveloutputs of ALE and Ports 1, 2 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins change from 1 to 0. In applications where capacitive loading exceeds 100pF, the noise pulses on these signals may exceed 0.8 V. It may be desirable to qualify ALE or other signals with a Schmitt Trigger or CMOS-level input logic.4.Capacitive loading on Ports 0 and 2 cause the V OH on ALE and PSEN to drop below the V CC specifica-tion when the address lines are stabilizing.5.The abbreviations “LS” and “FS” indicate “Low Speed” and “Full Speed,” respectively.5.3Definition of AC SymbolsI CC (5)Active I CC 60mAPLLSEL = 1103 MHz – FS(in low clock mode)150PLLSEL = 11012 MHz – FS (not in low clock mode)45PLLSEL = 0013 MHz – LS 75PLLSEL = 1006 MHz – LSTable 10. AC Timing Symbol DefinitionsSignalsConditionsA Address H High D Data In L Low L ALE V Valid Q Data Out X Hold R RD#/PSEN#ZFloatingWWR#Table 9. DC Characteristics at Operating Conditions (Continued)SymbolParameterMinTypical (1)MaxUnitsTest ConditionsNOTE:1.Typical values are obtained using V CC = 5.0V, T A = 25°C and are not guaranteed.2.Under steady state (non-transient) conditions, I OL must be externally limited as follows:Maximum I OH per port pin:10 mA Maximum I OL per 8-bit port:Port 0: 26 mA Ports 1-3: 15 mA Maximum Total I OL for all output pins: 71 mAIf I OL exceeds the test conditions, V OL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.3.Capacitive loading on Ports 0 and 2 may cause spurious noise pulses above 0.4 V on the low-leveloutputs of ALE and Ports 1, 2 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins change from 1 to 0. In applications where capacitive loading exceeds 100pF, the noise pulses on these signals may exceed 0.8 V. It may be desirable to qualify ALE or other signals with a Schmitt Trigger or CMOS-level input logic.4.Capacitive loading on Ports 0 and 2 cause the V OH on ALE and PSEN to drop below the V CC specifica-tion when the address lines are stabilizing.5.The abbreviations “LS” and “FS” indicate “Low Speed” and “Full Speed,” respectively.5.4AC CharacteristicsTest Conditions: Capacitive load on all pins = 50 pF, Rise and Fall times = 10 ns, FOSC= 6 MHz or 12 MHz 5.4.1SYSTEM BUS AC CHARACTERISTICSTable 11. AC Characteristics at Operating ConditionsSymbol Parameter CPU Frequency@ 12 MHz(M, N = 0)CPU Frequency (FCLK) VariableUnitsMin MaxT CLK 1/(CPU Frequency)83.33(Typical)ns(1, 2)T LHLL ALE Pulse Width34.66(0.5+M)TCLK– 7ns(3)T AVLL Address Valid to ALE Low26.66(0.5+M)TCLK–17ns (3)TLLAXAddress Hold after ALE Low44ns (4)T RLRH (5)RD# or PSEN# Pulse Width73.33(1+N)TCLK– 10ns (6)T WLWH WR# Pulse Width71.33(1+N)TCLK– 12ns (6)TLLRL(5)ALE Low to RD# or PSEN# Low88nsT LHAX ALE High to Address Hold40.33(1+M)TCLK– 43ns (3)T RLDV (5)RD# or PSEN# Low to ValidData/Instruction In50.33(1+N)TCLK– 33ns (6)T RHDX (5)Data/Instruct. Hold After RD# orPSEN# High00nsT RLAZ (5)RD# or PSEN# Low to AddressFloat00nsTRHDZ1(5)Instruct. Float After PSEN# High1010nsT RHDZ2 (5)Data Float After RD# or PSEN#High83.33TCLKnsT RHLH1 (5)PSEN# High to ALE High(Instruction)1010nsT RHLH2 (5)RD# or PSEN# High to ALEHigh (Data)83.33TCLKnsT WHLH WR# High to ALE High88.33TCLK+ 5nsT AVDV1Address (P0) Valid to ValidData/Instruction In106.66(2+M+N)TCLK–63ns(3, 6)NOTES:1.Refer to Table 8 on page 12 for CPU frequencies vs. XTAL1 frequencies.2.XTAL1 frequency is ± 0.25% for full speed and ± 1.5% for low speed.3.M= 0,1 is the extended ALE state.4.At 50° C, TLLAX = 8 ns5.Specifications for PSEN# are identical to those for RD#.6.N= 0,1,2,3 is the RD#/PSEN#/WR# wait state.T AVDV2 Address (P2) Valid to ValidData/Instruction In118.66(2+M+N)TCLK– 48ns(3, 6)T AVDV3Address (P2) Valid to ValidInstruction In23.33(1+N)TCLK– 60ns (6)T AVRL (5)Address Valid to RD# or PSEN#Low40.33(1+M)TCLK– 46ns (3)T AVWL1Address (P0) Valid to WR# Low40.33(1+M)TCLK– 46ns (3)T AVWL2Address (P2) Valid to WR# Low66.33(1+M)TCLK– 17ns (3)T WHQX Data Hold after WR# High28.660.5 TCLK– 13nsT QVWH Data Valid to WR# High68.33(1+N)TCLK–15ns (6)T WHAX WR# High to Address Hold70.33TCLK– 13ns Table 11. AC Characteristics at Operating Conditions (Continued)Symbol Parameter CPU Frequency@ 12 MHz(M, N = 0)CPU Frequency (FCLK) VariableUnitsMin MaxNOTES:1.Refer to Table 8 on page 12 for CPU frequencies vs. XTAL1 frequencies.2.XTAL1 frequency is ± 0.25% for full speed and ± 1.5% for low speed.3.M= 0,1 is the extended ALE state.4.At 50° C, TLLAX = 8 ns5.Specifications for PSEN# are identical to those for RD#.6.N= 0,1,2,3 is the RD#/PSEN#/WR# wait state.。

19U100PG7K资料

Pressure SensorsLow-Cost, Stainless Steel, Isolated Sensors 19 mm SeriesPERSONAL INJURYDO NOT USE theseMISUSE OF DOCUMENTATION•The information presented in this product sheet is for reference only. DoPressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm Series2 Honeywell • Sensing and ControlPRESSURE SENSOR CHARACTERISTICS – ALL DEVICESEnvironmental specifications Compensated temperature range 0 °C to 82 °C [32 °F to 180 °F] Operating temperature range -40 °C to 125 °C [-40 °F to 257 °F] Storage temperature range -40 °C to 125 °C [-40 °F to 257 °F] Vibration 10 G at 20 Hz to 2000 Hz Shock 100 G for 11 ms Life1 million cycles min. Insulation resistance 100 m Ω at 50 VdcMaximum ratings Voltage version “K” Supply voltage V S = +15 Vdc Voltage version “L”Supply current I S = +2.0 mAPRESSURE RANGE SPECIFICATIONS (19C, 19U)Catalog ListingPressure range Proof pressure (7)Burst pressure (8)19(C,U) 003P G (1…9) (K/L) 0 psig to 3 psig 9 psig 15 psig 19(C,U) 005P G (1…9) (K/L) 0 psig to 5 psig 15 psig 25 psig 19(C,U) 010P G (1…9) (K/L)0 psig to 10 psig 30 psig 50 psig 19(C,U) 015P (A,G,V) (1…9) (K/L) 0 psi to 15 psi 45 psi 75 psi 19(C,U) 030P (A,G,V) (1…9) (K/L) 0 psi to 30 psi 90 psi 150 psi 19(C,U) 050P (A,G,V) (1…9) (K/L) 0 psi to 50 psi 150 psi 250 psi 19(C,U) 100P (A,G,V) (1…9) (K/L) 0 psi to 100 psi 300 psi 500 psi 19(C,U) 200P (A,G,V) (1…9) (K/L) 0 psi to 200 psi 600 psi 1000 psi 19(C,U) 300P (A,G,V) (1…9) (K/L) 0 psi to 300 psi 900 psi 1500 psi 19(C,U) 500P (A,G,V) (1…9) (K/L)0 psi to 500 psi1200 psi 2400 psiNotes:7. The maximum pressure that can be applied without changing the transducer’s performance or accuracy.8.The maximum pressure that can be applied to a transducer without rupture of either the sensing element or transducer case.19C SERIES PERFORMANCE CHARACTERISTICS (1)Characteristic Minimum Typical Maximum Unit Zero pressure offset -2 0 2 mVFull-scale span (2)98 100 102 mVFull-scale span (3 psi and 5 psi “K” units only) (2)48 50 52 mVPressure non-linearity (3)– ±0.1 ±0.25 %FSSPressure hysteresis (3)– ±0.015 ±0.030 %FSS Repeatability – ±0.010 ±0.030 %FSSTemp. effect on span (4)– ±0.5 ±1.0 %FSSTemp. effect on offset (4)– ±0.5 ±1.0 %FSSTemp. effect on span (0 psi to 3 psi and 0 psi to 5 psi only) (4)– – ±2.0 %FSSTemp. effect on offset (0 psi to 3 psi and 0 psi to 5 psi only) (4)– – ±2.0 %FSS Thermal hysteresis (0 °C to 82 °C [32 °F to 180 °F]) – ±0.1 ±0.3 %FSSLong-term stability of offset and span (5)– ±0.1 ±0.3 %FSSResponse time (6)– 0.1 – msCommon mode voltage (voltage version “K”) (9)0.5 1.3 2.0 Vdc Input impedance (current version “L”) 2.0 4.5 8.0 k Ω Input impedance (voltage version “K”) 8.0 25 50 k Ω Output resistance 3.0 4.5 6.0 k ΩPressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm SeriesHoneywell • Sensing and Control 319U SERIES PERFORMANCE CHARACTERISTICS (1)Characteristic Minimum Typical Maximum Unit Zero pressure offset -7.5 1.0 7.5 mV/VFull-scale span (2)35 40 60 mV/VFull-scale span (3 psi and 5 psi only) (2)20 30 40 mV/VPressure non-linearity (3)– ±0.1 ±0.25 %FSSPressure hysteresis (3)– ±0.015 ±0.030 %FSS Repeatability – ±0.010 ±0.030 %FSSTemp. coefficient of resistance (10)(0 °C to 82 °C [32 °F to 180 °F]) 2700 3420 4500 ppm/°CTemp. coefficient of offset (10)(0 °C to 82 °C [32 °F to 180 °F]) – 30 – µV/V/°CTemp. coefficient of span (10)(0 °C to 82 °C [32 °F to 180 °F]) 360 720 1260 ppm/°C Thermal hysteresis (0 °C to 82 °C [32 °F to 180 °F]) – ±0.1 ±0.3 %FSSLong-term stability of offset and span (5)– ±0.1 ±0.3 %FSSResponse time (6)– ±0.1 – ms Input resistance 4.00 4.75 6.0 k Ω Output resistance 4.00 4.75 6.0 k Ω19C VACUUM GAGE COMPENSATED SERIES PERFORMANCE CHARACTERISTICS (1)Characteristic Minimum Typical Maximum Unit Zero pressure offset (at 0 psig) -2 0 2 mVFull-scale span (2)(0 psig to positive full-scale) 98 100 102 mVPressure non-linearity (3)– ±0.1 ±0.25 %FSSPressure hysteresis (3)– ±0.015 ±0.030 %FSS Repeatability – ±0.010 ±0.030 %FSSTemp. effect on span (4)– ±0.5 ±1.0 %FSSTemp. effect on offset (4)– ±0.5 ±1.0 %FSS Thermal hysteresis (0 °C to 82 °C [32 °F to 180 °F]) – ±0.1 ±0.3 %FSSLong-term stability of offset and span (5)– ±0.1 ±0.3 %FSSResponse time (6)– 0.1 – msCommon mode voltage (voltage version “K”) (9)0.5 1.3 2.0 Vdc Input impedance (current version “L”) 1.5 4.5 8.0 k Ω Input impedance (voltage version “K”) 8.0 25 50 k Ω Output resistance 3.0 4.5 6.0 k Ω19U VACUUM GAGE UNCOMPENSATED SERIES PERFORMANCE CHARACTERISTICS (1)Characteristic Minimum Typical Maximum Unit Zero pressure offset -7.5 1.0 7.5 mV/VFull-scale span (2)(0 psig to positive full-scale) 35 40 60 mV/VPressure non-linearity (3)– ±0.1 ±0.25 %FSSPressure hysteresis (3)– ±0.015 ±0.030 %FSS Repeatability – ±0.010 ±0.030 %FSSTemp. coefficient of resistance (10)(0 °C to 82 °C [32 °F to 180 °F]) 2700 3420 4500 ppm/°CTemp. coefficient of offset (10)(0 °C to 82 °C [32 °F to 180 °F]) – 30 – µV/V/°CTemp. coefficient of span (10)(0 °C to 82 °C [32 °F to 180 °F]) 360 720 1260 ppm/°C Thermal hysteresis (0 °C to 82 °C [32 °F to 180 °F]) – ±0.1 ±0.3 %FSSLong-term stability of offset and span (5)– ±0.1 ±0.3 %FSSResponse time (6)– ±0.1 – ms Input resistance 4.00 4.75 6.0 k Ω Output resistance 4.00 4.75 6.0 k ΩPressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm Series4 Honeywell • Sensing and ControlNOTES1. Reference conditions (unless otherwise noted): T A = 25 °C [77 °F]; 19C Supply V S = 10 Vdc ±0.01 Vdc orI S = 1.5 mA ±0.0015 mA; 19U Supply V S = 5 Vdc ±0.01 Vdc or I = 1.0 mA ±0.0015 mA2. Full-scale span (FSS) is the algebraic difference between the output voltage at full-scale pressure and the output at zeropressure. FSS is ratiometric to supply voltage.3. Pressure non-linearity is based on best-fit straight line from zero to the full-scale pressure. Pressure hysteresis is themaximum output difference at any point within the operation pressure range for increasing and decreasing pressure. 4. Maximum error band of the offset voltage or span over the compensated temperature range, relative to the 25 °C [77 °F]reading.5. Long-term stability over a six-month period.6. Response time for a 0 psi to FSS pressure step change, 10 % to 90 % rise time.9. Common mode voltage as measured from output to ground. For higher levels of common mode voltage, contact factory. 10. The error band resulting from a maximum deviation of a transducer’s output parameter (offset, span, or resistance) astemperature is varied 25 °C [77 °F] to any other temperature within the specified range (0 °C to 82 °C [32 °F to 180 °F]). This parameter is not 100 % tested and is guaranteed by process design and tested on a sample basis only. Temperature coefficient of span is evaluated using a constant current source.PHYSICAL DIMENSIONS, for reference only, mm [in]Package 1 (see note): Cell PackageNote: Non-concentricity effects at the diaphragm weld area may cause runout of up to ±0.006 in between the upper and lower portions of the sensor body. (It is recommended to use a counter bore to mate with this device to allow for this non-concentricity).Package 2: Flush Mount PackagePressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm SeriesHoneywell • Sensing and Control 5Package 3: Flush Mount with FlangePackage 4: Male 1/8-27 NPTPackage 5: Male 1/4-18 NPTPressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm Series6 Honeywell • Sensing and ControlPackage 6: Male 7/16 UNFPackage 7: Male 1/4 BSPPPackage 8: Euro Ring (See note)Note: Non-concentricity effects at the diaphragm weld area may cause runout of up to ±0.006 in between the upper and lower portions of the sensor body. (It is recommended to use a counter bore to mate with this device to allow for this non-concentricity).Pressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm SeriesHoneywell • Sensing and Control 7Package 9: VCR Gland (Female nut)ORDERING INFORMATIONPressure SensorsLow-Cost, Stainless Steel, Isolated Sensors19 mm SeriesSensing and Control/sensing Honeywell11 West Spring Street Freeport, Illinois 61032008132-1-EN IL50 GLO 1004 Printed in USACopyright 2004 Honeywell International Inc. All Rights Reserved.WARRANTY/REMEDYHoneywell warrants goods of its manufacture as being free of defective materials and faultyworkmanship. Contact your local sales office for warranty information. If warranted goods arereturned to Honeywell during the period of coverage, Honeywell will repair or replace without charge those items it finds defective. The foregoing is Buyer’s sole remedy and is in lieu of all other warranties, expressed or implied, including those of merchantability and fitness for a particular purpose.Specifications may change without notice. Theinformation we supply is believed to be accurate and reliable as of this printing. However, we assume no responsibility for its use.While we provide application assistance personally, through our literature and the Honeywell web site, it is up to the customer to determine the suitability of the product in the application.For application assistance, current specifications, or name of the nearest Authorized Distributor, contact a nearby sales office. Or call:1-800-537-6945 USA/Canada 1-815-235-6847 International FAX1-815-235-6545 USA INTERNET/sensing info.sc@。

MPU-9250 九轴产品中文说明书

4.9 运动数字处理引擎(DMP)...........................................................................................23

4.10 主 I2C 及 SPI 通信..........................................................................................................23

3.1 陀螺仪参数.........................................................................................................................8

3.2 加速度参数.........................................................................................................................9

4.7 16 位 ADC 三轴加速度信号输出及调理.......................................................................22

4.8 16 位 ADC 三轴磁力计信号输出及调理......................................................................22

MPU-9250 产品中文说明书

1.0 版

1 / 41

目录

1. 产品信息...................................................................................................................................4

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

UNISONIC TECHNOLOGIES CO., LTD9N90 Power MOSFET900V N-CHANNEL MOSFETDESCRIPTIONThe UTC 9N90 uses UTC’s advanced proprietary, planar stripe, DMOS technology to provide excellent R DS(ON), low gate charge and operation with low gate voltages. This device is suitable for use as a load switch or in PWM applications.FEATURES* R DS(ON) = 1.4Ω @V GS = 10 V* Ultra low gate charge ( typical 45 nC )* Low reverse transfer capacitance ( C RSS = typical 14 pF ) * Fast switching capability * Avalanche energy specified* Improved dv/dt capability, high ruggednessSYMBOL1.Gate*Pb-free plating product number: 9N90LORDERING INFORMATIONOrdering Number Pin AssignmentNormal Lead Free Plating Package 1 2 3Packing9N90-T3P-T 9N90L-T3P-T TO-3P G D STubeABSOLUTE MAXIMUM RATING (T C =25℃, unless otherwise specified)PARAMETER SYMBOL RATINGS UNITDrain-Source Voltage V DSS 900 V Gate-Source Voltage V GSS ±30 VContinuous Drain Current(T C = 25℃) I D 9.0 A Pulsed Drain Current (Note 1) I DM 36 A Avalanche Current (Note 1) I AR 9.0 ASingle Pulsed(Note 2)E AS 900Avalanche Energy Repetitive(Note 1) E AR 28mJPeak Diode Recovery dv/dt (Note 3) dv/dt 4.0 V/ns 280 WPower Dissipation Derate above 25℃ P D2.22 W/℃ Junction Temperature T J 125 ℃ Operating Temperature T OPR -20 ~ +85 ℃ Storage Temperature T STG -40 ~ +150 ℃ Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.THERMAL CHARACTERISTICSPARAMETER SYMBOL MIN TYP MAX UNITJunction-to- Ambient θJA 40 ℃/W Junction-to-Case θJC 0.45 ℃/WELECTRICAL CHARACTERISTICS (T J =25℃, unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT OFF CHARACTERISTICSDrain-Source Breakdown Voltage BV DSS V GS = 0 V, I D = 250 μA 900 V Drain-Source Leakage Current I DSS V DS = 900 V, V GS = 0 V 10 μAForward I GSSF V GS = 30 V, V DS = 0 V 100Gate-Body Leakage CurrentReverse I GSSRV GS = -30 V, V DS = 0 V -100nA Breakdown Voltage TemperatureCoefficientBV △DSS /△T J I D = 250 μA, Referenced to 25℃ 0.99 V/℃ON CHARACTERISTICS Gate Threshold Voltage V GS(TH) V DS = V GS , I D = 250 μA 3.0 5.0V Static Drain-Source On-Resistance R DS(ON) V GS = 10 V, I D = 4.5 A 1.12 1.4Ω DYNAMIC PARAMETERS Input Capacitance C ISS 2100 2730pFOutput Capacitance C OSS 175 230pFReverse Transfer Capacitance C RSSV DS = 25 V, V GS = 0 V,f = 1.0 MHz14 18 pF SWITCHING CHARACTERISTICS Turn-On Delay Time t D(ON) 50 110nsTurn-On Rise Time t R 120 250ns Turn-Off Delay Time t D(OFF) 100 210nsTurn-Off Fall Time t F V DD = 4500V, I D =11.0 A, R G = 25Ω (Note 4, 5) 75 160ns Total Gate Charge Q G 45 58 nCGate-Source Charge Q GS 13 nCGate-Drain Charge Q GDV DS = 720V, I D = 11.0A,V GS = 10 V (Note 4, 5)18 nCELECTRICAL CHARACTERISTICS(Cont.)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITDRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS Drain-Source Diode Forward Voltage V SD V GS = 0 V, I S = 9.0 A 1.4VMaximum Continuous Drain-SourceDiode Forward CurrentI S 9.0 AMaximum Pulsed Drain-Source DiodeForward CurrentI SM 36 AReverse Recovery Time t RR 550 ns Reverse Recovery Charge Q RR V GS = 0 V, I S = 9.0 A,d IF / dt = 100 A/μs (Note 4) 6.5 μCNote 1. Repetitive Rating : Pulse width limited by maximum junction temperature2. L = 21mH, I AS = 9.0A, V DD = 50V, R G = 25 Ω, Starting T J = 25℃3. I SD ≤ 9.0A, di/dt ≤ 200A/μs, V DD ≤ BV DSS , Starting T J = 25℃4. Pulse Test : Pulse width ≤ 300μs, Duty cycle ≤ 2%5. Essentially independent of operating temperatureTEST CIRCUITFig. 2A Switching Test Circuit Fig. 2B Switching WaveformsFig. 3A Gate Charge Test Circuit Fig. 3B Gate Charge WaveformFig. 4A Unclamped Inductive Switching Test Circuit Fig. 4B Unclamped Inductive Switching WaveformsTEST CIRCUIT(Cont.)TYPICAL CHARACTERISTICSTYPICAL CHARACTERISTICS(Cont.)D r a i n -S o u r c e B r e a k d o w n V o l t a g e , B V D S S (N o r m a l i z e d )D r a i n -S o u r c e O n -R e s i s t a n c e , R D S (O N ) (N o r m a l i z e d )D r a i n C u r r e n t , I D (A )D r a i n C u r r e n t , I D (A )。