2708中文资料

PM-DB2707中文资料

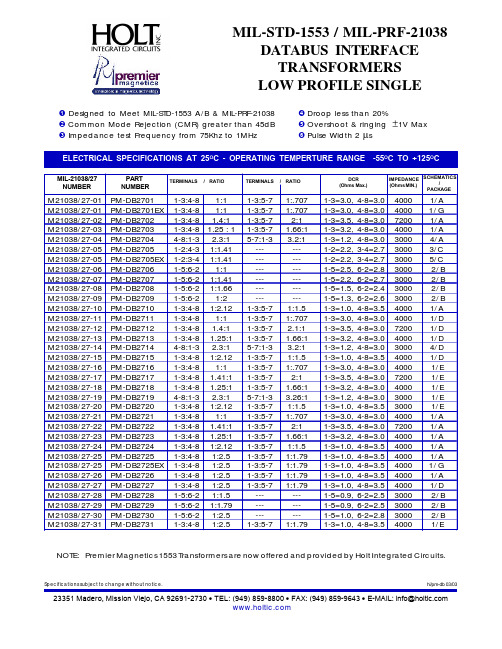

DCR (Ohms Max.)

IMPEDANCE SCHEMATICS

(Ohms MIN.)

/

PACKAGE

1-3=3.0, 4-8=3.0 4000 1/M

1-3=3.5, 4-8=3.0 7200 1/M

1-3=3.2, 4-8=3.0 4000 1/M

1-3=1.0, 4-8=3.5 4000 1/M

1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 4-8:1-3 1-2:4-3 1-2:3-4 1-5:6-2 1-5:6-2 1-5:6-2 1-5:6-2 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 4-8:1-3 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 4-8:1-3 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-5:6-2 1-5:6-2 1-5:6-2 1-3:4-8

TERMINALS / RATIO

1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8

1:1 1.4:1 1.25:1 1:2.12 1:2.5

TERMINALS / RATIO

1-3:5-7 1-3:5-7 1-3:5-7 1-3:5-7 1-3:5-7

1:.707 2:1

1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8 1-3:4-8

1:1 1.4:1 1.25:1 1:2.12 1:2.5

TERMINALS / RATIO

1-3:5-7 1-3:5-7 1-3:5-7 1-3:5-7 1-3:5-7

口译技巧5:数字口译资料

8,669,000 visitors

436.75万名新生

4,367,500 newcomers

数字的记录

快速精准的数字笔记对于interpreter在遇到 数字大量密集出现的情况下至关重要。

介绍三种常见数字记录方法: 1、缩略语记录法 2、填空记录法 3、分节号记录法

1、缩略语记录法

听到什么,记下什么 如:九亿五千三百二十万八千

汉语数字分段法:

第一段位

个

十

第二段位

万

十万

第三段位

亿

十亿

第四段位

兆(万亿)

百 百万 百亿

千 千万 千亿

英语数字分段法:

第一段位

One

第二段位

Thousand

第三段位

Million

第四段位

Billion

第五段位

Trillion

Ten

Ten thousand Ten million Ten billion

记作“9亿5千3百20万8千”, 或“9亿5320万8000” 再如:seventy-five million eight hundred and sixty-four thousand two hundred and fifteen 记作75m864t215

1、缩略语记录法

优点:直接,听、记时不会造成障碍。 缺点:仅仅记下了数字,没有做任何转换,

thirty six million seven hundred twenty-four thousand six hundred and thirty-one

口译的步骤如下: 1.在笔记上记下:36,724,631 2.从右向左按汉语记数方式没四位一划:

3672/4631 3.最后,读出汉语数字: 三千六百七十二万

餐厅英语类 中文菜单翻译(二十七)

美联英语提供:中文菜单翻译(二十七)分享一个免费试听课,名额有限,碰碰运气吧/test/xingzuo.html?tid=16-73675-0 2677. 墨西哥冰咖啡Iced Mexican Coffee2678. 瑞士冰咖啡Iced Swiss Coffee2679. 巴西咖啡Brazil Coffee2680. 皇家咖啡Royal Coffee2681. 君度咖啡Cointreau Coffee2682. 爱尔咖啡Irish Coffee2683. 生姜咖啡Ginger Juice Coffee2684. 贵妇人咖啡Dame Coffee2685. 椰香咖啡Coconut Coffee2686. 墨西哥日落咖啡Mexico Ice Coffee茶(Tea)2687. 绿茶Green T ea2688. 太平猴魁T aiping Houkui Tea (Green Tea) 2689. 西湖龙井Xihu Longjing Tea (Green Tea)2690. 信阳毛尖Xinyang Maojian T ea (Green T ea) 2691. 碧螺春Biluochun Tea (Green Tea)2692. 毛尖茶Maojian T ea (Green Tea)2693. 日本煎茶Japanese Green Tea2694. 大红袍Dahongpao Tea(Wuyi Mountain Rock Tea) 2695. 安溪铁观音Anxi Tieguanyin T ea (Oolong T ea)2696. 台湾阿里山乌龙Taiwan Alishan Oolong Tea 2697. 台湾冻顶乌龙T aiwan Dongding Oolong Tea 2698. 台湾金萱乌龙T aiwan Jinxuan Oolong Tea 2699. 台湾人参乌龙T aiwan Ginsen Oolong Tea 2700. 台湾桂花乌龙T aiwan Cassia Oolong Tea 2701. 君山银针Junshan Silver Needle Tea 2702. 大白毫White Milli- Silver Needle Tea 2703. 茉莉花茶Jasmine Tea2704. 茉莉大白毫Jasmine Silver Needle Tea 2705. 牡丹绣球Peony Jasmine T ea2706. 普洱Pu 'er Tea2707. 陈年普洱Aged Pu 'er Tea2708. 陈年普洱(31年)31-Year Pu 'er Tea 2709. 红茶Black Tea2710. 祁门红茶Keemun Black Tea 2711. 立顿红茶Lipton Black Tea2712. 大吉岭茶Darjeeling Tea2713. 伯爵茶Earl Grey T ea2714. 薄荷锡兰茶Mint T ea2715. 绿毛峰Lǜmaofeng Tea2716. 八宝茶Assorted Chinese Herbal Tea 2717. 薰衣草茶Lavender Tea2718. 意大利桔茶Italian Orange Tea2719. 俄罗斯红茶Russian Black Tea2720. 梅子红茶Greengage Black Tea2721. 菊花茶Chrysanthemum Tea茶饮料(Tea Drinks)2722. 冰茶Iced Tea2723. 冰红(绿)茶Iced Black Tea / Iced Green Tea 2724. 冰奶茶Iced Milk Tea2725. 乌龙茶(无糖型) Oolong Tea (Sugar Free) 2726. 港式奶茶Hot Tea, HK Style2727. 巧克力奶茶Chocolate Milk Tea2728. 冰巧克力奶茶Iced Chocolate Milk Tea 2729. 草莓奶茶Strawberry Milk Tea 2730. 花生奶茶Peanut Milk Tea2731. 哈密瓜奶茶Hami Melon Milk Tea 2732. 椰香奶茶Coconut Milk Tea2733. 芋香奶茶T aro Milk Tea2734. 热柠檬茶Hot Lemon T ea2735. 冰柠檬茶Iced Lemon T ea2736. 菠萝果茶Pineapple Tea2737. 菠萝冰茶Iced Pineapple Tea 2738. 黑莓冰茶Iced Blackberry Tea2739. 草莓冰茶Iced Strawberry Tea 2740. 蓝莓冰茶Iced Blueberry Tea 2741. 芒果冰茶Iced Mango Tea 2742. 蜜桃冰茶Iced Peach Tea 2743. 香蕉冰茶Iced Banana Tea 2744. 奇异果冰茶Iced Kiwi Tea果蔬汁(Juice)2745. 百香果汁Passion Fruit Juice 2746. 冰果汁Chilled Juice 2747. 菠萝汁Pineapple Juice2748. 苹果汁Apple Juice2749. 橙汁Orange Juice2750. 纯木瓜汁Papaya Juice2751. 凤梨木瓜汁Papaya and Pineapple Juice 2752. 哈蜜瓜汁Cantaloupe Juice2753. 红莓汁Cranberry Juice2754. 火龙果汁Dragonfruit Juice2755. 苦柠檬水Bitter Lemon Juice2756. 西瓜汁Watermelon Juice2757. 葡萄汁Grape Juice2758. 酸枣汁Wild Jujube Juice2759. 西柚汁/蜜柚汁(冷/热) Grapefruit Juice(Cold / Hot) 2760. 时令果汁Seasonal Fruit Juice2761. 西柠蜜瓜汁Melon and Lemon Juice2762. 椰汁Coconut Juice2763. 草莓果茶Strawberry Juice2764. 蓝莓果茶Blueberry Juice2765. 蜜桃果茶Peach Juice2766. 汇源梨汁Huiyuan Pear Juice2767. 汇源桃汁Huiyuan Peach Juice2768. 汇源橙汁Huiyuan Orange Juice2769. 新奇士橙汁Sunkist Orange Juice2770. 新奇士柠檬汁Sunkist Lemon Juice2771. 鲜榨果汁Fresh Juice2772. 鲜榨青柠汁Fresh Lemon Juice2773. 鲜榨蔬菜汁Fresh Vegetable Juice2774. 番茄汁Tomato Juice2775. 胡萝卜橙子汁Carrot and Orange Juice 2776. 胡萝卜芹菜汁Celery and Carrot Juice 2777. 山楂胡萝卜汁Hawthorn and Carrot Juice 2778. 黄瓜汁Fresh Cucumber Juice分享一个免费试听课,名额有限,碰碰运气吧/test/xingzuo.html?tid=16-73675-0。

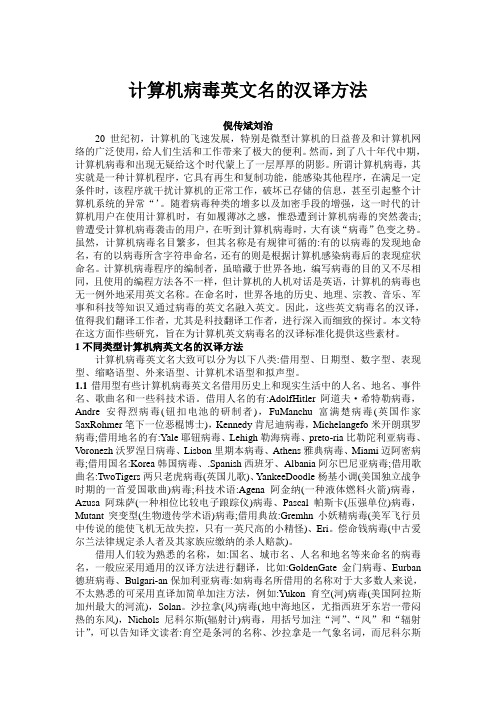

计算机病毒英文名的汉译方法

计算机病毒英文名的汉译方法倪传斌刘治20世纪初,计算机的飞速发展,特别是微型计算机的日益普及和计算机网络的广泛使用,给人们生活和工作带来了极大的便利。

然而,到了八十年代中期,计算机病毒和出现无疑给这个时代蒙上了一层厚厚的阴影。

所谓计算机病毒,其实就是一种计算机程序,它具有再生和复制功能,能感染其他程序,在满足一定条件时,该程序就干扰计算机的正常工作,破坏已存储的信息,甚至引起整个计算机系统的异常“’。

随着病毒种类的增多以及加密手段的增强,这一时代的计算机用户在使用计算机时,有如履薄冰之感,惟恐遭到计算机病毒的突然袭击;曾遭受计算机病毒袭击的用户,在听到计算机病毒时,大有谈“病毒”色变之势。

虽然,计算机病毒名目繁多,但其名称是有规律可循的:有的以病毒的发现地命名,有的以病毒所含字符串命名,还有的则是根据计算机感染病毒后的表现症状命名。

计算机病毒程序的编制者,虽暗藏于世界各地,编写病毒的目的又不尽相同,且使用的编程方法各不一样,但计算机的人机对话是英语,计算机的病毒也无一例外地采用英文名称。

在命名时,世界各地的历史、地理、宗教、音乐、军事和科技等知识又通过病毒的英文名融入英文。

因此,这些英文病毒名的汉译,值得我们翻译工作者,尤其是科技翻译工作者,进行深入而细致的探讨。

本文特在这方面作些研究,旨在为计算机英文病毒名的汉译标准化提供这些素材。

1不同类型计算机病英文名的汉译方法计算机病毒英文名大致可以分为以下八类:借用型、日期型、数字型、表现型、缩略语型、外来语型、计算机术语型和拟声型。

1.1借用型有些计算机病毒英文名借用历史上和现实生活中的人名、地名、事件名、歌曲名和一些科技术语。

借用人名的有:AdolfHitler阿道夫·希特勒病毒,Andre安得烈病毒(钮扣电池的研制者),FuManchu富满楚病毒(英国作家SaxRohmer笔下一位恶棍博士),Kennedy肯尼迪病毒,Michelangefo米开朗琪罗病毒;借用地名的有:Yale耶钮病毒、Lehigh勒海病毒、preto-ria比勒陀利亚病毒、V oronezh沃罗涅日病毒、Lisbon里期本病毒、Athens雅典病毒、Miami迈阿密病毒;借用国名:Korea韩国病毒、.Spanish西班牙、Albania阿尔巴尼亚病毒;借用歌曲名:TwoTigers两只老虎病毒(英国儿歌)、YankeeDoodle杨基小调(美国独立战争时期的一首爱国歌曲)病毒;科技术语:Agena阿金纳(一种液体燃料火箭)病毒,Azusa阿珠萨(一种相位比较电子踉踪仪)病毒、Pascal帕斯卡(压强单位)病毒,Mutant突变型(生物遗传学术语)病毒;借用典故:Gremhn小妖精病毒(美军飞行员中传说的能使飞机无故失控,只有一英尺高的小精怪)、Eri。

UC1708中文资料

BLOCK DIAGRAM• 3.0A Peak Current Totem Pole Output• 5 to 35V Operation •25ns Rise and Fall Times •25ns Propagation Delays •Thermal Shutdown and Under-Voltage Protection•High-Speed, Power MOSFET Compatible•Efficient High Frequency Operation •Low Cross-Conduction Current Spike •Enable and Shutdown Functions •Wide Input Voltage Range •ESD Protection to 2kVThe UC1708 family of power drivers is made with a high-speed, high-voltage, Schottky process to interface control functions and high-power switching devices – particularly power MOSFETs. Operating over a 5 to 35 volt supply range, these devices contain two independent channels.The A and B inputs are compatible with TTL and CMOS logic families,but can withstand input voltages as high as V IN . Each output can source or sink up to 3A as long as power dissipation limits are not exceeded.Although each output can be activated independently with its own inputs,they can be forced low in common through the action of either a digital high signal at the Shutdown terminal or by forcing the Enable terminal low. The Shutdown terminal will only force the outputs low, it will not ef-fect the behavior of the rest of the device. The Enable terminal effectively places the device in under-voltage lockout, reducing power consumption by as much as 90%. During under-voltage and disable (Enable terminal forced low) conditions, the outputs are held in a self-biasing, low-voltage,state.The UC3708 and UC2708 are available in plastic 8-pin MINIDIP and 16-pin "bat-wing" DIP packages for commercial operation over a 0o C to +70o C temperature range and industrial temperature range of -25o C to +85o C respectively. For operation over a -55o C to +125o C temperature range, the UC1708 is available in hermetically sealed 8-pin MINIDIP and 16 pin DIP packages. Surface mount devices are also available.UC2708UC3708Dual Non-Inverting Power DriverNote: Shutdown feature available only in JE , NE or DW packages.UDG-92024-1FEATURESDESCRIPTIONCONNECTION DIAGRAMSSupply Voltage V IN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35V Output Current (Each Output, Source or Sink)Steady-State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5A Peak Transient . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3A Ouput Voltage . . . . . . . . . . . . . . . . . . . . . . . -0.3 to (V IN + 0.3)V Enable and Shutdown Inputs . . . . . . . . . . . . . . . . . -0.3 to 6.2V A and B Inputs . . . . . . . . . . . . . . . . . . . . . . . -0.3 to (V IN + 0.3)V Operating Junction Temperature (Note 2). . . . . . . . . . . . 150°C Storage Temperature Range . . . . . . . . . . . . . . . . -65° to 150°C Lead Temperature (Soldering, 10 Seconds). . . . . . . . . . 300°CABSOLUTE MAXIMUM RATINGS (Note 1)NOTE 1: All voltages are with respect to Logic Gnd pin. All cur-rents are positive into, negative out of, device terminals.NOTE 2: Consult Unitrode Integrated Circuits databook for information regarding thermal specifications and limitations of packages.PARAMETERTEST CONDITIONSMINTYP MAX UNITS V IN Supply CurrentOutputsLow 1826mA Outputs High 1418mA Enable = 0V14mA A, B and Shutdown Inputs Low Level0.8V A, B and Shutdown Inputs High Level2.0V A, B Input Current Low V A,B = 0.4V -1-0.6mA A, B Input Current HighV A,B = 2.4V -20050µA A, B Input Leakage Current High V A,B = 35.3V 200µA Shutdown Input Current Low V SHUTDOWN = 0.4V 20100µA Shutdown Input Current HighV SHUTDOWN = 2.4V 170500µA V SHUTDOWN = 6.2V0.61.5mAELECTRICAL CHARACTERISTICS: Unless otherwise stated, V IN =10V to 35V, and these specifications apply for:–55o C<T A <125o C for the UC1708, –25o C<T A <+85o C for the UC2708, and 0o C<T A <70o C for the UC3708. T A = T J.DIL-8 (Top View)J Or N PackageNote: In JE package Pin 4 is logic ground. Pins 5, 12,and 13 are N/C.DIL-16 (Top View)JE or NE PackageSOIC-16 (Top View)DW PackageELECTRICAL CHARACTERISTICS (cont.): Unless otherwise stated, V IN = 10V to 35V, and these specifications apply for: –55o C<T A<125o C for the UC1708, –25o C<T A<+85o C for the UC2708, and 0o C<T A<70o C for the UC3708. T A = T J.PARAMETER TEST CONDITIONS MIN TYP MAX UNITS Enable Input Current Low V ENABLE = 0V-600-460200µA Enable Input Current High V ENABLE = 6.2V200µA Enable Threshold Rising 2.8 3.6V Enable Threshold Falling 1.0 2.4 3.4V Output High Sat., V IN - V OUT I OUT = -50mA 2.0VI OUT = -500mA 2.5VOutput Low Sat., V OUT I OUT = 50mA0.5VI OUT = 500mA 2.5VThermal Shutdown155°CSWITCHING CHARACTERISTICS (Figure 1)(V IN = 20V, delays measured to 10% output change.)PARAMETER TEST CONDITIONS MIN TYP MAX UNITS From A,B Input to Output:Rise Time Delay (TPLH)CL = 0pF2540nsCL = 1000pF (Note 3)2540nsCL = 2200pF3045ns 10% to 90% Rise (TTLH)CL = 0pF5575nsCL = 1000pF (Note 3)2550nsCL = 2200pF4055ns Fall Time Delay (TPHL)CL = 0pF2540nsCL = 1000pF (Note 3)2545nsCL = 2200pF3550ns 90% to 10% Fall (TTHL)CL = 0pF1520nsCL = 1000pF (Note 3)2545nsCL = 2200pF4055ns From Shutdown Input to OutputRise Time Delay (TPLH)CL = 0pF2575nsCL = 1000pF (Note 3)3075nsCL = 2200pF3575ns 10% to 90% Rise (TTLH)CL = 0pf5075nsCL = 1000pF (Note 3)2550nsCL = 2200pF4055ns Fall Time Delay (TPHL)CL = 0pF2545nsCL = 1000pF (Note 3)3050nsCL = 2200pF3555ns 90% to 10% Fall (TTHL)CL = 0pF2520nsCL = 1000pF (Note 3)2545nsCL = 2200pF4055ns Total Supply Current F = 200kHz, 50% duty cycle, both channels; CL = 0pF2325mAF = 200kHz, 50% duty cycle, both channels; CL = 2200pF3845mA NOTE 3: These parameters, specified at 1000pF, although guaranteed over recommended operating conditions, are not tested in production.Note: Shutdown feature available only in JE, NE or DW Packages.UNITRODE CORPORA TION7 CONTINENT AL BL VD. • MERRIMACK, NH 03054TEL. (603) 424-2410 • FAX (603) 424-3460Figure 2: Equivalent Input Circuits4.3V 0V20V0VINPUT90%50%10%OUTPUT90%10%50%TP TP TT TT LHLHHLHLFigure 1: AC T est Circuit and Switching Time WaveformsUDG-92025UDG-92026IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

CU 3X2安装和使用说明书

中文 (C N )277中文 (CN) 安装和使用说明书目录页1. 本文献中所用符号2. 产品说明CU 3X2是一种灵活的控制装置,可控制并监视多达6个水泵。

在以下章节中将对两个型号进行说明:•CU 352– 供水和增压系统– 加热及空调系统。

•CU 362– 污水处理和排水应用。

下文中的两个型号特指CU 3X2。

1.本文献中所用符号2772.产品说明2772.1指示灯2782.2端子2782.3潜在爆炸性环境2783.标识2793.1型号说明2794.安装2794.1安装场地2804.2防护等级2804.3端子2804.4电缆2805.机械安装2806.电磁兼容问题 --正确的安装方式2816.1内部 GENIbus 总线接头2826.2Fieldbus 通信接口模块2826.3CIM 模块的安装2827.启动2848.技术资料2849.电气数据2849.1电源电压2849.2功耗2849.3断路器2849.4备用保险丝2849.5短路保护2849.6数字输入2849.7模拟输入2849.8数字输出 (继电器输出)2849.9导线2849.10USB 端口2849.11备用电池 (UPS)2859.12终端组28510.输入输出概览表28611.维护和服务28712.维护28713.更换CU 3X228713.1更换 CIM 模块28714.尺寸规格28715.回收处理287警告装机前,先仔细阅读本安装操作手册。

安装和运行必须遵守当地规章制度并符合公认的良好操作习惯。

警告不执行这些安全须知可能会引起人身伤害。

小心不执行这些安全须知可能会导致故障发生或设备损坏。

注意可以使工作简化和保证安全的注意事项或须知。

中文 (CN)278图 1CU 3X2举例*部分帮助文本适用于整个显示屏,其余文本适用于显示屏的部分系列。

2.1 指示灯CU 3X2具有1个绿色指示灯和1个红色指示灯。

绿色指示灯在电源接通后亮起。

UPC2711T中文资料

Gain, GS (dB)

Noise Figure, NF (dB) Gain, GS (dB)

* UPC2708T only

Circuit Current, ICC (mA)

CIRCUIT CURRENT vs. TEMPERATURE

40 VCC = 5.0 V

35

30 UPC2708T

25

20

UPC2708T POWER vs. FREQUENCY

25 VCC = 5.0 V

20 X

15 X

10

P1dB 5

X PSAT

0

-5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5

Frequency, f (GHz) X: Typical SSB Third Order intercept Point

元器件交易网

3 GHz SILICON MMIC UPC2708T WIDE-BAND AMPLIFIER UPC2711T

FEATURES

• WIDE FREQUENCY RESPONSE: 3 GHz • HIGH GAIN: 15 dB (UPC2708T) • SATURATED OUTPUT POWER: +10 dBm (UPC2708T) • INTERNAL CURRENT REGULATION MINIMIZES GAIN

5

4 0

0.5

1.0 1.5 2.0 2.5 3.0

Frequency, f (GHz)

Output Power, POUT (dBm)

Output Power, Pout (dBm)

UPC2711T OUTPUT POWER vs. INPUT POWER AND TEMPERATURE

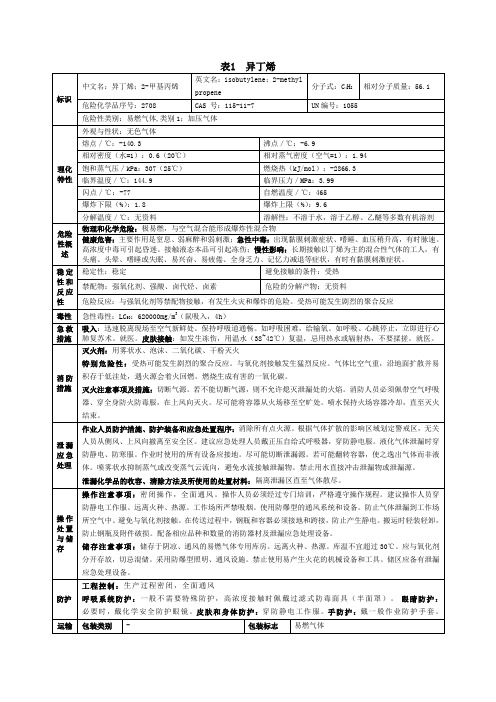

异丁烯msds

灭火剂:用雾状水、泡沫、二氧化碳、干粉灭火

特别危险性:受热可能发生剧烈的聚合反应。与氧化剂接触发生猛烈反应。气体比空气重,沿地面扩散并易积存于低洼处,遇火源会着火回燃。燃烧生成有害的一氧化碳。

灭火注意事项及措施:切断气源。若不能切断气源,则不允许熄灭泄漏处的火焰。消防人员必须佩带空气呼吸器、穿全身防火防毒服,在上风向灭火。尽可能将容器从火场移至空旷处。喷水保持火场容器冷却,直至灭火结束。

储存注意事项:储存于阴凉、通风的易燃气体专用库房。远离火种、热源。库温不宜超过30℃。应与氧化剂分开存放,切忌混储。采用防爆型照明、通风设施。禁止使用易产生火花的机械设备和工具。储区应备有泄漏应急处理设备。

防护

工程控制:生产过程密闭,全面通风

呼吸系统防护:一般不需要特殊防护,高浓度接触时佩戴过滤式防毒面具(半面罩)。眼睛防护:必要时,戴化学安全防护眼镜。皮肤和身体防护:穿防静电工作服。手防护:戴一般作业防护手套。

溶解性:不溶于水,溶于乙醇、乙醚等多数有机溶剂

危险性概述

物理和化学危险:极易燃,与空气混合能形成爆炸性混合物

健康危害:主要作用是窒息、弱麻醉和弱刺激;急性中毒:出现黏膜刺激症状、嗜睡、血压稍升高,有时脉速。高浓度中毒可引起昏迷。接触液态本品可引起冻伤;慢性影响:长期接触以丁烯为主的混合性气体的工人,有头痛、头晕、嗜睡或失眠、易兴奋、易疲倦、全身乏力、记忆力减退等症状,有时有黏膜刺激症状。

表1异丁烯

标识

中文名:异丁烯;2-甲基丙烯

英文名:isobutylene;2-methyl propene

分子式:C4H8

相对分子质量:56.1

危险化学品序号:2708

CAS号:115-11-7

UN编号:1055

74680-XXXX中文资料

FEATURES AND SPECIFICATIONS2.00 by 2.25mm (.079 by .089") Pitch 5-Row, 6-Row and 8-Row VHDM-HSD ™Module-to-BackplaneConnector SystemFeatures and Benefitss Up to 5.0 Gbps bandwidth per signal pair enables state-of-the-art system design and performance s2.00 by 2.25mm (.079 by .089”) pitch provides real signal density of 10 differential pairs for 5-row and 6-row and 15 differential pairs for 8-row per centimeter (25 and 38 pairs respectively per inch) sMinimum distance between daughtercards:– 5-row system offers 15.00mm (.591")– 6-row system offers 18.00mm (.709")– 8-row system offers 22.00mm (.866")sGround planes between signal columns provide tightly controlled impedance for rise times down to 50 picoseconds (10-90%). This ensures very low cross talk between signals within and between columnssGround pins are in the same grid as signal pins, allowing wider channels for PCB routing and traces up to 0.25mm (.010”) wides6-row or 8-row VHDM-HSD wafers can be applied to the same stiffener as standard VHDM ® 6-row or 8-row wafers. The combination of VHDM and VHDM-HSD wafers, grouped together in the same stiffener, provides cost effective solutions to different performance parametersThe Very High Density Metric High Speed Differential (VHDM-HSD) connector system has been expanded to include 5-row, 6-row and 8-row daughtercard and backplane modules. VHDM-HSD is designed for differential-pair architecture applications that require very high interconnect density and signal integrity in a single-ended configuration.The same great modularity features and components ofVHDM are provided in the VHDM-HSD. The 5-row and 6-row systems feature 2 signal pairs per column and the8-row system features 3 signal pairs per column inincrements of 10 and 25 columns. All circuits areutilized as signal circuits without the need to use some asground circuits.The daughtercard connector consists of a metal stiffener just as with the VHDM system. The system combines the signal wafers, power modules and guidance modules into one continuous connector that can be ordered as a single specific part number. The card pitch of the VHDM-HSD 8-row system is the same as the standard VHDM 8-row system, allowing both signal wafer types for single ended and differential pair to be used together. Thismodularity and design flexibility allow engineers toincorporate both connector systems on the sameplatforms. The system is based on a 2.00mm (.079")pitch and includes vertical and right angle products thatcan be configured up to 2000 circuits. The maximumlength of a daughtercard connector on a single stiffeneris 300mm (12").The backplane connectors feature headers with open ends for continuous side-to-side stacking and headers with guide pins and polarizing keys on either end to aid in proper alignment of the mating daughtercard. The power modules occupy just a small width and hold sequentially matable pins that each manage 10.0 amps of current.Molex offers application tooling for pressing VHDM-HSD connectors into PCBs as separate modules or as complete assemblies. VHDM-HSD cable assemblies are also available for connecting backplane headers to high-performance cables.Note: VHDM and VHDM-HSD are trademarks or registered trademarks of Teradyne,Inc.元器件交易网FEATURES AND SPECIFICATIONS2.00 by 2.25mm (.079 by .089") Pitch 5-Row, 6-Row and 8-Row VHDM-HSD ™Module-to-Backplane Connector SystemPress Fit Right Angle ReceptacleApplicationsThe VHDM-HSD products are used in very high speed, short rise-time, high circuit count applications connecting daughtercards to the backplane:s Network Switches s Routerss Computer Serverss Telecommunication Equipment sInternetworking DevicesORDERING INFORMATIONDaughtercard AssemblyConfiguration 5-Row 6-Row 8-Row Signal wafers, power modules and guide modules sequentiallyassigned by application VHDM-HSD wafers74670-XXXX 74880-XXXX 74680-XXXX Combination of VHDM and VHDM-HSD wafers74686-XXXX 74886-XXXX74686-XXXXBackplane Header Signal Module Standard Loaded Pin Height 0.76µm (30µ”) Gold5-Row6-Row8-Row10-Column 25-Column 10-Column 25-Column 10-Column 25-Column Open Ended4.25mm (.167”)74695-100374695-250374979-100374979-250374649-100374649-25034.75mm (.187”)74695-100174695-250174979-100174979-250174649-100174649-25015.15mm (.203”)74695-100474695-250474979-100474979-250474649-100474649-25046.25mm (.266”)74695-100274695-250274979-100274979-250274649-100274649-2502Left Guide PinNo Polarizing Key 4.25mm (.167”)74696-100374696-2503––74650-100374650-25034.75mm (.187”)74696-100174696-2501––74650-100174650-25015.15mm (.203”)74696-100474696-2504––74650-100474650-25046.25mm (.266”)74696-100274696-2502––74650-100274650-2502Left Guide Pin“A” Polarizing Key 4.25mm (.167”)74696-101374696-2513––74650-101374650-25134.75mm (.187”)74696-101174696-2511––74650-101174650-25115.15mm (.203”)74696-101474696-2514––74650-101474650-25146.25mm (.266”)74696-101274696-2512––74650-101274650-2512Right Guide PinNo Polarizing Key 4.25mm (.167”)74697-100374697-2503––74651-100374651-25034.75mm (.187”)74697-100174697-2501––74651-100174651-25015.15mm (.203”)74697-100474697-2504––74651-100474651-25046.25mm (.266”)74697-100274697-2502––74651-100274651-2502Right Guide Pin“A” Polarizing Key 4.25mm (.167”)74697-101374697-2513––74651-101374651-25134.75mm (.187”)74697-101174697-2511––74651-101174651-25115.15mm (.203”)74697-101474697-2514––74651-101474651-25146.25mm (.266”)74697-101274697-2512––74651-101274651-2512Backplane Power and Guide Components5-Row and 6-Row 8-Row Power Module 74029-600074029-8000Keying Post 74069-001074069-0010Guide Pin74076-0001/000274076-0001/0002Americas Headquarters Lisle, Illinois 60532 U.S.A.1-800-78MOLEX amerinfo@ Far East North Headquarters Yamato, Kanagawa, Japan 81-462-65-2324feninfo@ Far East South Headquarters Jurong, Singapore 65-6-268-6868fesinfo@ European Headquarters Munich, Germany 49-89-413092-0eurinfo@ Corporate Headquarters 2222 Wellington Ct.Lisle, IL 60532 U.S.A.630-969-4550Visit our Web site at /product/backplan/hsd.htmlOrder No. USA-158 Rev. 2Printed in USA/2.5K/JI/JI/2003.03©2003, MolexNote: VHDM and VHDM-HSD are trademarks or registered trademarks of Teradyne,Inc.元器件交易网。

74ALVC16373资料

© 2005 Fairchild Semiconductor Corporation DS500687October 2001Revised May 200574ALVC16373 Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and Outputs74ALVC16373Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and OutputsGeneral DescriptionThe ALVC16373 contains sixteen non-inverting latches with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled. The flip-flops appear to be transparent to the data when the Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in a high impedance state.The 74ALVC16373 is designed for low voltage (1.1V to 3.6V) V CC applications with I/O compatibility up to 3.6V.The 74ALVC16373 is fabricated with an advanced CMOS technology to achieve high speed operation while maintain-ing low CMOS power dissipation.Featuress 1.1V to 3.6V V CC supply operation s 3.6V tolerant inputs and outputs s t PD (I n to O n )3.5 ns max for 3.0V to 3.6V V CC 3.9 ns max for 2.3V to 2.7V V CC 6.8 ns max for 1.65V to 1.95V V CCs Power-off high impedance inputs and outputs s Support live insertion and withdrawal (Note 1)s Uses patented noise/EMI reduction circuitry s Latchup conforms to JEDEC JED78s ESD performance:Human body model ! 2000V Machine model ! 200Vs Also packaged in plastic Fine-Pitch Ball Grid Array (FBGA) (Preliminary)Note 1: To ensure the high-impedance state during power up or power down, OE should be tied to V CC through a pull-up resistor; the minimum value of the resistor is determined by the current-sourcing capability of the driver.Ordering Code:Note 2: BGA package available in Tape and Reel only.Note 3: Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic SymbolOrder Number Package Number Package Description74ALVC16373GX (Note 2)BGA54A (Preliminary)54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL]74ALVC16373MTD (Note 3)MTD4848-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide 274A L V C 16373Connection DiagramsPin Assignment for TSSOPPin Assignment for FBGA(Top Thru View)Pin DescriptionsFBGA Pin AssignmentsTruth TablesH HIGH Voltage Level L LOW Voltage LevelX Immaterial (HIGH or LOW, inputs may not float)Z High ImpedanceO 0 Previous O 0 before HIGH-to-LOW of Latch EnablePin NamesDescriptionOE n Output Enable Input (Active LOW)LE n Latch Enable InputI 0–I 15Inputs O 0–O 15Outputs NCNo Connect123456A O 0NC OE 1LE 1NC I 0B O 2O 1NC NC I 1I 2C O 4O 3V CC V CC I 3I 4D O 6O 5GND GND I 5I 6E O 8O 7GND GND I 7I 8F O 10O 9GND GND I 9I 10G O 12O 11V CC V CC I 11I 12H O 14O 13NC NC I 13I 14JO 15NCOE 2LE 2NCI 15InputsOutputs LE 1OE 1I 0–I 7O 0–O 7X H X Z HL L L H L H H LL XO 0 InputsOutputs LE 2OE 2I 8–I 15O 8–O 15X H X Z H L L L H L H H LLX O 074ALVC16373Functional DescriptionThe 74ALVC16373 contains sixteen edge D-type latches with 3-STATE outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LE n ) input is HIGH, data on the I n enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each timeits I input changes. When LE n is LOW, the latches store information that was present on the I inputs a setup time preceding the HIGH-to-LOW transition on LE n . The 3-STATE outputs are controlled by the Output Enable (OE n ) input. When OE n is LOW the standard outputs are in the 2-state mode. When OE n is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.Logic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays. 474A L V C 16373Absolute Maximum Ratings (Note 4)Recommended Operating Conditions (Note 6)Note 4: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Rat-ings. The “Recommended Operating Conditions ” table will define the condi-tions for actual device operation.Note 5: I O Absolute Maximum Rating must be observed.Note 6: Floating or unused inputs must be held HIGH or LOW.DC Electrical CharacteristicsSupply Voltage (V CC ) 0.5V to 4.6V DC Input Voltage (V I ) 0.5V to 4.6V Output Voltage (V O ) (Note 5) 0.5V to V CC 0.5VDC Input Diode Current (I IK ) V I 0V50 mA DC Output Diode Current (I OK )V O 0V50 mA DC Output Source/Sink Current (I OH /I OL )r 50 mA DC V CC or GND Current per Supply Pin (I CC or GND)r 100 mAStorage Temperature Range (T STG )65q C to 150q CPower SupplyOperating 1.65V to 3.6V Input Voltage (V I )0V to V CC Output Voltage (V O )0V to V CCFree Air Operating Temperature (T A ) 40q C to 85q CMinimum Input Edge Rate ('t/'V)V IN 0.8V to 2.0V, V CC 3.0V10 ns/VSymbol ParameterConditionsV CC Min MaxUnits(V)V IHHIGH Level Input Voltage1.65 -1.950.65 x V CCV2.3 - 2.7 1.72.7 -3.62.0V ILLOW Level Input Voltage1.65 -1.950.35 x V CCV 2.3 - 2.70.72.7 - 3.60.8V OHHIGH Level Output VoltageI OH 100 P A 1.65 - 3.6V CC - 0.2VI OH 4 mA 1.65 1.2I OH 6 mA 2.32I OH 12 mA2.3 1.72.7 2.23.02.4I OH 24 mA3.02V OLLOW Level Output VoltageI OL 100 P A 1.65 - 3.60.2V I OL 4 mA 1.650.45I OL 6 mA 2.30.4I OL 12mA 2.30.72.70.4I OL 24 mA30.55I I Input Leakage Current 0 d V I d 3.6V 3.6r 5.0P A I OZ 3-STATE Output Leakage 0 d V O d 3.6V3.6r 10P A I CC Quiescent Supply Current V I V CC or GND, I O 0 3.640P A 'I CCIncrease in I CC per InputV IH V CC 0.6V3 -3.6750P A74ALVC16373AC Electrical CharacteristicsCapacitanceSymbolParameterT A 40q C to 85q C, R L 500:UnitsC L 50 pFC L 30 pFV CC 3.3V r 0.3V V CC 2.7V V CC 2.5V r 0.2VV CC 1.8V r 0.15V MinMax Min Max Min Max Min Max t PHL , t PLH Propagation Delay 1.3 3.5 1.5 3.9 1.0 3.4 1.5 6.8ns Bus to Bus t PHL , t PLH Propagation Delay 1.3 3.5 1.5 4.4 1.0 3.9 1.57.8ns LE to Bust PZL , t PZH Output Enable Time 1.3 4.0 1.5 5.1 1.0 4.6 1.59.2ns t PLZ , t PHZOutput Disable Time1.34.01.54.31.03.81.56.8ns Symbol ParameterConditionsT A 25q C Units V CC Typical C IN Input Capacitance V I 0V or V CC 3.36pF C OUT Output CapacitanceV I 0V or V CC3.37pF C PDPower Dissipation Capacitance Outputs Enabled f 10 MHz, C L 50 pF3.320pF2.520 674A L V C 16373AC Loading and WaveformsFIGURE 1. AC Test CircuitTABLE 1. Values for Figure 1TABLE 2. Variable Matrix(Input Characteristics: f 1MHz; t r t f 2ns; Z 0 50:)FIGURE 2. Waveform for Inverting andNon-Inverting FunctionsFIGURE 3. 3-STATE Output HIGH Enable andDisable Times for Low Voltage LogicFIGURE 4. 3-STATE Output LOW Enable and Disable Times for Low Voltage LogicFIGURE 5. Propagation Delay, Pulse Width andt rec WaveformsFIGURE 6. Setup Time, Hold Time and Recovery Time for Low Voltage LogicTEST SWITCH t PLH , t PHL Open t PZL , t PLZ V L t PZH , t PHZGNDSymbol V CC3.3V r 0.3V2.7V 2.5V r 0.2V 1.8V r 0.15VV mi 1.5V 1.5V V CC /2V CC /2V mo 1.5V 1.5V V CC /2V CC /2V X V OL 0.3V V OL 0.3V V OL 0.15V V OL 0.15V V Y V OH 0.3VV OH 0.3VV OH 0.15V V OH 0.15V V L6V6VV CC *2V CC *274ALVC16373 Physical Dimensionsinches (millimeters) unless otherwise noted54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm WidePackage Number BGA54A(Preliminary)874A L V C 16373 L o w V o l t a g e 16-B i t T r a n s p a r e n t L a t c h w i t h 3.6V T o l e r a n t I n p u t s a n d O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm WidePackage Number MTD48Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

1909278中文资料

Extract from the onlinecatalogFKCT 2,5/14-STOrder No.: 1909333The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1909333Plug component, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0 mm, no. of positions: 14, type of connection: Spring-cage connectionhttp://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsPitch 5 mmDimension a35 mmNumber of positions8Technical dataInsulating material group IRated surge voltage (III/3) 4 kV Rated surge voltage (III/2) 4 kV Rated surge voltage (II/2) 4 kV Rated voltage (III/2)320 V Rated voltage (II/2)630 V Connection in acc. with standard EN-VDE Nominal current I N12 A Nominal voltage U N250 V Nominal cross section 2.5 mm2 Maximum load current12 A Insulating material PA Inflammability class acc. to UL 94V0 Internal cylindrical gage A2 Stripping length10 mmConnection dataConductor cross section solid min.0.2 mm2 Conductor cross section solid max. 2.5 mm2 Conductor cross section stranded min.0.2 mm2 Conductor cross section stranded max. 2.5 mm2 Conductor cross section stranded, with ferrule0.25 mm2 without plastic sleeve min.Conductor cross section stranded, with ferrule2.5 mm2 without plastic sleeve max.Conductor cross section stranded, with ferrule0.25 mm2 with plastic sleeve min.Conductor cross section stranded, with ferrule2.5 mm2 with plastic sleeve max.Conductor cross section AWG/kcmil min.24 Conductor cross section AWG/kcmil max122 conductors with same cross section, stranded,0.5 mm2 TWIN ferrules with plastic sleeve, min.2 conductors with same cross section, stranded,1.5 mm2 TWIN ferrules with plastic sleeve, max.Certificates / ApprovalsApproval logoCSANominal voltage U N300 VNominal current I N10 AAWG/kcmil24-12CULNominal voltage U N300 VNominal current I N10 AAWG/kcmil26-12ULNominal voltage U N300 VNominal current I N10 AAWG/kcmil26-12Certification CB, CSA, CUL, GOST, UL, VDE-PZIAccessoriesItem Designation DescriptionAssembly1876880STZ 8-FKC-5,08Strain relief for snapping into the latching chambers of the plugcomponents, 8-pos.1876877STZ 4-FKC-5,08Strain relief for snapping into the latching chambers of the plugs,4-pos.Marking0804183SK 5/3,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 12 identicaldecades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for120 terminal blocksPlug/Adapter1734634CP-MSTB Coding profile, is inserted into the slot on the plug or invertedheader, red insulating material0201689MPS-IH BU Insulating sleeve (blue), for MPS metal part to be orderedseparately (0201744)0201702MPS-IH GN Insulating sleeve (green), for MPS metal part to be orderedseparately (0201744)0201676MPS-IH RD Insulating sleeve (red), for MPS metal part to be orderedseparately (0201744)0201663MPS-IH WH Insulating sleeve (white), for MPS metal part to be orderedseparately (0201744)0201744MPS-MT Test plug, consisting of: Metal part for 2.3 mm diameter sockethole0201647RPS Reducing plug, for transition from 4 mm diameter test plug socket,insulation: grayTools1205053SZS 0,6X3,5Screwdriver, bladed, matches all screw terminal blocks up to 4.0mm² connection cross section, blade: 0.6 x 3.5 mm, without VDEapprovalAdditional productsItem Designation DescriptionGeneral0707060DFK-MSTB 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 320 V, pitch: 5.0mm, no. of positions: 8, mounting: Direct mounting1899906EMSTBA 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Press in1914917EMSTBVA 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 200 V, pitch: 5.0mm, no. of positions: 8, mounting: press in1762758MDSTB 2,5/ 8-G1Header, nominal current: 10 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1846577MDSTBA 2,5/ 8-G Header, nominal current: 10 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1762907MDSTBV 2,5/ 8-G1Header, nominal current: 10 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1845840MDSTBVA 2,5/ 8-G Header, nominal current: 10 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1754559MSTB 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1768244MSTB 2,5/ 8-G-LA Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1757527MSTBA 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1770546MSTBA 2,5/ 8-G-LA Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1753550MSTBV 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1755574MSTBVA 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1736056MSTBW 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1769298SMSTB 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: Soldering1769861SMSTBA 2,5/ 8-G Header, nominal current: 12 A, rated voltage: 250 V, pitch: 5.0mm, no. of positions: 8, mounting: SolderingDrawingsDimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

KAD2708L-21Q68中文资料

KAD2708LDescriptionThe Kenet KAD2708L is the industry’s lowest power, 8-bit, 350MSPS, high performance Analog-to-Digital converter. It is designed with Kenet’s proprietary FemtoCharge® technology on a standard CMOS process. The KAD2708L offers high dynamic performance (48.8dBFS SNR @ f IN = 175MHz) while consuming less than 330mW. Features include an over-range indicator and a selectable divide-by-2 input clock divider. The KAD2708L is one member of a pin-compatible family offering 8 and 10-bit ADCs with sample rates from 105 to 350MSPS and LVDS-compatible or LVCMOS outputs (Table 1). This family of products is available in 68-pin RoHS-compliant QFN packages with exposed paddle. Performance is specified over the full industrial temperature range(-40 to +85°C).Key Specifications• SNR = 48.8dBFS at f S = 350MSPS, f IN = 175MHz • SFDR = 64dBc at f S = 350MSPS, f IN = 175MHz • Power consumption < 330mW at f S = 350MSPSFeatures• On-chip reference• Internal track and hold• 1.5V PP differential input voltage• 600MHz analog input bandwidth• Two’s complement or binary output• Over-range indicator• Selectable ÷2 Clock Divider• LVDS compatible outputs Applications• High-Performance Data Acquisition• Portable Oscilloscope• Medical Imaging• Cable Head Ends• Power-Amplifier Linearization• Radar and Satellite Antenna Array Processing • Broadband Communications• Point-to-Point Microwave Systems• Communications Test Equipment8-Bit, 350/275/210/170/105MSPS A/D ConverterResolution, Speed LVDS Outputs LVCMOS Outputs8 Bits 350MSPS KAD2708L-3510 Bits 275MSPS KAD2710L-27 KAD2710C-278 Bits 275MSPS KAD2708L-27 KAD2708C-2710 Bits 210MSPS KAD2710L-21 KAD2710C-218 Bits 210MSPS KAD2708L-21 KAD2708C-2110 Bits 170MSPS KAD2710L-17 KAD2710C-178 Bits 170MSPS KAD2708L-17 KAD2708C-1710 Bits 105MSPS KAD2710L-10 KAD2710C-108 Bits 105MSPS KAD2708L-10 KAD2708C-10Table 1. Pin-Compatible ProductsPin-Compatible FamilyKAD2708L Table of ContentsSection PagesElectrical Specifications 3-7Specifications 3DCACSpecifications 4,5DigitalSpecifications 6TimingSpecifications 7TimingDiagram 7Absolute Maximum Ratings 8ThermalImpedance 8ESD 8Pin Descriptions 9Pin Configuration 10Typical Operating Characteristics 11-13Functional Description 14Reset 14VoltageReference 14AnalogInput 14Input 15ClockJitter 16Digital Outputs 16Equivalent Circuits 16,17Layout Considerations 17Definitions 18Outline Dimensions 19Package Dimensions 20Ordering Guide 20Electrical SpecificationsAll specifications apply under the following conditions unless otherwise noted: AVDD2=1.8V, AVDD3=3.3V, OVDD=1.8V. T A= -40°C to +85°C, Typ values at 25°C. f SAMPLE = 350, 270, 210, 170 and 105MSPS, f IN = Nyquist, at –0.5dBFS. DC SpecificationsKAD2708L-35 KAD2708L-27 KAD2708L-21Min Typ Max Min Typ Max Min Typ Max Units Parameter Symbol TempRangeAnalog InputFull-Scale Analog Input Range V FS 1.4 1.5 1.6 1.4 1.5 1.6 1.4 1.5 1.6 V PPFull Scale Range Temperature Drift A VTC Full 257 230 210 ppm/°C Common-Mode Output Voltage V CM860 860 860 mVPower Requirements1.8V Analog Supply Voltage AVDD2 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V3.3V Analog Supply Voltage AVDD3 3.15 3.3 3.45 3.15 3.3 3.45 3.15 3.3 3.45 V1.8V Digital Supply Voltage OVDD 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V1.8V Analog Supply Current I AVDD2 51 60 44 51 38 42 mA3.3V Analog Supply Current I AVDD3 50 54 41 45 33 37 mA1.8V Digital Supply Current I OVDD 39 44 34 39 33 36 mA Power Dissipation P D327 365 275 310 237 263 mWKAD2708L-17 KAD2708L-10Min Typ Max Min Typ Max UnitsParameter Symbol TempRangeAnalog InputFull-Scale Analog Input Range V FS 1.4 1.5 1.6 1.4 1.5 1.6 V PPFull Scale Range Temperature Drift A VTC Full 198 176 ppm/°CCommon-Mode Output Voltage V CM860 860 mVPower Requirements1.8V Analog Supply Voltage AVDD2 1.7 1.8 1.9 1.7 1.8 1.9 V3.3V Analog Supply Voltage AVDD3 3.15 3.3 3.45 3.15 3.3 3.45 V1.8V Digital Supply Voltage OVDD 1.7 1.8 1.9 1.7 1.8 1.9 V1.8V Analog Supply Current I AVDD235 39 29 33 mA3.3V Analog Supply Current I AVDD3 28 32 21 24 mA1.8V Digital Supply Current I OVDD31 36 28 32 mAPower Dissipation P D211 241 172 196 mWAC SpecificationsKAD2708L-35 KAD2708L-27 KAD2708L-21 Parameter Symbol Conditions Min Typ Max Min Typ Max Min Typ Max Units Maximum Conversion Rate f S Max 350 275 210 MSPS Minimum Conversion Rate f S Min 50 50 50 MSPS Differential Nonlinearity DNL -0.3 ±0.2 0.4 -0.3 ±0.2 0.4 -0.3 ±0.2 0.4 LSB Integral Nonlinearity INL -0.8 ±0.2 0.8 -0.8 ±0.2 0.8 -0.8 ±0.2 0.8 LSB Signal-to-Noise Ratio SNR f IN = 10MHz 49.0 50.4 49.5 dBFSf IN = Nyquist 46.5 48.8 46.5 49.2 46.5 49.2 dBFSf IN = 430MHz 48.0 49.0 49.1 dBFS Signal-to-Noise and SINAD f IN = 10MHz 48.9 49.2 49.5 dBFS Distortion f IN = Nyquist 46.5 48.2 46.5 49.2 46.5 49.2 dBFSf IN = 430MHz 47.7 48.9 48.9 dBFS Effective Number of Bits ENOBFS f IN = 10MHz 7.8 7.9 7.9 Bitsf IN = Nyquist 7.4 7.9 7.4 7.9 7.4 7.9 Bitsf IN = 430MHz 7.6 7.8 7.8 Bits Spurious-Free Dynamic SFDR f IN = 10MHz 65 67.6 69.1 dBc Range f IN = Nyquist 61 64 61 66.6 61 69.1 dBcf IN = 430MHz 62 66.1 69.0 dBc61 63 65 dBc Two-Tone SFDR 2TSFDR f IN =133,135MHzWord Error Rate WER 10-1210-1210-12Full Power Bandwidth FPBW 600 600 600 MHzAC Specifications continuedKAD2708L-17 KAD2708L-10TypUnitsMinMaxMaxParameter SymbolConditionsMinTypMaximum ConversionfS Max 170 105 MSPSRateMinimum ConversionfS Min 50 50 MSPSRateDifferential Nonlinearity DNL f IN = 10MHz -0.3 ±0.2 0.4 -0.3 ±0.2 0.4 LSBIntegral Nonlinearity INL f IN = 10MHz -0.8 ±0.2 0.8 -0.8 ±0.2 0.8 LSBSignal-to-Noise Ratio SNR f IN = 10MHz 49.5 49.5 dBFSf IN = Nyquist 46.5 49.2 46.5 49.2 dBFSf IN = 430MHz 49.1 49.1 dBFSSignal-to-Noise and SINAD f IN = 10MHz 49.5 49.5 dBFSDistortion f IN = Nyquist 46.5 49.2 46.5 49.2 dBFSf IN = 430MHz 49.0 48.9 dBFSEffective Number of Bits ENOB f IN = 10MHz 7.9 7.9 Bitsf IN = Nyquist 7.4 7.9 7.4 7.9 Bitsf IN = 430MHz 7.8 7.8 BitsSpurious-Free Dynamic SFDR f IN = 10MHz 69.1 69.1 dBcRange f IN = Nyquist 61 69.1 61 69.1 dBcf IN = 430MHz 69.0 68.9 dBc65 65 dBcTwo-Tone SFDR 2TSFDR f IN =133,135MHzWord Error Rate WER 10-1210-12Full Power Bandwidth FPBW 600 600 MHzDigital SpecificationsParameter Symbol Conditions Min Typ Max Units InputsHigh Input Voltage (VREFSEL) VREFSEL V IH 0.8*AVDD3 V Low Input Voltage (VREFSEL) VREFSEL V IL 0.2*AVDD3 V Input Current High (VREFSEL) VREFSEL I IH VIN = AVDD3 0 1 10 µA Input Current Low (VREFSEL) VREFSEL I IL VIN = AVSS256575µAHigh Input Voltage (CLKDIV) CLKDIV V IH 0.8*AVDD3 VLow Input Voltage (CLKDIV) CLKDIV V IL 0.2*AVDD3 V Input Current High (CLKDIV) CLKDIV I IH VIN = AVDD3 25 65 75 µA Input Current Low (CLKDIV) CLKDIV I IL VIN = AVSS110µAHigh Input Voltage (RST,2SC) RST,2SC V IH 0.8*OVDD2 VLow Input Voltage (RST,2SC) RST,2SC V IL 0.2*OVDD2 V Input Current High (RST,2SC) RST,2SC I IH VIN = OVDD 0 1 10 µA Input Current Low (RST,2SC) RST,2SC I ILVIN = OVSS 25 50 75 µA Input Capacitance C DI 3 pF LVDS OutputsDifferential Output Voltage V T 210 mV Output Offset Voltage V OS 1.15V Output Rise Time t R 500 ps Output Fall Timet F500psCLKP, CLKN P-P Differential Input VoltageV CDI 0.5 3.6 V PP CLKP, CLKN Differential Input ResistanceR CDI 10 M Ω CLKP, CLKN Common-Mode Input Voltage V CCI0.9VTiming DiagramFigure 1. LVDS Timing DiagramTiming SpecificationsParameter Symbol Min Typ Max Units Aperture Delay t A 1.7 ns RMS Aperture Jitterj A200fsInput Clock to Data Propagation Delay tPID3.55.06.5ns Data Hold TimetPH -300ps Output Clock to Data Propagation Delayt PCD2.83.7ns Latency (Pipeline Delay)L 28 cycles Over Voltage Recoveryt OVR1cycleAbsolute Maximum Ratings11. Exposing the device to levels in excess of the maximum ratings may cause permanent damage. Operation at maximum conditions for extended periods may affect device reliability.Thermal Impedance2. Paddle soldered to ground plane.ESDElectrostatic charge accumulates on humans, tools and equipment, and may dischargethrough any metallic package contacts (pins, balls, exposed paddle, etc.) of an integratedcircuit. Industry-standard protection techniques have been utilized in the design of this prod-uct. However, reasonable care must be taken in the storage and handling of ESD sensitiveproducts. Contact Kenet for the specific ESD sensitivity rating of this product.Parameter MinMaxUnit AVDD2 to AVSS -0.4 2.1 VOVDD2 to OVSS -0.4 2.1 VAnalog Inputs to AVSS -0.4 AVDD3 + 0.3 VClock Inputs to AVSS -0.4 AVDD2 + 0.3 VLogic Inputs to AVSS (VREFSEL, CLKDIV) -0.4 AVDD3 + 0.3 VLogic Inputs to OVSS (RST, 2SC) -0.4 OVDD2 + 0.3 VOperating Temperature -40 85 °CStorage Temperature -65 150 °CJunction Temperature 150 °CAVDD3 to AVSS -0.4 3.7 VLogic Output Currents 10 mALVDS Output Currents 20 mAVREF TO AVSS -0.4 AVDD3 + 0.3 VAnalog Output Currents 10 mAParameter SymbolTypUnitJunction to Paddle2ΦJP 30 °C/WPin DescriptionPin # Name Function1, 14, 18, 20 AVDD2 1.8V Analog Supply2, 7, 10, 19, 21, 24 AVSS Analog Supply ReturnOut/InVoltageReference3 VREF4 VREFSEL Reference Voltage Select (0:Int 1:Ext)OutputVoltageCommon-Mode5 VCM6, 15, 16, 25 AVDD3 3.3V Analog Supply8, 9 INP, INN Analog Input Positive, Negative11-13, 29-36, 62, 63, 67 DNC Do Not Connect17 CLKDIV Clock Divide by Two (Active Low)22, 23 CLKN, CLKP Clock Input Complement, True26, 45, 61 OVSS Output Supply Return27, 41, 44, 60 OVDD2 1.8V LVDS Supply28 RST Power On Reset (Active Low)37, 38 D0N, D0P LVDS Bit 0 (LSB) Output Complement, True39, 40 D1N, D1P LVDS Bit 1 Output Complement, True42, 43 CLKOUTN, CLKOUTP LVDS Clock Output Complement, True46, 47 D2N, D2P LVDS Bit 2 Output Complement, True48, 49 D3N, D3P LVDS Bit 3 Output Complement, True50, 51 D4N, D4P LVDS Bit 4 Output Complement, True52, 53 D5N, D5P LVDS Bit 5 Output Complement, True54, 55 D6N, D6P LVDS Bit 6 Output Complement, True56, 57 D7N, D7P LVDS Bit 7 Output Complement, True58, 59 ORN, ORP Over-Range Complement, TruetoOVDD2Connect64-6668 2SC Two’s Complement Select (Active Low)Exposed Paddle AVSS Analog Supply ReturnPin ConfigurationFigure 2. Pin Configuration2S CD N CO V D D 2O V D D 2O V D D 2D N CD N CO V S SO V D D 2O R PO R ND 7PD 7ND 6PD 6N D 5PD 5NA V D D 2A V S SA V D D 2A V S SC L K NC L K PA V S SA V D D 3O V S SO V D D 2R S TD N CD N CD N CD N CD N CD N CAVDD2AVSS VREF VREFSELVCM AVDD3AVSS INP INN AVSS DNC DNC DNC AVDD2AVDD3AVDD3CLKDIVD2P D2N OVSS OVDD2CLKOUTP CLKOUTN OVDD2D1P D1N D0P D0N DNC DNCD4P D4N D3P D3N 1234567891011121314151617181920212223242526272829303132333447464544434241403938373635686766656463626160595857565554535251504948元器件交易网KAD2708LTypical Operating CharacteristicsAVDD2=OVDD2= 1.8V, AVDD3= 3.3V, TAMBIENT (TA)= 25°C, fSAMPLE= 350MHz, fIN=175MHz, AIN= -0.5dBFS unless noted.70 65 SNR(dBFS), SFDR(dBc) 60 55 50 45 40 5 105 205 305 fIN(MHz) 405 505-50 -55SFDRHD2, HD3(dBc)-60 -65 -70 -75 -80HD3SNRHD2-85 -90 5 105 205 305 fIN(MHz) 405 505Figure 3. SNR, SFDR vs. fIN80 70 SNR (dBFS), SFDR (dBc) 60 50 40 30 20 -30 -25 -20 -15 A IN (dBFS) -10 -5 0Figure 4. HD2, HD3 vs. fIN-20 -30 H D 2, H D 3 dBc -40 -50HD2 HD3SNR-60 -70 -80 -30 -25 -20 -15 -10 -5 0 Input Amplitude (dBFS)SFDRFigure 5. SNR, SFDR vs. AIN80 76SNR(dBFS), SFDR (dBc)Figure 6. HD2, HD3 vs. AIN-6572 68 64 60 56 52 48 44 40 50SFDR-70 HD2, HD3(dBc) -75 -80 -85HD3SNRHD2-90100 150 200 250 300 35050100150200 fSAMPLE (MSPS)250300350fSAMPLE (fS) (MSPS)Figure 7. SNR, SFDR vs. fSAMPLEFigure 8. HD2, 3 vs. fSAMPLE Page 11 of 20元器件交易网KAD2708LTypical Operating CharacteristicsAVDD2=OVDD2= 1.8V, AVDD3= 3.3V, TAMBIENT (TA)= 25°C, fSAMPLE= 350MHz, fIN=175MHz, AIN= -0.5dBFS unless noted.350 330 Power Dissipation (P D)(mW) 310 290 250 230 210 190 170 150 100 150 200 250 300 350DNL (LSBs) 1 0.75 0.5 0.25 0 -0.25 -0.5 -0.75 -1 0 32 64 96 128 CODE 160 192 224 255270Figure 9. Power Dissipation vs. fSAMPLE1 0.75 0.5 0.25 INL (LSBs) 0 -0.25 -0.5 -0.75 -1f S (MSPS)Figure 10. Differential Nonlinearity vs. Output Code50,000 45,000 40,000 35,000 CODE COUNT 30,000 25,000 20,000 15,000 10,000 5,0000326496128 CODE1601922242550 124125126127 CODE128129130Figure 11. Integral Nonlinearity vs. Output Code0 Ain = -0.47dBFS -20 SNR = 49.4dBFS SFDR = 68.4dBc AMPLITUDE (dB)AMPLITUDE (dB) -20 0Figure 12. Noise HistogramAin = -0.47dBFS SNR = 49.4dBFS SFDR = 69.2dBc -40 SINAD = 49.4dBFS HD2 = -81dBc -60 HD3 = -91dBc-40SINAD = 49.3dBFS HD2 = -86dBc-60HD3 = -69dBc-80-80-100-100-1200204060 80 FREQUENCY (MHz)100120-1200204060 80 FREQUENCY (MHz)100120Figure 13. Output Spectrum at 9.865MHzFigure 14. Output Spectrum at 133.805MHz Page 12 of 20元器件交易网KAD2708LTypical Operating CharacteristicsAVDD2=OVDD2= 1.8V, AVDD3= 3.3V, TAMBIENT (TA)= 25°C, fSAMPLE= 350MHz, fIN=175MHz, AIN= -0.5dBFS unless noted.0 Ain = -0.48dBFS -20 SNR = 49.3dBFS SFDR = 63dBc -40 AMPLITUDE (dB) SINAD = 49.1dBFS HD2 = -63dBc -60 HD3 = -67dBc0 Ain = -7.1dBFS -20 2TSFDR = 67dBc IMD3 = -74dBFS AMPLITUDE (dB) -40-60-80-80-100-100-1200204060 80 FREQUENCY (MHz)100120-1200204060 80 FREQUENCY (MHz)100120Figure 15. Output Spectrum at 299.645MHz0 Ain = -7dBFS -20 2TSFDR = 73dBc IMD3 = -81dBFS AMPLITUDE (dB) -40AMPLITUDE (dB) -40 -20 0Figure 16. Two-Tone Spectrum at 69, 70MHzAin = -7dBFS 2TSFDR = 63dBc IMD3 = -76dBFS-60-60-80-80-100-100-1200204060 80 FREQUENCY (MHz)100120-1200204060 80 FREQUENCY (MHz)100120Figure 17. Two-Tone Spectrum at 140,141MHz75 70 SNR(dBFS), SFDR(dBc) 65 60 55 50 45 40 -40 -20 0 20 40 AMBIENT TEMPERATURE, C 60 80SNR SFDRFigure 18. Two-Tone Spectrum at 300, 305MHz700 600 500 tCAL (ms) 400 300 200 100 100125150175200225250275300325350f SAMPLE (f S ) (MSPS)Figure 19. SNR and SFDR vs. TemperatureFigure 20. Calibration Time vs. fS Page 13 of 20元器件交易网KAD2708LFunctional DescriptionThe KAD2708 is an eight bit, 350MSPS A/D converter in a pipelined architecture. The input voltage is captured by a sample & hold circuit and converted to a unit of charge. Proprietary charge-domain techniques are used to compare the input to a series of reference charges. These comparisons determine the digital code for each input value. The converter pipeline requires 24 sample clocks to produce a result. Digital error correction is also applied, resulting in a total latency of 28 clock cycles. This is evident to the user as a latency between the start of a conversion and the data being available on the digital outputs. At start-up, a self-calibration is performed to minimize gain and offset errors. The reset pin (RST) is initially held low internally at power-up and will remain in that state until the calibration is complete. The clock frequency should remain fixed during this time. Calibration accuracy is maintained for the sample rate at which it is performed, and therefore should be repeated if the clock frequency is changed by more than 10%. Recalibration can be initiated via the RST pin, or power cycling, at any time.Figure 21. Calibration TimingVoltage ReferenceThe VREF pin is the full-scale reference, which sets the full-scale input voltage for the chip and requires a bypass capacitor of 0.1uF or larger. An internally generated reference voltage is provided from a bandgap voltage buffer. This buffer can sink or source up to 50µA externally. An external voltage may be applied to this pin to provide a more accurate reference than the internally generated bandgap voltage or to match the full-scale reference among a system of KAD2708L chips. One option in the latter configuration is to use one KAD2708L's internally generated reference as the external reference voltage for the other chips in the system. Additionally, an externally provided reference can be changed from the nominal value to adjust the full-scale input voltage within a limited range. To select whether the full-scale reference is internally generated or externally provided, the digital input port VREFSEL should be set appropriately, low for internal or high for external. This pin also has an internal 18kΩ pull-up resistor. To use the internally generated reference VREFSEL can be tied directly to AVSS, and to use an external reference VREFSEL can be left unconnected.ResetRecalibration of the ADC can be initiated at any time by driving the RST pin low for a minimum of one clock cycle. An open-drain driver is recommended. The calibration sequence is initiated on the rising edge of RST, as shown in Figure 21. The over-range output (ORP) is set high once RST is pulled low, and remains in that state until calibration is complete. The ORP output returns to normal operation at that time, so it is important that the analog input be within the converter’s full-scale range in order to observe the transition. If the input is in an over-range state the ORP pin will stay high and it will not be possible to detect the end of the calibration cycle. While RST is low, the output clock (CLKOUTP/CLKOUTN) stops toggling and is set low. Normal operation of the output clock resumes at the next input clock edge (CLKP/CLKN) after RST is deasserted. At 350MSPS the nominal calibration time is ~190ms.Analog InputThe fully differential ADC input (INP/INN) connects to the sample and hold circuit. The ideal full-scale input voltage is 1.5VPP, centered at the VCM voltage of 0.86V as shown in Figure 22.Page 14 of 20元器件交易网KAD2708Lsettling and improved performance. Therefore a 1:1 transformer and low shunt resistance are recommended for optimal performance. A differential amplifier can be used in applications that require dc coupling, at the expense of reduced dynamic performance. In this configuration the amplifier will typically reduce the achievable SNR and distortion performance. A typical differential amplifier configuration is shown in Figure 25.Figure 22. Analog Input Range Best performance is obtained when the analog inputs are driven differentially. The common-mode output voltage, VCM, should be used to properly bias each input as shown in Figures 23 and 24. An RF transformer will give the best noise and distortion performance for wideband and/or high intermediate frequency (IF) inputs. Two different transformer input schemes are shown in Figures 23 and 24. Figure 25. Differential Amplifier InputClock InputThe clock input circuit is a differential pair (see Figure 29). Driving these inputs with a high level (up to 1.8VPP on each input) sine or square wave will provide the lowest jitter performance. The recommended drive circuit is shown in Figure 26. The clock can be driven single-ended, but this will reduce the edge rate and may impact SNR performance.Figure 23. Transformer Input, General ApplicationFigure 24. Transformer Input, High IF Application A back-to-back transformer scheme is used to improve common-mode rejection, which keeps the common-mode level of the input matched to VCM. The value of the termination resistor should be determined based on the desired impedance. The sample and hold circuit design uses a switched capacitor input stage, which creates current spikes when the sampling capacitance is reconnected to the input voltage. This creates a disturbance at the input which must settle before the next sampling point. Lower source impedance will result in faster Figure 26. Recommended Clock Drive Use of the clock divider is optional. The KAD2708L's ADC requires a clock with 50% duty cycle for optimum performance. If such a clock is not available, one option is to generate twice the desired sampling rate, then use the KAD2708L's divide-by-2 to generate a 50%-duty-cycle clock. This frequency divider uses the rising edge of the clock, so 50% clock duty cycle is assured. Table 2 describes the CLKDIV connection. Page 15 of 20元器件交易网KAD2708LCLKDIV PinAVSS AVDDDivide Ratio2 1Digital OutputsData is output on a parallel bus with LVDScompatible drivers. The output format (Binary or Two’s Complement) is selected via the 2SC pin as shown in Table 4.Table 3. CLKDIV Pin Settings CLKDIV is internally pulled low, so a pull-up resistor or logic driver must be connected for undivided clock.2SC PinAVSS AVDD (or unconnected)ModeTwo’s Complement BinaryJitterIn a sampled data system, clock jitter directly impacts the achievable SNR performance. The theoretical relationship between clock jitter and maximum SNR is shown in Equation 1 and is illustrated in Figure 27.Table 4. 2SC Pin Settings⎛ ⎞ 1 SNR = 20 log 10 ⎜ ⎜ 2π f t ⎟ ⎟ IN J ⎠ ⎝Where tj is the RMS uncertainty in the sampling instant.Equivalent CircuitsEquation 1. This relationship shows the SNR that would be achieved if clock jitter were the only non-ideal factor. In reality, achievable SNR is limited by internal factors such as differential nonlinearity aperture jitter and thermal noise.100 95 90 85 tj=0.1ps 14 BitsFigure 28. Analog InputsSNR - dB80 75 70 65 60 55 50 1 10 tj=100ps tj=10pstj=1ps12 Bits10 Bits1001000Input Frequency - MHzFigure 27. SNR vs. Clock Jitter Any internal aperture jitter combines with the input clock jitter in a root-sum-square fashion since they are not statistically correlated, and this determines the total jitter in the system. The total jitter, combined with other noise sources, then determines the achievable SNR.Figure 29. Clock Inputs Page 16 of 20元器件交易网KAD2708LLVDS OutputsOVDDOVDD DATA DATA D[7:0]P OVDDOutput traces and connections must be designed for 50Ω (100Ω differential) characteristic impedance. Keep traces direct, and minimize bends where possible. Avoid crossing ground and power-plane breaks with signal traces.Unused InputsThe RST and 2SC inputs are internally pulled up, and can be left open-circuit if not used. CLKDIV is internally pulled low, which divides the input clock by two. VREFSEL is internally pulled up. It must be held low for internal reference, but can be left open for external reference.D[7:0]NDATADATAFigure 30. LVDS OutputsLayout ConsiderationsSplit Ground and Power PlanesData converters operating at high sampling frequencies require extra care in PC board layout. Many complex board designs benefit from isolating the analog and digital sections. Analog supply and ground planes should be laid out under signal and clock inputs. Locate the digital planes under outputs and logic pins. Ground planes, if separated, should be joined at the exposed paddle under the chip.Clock Input ConsiderationsUse matched transmission lines to the inputs for the analog input and clock signals. Locate transformers, drivers and terminations as close to the chip as possible.Bypass and FilteringBulk capacitors should have low equivalent series resistance. Tantalum is a good choice. For best performance, keep ceramic bypass capacitors very close to device pins. Longer traces will increase inductance, resulting in diminished dynamic performance and accuracy. Make sure that connections to ground are direct and low impedance.Page 17 of 20元器件交易网KAD2708LDefinitionsAnalog Input Bandwidth is the analog input frequency at which the spectral output power at the fundamental frequency (as determined by FFT analysis) is reduced by 3dB from its full-scale low-frequency value. This is also referred to as Full Power Bandwidth. Aperture Delay or Sampling Delay is the time required after the rise of the clock input for the sampling switch to open, at which time the signal is held for conversion. Aperture Jitter is the RMS variation in aperture delay for a set of samples. Clock Duty Cycle is the ratio of the time the clock wave is at logic high to the total time of one clock period. Differential Non-Linearity (DNL) is the deviation of any code width from an ideal 1 LSB step. Effective Number of Bits (ENOB) is an alternate method of specifying Signal to Noise-and-Distortion Ratio (SINAD). In dB, it is calculated as: ENOB = (SINAD-1.76) / 6.02. Integral Non-Linearity (INL) is the deviation of each individual code from a line drawn from negative fullscale (1/2 LSB below the first code transition) through positive full-scale (1/2 LSB above the last code transition). The deviation of any given code from this line is measured from the center of that code. Least Significant Bit (LSB) is the bit that has the smallest value or weight in a digital word. Its value in terms of input voltage is VFS/(2N-1) where N is the resolution in bits. Missing Codes are output codes that are skipped and will never appear at the ADC output. These codes cannot be reached with any input value. Most Significant Bit (MSB) is the bit that has the largest value or weight. Its value in terms of input voltage is VFS/2. Pipeline Delay is the number of clock cycles between the initiation of a conversion and the appearance at the output pins of the corresponding data. Power Supply Rejection Ratio (PSRR) is the ratio of a change in power supply voltage to the input voltage necessary to negate the resultant change in output code. Signal to Noise-and-Distortion (SINAD) is the ratio of the RMS signal amplitude to the RMS sum of all other Page 18 of 20 spectral components below one half the clock frequency, including harmonics but excluding DC. Signal-to-Noise Ratio (SNR) (without Harmonics) is the ratio of the RMS signal amplitude to the RMS sum of all other spectral components below one-half the sampling frequency, excluding harmonics and DC. Spurious-Free-Dynamic Range (SFDR) is the ratio of the RMS signal amplitude to the RMS value of the peak spurious spectral component. The peak spurious spectral component may or may not be a harmonic. Two-Tone SFDR is the ratio of the RMS value of either input tone to the RMS value of the peak spurious component. The peak spurious component may or may not be an IMD product.元器件交易网KAD2708LOutline Dimensions - QFN68 EPD D/2 D1 D1/2PIN 1 ID 0.80 DIA E1/2 E/2E1ETOP VIEWC CbA1eTERMINAL TIPSECTION “C-C” SCALE: NONEA A1 4X PbD2 D2/2 4X P 0.45E216Xe REF.E2/2Θ0.25 MIN L 0.25 MIN SEATING PLANE 16Xe REF.eBOTTOM VIEWPage 19 of 20。

0462070208;中文规格书,Datasheet资料

This document was generated on 08/16/2012PLEASE CHECK FOR LATEST PART INFORMATIONPart Number:46207-0208Status:ActiveOverview:Mini-Fit® RTCDescription:4.20mm Pitch Mini-Fit® RTC Reflow High Temperature Compatible Header, Dual Row,Vertical, 8 Circuits, 3.18mm PCB Thickness, with PCB Pegs, LCP Housing, with Tin (Sn) Over Nickel (Ni) Plating, Glow Wire CompliantDocuments:3D ModelProduct Specification PS-46207-001 (PDF)Drawing (PDF)RoHS Certificate of Compliance (PDF)Agency CertificationCSA LR19980ULE29179GeneralProduct Family PCB Headers Series46207Application Board-to-Board, Power, Wire-to-BoardCommentsCurrent = 13A max. per circuit when header is mated to a receptacle loaded with 45750 Mini-Fit® Plus HCS Crimp Terminal Crimped to 16 AWG wire.,See Molex product specification PS-45750-001 for additional current de-rating information.. . This Molex product is manufactured from material that has the following ratings, tested by independent agencies : .a) A Glow Wire Ignition Temperature (GWIT) of at least 775 deg C per IEC 60695-2-13. . b) A Glow Wire Flammability Index (GWFI) above 850 deg C per IEC 60695-2-12.and hence complies with the requirements set out in the International Standard IEC 60335-1 5th edition - household and similar electrical appliances - safety; section 30 Resistance to heat and fire. . .The customers using this product must determine its suitability for use in their particular application through testing or other acceptable means as described in end-product glow-wire flammability test standard IEC 60695-2-11 and any applicable product end-use standard(s). . . If it is determined during the customer’s evaluation of suitability, that higher performance is required, please contact Molex for possible product options.OverviewMini-Fit® RTC Product Name Mini-Fit® RTC UPC800756835686PhysicalBreakawayNo Circuits (Loaded)8Circuits (maximum)8Color - ResinBlack Durability (mating cycles max)100First Mate / Last Break No Flammability94V-0Glow-Wire Compliant Yes Guide to Mating PartNoSeriesimage - Reference onlyEU RoHSChina RoHSELV and RoHS Compliant REACH SVHCContains SVHC: No Low-Halogen Status Low-HalogenNeed more information on product environmental compliance?Email productcompliance@For a multiple part number RoHS Certificate of Compliance, click herePlease visit the Contact Us section for any non-product compliance questions.Search Parts in this Series 46207SeriesMates With5557 Mini Fit Jr.™ ReceptacleKeying to Mating Part NoneLock to Mating Part YesMaterial - Metal BrassMaterial - Plating Mating TinMaterial - Plating Termination NickelMaterial - Resin High Temperature ThermoplasticNet Weight 3.106/gNumber of Rows2Orientation VerticalPC Tail Length 5.26mmPCB Locator YesPCB Retention YesPCB Thickness - Recommended 3.18mmPackaging Type TrayPitch - Mating Interface 4.20mmPitch - Termination Interface 4.20mmPolarized to Mating Part YesPolarized to PCB YesShrouded FullyStackable NoSurface Mount Compatible (SMC)YesTemperature Range - Operating-40°C to +105°CTermination Interface: Style Through HoleElectricalCurrent - Maximum per Contact13AVoltage - Maximum600V AC (RMS)/DCSolder Process DataDuration at Max. Process Temperature (seconds)30Lead-free Process Capability SMC & Wave Capable (TH only)Max. Cycles at Max. Process Temperature3Process Temperature max. C265Material InfoReference - Drawing NumbersProduct Specification PS-46207-001Sales Drawing SD-46207-001This document was generated on 08/16/2012PLEASE CHECK FOR LATEST PART INFORMATION分销商库存信息: MOLEX 0462070208。

LC系列说明书(中文)-V3.0

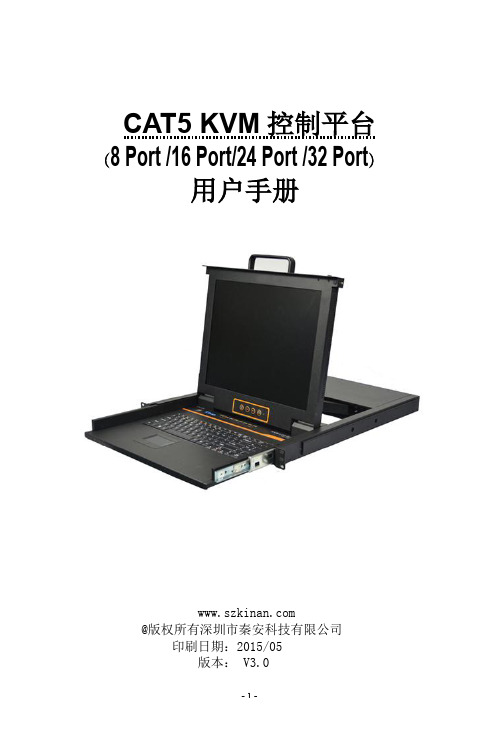

CAT5 KVM 控制平台 (8 Port /16 Port/24 Port /32 Port) 用户手册

@版权所有深圳市秦安科技有限公司 印刷日期:2015/05 版本: V3.0

-1-

Байду номын сангаас

用户手册 目录 概述................................................................................................................................................................................................... 3 产品描述 ......................................................................................................................................................3 产品特性 .....................

提臀疗法

雾花浓基因频谱解码仪与提臀周晓俊作品健康看臀疗:从健康上讲做臀疗对女性妇科方面有很好的改善、对女性的痔疮可以有很好的改善、提高女性对性生活的质量和要求。

美学看臀疗:拥有丰满、翘挺的臀部是每个女性的期待。

俗话称美女:前有凉台和后有花园的女人才叫美女。

性学看臀疗:常做臀疗的女性,可提高对性的热情,对性的情趣,提高夫妻间的和睦生活。

心理学看臀疗:据统计有95%的女性为自已有丰满的双乳和翘挺的臀部感到自信和快感。

基因频谱解码仪提臀手法流程:产品:雾花浓FHN27081.喝水:让客人做前喝200毫升的凉白开水,操作过程也须喝200毫升的凉白开水,操作完毕后须多喝水。

2.仪器配合:打开基因频谱解码仪开关,将时间调到60分钟,将功能调在最大档。

3.将导波带平放在美容床上,(为了导波带的清洁,在导波带上平放毛巾)客人平趴在导波带上。

4.导入能量:用40瓦日光灯管于客人头部、双侧颈部、腰部、四肢等导入能量,并用基因棒在臀部画“米”字,画9次米。

5.按摩耳朵:双手拇指与食指,从客人耳垂至耳尖来回按摩9次。

6.臀部展油:用FHN2708提臀理疗油2ml倒在手心,从腰部滑向臀部底部双侧抱回展油,并五段层层热臀按摩。

7.臀部点穴:臀部点穴非常重要,须按中医穴位对人体的身体改善而进行点穴,请依次点穴,括号中为双穴,用双手大拇指点穴,承扶穴(双穴)、长强穴、督脉正中线上的八髎穴:下髎穴、中髎穴、次髎穴、上髎穴、腰俞穴、腰阳关、腰眼穴、会阳穴、督脉旁开0.5寸:大肠俞、关元俞、小肠俞、膀胱俞、中膂俞、白环俞、督脉旁开3寸:胞肓穴、秩边穴、环跳穴、(双穴)8.臀部拔筯:用FHN2708提臀经络油2ml做臀部拔筯、先将1ml提臀经络油倒入手心展开后做单边臀部五段展油,单边臀部分五段拔筯,第一条:双手大拇指指腹交替从臀根承扶穴前方开始拔拉到腰部,单手排毒并甩手、第二条:双手大拇指指腹从下髎开始交替拔拉到腰部,单手排毒并甩手;第三条:双手大拇指指腹从中髎开始交替拔拉到腰部,单手排毒并甩手;第四条:双手大拇指指腹从次髎开始交替拔拉到腰部,单手排毒并甩手;第五条:双手大拇指指腹从上髎开始交替拔拉到腰部,单手排毒并甩手。

BU2708DX资料

GENERAL DESCRIPTIONHigh voltage, high-speed switching npn transistor with integrated damper diode in a plastic full-pack envelope.Intended for use in horizontal deflection circuits of colour television receivers. Features exceptional tolerance to base drive and collector current load variations resulting in a low worst case dissipation. Designed to withstand V CES pulses up to 1700V.QUICK REFERENCE DATASYMBOL PARAMETERCONDITIONS TYP.MAX.UNIT V CESM Collector-emitter voltage peak value V BE = 0 V-1700V V CEO Collector-emitter voltage (open base)-825V I C Collector current (DC)-8A I CM Collector current peak value -15A P tot Total power dissipationT hs ≤ 25 ˚C-45W V CEsat Collector-emitter saturation voltage I C = 4 A; I B = 1.33 A - 1.0V I Csat Collector saturation current f = 16 kHz 4.0-A V F Diode forward voltage I F = 4.0 A1.6-V t sStorage timeI Csat = 4 A; f = 16 kHz4.85.5µsPINNING - SOT399PIN CONFIGURATIONSYMBOLLIMITING VALUESLimiting values in accordance with the Absolute Maximum Rating System (IEC 134)SYMBOL PARAMETERCONDITIONS MIN.MAX.UNIT V CESM Collector-emitter voltage peak value V BE = 0 V-1700V V CEO Collector-emitter voltage (open base)-825V I C Collector current (DC)-8A I CM Collector current peak value -15A I B Base current (DC)-4A I BM Base current peak value-6A -I BM Reverse base current peak value 1-5A P tot Total power dissipation T hs ≤ 25 ˚C-45W T stg Storage temperature -65150˚C T jJunction temperature-150˚CESD LIMITING VALUESSYMBOL PARAMETERCONDITIONSMIN.MAX.UNIT V CElectrostatic discharge capacitor voltage Human body model (250 pF,-10kV1.5 k Ω)1 Turn-off current.THERMAL RESISTANCESSYMBOL PARAMETER CONDITIONSTYP.MAX.UNIT R th j-hs Junction to heatsink without heatsink compound - 3.7K/W R th j-hs Junction to heatsink with heatsink compound - 2.8K/W R th j-aJunction to ambientin free air35-K/WISOLATION LIMITING VALUE & CHARACTERISTICT hs = 25 ˚C unless otherwise specified SYMBOL PARAMETERCONDITIONSMIN.TYP.MAX.UNIT V isol Repetitive peak voltage from all R.H. ≤ 65 % ; clean and dustfree-2500V three terminals to external heatsinkC isolCapacitance from T2 to external f = 1 MHz -22-pFheatsinkSTATIC CHARACTERISTICST hs = 25 ˚C unless otherwise specified SYMBOL PARAMETERCONDITIONSMIN.TYP.MAX.UNIT I CES Collector cut-off current 2V BE = 0 V; V CE = V CESMmax -- 1.0mA I CES V BE = 0 V; V CE = V CESMmax ;-- 2.0mA T j = 125 ˚C BV EBO Emitter-base breakdown voltage I B = 600 mA 7.513.5-V R BE Base-emitter resistanceV EB = 7.5 V45ΩV CEsat Collector-emitter saturation voltage I C = 4 A; I B = 1.33 A -- 1.0V V BEsat Base-emitter saturation voltage I C = 4 A; I B = 1.33 A 0.830.91 1.00V V F Diode forward voltage I F = 4 A1.6Vh FE DC current gainI C = 1 A; V CE = 5 V -15-h FEI C = 4 A; V CE = 1 V367.3DYNAMIC CHARACTERISTICST hs = 25 ˚C unless otherwise specified SYMBOLPARAMETERCONDITIONSTYP.MAX.UNITSwitching times (line deflection I Csat = 4 A; L C = 1 mH; C FB = 12.2 nF;circuit 16 kHz)V CC = 120 V; I B(end) = 0.8 A; L B = 6 µH;-V BB = 4 V; -I BM = I CM /2t s Turn-off storage time 4.8 5.5µs t fTurn-off fall time0.40.52µs2 Measured with half sine-wave voltage (curve tracer).MECHANICAL DATANotes1. Refer to mounting instructions for F-pack envelopes.2. Epoxy meets UL94 V0 at 1/8".DEFINITIONSData sheet statusObjective specification This data sheet contains target or goal specifications for product development. Preliminary specification This data sheet contains preliminary data; supplementary data may be published later. Product specification This data sheet contains final product specifications.Limiting valuesLimiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application informationWhere application information is given, it is advisory and does not form part of the specification.© Philips Electronics N.V. 1997All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.LIFE SUPPORT APPLICATIONSThese products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.。

1996278资料

CUL Nominal voltage UN Nominal current IN UL Nominal voltage UN Nominal current IN Certification Accessories Item General 1970016 CS-IPC 16/ 6 Coding pin, serves to ensure correct polarization on the PCB during manual mounting Designation Description 600 V 66 A CB, CCA, CUL, SEV, UL 600 V 66 A

Page 2 / 4 Mar 9, 2008

元器件交易网

PC 6-16/ 6-G1U-10,16 Order No.: 1996278

http://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1996278

Dimensioned drawing

元器件交易网

Extract from the online catalog

PC 6-16/ 6-G1U-10,16

Order No.: 1996278

The figure shows a 5-pos. version of the product

http://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=19962mp; Co. KG http://www.phoenixcontact.de

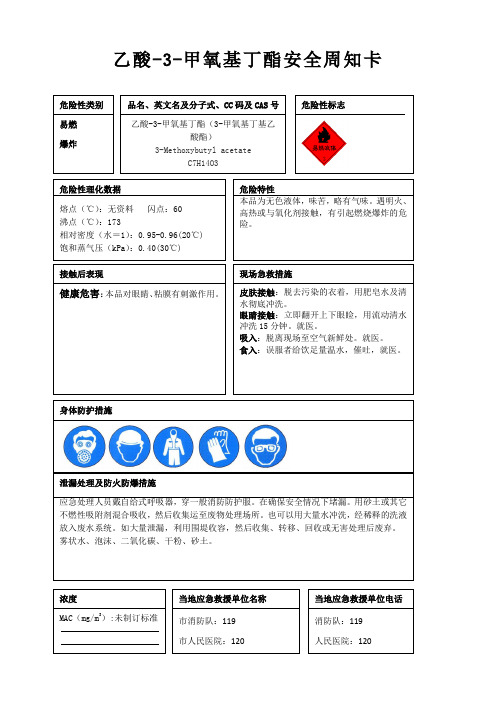

乙酸-3-甲氧基丁酯安全周知卡、职业危害告知卡、理化特性表

乙酸-3-甲氧基丁酯安全周知卡危险性类别易燃爆炸品名、英文名及分子式、CC码及CAS号乙酸-3-甲氧基丁酯(3-甲氧基丁基乙酸酯)3-Methoxybutyl acetateC7H14O3危险性理化数据熔点(℃):无资料闪点:60沸点(℃):173相对密度(水=1):0.95-0.96(20℃)饱和蒸气压(kPa):0.40(30℃)危险特性本品为无色液体,味苦,略有气味。

遇明火、高热或与氧化剂接触,有引起燃烧爆炸的危险。

接触后表现健康危害:本品对眼睛、粘膜有刺激作用。

现场急救措施皮肤接触:脱去污染的衣着,用肥皂水及清水彻底冲洗。

眼睛接触:立即翻开上下眼睑,用流动清水冲洗15分钟。

就医。

吸入:脱离现场至空气新鲜处。

就医。

食入:误服者给饮足量温水,催吐,就医。

身体防护措施泄漏处理及防火防爆措施应急处理人员戴自给式呼吸器,穿一般消防防护服。

在确保安全情况下堵漏。

用砂土或其它不燃性吸附剂混合吸收,然后收集运至废物处理场所。

也可以用大量水冲洗,经稀释的洗液放入废水系统。

如大量泄漏,利用围堤收容,然后收集、转移、回收或无害处理后废弃。

雾状水、泡沫、二氧化碳、干粉、砂土。

浓度MAC(mg/m3):未制订标准当地应急救援单位名称市消防队:119市人民医院:120当地应急救援单位电话消防队:119人民医院:120危险性标志乙酸-3-甲氧基丁酯职业病危害告知卡作业场所存在乙酸-3-甲氧基丁酯,对人体有损害,请注意防护乙酸-3-甲氧基丁酯3-Methoxybutylacetate健康危害理化特性本品对眼睛、粘膜有刺激作用。

溶于水,溶于多数有机溶剂。

遇明火、高热或与氧化剂接触,有引起燃烧爆炸的危险。

应急处理皮肤接触:脱去污染的衣着,用肥皂水及清水彻底冲洗。

眼睛接触:立即翻开上下眼睑,用流动清水冲洗15分钟。

就医。

吸入:脱离现场至空气新鲜处。

就医。

食入:误服者给饮足量温水,催吐,就医。

灭火方法:雾状水、泡沫、二氧化碳、干粉、砂土。