5962F0253502VYC中文资料

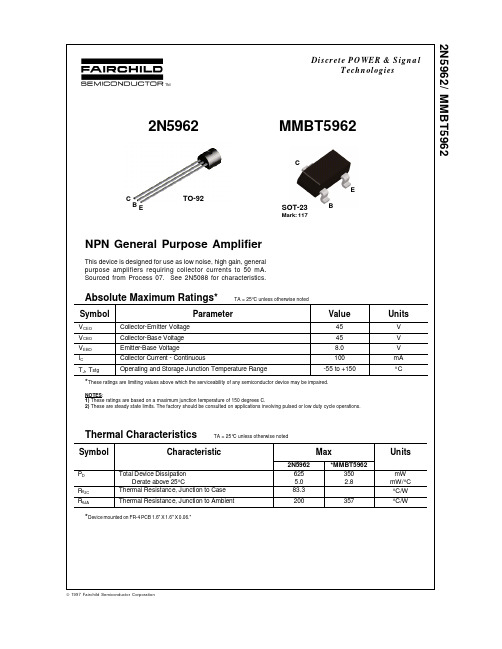

2N5962资料

VCE( sat) VBE( on)

Collector-Emitter Saturation Voltage Base-Emitter On Voltage

1400 0.2 0.7

V V

SMALL SIGNAL CHARACTERISTICS

Ccb Ceb hfe Collector-Base Capacitance Emitter-Base Capacitance Small-Signal Current Gain VCB = 5.0 V VEB = 0.5 V IC = 10 mA, VCE = 5.0 V, f = 1.0 kHz IC = 10 mA, VCE = 5.0 V, f = 100 MHz VCE = 5.0 V, IC = 10 µA, RS = 10 kΩ, f = 1.0 kHz, BW = 400 Hz VCE = 5.0 V, IC = 100 µA, RS = 1.0 kΩ, f = 1.0 kHz, BW = 400 Hz VCE = 5.0 V, IC = 100 µA, RS = 10 kΩ, f = 1.0 kHz, BW = 400 Hz VCE = 5.0 V, IC = 100 µA, RS = 100 kΩ, f = 1.0 kHz, BW = 400 Hz VCE = 5.0 V, IC = 10 µA, RS = 10 kΩ, f = 10 Hz -10 kHz BW = 15.7 kHz 600 1.0 4.0 6.0 200 pF pF

NF

Noise Figure

3.0

dB

6.0

dB

4.0

dB

8.0

dB

3.0

dB

*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

5962-8951105VEA中文资料

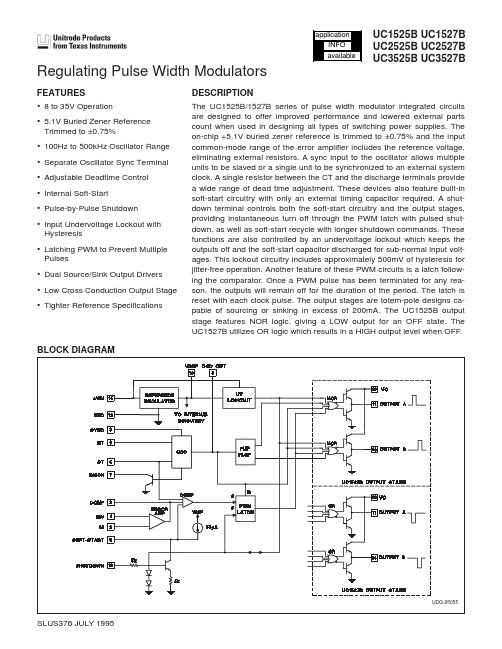

UC1525B UC1527B UC2525B UC2527B UC3525B UC3527BDESCRIPTIONThe UC1525B/1527B series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies.The on-chip +5.1V buried zener reference is trimmed to ±0.75%and the input common-mode range of the error amplifier includes the reference voltage,eliminating external resistors.A sync input to the oscillator allows multiple units to be slaved or a single unit to be synchronized to an external system clock.A single resistor between the CT and the discharge terminals provide a wide range of dead time adjustment.These devices also feature built-in soft-start circuitry with only an external timing capacitor required.A shut-down terminal controls both the soft-start circuitry and the output stages,providing instantaneous turn off through the PWM latch with pulsed shut-down,as well as soft-start recycle with longer shutdown commands.These functions are also controlled by an undervoltage lockout which keeps the outputs off and the soft-start capacitor discharged for sub-normal input volt-ages.This lockout circuitry includes approximately 500mV of hysteresis for jitter-free operation.Another feature of these PWM circuits is a latch follow-ing the comparator.Once a PWM pulse has been terminated for any rea-son,the outputs will remain off for the duration of the period.The latch is reset with each clock pulse.The output stages are totem-pole designs ca-pable of sourcing or sinking in excess of 200mA.The UC1525B output stage features NOR logic,giving a LOW output for an OFF state.The UC1527B utilizes OR logic which results in a HIGH output level when OFF.Regulating Pulse Width ModulatorsFEATURES•8to 35V Operation•5.1V Buried Zener Reference Trimmed to ±0.75%•100Hz to 500kHz Oscillator Range •Separate Oscillator Sync Terminal •Adjustable Deadtime Control •Internal Soft-Start •Pulse-by-Pulse Shutdown •Input Undervoltage Lockout with Hysteresis•Latching PWM to Prevent Multiple Pulses•Dual Source/Sink Output Drivers •Low Cross Conduction Output Stage •Tighter Reference SpecificationsBLOCK DIAGRAMABSOLUTE MAXIMUM RATINGSSupply Voltage,(+VIN)...........................+40V Collector Supply Voltage (VC)......................+40V Logic Inputs ............................–0.3V to +5.5V Analog Inputs.............................–0.3V to VIN Output Current,Source or Sink ...................500mA Reference Output Current ........................50mA Oscillator Charging Current ........................5mA Power Dissipation at T A =+25°C.................1000mW Power Dissipation at T C =+25°C ................2000mW Operating Junction Temperature ..........–55°C to +150°C Storage Temperature Range .............–65°C to +150°C Lead Temperature (Soldering,10sec.).............+300°C All currents are positive into,negative out of the specified ter-minal.Consult Packaging Section of Databook for thermal limi-tations and considerations of packages.RECOMMENDED OPERATING CONDITIONS (Note 1)Input Voltage (+VIN).......................+8V to +35V Collector Supply Voltage (VC)..............+4.5V to +35V Sink/Source Load Current (steady state)........0to 100mA Sink/Source Load Current (peak)..............0to 400mA Reference Load Current ......................0to 20mA Oscillator Frequency Range..............100Hz to 400kHz Oscillator Timing Resistor ..................2k Ωto 150k ΩOscillator Timing Capacitor ..............0.001µF to 0.1µF Dead Time Resistor Range...................0Ωto 500ΩNote 1:Range over which the device is functional and parame-ter limits are guaranteed.ELECTRICAL CHARACTERISTICS:Unless otherwise stated,these specifications apply for T A =–55°C to +125°C for theUC1525B and UC1527B;–40°C to +85°C for the UC2525B and UC2527B;0°C to +70°C for the UC3525B and UC3527B;+VIN =20V,T A =T J .PARAMETERTEST CONDITIONSUC1525B/UC2525B UC1527B/UC2527BUC3525B UC3527B MINTYPMAXMINTYPMAXUNITSReference Section Output Voltage T J =25°C 5.0625.10 5.138 5.0365.10 5.164V Line Regulation VIN =8V to 35V 510510mV Load RegulationI L =0mA to 20mA 715715mV Temperature Stability (Note 2)Over Operating Range 10501050mV Total Output Variation Line,Load,and Temperature 5.0365.164 5.0245.176V Short Circuit CurrentVREF =0,T J =25°C 8010080100mA Output Noise Voltage (Note 2)10Hz ≤f ≤10kHz,T J =25°C 4020040200µVrms Long Term Stability (Note 2)T J =125°C,1000Hrs.310310mVELECTRICAL CHARACTERISTICS:Unless otherwise stated,these specifications apply for T A=–55°C to+125°C for the UC1525B and UC1527B;–40°C to+85°C for the UC2525B and UC2527B;0°C to+70°C for the UC3525B and UC3527B;+VIN= 20V,T A=T J.PARAMETER TEST CONDITIONS UC1525B/UC2525BUC1527B/UC2527BUC3525BUC3527BMIN TYP MAX MIN TYP MAX UNITSOscillator Section(Note3)Initial Accuracy(Notes2&3)T J=25°C±2±6±2±6% Voltage Stability(Notes2&3)VIN=8V to35V±0.3±1±1±2% Temperature Stability(Note2)Over Operating Range±3±6±3±6% Minimum Frequency RT=200k W,CT=0.1m F120120Hz Maximum Frequency RT=2k W,CT=470pF400400kHz Current Mirror I RT=2mA 1.7 2.0 2.2 1.7 2.0 2.2mA Clock Amplitude(Notes2&3) 3.0 3.5 3.0 3.5V Clock Width(Notes2&3)T J=25°C0.30.5 1.00.30.5 1.0m s Sync Threshold 1.2 2.0 2.8 1.2 2.0 2.8V Sync Input Current Sync Voltage=3.5V 1.0 2.5 1.0 2.5mA Error Amplifier Section(VCM=5.1V)Input Offset Voltage0.55210mV Input Bias Current110110m A Input Offset Current11m A DC Open Loop Gain RL³10Meg W60756075dB Gain-Bandwidth Product(Note2)A V=0dB,T J=25°C1212MHz Output Low Level0.20.50.20.5V Output High Level 3.8 5.6 3.8 5.6V Common Mode Rejection V CM=1.5V to5.2V60756075dB Supply Voltage Rejection VIN=8V to35V50605060dB PWM ComparatorMinimum Duty Cycle00% Maximum Duty Cycle(Note3)45494549% Input Threshold(Note3)Zero Duty Cycle0.70.90.70.9V Input Threshold(Note3)Maximum Duty Cycle 3.3 3.6 3.3 3.6V Input Bias Current(Note2)0.05 1.00.05 1.0m A Shutdown SectionSoft Start Current V SHUTDOWN=0V,V SOFTSTART=0V255080255080m A Soft Start Low Level V SHUTDOWN=2.5V0.40.70.40.7V Shutdown Threshold To outputs,V SOFTSTART=5.1V,T J=25°C0.60.8 1.00.60.8 1.0V Shutdown Input Current V SHUTDOWN=2.5V0.4 1.00.4 1.0mA Shutdown Delay(Note2)V SHUTDOWN=2.5V,T J=25°C0.20.50.20.5m s Output Drivers(Each Output)(Vc=20V)Output Low Level I SINK=20mA0.20.40.20.4VI SINK=100mA 1.0 2.0 1.0 2.0V Output HIgh Level I SOURCE=20mA18191819VI SOURCE=100mA17181718V Undervoltage Lockout V COMP and V SOFTSTART=High678678V Collector Leakage VC=35V200200m AELECTRICAL CHARACTERISTICS:Unless otherwise stated,these specifications apply for T A =–55°C to +125°C for theUC1525B and UC1527B;–40°C to +85°C for the UC2525B and UC2527B;0°C to +70°C for the UC3525B and UC3527B;+VIN =20V,T A =T J .PARAMETERTEST CONDITIONS UC1525B/UC2525B UC1527B/UC2527BUC3525B UC3527B MINTYP MAX MINTYPMAXUNITSOutput Drivers (Each Output)(VC =20V)(cont.)Rise Time (Note 2)C L =1nF,T J =25°C 100600100600ns Fall Time (Note 2)C L =1nF,T J =25°C 5030050300ns Cross conduction charge Per cycle,T J =25°C3030ncTotal Standby Current Supply CurrentVIN =35V14201420mANote 2:Ensured by design.Not 100%tested in production.Note 3:Tested at fosc=40kHz (R T =3.6K W ,C T =0.01m F,R D =0W ).Approximate oscillator frequency is defined by:()f C R R T T D =••+1073.PRINCIPLES OF OPERATION AND TYPICAL CHARACTERISTICSPRINCIPLES OF OPERATION AND TYPICAL CHARACTERISTICSShutdown Options(See Block Diagram)Since both the compensation and soft-start terminals (Pins9and8)have current source pull-ups,either can readily accept a pull-down signal which only has to sink a maximum of100µA to turn off the outputs.This is subject to the added requirement of discharging whatever exter-nal capacitance may be attached to these pins.An alternate approach is the use of the shutdown cir-cuitry of Pin10which has been improved to enhance the available shutdown options.Activating this circuit by ap-plying a positive signal on Pin10performs two functions: the PWM latch is immediately set providing the fastest turn-off signal to the external soft-start capacitor.If the shutdown command is short,the PWM signal is termi-nated without significant discharge of the soft-start ca-pacitor,thus,allowing,for example,a convenient implementation of pulse-by-pulse current limiting. Holding Pin10high for a longer duration,however,will ultimately discharge this external capacitor,recycling slow turn-on upon release.LAB TEST FIXTUREPACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-8951105EA ACTIVE CDIP J161TBD A42SNPB Level-NC-NC-NC 5962-8951105V2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-8951105VEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC UC1525BJ ACTIVE CDIP J161TBD A42SNPB Level-NC-NC-NC UC1525BJ883B ACTIVE CDIP J161TBD A42SNPB Level-NC-NC-NC UC1525BJQMLV ACTIVE CDIP J16TBD Call TI Call TIUC1525BLQMLV ACTIVE LCCC FK20TBD Call TI Call TIUC2525BDWTR ACTIVE SOIC DW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC2525BDWTRG4ACTIVE SOIC DW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC3525BDW ACTIVE SOIC DW1640Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC3525BDWTR ACTIVE SOIC DW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC3525BDWTRG4ACTIVE SOIC DW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC3525BN ACTIVE PDIP N1625Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC3525BNG4ACTIVE PDIP N1625Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC3527BN ACTIVE PDIP N1625Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC3527BNG4ACTIVE PDIP N1625Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NC(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

5962-9232501MXA资料

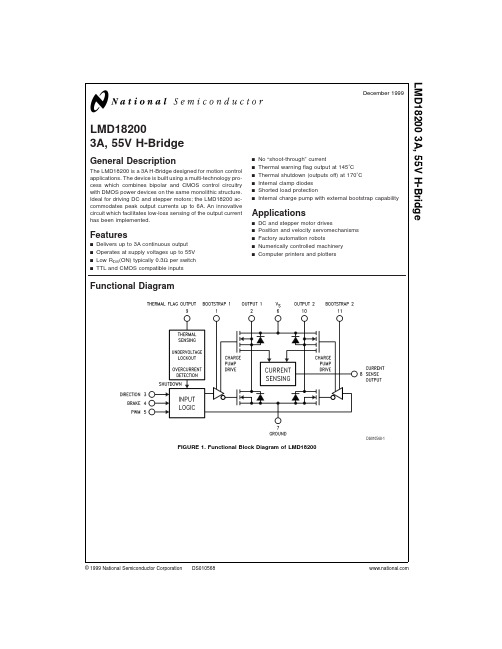

LMD182003A,55V H-BridgeGeneral DescriptionThe LMD18200is a 3A H-Bridge designed for motion control applications.The device is built using a multi-technology pro-cess which combines bipolar and CMOS control circuitry with DMOS power devices on the same monolithic structure.Ideal for driving DC and stepper motors;the LMD18200ac-commodates peak output currents up to 6A.An innovative circuit which facilitates low-loss sensing of the output current has been implemented.Featuresn Delivers up to 3A continuous output n Operates at supply voltages up to 55V n Low R DS (ON)typically 0.3Ωper switch nTTL and CMOS compatible inputsn No “shoot-through”currentn Thermal warning flag output at 145˚C n Thermal shutdown (outputs off)at 170˚C n Internal clamp diodes n Shorted load protectionnInternal charge pump with external bootstrap capabilityApplicationsn DC and stepper motor drivesn Position and velocity servomechanisms n Factory automation robotsn Numerically controlled machinery nComputer printers and plottersFunctional DiagramDS010568-1FIGURE 1.Functional Block Diagram of LMD18200December 1999LMD182003A,55V H-Bridge©1999National Semiconductor Corporation Connection Diagrams and Ordering InformationDS010568-211-Lead TO-220PackageTop ViewOrder Number LMD18200T See NS Package TA11BDS010568-2524-Lead Dual-in-Line PackageTop ViewOrder Number LMD18200-2D-QV5962-9232501VXA LMD18200-2D/8835962-9232501MXA See NS Package DA24BL M D 18200 2Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Total Supply Voltage(V S,Pin6)60V Voltage at Pins3,4,5,8and912V Voltage at Bootstrap Pins(Pins1and11)V OUT+16V Peak Output Current(200ms)6A Continuous Output Current(Note2)3A Power Dissipation(Note3)25W Power Dissipation(T A=25˚C,Free Air)3W Junction Temperature,T J(max)150˚C ESD Susceptibility(Note4)1500V Storage Temperature,T STG−40˚C to+150˚C Lead Temperature(Soldering,10sec.)300˚COperating Ratings(Note1)Junction Temperature,T J−40˚C to+125˚C V S Supply Voltage+12V to+55VElectrical Characteristics(Note5)The following specifications apply for V S=42V,unless otherwise specified.Boldface limits apply over the entire operating temperature range,−40˚C≤T J≤+125˚C,all other limits are for T A=T J=25˚C.Symbol Parameter Conditions Typ Limit UnitsR DS(ON)Switch ON Resistance Output Current=3A(Note6)0.330.4/0.6Ω(max)R DS(ON)Switch ON Resistance Output Current=6A(Note6)0.330.4/0.6Ω(max)V CLAMP Clamp Diode Forward Drop Clamp Current=3A(Note6) 1.2 1.5V(max)V IL Logic Low Input Voltage Pins3,4,5−0.1V(min)0.8V(max)I IL Logic Low Input Current V IN=−0.1V,Pins=3,4,5−10µA(max)V IH Logic High Input Voltage Pins3,4,52V(min)12V(max)I IH Logic High Input Current V IN=12V,Pins=3,4,510µA(max)Current Sense Output I OUT=1A(Note8)377325/300µA(min)425/450µA(max) Current Sense Linearity1A≤I OUT≤3A(Note7)±6±9%Undervoltage Lockout Outputs turn OFF9V(min)11V(max)T JW Warning Flag Temperature Pin9≤0.8V,I L=2mA145˚CV F(ON)Flag Output Saturation Voltage T J=T JW,I L=2mA0.15VI F(OFF)Flag Output Leakage V F=12V0.210µA(max)T JSD Shutdown Temperature Outputs Turn OFF170˚CI S Quiescent Supply Current All Logic Inputs Low1325mA(max)t Don Output Turn-On Delay Time Sourcing Outputs,I OUT=3A300nsSinking Outputs,I OUT=3A300nst on Output Turn-On Switching Time Bootstrap Capacitor=10nFSourcing Outputs,I OUT=3A100nsSinking Outputs,I OUT=3A80nst Doff Output Turn-Off Delay Times Sourcing Outputs,I OUT=3A200nsSinking Outputs,I OUT=3A200nst off Output Turn-Off Switching Times Bootstrap Capacitor=10nFSourcing Outputs,I OUT=3A75nsSinking Outputs,I OUT=3A70nst pw Minimum Input Pulse Width Pins3,4and51µst cpr Charge Pump Rise Time No Bootstrap Capacitor20µsLMD182003Electrical Characteristics NotesNote 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do not apply when op-erating the device beyond its rated operating conditions.Note 2:See Application Information for details regarding current limiting.Note 3:The maximum power dissipation must be derated at elevated temperatures and is a function of T J(max),θJA ,and T A .The maximum allowable power dis-sipation at any temperature is P D(max)=(T J(max)−T A )/θJA ,or the number given in the Absolute Ratings,whichever is lower.The typical thermal resistance from junc-tion to case (θJC )is 1.0˚C/W and from junction to ambient (θJA )is 30˚C/W.For guaranteed operation T J(max)=125˚C.Note 4:Human-body model,100pF discharged through a 1.5k Ωresistor.Except Bootstrap pins (pins 1and 11)which are protected to 1000V of ESD.Note 5:All limits are 100%production tested at 25˚C.Temperature extreme limits are guaranteed via correlation using accepted SQC (Statistical Quality Control)methods.All limits are used to calculate AOQL,(Average Outgoing Quality Level).Note 6:Output currents are pulsed (t W <2ms,Duty Cycle <5%).Note 7:Regulation is calculated relative to the current sense output value with a 1A load.Note 8:Selections for tighter tolerance are available.Contact factory.Typical Performance CharacteristicsV SAT vs Flag CurrentDS010568-16R DS (ON)vs TemperatureDS010568-17R DS (ON)vs Supply VoltageDS010568-18Supply Current vs Supply VoltageDS010568-19Supply Current vs Frequency (V S =42V)DS010568-20Supply Current vsTemperature (V S =42V)DS010568-21Current Sense Output vs Load Current DS010568-22Current Sense Operating RegionDS010568-23L M D 18200 4Test CircuitSwitching Time DefinitionsPinout Description(See Connection Diagram) Pin1,BOOTSTRAP1Input:Bootstrap capacitor pin for half H-bridge number1.The recommended capacitor(10nF)is connected between pins1and2.Pin2,OUTPUT1:Half H-bridge number1output.Pin3,DIRECTION Input:See Table1.This input controls the direction of current flow between OUTPUT1and OUT-PUT2(pins2and10)and,therefore,the direction of rotation of a motor load.Pin4,BRAKE Input:See Table1.This input is used to brake a motor by effectively shorting its terminals.When braking is desired,this input is taken to a logic high level andit is also necessary to apply logic high to PWM input,pin5.The drivers that short the motor are determined by the logiclevel at the DIRECTION input(Pin3):with Pin3logic high,both current sourcing output transistors are ON;with Pin3logic low,both current sinking output transistors are ON.Alloutput transistors can be turned OFF by applying a logic highto Pin4and a logic low to PWM input Pin5;in this case onlya small bias current(approximately−1.5mA)exists at eachoutput pin.Pin5,PWM Input:See Table1.How this input(and DIREC-TION input,Pin3)is used is determined by the format of thePWM Signal.DS010568-8DS010568-9LMD182005Pinout Description(See Connection Diagram)(Continued)Pin 6,V S Power SupplyPin 7,GROUND Connection:This pin is the ground return,and is internally connected to the mounting tab.Pin 8,CURRENT SENSE Output:This pin provides the sourcing current sensing output signal,which is typically 377µA/A.Pin 9,THERMAL FLAG Output:This pin provides the ther-mal warning flag output signal.Pin 9becomes active-low at 145˚C (junction temperature).However the chip will not shut itself down until 170˚C is reached at the junction.Pin 10,OUTPUT 2:Half H-bridge number 2output.Pin 11,BOOTSTRAP 2Input:Bootstrap capacitor pin for Half H-bridge number 2.The recommended capacitor (10nF)is connected between pins 10and 11.TABLE 1.Logic Truth TablePWM Dir Brake Active Output Drivers H H L Source 1,Sink 2H L L Sink 1,Source 2L X L Source 1,Source 2H H H Source 1,Source 2H L H Sink 1,Sink 2LXHNONEApplication InformationTYPES OF PWM SIGNALSThe LMD18200readily interfaces with different forms of PWM e of the part with two of the more popular forms of PWM is described in the following paragraphs.Simple,locked anti-phase PWM consists of a single,vari-able duty-cycle signal in which is encoded both direction and amplitude information (see Figure 2).A 50%duty-cycle PWM signal represents zero drive,since the net value of voltage (integrated over one period)delivered to the load is zero.For the LMD18200,the PWM signal drives the direc-tion input (pin 3)and the PWM input (pin 5)is tied to logic high.Sign/magnitude PWM consists of separate direction (sign)and amplitude (magnitude)signals (see Figure 3).The (ab-solute)magnitude signal is duty-cycle modulated,and the absence of a pulse signal (a continuous logic low level)rep-resents zero drive.Current delivered to the load is propor-tional to pulse width.For the LMD18200,the DIRECTION in-put (pin 3)is driven by the sign signal and the PWM input (pin 5)is driven by the magnitude signal.SIGNAL TRANSITION REQUIREMENTSTo ensure proper internal logic performance,it is good prac-tice to avoid aligning the falling and rising edges of input sig-nals.A delay of at least 1µsec should be incorporated be-tween transitions of the Direction,Brake,and/or PWM input signals.A conservative approach is be sure there is at least 500ns delay between the end of the first transition and the beginning of the second transition.See Figure 4.DS010568-4FIGURE 2.Locked Anti-Phase PWM Control DS010568-5FIGURE 3.Sign/Magnitude PWM ControlL M D 18200 6Application Information(Continued)USING THE CURRENT SENSE OUTPUTThe CURRENT SENSE output(pin8)has a sensitivity of 377µA per ampere of output current.For optimal accuracy and linearity of this signal,the value of voltage generating re-sistor between pin8and ground should be chosen to limit the maximum voltage developed at pin8to5V,or less.The maximum voltage compliance is12V.It should be noted that the recirculating currents(free wheel-ing currents)are ignored by the current sense circuitry. Therefore,only the currents in the upper sourcing outputs are sensed.USING THE THERMAL WARNING FLAGThe THERMAL FLAG output(pin9)is an open collector tran-sistor.This permits a wired OR connection of thermal warn-ing flag outputs from multiple LMD18200’s,and allows the user to set the logic high level of the output signal swing to match system requirements.This output typically drives the interrupt input of a system controller.The interrupt service routine would then be designed to take appropriate steps, such as reducing load currents or initiating an orderly system shutdown.The maximum voltage compliance on the flag pin is12V.SUPPLY BYPASSINGDuring switching transitions the levels of fast current changes experienced may cause troublesome voltage tran-sients across system stray inductance.It is normally necessary to bypass the supply rail with a high quality capacitor(s)connected as close as possible to the V S Power Supply(Pin6)and GROUND(Pin7).A1µF high-frequency ceramic capacitor is recommended.Care should be taken to limit the transients on the supply pin be-low the Absolute Maximum Rating of the device.When oper-ating the chip at supply voltages above40V a voltage sup-pressor(transorb)such as P6KE62A is recommended from supply to ground.Typically the ceramic capacitor can be eliminated in the presence of the voltage suppressor.Note that when driving high load currents a greater amount of sup-ply bypass capacitance(in general at least100µF per Ampof load current)is required to absorb the recirculating cur-rents of the inductive loads.CURRENT LIMITINGCurrent limiting protection circuitry has been incorporatedinto the design of the LMD18200.With any power device it isimportant to consider the effects of the substantial surge cur-rents through the device that may occur as a result ofshorted loads.The protection circuitry monitors this increasein current(the threshold is set to approximately10Amps)and shuts off the power device as quickly as possible in theevent of an overload condition.In a typical motor driving ap-plication the most common overload faults are caused byshorted motor windings and locked rotors.Under these con-ditions the inductance of the motor(as well as any series in-ductance in the V CC supply line)serves to reduce the mag-nitude of a current surge to a safe level for the LMD18200.Once the device is shut down,the control circuitry will peri-odically try to turn the power device back on.This feature al-lows the immediate return to normal operation in the eventthat the fault condition has been removed.While the fault re-mains however,the device will cycle in and out of thermalshutdown.This can create voltage transients on the V CCsupply line and therefore proper supply bypassing tech-niques are required.The most severe condition for any power device is a direct,hard-wired(“screwdriver”)long term short from an output toground.This condition can generate a surge of currentthrough the power device on the order of15Amps and re-quire the die and package to dissipate up to500Watts ofpower for the short time required for the protection circuitryto shut off the power device.This energy can be destructive,particularly at higher operating voltages(>30V)so some precautions are in order.Proper heat sink design is essentialand it is normally necessary to heat sink the V CC supply pin(pin6)with1square inch of copper on the PCB.DS010568-24FIGURE4.Transitions in Brake,Direction,or PWM Must Be Separated By At Least1µsecLMD182007Application Information(Continued)INTERNAL CHARGE PUMP AND USE OF BOOTSTRAP CAPACITORSTo turn on the high-side (sourcing)DMOS power devices,the gate of each device must be driven approximately 8V more positive than the supply voltage.To achieve this an in-ternal charge pump is used to provide the gate drive voltage.As shown in Figure 5,an internal capacitor is alternately switched to ground and charged to about 14V,then switched to V supply thereby providing a gate drive voltage greater than V supply.This switching action is controlled by a con-tinuously running internal 300kHz oscillator.The rise time of this drive voltage is typically 20µs which is suitable for oper-ating frequencies up to 1kHz.For higher switching frequencies,the LMD18200provides for the use of external bootstrap capacitors.The bootstrap principle is in essence a second charge pump whereby a large value capacitor is used which has enough energy to quickly charge the parasitic gate input capacitance of the power device resulting in much faster rise times.The switch-ing action is accomplished by the power switches them-selves Figure 6.External 10nF capacitors,connected from the outputs to the bootstrap pins of each high-side switch provide typically less than 100ns rise times allowing switch-ing frequencies up to 500kHz.INTERNAL PROTECTION DIODESA major consideration when switching current through induc-tive loads is protection of the switching power devices from the large voltage transients that occur.Each of the four switches in the LMD18200have a built-in protection diode to clamp transient voltages exceeding the positive supply or ground to a safe diode voltage drop across the switch.The reverse recovery characteristics of these diodes,once the transient has subsided,is important.These diodes must come out of conduction quickly and the power switches must be able to conduct the additional reverse recovery current of the diodes.The reverse recovery time of the diodes protect-ing the sourcing power devices is typically only 70ns with a reverse recovery current of 1A when tested with a full 6A of forward current through the diode.For the sinking devices the recovery time is typically 100ns with 4A of reverse cur-rent under the same conditions.Typical ApplicationsFIXED OFF-TIME CONTROLThis circuit controls the current through the motor by apply-ing an average voltage equal to zero to the motor terminals for a fixed period of time,whenever the current through the motor exceeds the commanded current.This action causesthe motor current to vary slightly about an externally con-trolled average level.The duration of the Off-period is ad-justed by the resistor and capacitor combination of the LM555.In this circuit the Sign/Magnitude mode of operation is implemented (see Types of PWM Signals).DS010568-6FIGURE 5.Internal Charge Pump CircuitryDS010568-7FIGURE 6.Bootstrap CircuitryL M D 18200 8Typical Applications(Continued)TORQUE REGULATIONLocked Anti-Phase Control of a brushed DC motor.Current sense output of the LMD18200provides load sensing.The LM3525A is a general purpose PWM controller.The relationship of peak motor current to adjustment voltage is shown in Figure 10.DS010568-10FIGURE 7.Fixed Off-Time ControlDS010568-11FIGURE 8.Switching WaveformsLMD182009Typical Applications(Continued)VELOCITY REGULATIONUtilizes tachometer output from the motor to sense motor speed for a locked anti-phase control loop.The relationship of motor speed to the speed adjustment control voltage is shown in Figure 12.DS010568-12FIGURE 9.Locked Anti-Phase Control Regulates TorqueDS010568-13FIGURE 10.Peak Motor Currentvs Adjustment VoltageL M D 18200 10Typical Applications(Continued)DS010568-14FIGURE 11.Regulate Velocity with Tachometer FeedbackDS010568-15FIGURE 12.Motor Speed vsControl VoltageLMD1820011Physical Dimensionsinches (millimeters)unless otherwise noted11-Lead TO-220Power Package (T)Order Number LMD18200T NS Package Number TA11BL M D 18200 12Physical Dimensions inches(millimeters)unless otherwise noted(Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implantinto the body,or(b)support or sustain life,andwhose failure to perform when properly used inaccordance with instructions for use provided in thelabeling,can be reasonably expected to result in asignificant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to performcan be reasonably expected to cause the failure ofthe life support device or system,or to affect itssafety or effectiveness.National SemiconductorCorporationAmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National SemiconductorEuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National SemiconductorAsia Pacific CustomerResponse GroupTel:65-2544466Fax:65-2504466Email:sea.support@National SemiconductorJapan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507 24-Lead Dual-in-Line PackageOrder Number LMD18200-2D-QV5962-9232501VXALMD18200-2D/8835962-9232501MXANS Package Number DA24BLMD182003A,55VH-Bridge National does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

5962-8405601VDA中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-8405601VCA ACTIVE CDIP J141None Call TI Level-NC-NC-NC 5962-8405601VDA ACTIVE CFP W141None Call TI Level-NC-NC-NC 84056012A ACTIVE LCCC FK201None Call TI Level-NC-NC-NC 8405601CA ACTIVE CDIP J141None Call TI Level-NC-NC-NC 8405601DA ACTIVE CFP W141None Call TI Level-NC-NC-NC JM38510/65302B2A ACTIVE LCCC FK201None Call TI Level-NC-NC-NC JM38510/65302BCA ACTIVE CDIP J141None Call TI Level-NC-NC-NC JM38510/65302BDA ACTIVE CFP W141None Call TI Level-NC-NC-NC SN54HC74J ACTIVE CDIP J141None Call TI Level-NC-NC-NC SN74HC74ADBLE OBSOLETE SSOP DB14None Call TI Call TISN74HC74D ACTIVE SOIC D1450Pb-Free(RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIMSN74HC74DBLE OBSOLETE SSOP DB14None Call TI Call TISN74HC74DBR ACTIVE SSOP DB142000Pb-Free(RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIMSN74HC74DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC74DT ACTIVE SOIC D14250Pb-Free(RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIMSN74HC74N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74HC74N3OBSOLETE PDIP N14None Call TI Call TISN74HC74NSR ACTIVE SO NS142000Pb-Free(RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIMSN74HC74PW ACTIVE TSSOP PW1490Pb-Free(RoHS)CU NIPDAU Level-1-250C-UNLIMSN74HC74PWLE OBSOLETE TSSOP PW14None Call TI Call TISN74HC74PWR ACTIVE TSSOP PW142000Pb-Free(RoHS)CU NIPDAU Level-1-250C-UNLIMSN74HC74PWT ACTIVE TSSOP PW14250Pb-Free(RoHS)CU NIPDAU Level-1-250C-UNLIM SNJ54HC74FK ACTIVE LCCC FK201None Call TI Level-NC-NC-NC SNJ54HC74J ACTIVE CDIP J141None Call TI Level-NC-NC-NC SNJ54HC74W ACTIVE CFP W141None Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-May not be currently available-please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead(Pb-Free).Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean"Pb-Free"and in addition,uses package materials that do not contain halogens, including bromine(Br)or antimony(Sb)above0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

5962-0053901QYA中文资料

Copyright 2002, Texas Instruments Incorporated

On products compliant to MIL−PRF−38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

元器件交易网

SM320VC33, SMJ320VC33 DIGITAL SIGNAL PROCESSOR

SGUS034E - FEBRUARY 2001 - REVISED OCTOBER 2002

D High-Performance Floating-Point Digital

Signal Processor (DSP): - SM/SMJ320VC33-150 - 13-ns Instruction Cycle Time - 150 Million Floating-Point Operations Per Second (MFLOPS) - 75 Million Instructions Per Second (MIPS) 34K × 32-Bit (1.1-Mbit) On-Chip Words of Dual-Access Static Random-Access Memory (SRAM) Configured in 2 × 16K plus 2 × 1K Blocks to improve Internal Performance Generator Very Low Power: < 200 mW @ 150 MFLOPS 32-Bit High-Performance CPU 16-/32-Bit Integer and 32-/40-Bit Floating-Point Operations Four Internally Decoded Page Strobes to Simplify Interface to I/O and Memory Devices Boot-Program Loader EDGEMODE Selectable External Interrupts 32-Bit Instruction Word, 24-Bit Addresses Eight Extended-Precision Registers Fabricated Using the 0.18-µm (leff-Effective Gate Length) TImeline Technology by Texas Instruments (TI)

5962-89957012A中文资料

The UC1637 is a pulse width modulator circuit intended to be used for a variety of PWM motor drive and amplifier applications requiring either uni-directional or bi-directional drive circuits. When used to replace conventional drivers, this circuit can increase efficiency and reduce component costs for many applications. All necessary circuitry is included to generate an analog error signal and modulate two bi-directional pulse train outputs in proportion to the error signal magnitude and polarity.This monolithic device contains a sawtooth oscillator, error amplifier, and two PWM comparators with ±100mA output stages as standard features. Protection circuitry includes under-voltage lockout, pulse-by-pulse current limiting, and a shutdown port with a 2.5V temperature compensated threshold.The UC1637 is characterized for operation over the full military temperature range of -55°C to +125°C, while the UC2637 and UC3637 are characterized for -25°C to +85°C and 0°C to +70°C, respectively.Switched Mode Controller for DC Motor DriveUC2637UC3637BLOCK DIAGRAM•Single or Dual Supply Operation•±2.5V to ±20V Input Supply Range•±5% Initial Oscillator Accuracy; ± 10% Over Temperature•Pulse-by-Pulse Current Limiting•Under-Voltage Lockout •Shutdown Input withTemperature Compensated 2.5V Threshold •Uncommitted PWM Comparators for Design Flexibility•Dual 100mA, Source/Sink Output DriversSupply Voltage (±Vs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20V Output Current, Source/Sink (Pins 4, 7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500mA Analog Inputs (Pins 1, 2, 3, 8, 9, 10, 11 12, 13, 14, 15, 16). . . . . . . . . . . . . . . . . . . . . . . ±Vs Error Amplifier Output Current (Pin 17). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20mA Oscillator Charging Current (Pin 18). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -2mA Power Dissipation at T A = 25°C (Note 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000mW Power Dissipation at T C = 25°C (Note 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2000mW Storage Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -65°C to +150°C Lead Temperature (Soldering, 10 Seconds). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +300°C Note 1:Currents are positive into, negative out of the specified terminal.Note 2: Consult Packaging Section of Databook for thermal limitations and considerationsof package.FEATURESABSOLUTE MAXIMUM RATINGS (Note 1)DESCRIPTIONUC3637PACKAGE PIN FUNCTION FUNCTION PIN+V TH 1C T 2-V TH 3A OUT 4-V S 5N/C 6+V S 7B OUT 8+B IN 9-B IN 10-A IN 11+A IN 12+C/L 13-C/L14SHUTDOWN 15N/C 16+E/A 17-E/A18E/A OUTPUT 19I SET 20PLCC-20, LCC-20(TOP VIEW) Q, L PackagesELECTRICAL CHARACTERISTICS:PARAMETERTEST CONDITIONSUC1637/UC2637UC3637UNITSMINTYPMAXMINTYPMAXOscillator Initial Accuracy T J = 25°C (Note 6)9.41010.691011kHz Voltage Stability V S = ±5V to ±20V, V PIN 1 = 3V, V PIN 3 = -3V5757%Temperature Stability Over Operating Range (Note 3)0.520.52%+V TH Input Bias Current V PIN 2 = 6V -100.110-100.110µA -V TH Input Bias Current V PIN 2 = 0V-10-0.5-10-0.5µA +V TH, -V TH Input Range +V S -2-V S +2+V S -2-V S +2VError Amplifier Input Offset Voltage V CM = 0V 1.55 1.510mV Input Bias Current V CM = 0V 0.550.55µA Input Offset Current V CM = 0V0.110.11µA Common Mode Range V S = ±2.5 to 20V -V S +2+V S-V S +2+V SV Open Loop Voltage Gain R L = 10k7510080100dB Slew Rate1515V/µS Unity Gain Bandwidth 22MHz CONNECTION DIAGRAMUnless otherwise stated, these specifications apply for T A = -55°C to +125°C for theUC1637; -25°C to +85°C for the UC2637; and 0°C to +70°C for the UC3637; +V S =+15V, -V S = - 15V, +V TH = 5V, -V TH = -5V, R T = 16.7k Ω, C T = 1500pF, T A =T J.DIL-18 (TOP VIEW)J or N PackageSOIC-20 (TOP VIEW) DW PackageELECTRICAL CHARACTERISTICS:PARAMETERS TEST CONDITIONS UC1637/UC2637UC3637UNITSMIN TYP MAX MIN TYP MAXError Amplifier (Continued)Output Sink Current V PIN 17 = 0V-50-20-50-20mA Output Source Current V PIN 17 = 0V511511mA High Level Output Voltage1313.61313.6V Low Level Output Voltage-14.8-13-14.8-13V PWM ComparatorsInput Offset Voltage V CM = 0V2020mV Input Bias Current V CM = 0V210210µA Input Hysteresis V CM = 0V1010mV Common Mode range V S = ±5V to ±20V-V S+1+V S-2-V S+1+V S-2V Current LimitInput Offset Voltage V CM = 0V, T J = 25°C190200210180200220mV Input Offset Voltage T.C.-0.2-0.2mV/°C Input Bias Current-10-1.5-10-1.5µA Common Mode Range V S = ±2.5V to ±20V-V S+V S-3-V S+V S-3V ShutdownShutdown Threshold(Note 4)-2.3-2.5-2.7-2.3-2.5-2.7V Hysteresis4040mV Input Bias Current V PIN 14 = +V S to -V S-10-0.5-10-0.5µA Under-Voltage LockoutStart Threshold(Note 5) 4.15 5.0 4.15 5.0V Hysteresis0.250.25mV Total Standby CurrentSupply Current8.5158.515mA Output SectionOutput Low Level I SINK = 20mA-14.9-13-14.9-13VI SINK = 100mA-14.5-13-14.5-13Output High Level I SOURCE = 20mA1313.51313.5VI SOURCE = 100mA1213.51213.5Rise Time(Note 3) C L = Inf, T J = 25°C100600100600ns Fall Time(Note 3) C L = Inf, T J = 25°C100300100300ns Note 3:These parameters, although guaranteed over the recommended operating conditions, are not 100% tested in production. Note 4:Parameter measured with respect to +V S (Pin 6).Note 5:Parameter measured at +V S (Pin 6) with respect to -V S (Pin 5).Note 6:R T and C T referenced to Ground.FUNCTIONAL DESCRIPTIONFollowing is a description of each of the functional blocks shown in the Block Diagram.OscillatorThe oscillator consists of two comparators, a charging and discharging current source, a current source set ter-minal, l SET and a flip-flop. The upper and lower threshold minal voltage is buffered internally and also applied to the l SET terminal to develop the capacitor charging current through R T. If R T is referenced to -V S as shown in Figure 1, both the threshold voltage and charging current will vary proportionally to the supply differential, and the oscil-lator frequency will remain constant. The triangle wave-Unless otherwise stated, these specifications apply for T A = -55°C to +125°C for the UC1637; -25°C to +85°C for the UC2637; and 0°C to +70°C for the UC3637: V S = +15V, -V S = - 15V, +V TH = 5V, -V TH = -5V, R T = 16.7kΩ, C T = 1500pF, T A=T J.MODULATION SCHEMESCase A Zero Deadtime (Equal voltage on Pin 9 and Pin 11)In this configuration, maximum holding torque or stiffness and position accuracy is achieved. However, the power in-put into the motor is increased. Figure 3A shows this con-figuration.Case B Small Deadtime (Voltage on Pin 9 > Pin 11)A small differential voltage between Pin 9 and 11 provides the necessary time delay to reduce the chances of mo-mentary short circuit in the output stage during transi-tions, especially where power-amplifiers are used. Refer to Figure 3B.Case C Increased Deadtime and Deadband Mode (Voltage on Pin 9 > Pin 11)With the reduction of stiffness and position accuracy, the power input into the motor around the null point of the servo loop can be reduced or eliminated by widening the window of the comparator circuit to a degree of accep-tance. Where position accuracy and mechanical stiffness is unimportant, deadband operation can be used. This is PWM ComparatorsT wo comparators are provided to perform pulse width modulation for each of the output drivers. Inputs are un-committed to allow maximum flexibility. The pulse width of the outputs A and B is a function of the sign and ampli-tude of the error signal. A negative signal at Pin 10 and 8will lengthen the high state of output A and shorten the high state of output B. Likewise, a positive error signal re-verses the procedure. T ypically, the oscillator waveform is compared against the summation of the error signal andthe level set on Pin 9 and 11.Figure 1.Oscillator SetupFigure 2. Comparator BiasingOutput DriversEach output driver is capable of both sourcing and sinking 100mA steady state and up to 500mA on a pulsed basis for rapid switching of either POWERFET or bipolar tran-sistors. Output levels are typically -V S + 0.2V @50mA low level and +V S - 2.0V @50mA high level.Error AmplifierThe error amplifier consists of a high slew rate (15V/µs)op-amp with a typical 1MHz bandwidth and low output im-pedance. Depending on the ±V S supply voltage, the com-mon mode input range and the voltage output swing is within 2V of the V S supply.Under-Voltage LockoutAn under-voltage lockout circuit holds the outputs in the low state until a minimum of 4V is reached. At this point,all internal circuitry is functional and the output drivers are enabled. If external circuitry requires a higher starting volt-age, an over-riding voltage can be programmed through the shutdown terminal as shown in Figure 4.Figure 3.Modulation Schemes Showing (A) Zero Deadtime (B) Deadtime and (C) Deadband ConfigurationsShutdown ComparatorThe shutdown terminal may be used for implementingvarious shutdown and protection schemes. By pulling theterminal more than 2.5V below V IN, the output drivers willbe enabled. This can be realized using an open collectorgate or NPN transistor biased to either ground or thenegative supply. Since the threshold is temperature stabi-lized, the comparator can be used as an accurate lowvoltage lockout (Figure 4) and/or delayed start as in Fig-ure 5. In the shutdown mode the outputs are held in thelow state.Current LimitA latched current limit amplifier with an internal 200mV-V S to within 3V of the +V S supply while providing excel-lent noise rejection. Figure 6 shows a typical currentsense circuit.Figure 4.External Under-Voltage LockoutFigure 5.Delayed Start-UpFigure 7. Bi-Directional Motor Drive with Speed Control Power-AmplifierFigure 8.Single Supply Position Servo Motor DrivePACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-89957012A ACTIVE LCCC FK201TBD POST-PLATE Level-NC-NC-NC 5962-8995701VA ACTIVE CDIP J181TBD A42SNPB Level-NC-NC-NC UC1637J ACTIVE CDIP J181TBD A42SNPB Level-NC-NC-NC UC1637J883B ACTIVE CDIP J181TBD A42SNPB Level-NC-NC-NC UC1637L ACTIVE LCCC FK201TBD POST-PLATE Level-NC-NC-NC UC1637L883B ACTIVE LCCC FK201TBD POST-PLATE Level-NC-NC-NCUC2637DW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC2637DWG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC2637DWTR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEAR UC2637J ACTIVE CDIP J181TBD A42SNPB Level-NC-NC-NCUC2637N ACTIVE PDIP N1820Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC2637NG4ACTIVE PDIP N1820Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC2637Q ACTIVE PLCC FN2046Green(RoHS&no Sb/Br)CU SN Level-2-260C-1YEARUC2637QTR ACTIVE PLCC FN201000Green(RoHS&no Sb/Br)CU SN Level-2-260C-1YEARUC3637DW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC3637DWTR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEARUC3637DWTRG4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-2-260C-1YEAR UC3637J ACTIVE CDIP J181TBD A42SNPB Level-NC-NC-NCUC3637N ACTIVE PDIP N1820Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC3637NG4ACTIVE PDIP N1820Green(RoHS&no Sb/Br)CU NIPDAU Level-NC-NC-NCUC3637Q ACTIVE PLCC FN2046Green(RoHS&no Sb/Br)CU SN Level-2-260C-1YEAR(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

lm596中文资料

LM2596开关电压调节器LM2596开关电压调节器是降压型电源管理单片集成电路,能够输出3A的驱动电流,同时具有很好的线性和负载调节特性。

固定输出版本有3.3V、5V、12V,可调版本可以输出小于37V的各种电压。

该器件内部集成频率补偿和固定频率发生器,开关频率为150KHz,与低频开关调节器相比较,可以使用更小规格的滤波元件。

由于该器件只需4个外接元件,可以使用通用的标准电感,这更优化了LM2596的使用,极大地简化了开关电源电路的设计。

其封装形式包括标准的5脚TO-220封装(DIP)和5脚TO-263表贴封装(SMD)。

该器件还有其他一些特点:在特定的输入电压和输出负载的条件下,输出电压的误差可以保证在±4%的范围内,振荡频率误差在±15%的范围内;可以用仅80μA的待机电流,实现外部断电;具有自我保护电路(一个两级降频限流保护和一个在异常情况下断电的过温完全保护电路)特点Ć 3.3V、5V、12V的固定电压输出和可调电压输出Ć可调输出电压范围1.2V~37V±4%Ć输出线性好且负载可调节Ć输出电流可高达3AĆ输入电压可高达40VĆ采用150KHz的内部振荡频率,属于第二代开关电压调节器,功耗小、效率高Ć低功耗待机模式,I Q的典型值为80μAĆTTL断电能力Ć具有过热保护和限流保护功能Ć封装形式:TO-220(T)和TO-263(S)Ć外围电路简单,仅需4个外接元件,且使用容易购买的标准电感应用领域Ć高效率降压调节器Ć单片开关电压调节器Ć正、负电压转换器典型应用(固定输出)LM2596□-5.0管脚图极限参数名称范围单位最大电源电压45V 脚输入电压-0.3~25V “反馈”脚电压-0.3~25V 到地的输出电压(静态)-1V 功耗由内部限定--储存温度-65~150℃静电释放(人体放电1)2000V 气流焊(60秒)215℃TO-263红外线焊接(10秒)245℃焊接时的管脚温度TO-220波峰焊/电烙铁焊接(10秒)260℃最高结温150℃温度范围-40~125℃工作条件电源电压4.5~40V注1:人体放电模式相当于一个100PF 的电容通过一个1.5K 的电阻向每个管脚放电。

5962-0052201HXC中文资料

1Size (max.): 1.075 x 1.075 x 0.270 inches (27.31 x 27.31 x 6.86 mm)Weight:15 grams maximum.Screening: Standard, ES, or 883 (Class H).DESCRIPTIONThe MSA Series™of high frequency DC/DC converters offers a new standard of performance for low power, military/aerospace grade DC/DC converters. MSA parts provide up to 5 watts output power over the full military temperature range with up to 76% efficiency.Thick-film hybrid techniques provide military/aerospace reliability levels and optimum miniaturization. The hermetically sealed case is only 1.075 by 1.075 inches — with a height of only 0.270 inches.Power density for the MSA Series parts is 16 watts per cubic inch.The MSA Series’small size, low height, and hermetically sealed metal enclosures make them ideal for use in military, aerospace and other high reliability applications. Units are available with standard,screening, “ES”, and fully compliant SMD “883” screening. See page 8 for screening options and descriptions.C ONVERTERD ESIGNThe MSA converters are switching regulators that use a flyback converter design with a constant switching frequency of 550 kHz.They are regulated, isolated units using a pulse width modulated topology and built as high reliability thick-film hybrids. Isolation between input and output circuits is provided with a transformer in the forward power path and an optical link in the feedback control loop. Excellent input line transient response and audio rejection is achieved by an advanced feed-forward compensation technique.Negative output regulation is maintained by tightly coupled magnetics. Up to 4 watts, 80% of the total output power, is available from either output, provided that the opposite output is simultane-ously carrying 20% of the total power. Each output must carry a minimum of 20% of the total output power in order to maintain spec-ified regulation on the negative output. Predictable current limit is accomplished by direct monitoring of the output load current, which results in a constant current output above the overload point.Internal input and output filters eliminate the need for external capacitors.W IDE V OLTAGE R ANGEThe MSA converters are designed to provide full power operation over a full 16 to 40 VDC voltage range. Operation below 16 volts,including MIL-STD-704E emergency power conditions is possible with derated power. Please refer to the low line dropout graphs (Figures 17 and 18) for details. A low voltage lockout feature keeps the converter shutdown below approximately 13 VDC to ensure smooth initialization.I MPROVED D YNAMIC R ESPONSEThe MSA feed-forward compensation system provides excellent dynamic response and noise rejection. Audio rejection is typically 50dB. The minimum to maximum step line transient response is typi-cally less than 1%.I NHIBIT F UNCTIONMSA converters provide a TTL open collector-compatible inhibit feature that can be used to disable internal switching and inhibit the unit’s output. Inhibiting in this manner results in low standby current,and no generation of switching noise.The converter is inhibited when the TTL compatible low (≤0.8 V) is applied to the inhibit pin. The unit is enabled when the pin, which is internally connected to a pull-up resistor, is left unconnected or is connected to an open collector gate. The open circuit output voltage associated with the inhibit pin is 9 to 11 V. In the inhibit mode, a maximum of 4 mA must be sunk from the inhibit pin.U NDERVOLTAGE L OCKOUT AND T RANSIENT P ROTECTIONUndervoltage lockout helps keep system current levels low during initialization or re-start operations. They can withstand short term transients of up to 50 volts without damage.MSA SERIES5 WATTF EATURES•–55°to +125°C operation •16 to 40 VDC input •Fully isolated•Optocoupler feedback•Fixed frequency, 550 kHz typical (400 kHz typ. 60 V output model)•Topology – Flyback••Inhibit function•Indefinite short circuit protection •Up to 76% efficiency, 16 W/in 3RECOMMENDED OPERATING CONDITIONSTYPICAL CHARACTERISTICSINHIBITABSOLUTE MAXIMUM RATINGSInput Voltage •16 to 40 V Output Power •5 wattsLead Soldering Temperature (10 sec per lead)•300°CStorage Temperature Range (Case)•–65°C to +135°C2MSA SERIES 5 WATTDC/DC C ONVERTERSOutput Voltage Temperature Coefficient •100 ppm/°C typicalInput to Output Capacitance •50 pF typical Isolation•100 megohm minimum at 500 V Audio Rejection •50 dB typicalConversion Frequency•550 kHz typical (400 kHz 60 V model)450 kHz min, 600 kHz max350 kHz min, 450 kHz max 60 V model Inhibit Pin Voltage (unit enabled)•9to 11 VInput Voltage Range•16 to 40 VDC continuous•50 V for up to 50 msec transient Case Operating Temperature (Tc)•–55°C to +125°C full power •–55°C to +135°C absoluteDerating Output Power/Current (Tc)•Linearly from 100% at 125°C to 0% at 135°CElectrical Characteristics:25°C Tc,28 VDC Vin,100% load,unless otherwise specified.Inhibit TTL Open Collector •Logic low (output disabled)Logic low voltage ≤0.8 V max Inhibit pin current 4 mA max •Referenced to input common •Logic high (output enabled)Open collectorNotes1.M SA2860S specifications are at 25°Tc only,contact your Interpoint representative for more information on over temperature specs.2.Line regulation for /ES and non /ES 2805S models at 16 to 17 V IN and 110°C to 125°C (case) is 5% (max).3.Indefinite short circuit protection not guaranteed above 125°C (case).4.Recovery time is measured from application of the transient to point at which V OUT is within 1% of V OUT at final value.5.Transition time >10µs.SINGLE OUTPUT MODELS MSA2805S MSA285R2S MSA2812S MSA2815S MSA2860S 1PARAM ETER CONDITIONS M IN TYP M AX M IN TYP M AX M IN TYP M AX M IN TYP M AX M IN TYP M AX UNITS OUTPUT VOLTAGE Tc = –55°C TO +125°C 4.95 5.00 5.05 5.15 5.20 5.2511.8812.0012.1214.8515.0015.1559.160.0060.9VDC OUTPUT CURRENTTc = –55°C TO +125°C V IN = 16 TO 40 VDC 0—1000—962—417—333—20mAOUTPUT POWER V IN = 16 TO 40 VDC Tc = –55°C TO +125°C ——5——5——5——5—— 1.2W OUTPUT RIPPLE VOLTAGE10 kHz - 2 MHz —125350—110335—50200—50170——300mV p-p LINE REGULATION V IN = 16 TO 40 VDC Tc = –55°C TO +125°C —10502—1050—1050—1050——300mV LOAD REGULATION NO LOAD TO FULL Tc = –55°C TO +125°C —1050—1050—1050—1050——300mV INPUT VOLTAGE Tc = –55°C TO +125°CNO LOAD TO FULL CONTINUOUS 162840162840162840162840162840VDC TRANSIENT 50 ms0—500—500—500—500—50V INPUT CURRENT NO LOAD —2740—2840—2942—3144——30T c = –55°C TO +125°C FULL LOAD —250——250——235——235——72—mA INHIBITED —35—35—35—35—35INPUT RIPPLE 10 kHz - 10 MHz —25100—25100—25100—25100——90mA p-p CURRENT Tc = –55°C TO +125°C—30150—30150—30150—30150———EFFICIENCY 6671—6671—7076—7176—7075—%LOAD FAULT 3, 4POWER DISSIPATION— 1.5 2.0— 1.5 2.0— 1.2 1.9— 1.2 1.8———W SHORT CIRCUIT RECOVERY —12.525— 1.525—110—110———ms STEP LOAD 50% - 100% - 50%RESPONSE 4, 5TRANSIENT —100250—100250—150375—200500———mV pk RECOVERY—100250—100250—200500—200500———µs STEP LINE TRANSIENT RESPONSE 4, 516 TO 40 V IN—50150—50150—80200—50125———mV pk40 TO 16 V IN —50150—50150—100250—50125———RECOVERY 16 TO 40 V IN —100250—100250—250625—250625———µs 40 TO 16 V IN—200500—200500—250625—250625———START-UPDELAY—1025—1025—310—310———ms OVERSHOOT—50—50—120—150———mV pk元器件交易网3MSA SERIES5 WATTDC/DC CONVERTERSElectrical Characteristics:25°C Tc,28 VDC Vin,100% load,unless otherwise specified.Notes1.Up to 4 watts (80% of full power) is available from either output providing the opposite output is carrying 20% of total power.2.Shows regulation effect on the minus output during the defined cross loading conditions. See Figures 15 and 16.3.Indefinite short circuit protection not guaranteed above 125°C (case).4.Recovery time is measured from application of the transient to point at which V OUT is within 1% of V OUT at final value.5.Transition time >10µs.DUAL OUTPUT MODELSMSA 2805DMSA2812D MSA2815DPARAMETER CONDITIONSMIN TYP MAX MIN TYP MAX MIN TYPMAX UNITS OUTPUT VOLTAGE +V OUT 4.95 5.00 5.0511.8812.0012.1214.8515.0015.15VDC–V OUT4.95.0 5.111.7612.0012.2414.7015.0015.30OUTPUT CURRENT 1V IN = 16 to 40 VDC Tc = –55°C to +125°C —±500800—±208333—±167267mA OUTPUT POWER 1V IN = 16 to 40 VDC Tc = –55°C to +125°C——5——5——5W OUTPUT RIPPLE VOLT.10 kHz -2 MHz ——150—40140—60150mV p-pLINE REGULATION Tc = –55°C to +125°CVin = 16 to 40 VDC+V OUT—1025—1050—1050mV–V OUT—4075—40180—40180LOAD REGULATION Tc = –55°C to +125°CNO LOAD TO FULL +V OUT—1050—1050—1050mV–V OUT—50200—50200—50200CROSS REGULATION 2+P O = 20 - 80 %, –P O = 80 - 20%—1020—815—715–P O = 20 - 80 %, +P O = 80 - 20%%+P O = 50 - 10 %, –P O = 50%—58— 3.76—36–P O = 50 - 10 %, +P O = 50%INPUT VOLTAGE NO LOAD TO FULL Tc = –55°C to +125°˜CONTINUOUS 162840162840162840VDC TRANSIENT 50 msec——50——50——50V INPUT CURRENT NO LOAD—3035—3358—3860Tc = –55°C to +125°C FULL LOAD —248——235——235—mAINHIBITED —35—35—35INPUT RIPPLE 10 kHz TO 10 MHz —2580—25100—25100CURRENT Tc = –55°C to +125°C —30160—30150—30150mA p-p EFFICIENCY 6872—6975—7075—%LOAD FAULT 3, 4POWER DISSIPATION SHORT CIRCUIT — 1.3 1.8— 1.3 1.7— 1.3 1.6W RECOVERY——50—110—110ms STEP LOAD 50% - 100% - 50% BALANCEDRESPONSE 4, 5TRANSIENT ——±150—±300±750—±300±750mV RECOVERY——100—200500—5001250µs STEP LINE RESP .4, 5TRANSIENT16 TO 40 VDC ——±750—±50±125—±150±37540 TO 16 VDC ——±500—±50±125—±100±250mV pk RECOVERY16 TO 40 VDC——1200—150375—25062540 TO 16 VDC ——1200—4001000—8002000µs START-UPDELAY ——25—310—310ms OVERSHOOT ——500—120—150mV pk元器件交易网SMD NUMBERS4MSA SERIES5 WATTDC/DC C ONVERTERSS TANDARD M ICROCIRCUITD RAWING(SMD)5962-9309201HXCIN PROCESS5962-9309301HXC5962-9309401HXC5962-0052201HXC5962-9308901HXC5962-9309001HXCMSA S ERIESS IMILAR P ARTMSA2805S/883MSA285R2S/883MSA2812S/883MSA2815S/883MSA2860S/883MSA2812D/883MSA2815D/883For exact specifications for an SMD product, refer to the SMDdrawing.Call your Interpoint representative for status onMSA SMD releases. “883” suffix indicates SMD similar part.SMDs can be downloaded from:/programs/smcr元器件交易网5MSA SERIES5 WATTDC/DC CONVERTERSTypical Performance Curves:25°C Tc,28 VDC Vin,100% load,unless otherwise specified.F IGURE 7IGUREF IGURE 6F IGURE 11F IGURE 13F IGURE 8F IGURE 9F IGURE 12F IGURE 10元器件交易网6MSA SERIES 5 WATTDC/DC CONVERTERSTypical Performance Curves:25°C Tc,28 VDC Vin,100% load,unless otherwise specified.IGUREF IGURE 14IGURE IGURE IGURE 元器件交易网7MSA SERIES5 WATTDC/DC CONVERTERSNote: Although every effort has been made to render the case drawings at actual size, variations in the printing process may cause some distortion. Please refer to the numerical dimensions for accuracy.元器件交易网8MSA SERIES 5 WATTDC/DC CONVERTERSTEST (125°C Products)STANDARD/ES/883 (Class H)*PRE-CAP INSPECTION Method 2017,2032yesyesyesTEMPERATURE CYCLE (10 times)Method 1010, Cond. C, -65°C to 150°C no no yes Method 1010, Cond. B, -55°C to 125°C no yes noCONSTANT ACCELERATION Method 2001, 3000 g no no yes Method 2001, 500 gno yes noBURN-INMethod 1015, 160 hours at 125°C no no yes 96 hours at 125°C case (typical)no yes noFINAL ELECTRICAL TEST MIL-PRF-38534, Group A Subgroups 1 through 6: -55°C, +25°C, +125°C no no yes Subgroups 1 and 4: +25°C case yes yes noHERMETICITY TESTINGFine Leak, Method 1014, Cond. A no yes yes Gross Leak, Method 1014, Cond. C no yes yes Gross Leak, Dip (1 x 10-3)yes no noFINAL VISUAL INSPECTION Method 2009yes yes yesTest methods are referenced to MIL-STD-883 as determined by MIL-PRF-38534.*883 products are built with element evaluated components and are 100% tested and guaranteed over the full military temperature range of –55°C to +125°C.E NVIRONMENTAL S CREENING22021-001-DTS Rev C This revision supercedes all previous releases.All technical information is believed to be accurate, but no responsibility is assumed for errors or omissions. Interpoint reserves the right to make changes in products or specifications without notice. MSA Series is a trademark of Interpoint.Copyright ©1994 - 2001 Interpoint Corporation. All rights reserved.Contact Information:Interpoint Headquarters USA Phone:1-800-822-8782+425-882-3100Email:power@ Interpoint UKPhone:+44-1252-815511Email:poweruk@Interpoint FrancePhone:+33-134285455Email:powerfr@元器件交易网。

5962-9665801QCA资料