CAT4104V-GT3;CAT4104VP2-GT3;中文规格书,Datasheet资料

CAT4139TD-GT3;中文规格书,Datasheet资料

CAT413922 V High Current Boost White LED DriverDescriptionThe CAT4139 is a DC/DC step−up converter that delivers an accurate constant current ideal for driving LEDs. Operation at a fixed switching frequency of 1 MHz allows the device to be used with small value external ceramic capacitors and inductor. LEDs connected in series are driven with a regulated current set by the external resistor R1. The CAT4139 is ideal for driving parallel strings of up to five white LEDs in series or up to 22 V.LED dimming can be done by using a DC voltage, a logic signal, or a pulse width modulation (PWM) signal. The shutdown input pin allows the device to be placed in power−down mode with “zero”quiescent current.In addition to thermal protection and overload current limiting, the device also enters a very low power operating mode during “Open LED” fault conditions. The device is housed in a low profile (1mm max height) 5−lead TSOT−23 package for space critical applications. Features•Switch Current Limit 750 mA•Drives LED Strings up to 22 V•Up to 87% Efficiency•Low Quiescent Ground Current 0.6 mA•1 MHz Fixed Frequency Low Noise Operation•Soft Start “In−rush” Current Limiting•Shutdown Current Less than 1 m A•Open LED Overvoltage Protection•Automatic Shutdown at 1.9 V (UVLO)•Thermal Overload Protection•TSOT−23 5−Lead (1 mm Max Height)•These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS CompliantApplications•GPS Navigation Systems•Portable Media Players•Handheld DevicesTSOT−23TD SUFFIXCASE 419AEPIN CONNECTIONSMARKING DIAGRAMDevice Package Shipping ORDERING INFORMATIONCAT4139TD−GT3(Note 1)TSOT−23(Pb−Free)3,000/Tape & Reel TP = Specific Device CodeY = Production Year (Last Digit)M = Production Month (1−9, A, B, C)(Top View)VINSHDNSWGNDFB1TPYM1.NiPdAu Plated Finish (RoHS−compliant)Figure 1. Typical Application Circuit9 strings at D: Central CMSH1−40 (rated 40 V)Table 1. ABSOLUTE MAXIMUM RATINGSParametersRatings Units VIN, FB Voltage −0.3 to +7V SHDN Voltage −0.3 to +7V SW Voltage−0.3 to +40V Storage Temperature Range −65 to +160_C Junction Temperature Range −40 to +150_C Lead Temperature300_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.Table 2. RECOMMENDED OPERATING CONDITIONS (Typical application circuit with external components is shown above.)ParametersRange Units VINup to 5.5V SW pin voltage0 to 22V Ambient Temperature Range (Note 2)−40 to +85_C2.TSOT23−5 package thermal resistance q JA = 135°C/W when mounted on board over a ground plane.Table 3. DC ELECTRICAL CHARACTERISTICS(V IN = 3.6 V, ambient temperature of 25°C (over recommended operating conditions unless otherwise specified))Symbol Parameter Test Conditions Min Typ Max UnitsI Q Operating Current V FB= 0.2 VV FB= 0.4 V (not switching)0.60.11.50.6mAI SD Shutdown Current V SHDN = 0 V0.11m A V FB FB Pin Voltage9 x 3 LEDs, I OUT = 180 mA285300315mV I FB FB pin input leakage1m AI LED Programmed LED Current R1 = 10 WR1 = 3 W 28.53010031.5mAV IH V IL SHDN Logic HighSHDN Logic LowEnable Threshold LevelShutdown Threshold Level0.40.80.71.5VF SW Switching Frequency0.8 1.0 1.3MHzI LIM Switch Current Limit V IN = 3.6 VV IN = 5 V 600750mAR SW Switch “On” Resistance I SW = 100 mA 1.0 2.0W I LEAK Switch Leakage Current Switch Off, V SW = 5 V15m A T SD Thermal Shutdown150°C T HYST Thermal Hysteresis20°C V UVLO Under−voltage lock out (UVLO) Threshold 1.9V V OV−DET Over−voltage detection threshold2324V V OCL Output Clamp voltage“Open LED”29VDC Maximum duty cycleMinimum duty cycle 9216%Figure 2. Quiescent Current vs. V IN(Not Switching)Figure 3. Quiescent Current vs. V IN(Switching)INPUT VOLTAGE (V)INPUT VOLTAGE (V)501001502005.04.54.03.53.000.51.01.52.0Figure 4. FB Pin Voltage vs. TemperatureFigure 5. FB Pin Voltage vs. Output CurrentTEMPERATURE (°C)OUTPUT CURRENT (mA)10015050−5029729830130230320018016014012010080290295300305310Figure 6. Switching Frequency vs. SupplyVoltage Figure 7. Switch ON Resistance vs.Input VoltageINPUT VOLTAGE (V)4.0 4.53.53.00.80.91.01.11.2Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )F B P I N V O L T A G E (m V )F B P I N V O L T AG E (m V )S W I T C H I N G F R E Q U E N C Y (M H z )INPUT VOLTAGE (V)4.54.05.03.53.000.51.01.52.0S W I T C H R E S I S T A N C E (W )5.5299300 5.0 5.55.5Figure 8. Output Current vs. Input VoltageFigure 9. Output Current RegulationINPUT VOLTAGE (V)INPUT VOLTAGE (V)5.04.54.03.53.0100120140160180200 5.55.14.94.74.5−2.0−0.500.52.0Figure 10. Efficiency vs. Output Current Figure 11. Efficiency vs. Input VoltageOUTPUT CURRENT (mA)INPUT VOLTAGE (V)2001801601201008075808590957580859095Figure 12. Power −up at 180 mA Figure 13. Switching WaveformL E D C U R R E N T (m A )I O U T V A R I A T I O N (%)E F F I C I E N C Y (%)E F F I C I E N C Y (%)5.3140 5.5−1.0−1.51.01.5Figure 14. Maximum Output CurrentFigure 15. Shutdown VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)501001502503000.20.61.0Figure 16. Switch Current LimitINPUT VOLTAGE (V)600650750800900M A X O U T P U T C U R R E N T (m A )S H U T D O W N V O L T A G E (V )S W I T C H C U R R E N T L I M I T (m A )0.40.8200700850VIN is the supply input for the internal logic. The device is compatible with supply voltages down to 2.8 V and up to 5.5V. It is recommended that a small bypass ceramic capacitor (4.7 m F) be placed between the VIN and GND pins near the device. If the supply voltage drops below 1.9 V, the device stops switching.SHDN is the shutdown logic input. When the pin is tied to a voltage lower than 0.4 V, the device is in shutdown mode, drawing nearly zero current. When the pin is connected to a voltage higher than 1.5 V, the device is enabled.GND is the ground reference pin. This pin should be connected directly to the ground plane on the PCB.SW pin is connected to the drain of the internal CMOS power switch of the boost converter. The inductor and the Schottky diode anode should be connected to the SW pin. Traces going to the SW pin should be as short as possible with minimum loop area. An over−voltage detection circuit is connected to the SW pin. When the voltage reaches 24V, the device enters a low power operating mode preventing the SW voltage from exceeding the maximum rating.FB feedback pin is regulated at 0.3 V. A resistor connected between the FB pin and ground sets the LED current according to the formula:I LED+0.3VR1The lower LED cathode is connected to the FB pin.Table 4. PIN DESCRIPTIONSPin #Name Function 1SW Switch pin. This is the drain of the internal power switch.2GND Ground pin. Connect the pin to the ground plane.3FB Feedback pin. Connect to the last LED cathode.4SHDN Shutdown pin (Logic Low). Set high to enable the driver.5VIN Power Supply input.The CAT4139 is a fixed frequency (1 MHz), low noise, inductive boost converter that provides a constant current with excellent line and load regulation. The device uses a high−voltage CMOS power switch between the SW pin and ground to energize the inductor. When the switch is turned off, the stored energy in the inductor is released into the load via the Schottky diode.The on/off duty cycle of the power switch is internally adjusted and controlled to maintain a constant regulated voltage of 0.3 V across the feedback resistor connected to the feedback pin (FB). The value of the resistor sets the LED current accordingly (0.3 V/R1).During the initial power−up stage, the duty cycle of the internal power switch is limited to prevent excessive in−rush currents and thereby provide a “soft−start” mode of operation.In the event of an “Open LED” fault condition, where the feedback control loop becomes open, the output voltage will continue to increase. Once this voltage exceeds 24 V, an internal protection circuit will become active and place the device into a very low power safe operating mode. Thermal overload protection circuitry has been included to prevent the device from operating at unsafe junction temperatures above 150°C. In the event of a thermal overload condition the device will automatically shutdown and wait till the junction temperatures cools to 130°C before normal operation is resumed.Application Information External Component SelectionCapacitorsThe CAT4139 only requires small ceramic capacitors of 4.7m F on the input and 1 m F on the output. Under normal condition, a 4.7 m F input capacitor is sufficient. For applications with higher output power, a larger input capacitor of 10 m F may be appropriate. X5R and X7R capacitor types are ideal due to their stability across temperature range.InductorA 22 m H inductor is recommended for most of the CAT4139 applications. In cases where the efficiency is critical, inductances with lower series resistance are preferred. Inductors with current rating of 800mA or higher are recommended for most applications. Sumida CDRH6D28−220 22 m H inductor has a rated current of 1.2A and a series resistance (D.C.R.) of 128 m W typical. Schottky DiodeThe current rating of the Schottky diode must exceed the peak current flowing through it. The Schottky diode performance is rated in terms of its forward voltage at a given current. In order to achieve the best efficiency, this forward voltage should be as low as possible. The response time is also critical since the driver is operating at 1MHz. Central Semiconductor Schottky rectifier CMSH1−40 (1A rated) is recommended for most applications.LED Current SettingThe LED current is set by the external resistor R1 connected between the feedback pin (FB) and ground. The formula below gives the relationship between the resistor and the current:R1+0.3VLED currentTable 5. RESISTOR R1 AND LED CURRENTLED Current (mA)R1 (W)20152512301010033001Open LED ProtectionIn the event of an “Open LED” fault condition, the CAT4139 will continue to boost the output voltage with maximum power until the output voltage reaches approximately 24 V . Once the output exceeds this level, the internal circuitry immediately places the device into a very low power mode where the total input power is limited to about 6 mW (about 1.6 mA input current with a 3.6V supply). The SW pin clamps at a voltage below its maximum rating of 40 V . There is no need to use an external zener diode between VOUT and the FB pin. A 35 V rated C2 capacitor is required to prevent any overvoltage damage in the open LED condition.Figure 18. Open LED Protection CircuitSchottky 40 V (Central CMSH05−4)V Figure 19. Open LED Disconnect and ReconnectFigure 20. Open LED DisconnectFigure 21. Open LED Supply Current Figure 22. Open LED Output VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)5.55.04.54.03.53.01.01.52.02.55.55.04.54.03.53.01520253035I N P U T C U R R E N T (m A )O U T P U T V O L T A G E (V )Dimming ControlThere are several methods available to control the LED brightness.PWM Signal on the SHDN PinLED brightness dimming can be done by applying a PWM signal to the SHDN input. The LED current is repetitively turned on and off, so that the average current is proportional to the duty cycle. A 100% duty cycle, with SHDN always high, corresponds to the LEDs at nominal current. Figure23 shows a 1 kHz signal with a 50% duty cycle applied to the SHDN pin. The recommended PWM frequency range is from 100Hz to 2 kHz.Figure 23. Switching Waveform with 1 kHzPWM on SHDN Filtered PWM SignalA filtered PWM signal used as a variable DC voltage can control the LED current. Figure 24 shows the PWM control circuitry connected to the CAT4139 FB pin. The PWM signal has a voltage swing of 0 V to 2.5 V. The LED current can be dimmed within a range from 0 mA to 20 mA. The PWM signal frequency can vary from very low frequency and up to 100 kHz.Figure 24. Circuit for Filtered PWM Signal0 V2.5 VW PWMSignalVA PWM signal at 0 V DC, or a 0% duty cycle, results in a max LED current of about 22 mA. A PWM signal with a 93% duty cycle or more, results in an LED current of 0mA.Figure 25. Filtered PWM Dimming (0 V to 2.5 V)LEDCURRENT(mA)2520151050102030405060708090100PWM DUTY CYCLE (%)分销商库存信息: ONSEMICAT4139TD-GT3。

海康威视 cMT-G04 产品说明书

使用手冊目錄第一章概要 (1)1.1規格介紹 (1)1.2尺寸圖 (2)1.3恢復出廠值 (3)1.4LED 指示燈 (3)1.5CR1220 電池 (3)1.6電源連接 (3)第二章cMT-G04 系統設定 (4)2.1找尋cMT-G04 的IP位址 (4)2.2透過網路瀏覽器設定 (4)2.3System Setting (5)2.3.1Network (5)2.3.2Date/Time (6)2.3.3HMI Name (6)2.3.4History (7)2.3.5Email (7)2.3.6Project Management (8)2.3.7System Password (8)2.3.8Enhanced Security (9)2.3.9EasyAccess 2.0 (9)2.3.10OPC UA (10)2.3.11Communication (10)第三章Web package及OS更新 (12)3.1更新網頁套件 (12)3.2更新OS (13)第四章如何建立cMT-G04 工程檔案 (14)4.1 建立一個新工程檔案 (14)4.2 下載工程檔案至cMT-G04 (16)4.3 OPC UA Client監控 (17)4.4 連線模擬/離線模擬 (17)第五章cMT-G04支援的功能 (19)第六章使用網頁介面管理OPC UA (20)6.1.概要 (20)6.2.開啟/關閉OPC UA伺服器 (21)6.3.Server Settings (22)6.4.Edit Node (23)6.5.Certificates (24)6.6.Discovery (25)6.7.Advanced (26)第一章概要1.1規格介紹IIoT Gateway with Ethernet Bridge特點●內建乙太網路交換器,可節省佈線成本,SW1與SW2 方便連接現有的HMI和PLC, 不需要外加乙太網路交換器,而LAN則連接辦公室或工廠網路●支援OPC UA 及MQTT●薄型輕量設計並可使用鋁軌固定●無風扇冷卻系統●內建256 MB 儲存記憶體●內建電源隔離●寬輸入電壓範圍10.5~28VDC1.2尺寸圖adeFront View Side ViewTop View BottomViewbcadbc27mm [1.06"]1.3恢復出廠值每台cMT-G04皆有一個Default按鈕,長按此按鈕至少15秒,Gateway就會恢復成出廠預設值。

CAV24C32WE-GT3;CAV24C32YE-GT3;中文规格书,Datasheet资料

CAV24C3232-Kb I2C CMOS Serial EEPROMDescriptionThe CA V24C32 is a 32−Kb CMOS Serial EEPROM devices, internally organized as 4096 words of 8 bits each.It features a 32−byte page write buffer and supports the Standard (100kHz) and Fast (400 kHz) I2C protocol.External address pins make it possible to address up to eight CA V24C32 devices on the same bus.Features•Automotive Temperature Grade 1 (−40°C to +125°C)•Supports Standard and Fast I2C Protocol•2.5 V to 5.5 V Supply V oltage Range•32−Byte Page Write Buffer•Hardware Write Protection for Entire Memory•CA V Prefix for Automotive and Other Applications Requiring Site and Change Control•Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs (SCL and SDA)•Low Power CMOS Technology•1,000,000 Program/Erase Cycles•100 Year Data Retention•SOIC, TSSOP 8−lead Packages•This Device is Pb−Free, Halogen Free/BFR Free, and RoHS CompliantFigure 1. Functional Symbol SDASCL WPV CC SSA2, A1, APIN CONFIGURATIONSSDAWPV CCV SSA2A1A01See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.ORDERING INFORMATIONSOIC−8W SUFFIXCASE 751BDSCLSOIC (W), TSSOP (Y)TSSOP−8Y SUFFIXCASE 948ALFor the location of Pin 1, please consult thecorresponding package drawing.Device Address Input A0, A1, A2Serial Data Input/OutputSDASerial Clock InputSCLWrite Protect InputWPPower SupplyV CCGroundV SSFunctionPin NamePIN FUNCTIONDEVICE MARKINGS(SOIC−8) (TSSOP−8)C32FAYMXXXC32F= Specific Device CodeA= Assembly LocationY= Production Year (Last Digit)M= Production Month (1-9, O, N, D)XXX= Last Three Digits of Assembly Lot Number G= Pb−Free Package 24C32F= Specific Device CodeA= Assembly LocationY= Production Year (Last Digit)M= Production Month (1-9, O, N, D)XXX= Last Three Digits of Assembly Lot Number G= Pb−Free Package24C32FAYMXXXGGTable 1. ABSOLUTE MAXIMUM RATINGSParameters Ratings Units Storage Temperature–65 to +150°C Voltage on any Pin with Respect to Ground (Note 1)–0.5 to +6.5V Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.During input transitions, voltage undershoot on any pin should not exceed −1 V for more than 20 ns. Voltage overshoot on pins A0, A1, A2and WP should not exceed V CC + 1 V for more than 20 ns, while voltage on the I2C bus pins, SCL and SDA, should not exceed the absolute maximum ratings, irrespective of V CC.Table 2. RELIABILITY CHARACTERISTICS (Note 2)Symbol Parameter Min UnitsN END (Note 3)Endurance1,000,000Program/Erase Cycles T DR Data Retention100Years2.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.3.Page Mode, V CC = 5 V, 25°C.Table 3. D.C. OPERATING CHARACTERISTICS (V CC = 2.5 V to 5.5 V, T A = −40°C to +125°C, unless otherwise specified.) Symbol Parameter Test Conditions Min Max UnitsI CCR Read Current Read, f SCL = 400 kHz1mAI CCW Write Current Write, f SCL = 400 kHz2mAI SB Standby Current All I/O Pins at GND or V CC T A = −40°C to +125°C5m AI L I/O Pin Leakage Pin at GND or V CC2m AV IL Input Low Voltage−0.50.3 x V CC V V IH Input High Voltage A0, A1, A2 and WP0.7 x V CC V CC + 0.5VSCL and SDA0.7 x V CC 5.5 V OL Output Low Voltage V CC > 2.5 V, I OL = 3 mA0.4VTable 4. PIN IMPEDANCE CHARACTERISTICS (V CC = 2.5 V to 5.5 V, T A = −40°C to +125°C, unless otherwise specified.) Symbol Parameter Conditions Max Units C IN (Note 4)SDA I/O Pin Capacitance V IN = 0 V, T A = 25°C, V CC = 5.0 V8pF C IN (Note 4)Input Capacitance (other pins)V IN = 0 V, T A = 25°C, V CC = 5.0 V6pF I WP (Note 5)WP Input Current V IN< V IH, V CC = 5.5 V130m AV IN < V IH, V CC = 3.3 V120V IN < V IH, V CC = 2.5 V80V IN < V IH2I A (Note 5)Address Input Current(A0, A1, A2)Product Rev F V IN< V IH, V CC = 5.5 V50m A V IN < V IH, V CC = 3.3 V35V IN < V IH, V CC = 2.5 V25V IN > V IH24.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.5.When not driven, the WP, A0, A1 and A2 pins are pulled down to GND internally. For improved noise immunity, the internal pull−down is relativelystrong; therefore the external driver must be able to supply the pull−down current when attempting to drive the input HIGH. T o conserve power, as the input level exceeds the trip point of the CMOS input buffer (~ 0.5 x V CC), the strong pull−down reverts to a weak current source.Table 5. A.C. CHARACTERISTICS (V CC = 2.5 V to 5.5 V, T A = −40°C to +125°C, unless otherwise specified.) (Note 6)Symbol ParameterStandard FastUnits Min Max Min MaxF SCL Clock Frequency100400kHzt HD:STA START Condition Hold Time40.6m s t LOW Low Period of SCL Clock 4.7 1.3m s t HIGH High Period of SCL Clock40.6m s t SU:STA START Condition Setup Time 4.70.6m s t HD:DAT Data In Hold Time00m s t SU:DAT Data In Setup Time250100ns t R SDA and SCL Rise Time1000300ns t F (Note 6)SDA and SCL Fall Time300300ns t SU:STO STOP Condition Setup Time40.6m s t BUF Bus Free Time Between STOP and START 4.7 1.3m s t AA SCL Low to Data Out Valid 3.50.9m s t DH Data Out Hold Time100100ns T i (Note 6)Noise Pulse Filtered at SCL and SDA Inputs100100ns t SU:WP WP Setup Time00m s t HD:WP WP Hold Time 2.5 2.5m s t WR Write Cycle Time55ms t PU (Notes 7, 8)Power−up to Ready Mode11ms6.Test conditions according to “AC Test Conditions” table.7.Tested initially and after a design or process change that affects this parameter.8.t PU is the delay between the time V CC is stable and the device is ready to accept commands.Table 6. A.C. TEST CONDITIONSInput Drive Levels0.2 x V CC to 0.8 x V CCInput Rise and Fall Time≤ 50 nsInput Reference Levels0.3 x V CC, 0.7 x V CCOutput Reference Level0.5 x V CCOutput Test Load Current Source I OL = 3 mA; C L = 100 pFPower-On Reset (POR)Each CA V24C32 incorporates Power-On Reset (POR)circuitry which protects the internal logic against powering up in the wrong state. The device will power up into Standby mode after V CC exceeds the POR trigger level and will power down into Reset mode when V CC drops below the POR trigger level. This bi-directional POR behavior protects the device against ‘brown-out’ failure following a temporary loss of power.Pin DescriptionSCL: The Serial Clock input pin accepts the clock signal generated by the Master.SDA: The Serial Data I/O pin accepts input data and delivers output data. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and is delivered on the negative edge of SCL.A 0, A 1 and A 2: The Address inputs set the device address that must be matched by the corresponding Slave address bits. The Address inputs are hard-wired HIGH or LOW allowing for up to eight devices to be used (cascaded) on the same bus. When left floating, these pins are pulled LOW internally.WP: When pulled HIGH, the Write Protect input pin inhibits all write operations. When left floating, this pin is pulled LOW internally.Functional DescriptionThe CA V24C32 supports the Inter-Integrated Circuit (I 2C) Bus protocol. The protocol relies on the use of a Master device, which provides the clock and directs bus traffic, and Slave devices which execute requests. The CA V24C32operates as a Slave device. Both Master and Slave can transmit or receive, but only the Master can assign those roles.I 2C Bus ProtocolThe 2-wire I 2C bus consists of two lines, SCL and SDA,connected to the V CC supply via pull-up resistors. The Master provides the clock to the SCL line, and either the Master or the Slaves drive the SDA line. A ‘0’ is transmitted by pulling a line LOW and a ‘1’ by letting it stay HIGH. Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics). During data transfer, SDA must remain stable while SCL is HIGH.START/STOP Condition An SDA transition while SCL is HIGH creates a START or STOP condition (Figure 2). The START consists of a HIGH to LOW SDA transition, while SCL is HIGH. Absent the START, a Slave will not respond to the Master. The STOP completes all commands, and consists of a LOW to HIGH SDA transition, while SCL is HIGH.Device AddressingThe Master addresses a Slave by creating a START condition and then broadcasting an 8-bit Slave address. For the CA V24C32, the first four bits of the Slave address are set to 1010 (Ah); the next three bits, A 2, A 1 and A 0, must match the logic state of the similarly named input pins. The R/W bit tells the Slave whether the Master intends to read (1) or write (0) data (Figure 3).AcknowledgeDuring the 9th clock cycle following every byte sent to the bus, the transmitter releases the SDA line, allowing the receiver to respond. The receiver then either acknowledges (ACK) by pulling SDA LOW, or does not acknowledge (NoACK) by letting SDA stay HIGH (Figure 4). Bus timing is illustrated in Figure 5.START CONDITIONSTOP CONDITIONSDASCLFigure 2. Start/Stop TimingFigure 3. Slave Address BitsDEVICE ADDRESSFigure 4. Acknowledge TimingSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER≥ t SU:DAT )Figure 5. Bus TimingSCLSDA INSDA OUTWRITE OPERATIONSByte WriteTo write data to memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘0’. The Master then sends two address bytes and a data byte and concludes the session by creating a STOP condition on the bus. The Slave responds with ACK after every byte sent by the Master (Figure 6). The STOP starts the internal Write cycle, and while this operation is in progress (t WR ), the SDA output is tri-stated and the Slave does not acknowledge the Master (Figure 7).Page WriteThe Byte Write operation can be expanded to Page Write,by sending more than one data byte to the Slave before issuing the STOP condition (Figure 8). Up to 32 distinct data bytes can be loaded into the internal Page Write Buffer starting at the address provided by the Master. The page address is latched, and as long as the Master keeps sending data, the internal byte address is incremented up to the end of page, where it then wraps around (within the page). New data can therefore replace data loaded earlier. Following the STOP, data loaded during the Page Write session will be written to memory in a single internal Write cycle (t WR ).Acknowledge PollingAs soon (and as long) as internal Write is in progress, the Slave will not acknowledge the Master. This feature enables the Master to immediately follow-up with a new Read or Write request, rather than wait for the maximum specified Write time (t WR ) to elapse. Upon receiving a NoACK response from the Slave, the Master simply repeats the request until the Slave responds with ACK.Hardware Write ProtectionWith the WP pin held HIGH, the entire memory is protected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the Write operation. The state of the WP pin is strobed on the last falling edge of SCL immediately preceding the 1st data byte (Figure 9). If the WP pin is HIGH during the strobe interval,the Slave will not acknowledge the data byte and the Write request will be rejected.Delivery StateThe CA V24C32 is shipped erased, i.e., all bytes are FFh.SLAVE ADDRESSSA ****C KA C KA C KS T O P PST ARTA CKBUS ACTIVITY:MASTER SLAVEADDRESS BYTE ADDRESS BYTE DAT A BYTE Figure 6. Byte Write Sequence*a 15 − a 12 are don’t care bitsa 15 − a 8a 7 − a 0d 7 − d 0Figure 7. Write Cycle TimingSTOPCONDITIONSTARTCONDITIONADDRESSSCLSDASLAVE ADDRESSSA C K A C K C K ST ARTC K S T O C KC K C K BUSACTIVITY:MASTER SLAVEn = 1ADDRESS BYTE ADDRESS BYTEDATA BYTE DATA BYTE DATA BYTE Figure 8. Page Write SequenceP ≤ 31Figure 9. WP TimingADDRESS BYTE DATA BYTESCLSDA WPREAD OPERATIONSImmediate ReadTo read data from memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK and starts shifting out data residing at the current address.After receiving the data, the Master responds with NoACK and terminates the session by creating a STOP condition on the bus (Figure 10). The Slave then returns to Standby mode.Selective ReadTo read data residing at a speci fic address, the selected address must first be loaded into the internal address register.This is done by starting a Byte Write sequence, whereby the Master creates a START condition, then broadcasts a Slave address with the R/W bit set to ‘0’ and then sends two address bytes to the Slave. Rather than completing the ByteWrite sequence by sending data, the Master then creates a START condition and broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK after every byte sent by the Master and then sends out data residing at the selected address. After receiving the data, the Master responds with NoACK and then terminates the session by creating a STOP condition on the bus (Figure 11).Sequential ReadIf, after receiving data sent by the Slave, the Master responds with ACK, then the Slave will continue transmitting until the Master responds with NoACK followed by STOP (Figure 12). During Sequential Read the internal byte address is automatically incremented up to the end of memory, where it then wraps around to the beginning of memory.Figure 10. Immediate Read Sequence and TimingSCL SDA 8th Bit STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDATA BYTEN OA C K S T O P PS T A R T BUS ACTIVITYMASTERSLAVEFigure 11. Selective Read SequenceSLAVE ADDRESS SA C KA C KA C K ST ARTSLAVE SA C KS T A R T PS T O P ADDRESS BYTE ADDRESS BYTE ADDRESSN O A C KBYTEBUS ACTIVITY:MASTER SLAVEFigure 12. Sequential Read SequenceS T O SLAVE C KA C A C N O A C A C BYTE n BYTE n+1BYTE n+2BYTE n+xBUS ACTIVITY:MASTERSLAVESOIC 8, 150 mils CASE 751BD −01ISSUE OIDENTIFICATIONTOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MS-012.SYMBOLMIN NOMMAX θA A1b cD E E1e h 0º8º0.100.330.190.254.805.803.801.27 BSC1.750.250.510.250.505.006.204.00L0.40 1.271.35TSSOP8, 4.4x3CASE 948AL −01ISSUE OA1TOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MO-153.SYMBOLθMINNOM MAXA A1A2bc D E E1e L10º8ºL 0.050.800.190.090.502.906.304.300.65 BSC 1.00 REF1.200.151.050.300.200.753.106.504.500.900.603.006.404.40Example of Ordering InformationCAV24C32WE −GT3 (Note 11)Prefix Device #Suffix 9.All packages are RoHS-compliant (Lead-free, Halogen-free).10.The standard lead finish is NiPdAu.11.The device used in the above example is a CAV24C32WE −GT3 (SOIC, Automotive Temperature, NiPdAu, Tape & Reel, 3,000/Reel).12.For other package options, please contact your nearest ON Semiconductor Sales office.13.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.ON Semiconductor is licensed by Philips Corporation to carry the I 2C Bus Protocol.PUBLICATION ORDERING INFORMATION分销商库存信息:ONSEMICAV24C32WE-GT3CAV24C32YE-GT3。

M-AUDIO_410中文说明书

M-AUDIO FireWire410中文说明书1.FireWire410 简介FireWire410 是一个4 进10 出音频接口,它通过IEEE-1394 端口(俗称"火线")与计算机进行连接。

如果你的计算机没有火线端口,只需向计算机经销商购买一块PCI 的火线卡,便能与FireWire410 连接。

笔记本电脑通常都自备火线端口。

FireWire410 包装内带一条高质量的六针到六针1394 数据线,建议你使用它或相同品质的火线与电脑连接。

如果电脑上只有四针火线接口,则需购买一条六针到四针的1394 数据线。

另外需指出,FireWire410 使用六针的端口自供电,若使用四针的火线口,需要为FireWire410 提供外部电源。

提示:火线口即是1394 口,在Sony 设备中又称iLink 口。

FireWire410 提供两个卡侬和大三芯的复合模拟输入口,可以连接话筒,也可接电吉它、电贝司等乐器;八个大三芯模拟输出口及一对S/PDIF 的同轴、光纤输入/输出。

FireWire410提供了高品质模拟、数字输入输出,支持24 比特的采样精度、96kHz 录音采样频率和192kHz 输出采样频率,S/PDIF 端口支持AC3 和DTS 双编码。

FileWire410 还提供了一进一出MIDI端口,并有开关选择MIDI 输出或是旁通,可作为独立MIDI 接口使用。

FireWire410 具有简捷实用的软件控制系统,提供了跳线和调音台控制功能,为音频软件虚拟了10 个输出通道。

你可任意分配输入端口到输出端,每个内部通道又支持具有超大控制幅度的辅助发送。

FireWire 还提供了零延迟硬件直接监听和基于ASIO 的超低延迟软监听;具有两个独立的耳机监听输出,信号来源可选择,并有独立增益控制;两个麦克风/乐器功放提供了电平控制和监测功能、48V 幻像电源、20dB 衰减和最大66dB 的增益。

CAT2300VP2-GT3;中文规格书,Datasheet资料

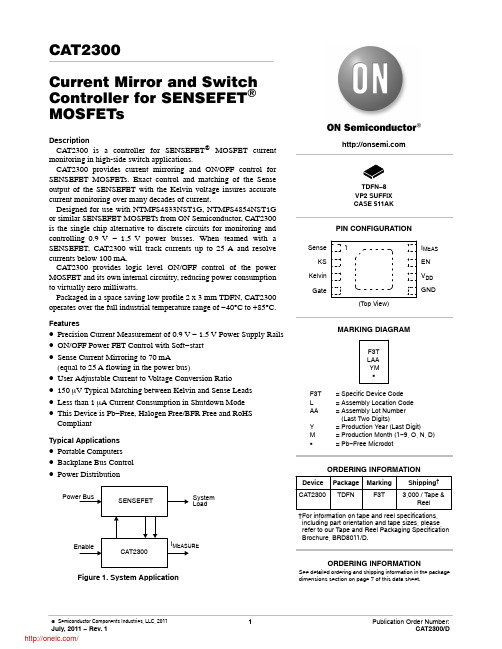

CAT2300Current Mirror and Switch Controller for SENSEFET )MOSFETsDescriptionCAT2300 is a controller for SENSEFET ® MOSFET current monitoring in high-side switch applications.CAT2300 provides current mirroring and ON/OFF control for SENSEFET MOSFETs. Exact control and matching of the Sense output of the SENSEFET with the Kelvin voltage insures accurate current monitoring over many decades of current.Designed for use with NTMFS4833NST1G, NTMFS4854NST1G or similar SENSEFET MOSFETs from ON Semiconductor, CA T2300is the single chip alternative to discrete circuits for monitoring and controlling 0.9 V − 1.5 V power busses. When teamed with a SENSEFET, CAT2300 will track currents up to 25 A and resolve currents below 100 mA.CAT2300 provides logic level ON/OFF control of the power MOSFET and its own internal circuitry, reducing power consumption to virtually zero milliwatts.Packaged in a space saving low profile 2 x 3 mm TDFN, CAT2300operates over the full industrial temperature range of −40°C to +85°C.Features •Precision Current Measurement of 0.9 V − 1.5 V Power Supply Rails •ON/OFF Power FET Control with Soft −start •Sense Current Mirroring to 70 mA (equal to 25 A flowing in the power bus)•User Adjustable Current to V oltage Conversion Ratio•150 m V Typical Matching between Kelvin and Sense Leads •Less than 1 m A Current Consumption in Shutdown Mode •This Device is Pb −Free, Halogen Free/BFR Free and RoHS CompliantTypical Applications•Portable Computers •Backplane Bus Control •Power DistributionFigure 1. System ApplicationSystem LoadSee detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.ORDERING INFORMATIONPIN CONFIGURATIONTDFN −8VP2 SUFFIX CASE 511AKSense KS Kelvin Gate1GNDV DD EN I MEAS (Top View)MARKING DIAGRAMF3T = Specific Device Code L = Assembly Location Code AA = Assembly Lot Number (Last Two Digits)Y = Production Year (Last Digit)M = Production Month (1−9, O, N, D)G= Pb −Free MicrodotF3T LAA YM GDevice Package Shipping †ORDERING INFORMATIONCAT2300TDFN3,000 / Tape &ReelMarking F3T†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.SenseKSKelvin Gate ENFigure 2. Simplified Block DiagramI MEASV DDTable 1. PIN FUNCTION DESCRIPTIONPin No.Pin Name Function1Sense Connects to Sense pin of SENSEFET and directs sensed current to IMEAS output.2KS Kelvin Sense; a Kelvin connection for the current mirror control amplifier. This connection must be made directly to Sense on the SENSEFET package. Do not share any trace length with CAT2300’s Sense lead.3Kelvin Connects to Kelvin pin of the SENSEFET. Serves as the reference point for Sense lead biasing.4Gate Connects to Gate of the SENSEFET and controls SENSEFET operation.5GND Electrical ground for IC.6V DD External voltage supply for driving the gate of the SENSEFET and power supply for CAT2300 internal circuitry via an internal voltage regulator.7EN Enable: High true logic input. Turns ON SENSEFET and CAT2300’s internal circuitry. A logic LOW on EN grounds Gate, shutting off the SENSEFET and shuts down the internal current source and mirroring circuitry.8I MEASSensed current output. A resistor between I MEAS and ground develops a voltage proportional to the current flowing through the SENSEFET.PADBackside paddle is internally connected to GND. This pad may be left floating but if connected with PCB it must be to the ground plane of circuitry which is also grounded.Table 2. ABSOLUTE MAXIMUM RATINGS (Note 1)ParameterSymbol Value Unit V DD V DD6.5V Gate±15mA V K , EN, Sense, KS, Kelvin, I MEAS 6.5V Junction Temperature150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Guaranteed by design.Table 3. RECOMMENDED OPERATING CONDITIONSParameterSymbol Value Unit V K V K 0.9 to 1.5V V DDV DD 5V Maximum Junction Temperature T JUNCTION 125°C Ambient Temperature RangeT AMBIENT−40 to +85°CTable 4. PACKAGE THERMAL PERFORMANCEPackage Symbol Test Conditions Min Typ Max UnitTDFN−8q JA1 oz Copper Thickness, 100 mm2160°C/W q JC35SOIC−8q JA1 oz Copper Thickness, 100 mm2160°C/W q JC25Table 5. DC ELECTRICAL CHARACTERISTICS(V K = 0.9 – 1.5 V; V DD = +5 V; T AMBIENT =−40°C to +85°C, T JUNCTION =−40°C to +125°C, unless otherwise specified.)Parameter Symbol Test ConditionsLimitsUnits Min Typ MaxKelvin voltage V K0.9 1.5V Gate Drive input voltage V DD 4.5 5.5V Supply Current on V DD pin I VDD EN = logic 01m AEN = logic 16577100m A Gate drive Sourcing I GATE V GATE = V DD– 1 V−235−280−330m A Gate drive Sinking V GATE = 0.6 V79.613mA Offset Voltage V OS V OS = V KELVIN− V SENSEV K = 0.9 V to 1.5 V±150±300m VInput Bias Current;Kelvin and KS inputsI K100150nA Power Supply Rejection Ratio PSRR70db I MEAS output current I MEAS070mA Output voltage of I MEAS amplifier V O_IM0V K – 0.1V LOGICLow level input voltage V IL EN0.9 1.1 1.26V High level input voltage V IH EN 1.4 1.65 1.9V Hysteresis0.55V Low level input current I IL EN, V DD = 0 V or 5.5 V2m A High level input current I IH EN, V DD = 0 V or 5.5 V2m A Table 6. AC OPERATING CHARACTERISTICS(V K = 0.9 V – 1.5 V; V DD = 5 V; T AMBIENT =−40°C to +85°C, T JUNCTION =−40°C to +125°C, unless otherwise specified.)Parameter Symbol Test ConditionsLimitsUnits Min Typ MaxI MEAS output rise time t R 20 W, 100 pF, V K = 1.5 VI SENSE : 2 mA – 70 mA 38m sI MEAS output fall time t F33m s I MEAS Settling time t S EN = Logic 0³1, I SENSE = 1 mA30m sEN = Logic 0³1, I SENSE = 70 mA50m sTYPICAL PERFORMANCE CHARACTERISTICSFigure 3. Load Step: 1 A – 10 A50 m s / divI BusV MEASPIN DESCRIPTIONSenseSense connects directly to the SENSEFET’s Sense pin and directs the sensed current to the I MEAS output. Sense is controlled by an amplifier with a FET follower stage to maintain Sense at exactly the Kelvin voltage, thus insuring accuracy of the SENSEFET’s mirror current.KSKS = Kelvin Sense; a Kelvin connection for the mirroring amplifier. Current measurement accuracy is dependent upon the voltage match between the SENSEFET’s Sense and Kelvin leads. To minimize voltage losses in the PCB trace between CA T2300 and the SENSEFET, a Kelvin connection for the control amplifier is provided. KS must be a dedicated connection, shared by no other circuitry , and tied directly to the Sense pin on of the SENSEFET.Figure 4. Current SenseSENSEFETSENSEFETSENSEFETCareful layout is critical in achieving full SENSEFET perfomance. PCB trace resistance can no longer be ignored as it can be in typical low current circuit designs. Microvolt offsets (m V) produce meaningful errors in current ratio tracking. A few milliohms of trace resistance carrying a few milliamps of current produces microvolts of potential difference between CAT2300 and the SENSEFET. To circumvent this error CA T2300 provides a Kelvin lead (KS)for monitoring the SENSEFET’s Sense pin. Under no circumstances should the KS connection share any portion of the current path between the sense pins of CAT2300 and the SENSEFET. Doing so will degrade measurement accuracy.KelvinKelvin connects directly to the SENSEFET’s Kelvin pin and acts the reference voltage for CAT2300’s mirroring circuit. It too must be a dedicated connection, shared by no other circuitry.GateGate connects to the SENSEFET’s Gate pin and controls the SENSEFET’s operation. Gate is controlled by EN: a logic 1 turns the SENSEFET ON, a logic 0 turns it OFF.When ON, voltage is applied to the SENSEFET’s gate via a current source inside CAT2300.By controlling the gate drive current a controlled turn-ON is achieved. Faster turn-on times can be done by adding a supplemental current source to augment the internal current source. Placing a resistor between V DD and Gate will provide extra current and boost turn-on speeds.For a softer turn-on characteristic, add capacitance between the SENSEFET’s Gate and Source pins;approximately 1 nF for every ms of increased delay.When switching OFF the SENSEFET, Gate provides a strong pull-down, 7.5 mA typical, so the SENSEFET will be switched off quickly.V DDV DD provides gate drive for the SENSEFET and power for CAT2300’s internal circuitry and must be +5 V .I MEAS I MEAS is the mirror current output. Placing a resistor between I MEAS and ground produces a voltage proportional to I BUS . The maximum voltage producible at IMEAS is the Kelvin voltage (V K ) – 0.1 V . This sets a limitation on the maximum value of R MEAS .R MEAS +ǒV K *0.1V ǓI SENSE+CSRǒV K *0.1V ǓI buswhere:CSR = Current Sensing Ratio taken from the SENSEFET data sheet.I bus = Max current through the SENSEFET.ENEnable is a high true logic input controlling the SENSEFET’s ON/OFF state. A logic high on EN turns the switch ON; a logic low turns it OFF.Bus turn-ON time is controlled by the FET’s input gate capacitance and the drive current applied to the gate.To minimize power consumption EN disables the internal gate drive current source and current mirroring circuitry whenever the SENSEFET is OFF.ENFigure 5. Typical ApplicationV DDV MEASPACKAGE DIMENSIONSTDFN8, 2x3CASE 511AK −01ISSUE ATOP VIEW SIDE VIEW BOTTOM VIEWFRONT VIEWA1Notes:(1) All dimensions are in millimeters.(2) Complies with JEDEC MO-229.SYMBOLMIN NOM MAX A 0.700.750.80A10.000.020.05A30.20 REFb 0.200.250.30D 1.90 2.00 2.10D2 1.30 1.40 1.50E 3.00E2 1.201.30 1.40e 2.900.50 TYP3.10L0.200.300.40A20.450.550.65Example of Ordering Information (Notes 2 − 5)Prefix Device #Suffix ORDERING INFORMATIONPart Number Temperature Range Package Quantity per Reel (Note 6)Package MarkingCAT2300VP2−GT3−40°C to +85°CTDFN3,000F3T2.All packages are RoHS −compliant (Lead −free, Halogen −free).3.The standard lead finish is NiPdAu pre −plated (PPF).4.The device used in the above example is a CAT2300VP2−GT3 (TDFN, NiPdAu, Tape & Reel, 3,000).5.For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.6.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.SENSEFET is a registered trademark of Semiconductor Components Industries, LLCPUBLICATION ORDERING INFORMATION分销商库存信息: ONSEMICAT2300VP2-GT3。

pc104工控主板说明书

pc104工控主板说明书本文旨在对PC104工控主板进行全面的介绍和说明,以帮助用户更好地了解和使用该产品。

以下是对PC104工控主板的详细说明:一、产品概述PC104工控主板是一种紧凑型的嵌入式计算机主板,采用标准的PC104规格设计,适用于各类工业控制和嵌入式应用场景。

本产品具有高性能、低功耗、稳定可靠等特点,是工业自动化领域的理想选择。

二、产品特点1. 紧凑型设计:采用PC104规格,尺寸小巧,方便安装和布线。

2. 高性能处理器:搭载XXXX处理器,功耗低,性能强悍,可以满足复杂的计算需求。

3. 多种接口:提供丰富的标准接口,包括USB、RS232、以太网等,方便与外部设备连接。

4. 良好的扩展性:支持多种扩展模块,包括扩展IO、采集卡等,可以满足不同应用场景的需求。

5. 可靠稳定:采用高质量元件,经过严格测试和质量控制,确保产品的稳定性和可靠性。

三、产品规格1. 处理器:XXXX处理器,主频XXXGHz。

2. 内存:标配4GB DDR4内存,支持最大扩展至16GB。

3. 存储:标配128GB固态硬盘,支持SATA接口。

4. 显示接口:支持VGA和HDMI双显接口,最大分辨率XXXX。

5. 网络接口:支持千兆以太网接口,可实现高速网络通信。

6. 扩展接口:提供4个USB接口、2个RS232串口、1个RS485串口、1个MINI-PCIE接口等,满足各类外设连接需求。

7. 工作温度:-20℃~70℃,适应各种恶劣环境。

四、使用说明1. 安装前请先阅读本说明书,了解产品特点和规格。

2. 安装时请确保主板与其他设备断电,并按照说明书中的接线图进行正确连线。

3. 使用时请注意产品的工作温度范围,避免高温或低温环境对产品性能产生影响。

4. 如需扩展功能,请按照本规格书提供的接口进行连接。

5. 如有故障或使用问题,请联系我们的技术支持团队寻求帮助。

五、注意事项1. 本产品严禁拆解或改装,否则将会导致保修失效。

CAT4238TD-GT3;中文规格书,Datasheet资料

CAT4238High Efficiency 10 LED Boost ConverterDescriptionThe CAT4238 is a DC/DC step−up converter that delivers an accurate constant current ideal for driving LEDs. Operation at a fixed switching frequency of 1 MHz allows the device to be used with small value external ceramic capacitors and inductor. LEDs connected in series are driven with a regulated current set by the external resistor R1. LED currents up to 40 mA can be supported over a wide range of input supply voltages up to 5.5 V, making the device ideal for battery−powered applications. The CAT4238 high−voltage output stage is perfect for driving mid−size and large panel displays containing up to ten white LEDs in series.LED dimming can be done by using a DC voltage, a logic signal, or a pulse width modulation (PWM) signal. The shutdown input pin allows the device to be placed in power−down mode with “zero”quiescent current.In addition to thermal protection and overload current limiting, the device also enters a very low power operating mode during “Open LED” fault conditions. The device is housed in a low profile (1mm max height) 5−lead thin SOT23 package for space critical applications.Features•Drives High V oltage LED Strings (38 V)•Up to 87% Efficiency•Low Quiescent Ground Current 0.6 mA•Adjustable Output Current•1 MHz Fixed Frequency Low Noise Operation•Soft Start “In−rush” Current Limiting•Shutdown Current Less than 1 m A•Open LED Overvoltage Protection•Automatic Shutdown at 1.9 V (UVLO)•Thermal Overload Protection•Thin SOT23 5−lead (1 mm Max Height)•These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS CompliantApplications•GPS Navigation Systems•Portable Media Players•Handheld Devices, Digital Cameras•Portable Game MachinesTSOT−23TD SUFFIXCASE 419AEPIN CONNECTIONSMUYMMARKING DIAGRAMDevice Package Shipping ORDERING INFORMATIONCAT4238TD−GT3TSOT−23(Pb−Free)Green*3,000/Tape & Reel MU = Specific Device CodeY = Production Year (Last Digit)M = Production Month (1−9, A, B, C)(Top View)VINSHDNSWGNDFB1* Lead Finish NiPdAuFigure 1. Typical Application CircuitL: Sumida CDC5D23B −470D: Central CMDSH05−4C2: Taiyo Yuden UMK212BJ224 (rated 50 V)Table 1. ABSOLUTE MAXIMUM RATINGSParametersRatings Units V IN , FB voltage −0.3 to +7V SHDN voltage −0.3 to +7V SW voltage (Note 1)up to 60V Storage Temperature Range −65 to +160_C Junction Temperature Range −40 to +150_C Lead Temperature300_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.The SW pin voltage is rated up to 39 V for external continuous DC voltage.Table 2. RECOMMENDED OPERATING CONDITIONSParametersRange Units V INup to 5.5V SW pin voltage0 to 38V Ambient Temperature Range −40 to +85_CNOTE:Typical application circuit with external components is shown above.Table 3. DC ELECTRICAL CHARACTERISTICS(V IN = 3.6 V, ambient temperature of 25°C (over recommended operating conditions unless otherwise specified))Symbol Parameter Test Conditions Min Typ Max UnitsI Q Operating Current V FB= 0.2 VV FB= 0.4 V (not switching)0.60.11.50.6mAI SD Shutdown Current V SHDN = 0 V0.11m A V FB FB Pin Voltage10 LEDs with I LED = 20 mA285300315mV I FB FB pin input leakage1m AI LED Programmed LED Current R1 = 10 WR1 = 15 WR1 = 20 W 28.51914.2530201531.52115.75mAV IH V IL SHDN Logic HighSHDN Logic LowEnable Threshold LevelShutdown Threshold Level0.40.80.71.5VF SW Switching Frequency0.8 1.0 1.3MHzDC Maximum Duty Cycle VIN = 3 V92%I LIM Switch Current Limit350450600mAR SW Switch “On” Resistance I SW = 100 mA 1.0 2.0WI LEAK Switch Leakage Current Switch Off, V SW = 5 V15m AThermal Shutdown150°CThermal Hysteresis20°C V UVLO Undervoltage Lockout (UVLO) Threshold 1.9V V OV-SW Overvoltage Detection Threshold40V V OCL Output Voltage Clamp“Open LED” with VIN = 5 V434548VPin DescriptionVIN is the supply input for the internal logic. The device is compatible with supply voltages down to 2.8 V and up to 5.5V. It is recommended that a small bypass ceramic capacitor (4.7 m F) be placed between the VIN and GND pins near the device. If the supply voltage drops below 1.9 V, the device stops switching.SHDN is the shutdown logic input. When the pin is tied to a voltage lower than 0.4 V, the device is in shutdown mode, drawing nearly zero current. When the pin is connected to a voltage higher than 1.5 V, the device is enabled.GND is the ground reference pin. This pin should be connected directly to the ground place on the PCB.SW pin is connected to the drain of the internal CMOS power switch of the boost converter. The inductor and the Schottky diode anode should be connected to the SW pin. Traces going to the SW pin should be as short as possible with minimum loop area. An over-voltage detection circuit is connected to the SW pin. When the voltage reaches 40V, the device enters a low power operating mode preventing the SW voltage from exceeding the maximum rating.FB feedback pin is regulated at 0.3 V. A resistor connected between the FB pin and ground sets the LED current according to the formula:I LED+0.3VR1The lower LED cathode is connected to the FB pin.Table 4. PIN DESCRIPTIONSPin #Name Function 1SW Switch pin. This is the drain of the internal power switch.2GND Ground pin. Connect the pin to the ground plane.3FB Feedback pin. Connect to the last LED cathode.4SHDN Shutdown pin (Logic Low). Set high to enable the driver.5VIN Power Supply input.Block DiagramDevice OperationThe CAT4238 is a fixed frequency (1 MHz), low noise,inductive boost converter that provides a constant current with excellent line and load regulation. The device uses a high-voltage CMOS power switch between the SW pin and ground to energize the inductor. When the switch is turned off, the stored energy in the inductor is released into the load via the Schottky diode.The on/off duty cycle of the power switch is internally adjusted and controlled to maintain a constant regulated voltage of 0.3 V across the feedback resistor connected to the feedback pin (FB). The value of the resistor sets the LED current accordingly (0.3 V/R 1).During the initial power-up stage, the duty cycle of the internal power switch is limited to prevent excessive in-rush currents and thereby provide a “soft-start” mode of operation.While operating from a Li −Ion battery, the device can deliver 20mA of load current into a string of up to 10 white LEDs. For higher input voltages, the LED current can be increased.In the event of an “Open LED” fault condition, where the feedback control loop becomes open, the output voltage will continue to increase. Once this voltage exceeds 40 V , an internal protection circuit will become active and place the device into a very low power safe operating mode where only a small amount of power is transferred to the output.This is achieved by pulsing the switch once every 6 m s and keeping it on for about 1 m s.Thermal overload protection circuitry has been included to prevent the device from operating at unsafe junction temperatures above 150°C. In the event of a thermal overload condition the device will automatically shutdown and wait till the junction temperatures cools to 130°C before normal operation is resumed.Light Load OperationUnder light load condition (under 2 mA) and with input voltage above 5.0 V , the CAT4238 driving 10 LEDs, the driver starts pulse skipping. Although the LED current remains well regulated, some lower frequency ripple may appear.Figure 3. Switching Waveform V IN = 5.0 V,I LED = 1.5 mAFigure 4. Quiescent Current vs. V IN(Not Switching)Figure 5. Quiescent Current vs. V IN(Switching)INPUT VOLTAGE (V)INPUT VOLTAGE (V)50751001251505.04.54.03.53.000.51.01.52.0Figure 6. FB Pin Voltage vs. TemperatureFigure 7. FB Pin Voltage vs. Output CurrentTEMPERATURE (°C)OUTPUT CURRENT (mA)150100500−50297298299300301302303290295300305310Figure 8. Switching Frequency vs. SupplyVoltageFigure 9. Switching WaveformsINPUT VOLTAGE (V)500 ns/div5.04.55.54.03.53.00.80.91.01.11.2Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )F B P I N V O L T AG E (m V )F B P I N V O L T AG E (m V )S W I T C H I N G F R E Q U E N C Y (M H z )SW 20V/divInductor Current 100mA/divVOUT AC coupled 500mV/div5.5Figure 10. LED Current vs. Input VoltageFigure 11. LED Current Regulation (10 mA)INPUT VOLTAGE (V)INPUT VOLTAGE (V)−1.0−0.50.51.0Figure 12. Efficiency vs. Load Current(10 LEDs)Figure 13. Efficiency vs. Input Voltage(10 LEDs)LED CURRENT (mA)INPUT VOLTAGE (V)6070809010060708090100Figure 14. Power −up with 10 LEDs at 20 mAFigure 15. Switch ON Resistance vs. InputVoltageINPUT VOLTAGE (V)5.55.04.54.03.53.000.51.01.52.0L E D C U R R E N T (m A )L E D C U R R E N T V A R I A T I O N (%)E F F I C I E N C Y (%)E F F I C I E N C Y (%)S W I T C H R E S I S T A N C E (W )Figure 16. Maximum Output Current vs. InputVoltageFigure 17. Shutdown Voltage vs. Input VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)1020304050600.20.40.60.81.0O U T P U T C U R R E N T (m A )S H U T D O W N V O L T A G E (V )Application InformationExternal Component Selection CapacitorsThe CAT4238 only requires small ceramic capacitors of 4.7m F on the input and 0.22 m F on the output. Under normal condition, a 4.7 m F input capacitor is sufficient. For applications with higher output power, a larger input capacitor of 10 m F may be appropriate. X5R and X7R capacitor types are ideal due to their stability across temperature range.InductorA 47 m H inductor is recommended for most of the CAT4238 applications. In cases where the efficiency is critical, inductances with lower series resistance are preferred. Inductors with current rating of 300 mA or higher are recommended for most applications. Sumida CDC5D23B −470 47 m H inductor has a rated current of 490mA and a series resistance (D.C.R.) of 420 m W typical.Schottky DiodeThe current rating of the Schottky diode must exceed the peak current flowing through it. The Schottky diode performance is rated in terms of its forward voltage at agiven current. In order to achieve the best efficiency, this forward voltage should be as low as possible. The response time is also critical since the driver is operating at 1MHz.Central Semiconductor Schottky diode CMDSH05−4(500mA rated) is recommended for most applications.LED Current SettingThe LED current is set by the external resistor R 1connected between the feedback pin (FB) and ground. The formula below gives the relationship between the resistor and the current:R 1+0.3VLEDcurrent Table 5. RESISTOR R 1 AND LED CURRENTLED Current (mA)R 1 (W )56010301520201525123010Open LED ProtectionIn the event of an “Open LED” fault condition, the CAT4238 will continue to boost the output voltage with maximum power until the output voltage reaches approximately 40 V . Once the output exceeds this level, the internal circuitry immediately places the device into a very low power mode where the total input power is limited to about 6 mW (about 1.6 mA input current with a 3.6 V supply). The SW pin clamps at a voltage below its maximum rating of 60 V . There is no need to use an external zener diode between V out and the FB pin. A 50 V rated C 2 capacitor is required to prevent any overvoltage damage in the open LED condition.Figure 18. Open LED Protection without ZenerSchottky 100 V(Central CMSH1−100)V INV OUTFigure 19. Open LED Switching Waveforms withoutZener2 m s/divS W 10 V /d i vFigure 20. Open LED Supply Current vs. V IN withoutZenerINPUT VOLTAGE (V)5.04.54.03.53.002.01.04.05.0S U P P L Y C U R R E N T (m A )5.53.0Figure 21. Open LED Output Voltage vs. V IN withoutZenerINPUT VOLTAGE (V)5.04.54.03.53.035404550O U T P U T V O L T A G E (V )5.555Dimming ControlThere are several methods available to control the LED brightness.PWM Signal on the SHDN PinLED brightness dimming can be done by applying a PWM signal to the SHDN input. The LED current is repetitively turned on and off, so that the average current is proportional to the duty cycle. A 100% duty cycle, with SHDN always high, corresponds to the LEDs at nominal current. Figure 22shows a 1kHz signal with a 50% duty cycle applied to the SHDN pin. The recommended PWM frequency range is from 100Hz to 2kHz.Figure 22. Switching Waveform with 1 kHz PWM onSHDN Filtered PWM SignalA filtered PWM signal used as a variable DC voltage can control the LED current. Figure 23 shows the PWM control circuitry connected to the CAT4238 FB pin. The PWM signal has a voltage swing of 0 V to 2.5 V . The LED current can be dimmed within a range from 0 mA to 20 mA. The PWM signal frequency can vary from very low frequency up to 100 kHz.Figure 23. Circuit for Filtered PWM Signal0 V2.5 V PWM Signal WA PWM signal at 0 V DC, or a 0% duty cycle, results in a max LED current of about 22 mA. A PWM signal with a 93% duty cycle or more, results in an LED current of 0mA.Figure 24. Filtered PWM Dimming (0 V to 2.5 V)L E D C U R R E N T (m A )2520151050102030405060708090100PWM DUTY CYCLE (%)Board LayoutThe CAT4238 is a high−frequency switching regulator. The traces that carry the high−frequency switching current have to be carefully layout on the board in order to minimize EMI, ripple and noise in general. The thicker lines on Figure25 show the switching current path. All these traces have to be short and wide enough to minimize the parasitic inductance and resistance. The loop shown on Figure25 corresponds to the current path when the CA T4238 internal switch is closed. On Figure 26 is shown the current loop,when the CAT4238 switch is open. Both loop areas should be as small as possible.Capacitor C1 has to be placed as close as possible to the V IN pin and GND. The capacitor C2 has to be connected separately to the top LED anode. A ground plane under the CAT4238 allows for direct connection of the capacitors to ground. The resistor R1 must be connected directly to the GND pin of the CA T4238 and not shared with the switchingcurrent loops and any other components. Figure 25. Closed−switch Current Loop Figure 26. Open−switch Current LoopFigure 27. Recommended PCB Layout分销商库存信息: ONSEMICAT4238TD-GT3。

毛家V2403系列无风扇x86工业级物联网嵌入式计算机产品介绍说明书

V2403SeriesFanless,rugged,ready-to-go x86Industrial IoT embeddedcomputersFeatures and Benefits•Intel Core-i Series processor with three performance options•-40to70°C(system and LTE)operating temperature•Dual CFast sockets for storing OS and OS backup•Triple mini-PCIe sockets for storage and wireless modules that supportmSATA,Wi-Fi,3G,LTE,GPS,and Bluetooth•Variety of interfaces:4serial ports,2Ethernet LAN ports,4DIs,4DOs,USB,HDMI,wireless•EN61000-6-2and EN61000-6-4certification;meets EMC standard for heavyindustry•Up to5Grms anti-vibration and100g/11ms anti-shock protection•Ready-to-run Debian8,Windows Embedded Standard7,and Windows10Embedded IoT Enterprise2016LTSB platforms•Moxa Proactive Monitoring utility for system hardware health monitoring•Moxa Smart Recovery utility to recover system from boot failure(W7E only)CertificationsIntroductionThe V2403Series fanless x86embedded computer is based on the Intel®3rd gen Core-i™Series processor,features the most reliable I/O design to maximize connectivity,and supports dual wireless modules,making it suitable for a diverse range of communication applications.The computer’s thermal design ensures reliable system operation in temperatures ranging from-40to70°C(with a special purpose Moxa wireless module installed).The V2403Series supports“Moxa Proactive Monitoring”for device I/O status monitoring and alerts,system temperature monitoring and alerts,and system power management.Monitoring system status closely makes it easier to recover from errors and provides the most reliable platform for your applications.Applications•Remote Terminal Unit(RTU)•Data acquisition•M2M communication(smart gateway)•Digital signage•Factory automation •In-vehicle monitor/data logger(transportation)•Programmable router•Energy usage optimization•Predictive maintenance•Asset managementAppearanceFront View Rear ViewSpecificationsComputerCPU V2403-C2Series:Intel®Celeron®Processor1047UE(2M cache,1.40GHz)V2403-C7Series:Intel®Core™i7-3517UE Processor(4M cache,up to2.80GHz) System Chipset Mobile Intel®HM65Express ChipsetGraphics Controller Intel®HD GraphicsSystem Memory Pre-installed Default4GB DDR3System Memory Slot SODIMM DDR3/DDR3L slot x1Supported OS Linux Debian8(Linux kernel v4.1)Windows Embedded Standard7(WS7E)32-bitWindows Embedded Standard7(WS7E)64-bitStorage Slot 2.5-inch HDD/SSD slots x1CFast slot x2mSATA slots x1Computer InterfaceEthernet Ports Auto-sensing10/100/1000Mbps ports(RJ45connector)x2Serial Ports RS-232/422/485ports x4,software selectable(DB9male)USB2.0USB2.0hosts x4,type-A connectorsAudio Input/Output Line in x1,Line out x1,3.5mm phone jackDigital Input DIs x4Digital Output DOs x4Expansion Slots mPCIe slot x2Video Output DVI-I x1,29-pin DVI-I connectors(female)HDMI x1,HDMI connector(type A)Wi-Fi Antenna Connector RP-SMA x2Cellular Antenna Connector SMA x2Number of SIMs2SIM Format MiniGPS Antenna Connector SMA x1Digital InputsIsolation3k VDCConnector Screw-fastened Euroblock terminalDry Contact On:short to GNDOff:openI/O Mode DISensor Type Dry contactWet Contact(NPN or PNP)Wet Contact(DI to COM)On:10to30VDCOff:0to3VDCDigital OutputsConnector Screw-fastened Euroblock terminalCurrent Rating200mA per channelI/O Type SinkVoltage24to40VDCLED IndicatorsSystem Power x1Storage x1LAN2per port(10/100/1000Mbps)Serial2per port(Tx,Rx)Serial InterfaceBaudrate50bps to921.6kbpsFlow Control RTS/CTS,XON/XOFF,ADDC®(automatic data direction control)for RS-485,RTSToggle(RS-232only)Isolation N/AParity None,Even,Odd,Space,MarkData Bits5,6,7,8Stop Bits1,1.5,2Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GNDRS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDPower ParametersInput Voltage9to36VDCPower Connector Terminal block(for DC models)Power Consumption(Max.) 3.51A@9VDC1.39A@24VDC0.93A@36VDCPower Consumption34W(max.)Physical CharacteristicsHousing AluminumIP Rating IP30Dimensions(with ears)275x63x154mm(10.83x2.47x6.06in) Dimensions(without ears)250x57x154mm(9.84x2.23x6.06in)Weight2,168g(4.82lb)Installation DIN-rail mounting(optional),Wall mounting(standard) Environmental LimitsOperating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMC EN55032/24,EN61000-6-2/-6-4EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:4kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:10V/mIEC61000-4-4EFT:Power:2kV;Signal:1kVIEC61000-4-5Surge:Power:2kV;Signal:1kVIEC61000-4-6CS:1VIEC61000-4-8PFMFSafety EN60950-1,UL508,UL60950-1Shock IEC60068-2-27Vibration IEC60068-2-64DeclarationGreen Product RoHS,CRoHS,WEEEMTBFTime329,398hrsStandards Telcordia(Bellcore),GBWarrantyWarranty Period3yearsDetails See /warrantyPackage ContentsDevice1x V2403Series computerInstallation Kit1x wall-mounting kitCable1x terminal block to power jack converter Documentation1x document and software CD1x quick installation guide1x warranty cardDimensionsOrdering InformationModel Name CPU Memory(Default)OS CFast(CTO)Backup CFast(CTO)SSD/HDD Tray(CTO)USIM SlotAntennaConnectorsOperatingTemp.V2403-C2-T Celeron1047UE4GB1(Optional)1(Optional)1(Optional)––-40to70°CV2403-C2-W-T Celeron1047UE4GB1(Optional)1(Optional)1(Optional)––-40to70°CV2403-C3-T i3-3217UE4GB1(Optional)1(Optional)1(Optional)––-40to70°C V2403-C3-W-T i3-3217UE4GB1(Optional)1(Optional)1(Optional)25-40to70°C V2403-C7-T i7-3517UE4GB1(Optional)1(Optional)1(Optional)25-40to70°C V2403-C7-W-T i7-3517UE4GB1(Optional)1(Optional)1(Optional)25-40to70°CV2403-C2-T-LX Celeron1047UE4GB8GB1(Optional)1(Optional)––-40to70°CV2403-C2-T-W7E Celeron1047UE4GB8GB1(Optional)1(Optional)––-40to70°CV2403-C2-T-W7E1Celeron1047UE8GB32GB1(Optional)64GB MLC––-40to70°CAccessories(sold separately)Battery KitsRTC Battery Kit Lithium battery with built-in connectorPower AdaptersPWR-24270-DT-S1Power adapter,input voltage90to264VAC,output voltage24V with2.5A DC loadPower CordsPWC-C7AU-2B-183Power cord with Australian(AU)plug,2.5A/250V,1.83mPWC-C7CN-2B-183Power cord with two-prong China(CN)plug,1.83mPWC-C7EU-2B-183Power cord with Continental Europe(EU)plug,2.5A/250V,1.83mPWC-C7UK-2B-183Power cord with United Kingdom(UK)plug,2.5A/250V,1.83mPWC-C7US-2B-183Power cord with United States(US)plug,10A/125V,1.83mDIN-Rail Mounting KitsDK-DC50131-01DIN-rail mounting kit,6screwsWall-Mounting KitsV2400Isolated Wall Mount Kit Wall-mounting kit with isolation protection,2wall-mounting brackets,4screwsStorage KitsFK-75125-02Storage bracket,4large silver screws,4soft washers,4small sliver bronze screws,1SATA powercable,4golden spacers(only for the V2406and V2426)AntennasANT-GPS-OSM-05-3M BK Active GPS antenna,26dBi,1572MHz,L1band antenna for GPSANT-LTEUS-ASM-01GSM/GPRS/EDGE/UMTS/HSPA/LTE,omni-directional rubber duck antenna,1dBiANT-WDB-ARM-02 2.4/5GHz,omni-directional rubber duck antenna,2dBi,RP-SMA(male)ANT-WCDMA-ASM-1.5GSM/GPRS/EDGE/UMTS/HSPA,omni-directional rubber duck antenna,1.5dBiANT-LTE-ASM-02GPRS/EDGE/UMTS/HSPA/LTE,omni-directional rubber duck antenna,2dBiWi-Fi Wireless ModulesV2403Wi-Fi mini Card SparkLAN WPEA-252NI Wi-Fi mini card,4black screws©Moxa Inc.All rights reserved.Updated Jun12,2019.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

PT4104A;PT4106A;PT4105C;PT4105A;PT4104C;中文规格书,Datasheet资料

For technical support and more information, see inside back cover or visit /powertrends15 Watt Isolated DC-DC ConverterSLTS020A(Revised 1/15/2001)•Input Voltage Range:18V to 40V •1500 VDC Isolation •Low Profile •Current Limit•Short-Circuit Protection •Over-T emperature Shutdown •UL1950 recognized •CSA 22.2 950 certified •Meets EN60950The PT4100—24V series of dc/dc converters provide 18 Watts/in 3 of isolated power in a single low-profile module. De-signed to operate from a standard 24V telecom bus, these modules employ switching frequencies of up to 850kHz,planar magnetics, and surface-mount con-struction. They are designed for T elecom,Industrial, Computer, Medical, and other distributed power applications that require input-to-output isolation.For technical support and more information, see inside back cover or visit /powertrendsTypical Characteristics15 Watt Isolated DC-DC ConverterPACKAGAddendum-Page 1PACKAGING INFORMATIONOrderable DeviceStatus(1)Package Type PackageDrawing Pins Package QtyEco Plan(2)Lead/Ball Finish MSL PeaPT4104A NRND DIP MODULE EGD 616Pb-Free (RoHS)Call TI N / A for PkgPT4106ANRNDDIP MODULEEGD616Pb-Free (RoHS)Call TIN / A for Pkg(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2)Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.t information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable fo Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retard in homogeneous material)(3)MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate inf continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical an TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for releasIn no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Cu/IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connctivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated分销商库存信息:TIPT4104A PT4106A PT4105C PT4105A PT4104C PT4104CT。

DPtech FW1000系列应用防火墙安装手册v2.01

DPtech FW1000 系列应用防火墙安装手册

2.2.4 抗干扰要求............................................................................................................................... 3 2.2.5 防雷击要求............................................................................................................................... 3 2.2.6 接地要求................................................................................................................................... 3 2.2.7 布线要求................................................................................................................................... 3 2.3 安装工具......................................................................................................................................4

杭州迪普科技有限公司为客户提供全方位的技术支持。 通过杭州迪普科技有限公司代理商购买产品的用户,请直接与销售 代理商联系;直接向杭州迪普科技有限公司购买产品的用户,可直 接与公司联系。

Google Cloud VPN 配置指南说明书

2. On the VPC network page, click on Create VPC Network. 3. Fill in a Name and, optionally, a Description.

ISAKMP peer. 14. Copy this and save it somewhere secure 15. Under Routing options, choose Policy-based. 16. Under Remote network IP ranges, enter the internal IP address range of your router. 17. Under Local IP ranges, enter the local-address-selector that you created earlier.

5. Click on Create to create the VPC network.

6. Once the VPC network has been created, you will be returned to the Home Page. On the Home Page, from the menu on the left under Networking, select Hybrid Connectivity, then VPN.

C613-02084-00 REV A

Introduction | Page 3

Google Cloud VPN

Static routing

To configure static routing to a Google Cloud VPN, use the following steps: 1. Log in to your Google Cloud Account. Navigate to the Home Page. From the menu on the left,

APM32F407 417xExG 用户手册说明书