小度写范文[数字计算机算术数据通路设计:使用Verilog语言]计算机数据通路模板

数据通路实验报告

数据通路实验报告一、实验目的本实验旨在通过设计与实现一个简单的数据通路,加深对数据通路的理解,并且通过实验验证所学知识的准确性和实用性。

二、实验器材和软件实验器材:计算机、VHDL开发板、配套接口线实验软件:Quartus II三、实验内容1.设计基本数据通路的单元模块,并对其进行仿真验证。

2.将各单元模块综合到一起,形成完整的数据通路,并对其进行逻辑分析和综合。

3.编写测试代码,对数据通路进行功能验证。

四、实验步骤1.设计基本数据通路的单元模块首先,根据实验要求,设计并实现各个基本数据通路的单元模块,如加法器、减法器、乘法器等。

根据需要,还可以设计其他辅助模块,如多路选择器、寄存器等。

在设计单元模块时,需要根据实验要求确定输入和输出信号的位数,并且保证设计的模块功能的准确性和完整性。

2.仿真验证单元模块利用Quartus II提供的ModelSim进行仿真验证。

将设计好的单元模块进行连接,并通过给定的测试向量,验证各个模块的功能是否符合预期。

3.综合设计数据通路将各个单元模块综合到一起,形成完整的数据通路。

在综合的过程中,需要注意各个模块之间的连接和信号的传递。

对综合后的数据通路进行逻辑分析和综合,检查是否存在逻辑错误,并根据需要进行优化处理。

4.编写测试代码根据数据通路的功能,编写相应的测试代码,对数据通路进行功能验证。

测试代码中应包含各种不同类型的测试用例,以确保数据通路的正确性。

五、实验结果分析经过各个步骤的设计与实验,我们成功实现了一个简单的数据通路,并且通过测试代码的运行,验证了数据通路的功能的正确性。

六、实验心得通过本次实验,我深入了解了数据通路的设计与实现过程,加深了对数据通路的理解。

通过实践操作,掌握了Quartus II软件的使用技巧,提高了自己的综合设计能力。

在实验过程中,我遇到了一些问题,通过与同学和老师的交流,顺利解决了这些问题。

通过自己的努力和团队合作,成功完成了本次实验,并且对数据通路有了更深入的认识。

verilog计数器设计原理

Verilog计数器设计原理1. 介绍计数器是一种常见的数字电路,用于计算和记录事件的数量。

在数字系统中,计数器通常用于生成时钟信号、控制状态机、实现频率分频等应用。

Verilog是一种硬件描述语言,可以用于设计和仿真数字电路。

本文将详细介绍与Verilog计数器设计相关的基本原理。

2. 计数器的基本概念计数器是一种能够在输入脉冲信号的作用下进行累加或递减操作的数字电路。

它通常由触发器和逻辑门组成,触发器用于存储和传递数据,逻辑门用于控制触发器的工作状态。

2.1 同步计数器同步计数器是通过时钟信号来同步各个触发器的状态转换,以实现数据的累加或递减操作。

它包含一个时钟输入端(CLK)和一个复位输入端(RST)。

2.1.1 同步正向计数器同步正向计数器是最简单的同步计数器之一,它能够在每个上升沿时钟信号到达时进行累加操作。

2.1.1.1 原理同步正向计数器由多个触发器和逻辑门组成,其中每个触发器都有一个时钟输入端和一个复位输入端。

当时钟信号的上升沿到达时,触发器的状态将根据输入信号进行更新。

具体的原理如下:1.初始化:将计数器的初始值设置为0。

2.时钟边沿检测:当时钟信号的上升沿到达时,进入下一步操作。

3.累加操作:根据触发器的当前状态进行累加操作。

如果触发器为0,则变为1;如果触发器为1,则变为0。

4.检测溢出:如果最高位触发器由1变为0,则表示计数溢出,需要将其他低位触发器进行进位操作。

2.1.1.2 Verilog代码示例以下是一个4位同步正向计数器的Verilog代码示例:module synchronous_counter(input wire clk,input wire rst,output wire [3:0] count);reg [3:0] count;always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule2.1.2 同步递减计数器同步递减计数器是同步正向计数器的一种扩展,它能够在每个上升沿时钟信号到达时进行递减操作。

verilog语言及程序设计

verilog语言及程序设计Verilog语言及程序设计1.引言1.1 目的本文档旨在提供Verilog语言及程序设计的详细说明和指导,帮助读者了解Verilog语言的基本概念、语法和编程技巧,以及如何设计和开发Verilog程序。

1.2 背景Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统的行为和结构。

它广泛应用于硬件设计、逻辑仿真和电路验证等领域。

Verilog可以用于设计各种数字系统,从简单的逻辑门到复杂的处理器和通信接口。

2.Verilog语言基础2.1 Verilog简介2.1.1 Verilog的历史2.1.2 Verilog的应用领域2.2 Verilog的基本元素2.2.1 模块(module)2.2.2 端口(port)2.2.3 信号(signal)2.2.4 注释(comment)3.Verilog语法和语句3.1 模块声明与实例化3.1.1 模块声明3.1.2 模块实例化3.2 数据类型3.2.1 整数类型(integer)3.2.2 实数类型(real)3.2.3 位向量类型(bit vector)3.2.4 枚举类型(enum)3.3 运算符3.3.1 算术运算符3.3.2 关系运算符3.3.3 逻辑运算符3.3.4 位运算符3.3.5 赋值运算符3.4 控制语句3.4.1 if语句3.4.2 case语句3.4.3 for循环语句3.4.4 while循环语句4.Verilog模块设计4.1 模块设计流程4.1.1 需求分析4.1.2 模块接口设计4.1.3 数据流图设计4.1.4 代码实现4.1.5 仿真与验证4.2 常见模块设计实例4.2.1 时钟分频器4.2.2 状态机4.2.3 寄存器堆4.2.4 串行通信接口5.高级Verilog编程技巧5.1 参数化模块设计5.2 位向量操作技巧5.3 时序逻辑设计5.4 RTL设计规范5.5 验证技术和方法6.附件7.法律名词及注释7.1 版权(Copyright)在法律上,版权是指对原创作品的独占性控制权,包括复制、分发和修改等权力。

计算机组成CPU数据通路verilog实验报告.doc

计算机组成与系统结构实验报告院(系):计算机科学与技术学院专业班级:学号:姓名:同组者:指导教师:实验时间: 2012 年 5 月 23 日实验目的:完成处理器的单周期cpu的设计。

实验仪器:PC机(安装Altebra 公司的开发软件 QuartusII)一台实验原理:控制器分为主控制器和局部ALU控制器两部分。

主控制器的输入为指令操作码op,输出各种控制信号,并根据指令所涉及的ALU运算类型产生ALUop,同时,生成一个R-型指令的控制信号R-type,用它来控制选择将ALUop输出作为ALUctr信号,还是根据R-型指令中的func字段来产生ALUctr信号。

实验过程及实验记录:1.设计过程:第一步:分析每条指令的功能,并用RTL来表示。

第二步:根据指令的功能给出所需的元件,并考虑如何将它们互连。

第三步:确定每个元件所需控制信号的取值。

第四步:汇总各指令涉及的控制信号,生成所反映指令与控制信号之间的关系图。

第五步:根据关系表,得到每个控制信号的逻辑表达式,据此设计控制电路。

2.完成代码的编写,并调试运行。

1)controlmoduleControl(op,func,Branch,Jump,RegDst,ALUSrc,ALUctr,MemtoReg, RegWr,MemWr,ExtOp);input [5:0] op,func;output regBranch,Jump,RegDst,ALUSrc,MemtoReg,RegWr,MemWr,ExtOp; output reg [2:0] ALUctr;always @(op)case(op)6'b000000:beginBranch=0;Jump=0;RegDst=1;ALUSrc=0;MemtoReg=0;RegWr=1;MemWr =0;case(func)6'b100000:ALUctr=3'b001;6'b100010:ALUctr=3'b101;6'b100011:ALUctr=3'b100;6'b101010:ALUctr=3'b111;6'b101011:ALUctr=3'b110;endcaseend6'b001101:beginBranch=0;Jump=0;RegDst=0;ALUSrc=1;MemtoReg=0;RegWr=1;MemWr =0;ExtOp=0;ALUctr=3'b010;end6'b001001:beginBranch=0;Jump=0;RegDst=0;ALUSrc=1;MemtoReg=0;RegWr=1;MemWr =0;ExtOp=1;ALUctr=3'b000;end6'b100011:beginBranch=0;Jump=0;RegDst=0;ALUSrc=1;MemtoReg=1;RegWr=1;MemWr =0;ExtOp=1;ALUctr=3'b000;end6'b101011:beginBranch=0;Jump=0;ALUSrc=1;RegWr=0;MemWr=1;ExtOp=1;ALUctr=3' b000;end6'b000100:beginBranch=1;Jump=0;ALUSrc=0;RegWr=0;MemWr=0;ALUctr=3'b100; end6'b000010:beginBranch=0;Jump=1;RegWr=0;MemWr=0;endendcaseendmodule2)数据通路DataRoadmoduleDataRoad(Run,Clk,RegWr,MemWr,MemtoReg,RegDst,Branch,Jump,E xtOp,ALUctr,ALUSrc,busA,busB,busW,Instruction,Reg0,Reg1,Re g2,Reg3,Reg4,Mem1,Mem2,Mem3,Result,Im);inputRun,Clk,RegWr,MemWr,MemtoReg,RegDst,Branch,Jump,ExtOp,ALUS rc;input [2:0] ALUctr;output [31:0]Instruction,busA,busB,busW,Reg0,Reg1,Reg2,Reg3,Reg4,Mem1,M em2,Mem3,Result,Im;wire [31:0] busC,DataOut;wire [15:0] im;wire [4:0] Rs,Rd,Rt;wire Overflow,Zero;QZL qzl(Clk,Branch,Jump,Zero,Instruction,Run);assign Rs=Instruction[25:21];assign Rt=Instruction[20:16];assign Rd=Instruction[15:11];assign im=Instruction[15:0];Registerregister(Run,RegWr,Overflow,RegDst,Rd,Rs,Rt,busW,busA,busB ,Clk,Reg0,Reg1,Reg2,Reg3,Reg4);ALU alu(busA,busC,ALUctr,Zero,Overflow,Result);DataMem(Run,MemWr,Clk,busB,DataOut,Result,Mem1,Mem2,Mem3); MUX mux1(ALUSrc,busB,Im,busC);MUX mux2(MemtoReg,Result,DataOut,busW);Extender ext(im,Im,ExtOp);endmodule3)取指令module QZL(Clk,Branch,Jump,Zero,Instruction,Run);input Clk,Branch,Jump,Zero,Run;output [31:0] Instruction;wire [4:0] addmem;reg [29:0] PC;wire [29:0] Newpc,pc_1,pc_2,pc_3,pc_12,imm30;wire Branch_Zero;assign addmem={PC[2:0],2'b00};InsMem GetIns(addmem,Instruction);always @(negedge Clk)if(Run==1)beginPC<=Newpc;endelsebeginPC<=0;endassign pc_1=PC+1;assign imm30={{14{Instruction[15]}},Instruction[15:0]}; assign pc_2=pc_1+imm30;assign pc_3={PC[29:26],Instruction[25:0]};assign Branch_Zero=Branch&Zero;MUX m1(Branch_Zero,pc_1,pc_2,pc_12);MUX m2(Jump,pc_12,pc_3,Newpc);endmodulemodule InsMem(addmem,Instruction);input [4:0] addmem;output reg[31:0] Instruction;reg [31:0] Mem[31:0];always @(*)beginMem[0]<={6'b100011,5'b00000,5'b00001,5'b00000,5'b00000,6'b 000001};Mem[4]<={6'b100011,5'b00000,5'b00010,5'b00000,5'b00000,6'b 000010};Mem[8]<={6'b000000,5'b00001,5'b00010,5'b00011,5'b00000,6'b 100000};Mem[12]<={6'b101011,5'b00000,5'b00011,5'b00000,5'b00000,6' b000010};Mem[16]<={6'b001101,5'b00100,5'b00100,5'b11111,5'b11111,6' b111111};Mem[20]<={6'b000000,5'b00011,5'b00010,5'b00010,5'b00000,6' b100010};Mem[24]<={6'b000100,5'b00010,5'b00001,5'b00000,5'b00000,6' b001000};Mem[28]<={6'b000010,5'b00000,5'b00000,5'b00000,5'b00000,6' b000000};endalways @(*)。

Verilog语言描述常见电路结构范例

Verilog语言描述常见电路结构范例组合逻辑常见的组合逻辑有:算术逻辑部件、多路选择器、编码器、优先编码器、译码器和比较器等。

逻辑结构控制使用括号可以改变组合逻辑的结构。

虽然EDA工具可以对组合逻辑设计进行重新优化组合,但在Verilog 描述中使用括号可以降低EDA工具的压力,并且减少工具的综合时间。

在下面的例子中,虽然y2和y1的功能是一样的,但y1会使用三级加法器,使用括号的y2只使用二级加法器。

always @ (a1 or a2 or b1 or b2 or c1 or c2 or d1 or d2) beginy1 = a1 + b1 + c1 + d1;y2 = (a2 + b2) + (c2 + d2);end二选一多路选择器下面给出了三种描述2:1 MUX 的方法。

y1是通过条件赋值语句实现的,y2和y3都是通过if语句实现的。

wire y1 = sel1? a1: b1;always @ (a2 or a3 or b2 or b3 or sel2 or sel3) beginy2 = b2;if (sel2) y2 = a2;if (sel3) y3 = a3;else y3 = b3;end四选一多路选择器用Verilog描述4:1 MUX 可以有如下方法:一个if语句加多个else if从句嵌套if 语句case 语句always @ (a or b or c or d or sel) beginif (sel == 2'b00) y = a;else if (sel == 2'b01) y = b;else if (sel == 2'b10) y = c;else y = d;endalways @ (a or b or c or d or sel) beginif (sel[1] == 0)if (sel[0] == 0) y = a;else y = b;elseif (sel[0] == 0) y = c;else y = d;endalways @ ( a or b or c or d or sel) begincase (sel)2'b00: y = a;2'b01: y = b;2'b10: y = c;2'b11: y = d;default: y = a;endcaseend八选一多路选择器描述8:1 MUX 最好使用case 语句always @ ( a0 or a1 or a2 or a3 or a4 or a5 or a6 or a7 or sel) begincase (sel)0: y = a0;1: y = a1;2: y = a2;3: y = a3;4: y = a4;5: y = a5;6: y = a6;7: y = a7;default: y = a0;endcaseend8:3编码器编码器可以将多个离散的信号用编码表示出来,比如3位的编码可以表示8个信号。

基于VerilogHDL的通信系统设计 第6章 数字调制与解调系统设计

6-4-2 2-PSK调制的Verilog HDL实现

根据PSK调制原理,这里给出采用键控法来实现2-PSK的Verilog HDL实现。

基于Verilog HDL的通信系统设计

6-4-3 2-PSK解调原理

2-PSK解调通常采用相干解调的方式,其解调原理框图如 图6-24所示。

已调PSK 信号

BPF

ppm_de x rst clk inst

图6-40 PPM解调电路符号

y

基于Verilog HDL的通信系统设计

6-7 本章小结

本章介绍最基本的三种调制形式—ASK、PSK、FSK的 基本原理及其Verilog HDL实现,然后由二进制调制进入多进 制调制,着重介绍了QPSK的原理及其实现,最后介绍了PPM (脉冲调制的一种),脉冲调制有别于前面介绍的几种调制 形式,脉冲调制的载波是离散的脉冲串,而前面介绍的调制 形式,载波采用的是连续波。由于篇幅有限,本章介绍的几 种调制是常见的、基本的调制形式,可以作为更复杂调制形 式的基础。

6-3-2 2-FSK调制的Verilog HDL实现

基于Verilog HDL的通信系统设计

6-3-3 2-FSK解调原理

二进制数字频率键控(2-FSK)信号常用的解调方法有3 种:

同步检测法。 过零检测法。 差分检波法。

基于Verilog HDL的通信系统设计

6-4 PSK调制与解调系统的设计

a

LPF

b

抽样判决 cp(t) 抽样判决

c

cos c t

载波同步

Hale Waihona Puke 图6-24 2-PSK相干解调原理框图

基于Verilog HDL的通信系统设计

verilog 算数指令

verilog 算数指令

在Verilog HDL语言中,算术指令有加法运算符(+)、减法运算符(-)、乘法运算符(×)、除法运算符(/)、模运算符(%)等。

下面以向量算术右移(SRAV)与向量逻辑右移(SRLV)为例进行说明:

- 算术右移:将操作数右移$s$位,并且在左边空出来的位置补$s$位操作数的符号。

对于算术右移操作来说,将二进制的数值左移$n$位等同于将原来的数值除$2^n$。

- 逻辑右移:将操作数右移$s$位,并且在左边空出来的位置补$s$位0,忽略操作数的符号。

在实际应用中,可以根据具体需求选择合适的算术指令,并编写相应的Verilog代码。

如需了解更多Verilog相关内容,请继续向我提问。

常用数字处理算法的Verilog实现

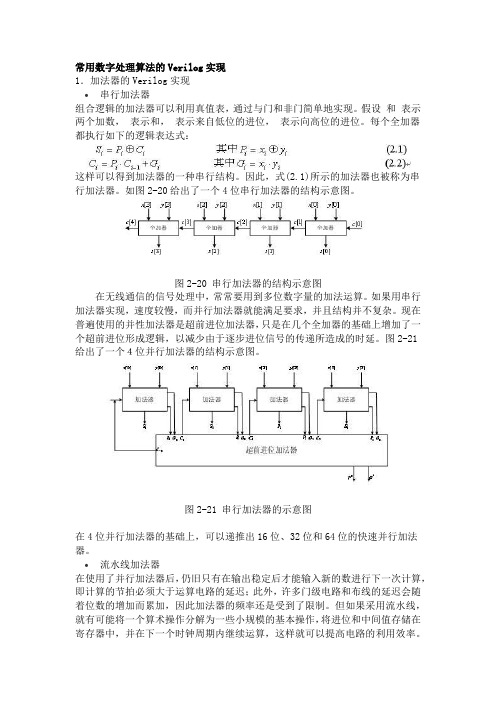

常用数字处理算法的Verilog实现常用数字处理算法的Verilog实现1.加法器的Verilog实现•串行加法器组合逻辑的加法器可以利用真值表,通过与门和非门简单地实现。

假设和表示两个加数,表示和,表示来自低位的进位,表示向高位的进位。

每个全加器都执行如下的逻辑表达式:这样可以得到加法器的一种串行结构。

因此,式(2.1)所示的加法器也被称为串行加法器。

如图2-20给出了一个4位串行加法器的结构示意图。

图2-20 串行加法器的结构示意图在无线通信的信号处理中,常常要用到多位数字量的加法运算。

如果用串行加法器实现,速度较慢,而并行加法器就能满足要求,并且结构并不复杂。

现在普遍使用的并性加法器是超前进位加法器,只是在几个全加器的基础上增加了一个超前进位形成逻辑,以减少由于逐步进位信号的传递所造成的时延。

图2-21给出了一个4位并行加法器的结构示意图。

图2-21 串行加法器的示意图在4位并行加法器的基础上,可以递推出16位、32位和64位的快速并行加法器。

•流水线加法器在使用了并行加法器后,仍旧只有在输出稳定后才能输入新的数进行下一次计算,即计算的节拍必须大于运算电路的延迟;此外,许多门级电路和布线的延迟会随着位数的增加而累加,因此加法器的频率还是受到了限制。

但如果采用流水线,就有可能将一个算术操作分解为一些小规模的基本操作,将进位和中间值存储在寄存器中,并在下一个时钟周期内继续运算,这样就可以提高电路的利用效率。

将流水线规则应用于FPGA中,只需要很少或根本不需要额外的成本。

这是因为每个逻辑单元都包含两个触发器,大多数情况下这两个触发器或者没有用到,或者用于存储布线资源,那么就可以利用其来实现流水线结构。

如果采用了流水线后,加法器的速度仍然不能满足需要的话,可以采用第3章中将会提到的串并转换来进一步提高计算的并行度。

由于一个slice中有两个触发器,还需要有1个触发器来作为进位输出,那么采用级流水线,就可以构造一个最大位数为位的加法器。

Verilog 开发经验总结说明书

Verilog 开发经验总结●以硬件为基础的原则Verilog是硬件描述语言,所谓描述就是是在在描绘已经设计好的电路。

尤其是在刚开始学习HDL时,还没有能直接把语言对应到具体电路的能力,更不能上手直接写Verilog代码。

所以最优方案是先设计好硬件电路,再按照电路编写Verilog。

●模块化思想这个思想不仅仅是Verilog的开发了,就算是C语言甚至现在的超高级语言,也一直在强调封装的概念。

Verilog开发遵循的是自顶向下的模块化设计,思路基本是从最终功能不断细分,直到Verilog可以很直接地描述最基础的硬件单元,例如加法器,移位寄存器等等。

模块划分一定要尽量细,功能单一,且一定要留出使能、复位等接口以便于系统搭建。

说明以下,所谓Verilog可直接描述指的是按照规范描述出来的电路,开发工具能够很清晰地理解所要描述的功能,而不会发生误解等现象。

一个只使用编译器能理解的代码开发的电路,错误率会大大降低。

相反,如果功能划分不够清晰,使得一个模块的功能过于庞杂,不仅描述困难,编译器也可能产生很大的误解。

把握编译器的理解方式是有助于做Verilog的开发的,但这就需要一个长远的积累了,我在最后会给出一些例子。

●时序电路与逻辑电路完全分开Verilog中除了数据流模型和门级模型以外,最常用的是always即行为级模型描述电路。

一个always块可以理解为一个电路,或者实物上的一个芯片。

所以不要在一个always里杂糅时序电路和逻辑电路,那样很可能导致编译器综合出一些奇葩的结果。

时序always模块的敏感变量有且最多两个,一个是时钟边沿,一个是复位边沿,没有再多的敏感变量了。

组合逻辑always中敏感变量列表必须包含该模块所有涉及到的变量,或者直接用(*)代替,个人推荐后者。

●时序always块编写规范在时序always中,统一使用非阻塞赋值<=,因为时序always中在赋值号左侧的变量是真实的触发器,非阻塞赋值在触发时是同时赋值的,这很符合触发器在上升沿到来后同时将D输出到Q的实际情况。

计算机组成原理实验报告心得体会

计算机组成原理实验报告心得体会一、引言在计算机组成原理实验中,我有幸参与了多次实验,涵盖了CPU的设计与模拟、数据通路与控制器的实现、存储器的设计与测试等多个方面。

通过这些实验,我深刻认识到了计算机组成原理在实际应用中的重要性,同时也收获了许多宝贵的经验和心得体会。

二、CPU的设计与模拟通过这次实验,我深入了解了CPU的组成和原理。

我首先完成了对CPU的整体设计,包括指令集、指令译码、数据通路等方面的设计。

然后,我使用多种模拟软件,如Proteus和Logisim,对我设计的CPU进行模拟验证。

这个过程非常有趣,我能够通过模拟软件来观察CPU的内部执行过程,了解每个时钟周期中各个部件的工作情况。

通过实验,我深刻认识到了CPU对于计算机运行的关键作用,同时也意识到了CPU设计和优化的重要性。

三、数据通路与控制器的实现数据通路和控制器的实现是计算机组成原理中的核心部分之一。

在实验中,我使用Verilog语言进行了数据通路和控制器的设计和实现。

我首先对数据通路进行了拓扑图的设计,并使用Verilog语言将其转换为硬件描述。

接着,我设计了对应的控制器,实现了对数据通路的控制和调度。

通过这个实验,我深刻理解到了数据通路和控制器之间的紧密联系,以及二者的协同工作是如何实现计算功能的。

四、存储器的设计与测试存储器在计算机系统中具有关键的地位。

在实验中,我使用Verilog 语言设计了存储器的模块,并进行了相应的功能测试。

我设计了读取和写入操作,同时进行了多个读写操作的并发测试。

通过实验,我深刻认识到了存储器的重要性和设计原则,也意识到了存储器访问速度和容量的影响对于计算机性能的重要性。

五、其他实验心得在以上的实验之外,我还参与了其他一些实验,如中断、流水线和指令缓存等的设计与实现。

这些实验拓宽了我的视野,让我了解到计算机组成原理在实际应用中的诸多问题和挑战。

在实验过程中,我也遇到了许多困难,但通过团队合作和导师的帮助,我最终找到了解决问题的方法。

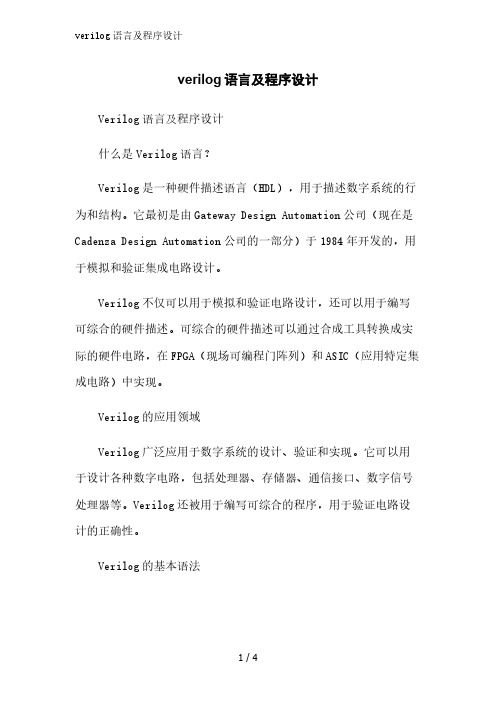

verilog语言及程序设计精简版范文

verilog语言及程序设计Verilog语言及程序设计什么是Verilog语言?Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它最初是由Gateway Design Automation公司(现在是Cadenza Design Automation公司的一部分)于1984年开发的,用于模拟和验证集成电路设计。

Verilog不仅可以用于模拟和验证电路设计,还可以用于编写可综合的硬件描述。

可综合的硬件描述可以通过合成工具转换成实际的硬件电路,在FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)中实现。

Verilog的应用领域Verilog广泛应用于数字系统的设计、验证和实现。

它可以用于设计各种数字电路,包括处理器、存储器、通信接口、数字信号处理器等。

Verilog还被用于编写可综合的程序,用于验证电路设计的正确性。

Verilog的基本语法Verilog语言的基本语法与C语言类似,包括模块定义、端口声明、信号声明、组合逻辑、时序逻辑等。

下面是一个简单的Verilog模块的例子:verilogmodule MyModule (input wire clk,input wire rst,input wire in_data,output wire out_data);reg [7:0] reg1;always (posedge clk or posedge rst) beginif (rst)reg1 <= 8'b0;elsereg1 <= reg1 + in_data;endassign out_data = reg1;endmodule上面的例子定义了一个名为`MyModule`的Verilog模块,有4个端口:`clk`(时钟),`rst`(复位),`in_data`(输入数据),`out_data`(输出数据)。

其中的`reg1`是一个8位的寄存器,使用时序逻辑进行更新。

verilog编程实例

verilog编程实例我们需要明确这个电路的功能和设计要求。

假设我们需要实现一个4位二进制加法器,即输入两个4位的二进制数,输出它们的和。

为了简化问题,我们先考虑只有无符号整数的加法,即只需要实现两个正整数的相加。

接下来,我们可以使用Verilog语言来描述这个电路的结构和行为。

我们首先声明输入端口和输出端口的位宽,即4位。

然后,我们定义一个module,命名为"binary_adder"。

在这个module中,我们定义了两个4位的输入信号a和b,以及一个4位的输出信号sum。

同时,我们还定义了一个内部信号carry,用于记录进位信息。

在module的主体部分,我们使用assign语句来实现信号之间的逻辑关系。

具体地,我们可以通过逐位相加的方式,将输入信号a和b的每一位与进位carry相加,并将结果存储在输出信号sum的对应位上。

同时,我们还需要更新进位carry的值,以确保加法运算的正确性。

为了实现这个逻辑,我们可以使用Verilog中的加法运算符"+"和逻辑与运算符"&"。

通过对输入信号的每一位进行逐位运算,我们可以得到输出信号sum的每一位的值。

同时,我们还需要根据输入信号和进位carry的值,计算出新的进位carry的值。

在实际的Verilog编程中,我们需要注意信号的声明和赋值的顺序。

一般而言,我们需要先声明信号,然后再通过assign语句对信号进行赋值。

这样可以确保信号的值能够正确传递和计算。

完成Verilog代码的编写后,我们需要使用相应的仿真工具来验证电路的功能。

常用的仿真工具有ModelSim和Xilinx ISE等。

通过仿真工具,我们可以为输入信号a和b设置不同的值,并观察输出信号sum的变化。

通过比较输出信号sum和预期的结果,我们可以验证电路的正确性。

除了验证电路的正确性外,我们还可以通过综合工具将Verilog代码转换成对应的门级电路。

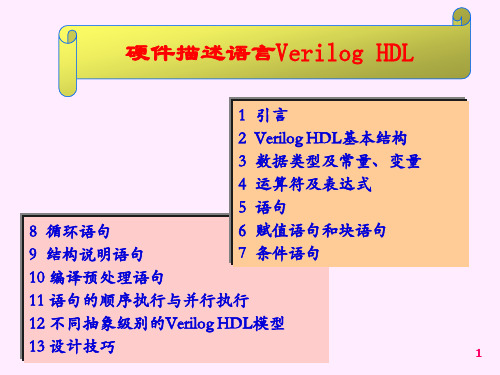

数字逻辑实验-Verilog教程

功能进行行为逻辑描述。 ➢ 程序书写格式自由,一行可以写几个语句,一个语句也可以分多

行写。 ➢ 除了endmodule语句、begin_end语句和fork_join语句外,每个语

➢ 开关级(switch level): 描述器件中三极管和储存节点

及其之间连接的模型。

5

1 引言

四、Verilog HDL的特点

▪ 语法结构上的主要特点:

➢ 形式化地表示电路的行为和结构; ➢ 借用C语言的结构和语句; ➢ 可在多个层次上对所设计的系统加以描述,语言对设计规

模不加任何限制; ➢ 具有混合建模能力:一个设计中的各子模块可用不同级别

output cout; input [7:0] data;

I/O说明

input load, cin,clk ; reg[7:0] out;

信号类型声明

always @(posedge clk)

begin

if(load) out <= data;

// 同步预置数据 功能描述

else out < = out + 1 + cin; // 加1计数

7

2 Verilog HDL基本结构

一、简单的Verilog HDL例子

[例2.1] 8位全加器

模块名(文件名)

module adder8 ( cout,sum,a,b,cin ); 端口定义

output cout; output [7:0] sum;

// 输出端口声明

I/O说明

input [7:0] a,b;

《计算机组成原理数据通路实验

《计算机组成原理数据通路实验这是一个关于计算机组成原理数据通路的实验,旨在帮助学生学习数据通路的实现原理和设计方法。

实验内容:1. 实现一个简单的数据通路,包括加法器、移位器、选择器等基本模块。

2. 利用数据通路实现一个ALU(算术逻辑单元),能够进行基本的算术和逻辑运算。

3. 实现一个简单的CPU(中央处理单元),包括指令寄存器、程序计数器、控制信号产生器、数据通路等模块。

4. 编写一些简单的汇编程序,测试CPU 的正确性和性能。

实验设备:1. 一个可编程逻辑器件(FPGA)开发板,用于实现电路的硬件化。

2. 一个集成开发环境(IDE),用于编写和调试程序。

实验步骤:1. 学习数据通路的基本实现原理和设计方法。

2. 设计并实现一个简单的数据通路,包括加法器、移位器、选择器等基本模块。

3. 利用数据通路实现一个ALU(算术逻辑单元),能够进行基本的算术和逻辑运算。

4. 实现一个简单的CPU(中央处理单元),包括指令寄存器、程序计数器、控制信号产生器、数据通路等模块。

5. 编写一些简单的汇编程序,测试CPU 的正确性和性能。

6. 考虑优化CPU 的设计,提高性能和可扩展性。

7. 结合实际应用场景,设计和实现更复杂的数据通路和CPU,提高实验难度和实用性。

实验目的:1. 掌握计算机组成原理的基本知识和实现方法。

2. 熟悉数据通路和CPU 的设计原理和流程。

3. 培养创新能力和解决问题的能力。

4. 提高学生理论与实践相结合的能力。

5. 培养学生合作和交流的能力。

6. 实现自己的创意和想法,提高实验的趣味性和挑战性。

数据通路设计实验报告

数据通路设计实验报告1. 引言数据通路是计算机中的核心部分,负责处理和传输数据。

在本次实验中,我们设计了一个简单的数据通路来实现特定的功能。

本报告将介绍实验设计的目标、方法和实验结果,并进行讨论和总结。

2. 实验目标本次实验的目标是设计一个数据通路,该数据通路能够执行数据输入、运算和输出的功能。

具体而言,我们需要设计以下模块:1. 输入模块:从外部读取输入数据;2. 运算模块:对输入数据进行运算;3. 输出模块:将运算结果输出到外部。

3. 实验方法为了实现上述目标,我们采用了以下步骤和方法:3.1 模块划分首先,我们将整个数据通路划分为三个模块:输入模块、运算模块和输出模块。

这样的划分既便于理解,又便于设计和实现。

3.2 模块设计接下来,我们对每个模块进行详细的设计。

具体而言,我们需要设计以下部分:3.2.1 输入模块输入模块负责从外部读取输入数据。

我们设计了一个输入寄存器,用于存储输入数据。

输入模块通过读取输入寄存器的内容,将数据传输到运算模块。

3.2.2 运算模块运算模块是整个数据通路的核心部分,负责对输入数据进行运算。

我们设计了一个加法器和一个乘法器来执行相应的运算。

运算模块从输入模块读取数据,并将计算结果存储到输出寄存器中。

3.2.3 输出模块输出模块将运算结果输出到外部。

我们设计了一个输出寄存器,用于存储运算结果。

输出模块从运算模块读取结果,并将其传输到外部。

3.3 数据通路连接最后,我们将各个模块连接起来,形成完整的数据通路。

具体而言,我们将输入模块与运算模块连接,将运算模块与输出模块连接,从而实现数据的输入、运算和输出。

4. 实验结果经过设计和实现,我们成功完成了数据通路的构建。

经过测试,数据通路能够正确地执行输入、运算和输出功能。

具体而言,我们测试了不同的输入数据和运算操作,并验证了结果的正确性。

5. 讨论在实验过程中,我们遇到了一些困难和挑战。

首先,我们在模块设计和连接中需要考虑各个模块之间的数据传输和时序管理。

计算机组成CPU数据通路verilog实验报告

计算机组成与系统结构实验报告院(系):计算机科学与技术学院专业班级:学号:姓名:同组者:指导教师:实验时间: 2012 年 5 月 23 日实验目的:完成处理器的单周期cpu的设计。

实验仪器:PC机(安装Altebra 公司的开发软件 QuartusII)一台实验原理:控制器分为主控制器和局部ALU控制器两部分。

主控制器的输入为指令操作码op,输出各种控制信号,并根据指令所涉及的ALU运算类型产生ALUop,同时,生成一个R-型指令的控制信号R-type,用它来控制选择将ALUop输出作为ALUctr信号,还是根据R-型指令中的func字段来产生ALUctr信号。

实验过程及实验记录:1.设计过程:第一步:分析每条指令的功能,并用RTL来表示。

第二步:根据指令的功能给出所需的元件,并考虑如何将它们互连。

第三步:确定每个元件所需控制信号的取值。

第四步:汇总各指令涉及的控制信号,生成所反映指令与控制信号之间的关系图。

第五步:根据关系表,得到每个控制信号的逻辑表达式,据此设计控制电路。

2.完成代码的编写,并调试运行。

1)controlmoduleControl(op,func,Branch,Jump,RegDst,ALUSrc,ALUctr,MemtoReg, RegWr,MemWr,ExtOp);input [5:0] op,func;output regBranch,Jump,RegDst,ALUSrc,MemtoReg,RegWr,MemWr,ExtOp; output reg [2:0] ALUctr;always @(op)case(op)6'b000000:beginBranch=0;Jump=0;RegDst=1;ALUSrc=0;MemtoReg=0;RegWr=1;MemWr =0;case(func)6'b100000:ALUctr=3'b001;6'b100010:ALUctr=3'b101;6'b100011:ALUctr=3'b100;6'b101010:ALUctr=3'b111;6'b101011:ALUctr=3'b110;endcaseend6'b001101:beginBranch=0;Jump=0;RegDst=0;ALUSrc=1;MemtoReg=0;RegWr=1;MemWr =0;ExtOp=0;ALUctr=3'b010;end6'b001001:beginBranch=0;Jump=0;RegDst=0;ALUSrc=1;MemtoReg=0;RegWr=1;MemWr =0;ExtOp=1;ALUctr=3'b000;end6'b100011:beginBranch=0;Jump=0;RegDst=0;ALUSrc=1;MemtoReg=1;RegWr=1;MemWr =0;ExtOp=1;ALUctr=3'b000;end6'b101011:beginBranch=0;Jump=0;ALUSrc=1;RegWr=0;MemWr=1;ExtOp=1;ALUctr=3' b000;end6'b000100:beginBranch=1;Jump=0;ALUSrc=0;RegWr=0;MemWr=0;ALUctr=3'b100; end6'b000010:beginBranch=0;Jump=1;RegWr=0;MemWr=0;endendcaseendmodule2)数据通路DataRoadmoduleDataRoad(Run,Clk,RegWr,MemWr,MemtoReg,RegDst,Branch,Jump,E xtOp,ALUctr,ALUSrc,busA,busB,busW,Instruction,Reg0,Reg1,Re g2,Reg3,Reg4,Mem1,Mem2,Mem3,Result,Im);inputRun,Clk,RegWr,MemWr,MemtoReg,RegDst,Branch,Jump,ExtOp,ALUS rc;input [2:0] ALUctr;output [31:0]Instruction,busA,busB,busW,Reg0,Reg1,Reg2,Reg3,Reg4,Mem1,M em2,Mem3,Result,Im;wire [31:0] busC,DataOut;wire [15:0] im;wire [4:0] Rs,Rd,Rt;wire Overflow,Zero;QZL qzl(Clk,Branch,Jump,Zero,Instruction,Run);assign Rs=Instruction[25:21];assign Rt=Instruction[20:16];assign Rd=Instruction[15:11];assign im=Instruction[15:0];Registerregister(Run,RegWr,Overflow,RegDst,Rd,Rs,Rt,busW,busA,busB ,Clk,Reg0,Reg1,Reg2,Reg3,Reg4);ALU alu(busA,busC,ALUctr,Zero,Overflow,Result);DataMem(Run,MemWr,Clk,busB,DataOut,Result,Mem1,Mem2,Mem3); MUX mux1(ALUSrc,busB,Im,busC);MUX mux2(MemtoReg,Result,DataOut,busW);Extender ext(im,Im,ExtOp);endmodule3)取指令module QZL(Clk,Branch,Jump,Zero,Instruction,Run);input Clk,Branch,Jump,Zero,Run;output [31:0] Instruction;wire [4:0] addmem;reg [29:0] PC;wire [29:0] Newpc,pc_1,pc_2,pc_3,pc_12,imm30;wire Branch_Zero;assign addmem={PC[2:0],2'b00};InsMem GetIns(addmem,Instruction);always @(negedge Clk)if(Run==1)beginPC<=Newpc;endelsebeginPC<=0;endassign pc_1=PC+1;assign imm30={{14{Instruction[15]}},Instruction[15:0]}; assign pc_2=pc_1+imm30;assign pc_3={PC[29:26],Instruction[25:0]};assign Branch_Zero=Branch&Zero;MUX m1(Branch_Zero,pc_1,pc_2,pc_12);MUX m2(Jump,pc_12,pc_3,Newpc);endmodulemodule InsMem(addmem,Instruction);input [4:0] addmem;output reg[31:0] Instruction;reg [31:0] Mem[31:0];always @(*)beginMem[0]<={6'b100011,5'b00000,5'b00001,5'b00000,5'b00000,6'b 000001};Mem[4]<={6'b100011,5'b00000,5'b00010,5'b00000,5'b00000,6'b 000010};Mem[8]<={6'b000000,5'b00001,5'b00010,5'b00011,5'b00000,6'b 100000};Mem[12]<={6'b101011,5'b00000,5'b00011,5'b00000,5'b00000,6' b000010};Mem[16]<={6'b001101,5'b00100,5'b00100,5'b11111,5'b11111,6' b111111};Mem[20]<={6'b000000,5'b00011,5'b00010,5'b00010,5'b00000,6' b100010};Mem[24]<={6'b000100,5'b00010,5'b00001,5'b00000,5'b00000,6' b001000};Mem[28]<={6'b000010,5'b00000,5'b00000,5'b00000,5'b00000,6' b000000};endalways @(*)Instruction=Mem[addmem];Endmodule4)ALUmodule ALU(A,B,ALUctr,Zero,Overflow,Result);parameter n=32;input [n-1:0] A,B;input [2:0] ALUctr;output Zero,Overflow;output [n-1:0] Result;wire SUBctr,OVctr,SIGctr,SignA,SignB,Cin;wire [1:0] OPctr;wire [n-1:0] X,Y,Z,Less,M,N,Add_Result;wire Add_Carry,Add_Overflow,Add_Sign;assign M={n{1'b0}};assign N={n{1'b1}};assign SUBctr=ALUctr[2];assign OVctr=!ALUctr[1]&ALUctr[0];assign SIGctr=ALUctr[0];assign OPctr[1]=ALUctr[2]&ALUctr[1];assign OPctr[0]=!ALUctr[2]&ALUctr[1]&!ALUctr[0];assign Cin=SUBctr;assign X=B^{n{SUBctr}};assign Y=A|B;Adderad(Cin,A,X,Add_Carry,Add_Overflow,Add_Sign,Add_Result,Zero );assign SignA=Cin^Add_Carry;assign SignB=Add_Overflow^Add_Sign;assign Overflow=Add_Overflow&OVctr;MUX m1(SIGctr,SignA,SignB,Less);defparam m1.k=1;MUX m2(Less,M,N,Z);MUX3_1 m3(Add_Result,Y,Z,Result,OPctr);endmodulemodule MUX3_1(A,B,C,D,ctr);parameter k=32;input [k-1:0] A,B,C;output reg [k-1:0] D;input [1:0] ctr;always @(A or B or C or ctr)if(ctr==2'b00) D=A;elseif(ctr==2'b01) D=B;elseif(ctr==2'b10) D=C;endmodulemoduleAdder(Cin,X,Y,Add_Carry,Add_Overflow,Add_Sign,Add_Result,Z ero);parameter k=32;input [k-1:0] X,Y;input Cin;output reg [k-1:0] Add_Result;output Add_Carry,Add_Overflow,Add_Sign,Zero;reg Add_Carry;assign Zero=~|Add_Result;assign Add_Sign=Add_Result[k-1];assignAdd_Overflow=(X[k-1]&Y[k-1]&~Add_Result[k-1])|(~X[k-1]&~Y[ k-1]&Add_Result[k-1]);always @(X or Y or Cin){Add_Carry,Add_Result}=X+Y+Cin;Endmodule5)数据存数moduleDataMem(Run,MemWr,Clk,DataIn,DataOut,Adr,Mem1,Mem2,Mem3);input Run,MemWr,Clk;input [31:0] DataIn,Adr;output [31:0] DataOut;output [31:0] Mem1,Mem2,Mem3;reg[31:0] Mem[31:0];assign Mem1=Mem[1];assign Mem2=Mem[2];assign Mem3=Mem[3];assign DataOut=Mem[Adr];always @(negedge Clk)if(Run==0)beginMem[0]=0;Mem[1]=10;Mem[2]=20;Mem[3]=30;endelsebeginif(MemWr==1)Mem[Adr]=DataIn;endendmodule6)寄存器moduleRegister(Run,Regwr,Overflow,RegDst,Rd,Rs,Rt,busW,busA,busB ,Clk,Reg0,Reg1,Reg2,Reg3,Reg4);input Regwr,Clk,RegDst,Run,Overflow;input [31:0] busW;input [4:0] Rd,Rt,Rs;output reg [31:0] busA,busB;output [31:0] Reg0,Reg1,Reg2,Reg3,Reg4;reg [31:0] Mem[31:0];reg [4:0] Rw;wire [4:0] Ra,Rb;wire RegWr;assign RegWr=Regwr&~Overflow; assign Ra=Rs;assign Rb=Rt;assign Reg0=Mem[0];assign Reg1=Mem[1];assign Reg2=Mem[2];assign Reg3=Mem[3];assign Reg4=Mem[4];always @(Rd or Rt or RegDst) if(RegDst==1'b1)Rw=Rd;elseRw=Rt;always @(negedge Clk)if(Run==1'b1)beginif(RegWr==1'b1)Mem[Rw]=busW;endelsebeginMem[0]<=0;Mem[1]<=2;Mem[2]<=4;Mem[3]<=6;Mem[4]<=8;endalways @(Ra or Rb)if(Run==1'b1)beginbusA=Mem[Ra];busB=Mem[Rb];endelsebeginbusA=0;busB=0;endendmodule7)数据选择module MUX(ctr,X,Y,Z); parameter k=32;input [k-1:0] X,Y;output reg [k-1:0] Z;input ctr;always @(X or Y or ctr)if(ctr==1'b0) Z<=X;else Z<=Y;endmodule3.进行仿真并验证其正确性:。

verilog语法学习心得

verilog语法学习心得

1.数字电路基础知识:布尔代数、门级电路的内部晶体管结构、组合逻辑电路分析与设计、触发器、时序逻辑电路分析与设计

2.数字系统的构成:传感器 AD 数字处理器 DA 执行部件

3.程序通在硬件上的执行过程:

C语言(经过编译)--﹥该处理器的机器语言(放入存储器)--﹥按时钟的节拍,逐条取出指令、分析指令、执行指令

4.DSP处理是个广泛概念,统指在数字系统中做的变换(DFT)、滤波、编码解码、加密解密、压缩解压等处理

5.数字处理器包括两部分:高速数据通道接口逻辑、高速算法电路逻辑

6.当前,IC产业包括IC制造和IC设计两部分,IC设计技术发展速度高于IC设计

7.FPGA设计的前续课程:数值分析、DSP、C语言、算法与数据结构、数字电路、HDL语言计算机微体系结构

8.数字处理器处理性能的提高:软件算法的优化、微体系结构的优化

......。

对数字电路的看法英语作文

对数字电路的看法英语作文英文回答:Digital circuits have played a pivotal role in shaping the modern world as we know it. They form the backbone of countless electronic devices, from smartphones to supercomputers, enabling them to perform complex calculations, store vast amounts of data, and communicate with each other seamlessly.The advent of digital circuits has revolutionized various industries. In the field of computing, they have made possible the development of powerful computers that can handle intricate tasks such as artificial intelligence, machine learning, and scientific simulations. In the realm of telecommunications, digital circuits have laid the foundation for modern communication systems, enabling us to make phone calls, send text messages, and access the internet at blazing-fast speeds.The beauty of digital circuits lies in their simplicity and reliability. They operate based on a binary system, where all information is represented using only two digits: 0 and 1. This simplicity allows for the design of circuits that are highly accurate and robust, capable of withstanding noise and other disturbances.Moreover, digital circuits are incredibly versatile. They can be configured to perform a wide range of functions, from basic arithmetic operations to complex signal processing and data manipulation. This versatility has made them indispensable in a myriad of applications, from consumer electronics to industrial control systems.As the world continues to embrace digitalization, the demand for digital circuits is only expected to grow. These circuits will continue to drive innovation and shape the future of technology, empowering us to solve complex problems, connect with each other, and unlock new possibilities.中文回答:数字电路的魅力数字电路在塑造我们所知的现代世界中发挥了至关重要的作用。

常用数字处理算法的Verilog实现

常用数字处理算法的Verilog实现1.加法器的Verilog实现∙串行加法器组合逻辑的加法器可以利用真值表,通过与门和非门简单地实现。

假设和表示两个加数,表示和,表示来自低位的进位,表示向高位的进位。

每个全加器都执行如下的逻辑表达式:这样可以得到加法器的一种串行结构。

因此,式(2.1)所示的加法器也被称为串行加法器。

如图2-20给出了一个4位串行加法器的结构示意图。

图2-20 串行加法器的结构示意图在无线通信的信号处理中,常常要用到多位数字量的加法运算。

如果用串行加法器实现,速度较慢,而并行加法器就能满足要求,并且结构并不复杂。

现在普遍使用的并性加法器是超前进位加法器,只是在几个全加器的基础上增加了一个超前进位形成逻辑,以减少由于逐步进位信号的传递所造成的时延。

图2-21给出了一个4位并行加法器的结构示意图。

图2-21 串行加法器的示意图在4位并行加法器的基础上,可以递推出16位、32位和64位的快速并行加法器。

∙流水线加法器在使用了并行加法器后,仍旧只有在输出稳定后才能输入新的数进行下一次计算,即计算的节拍必须大于运算电路的延迟;此外,许多门级电路和布线的延迟会随着位数的增加而累加,因此加法器的频率还是受到了限制。

但如果采用流水线,就有可能将一个算术操作分解为一些小规模的基本操作,将进位和中间值存储在寄存器中,并在下一个时钟周期内继续运算,这样就可以提高电路的利用效率。

将流水线规则应用于FPGA中,只需要很少或根本不需要额外的成本。

这是因为每个逻辑单元都包含两个触发器,大多数情况下这两个触发器或者没有用到,或者用于存储布线资源,那么就可以利用其来实现流水线结构。

如果采用了流水线后,加法器的速度仍然不能满足需要的话,可以采用第3章中将会提到的串并转换来进一步提高计算的并行度。

由于一个slice中有两个触发器,还需要有1个触发器来作为进位输出,那么采用级流水线,就可以构造一个最大位数为位的加法器。

基于VHDL语言的并行数字相关器的数据通道设计

1 引言在扩频通讯、GPS、雷达、声纳、机械震动测试等诸多领域,数字相关技术有着非常广泛的应用。

在直扩通信系统中,它主要完成扩频码的同步捕捉,根据应用的场合不同,有多种方法来实现扩频码的同步捕捉。

比如,采用滑动相关法、序列匹配滤波器法、发射参考信号法、通用定时法以及突发同步法等。

其中,滑动相关器法是直扩系统中最简单也是最基本的搜索同步扩频码的方法,它是利用PN序列的自相关特性,当两个相同的码序列相位一致时,其相关器有最大的输出峰值,当检测到该峰值时,就停止本地码的滑动,立即进入跟踪状态。

由于这种方法是对两个码序列顺序比较相位的,故该法又称顺序搜索法。

它的缺点是当PN码周期很长、相对滑动速度又很慢时,将导致同步捕捉时间过长。

一般都要在其基础上采用一些技术措施来限制搜索范围或加快搜索速度。

本文研究一种并行搜索法来加快扩频码的同步捕捉,该并行数字相关器的设计包括并行数据通道、控制通道、本地PN码调相器等三部分,全部采用VHDL语言描述,限于篇幅我们仅能在此讨论它的数据通道设计,并给出其综合优化后的TRL级逻辑图及其求出最大值的仿真波形图。

2并行数字相关器的结构我们首先给出PN码的本原多项式F(x)=x8+x4+x3+x2+1, 由该本原多项式产生的m序列周期基于VHDL语言的并行数字相关器的数据通道设计张 欣(成都Nimrod-Silicon微系统设计有限公司,四川 成都 610041)摘要:在采用并行数字相关器对直扩码进行解扩时,其数据通道设计十分关键。

对数据通道使用流水线技术,可以提高其运算速度。

整个数字相关器用VHDL语言来描述,经逻辑综合后,适配到FPGA芯片中。

文中还给出布局布线后的时序仿真。

关键词:数字相关器;VHDL;数据通道中图分类号:TP273 文献标识码:A 文章编号:1003-353X(2003)01-0040-04A data path design of parallel digital correlatorbased on VHDLZhang xin(Nimrod-silicon Microsystems Design Ltd., Chengdu, 610041 China)Abstract :The data path design is quite important when it is dispread for spread-spectrum codewith parallel digital correlator.The data path is improved in operation speed by pipeline technology.The digital correlator is described by VHDL language and be fitted to the PAGA chips after logicsynthesizing. It also presents timing simulation in placement and routing.Key words:digital correlator;VHDL;data pathEDA技术专栏技术交流2.1 数据通道设计我们不妨设输入的扩频码片信号为C(t);本地PN码序列信号为m(t-δ) ;P为相关运算的输出值;码片速率为125K/chip,系统时钟为10.7MHz;根据直扩通信理论,我们可以推导出如下离散相关运这里的k=1,2,…,8。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[数字计算机算术数据通路设计:使用Verilog语言]计算机数据通路

James E. Stine Digital Computer Arithmetic Datapath Design Using Verilog HDL CD-ROM Included 2004 180pp. Hardcover $ 102.09 ISBN 1-4020-7710-6 Kluwer Academic Publishers J.E.斯泰恩著在VLSI的数据通路中算术显得越来越重要了,这是由于处理器的尺寸需要越来越小,运算速度需要越来越快,功耗需要越来越低。

这意味着很多数据通路将会变得更加复杂,无论是在算法上还是在电路上。

由于芯片的复杂度上升,了解特定的算术数据通路设计如何实现显得越来越不重要,而人们更加注意什么时候产品才能投放市场。

因为当今可以使用很多设计工具来最大限度提高设计效率。

然而,这也许会在实现特定数据通路的时候出现问题。

高性能体系结构的设计变得愈来愈复杂,在集成电路层一块芯片上可以有数以亿计的晶体管。

很多工程师依赖于软件工具来最优化他们的工作,于是,随着设计越来越复杂,对于具体硬件实现的了解却越来越小,因为这些设计的具体实现都由软件自动完成。

虽然软件工具对于工程师而言很有价值,但是这不能说明了解数据通路不重要。

所以,数字系统设计师也要知道算法怎样用数据通路来实现,很多时候不看代码很难懂得特定算法的实现。

本书的目标就是为算术数据通路设计提供基础实现及其用到的方法。

这不是一本关于理论的书,但是,理论是用来证明该做什么样的选择和为什么要选择?一本优秀的算术书籍也是需要理论的。

与Verilog语言代码一起阅读一本关于算术和体系结构的教科书将会使读者快速而透彻的了解算术数据通路涉及的具体实现。

无论如何,结构化模型可以用来阐释设计原理,而设计的重点应该放在设计算法上而不是电路实现上。

但是这两者应当在设计当中都具体考虑。

本书的观点都是在RTL层实现的,因此具体实现可能有很多不同方式。

全书共7章。

第1章引言,简要介绍Verilog语言,本书写作目的,以及数据通路设计;第2章在RTL层的Verilog语言,介绍Verilog语言在这个层次上的具体使用;第3章加法器,介绍加法器的具体设计;第4章乘法器,介绍乘法器的具体设计;第5章循环触发器,介绍触发器的设计;第6章基本功能,介绍计算机的几种基本功能的设计;第7章基于乘法的除法器,主要介绍Newton-Raphson除法器的设计。

本书适合从事计算机体系结构和电子专业的研究人员阅读使用,也适合相关专业的研究生参考。

丁丹,硕士生(中国科学院计算技术研究所)Ding Dan, Master (Institute of Computer Technology, the Chinese Academy of Sciences)。