基于Verilog HDL设计的数字时钟

基于FPGA的数字钟设计(VerilogHDL语言实现)

基于FPGA的数字钟设计摘要:本设计为一个多功能的数字钟,具有时、分、秒计数显示功能,以12小时循环计数。

本设计采用EDA技术,以硬件描述语言VerilogHDL为系统逻辑描述手段设计文件,在QUARTUS II工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统主芯片采用EP1K100QC208-3,由时钟模块、控制模块、计时模块、数据译码模块、显示以及报时模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统能够完成时、分、秒的分别显示,由按键输入进行数字钟的清零功能。

关键词:数字钟;硬件描述语言;VerilogHDL;FPGA;引言:现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。

支撑信息电子产品高速发展的基础就是微电子制造工艺水平的提高和电子产品设计开发技术的发展。

前者以微细加工技术为代表,而后者的代表就是电子设计自动化(electronic design automatic,EDA)技术。

本设计采用的VerilogHDL是一种全方位的硬件描述语言,具有极强的描述能力,能支持系统行为级、寄存器传输级和逻辑门级三个不同层次的设计;支持结构、数据流、行为三种描述形式的混合描述、覆盖面广、抽象能力强,因此在实际应用中越来越广泛。

ASIC是专用的系统集成电路,是一种带有逻辑处理的加速处理器。

而FPGA是特殊的ASIC芯片,与其他的ASIC芯片相比,它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检测等优点。

在控制系统中,键盘是常用的人机交换接口,当所设置的功能键或数字键按下的时候,系统应该完成该键所设置的功能。

因此,键信息输入是与软件结构密切相关的过程。

根据键盘的结构不同,采用不同的编码方法。

但无论有无编码以及采用什么样的编码,最后都要转换成为相应的键值,以实现按键功能程序的转移。

VerilogHDL语言数字时钟

VerilogHDL语言数字时钟EDA与数字系统设计报告实验名称:带有设臵时间功能和闹钟功能的数字钟一、设计内容和要求实验要求使用Verilog HDL进行多功能时钟的设计具体要求如下:1.能将基本的小时、分钟、及秒钟显示在数码管上2.能利用拨码开关进行时间的校正3.具有整点报时和闹钟的功能二、设计原理1.工作原理多功能数字钟系统共包括三个模块,即分频器模块、计数器模块和显示译码模块。

多功能数字钟的功能可以从整体上分为三类,分别是正常计时、时钟校对和闹钟设臵,所以考虑在系统中设臵一个模式控制信号mode。

模式控制信号对应一个按键,每按一次按键相当于工作模式进行一次变换,多次按下则数字钟将在正常计时、时间校对和闹钟设臵三个工作模式下依次循环。

在设计中,时钟校对和闹钟设臵工作模式都需要对时间进行设臵,通常是对小时和分钟进行设臵,所以需要在系统中设臵一个时间设臵信号set,对应一个按键,每按一次相当于在小时设臵和分钟设臵之间进行转换。

时间设臵时,分钟和小时计时单位之间互相独立,不存在进位关系。

同时设臵一个时间调整信号accum,每按一次与accum对应的按键,相当于对需要调整的分钟或小时的数字进行加1操作。

数字钟的计时输出信号时必不可少的,用hour,min和sec信号分别表示需要显示的小时、分钟和秒钟的计时结果,上述计时结果将通过译码显示模块进行译码后,连接到外部的七段数码显示器。

在带有闹钟设臵功能的数字钟中,闹钟输出信号也是必不可少的,到达到闹钟设臵的时间后,要向外部扬声器发送一个闹铃信号,设臵alert。

另外,我们还提供了闹钟铃声信号voice,当voice为0的时候,闹钟处于静音状态下,即使时间达到闹钟设定的时间也不会发声,当voice为1的时候,可以正常闹铃,voice信号对应一个拨码开关。

本设计中的小时、分钟和秒钟的计时结果采用BCD码表示方法。

采用这种表示方法便于对数结果的高位和低位分别进行译码。

用Verilog语言编写的多功能数字钟

这次的闹钟电路设计和多功能数字钟有一些相似的地方,不同在于整体构思和细

节上要求的差异。

构思根据要求采用的是状态机设计方法。从一个状态进入另一个状态最适合这个

设计了。细节上和数字钟也有很大的差异。中间的控制逻辑有时候需要反馈。前

后都是有联系的,并不是独立存在的。

本次设计基本上完成的所以的要求,但是由于时间紧急,一些细节并不是很完美,

分频器的作用是对 50Mhz 的系统时钟信号进行分频,得到频率为 1hz 的信号,

作为时钟的输入信号。

2

2.控制器和计数器 控制器的作用是,调整小时和分钟的值,并能实现清零功能。计数器的

作用是实现分钟和秒钟满 60 进 1,小时则由 23 跳到 00。当到达 59 分 55 秒的时 候,LED 灯会闪烁来进行报时。

end 2:

begin state<=2; s=1;

end 3:

begin s=0; if(k1==0) //时调整

7

begin

if(nz_h_l==3)

begin

nz_h_l=0;

if(nz_h_h==2)nz_h_h=0;

else nz_h_h=nz_h_h+1;

end

else nz_h_l=nz_h_l+1;

end

else if(k3==0) finish=1;

//设置完成

else if(k4==0) spker_en=1; //停止声响

end

8

4: begin s=0; if(k4==0) begin on_off<=!on_off;state=0;end end

endcase end end endmodule 3.显示器 显示器的作用是将时:分的值在数码管上依次显示出来。从分频器输出的 1Khz 的信号作为数码管的扫描信号。SEL 表示 6 个数码管选择位,它的取值表示八个 数码管,从左至右依次是 111~000。seg 表示七段数码管,它的取值决定特定位 数上显示的数字。

基于FPGA的数字钟设计

基于FPGA的数字钟设计摘要:现实生活中经常会出现需要用时间测定参数数值的情况,服务日常生活和生产。

基于FPGA设计数字电路产品已经成为当前的重要设计方法。

本文设计选用了Quartus软件环境,运用描述逻辑Verilog HDL,由上至下的模式,基于FPGA完成了数字时钟的设计方案。

本次设计成果采用按键对闹钟的起止点进行控制,能够显示时,分,秒等并且能够实现整点报时。

其中的FPGA技术就是本次试验的亮点之一,其设计易于学习,各个模块分工清晰,在模拟软件上很容易运行,还能够适配于许多种环境,因此总体的系统性能指标还是相当有保证的。

关键词:数字钟;FPGA;Verilog HDL;Quartus1.1 课题研究背景在现代社会,数据集成电路已广泛运用于日常日常生活的各行各业。

数据集成电路也在不停拆换。

从起初的整流管、电子管、大中小型集成电路发展趋势为具备特大型集成电路和独特作用的各类专用型集成电路。

可是,因为微电子技术科技进步的迅猛发展,集成电路设计方案和生产制造工作中再也不会由半导体生产商独立担负。

系统软件室内设计师更喜欢立即设计方案专用型集成电路(ASIC)处理芯片,并马上资金投入具体运用,因而发生了当场可编程逻辑机器设备(FPLD),在其中应用最普遍的是当场可编门阵列(FPGA)。

数字钟是一种选用数字电路设计技术性完成时、分、秒计时的装置,在完成数据与此同时表明时、分、秒的准确时间和精确校正时,体积小、重量轻、抗干扰能力强、对自然环境需要高、高精密、易于开发设计等与在办公系统系统软件等众多行业运用非常普遍的传统式表壳式机械手表对比,数字表更精确、形象化,因为沒有机械设备装置,使用期限长。

1.2 国内外研究现状近些年来已经有许多技术人员针对电子器件以及时钟等技术进行了研究,但真正意义上的数字钟表起源于50年代或60年代。

伴随着在我国数字钟表电源电路销售市场的迅速发展趋势,尤其是十二五阶段经济发展方法这一领土主权主旋律早已明确,与之有关的关键生产制造技术运用和产品研发将变成领域公司关心的焦点。

基于VerilogHDL设计的多功能数字钟

3' b101: Disp_Temp=4' b1010;

#(60000*HALF_PERIOD) S1_in=1;

3' b110: Disp_Temp=SECH;

end

3' b111: Disp_Temp=SECL;

//产 生 调 节 分 钟 信 号

endcase

initial

end

begin

always@(Disp_Temp) //显示转换

新

图 1 多功能数字钟端口功能图

Clk: 10KHZ 的系统基准时钟输入。作为七段码管 扫描频率。将其 10000 分频可得到 1HZ 的数字钟工作 频率。将其 8 分频和 4 分频分别分时送入扬声器, 使 其产生嘀( 1.25KHZ) 、嗒( 2.5KHZ) 的报时声。

Rst: 系统复位信号, 低电平有效。复位后显示 00- 00- 00。

Abstr act: In this paper, the process of designing multifunctional digital clock by the Verilog HDL top- down design method is pre- sented, which has shown the readability, portability and easily understanding of Verilog HDL as a hard description language. Circuit synthesis and simulation are performed by Altera QuartusⅡ 4.1 and ModelSim SE 6.0. The program can be used in the truly digital clock display by downloading to the FPGA chip. Keywor ds: Ver ilog HDL; har dwar e descr iption language; FPGA

简单的数字时钟(verilog设计)

设计目标与要求

设计一个简单的数字 时钟,能够显示时、 分、秒。

时钟应具有可靠性、 稳定性和可扩展性。

要求使用Verilog语 言实现,并能够在 FPGA或ASIC上实现。

设计思路及流程

• 设计思路:采用模块化设计方法,将数字时钟划分为不同的模 块,如计数器模块、显示模块等。每个模块负责实现特定的功 能,并通过接口与其他模块进行通信。

设计思路及流程

设计流程 1. 确定设计需求和目标。 2. 制定设计方案和计划。

设计思路及流程

3. 编写Verilog代码,实现各个模块的功能。 5. 根据测试结果进行调试和优化。

未来改进方向探讨

提高计时精度

通过改进算法或采用更高 性能的硬件平台,提高数

字时钟的计时精度。

降低资源占用

优化代码结构,减少不 必要的资源占用,提高 时钟系统的运行效率。

增加实用功能

拓展应用领域

考虑增加闹钟、定时器 等实用功能,使数字时 钟更加符合用户需求。

探索将数字时钟应用于 更多领域,如智能家居、

数据类型与运算符

Verilog中的数据类型包括

整型、实型、时间型、数组、结构体等。

Verilog中的运算符包括

算术运算符、关系运算符、逻辑运算符、位运算符等。

顺序语句与并行语句

Verilog中的顺序语句包括

赋值语句、条件语句、循环语句等,用于描述电路的时序行为。

Verilog中的并行语句包括

模块实例化、连续赋值语句、门级电路描述等,用于描述电路的并行行为。

用verilog-HDL多功能数字钟

用verilog-HDL多功能数字钟Verilog HDL实验报告基于Verilog HDL语言的多功能数字钟设计一、试验目的设计一个有如下功能的数字钟:(1)计时功能:包括时、分、秒。

(2)定时与闹钟功能:能在所设定的时间发出铃音。

(3)校时功能:对小时、分钟和秒钟进行手动校时。

(4)整点报时功能:每到整点能够发出“嘀嘀嘀嘀嘟”四短一长的报时。

二、试验原理ALERT HOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MINCLK CLK_1K MODE TURN CHANGEclockCLK CLK_1K MODE TURN CHANGEALERTHOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MIN多功能数字钟端口示意图数字钟设有五个输入端,分别为时钟输入(CLK )、模式(MODE )、产生声音的时钟信号(CLK_1K )、切换(TURN )和调时(CHANGE )键。

输出共七个,其中HOUR[7..0]、MIN[7..0]和SEC[7..0]采用BCD 计数方式,分别驱动2个数码管。

硬件电路原理图如下:三、试验内容1. 代码/*信号定义:clk: 标准时钟信号,其频率为4Hz;clk_1k:产生闹铃声、报时音的时钟信号,其频率为1024Hz;mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时还是分钟;若长时间按住改建,还可使秒信号清零,用于精确调时;change: 接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;hour,min,sec:此三信号分别输出并显示时、分、秒信号,皆采用BCD码计数,分别驱动6个数码管显示时间;alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号*/moduleclock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_mi n);input clk,clk_1k,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] hour,min,sec;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;reg LD_hour,LD_min;reg clk_1Hz,clk_2Hz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;wire ct1,ct2,cta,ctb,m_clk,h_clk;always @(posedge clk)beginclk_2Hz<=~clk_2Hz;if(sound==3) begin sound<=0; ear<=1; end //ear信号用于产生或屏蔽声音else begin sound<=sound+1; ear<=0; endendalways @(posedge clk_2Hz) //由4Hz的输入时钟产生1Hz的时基信号clk_1Hz<=~clk_1Hz;always @(posedge mode) //mode信号控制系统在三种功能间转换begin if(m==2) m<=0; else m<=m+1; endalways @(posedge turn)fm<=~fm;always //产生count1,count2,counta,countb四个信号begincase(m)2:begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=0;end1:begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelsebegin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b00;enddefault:{count1,count2,counta,countb,LD_min,LD_hour}<=0;endcaseendalways @(negedge clk) //如果长时间按下“change”键,则生成“num1”信号用于连续快速加1if(count2) beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1; num2<=0;endendelse begin loop2<=0; num2<=0; endalways @(negedge clk) //产生num2信号if(count1) beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1; num3<=0; endendelse begin loop3<=0; num3<=0; endalways @(negedge clk)if(counta) beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1; num4<=0; endendelse begin loop4<=0; num4<=0; endassign ct1=(num3&clk)|(!num3&m_clk); //ct1用于计时、校时中的分钟计数assign ct2=(num1&clk)|(!num1&count2); //ct2用于在定时状态下调整分钟信号assign cta=(num4&clk)|(!num4&h_clk); //cta用于计时、校时中的小时计数assign ctb=(num2&clk)|(!num2&countb); //ctb用于在定时状态下调整小时信号always @(posedge clk_1Hz) //秒计时和秒调整进程if(!(sec1^8'h59)|turn&(!m))beginsec1<=0;if(!(turn&(!m))) minclk<=1;end//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时else beginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1; endelse sec1[3:0]<=sec1[3:0]+1; minclk<=0;endassign m_clk=minclk||count1;always @(posedge ct1) //分计时和分调整进程beginif(min1==8'h59) begin min1<=0; hclk<=1; endelse beginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1; endelse min1[3:0]<=min1[3:0]+1; hclk<=0;endendassign h_clk=hclk||counta;always @(posedge cta) //小时计时和小时调整进程if(hour1==8'h23) hour1<=0;else if(hour1[3:0]==9)begin hour1[7:0]<=hour1[7:4]+1; hour1[3:0]<=0; endelse hour1[3:0]<=hour1[3:0]+1;always @(posedge ct2) //闹钟定时功能中的分钟调节进程if(amin==8'h59) amin<=0;else if(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1; endelse amin[3:0]<=amin[3:0]+1;always @(posedge ctb) //闹钟定时功能中的小时调节进程if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; endelse ahour[3:0]<=ahour[3:0]+1;always //闹铃功能if((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(!change))//若按住“change”键不放,可屏蔽闹铃音if(sec1<8'h20) alert1<=1; //控制闹铃的时间长短else alert1<=0;else alert1<=0;always //时、分、秒的现实控制case(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end//计时状态下的时、分、秒显示3'b01: begin hour<=ahour; min<=amin; sec<=8'hzz; end//定时状态下的时、分、秒显示3'b10: begin hour<=hour1; min<=min1; sec<=8'hzz; end//校时状态下的时、分、秒显示endcaseassign LD_alert=(ahour|amin)?1:0; //指示是否进行了闹铃定时assign alert=((alert1)?clk_1k&clk:0)|alert2; //产生闹铃音或整点报时音always //产生整点报时信号alert2beginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk_1k; //产生短音else alert2<=!ear&clk_1k; //产生长音else alert2<=0;endendmodule2. 仿真图四、小结及体会为了做多功能数字钟,我借了多本关于Verilog HDL的程序设计书。

课程设计---基于Verilog HDL数字时钟设计与实现

课程设计---基于Verilog HDL数字时钟设

计与实现

简介

本课程设计旨在通过使用Verilog硬件描述语言(HDL)设计和实现数字时钟。

学生将研究如何使用Verilog语言来描述数字电路,并将其应用于设计和实现一个简单的数字时钟电路。

设计目标

- 研究使用Verilog HDL来描述和设计数字电路

- 实现一个简单的数字时钟电路

- 熟悉数字时钟的工作原理和设计流程

实施步骤

1. 了解数字时钟的原理和工作方式

2. 研究Verilog HDL语言的基本语法和使用方法

3. 设计并实现时钟的各个功能模块,如时钟显示模块、时钟计数模块等

4. 使用仿真工具验证设计的正确性

5. 进行实际的硬件验证,将设计烧录到FPGA开发板上并进行测试

实验要求

1. 设计的数字时钟应具备基本的时分秒显示功能

2. 时钟应具备可调节的时间设置功能

3. 需要使用FPGA开发板进行实际硬件验证

4. 实验报告应包含设计原理、设计流程、仿真结果和实际硬件验证结果

参考资料

1. Verilog HDL教程

2. FPGA开发板用户手册

3. 相关学术论文和文献

以上为课程设计---基于Verilog HDL数字时钟设计与实现的文档简介。

本课程设计将帮助学生学习Verilog HDL语言并应用于设计和实现数字时钟电路。

基于veriloghdl设计的数字时钟

大学考试答题纸(以论文、报告等形式考核专用)二○ 18 ~二○ 19 学年度第 一 学期 课程编号 1602080001课程名称 学 号姓名 思豪 专业年级 电子科学与技术16级1班题目:基于Verilog HDL 设计的数字时钟摘 要:本文利用Verilog HDL 语言自顶向下的设计法设计多功能数字钟,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Altera Quartus Ⅱ 6.0和cyclnoe II EP2C35F672C6完成综合、仿真。

此程序通过下载到FPGA 芯片后,可应用于实际的数字钟显示中关键词:Verilog HDL ;硬件描述语言;FPGA目录一、实验任务 (3)实验目的 (3)实验要求 (3)二、设计思路 (3)三、实验结果 (10)四、总结与收获 (14)一、实验任务实验目的1.深入了解基于quartus ii工具的复杂时序逻辑电路的设计。

2.理解并熟练利用EDA工具进行综合设计。

3.熟练掌握芯片烧录的流程及步骤。

4.掌握Verilog HDL 语言的语法规及时序电路描述法。

实验要求设计一个带秒表功能的24 小时数字钟,它包括以下几个组成部分:①显示屏,由6 个七段数码管组成,用于显示当前时间(时:分,秒)或设置的秒表时间;②复位键复位所有显示和计数③设置键,用于确定新的时间设置,三个消抖按键分别用于时分秒的设置④秒表键,用于切换成秒表功能基本要求(1) 计时功能:这是本计时器设计的基本功能,每隔一秒计时一次,并在显示屏上显示当前时间。

(2) 秒表功能:设置时间,进行倒计时功能(3) 设置新的计时器时间:按下设置键后,用户能通过时分秒三个消抖按键对时间进行设置。

二、设计思路1、总原理框图:原理如上图所示,时钟由分频器模块,数码管显示模块,计时器模块三个模块构成,每个模块实现如下的不同功能,最后通过在顶层模块的调用,来实现时钟功能。

2.顶层模块:顶层模块调用三个字模块,并且定义输入输出口,代码输入所示:modulemyclock2(daojishi,stop,clk,reset,shi,fen,miao,miaoout1,miaoout2,fenout1,fenout2,shiout1,s hiout2);input clk,reset,stop,shi,fen,miao,daojishi;output[6:0] miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2;wire[3:0] miao1,miao2,fen1,fen2,shi1,shi2;wire clk_1hz;divider_1HZ divider1hz(clk_1hz,reset,clk);count count1(daojishi,shi,fen,miao,stop,miao1,miao2,fen1,fen2,shi1,shi2,reset,clk_1hz); decode4_7 d0(miaoout1,miao1);decode4_7 d1(miaoout2,miao2);decode4_7 d2(fenout1,fen1);decode4_7 d3(fenout2,fen2);decode4_7 d4(shiout1,shi1);decode4_7 d5(shiout2,shi2);endmodule输入输出端口类型功能表:三个子模块的原理和代码:(1)分频模块:分频模块的作用主要是要获得各种频率的时钟信号。

基于verilog的数字秒表的设计实现

数字秒表的设计实现团队成员:董婷詹磊胡鹏一、测试要求1. 有源晶振频率:24MHZ2. 测试计时范围:00’00”00 ~ 59’59”99,显示的最长时间为59分59 秒3. 数字秒表的计时精度是10ms4. 显示工作方式:a、用八位数码管显示读数b、用两个按钮开关(一个按钮使秒表复位,另一个按钮控制秒表的启动/暂停)二、设计要求1. 设计出符合设计要求的解决方案2. 利用软件对各单元电路及整体电路进行仿真3. 在开发板上实现设计5. 撰写设计报告三、秒表功能键1、power:秒表电源键2、Reset:秒表复位清零键3、run/stop:秒表启动/停止键四、实验原理1 .实验设计原理(1)秒表的逻辑结构较简单,它主要由十进制计数器、六进制计数器、分频器、数据选择器、和显示译码器等组成。

在整个秒表中最关键的是如何获得一个精确的100HZ计时脉冲,除此之外,整个秒表还需有一个启动信号和一个清零信号,以便秒表能随意停止、启动以及清零复位。

(2)秒表有共有8个输出显示,其中6个显示输出数据,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应;另外两个为间隔符,显示‘-’。

8个计数器的输出全都为BCD码输出,这样便与同显示译码器连接。

(3)可定义一个24位二进制的寄存器hour用于存放8个计数器的输出,寄存器从高位到低位每连续4位为一组,分别存放百分之一秒、十分之一秒、间隔符、秒、十秒、间隔符、分、十分。

由频率信号输出端输出频率为100HZ的时钟信号,输入到百分之一秒模块的时钟端clk,百分之一秒模块为100进制的计数器,当计数到“1001”时,百分之一秒模块清零,同时十分之一秒模块加1;十分之一秒模块也为100进制的计数器,当计数到“1001”时,十分之一秒模块清零,同时秒模块加1;以此类推。

直到分模块计数到59进59。

(4)为了消除按键消抖问题,定义寄存器key-inner来存储按键key的输入信号,key-flag作为启动/暂停的转换标志,key-inner[0]出现一个下降沿时,key-flag取反一次,当key-flag为0时计数器启动,1时计数器暂停,当key-flag 为1同时key-inner[1]为9时,计数器清零。

Verilog数字钟设计

hclk<=0;

end

end

////////小时计时模块///

assign h_clk=hclk||counta;//////h_clk 产生进位或校正改变

assign cta=(num4&clk)|(!num4&h_clk); //cta 用于计时、校时中的小时计数

always @(posedge cta)

Hale Waihona Puke always @(posedge ctb)

if(ahour==8'h23) ahour<=0;

else

if(ahour[3:0]==9)

begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; end

else ahour[3:0]<=ahour[3:0]+1;

endmodule

else

begin counta<=change; {LD_min,LD_hour}<=1; end/////指示当前调整的是小时

always @(posedge clk_2) if ( cnt5 < 10/2-1) /////////////////////////////////////////10 分频,生成 1kHz 标准信号 begin cnt5<= cnt5 + 1; end

else begin cnt5<= 0; clk_1k<= ~clk_1k; end

代码如下:

//fenpin module fenpin(clk,clk_1Hz,clk_100Hz,clk_1k); output clk_1Hz,clk_100Hz,clk_1k; input clk; reg clk_1Hz=0,clk_3=0,clk_1=0,clk_2=0,clk_1k=0; reg [6:0] cnt1=0,cnt2=0,cnt3=0,cnt4=0,cnt5=0; wire clk_100Hz; always @(posedge clk) begin if ( cnt1 < 156/2-1) /////////////////////////////////////////////156 分频,生成 1MHz 信号 begin cnt1 <= cnt1 + 1; end else begin cnt1 <= 0; clk_1 <= ~clk_1; end end

基于verilogHDL的数字时钟

*****顶层模块信号定义:clk : 基准时钟信号输入;keysel : 校时状态/正常计时状态选择键输入;key_s : 校秒信号选择键输入;key_m : 校分信号选择键输入;key_h : 校时信号选择键输入;keyclr : 计时清零键;keyen : 计时开始键;buzzout : 声响输出;sled : 4位数码管段码输出;sl : 4位数码管位码输出;seg : 单个数码管输出;********************************************************* ******/moduleclock(clk,keysel,key_s,key_m,key_h,keyen,keyclr,sled,sl,seg,buzzout);output[7:0] sled;output[3:0] sl;output[7:0] seg;output buzzout;input clk;input keysel,key_s,key_m,key_h,keyen,keyclr;reg[24:0] count;wire[23:0] min;wire sec;wire sec_s,sec_m,sec_h,sec_narmal;divclk Q1(clk,sec_narmal,sec_s,sec_m,sec_h);modifyQ2(clk,keysel,key_s,key_m,key_h,sec,sec_narmal,sec_s,sec_m,sec_h);counttime Q3(sec,keyclr,keyen,min);display Q4(clk,sec,min,sled,sl,seg);music Q5(clk,min,buzzout,sec_narmal);endmodule*****分频模块信号定义:clk : 基准时钟信号输入;sec_narmal : 周期为1的信号输出;sec_s : 周期为0.5s的信号输出;sec_m : 周期为0.05s的信号输出;sec_h : 周期为0.0005s的信号输出;********************************************************* ******/module divclk(clk,sec_narmal,sec_s,sec_m,sec_h);input clk;output sec_narmal,sec_s,sec_m,sec_h;reg[23:0] count1;reg[22:0] count2;reg[19:0] count3;reg[12:0] count4;reg sec_narmal,sec_s,sec_m,sec_h;always@(negedge clk)begincount1=count1+1'b1;if(count1==24'd1*******)begincount1=24'h0;sec_narmal=~sec_narmal;endendalways@(negedge clk)begincount2=count2+1'b1;if(count2==23'd6000000)begincount2=23'h0;sec_s=~sec_s;endendalways@(negedge clk)begincount3=count3+1'b1;if(count3==20'd600000)begincount3=20'h0;sec_m=~sec_m;endendalways@(negedge clk)begincount4=count4+1'b1;if(count4==13'd6000)begincount4=13'h0;sec_h=~sec_h;endendendmodule/********************************************************* *****计时处理模块信号定义:sec : 计时信号输入;keyclr : 计时清零键;keyen : 计时开始键;min : 计时结果输出;********************************************************* ******/module counttime(sec,keyclr,keyen,min);input sec;input keyclr,keyen;output[23:0] min;reg[23:0] min;always@(posedge sec)beginif(!keyclr)beginmin=24'h0;endelseif(!keyen)beginmin=min+1'b1;if(min[3:0]==4'ha)beginmin[3:0]=4'h0;min[7:4]=min[7:4]+1'b1;if(min[7:4]==4'h6)beginmin[7:4]=4'h0;min[11:8]=min[11:8]+1'b1;if(min[11:8]==4'ha)beginmin[11:8]=4'h0;min[15:12]=min[15:12]+1'b1;if(min[15:12]==4'h6)beginmin[15:12]=4'h0;min[19:16]=min[19:16]+1'b1;if(min[19:16]==4'ha)beginmin[19:16]=4'h0;min[23:20]=min[23:20]+1'b1;endif(min[23:16]==8'h24)min[23:16]=0;endendendendendendendmodule/********************************************************* *****校时模块信号定义:clk : 基准时钟信号输入;keysel : 校时状态/正常计时状态选择键输入key_s : 校秒信号选择键输入key_m : 校分信号选择键输入key_h : 校时信号选择键输入sec_narmal : 周期为1的信号输出;sec_s : 周期为0.5s的信号输出;sec_m : 周期为0.05s的信号输出;sec_h : 周期为0.0005s的信号输出;sec : 计时信号输出;********************************************************* ******/modulemodify(clk,keysel,key_s,key_m,key_h,sec,sec_narmal,sec_s,sec_m,sec _h);input clk;input keysel;input key_s,key_m,key_h;input sec_narmal,sec_s,sec_m,sec_h;output sec;reg sec;always@(negedge clk)beginif(!keysel)beginif(!key_s)sec=sec_s;if(!key_m)sec=sec_m;if(!key_h)sec=sec_h;endelsesec=sec_narmal;endendmodule/********************************************************* *****报时模块信号定义:clk : 基准时钟信号输入;min : 当前计时结果输入;buzzout : 声响输出;********************************************************* ******/module music(clk,min,buzzout,sec_narmal);input clk,sec_narmal;input[23:0] min;output buzzout;reg[3:0] high,med,low;reg buzzout_reg;reg[24:0] count1,count2;reg[15:0] count_end,count_now;reg[7:0] counter;reg clk_4HZ;always@(posedge clk)beginif(count1<22'd3000000)count1=count1+1'b1;elsebegincount1=0;clk_4HZ=~clk_4HZ;endendalways@(posedge clk)beginif(count_now!=count_end)begincount2=25'h0;count_now=count_end;endcount2=count2+1'b1;if((min[15:0]>=16'h5945)&&(min[15:0]<=16'h5959))beginif((count2==count_end)&&(min[23:16]==8'h11))begincount2=25'h0;buzzout_reg=!buzzout_reg;endendif((min[15:0]>=16'h5950)&&(min[15:0]<=16'h5959)) beginif(min[23:16]!=8'h11)beginbuzzout_reg=!(count2[10]&sec_narmal);endendendalways@(posedge clk_4HZ)begincase({high,med,low})9'b000000001:count_end=16'hbb9a;9'b000000010:count_end=16'ha72f;9'b000000011:count_end=16'h94f2;9'b000000100:count_end=16'h8e78;9'b000000101:count_end=16'h7d63;9'b000000110:count_end=16'h6fb5;9'b000000111:count_end=16'h637f;9'b000001000:count_end=16'h5dfb;9'b000010000:count_end=16'h53bb;9'b000011000:count_end=16'h4a95;9'b000100000:count_end=16'h4651;9'b000101000:count_end=16'h3eb1;9'b000110000:count_end=16'h37da;9'b000111000:count_end=16'h31bf;9'b001000000:count_end=16'h2ef2;9'b010000000:count_end=16'h29d4;9'b011000000:count_end=16'h2543;9'b100000000:count_end=16'h232f;9'b101000000:count_end=16'h1f58;9'b110000000:count_end=16'h1bed;9'b111000000:count_end=16'h18df;endcaseendalways@(posedge clk_4HZ)beginif(counter==57)counter=0;elsecounter=counter+1'b1;case(counter)0:{high,med,low}=9'b000001000;1:{high,med,low}=9'b000001000;2:{high,med,low}=9'b000001000;3:{high,med,low}=9'b000001000;4:{high,med,low}=9'b000010000;5:{high,med,low}=9'b000010000;6:{high,med,low}=9'b000010000;7:{high,med,low}=9'b000010000;8:{high,med,low}=9'b000011000;9:{high,med,low}=9'b000011000;10:{high,med,low}=9'b000011000;11:{high,med,low}=9'b000011000;12:{high,med,low}=9'b000001000;13:{high,med,low}=9'b000001000;14:{high,med,low}=9'b000001000;15:{high,med,low}=9'b000001000;16:{high,med,low}=9'b000001000;17:{high,med,low}=9'b000001000;19:{high,med,low}=9'b000001000; 20:{high,med,low}=9'b000010000; 21:{high,med,low}=9'b000010000; 22:{high,med,low}=9'b000010000; 23:{high,med,low}=9'b000010000; 24:{high,med,low}=9'b000011000; 25:{high,med,low}=9'b000011000; 26:{high,med,low}=9'b000011000; 27:{high,med,low}=9'b000011000; 28:{high,med,low}=9'b000001000; 29:{high,med,low}=9'b000001000; 30:{high,med,low}=9'b000001000; 31:{high,med,low}=9'b000001000; 32:{high,med,low}=9'b000011000; 33:{high,med,low}=9'b000011000; 34:{high,med,low}=9'b000011000; 35:{high,med,low}=9'b000011000; 36:{high,med,low}=9'b000100000; 37:{high,med,low}=9'b000100000; 38:{high,med,low}=9'b000100000; 39:{high,med,low}=9'b000100000; 40:{high,med,low}=9'b000101000; 41:{high,med,low}=9'b000101000; 42:{high,med,low}=9'b000101000; 43:{high,med,low}=9'b000101000; 44:{high,med,low}=9'b000001000; 45:{high,med,low}=9'b000001000; 46:{high,med,low}=9'b000001000; 47:{high,med,low}=9'b000011000; 48:{high,med,low}=9'b000011000; 49:{high,med,low}=9'b000011000; 50:{high,med,low}=9'b000011000; 51:{high,med,low}=9'b000100000; 52:{high,med,low}=9'b000100000; 53:{high,med,low}=9'b000100000; 54:{high,med,low}=9'b000100000;56:{high,med,low}=9'b000101000;57:{high,med,low}=9'b000101000;endcaseendassign buzzout=buzzout_reg;endmodule/********************************************************* *****显示模块信号定义:clk : 基准时钟信号输入;min : 当前计时结果输入;sec : 计时的秒信号输入;sled_reg : 数码管短码输出;sl_reg : 数码管位码输出;seg_reg : 单个数码管输出;********************************************************* ******/module display(clk,sec,min,sled_reg,sl_reg,seg_reg);input clk;input sec;input[23:0] min;output[7:0] sled_reg;output[3:0] sl_reg;output[7:0] seg_reg;reg[7:0] sled_reg;reg[3:0] sl_reg;reg[7:0] seg_reg;reg[15:0] count;reg[3:0] ledbuf;always@(negedge clk)begincount=count+1'b1;endalways@(count[11:10])begincase(count[11:10])2'h0:ledbuf=min[3:0];2'h1:ledbuf=min[7:4];2'h2:ledbuf=min[11:8];2'h3:ledbuf=min[15:12];endcasecase(count[11:10])2'h0:sl_reg=4'b0111;2'h1:sl_reg=4'b1011;2'h2:sl_reg=4'b1101;2'h3:sl_reg=4'b1110;endcaseendalways@(ledbuf)begincase(ledbuf)4'h0:sled_reg=8'hc0;4'h1:sled_reg=8'hf9;4'h2:sled_reg=8'ha4;4'h3:sled_reg=8'hb0;4'h4:sled_reg=8'h99;4'h5:sled_reg=8'h92;4'h6:sled_reg=8'h82;4'h7:sled_reg=8'hf8;4'h8:sled_reg=8'h80;4'h9:sled_reg=8'h90;4'ha:sled_reg=8'h88;4'hb:sled_reg=8'h83;4'hc:sled_reg=8'hc6;4'hd:sled_reg=8'ha1;4'he:sled_reg=8'h86;4'hf:sled_reg=8'h8e;endcaseif((count[11:10]==2'b10)&sec)sled_reg=sled_reg&8'h7f; endalways@(min[23:16])begincase(min[23:16])8'h0:seg_reg=8'h3f;8'h1:seg_reg=8'h06;8'h2:seg_reg=8'h5b;8'h3:seg_reg=8'h4f;8'h4:seg_reg=8'h66;8'h5:seg_reg=8'h6d;8'h6:seg_reg=8'h7d;8'h7:seg_reg=8'h07;8'h8:seg_reg=8'h7f;8'h9:seg_reg=8'h6f;8'h10:seg_reg=8'h77;8'h11:seg_reg=8'h7c;8'h12:seg_reg=8'hbf;8'h13:seg_reg=8'h86;8'h14:seg_reg=8'hdb;8'h15:seg_reg=8'hcf;8'h16:seg_reg=8'he6;8'h17:seg_reg=8'hed;8'h18:seg_reg=8'hfd;8'h19:seg_reg=8'h87;8'h20:seg_reg=8'hff;8'h21:seg_reg=8'hef;8'h22:seg_reg=8'hf7;8'h23:seg_reg=8'hfc;endcaseendendmodule。

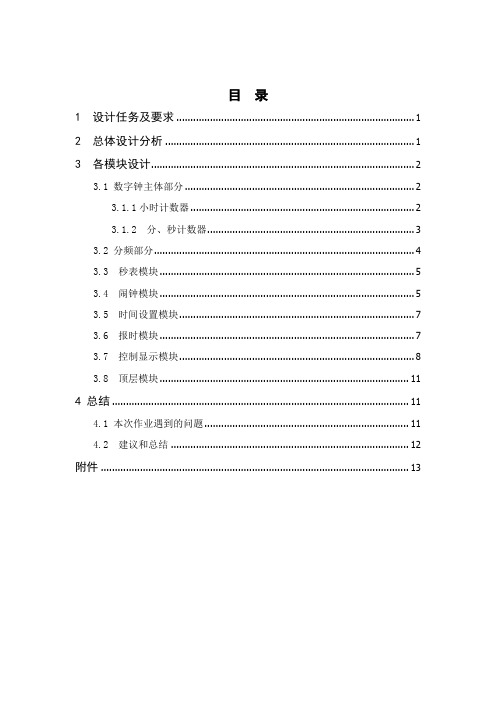

(完整word版)数字钟verilog(word文档良心出品)

目录1 设计任务及要求 (1)2 总体设计分析 (1)3 各模块设计 (2)3.1 数字钟主体部分 (2)3.1.1小时计数器 (2)3.1.2 分、秒计数器 (3)3.2 分频部分 (4)3.3 秒表模块 (5)3.4 闹钟模块 (5)3.5 时间设置模块 (7)3.6 报时模块 (7)3.7 控制显示模块 (8)3.8 顶层模块 (11)4 总结 (11)4.1 本次作业遇到的问题 (11)4.2 建议和总结 (12)附件 (13)1 设计任务及要求本次大作业的要求为设计一个多功能数字钟,其具体要求如下:1.有基础的实时数字钟显示功能,即时、分、秒的正常显示模式,并且在此基础上增加上,下午显示。

2.手动校准。

按动方式键,将电路置于校时状态,则计时电路可用手动方式校准,每按一下校时键,时计数器加1;按动方式键,将电路置于校分状态,以同样方式手动校分。

3.整点报时,仿中央人民广播电台整点报时信号,从59分50秒起每隔2秒发出一次低音“嘟”信号(信号鸣叫持续时间1S,间隙时间1S)连续5次,到达整点(00分00秒时),发一次高音“哒”信号(信号持续时间1S)。

4.闹时功能,按动方式键,使电路工作于预置状态,此时显示器与时钟脱开,而与预置计数器相连,利用前面手动校时,校分方式进行预置,预置后回到正常模式。

当计时计至预置的时间时,扬声器发出闹铃信号,时间为半分钟,闹铃信号可以用开关“止闹”,按下此开关后,闹铃声立刻中止,正常情况下应将此开关释放,否则无闹时作用。

5.秒表功能。

按start键开始计秒,按stop键停止计秒并保持显示数不变,直到复位信号加入。

2 总体设计分析设计的总体部分按照要求可以分为基本的数字时钟显示、手动校准、整点报时、闹钟功能和秒表功能5大部分。

其总体设计框图如下:图1 总体设计框图其中整点报时跟闹钟部分要求不同频率的声响,所以需要加入分频器模块将输入的1kHZ的分频产生500HZ及1HZ的方波信号,其中1HZ的信号对应1S 的周期,可以用作时钟秒的显示及秒表部分。

基于FPGA的数字时钟设计设计

基于FPGA的数字时钟设计设计设计(论文)题目:基于FPGA的数字时钟设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日摘要随着科学技术的飞速发展,系统向着高速度、低功耗、低电压和网络化、移动化方向发展,各个领域对电路的要求越来越高,传统单一功能的电路很难满足发展的要求,而可编程逻辑器件(CPLD/FPGA)可以很方便地通过对逻辑结构的修改和配置,完成对系统和设备的升级。

基于Verilog HDL设计的数字时钟

深圳大学考试答题纸(以论文、报告等形式考核专用)二○18 ~二○19 学年度第一学期课程编1602080001 课程名称号学姓名李思豪专业年级电子科学与技术16级1班号题目:基于Verilog HDL设计的数字时钟摘要:本文利用Verilog HDL语言自顶向下的设计方法设计多功能数字钟,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Altera QuartusⅡ 6.0和cyclnoe II EP2C35F672C6完成综合、仿真。

此程序通过下载到FPGA芯片后,可应用于实际的数字钟显示中关键词:Verilog HDL;硬件描述语言;FPGA目录一、实验任务 (3)实验目的 (3)实验要求 (3)二、设计思路 (3)三、实验结果 (10)四、总结与收获 (14)一、实验任务实验目的1.深入了解基于quartus ii工具的复杂时序逻辑电路的设计。

2.理解并熟练利用EDA工具进行综合设计。

3.熟练掌握芯片烧录的流程及步骤。

4.掌握Verilog HDL 语言的语法规范及时序电路描述方法。

实验要求设计一个带秒表功能的24 小时数字钟,它包括以下几个组成部分:①显示屏,由6 个七段数码管组成,用于显示当前时间(时:分,秒)或设置的秒表时间;②复位键复位所有显示和计数③设置键,用于确定新的时间设置,三个消抖按键分别用于时分秒的设置④秒表键,用于切换成秒表功能基本要求(1) 计时功能:这是本计时器设计的基本功能,每隔一秒计时一次,并在显示屏上显示当前时间。

(2) 秒表功能:设置时间,进行倒计时功能(3) 设置新的计时器时间:按下设置键后,用户能通过时分秒三个消抖按键对时间进行设置。

二、设计思路1、总原理框图:原理如上图所示,时钟由分频器模块,数码管显示模块,计时器模块三个模块构成,每个模块实现如下的不同功能,最后通过在顶层模块的调用,来实现时钟功能。

2.顶层模块:顶层模块调用三个字模块,并且定义输入输出口,代码输入所示:modulemyclock2(daojishi,stop,clk,reset,shi,fen,miao,miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2) ;input clk,reset,stop,shi,fen,miao,daojishi;output[6:0] miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2;wire[3:0] miao1,miao2,fen1,fen2,shi1,shi2;wire clk_1hz;divider_1HZ divider1hz(clk_1hz,reset,clk);count count1(daojishi,shi,fen,miao,stop,miao1,miao2,fen1,fen2,shi1,shi2,reset,clk_1hz); decode4_7 d0(miaoout1,miao1);decode4_7 d1(miaoout2,miao2);decode4_7 d2(fenout1,fen1);decode4_7 d3(fenout2,fen2);decode4_7 d4(shiout1,shi1);decode4_7 d5(shiout2,shi2);endmodule输入输出端口类型功能表:三个子模块的原理和代码:(1)分频模块:分频模块的作用主要是要获得各种频率的时钟信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

深圳大学考试答题纸(以论文、报告等形式考核专用)二○18 ~二○19 学年度第一学期课程编1602080001 课程名称号学姓名李思豪专业年级电子科学与技术16级1班号题目: 基于Verilog HDL设计的数字时钟摘要:本文利用Verilog HDL语言自顶向下的设计方法设计多功能数字钟,突出了其作为硬件描述语言的良好的可读性、可移植性与易理解等优点,并通过Altera QuartusⅡ6、0与cyclnoe II EP2C35F672C6完成综合、仿真。

此程序通过下载到FPGA芯片后,可应用于实际的数字钟显示中关键词:Verilog HDL;硬件描述语言;FPGA目录一、实验任务 (3)实验目的 (3)实验要求 (3)二、设计思路 (3)三、实验结果 (10)四、总结与收获 (14)一、实验任务实验目的1.深入了解基于quartus ii工具的复杂时序逻辑电路的设计。

2.理解并熟练利用EDA工具进行综合设计。

3.熟练掌握芯片烧录的流程及步骤。

4.掌握Verilog HDL 语言的语法规范及时序电路描述方法。

实验要求设计一个带秒表功能的24 小时数字钟,它包括以下几个组成部分:①显示屏,由6 个七段数码管组成,用于显示当前时间(时:分,秒)或设置的秒表时间;②复位键复位所有显示与计数③设置键,用于确定新的时间设置,三个消抖按键分别用于时分秒的设置④秒表键,用于切换成秒表功能基本要求(1) 计时功能:这就是本计时器设计的基本功能,每隔一秒计时一次,并在显示屏上显示当前时间。

(2) 秒表功能:设置时间,进行倒计时功能(3) 设置新的计时器时间:按下设置键后,用户能通过时分秒三个消抖按键对时间进行设置。

二、设计思路1、总原理框图:原理如上图所示,时钟由分频器模块,数码管显示模块,计时器模块三个模块构成,每个模块实现如下的不同功能,最后通过在顶层模块的调用,来实现时钟功能。

2.顶层模块:顶层模块调用三个字模块,并且定义输入输出口,代码输入所示:modulemyclock2(daojishi,stop,clk,reset,shi,fen,miao,miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2) ;input clk,reset,stop,shi,fen,miao,daojishi;output[6:0] miaoout1,miaoout2,fenout1,fenout2,shiout1,shiout2;wire[3:0] miao1,miao2,fen1,fen2,shi1,shi2;wire clk_1hz;divider_1HZ divider1hz(clk_1hz,reset,clk);count count1(daojishi,shi,fen,miao,stop,miao1,miao2,fen1,fen2,shi1,shi2,reset,clk_1hz); decode4_7 d0(miaoout1,miao1);decode4_7 d1(miaoout2,miao2);decode4_7 d2(fenout1,fen1);decode4_7 d3(fenout2,fen2);decode4_7 d4(shiout1,shi1);decode4_7 d5(shiout2,shi2);endmodule输入输出端口类型功能表:三个子模块的原理与代码:(1)分频模块:分频模块的作用主要就是要获得各种频率的时钟信号。

输入信号27MHZ的信号,要想获得1HZ的信号作为秒脉冲计时,则要对27MHZ信号分频。

通过计数的方式,当计数从0开始到时,1HZ信号取反一次,计数又从0开始,如此循环,就可以得到1HZ脉冲信号。

对于其她信号也就是如此,只就是计数值不一样,得到的分频信号不同。

模块代码如下:module divider_1HZ(clk_1hz,reset,clk);output clk_1hz;input reset,clk;reg clk_1hz;reg[23:0] count;always @(posedge clk)beginif(reset)begincount<=0;clk_1hz<=0;endelsebeginif(count==)begincount<=0;clk_1hz<=~clk_1hz;endelsecount<=count+1;//计数endendendmodule(2)译码显示模块:一、数码管显示:通过传入响应的十进制数,运用case语句转换输出相应的7位二进制显示码,送入数码管显示。

代码如下:module decode4_7(temp,indec);output[6:0] temp;input[3:0] indec;reg[6:0] temp;always @(indec)begincase(indec) //用case 语句进行译码4'd0:temp[6:0]=7'b1000000;4'd1:temp[6:0]=7'b1111001;4'd2:temp[6:0]=7'b0100100;4'd3:temp[6:0]=7'b0110000;4'd4:temp[6:0]=7'b0011001;4'd5:temp[6:0]=7'b0010010;4'd6:temp[6:0]=7'b0000010;4'd7:temp[6:0]=7'b1111000;4'd8:temp[6:0]=7'b0000000;4'd9:temp[6:0]=7'b0010000;default: temp=7'bz;endcaseendendmodule(3)、计时器模块:秒计数:在1HZ脉冲下进行秒计时,当计时达到59秒后,在下一个脉冲来临变0,并发出一个脉冲信号,可供下面分钟计数作为输入脉冲信号计时。

分钟计数:在输入脉冲下,分钟开始计时,当计时达到59后,在下一个脉冲来临变0,并发出一个脉冲,供小时计数的输入脉冲新号。

小时计数:脉冲信号来临时,计数加1,达到23后在下一个脉冲的作用下清零,从新计时。

如果有复位信号,则时分秒全部清零。

计时器模块还包含了设置时间与秒表切换的功能部分代码如下:module count(daojishi,shi,fen,miao,stop,miao1,miao2,fen1,fen2,shi1,shi2,reset,clk_1hz); input reset,clk_1hz,stop,daojishi;input shi,fen,miao;output miao1,miao2,fen1,fen2,shi1,shi2;reg[3:0] miao1,miao2,fen1,fen2,shi1,shi2;always @(posedge clk_1hz)beginif(reset)beginmiao1<=0;miao2<=0;fen1<=0;fen2<=0;shi1<=0;shi2<=0;endif(stop==1)begin //秒调节if(miao==0)beginmiao1<=miao1+1;if(miao1==9)beginmiao1<=0;miao2<=miao2+1;if(miao2==5)beginmiao2<=0;endendendif(fen==0) //分调节beginfen1<=fen1+1;if(fen1==9)beginfen1<=0;fen2<=fen2+1;if(fen2==5)beginfen2<=0;endendendif(shi==0) //时调节beginshi1<=shi1+1;if(shi1==9||((shi1==3)&&(shi2==2)))beginshi1<=0;shi2<=shi2+1;if(shi2>=2)beginshi2<=0;endendendendif((!reset)&&(stop==0))beginif(daojishi==0) //时钟程序beginmiao1<=miao1+1;if(miao1==9)beginmiao1<=0;miao2<=miao2+1;if(miao2==5)beginmiao2<=0;fen1<=fen1+1;if(fen1==9)beginfen1<=0;fen2<=fen2+1;if(fen2==5)beginfen2<=0;shi1<=shi1+1;if((shi1==9)||((shi1==3)&&(shi2==2)))beginshi1<=0;shi2<=shi2+1;if(shi2==2)beginshi2<=0;endendendendendendendelse //倒计时程序beginif(!((shi1==0)&&(shi2==0)&&(fen1==0)&&(fen2==0)&&(miao2==0)&&(miao1==0)))beginmiao1<=miao1-1;if(miao1==0)beginmiao1<=9;miao2<=miao2-1;if(miao2==0)beginmiao2<=5;fen1<=fen1-1;if(fen1==0)beginfen1<=9;fen2<=fen2-1;if(fen2==0)beginfen2<=5;shi1<=shi1-1;if(shi1==0)beginshi1<=9;shi2<=shi2-1;if(shi2==0)beginshi2<=0;endendendendendendendendendendendmodule3.引脚排布:如下所示:引脚分布图二、实验结果(1)波形仿真在Quartus II中利用仿真波形进行功能或时序仿真的基本步骤如下:(1)创建新的矢量波形文件(*、vwf)、(2)添加输入、输出节点。

(3)编译输入节点的波形。

(4)完成矢量波形文件的创建之后,用户即可以对设计进行功能或时序仿真。

(5)仿真启动后,状态窗口会同时自动打开,在状态窗口中显示仿真进度及所用时间。