精品课件-Xilinx FPGACPLD设计初级教程-第6章

《FPGA入门学习》课件

LED闪烁设计

总结词

通过LED闪烁设计,掌握FPGA的基本控制功能和数字逻辑设计。

详细描述

LED闪烁设计是FPGA入门学习的基本项目之一,通过该设计,学习者可以了解FPGA的基本控制功能 ,掌握数字逻辑设计的基本原理和方法。LED闪烁设计通常涉及到LED灯的驱动和控制,需要学习者 掌握基本的数字逻辑门电路和时序控制。

FPGA具有并行处理和高速计算的优点,适 用于数字信号处理中的实时信号处理和算 法加速。

数字滤波器设计

频谱分析和正交变换

FPGA可以实现高性能的数字滤波器,如 FIR滤波器和IIR滤波器,用于信号降噪和特 征提取。

FPGA可以高效地实现FFT等正交变换算法 ,用于频谱分析和信号频率成分的提取。

图像处理应用

优化设计技巧

时序优化

讲解如何通过布局布线、时序分析等手段优化 FPGA设计,提高时序性能。

资源共享

介绍如何通过资源共享减少FPGA资源占用,提 高设计效率。

流水线设计

讲解如何利用流水线设计技术提高系统吞吐量。

硬件仿真与调试技术

仿真工具使用

介绍常用HDL仿真工具(如ModelSim)的使用方法 。

03

CATALOGUE

FPGA开发实战

数字钟设计

总结词

通过数字钟设计,掌握FPGA的基本开发流程和硬件描述语言的应用。

详细描述

数字钟设计是FPGA入门学习的经典项目之一,通过该设计,学习者可以了解FPGA开 发的基本流程,包括设计输入、综合、布局布线、配置下载等。同时,数字钟设计也涉 及到硬件描述语言(如Verilog或VHDL)的应用,学习者可以掌握基本的逻辑设计和

基础语言。

FPGA开发流程

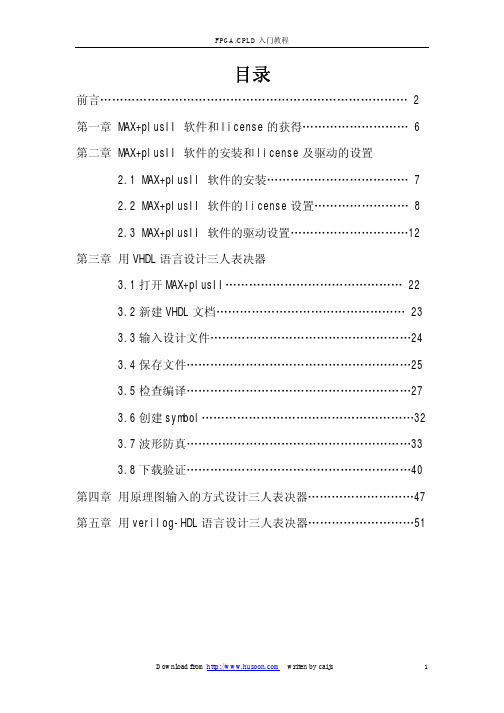

CPLD入门教程

目录前言 (2)第一章 MAX+plusII 软件和license的获得 (6)第二章 MAX+plusII 软件的安装和license及驱动的设置2.1 MAX+plusII 软件的安装 (7)2.2 MAX+plusII 软件的license设置 (8)2.3 MAX+plusII 软件的驱动设置 (12)第三章用VHDL语言设计三人表决器3.1打开MAX+plusII (22)3.2新建VHDL文档 (23)3.3输入设计文件 (24)3.4保存文件 (25)3.5检查编译 (27)3.6创建symbol (32)3.7波形防真 (33)3.8下载验证 (40)第四章用原理图输入的方式设计三人表决器 (47)第五章用verilog-HDL语言设计三人表决器 (51)前言编写本入门教程(V1.2)的目点是为了让FPGA/CPLD初学者快速地入门。

该教程的特点是通过基本概念讲解和实际的例子来让初学者迅速了解FPGA/CPLD。

该教程是共享文件,可以复制、下载、转载,如果转载该文章请注明出处:;该教程未经许可,不得用于商业用途。

FPGA/CPLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

FPGA/CPLD的基本知识:1.什么是FPGA/CPLDFPGA (Field Programmable Gate Array)是现场可编程门阵列,CPLD是复杂的可编程逻辑器件(Complex Programmable Logic Device)的简称,不同厂家有不同的称呼,Xilinx把SRAM工艺,要外挂配置用的EEPROM的PLD叫FPGA,把Flash工艺(类似EEPROM工艺),乘积项结构的PLD叫CPLD; Altera把自己的PLD产品MAX系列(EEPROM工艺),FLEX/ACEX/APEX系列(SRAM工艺)都叫作CPLD,即复杂PLD(Complex PLD),由于FLEX/ACEX/APEX系列也是SRAM工艺,要外挂配置用的EPROM,用法和Xilinx的FPGA一样,所以很多人把Altera的FELX/ACEX/APEX系列产品也叫做FPGA.但由于FPGA和CPLD功能基本相同,只是工艺和实现形式不同,所以初学者可以不要详细区分,我们可以统称为FPGA/CPLD。

《FPGACPLD器件》课件

FPGA和CPLD器件的未来发展方向

随着技术的不断进步,FPGA和CPLD的性能将进一步提升,并且将探索新的应用领域,如医疗、汽车、空天 等。

相关技术和标准的趋势预测

未来的技术和标准的发展方向是对FPGA和CPLD而言众所周知的。重点将放在性能提升、功耗优化和多样化 应用等方面。

开发工具

端口逻辑设计工具,硬件说明设计工具和硬件调试工具等都是硬件开发过程中的重要工具。

VHDL和Verilog两种设计语言 简介

Verilog和VHDL都是可编程逻辑设计中使用非常广泛的硬件描述语言, Verilog更适合硬件验证,VHDL更适合系统级描述。

FPGA和CPLD器件的编程方式

通常,FPGA和CPLD器件的编程方式可以从编译和下载两个方面进行,其中 编译是由设计委员会生成原始编程文件,而下载通常是将生成的原始编程文 件加载到器件中的部分或全部逻辑元素。

占用资源相对较高,以提供 更多硬件资源和输出端口

相对较高

相对较低

应用场景与优势

1 人工智能

FPGA为高速深度学习网 络带来了强大的计算性能 和处理速度。

2 通信

CPLD驱动芯片能够快速 建立通信通道,FPGA能 够将它们集成到一个芯片 上。

3 开发调试

设计流程快,性价比高, 并且可编写脚本自动化设 计流程,提高开发效率。

IOB(输入输出块)的组成和功能

IOB是用于将芯片内部和外部芯片系统中的信号连接起来的接口,通常完成与外部设备通信的输入和输出任务。

BRAM(存储单元)的组成和 功能

BRAM是一种FPGA内部内存单元,通常由一组存储器块、数据线、地址线和 控制单元组成,可用于逻辑电路和嵌入式处理器存储数据。

DSP(数字信号处理器)的功能和应用

FPGA入门培训教材共45张PPT课件

# STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out route_design write_checkpoint -force $outputDir/post_route report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

精品课件-Xilinx FPGACPLD设计初级教程-实验六

实验六 数码管蛇形显示 图T6.7 保存文件

实验六 数码管蛇形显示 ⑤ 在工程项目的“Sources”窗口中右击“xc95144xl10TQ100”,选择“Add Source...”,如图T6.8所示。

图T6.8 加入源代码

实验六 数码管蛇形显示 ⑥ 通过上一步骤会出现“Add Existing Sources”对话 框,在此对话框中选择lab6.v文件,点击“打开”按钮,如 图T6.9所示。

实验六 数码管蛇形显示

3. 实验步骤 (1) 建立ISE工程。 具体步骤如下: ① 打开ISE 9.1i,选择“开始”→“程序”→“Xilinx ISE 9.1i”→“Project Navigator”(或者直接双击桌面图 标启动ISE)。 ② 新建一个工程项目,选择菜单命令“File”→“New Project”(如果打开ISE后,上面已经有存在的工程项目,请 选择“File”→“Close Project”)。

实验六 数码管蛇形显示 图T6.14 参考“lab6_ucf.txt”文件配置引脚

实验六 数码管蛇形显示

③ 在Xilinx PACE窗口中,选择“File”→“Save”。 在出现的“Bus Delimiter”对话框里,选择默认的“XST Default”形式,点击“OK”按钮。

④ 关闭Xilinx PACE窗口。在工程项目的资源操作窗口 (Processes)中双击“Implement Design”,进行布局布线并 生成jed下载文件,如图T6.15所示。

2. 实验内容 本实验要求以EZBoard为开发板,完成逻辑设计后并下板 测试。实现的功能为:以一只pb按键作为复位键,另一只pb 按键作为启动键。启动后蛇形显示从左向右、从右向左不停地 移动。EZBoard开发板上的晶振频率为4 MHz,按键pb(1)~ pb(4)在按下时为低电平,数码管低电平驱动。 设计的端口连接如图T6.1所示,方框里的名称为设计模 块中定义的名称(此名称是本实验参考程序中定义的名称),方 框外的名称为对应EZBoard开发板上的器件名称。

CPLD-FPGA课件(第6章)好东西

•

Example will be more clear

Entity test1 is port (a, b, sel1, sel2 : in bit; result : out bit); end test1; architecture test1_body of test1 is begin process (sel1, sel2,a, b) begin if (sel1 = ‘1’) then result <= a; elsif (sel2 = ‘1’) then result <= b; else result <= ‘0’; Result change if sel1, sel2, a or b change the value end if; end process; Wait : I can do the same join with Concurrent Statement end test1_body;

注意:WITH-SELECT-WHEN语句必须指明所有互斥条 注意:WITH-SELECT-WHEN语句必须指明所有互斥条 即穷举),在上例中即“sel”的所有取值组合 ),在上例中即 的所有取值组合。 件(即穷举),在上例中即“sel 的所有取值组合。 假设“sel”的类型为 std_logic_vector”, 的类型为“ 假设“sel 的类型为“std_logic_vector ,则取值 组合除了00,01,10,11外还有0X,0Z,x1 00,01,10,11外还有0X,0Z,x1…等 组合除了00,01,10,11外还有0X,0Z,x1 等。虽然这 些取值组合在实际电路中不一定出现,但也应列出。 些取值组合在实际电路中不一定出现,但也应列出。 因此在选择信号赋值语句中为避免麻烦可以用 others”代替其他各种组合情况 代替其他各种组合情况。 “others 代替其他各种组合情况。

《FPGACPLD简介》PPT课件

三、FPGA的用途

FPGA能完成任何数字器件的功能,上至高性能CPU,下至简单的74

系列电路。在汽车、军事和航空航天、广播、测量和测试、消

费类、有线或无线通信、工业、医疗等等方面都有广泛的运用。

四、CPLD/FPGA与MCU的比较

(一)、MCU(微处理器或单片机)面临的问题

由MCU为主构成的电子应用系统通常出现的问题可以分为两

五、学习FPGA/CPLD所要掌握的知识 1、硬件知识 FPGA/CPLD就像一张白纸,我们不许要

对内部有太深的了解,在编程的时候也不要像MCU那样对内部什 么寄存器进行初始化什么的,我们只要写程序就好。而且我们对 于他的那么多的管脚,其实一部分是有专门用途的,那么我们可 以不用,别的IO口都是可以用的,而且都是一样的,比如EPF10K 10TC144-4的可用IO口为102个(一般的单片机只有32个端口,而 且这些端口不是都可以用的),都是一样的端口。因此,硬件不 需要太多的了解。

哈尔滨工程大学信通学院

FPGA/CPLD简介

缪善 林

QQ:330495908 Email:mshl1981@ 2007-04-04

(一)、现场可编程门阵列(FPGA) -------(Field Progr

ammable Gate Array) (二)、复杂可编程逻辑器件(CPLD) -------(Complex Pro

grammable Logic Device)

二、FPGA与CPLD的比较

尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但 由于CPLD和FPGA结构上的差异,具有各自的特点: (一)、CPLD更适合各种算法和组合逻辑,FPGA更适合于时序逻辑。 (二)、由于内部布线结构,CPLD的时序延迟是均匀的和可预测的, 而FPGA的延迟的不可预测性。(我们在用的时候不用考虑内部结构 的布线问题) (三)、在编程上FPGA比CPLD具有更大的灵活性。

FPGACPLD基本结构及原理课件

2024/2/20

7

浮栅型电可擦除熔丝结构

G1 S

n+

G2 SiO2 D

n+

大多数CPLD器 件采用此工艺

可反复编程 不用每次上电重新 下载,但相对速度 慢,功耗较大

2024/2/20

8

(4)SRAM编程技术

与浮栅型熔丝结构基本相同。SRAM编程技术是 在FPGA器件中采用的主要编程工艺之一。SRAM型的 FPGA是易失性的,断电后其内部编程数据(构造代码) 将丢失,需在外部配接ROM存放FPGA的编程数据。

3.可编程互连资源(PIR)

PIR由许多金属线段构成,这些金属线段带有可编 程开关,通过自动布线实现各种电路的连接。实现 FPGA内部的CLB和CLB之间、CLB和IOB之间的连接。

XC4000系列采用分段互连资源结构,按相对长度 可分为单长线、双长线和长线等三种。

2024/2/20

25

四、CPLD与FPGA的区别

2024/2/20

15

EPM7128E乘积项扩展和并联扩展项的结构图

来自 上一个宏单元

乘积项 选择 矩阵

Preset

Clock Clear

宏单元 乘积项逻

辑

共享乘积 项

并联扩展

乘积项 选择 矩阵

Preset

Clock Clear

宏单元 乘积项逻

辑

到下一个 宏单元

2024/2/20

16

(2)多触发器结构

2024/2/20

5

浮栅型紫外线擦除熔丝结构

G1 S

G2 D SiO2

早期PROM器件 采用此工艺

n+

n+

可反复编程

CPLD配置讲稿-精品课件

中国矿大 信电学院

③ 十六进制格式(.hex): HEX格式文件是使用第三方编程硬件对并行

EPROM编程的数据文件, 从而可以将并行EPROM作 为数据源, 用微处理器对FLEX器件进行被动串行同步 (PS)配置或被动串行异步(PSA)配置。 ④ ASCII码文本格式(.ttf):

TTF格式文件适用于被动串行同步(PS)配置和被 动串行异步(PSA)配置类型, 它在配置数据之间以逗 号分隔。

15、我就像一个厨师,喜欢品尝食物。如果不好吃,我就不要它。2021年8月下午6时15分21.8.1518:15August 15, 2021

16、我总是站在顾客的角度看待即将推出的产品或服务,因为我就是顾客。2021年8月15日星期日6时15分35秒18:15:3515 August 2021

17、利人为利已的根基,市场营销上老是为自己着想,而不顾及到他人,他人也不会顾及你。下午6时15分35秒下午6时15分18:15:3521.8.15

1、用户状态(User mode) 即电路中CPLD器件正常工作时的状态;

2、配置状态(Configuration mode ) 指将编程数据装入CPLD/FPGA器件的过程,也可称 之为下载状态;

3、初始化状态(Initialization) 此时CPLD/FPGA器件内部的各类寄存器复位, 让I/O引脚为使器件正常工作作好准备。

中国矿大 信电学院

ALTERA的编程文件

ALTERA 公司的开发系统MAX+PLUSⅡ可以生成多种格式的编 程数据文件。对于不同系列器件, 所能生成的编程/配置文 件类型有所不同, 但大致可有下面几种类型:

① SRAM Object格式(.sof): SOF格式文件用于FLEX器件的Bit Blaster或Byteblaster被 动配置方式。 MAX+PLUS II编译综合工具会在编译综合过程中自动为 FLEX系列器件生成SOF数据格式文件, 其它数据格式均可由 该种格式转化而成。

精品课件-Xilinx FPGA设计基础-第6章

第6章 VHDL程序设计实验

component MY_OR2 port ( A: in STD_LOGIC; B : in STD_LOGIC; C : out STD_LOGIC);

end component;

signal SIG1, SIG2 : STD_LOGIC;

第6章 VHDL程序设计实验

entity AND_OR is port ( INP: in STD_LOGIC_VECTOR(3 downto 0); Z: out STD_LOGIC);

TRUCT of AND_OR is

component MY_AND2 port ( A: in STD_LOGIC; B: in STD_LOGIC; C: out STD_LOGIC);

(5) 选择菜单栏中的Porject→Add Copy of Source。 (6) 文件查找路径选择为\VHDL_LABS\LAB1,选择已存在 的三个文件AND_OR,MY_AND2,MY_OR2,然后单击Open按钮。 (7) ISE会自动检测加入的文件,如图6.10所示。单击 OK按钮,确认添加的文件。

第6章 VHDL程序设计实验

第6章 VHDL程序设计实验

6.1 实验一 层次化工程的创建 6.2 实验二 仿真测试平台的创建 6.3 实验三 存储器和记录类型实验 6.4 实验四 n比特计数器及RTL验证实验 6.5 实验五 比较器实验 6.6 实验六 算术逻辑单元实验 6.7 实验七 状态机实验 6.8 实验八 计数器实验 6.9 实验九 IP核应用实验 6.10 实验十 数字时钟管理IP核实验

LAB2,并导入已有的VDHL程序。具体操作步骤如下: (1) 选择“开始→所有程序→Xilinx ISE 9.1i”或直接

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第6章 F3;BUFG的连接图

第6章 FPGA器件的全局时钟资源的使用

(5) Logic+DCM+BUFG的使用方法。DCM同样也可以控制 并变换普通时钟信号,即DCM的输入也可以是普通片内信号, 如图6.5所示。使用全局时钟资源时应注意以下原则:使用 IBUFG或IBUFGDS的充分必要条件是信号从专用全局时钟引脚 输入。换言之,当某个信号从全局时钟引脚输入时,不论它是 否为时钟信号,都必须使用IBUFG或IBUFGDS;如果对某个信 号使用了IBUFG或IBUFGDS硬件原语,则这个信号必定是从全 局时钟引脚输入的。如果违反了这条原则,那么在布局布线时 会报错。这条规则的使用是由FPGA的内部结构决定的,即 IBUFG和IBUFGDS的输入端仅仅与芯片的专用全局时钟输入引 脚有物理连接,

第6章 FPGA器件的全局时钟资源的使用 (3) IBUFG+DCM+BUFG的使用方法。这种使用方法最灵活, 对全局时钟的控制更加有效。通过DCM模块不仅仅能对时钟进 行同步、移相、分频和倍频等变换,而且可以使全局时钟的输 出无抖动延迟,如图6.3所示。

图6.3 IBUFG+DCM+BUFG的连接图

第6章 FPGA器件的全局时钟资源的使用

(2) IBUFGDS:即IBUFG的差分形式。当信号从一对差分 全局时钟引脚输入时,必须使用IBUFGDS作为全局时钟输入缓 冲。

(3) BUFG:即全局时钟缓冲器。它的输入是IBUFG的输 出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时 钟延迟和抖动最小。一般BUFG由综合器自动推断并使用,如 果对全局时钟实行DLL或DCM时钟管理,则必须手动例化该缓 冲器。

(8) DCM:即数字时钟管理单元。它主要完成时钟的同 步、移相、分频、倍频和去抖动等。DCM与全局时钟有着密不 可分的联系。为了达到最小的延迟和抖动,几乎所有的DCM应 用都要使用全局缓冲资源。DCM可以用Xilinx ISE软件中的 ArchitectureWizard直接生成。

一般全局时钟资源的使用有以下五种方法: (1) IBUFG+BUFG的使用方法。IBUFG后面连接BUFG的方 法是全局时钟资源的最基本的使用方法,如图6.1所示。由于 IBUFG组合BUFG相当于BUFGP,所以这种使用方法也称为BUFGP 方法。

第6章 FPGA器件的全局时钟资源的使用 与普通IO和其他内部CLB等没有物理连接。另外,由于BUFGP 相当于IBUFG和BUFG的组合,所以BUFGP的使用也必须遵循上 述原则。

图6.5 Logic+DCM+BUFG的连接图

第6章 FPGA器件的全局时钟资源的使用

上述方法(3)和(5)只是针对器件中有DCM模块而设计的, 如果器件中只有DLL,则可用DLL代替DCM。全局时钟资源的例 化方法大致可分为两种:一是在程序中直接例化全局时钟资源; 二是通过综合阶段约束来实现对全局时钟资源的使用。第一种 方法比较简单,用户只需按照前面讲述的5种全局时钟资源的 基本使用方法编写代码或者绘制原理图即可。第二种方法则需 根据综合工具和布局布线工具的不同的自身优化特性来例化。 另外,如果用Xilinx ISE软件进行时钟布线,则只要时钟从 全局时钟引脚进入,并且按照方法(1)和(2)连入全局时钟引 脚(即不对时钟作任何运算处理),一般软件会自动加上BUFGP。

第6章 FPGA器件的全局时钟资源的使用 图6.1 IBUFG+BUFG的连接图

第6章 FPGA器件的全局时钟资源的使用 (2) IBUFGDS+BUFG的使用方法。当输入时钟信号为差分 信号时,需要使用IBUFGDS代替IBUFG,如图6.2所示。

图6.2 IBUFGDS + BUFG的连接图

(6) BUFGP:相当于IBUG加上BUFG。 (7) CLKDLL:即时钟延迟锁相环。CLKDLL在早期设计中 经常使用,用以完成全局时钟的同步和驱动等功能。随着数字 时钟管理模块(Digital Clock Manager,DCM)的出现,目前 CLKDLL的应用已经逐渐被DCM所取代。

第6章 FPGA器件的全局时钟资源的使用

第6章 FPGA器件的全局时钟资源的使用 图6.7 BUFGDLL结构图

第6章 FPGA器件的全局时钟资源的使用 在电路设计中,我们经常会碰到时钟分频设计。下面以用 CLKDLL模块进行时钟3分频为例进行介绍,其原理图如图6.8 所示(图中IBUF为输入缓冲器,OBUF为输出缓冲器),其 Verilog语言用法源程序如下:

.I(CLKIN),

第6章 FPGA器件的全局时钟资源的使用

.O (C LK IN_w)); IBUF rstpad (

.I(RESET), .O (R ES ET_w)); CLKDLL #( .C LKDV_D IVIDE(3); //CLKDV 分频比设置为 3(缺省值是 2) .D UTY_CY CLE_C ORR EC TION ("TRUE"); //设置输出信号的占空比是 50/50,为 FALSE 时输 出时钟就和时 钟源有相同的 //占空 //比(缺省值是 TRUE)

第6章 FPGA器件的全局时钟资源的使用

在利用FPGA的全局时钟资源时,有时会用到BUFGDLL原语 模块,其实BUFGDLL原语是一种最简单的DLL方式。它利用 IBUFG、CLKDLL和BUFG来实现最基本的DLL应用(如图6.7所示)。 在BUFGDLL中,BUFG用于时钟输出驱动,而用于BUFGDLL的 IBUFG、CLKDLL、BUFG必须在芯片的同一侧(顶部或底部)。

(3) RST(复位):控制DLL的初始化,高电平有效,通常 接地。

(4) CLK0(同频信号输出):与CLKIN无相位偏移。CLK90 与CLKIN有90°相位偏移,CLK180与CLKIN有180°相位偏移, CLK270与CLKIN有270°相位偏移。

第6章 FPGA器件的全局时钟资源的使用

(4) BUFGCE:即带有时钟使能端的全局缓冲。它有一个 输入端I、一个使能端CE和一个输出端O。只有当BUFGCE的使 能端CE有效(为高电平)时,BUFGCE才有输出。

第6章 FPGA器件的全局时钟资源的使用

(5) BUFGMUX:即全局时钟选择缓冲。它有I0和I1两个 输入、一个控制端S和一个输出端O。当S为低电平时输出时钟 为I0,反之为I1。需要指出的是,BUFGMUX的应用十分灵活, I0和I1两个输入时钟甚至可以为异步关系。

在Xilinx芯片中,CLKDLL模块的原型如图6.6所示。其引 脚说明如下:

第6章 FPGA器件的全局时钟资源的使用 图6.6 标准的DLL宏CLKDLL模块

第6章 FPGA器件的全局时钟资源的使用

(1) CLKIN(时钟源输入):输入时钟信号。CLKIN通常来 自IBUFG或BUFG。

(2) CLKFB(反馈时钟输入):DLL时钟反馈信号。DLL需 要一个参考信号或反馈信号来提供延迟补偿输出,该反馈信号 必须源自CLK0或CLK2X,并通过IBUFG或BUFG相连。

第6章 FPGA器件的全局时钟资源的使用

OBUF lckpad ( .I(LOCKED_dll ), .O (LOC KED));

endmodule

第6章 FPGA器件的全局时钟资源的使用

下面以用CLKDLL模块进行时钟4倍频为例进行介绍,其原 理图如图6.9所示。需要注意的是,此设计中用到SRL16原语, 其实SRL16是基于查找表(LUT)的移位寄存器,在实际应用中 既能节省资源,又能保证时序。其输入信号A3、A2、A1以及 A0选择移位寄存器的读取地址,当写使能信号高有效时,输入 信号将被加载到移位寄存器中。单个移位寄存器的深度可以是 固定的,也可以动态调整,最大不能超过16。使用SRL16单元 复位第二个DLL是非常重要的,否则,在输入从1x(25/75)波 形变化到2x(50/50)波形信号时,第二个DLL就不会识别频率 的变化。其Verilog语言用法源程序如下:

(5) CLKDV(分频输出):DLL输出时钟信号,是CLKIN的 分频时钟信号。DLL支持的分频系数可以为1.5、2、2.5、3、 4、5、8和16。

(6) CLK2X(两倍信号输出):CLKIN的2倍频时钟信号。 (7) LOCKED(锁存输出):为了实现锁存,DLL必须采样 几千个时钟周期的信号。在DLL锁存之后,LOCKED有效,此时 DLL输出的时钟才为有效信号。

第6章 FPGA器件的全局时钟资源的使用

.CLK180(), .CLK270(), .CLK2X(), .CLKDV(CLKDV_dll), .LOCKED(LOCKED_dll)); BUFG clkg ( .I(CLK0_dll), .O (C LK 0)); BUFG clkdv3 ( .I(CLKDV_ dl l), .O (C LK DV3));

第6章 FPGA器件的全局时钟资源的使用

.F ACTORY _JF (16'hC 080); //16 比特的 JF 因子参数 .S TA RTUP_WAIT("FALSE"); //等 DLL 锁相后再延迟配置 DONE 引脚,可 设置为 TRUE/FALSE(缺省值是 //FALSE) CLKDLL_inst ( .C LKIN (C LK IN_w), .CLKFB(CLK0), .RST(RESET_w), .CLK0(CLK0_dll), .CLK90(),

第6章 FPGA器件的全局时钟资源的使用

(4) Logic+BUFG的使用方法。BUFG不但可以驱动IBUFG 的输出,还可以驱动其他普通信号的输出。当某个信号(时钟、 使能、快速路径)的扇出非常大,并且要求抖动延迟最小时, 可以使用BUFG驱动该信号,使该信号利用全局时钟资源,如 图6.4所示。但需要注意的是,普通IO的输入或普通片内信号 进入全局时钟布线层需要一个固有的延时,一般在10 ns左右, 即普通IO和普通片内信号从输入到BUFG输出有一个约10 ns左 右的固有延时,但是BUFG的输出到片内所有单元(IOB、CLB、 选择性块RAM)的延时可以忽略不计,基本认为延时为0 ns。