海思方案HI3518E平台ISP调试环境搭建

Hi3518EV20XHi3516CV200 硬件设计 用户指南

海思方案 HI3518E平台ISP调试环境搭建

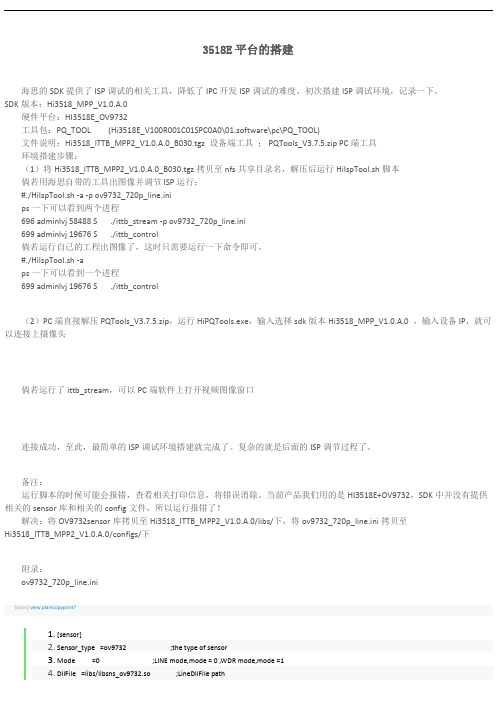

3518E平台的搭建海思的SDK提供了ISP调试的相关工具,降低了IPC开发ISP调试的难度。

初次搭建ISP调试环境,记录一下。

SDK版本:Hi3518_MPP_V1.0.A.0硬件平台:HI3518E_OV9732工具包:PQ_TOOL (Hi3518E_V100R001C01SPC0A0\01.software\pc\PQ_TOOL)文件说明:Hi3518_ITTB_MPP2_V1.0.A.0_B030.tgz 设备端工具; PQTools_V3.7.5.zip PC端工具环境搭建步骤:(1)将Hi3518_ITTB_MPP2_V1.0.A.0_B030.tgz拷贝至nfs共享目录名,解压后运行HiIspTool.sh脚本倘若用海思自带的工具出图像并调节ISP运行:#./HiIspTool.sh -a -p ov9732_720p_line.inips一下可以看到两个进程696 adminlvj 58488 S ./ittb_stream -p ov9732_720p_line.ini699 adminlvj 19676 S ./ittb_control倘若运行自己的工程出图像了,这时只需要运行一下命令即可。

ps一下可以看到一个进程699 adminlvj 19676 S ./ittb_control(2)PC端直接解压PQTools_V3.7.5.zip,运行HiPQTools.exe,输入选择sdk版本Hi3518_MPP_V1.0.A.0 ,输入设备IP,就可以连接上摄像头倘若运行了ittb_stream,可以PC端软件上打开视频图像窗口连接成功,至此,最简单的ISP调试环境搭建就完成了。

复杂的就是后面的ISP调节过程了。

备注:运行脚本的时候可能会报错,查看相关打印信息,将错误消除。

当前产品我们用的是HI3518E+OV9732,SDK中并没有提供相关的sensor库和相关的config文件,所以运行报错了!解决:将OV9732sensor库拷贝至Hi3518_ITTB_MPP2_V1.0.A.0/libs/下,将ov9732_720p_line.ini拷贝至Hi3518_ITTB_MPP2_V1.0.A.0/configs/下附录:ov9732_720p_line.ini[plain]view plaincopyprint?1.[sensor]2.Sensor_type =ov9732 ;the type of sensor3.Mode =0 ;LINE mode,mode = 0 ,WDR mode,mode =14.DllFile =libs/libsns_ov9732.so ;LineDllFile path5.6.[vi_dev]7.Input_mod =2 ;VI_INPUT_MODE_BT656 = 08. ;VI_INPUT_MODE_BT601,9. ;VI_INPUT_MODE_DIGITAL_CAMERA10.11.Work_mod =0 ;VI_WORK_MODE_1Multiplex = 012.13. ;VI_WORK_MODE_2Multiplex,14.15. ;VI_WORK_MODE_4Multiplexbine_mode =0 ;Y/C composite or separation mode18.19. ;VI_COMBINE_COMPOSITE = 0 /*Composite mode */20.21. ;VI_COMBINE_SEPARATE, /*Separate mode */22.p_mode =0 ;Component mode (single-component or dual-component)24.25. ;VI_COMP_MODE_SINGLE = 0, /*single component mode */26.27. ;VI_COMP_MODE_DOUBLE = 1, /*double component mode */28.29.Clock_edge =1 ;Clock edge mode (sampling on the rising or falling edge)30.31. ;VI_CLK_EDGE_SINGLE_UP=0, /*rising edge */32.33. ;VI_CLK_EDGE_SINGLE_DOWN, /*falling edge */34.35.Mask_num =2 ;Component mask37.Mask_0 =0xFFC0000038.39.Mask_1 =0x040.41.Scan_mode = 1;VI_SCAN_INTERLACED = 042.43. ;VI_SCAN_PROGRESSIVE,44.45.Data_seq =2 ;data sequence (ONLY for YUV format)46.47. ;----2th component U/V sequence in bt112048.49. ; VI_INPUT_DATA_VUVU = 0,50.51. ; VI_INPUT_DATA_UVUV,52.53. ;----input sequence for yuv54.55. ; VI_INPUT_DATA_UYVY = 0,56.59. ; VI_INPUT_DATA_YUYV,60.61. ; VI_INPUT_DATA_YVYU62.63.64.65.Vsync =1 ; vertical synchronization signal66.67. ;VI_VSYNC_FIELD = 0,68.69. ;VI_VSYNC_PULSE,70.71.VsyncNeg=0 ;Polarity of the vertical synchronization signal72.73. ;VI_VSYNC_NEG_HIGH = 0,74.75. ;VI_VSYNC_NEG_LOW /*if VIU_VSYNC_E76.77.Hsync =0 ;Attribute of the horizontal synchronization signal78.81. ;VI_HSYNC_PULSE,82.83.HsyncNeg =0 ;Polarity of the horizontal synchronization signal84.85. ;VI_HSYNC_NEG_HIGH = 0,86.87. ;VI_HSYNC_NEG_LOW88.89.VsyncValid =0 ;Attribute of the valid vertical synchronization signal90.91. ;VI_VSYNC_NORM_PULSE = 0,92.93. ;VI_VSYNC_VALID_SINGAL,94.95.VsyncValidNeg =0;Polarity of the valid vertical synchronization signal96.97. ;VI_VSYNC_VALID_NEG_HIGH = 0,98.99. ;VI_VSYNC_VALID_NEG_LOW101.Timingblank_HsyncHfb =0 ;Horizontal front blanking width102.103.Timingblank_HsyncAct =1280 ;Horizontal effetive width104.105.Timingblank_HsyncHbb =0 ;Horizontal back blanking width106.107.Timingblank_VsyncVfb =0 ;Vertical front blanking height108.109.Timingblank_VsyncVact =720 ;Vertical effetive width110.111.Timingblank_VsyncVbb=0 ;Vertical back blanking height112.113.Timingblank_VsyncVbfb =0 ;Even-field vertical front blanking height(inter lace, invalid progressive)114.115.Timingblank_VsyncVbact=0 ;Even-field vertical effetive width(interlace, i nvalid progressive)116.117.Timingblank_VsyncVbbb =0 ;Even-field vertical back blanking height(inte rlace, invalid progressive)118.121.;----- only for bt656 ----------122.FixCode =0 ;BT656_FIXCODE_1 = 0,123.124. ;BT656_FIXCODE_0125.126.FieldPolar=0 ;BT656_FIELD_POLAR_STD = 0127.128. ;BT656_FIELD_POLAR_NSTD129.130.DataPath =1 ;ISP enable or bypass131.132. ;VI_PATH_BYPASS = 0,/* ISP bypass */133.134. ;VI_PATH_ISP = 1,/* ISP enable */135.136. ;VI_PATH_RAW = 2,/* Capture raw data, for debug */ 137.138.InputDataType=1 ;VI_DATA_TYPE_YUV = 0,VI_DATA_TYPE_RGB = 1, 139.142.143.[vi_chn]144.145.CapRect_X =0146.147.CapRect_Y =0148.149.CapRect_Width=1280150.151.CapRect_Height=720152.153.DestSize_Width=1280154.155.DestSize_Height=720156.157.CapSel =2 ;Frame/field select. ONLY used in interlaced mode158. ;VI_CAPSEL_TOP = 0, /* top field */159. ;VI_CAPSEL_BOTTOM, /* bottom field */160. ;VI_CAPSEL_BOTH, /* top and bottom field */162.PixFormat =19 ;163.164.165.166.SrcFrameRate=-1 ;Source frame rate. -1: not controll 167.168.FrameRate =-1 ;Target frame rate. -1: not controll169.170.171.[vpss_group]172.Vpss_DrEn =FALSE173.174.Vpss_DbEn =FALSE175.176.Vpss_IeEn =TRUE177.178.Vpss_NrEn =TRUE179.180.Vpss_HistEn =TRUE181.182.Vpss_DieMode=0 ;Define de-interlace mode183.184. ;VPSS_DIE_MODE_AUTO = 0,185.186. ;VPSS_DIE_MODE_NODIE = 1,187.188. ;VPSS_DIE_MODE_DIE = 2,189.190.[vpss_chn]191.Vpss_W =1280192.Vpss_H =720193.194.[isp_image]195.196.Isp_W =1280197.198.Isp_H =720199.200.I sp_FrameRate=30201.202.Isp_Bayer =3 ;BAYER_RGGB=0, BAYER_GRBG=1, BAYER_GBRG=2, BAYER_ BGGR=3203.205.[isp_timing]206.207.Isp_WndMode=0 ;WIND_NONE= 0,WIND_HOR= 1,WIND_VER= 2,WIND_A LL= 3,208.209.I sp_HorWndStart=0210.211.Isp_HorWndLength=1280212.213.Isp_VerWndStart=0214.215.Isp_VerWndLength=720216.217.[vb_conf]218.219.VbCnt=8220.221.222.[venc]223.224.RcMode =VENC_RC_MODE_H264CBR226.Gop =30227.228.StatTime =1229.230.ViFrmRate =30231.232.TargetFrmRate=25233.;----- only for VENC_RC_MODE_H264CBR ----------234.BitRate=4096235.FluctuateLevel=1236.;----- only for VENC_RC_MODE_H264VBR ----------237.MaxBitRate =10000238.239.MaxQp=32240.241.MinQp=24242.;----- only for VENC_RC_MODE_H264FIXQP ----------243.IQp=20244.245.PQp=23 246.247.[bind]248.249.V iDev =0 250.251.ViChn =0 252.253.VpssGrp =0 254.255.VpssChn = 0 256.257.VencGrp =0 258.259.VencChn =0 260.261.VoDev =0 262.263.VoChn =0 264.265.V iSnapChn =0266.267.VpssSnapGrp=0 268.269.V pssSnapChn=1 270.271.VencSnapGrp=1 272.273.VencSnapChn=1。

Hi3518EV20X/Hi3516CV200 SDK 安装以及升级使用说明

5、编译osdrv

参见osdrv目录下readme

6、SDK目录介绍

Hi3518E_SDK_Vx.x.x.x 目录结构如下:

|-- sdk.cleanup # SDK清理脚本

| |-- rootfs_*.tgz # rootfs压缩包

| `-- image_* # 可供FLASH烧写的映像文件,如内核、根文件系统

|-- scripts # 存放shell脚本的目录

在"Hi3518EV200R001***/01.software/board"目录下,您可以看到一个 Hi3518E_SDK_Vx.x.x.x.tgz 的文件,该文件就是Hi3518EV20X/Hi3516CV200 的软件开发包。

2、解压缩SDK包

在linux服务器上(或者一台装有linux的PC上,主流的linux发行版本均可以),使用命令:tar -zxf Hi3518E_SDK_Vx.x.x.x.tgz,解压缩该文件,可以得到一个Hi3518E_SDK_Vx.x.x.x目录。

4、在linux服务器上安装交叉编译器

1)安装uclibc交叉编译器(注意,需要有sudo权限或者root权限):

进入Hi3518E_SDK_Vx.x.x.x/osdrv/opensource/toolchain/arm-hisiv300-linux目录,运行chmod +x cross.install,然后运行./cross.install即可。

# Demo单板默认为从SPI Flash启动。

Hi3518_ISP_3A版本使用指南

邮编:518129

文档版本 02 (2013-09-25)

海思专有和保密信息 版权所有 © 深圳市海思半导体有限公司

ii

Hi3518_ISP_3A 版本 使用指南

前言

前言

概述

本文档描述 Hi3518_ISP_3A 的功能、如何使用与开发。3A 功能包括 AE、AWB、AF。

产品版本

与本文档相对应的产品版本如下。

2 使用者指南......................................................................................................................................6

2.1 软件流程......................................................................................................................................................... 6 2.2 Sensor 对接.................................................................................................................................................... 10

Hi3516A/Hi3516D与Hi3518 ISP MPI差异

2 系统控制

差异项 MPI

数据结构

Hi3518 HI_MPI_ISP_SetImageAttr HI_MPI_ISP_SetInputTiming HI_MPI_ISP_GetImageAttr HI_MPI_ISP_GetInputTiming HI_MPI_ISP_FreezeFmw HI_MPI_ISP_SetWdrAttr HI_MPI_ISP_SetWdrAttr ISP_IMAGE_ATTR_S ISP_INPUT_TIMING_S ISP_WDR_ATTR_S ISP_SENSOR_REGISTER_S

i

Hi3516A/Hi3516D 与 Hi3518 ISP MPI 差异

前言

符号

说明 表示有中度或低度潜在危险,如果不能避免,可能导致人 员轻微或中等伤害。

表示有潜在风险,如果忽视这些文本,可能导致设备损 坏、数据丢失、设备性能降低或不可预知的结果。

表示能帮助您解决某个问题或节省您的时间。 表示是正文的附加信息,是对正文的强调和补充。

b. 相较 Hi3518,Hi3516A 中使用 HI_MPI_ISP_SetPubAttr 来设置接口相关的参数, 删除了冗余参数 enWndMode,并合并了图像属性和裁剪窗口的图像宽高配置。

文档版本 01 (2014-12-20)

海思专有和保密信息 版权所有 © 深圳市海思半导体有限公司

2

Hi3516A/Hi3516D 与 Hi3518 ISP MPI 差异

b. 相比 Hi3518,Hi3516A 支持的 ISO 最大值增加了,因此对于随 ISO 联动的参数, 其数组大小由 8 扩展为 16。

c. 对支持手动模式和自动模式的功能模块,Hi3516A 重新组织了数据结构:使用操 作类型(ISP_OP_TYPE_E)选择手动或自动模式;手动属性和自动属性分别使用 单独的变量。对于设置接口,当操作类型处于手动模式下,只能设置手动属性; 当操作类型处于自动模式下,只能设置自动属性。对于获取接口,获取操作总是 可以同时获取手动属性值和自动属性值。

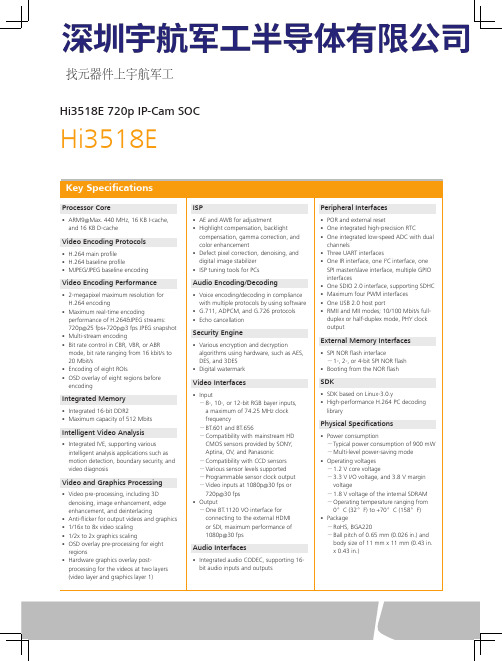

海思微控制器Hi3518ERBCV100

Audio Encoding/Decoding

DDRC GPIO DRAM 512Mb

Hi3518E

RTC ADC

SFC Uart 0 Uart 1 GPIO

clock MAC SDIO

USB 2.0 Host Audio Codec

GPIO GPIO GPIO

OSC

Crystal Temperature

RS232 RS485

Photo Nor resistance Flash

● Output - One BT.1120 VO interface for connecting to the external HDMI or SDI, maximum performance of 1080p@30 fps

Audio Interfaces

● Integrated audio CODEC, supporting 16bit audio inputs and outputs

● Multi-stream encoding ● Bit rate control in CBR, VBR, or ABR

mode, bit rate ranging from 16 kbit/s to 20 Mbit/s ● Encoding of eight ROIs ● OSD overlay of eight regions before encoding

海思处理器Hi3518 SDK架构分析和系统移植

了利于后续 芯片驱动 的开 发 ,在该 版本 中可以加 入我们 自己的

驱 动 库 替 代 原 先 的外 部 驱 动 ,把基 本 的 GP I O、 S P I 、 1 2 C 驱 动 移 植 进来 , 提 供 统 一 的接 口供 用 户 空 间调 用 。 原 先 媒 体 相 关 的 驱 动 保 持不 变 , 这些驱动模块和我们的驱动库相对独立 , 通 过 媒 体 控

Hi 3 5 1 8是 针 对 行 业 类 ( Hi 3 5 1 8 A) 或 消费 类 ( H i 3 5 1 8 C) I P — Ca me r a产 品 应 用 开 发 的 一 款 专 业 中 低 端 S OC 芯 片 , 其 7 2 0 p @3 0 f p s H2 6 4多码 流 编码 性 能 、 优异的 I S P和 编 码 视 频 质

关键词 : H i 3 5 1 8 , S D K , 架 构 分析 , 系统 移 植

Ab s t t a c t

Hi 3 51 6. a s a r epr es e n t a t i v e o f t h e m on i t o r i ng i n t h e f i e l d of Hi 351 8 c h i p i n m an y f a c t o r i es h a s be e n f u l l y us ed. Medi a

制 来 统 一调 度 ;

3 ) 媒 体 控 制 通过 mp p提 供 的 i n c l u d e和 1 . b库 提供 的 a p i 接 口函数 来 搭 建 媒 体 框 架 和 数 据 通 道 。

2 代码 移 植

在 H i s i l i c o n官 网可 以 下 载 到 最 新 的 H i 3 5 1 8 S DK,解 压 后

HiISP 开发参考

第 3 章 AE 3.5.1AE 的数据类型中 ISP_AE_MODE_E、ISP_AE_ATTR_S 的【注意】有更新。 第 6 章 IMP 6.9 去雾功能描述有更新,数据类型 ISP_ANTIFOG_S 增加说明及成员。

文档版本 00B07(2013-02-28)

表示有潜在风险,如果忽视这些文本,可能导致设备损 坏、数据丢失、设备性能降低或不可预知的结果。

表示能帮助您解决某个问题或节省您的时间。 表示是正文的附加信息,是对正文的强调和补充。

修订记录

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新 内容。

文档版本 03 (2014-02-26)

文档版本 02(2013-09-25)

第 3 章 AE ISP_AE_ATTR_EX_S 的【参数】u32SystemGainMax 的描述更新。 ISP_EXP_STA_INFO_S 新增【参数】u8ExpHistTarget[5]及描述;新增【注意事项】。 ISP_INNER_STATE_INFO_S 的【注意事项】中删除关于高精度 Sensor 模拟增益、数字 增益和高精度 ISP 数字增益的相关描述。 第 4 章 AWB ISP_WB_STA_INFO_S 新增【参数】u32Rgain、u32Ggain、u32Bgain 及描述。 第 8 章 AF ISP_FOCUS_STA_INFO_S 新增【参数】u8MetricsShift、u8NpOffset 及描述。 第 10 章 Proc 调试信息 新增。

6.2.2 API 参考,HI_MPI_ISP_GetGammaTable 的【注意】中的描述修改为“无”。

6.3.3 数据类型,ISP_DRC_ATTR_S 的【定义】和【成员】中新增 u32VarianceSpace 和 u32VarianceIntensity;并修改部分成员的描述。

Hi3518E 硬件设计 用户指南

1.1 小系统设计建议............................................................................................................................................. 1 1.1.1 Clocking 电路......................................................................................................................................... 1 1.1.2 复位和 Watchdog 电路.......................................................................................................................... 1 1.1.3 JTAG Debug 接口 .................................................................................................................................. 3 1.1.4 Hi3518E 硬件初始化系统配置电路 ..................................................................................................... 4 1.1.5 DDR 电路设计 ....................................................................................................................................... 5 1.1.6 Flash 原理图设计................................................................................................................................... 5

基于海思方案的ip解决方案

基于海思方案的ip解决方案一、引言海思方案是指海思半导体公司开发的一系列芯片和解决方案,主要用于视频监控、智能家居、智能交通等领域。

本文将介绍基于海思方案的IP解决方案,包括方案概述、技术要求、实施步骤和预期效果。

二、方案概述基于海思方案的IP解决方案旨在提供一种高效、稳定、安全的网络传输方案,以满足用户对视频监控、智能家居等应用场景的需求。

该方案通过利用海思芯片的强大处理能力和先进的网络通信技术,实现高清视频传输、远程监控、智能识别等功能。

三、技术要求1. 硬件要求:- 海思芯片:使用海思公司提供的最新一代芯片,具备高性能、低功耗、稳定可靠的特点。

- 摄像头:选择适合应用场景的高清摄像头,支持海思芯片的接口标准。

- 存储设备:提供足够的存储空间,支持视频数据的高速读写。

- 网络设备:使用高速、稳定的网络设备,确保视频数据的快速传输和实时性。

2. 软件要求:- 操作系统:基于海思芯片的开发板上安装适合的操作系统,如Linux等。

- 驱动程序:根据摄像头和其他外设的硬件接口要求,编写相应的驱动程序。

- 视频编解码:使用海思提供的编解码库,实现对高清视频的编码和解码。

- 网络传输:采用网络传输协议,如TCP/IP、RTSP等,实现视频数据的传输和接收。

- 远程访问:通过云服务器或者其他远程访问方式,实现对视频监控系统的远程访问和控制。

- 智能识别:利用海思芯片的图像处理能力,实现人脸识别、车牌识别等智能功能。

四、实施步骤1. 硬件搭建:- 根据实际需求,选购适合的海思芯片开发板、摄像头、存储设备和网络设备。

- 将摄像头和其他外设连接到开发板上,并确保硬件连接正常。

2. 软件开发:- 安装适合的操作系统到海思芯片开发板上,并进行相应的配置。

- 编写驱动程序,实现对摄像头和其他外设的控制和数据传输。

- 利用海思提供的编解码库,实现对高清视频的编码和解码。

- 使用网络传输协议,实现视频数据的传输和接收。

- 开发远程访问功能,实现对视频监控系统的远程访问和控制。

HI3515

外部设备和外围接口

时钟,复位电路:芯片基本电路 DDR控制器:控制外部内存 Flash芯片:存储芯片,测试时候用NOR falsh JTAG测试接口:JTAG是一种国际标准测试协议,这里用于Hi3515的测试 A/D芯片:数模转换

开发

视频编码模块——图像采集

采集模块流程图如右所示:

这一过程就是为之后要实现的视频编码通道组的 搭建, VI 绑定,视频编码的创建和注册做准备。这个 模块启用设置好的 VI 设备和通道打开,以便接收图像 。主要功能可认为是把图像进入的“大门”装好,接 收到原始的帧图像现在门口放好。

在接收到图像之后,可以直接输出到显示设备, 也可以继续在模块中传输,处理。即:将原始的帧图 像按需求放走或者放进门。

开发

模块化结构

这一过程就是编程,整体的,大致的思想和Windows下的软件开发一样。 此论文中的工程的模块结构如下:

内存需求大! 缓冲池+销毁释放

开发

就是通过特定的压缩技术,将某 个视频格式的文件转换成另一种 视频格式文件的方式

视频编码模块——主要实现功能的模块

视频编码模块是工程中的主题模 块,包括图像采集,编码,解码 三个,通过将VI绑定到通道来传 输图像(码流)。 整个视频编码模块完成图像---处 理图像的转换,接收摄像头拍摄 到的视频图像,处理后交由视频 输出模块负责显示成监控视频。 这一模块中完整的功能复杂,主 要包含两个:视频编码VENC和 通道组管理GROUP

海思3518e方案

海思3518e方案是一种广泛应用于视频监控、智能家居、车载电子等领域的芯片方案。

作为一款高性能、低功耗的方案,它在市场上享有很高的声誉。

本文将从的概述、技术特点、应用领域和未来发展趋势等方面进行探讨。

一、概述是海思半导体(Hisilicon)公司基于ARM架构开发的一款芯片方案。

该方案采用了先进的工艺技术,拥有较高的处理能力和较低的功耗。

同时,它还具备一系列丰富的外设接口和高性能的图像处理能力,适用于多种嵌入式应用领域。

二、技术特点1. 高性能处理能力采用了四核ARM Cortex-A7处理器,主频可达到1.2GHz。

此外,它还集成了一颗强大的图像处理单元(ISP),支持高清视频编解码和图像处理功能。

这些技术的综合应用,使得在处理多路高清视频和图像数据时表现出色。

2. 丰富的外设接口提供了丰富的外设接口,包括以太网口、USB接口、串口等。

这些接口的存在使得开发者可以方便地与其他外部设备进行通信,从而实现更为复杂的功能要求。

3. 低功耗设计在功耗控制方面拥有出色的性能。

采用先进的节能技术,该方案能够有效降低功耗,并延长应用设备的续航时间,提高整体系统的可靠性。

三、应用领域1. 视频监控在视频监控领域得到广泛应用。

其高性能处理器和图像处理单元能够实时处理多路高清视频和图像数据,为安防行业提供了可靠的解决方案。

同时,丰富的外设接口也方便了与其他设备的连接与通信。

2. 智能家居随着智能家居的兴起,在该领域也有着广泛应用。

它可以实现家庭安防、智能设备管理等功能,为用户带来更加智能化的家居体验。

同时,低功耗设计也符合智能家居设备长时间运行的要求。

3. 车载电子还适用于车载电子领域。

它能够处理多路车内外监控视频和图像数据,保障车内安全。

此外,该方案还支持车载多媒体系统、车载导航等功能的实现。

四、未来发展趋势随着物联网、人工智能等技术的快速发展,在未来有望得到更广泛的应用。

例如,在智能安防领域,可结合人脸识别、行为分析等技术,实现更加智能化的监控系统。

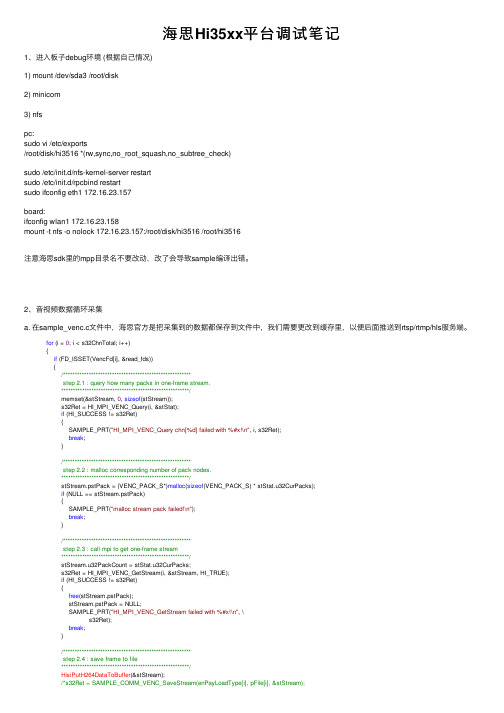

海思Hi35xx平台调试笔记

海思Hi35xx平台调试笔记1、进⼊板⼦debug环境 (根据⾃⼰情况)1) mount /dev/sda3 /root/disk2) minicom3) nfspc:sudo vi /etc/exports/root/disk/hi3516 *(rw,sync,no_root_squash,no_subtree_check)sudo /etc/init.d/nfs-kernel-server restartsudo /etc/init.d/rpcbind restartsudo ifconfig eth1 172.16.23.157board:ifconfig wlan1 172.16.23.158mount -t nfs -o nolock 172.16.23.157:/root/disk/hi3516 /root/hi3516注意海思sdk⾥的mpp⽬录名不要改动,改了会导致sample编译出错。

2、⾳视频数据循环采集a. 在sample_venc.c⽂件中,海思官⽅是把采集到的数据都保存到⽂件中,我们需要更改到缓存⾥,以便后⾯推送到rtsp/rtmp/hls服务端。

for (i = 0; i < s32ChnTotal; i++){if (FD_ISSET(VencFd[i], &read_fds)){/*******************************************************step 2.1 : query how many packs in one-frame stream.*******************************************************/memset(&stStream, 0, sizeof(stStream));s32Ret = HI_MPI_VENC_Query(i, &stStat);if (HI_SUCCESS != s32Ret){SAMPLE_PRT("HI_MPI_VENC_Query chn[%d] failed with %#x!\n", i, s32Ret);break;}/*******************************************************step 2.2 : malloc corresponding number of pack nodes.*******************************************************/stStream.pstPack = (VENC_PACK_S*)malloc(sizeof(VENC_PACK_S) * stStat.u32CurPacks);if (NULL == stStream.pstPack){SAMPLE_PRT("malloc stream pack failed!\n");break;}/*******************************************************step 2.3 : call mpi to get one-frame stream*******************************************************/stStream.u32PackCount = stStat.u32CurPacks;s32Ret = HI_MPI_VENC_GetStream(i, &stStream, HI_TRUE);if (HI_SUCCESS != s32Ret){free(stStream.pstPack);stStream.pstPack = NULL;SAMPLE_PRT("HI_MPI_VENC_GetStream failed with %#x!\n", \s32Ret);break;}/*******************************************************step 2.4 : save frame to file*******************************************************/HisiPutH264DataToBuffer(&stStream);/*s32Ret = SAMPLE_COMM_VENC_SaveStream(enPayLoadType[i], pFile[i], &stStream);if (HI_SUCCESS != s32Ret){free(stStream.pstPack);stStream.pstPack = NULL;SAMPLE_PRT("save stream failed!\n");break;}*//*******************************************************step 2.5 : release stream*******************************************************/s32Ret = HI_MPI_VENC_ReleaseStream(i, &stStream);if (HI_SUCCESS != s32Ret){free(stStream.pstPack);stStream.pstPack = NULL;break;}/*******************************************************step 2.6 : free pack nodes*******************************************************/free(stStream.pstPack);stStream.pstPack = NULL;}}b. HI_S32 HisiPutH264DataToBuffer(VENC_STREAM_S *pstStream)函数⽐较重要HI_S32 HisiPutH264DataToBuffer(VENC_STREAM_S *pstStream){HI_S32 i,j,x;HI_S32 len=0,off=0,len2=2,uplen=0;unsigned char *pstr;int iframe=0;for (i = 0; i < pstStream->u32PackCount; i++){len+=pstStream->pstPack[i].u32Len;}if(n<NMAX){for (i = 0; i < pstStream->u32PackCount; i++){memcpy(ringfifo[iput].buffer+off,pstStream->pstPack[i].pu8Addr,pstStream->pstPack[i].u32Len); off+=pstStream->pstPack[i].u32Len;pstr=pstStream->pstPack[i].pu8Addr;if(pstr[4]==0x67){UpdateSps(pstr+4,pstStream->pstPack[i].u32Len-4);iframe=1;}if(pstr[4]==0x68){UpdatePps(pstr+4,pstStream->pstPack[i].u32Len-4);}}ringfifo[iput].size= len;if(iframe){// printf("I");ringfifo[iput].frame_type = FRAME_TYPE_I;}else{ringfifo[iput].frame_type = FRAME_TYPE_P;// printf("P");}iput = addring(iput);// printf("(%d)",iput);// fflush(stdout);n++;}return HI_SUCCESS;}c. VENC_STREAM_S相关结构体//定义帧码流类型结构体:typedef structhiVENC_STREAM_S{VENC_PACK_S *pstPack; //帧码流包结构。

Hi3518A/Hi3518C/Hi3516C外围设备驱动 操作指南

产品版本

与本文档相对应的产品版本如下。

产品名称 Hi3518A 芯片 Hi3518C 芯片 Hi3516C 芯片

产品版本 V100 V100 V100

读者对象

本文档(本指南)主要适用于以下工程师: z 技术支持工程师 z 软件开发工程师

修订记录

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新 内容。

4.2 用 mkdosfs 工具格式化 ............................................................................................................................... 15 4.3 挂载目录....................................................................................................................................................... 15 4.4 读写文件....................................................................................................................................................... 15

海思MPP视频处理平台流程简介

海思MPP视频处理平台流程简介海思MPP视频处理平台流程简介hisi芯⽚系统概述⾸先先来了解⼀下海思芯⽚SOC,下图是hi3519A芯⽚设计图 图1 hi3519AV100 芯⽚设计图芯⽚的设计图有助于我们对海思的图像处理有⼀个⼤致的了解,从上图中我们可以看到,芯⽚SOC⾥集成了众多控制芯⽚,⽐如负责深度学习的NNIE硬核,负责图像处理的IVE硬核,视频编解码单元H265/H264Codec,以及图像处理单元ISP等。

为了减少⽤户对于硬件的直接操作,海思为⽤户封装了许多对于硬件的操作接⼝,能够控制芯⽚完成相应的媒体处理功能,对上屏蔽了硬件的处理细节,⽤户能够将精⼒集中在业务功能上,达到快速开发的⽬的。

这些相关硬件接⼝就构成了下图中的媒体软件处理平台层。

我们进⾏视频图像的处理主要是要调⽤该层提供的相关接⼝来完成相应的功能,也必须要按照它提供的操作流程来执⾏相关功能的完成,所以需要熟悉它提供的相关接⼝的使⽤⽅法和使⽤限制,开发⼿册中提供了系统的处理流程以及具体的API描述,仔细阅读该⽂档能帮助我们更好地完成开发⼯作。

图2 海思35xx 系统层次图海思媒体软件处理平台概述海思媒体处理平台的主要内部处理流程如图3所⽰,主要分为 VI-视频输⼊,VPSS-视频处理,VENC-视频编码,VDEC-视频解码,VO-视频输出,AVS-视频拼接等模块 图 3 mpp 内部处理流程图从上图可以看出,可以根据⽤户需求完成多种⽅案实现,⽐如视频输出,视频监控等⽅案。

有的功能单个模块就能完成,⽽更多的功能则需要依赖模块之间“联动”完成。

各个模块之间的关系,⽐如,第⼀条pipeline是:sensor -> VI -> VPSS -> VENC -> 压缩码流或者 sensor -> VI -> VPSS -> VO -> 显⽰屏,这应该是单⽬相机上常⽤的pipeline。

海思方案 HI3518E平台ISP调试环境搭建

3518E平台的搭建海思的SDK提供了ISP调试的相关工具,降低了IPC开发ISP调试的难度。

初次搭建ISP调试环境,记录一下。

SDK版本:Hi3518_MPP_V1.0.A.0硬件平台:HI3518E_OV9732工具包:PQ_TOOL (Hi3518E_V100R001C01SPC0A0\01.software\pc\PQ_TOOL)文件说明:Hi3518_ITTB_MPP2_V1.0.A.0_B030.tgz 设备端工具; PQTools_V3.7.5.zip PC端工具环境搭建步骤:(1)将Hi3518_ITTB_MPP2_V1.0.A.0_B030.tgz拷贝至nfs共享目录名,解压后运行HiIspTool.sh脚本倘若用海思自带的工具出图像并调节ISP运行:#./HiIspTool.sh -a -p ov9732_720p_line.inips一下可以看到两个进程696 adminlvj 58488 S ./ittb_stream -p ov9732_720p_line.ini699 adminlvj 19676 S ./ittb_control倘若运行自己的工程出图像了,这时只需要运行一下命令即可。

#./HiIspTool.sh -aps一下可以看到一个进程699 adminlvj 19676 S ./ittb_control(2)PC端直接解压PQTools_V3.7.5.zip,运行HiPQTools.exe,输入选择sdk版本Hi3518_MPP_V1.0.A.0 ,输入设备IP,就可以连接上摄像头倘若运行了ittb_stream,可以PC端软件上打开视频图像窗口连接成功,至此,最简单的ISP调试环境搭建就完成了。

复杂的就是后面的ISP调节过程了。

备注:运行脚本的时候可能会报错,查看相关打印信息,将错误消除。

当前产品我们用的是HI3518E+OV9732,SDK中并没有提供相关的sensor库和相关的config文件,所以运行报错了!解决:将OV9732sensor库拷贝至Hi3518_ITTB_MPP2_V1.0.A.0/libs/下,将ov9732_720p_line.ini拷贝至Hi3518_ITTB_MPP2_V1.0.A.0/configs/下附录:ov9732_720p_line.ini[plain]view plaincopyprint?1.[sensor]2.Sensor_type =ov9732 ;the type of sensor3.Mode =0 ;LINE mode,mode = 0 ,WDR mode,mode =14.DllFile =libs/libsns_ov9732.so ;LineDllFile path5.6.[vi_dev]7.Input_mod =2 ;VI_INPUT_MODE_BT656 = 08. ;VI_INPUT_MODE_BT601,9. ;VI_INPUT_MODE_DIGITAL_CAMERA10.11.Work_mod =0 ;VI_WORK_MODE_1Multiplex = 012.13. ;VI_WORK_MODE_2Multiplex,14.15. ;VI_WORK_MODE_4Multiplex16.bine_mode =0 ;Y/C composite or separation mode18.19. ;VI_COMBINE_COMPOSITE = 0 /*Composite mode */20.21. ;VI_COMBINE_SEPARATE, /*Separate mode */22.p_mode =0 ;Component mode (single-component or dual-component)24.25. ;VI_COMP_MODE_SINGLE = 0, /*single component mode */26.27. ;VI_COMP_MODE_DOUBLE = 1, /*double component mode */28.29.Clock_edge =1 ;Clock edge mode (sampling on the rising or falling edge)30.31. ;VI_CLK_EDGE_SINGLE_UP=0, /*rising edge */32.33. ;VI_CLK_EDGE_SINGLE_DOWN, /*falling edge */34.35.Mask_num =2 ;Component mask36.37.Mask_0 =0xFFC0000038.39.Mask_1 =0x040.41.Scan_mode = 1;VI_SCAN_INTERLACED = 042.43. ;VI_SCAN_PROGRESSIVE,44.45.Data_seq =2 ;data sequence (ONLY for YUV format)46.47. ;----2th component U/V sequence in bt112048.49. ; VI_INPUT_DATA_VUVU = 0,50.51. ; VI_INPUT_DATA_UVUV,52.53. ;----input sequence for yuv54.55. ; VI_INPUT_DATA_UYVY = 0,56.57. ; VI_INPUT_DATA_VYUY,58.59. ; VI_INPUT_DATA_YUYV,60.61. ; VI_INPUT_DATA_YVYU62.63.64.65.Vsync =1 ; vertical synchronization signal66.67. ;VI_VSYNC_FIELD = 0,68.69. ;VI_VSYNC_PULSE,70.71.VsyncNeg=0 ;Polarity of the vertical synchronization signal72.73. ;VI_VSYNC_NEG_HIGH = 0,74.75. ;VI_VSYNC_NEG_LOW /*if VIU_VSYNC_E76.77.Hsync =0 ;Attribute of the horizontal synchronization signal78.79. ;VI_HSYNC_VALID_SINGNAL = 0,80.81. ;VI_HSYNC_PULSE,82.83.HsyncNeg =0 ;Polarity of the horizontal synchronization signal84.85. ;VI_HSYNC_NEG_HIGH = 0,86.87. ;VI_HSYNC_NEG_LOW88.89.VsyncValid =0 ;Attribute of the valid vertical synchronization signal90.91. ;VI_VSYNC_NORM_PULSE = 0,92.93. ;VI_VSYNC_VALID_SINGAL,94.95.VsyncValidNeg =0;Polarity of the valid vertical synchronization signal96.97. ;VI_VSYNC_VALID_NEG_HIGH = 0,98.99. ;VI_VSYNC_VALID_NEG_LOW100.101.Timingblank_HsyncHfb =0 ;Horizontal front blanking width102.103.Timingblank_HsyncAct =1280 ;Horizontal effetive width104.105.Timingblank_HsyncHbb =0 ;Horizontal back blanking width106.107.Timingblank_VsyncVfb =0 ;Vertical front blanking height108.109.Timingblank_VsyncVact =720 ;Vertical effetive width110.111.Timingblank_VsyncVbb=0 ;Vertical back blanking height112.113.Timingblank_VsyncVbfb =0 ;Even-field vertical front blanking height(interlace, invalid progressive) 114.115.Timingblank_VsyncVbact=0 ;Even-field vertical effetive width(interlace, invalid progressive) 116.117.Timingblank_VsyncVbbb =0 ;Even-field vertical back blanking height(interlace, invalid progressive) 118.119.120.121.;----- only for bt656 ----------122.FixCode =0 ;BT656_FIXCODE_1 = 0,123.124. ;BT656_FIXCODE_0125.126.FieldPolar=0 ;BT656_FIELD_POLAR_STD = 0127.128. ;BT656_FIELD_POLAR_NSTD129.130.DataPath =1 ;ISP enable or bypass131.132. ;VI_PATH_BYPASS = 0,/* ISP bypass */133.134. ;VI_PATH_ISP = 1,/* ISP enable */135.136. ;VI_PATH_RAW = 2,/* Capture raw data, for debug */137.138.InputDataType=1 ;VI_DATA_TYPE_YUV = 0,VI_DATA_TYPE_RGB = 1,139.140.DataRev =FALSE ;Data reverse. FALSE = 0; TRUE = 1141.142.143.[vi_chn]144.145.CapRect_X =0146.147.CapRect_Y =0148.149.CapRect_Width=1280150.151.CapRect_Height=720152.153.DestSize_Width=1280154.155.DestSize_Height=720156.157.CapSel =2 ;Frame/field select. ONLY used in interlaced mode158. ;VI_CAPSEL_TOP = 0, /* top field */159. ;VI_CAPSEL_BOTTOM, /* bottom field */160. ;VI_CAPSEL_BOTH, /* top and bottom field */ 161.162.PixFormat =19 ;163.164.165.166.SrcFrameRate=-1 ;Source frame rate. -1: not controll167.168.FrameRate =-1 ;Target frame rate. -1: not controll169.170.171.[vpss_group]172.Vpss_DrEn =FALSE173.174.Vpss_DbEn =FALSE175.176.Vpss_IeEn =TRUE177.178.Vpss_NrEn =TRUE179.180.Vpss_HistEn =TRUE181.182.Vpss_DieMode=0 ;Define de-interlace mode183.184. ;VPSS_DIE_MODE_AUTO = 0,185.186. ;VPSS_DIE_MODE_NODIE = 1,187.188. ;VPSS_DIE_MODE_DIE = 2,189.190.[vpss_chn]191.Vpss_W =1280192.Vpss_H =720193.194.[isp_image]195.196.Isp_W =1280198.Isp_H =720199.200.Isp_FrameRate=30201.202.Isp_Bayer =3 ;BAYER_RGGB=0, BAYER_GRBG=1, BAYER_GBRG=2, BAYER_BGGR=3 203.204.205.[isp_timing]206.207.Isp_WndMode=0 ;WIND_NONE= 0,WIND_HOR= 1,WIND_VER= 2,WIND_ALL= 3, 208.209.Isp_HorWndStart=0210.211.Isp_HorWndLength=1280212.213.Isp_VerWndStart=0214.215.Isp_VerWndLength=720216.217.[vb_conf]218.219.VbCnt=8220.221.222.[venc]223.224.RcMode =VENC_RC_MODE_H264CBR225.226.Gop =30227.228.StatTime =1229.230.ViFrmRate =30231.232.TargetFrmRate=25233.;----- only for VENC_RC_MODE_H264CBR ----------234.BitRate=4096235.FluctuateLevel=1236.;----- only for VENC_RC_MODE_H264VBR ----------237.MaxBitRate =10000238.239.MaxQp=32240.241.MinQp=24242.;----- only for VENC_RC_MODE_H264FIXQP ----------243.IQp=20244.245.PQp=23247.[bind] 248.249.ViDev =0 250.251.ViChn =0 252.253.VpssGrp =0 254.255.VpssChn = 0 256.257.VencGrp =0 258.259.VencChn =0 260.261.VoDev =0 262.263.VoChn =0 264.265.ViSnapChn =0 266.267.VpssSnapGrp=0 268.269.VpssSnapChn=1 270.271.VencSnapGrp=1 272.273.VencSnapChn=1。

Hi3518E 硬件设计 用户指南

注意

您购买的产品、服务或特性等应受海思公司商业合同和条款的约束,本文档中描述的全部或部分产 品、服务或特性可能不在您的购买或使用范围之内。除非合同另有约定,海思公司对本文档内容不 做任何明示或默示的声明或保证。

由于产品版本升级或其他原因,本文档内容会不定期进行更新。除非另有约定,本文档仅作为使用 指导,本文档中的所有陈述、信息和建议不构成任何明示或暗示的担保。

2 PCB 设计建议................................................................................................................................14

2.1 小系统 PCB 设计建议 ................................................................................................................................. 14 2.1.1 小系统电源 ......................................................................................................................................... 14 2.1.2 时钟和复位电路.................................................................................................................................. 16 2.1.3 Flash 设计............................................................................................................................................. 16 2.1.4 网口信号设计...................................................................................................................................... 16

海思HI35XX之视频处理单元各通道间的关系

海思HI35XX之视频处理单元各通道间的关系最近在折腾HI3518C的芯片,应用到IPCamera上,最终获取多路不同分辨率的视频流供不同需求的预览切换。

此处简单记录一下视频前处理元VPSS(Video Process Sub-System)的多通道间的关系以及使用心得。

HI3518C的视频子系统包括:视频系统初始化模块(MPP_SYS_CONF_S)、视频输入模块(VI)、视频前处理模块(VPSS)、视频编码模块(VENC)和视频输出模块(VO)组成。

HI3518C的VPSS是视频数据编码前的预处理单元,主要完成对一幅输入图像的统一预处理,如去噪、去隔行等,然后再对各通道分别进行缩放、锐化等处理(如:PreScale、De-ring/De-block、NR、IE、DIE、Sharpen 等,具体可参见VPSS_GRP_ATTR_S结构体),最后输出多种不同分辨率的图像。

其中,HI3518C对用提供GROUP的概念来管理VPSS,最多支持128个GROUP(我目前只使用了一个组:GROUP0)。

VPSS的GROUP又包含多个通道(CHANNEL),对于不同规格的芯片,每个组包含的通道数也不相同,规格文档上都有详细说明。

HI3518C的各个GROUP包含8个CHANNEL,其中2个物理通道(PHY CHN)、一个直通通道(Bypass)和5个扩展通道(EXT CHN)。

物理通道是由硬件提供的,各物理通道的功能和限制各不相同;直通通道具备CROP功能,可以把不需要作预处理的一幅幅图像直接透传给接收者;扩展通道具备缩放功能,当它绑定到物理通道后,可以把从物理通道获取到的图像缩小或放大成用户所需要的不同分辨率的图像。

Hi3518C 提供 5 路扩展通道以提供更好的灵活性,扩展通道具备缩放和帧率控制功能,不经过其他硬件算法单元处理。

用户在使用的时候,需要首先创建VPSS GROUP,然后设置好GROUP属性并启用VPSS GROUP之后,再把VI作为源通道,把VPSS作为目标通道,通过调用 HI_MPI_SYS_Bind 绑定VI到VPSS,就可以建立视频输入到视频预处理间的通路,使得前端采集到的视频数据经由此通路到达VPSS单元。

海思HI3518EV200+AR0130开发板DIY——前篇

海思HI3518EV200+AR0130开发板DIY——前篇海思HI3518EV200+AR0130开发板DIY今天开始要围绕这个项目学习了(还是得从C开始学)缘起(这段主要水废话)相关开发资料→_→原理图设计原理图整体框架一、电源部分HI3518EV200+AR0130方案电源部分分别有5V/3V3/1V8/1V1。

输入电源USB端口供电5V输入,5V再通过DCDC降压转成3V3,1V8和1V1。

1V8和1V1需晚于3V3上电。

电源部分二、PHY网口部分PHY网口部分原方案是采用不带变压器的RJ45网口,后端外接变压器再街道PHY芯片RTL8201F。

看着自己手上有几个多余的HR911105A,自带变压器与LED,修改了一下电路应该是可以用的,但愿不会翻车。

网口部分三、Sensor部分开头也提了一点,上手资料的方案的sensor是GC2033,而且还是小小的BGA封装的,玻璃表面热风枪又不好吹。

为了让车稳一点还是改成教程里面的AR0130。

AR0130还有PLCC封装的,比较大而且相对好焊接一些。

sensor——AR0130PCB_LAYOUT设计PCB_LAYOUT设计就没有什么可以拿出来记录的了。

主要考虑到HI3518的封装是BGA192的,出现还是相对麻烦的。

线宽被控制在6mils才能从BGA里面把线拉出来。

同时还要考虑加工工艺以及制造成本(主要是穷),限制在了两层板。

于是三路电源3V3/1V8/1V1与GND相互纠缠了好久,经过不同的取舍(连通就差不多啦)终于硬硬的把板子lay完了。

TOP层布线bottom层布线完整图layoutTOP_3D图BOTTOM_3D图嘉X创打板DRC一轮感觉没啥问题,也懒得再检查了,一版调不通(佛祖保佑一次过)再第二版,嘉X创五块钱一版(哈哈,羊毛撸起来)。

直接导出Gerber,打包发嘉X创。

考虑到HI3518E的BGA封装,还真没有啥把握完美焊接,主要芯片还不便宜,一次焊接不成还得给BGA 值锡,干脆打包钢网一起。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3518E平台的搭建海思的SDK提供了ISP调试的相关工具,降低了IPC开发ISP调试的难度。

初次搭建ISP调试环境,记录一下。

SDK版本:Hi3518_MPP_V1.0.A.0硬件平台:HI3518E_OV9732工具包:PQ_TOOL (Hi3518E_V100R001C01SPC0A0\01.software\pc\PQ_TOOL)文件说明:Hi3518_ITTB_MPP2_V1.0.A.0_B030.tgz 设备端工具; PQTools_V3.7.5.zip PC端工具环境搭建步骤:(1)将Hi3518_ITTB_MPP2_V1.0.A.0_B030.tgz拷贝至nfs共享目录名,解压后运行HiIspTool.sh脚本倘若用海思自带的工具出图像并调节ISP运行:#./HiIspTool.sh -a -p ov9732_720p_line.inips一下可以看到两个进程696 adminlvj 58488 S ./ittb_stream -p ov9732_720p_line.ini699 adminlvj 19676 S ./ittb_control倘若运行自己的工程出图像了,这时只需要运行一下命令即可。

#./HiIspTool.sh -aps一下可以看到一个进程699 adminlvj 19676 S ./ittb_control(2)PC端直接解压PQTools_V3.7.5.zip,运行HiPQTools.exe,输入选择sdk版本Hi3518_MPP_V1.0.A.0 ,输入设备IP,就可以连接上摄像头倘若运行了ittb_stream,可以PC端软件上打开视频图像窗口连接成功,至此,最简单的ISP调试环境搭建就完成了。

复杂的就是后面的ISP调节过程了。

备注:解决:将OV9732sensor库拷贝至Hi3518_ITTB_MPP2_V1.0.A.0/libs/下,将ov9732_720p_line.ini拷贝至Hi3518_ITTB_MPP2_V1.0.A.0/configs/下附录:ov9732_720p_line.ini[plain]view plaincopyprint?1.[sensor]2.Sensor_type =ov9732 ;the type of sensor3.Mode =0 ;LINE mode,mode = 0 ,WDR mode,mode =14.DllFile =libs/libsns_ov9732.so ;LineDllFile path5.6.[vi_dev]7.Input_mod =2 ;VI_INPUT_MODE_BT656 = 08. ;VI_INPUT_MODE_BT601,9. ;VI_INPUT_MODE_DIGITAL_CAMERA10.11.Work_mod =0 ;VI_WORK_MODE_1Multiplex = 012.13. ;VI_WORK_MODE_2Multiplex,14.15. ;VI_WORK_MODE_4Multiplex16.bine_mode =0 ;Y/C composite or separation mode18.19. ;VI_COMBINE_COMPOSITE = 0 /*Composite mode */p_mode =0 ;Component mode (single-component or dual-component)24.25. ;VI_COMP_MODE_SINGLE = 0, /*single component mode */26.27. ;VI_COMP_MODE_DOUBLE = 1, /*double component mode */28.29.Clock_edge =1 ;Clock edge mode (sampling on the rising or falling edge)30.31. ;VI_CLK_EDGE_SINGLE_UP=0, /*rising edge */32.33. ;VI_CLK_EDGE_SINGLE_DOWN, /*falling edge */34.35.Mask_num =2 ;Component mask36.37.Mask_0 =0xFFC0000038.39.Mask_1 =0x040.41.Scan_mode = 1;VI_SCAN_INTERLACED = 042.43. ;VI_SCAN_PROGRESSIVE,44.45.Data_seq =2 ;data sequence (ONLY for YUV format)49. ; VI_INPUT_DATA_VUVU = 0,50.51. ; VI_INPUT_DATA_UVUV,52.53. ;----input sequence for yuv54.55. ; VI_INPUT_DATA_UYVY = 0,56.57. ; VI_INPUT_DATA_VYUY,58.59. ; VI_INPUT_DATA_YUYV,60.61. ; VI_INPUT_DATA_YVYU62.63.64.65.Vsync =1 ; vertical synchronization signal66.67. ;VI_VSYNC_FIELD = 0,68.69. ;VI_VSYNC_PULSE,70.71.VsyncNeg=0 ;Polarity of the vertical synchronization signal75. ;VI_VSYNC_NEG_LOW /*if VIU_VSYNC_E76.77.Hsync =0 ;Attribute of the horizontal synchronization signal78.79. ;VI_HSYNC_VALID_SINGNAL = 0,80.81. ;VI_HSYNC_PULSE,82.83.HsyncNeg =0 ;Polarity of the horizontal synchronization signal84.85. ;VI_HSYNC_NEG_HIGH = 0,86.87. ;VI_HSYNC_NEG_LOW88.89.VsyncValid =0 ;Attribute of the valid vertical synchronization signal90.91. ;VI_VSYNC_NORM_PULSE = 0,92.93. ;VI_VSYNC_VALID_SINGAL,94.95.VsyncValidNeg =0;Polarity of the valid vertical synchronization signal96.97. ;VI_VSYNC_VALID_NEG_HIGH = 0,101.Timingblank_HsyncHfb =0 ;Horizontal front blanking width102.103.Timingblank_HsyncAct =1280 ;Horizontal effetive width104.105.Timingblank_HsyncHbb =0 ;Horizontal back blanking width106.107.Timingblank_VsyncVfb =0 ;Vertical front blanking height108.109.Timingblank_VsyncVact =720 ;Vertical effetive width110.111.Timingblank_VsyncVbb=0 ;Vertical back blanking height112.113.Timingblank_VsyncVbfb =0 ;Even-field vertical front blanking height(interlace, invalid progressive) 114.115.Timingblank_VsyncVbact=0 ;Even-field vertical effetive width(interlace, invalid progressive) 116.117.Timingblank_VsyncVbbb =0 ;Even-field vertical back blanking height(interlace, invalid progressive) 118.119.120.121.;----- only for bt656 ----------122.FixCode =0 ;BT656_FIXCODE_1 = 0,123.126.FieldPolar=0 ;BT656_FIELD_POLAR_STD = 0127.128. ;BT656_FIELD_POLAR_NSTD129.130.DataPath =1 ;ISP enable or bypass131.132. ;VI_PATH_BYPASS = 0,/* ISP bypass */133.134. ;VI_PATH_ISP = 1,/* ISP enable */135.136. ;VI_PATH_RAW = 2,/* Capture raw data, for debug */ 137.138.InputDataType=1 ;VI_DATA_TYPE_YUV = 0,VI_DATA_TYPE_RGB = 1, 139.140.DataRev =FALSE ;Data reverse. FALSE = 0; TRUE = 1141.142.143.[vi_chn]144.145.CapRect_X =0146.147.CapRect_Y =0148.149.CapRect_Width=1280152.153.DestSize_Width=1280154.155.DestSize_Height=720156.157.CapSel =2 ;Frame/field select. ONLY used in interlaced mode 158. ;VI_CAPSEL_TOP = 0, /* top field */159. ;VI_CAPSEL_BOTTOM, /* bottom field */ 160. ;VI_CAPSEL_BOTH, /* top and bottom field */ 161.162.PixFormat =19 ;163.164.165.166.SrcFrameRate=-1 ;Source frame rate. -1: not controll167.168.FrameRate =-1 ;Target frame rate. -1: not controll169.170.171.[vpss_group]172.Vpss_DrEn =FALSE173.174.Vpss_DbEn =FALSE175.178.Vpss_NrEn =TRUE179.180.Vpss_HistEn =TRUE181.182.Vpss_DieMode=0 ;Define de-interlace mode 183.184. ;VPSS_DIE_MODE_AUTO = 0, 185.186. ;VPSS_DIE_MODE_NODIE = 1, 187.188. ;VPSS_DIE_MODE_DIE = 2, 189.190.[vpss_chn]191.Vpss_W =1280192.Vpss_H =720193.194.[isp_image]195.196.Isp_W =1280197.198.Isp_H =720199.200.Isp_FrameRate=30201.204.205.[isp_timing]206.207.Isp_WndMode=0 ;WIND_NONE= 0,WIND_HOR= 1,WIND_VER= 2,WIND_ALL= 3, 208.209.Isp_HorWndStart=0210.211.Isp_HorWndLength=1280212.213.Isp_VerWndStart=0214.215.Isp_VerWndLength=720216.217.[vb_conf]218.219.VbCnt=8220.221.222.[venc]223.224.RcMode =VENC_RC_MODE_H264CBR225.226.Gop =30227.230.ViFrmRate =30231.232.TargetFrmRate=25233.;----- only for VENC_RC_MODE_H264CBR ---------- 234.BitRate=4096235.FluctuateLevel=1236.;----- only for VENC_RC_MODE_H264VBR ---------- 237.MaxBitRate =10000238.239.MaxQp=32240.241.MinQp=24242.;----- only for VENC_RC_MODE_H264FIXQP ---------- 243.IQp=20244.245.PQp=23246.247.[bind]248.249.ViDev =0250.251.ViChn =0252.253.VpssGrp =0254.255.VpssChn = 0256.257.VencGrp =0 258.259.VencChn =0 260.261.VoDev =0 262.263.VoChn =0 264.265.ViSnapChn =0 266.267.VpssSnapGrp=0 268.269.VpssSnapChn=1 270.271.VencSnapGrp=1 272.273.VencSnapChn=1。