EDA实验讲义

eda讲义——7个的

实验一 maxplusII 软件的初步使用(图形的设计)一、实验目的:1、初步掌握Max+PlusII 软件的基本操作与应用。

2、初步了解可编程器件的设计全过程。

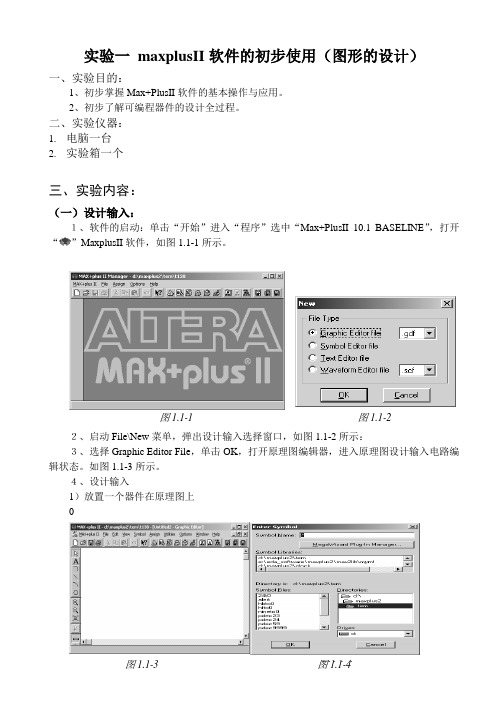

二、实验仪器: 1. 电脑一台 2. 实验箱一个三、实验内容:(一)设计输入:1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10.1 BASELINE ”,打开“”MaxplusII 软件,如图1.1-1所示。

2、启动File\New 菜单,弹出设计输入选择窗口,如图1.1-2所示:3、选择Graphic Editor File ,单击OK ,打开原理图编辑器,进入原理图设计输入电路编辑状态。

如图1.1-3所示。

4、设计输入1)放置一个器件在原理图上 01.1-4图1.1-1图1.1-2图1.1-3 图1.1-4b 、在光标处输入元件名称(如:input ,output ,and2,and3,nand2,or2,not ,xor ,dff 等)或用鼠标点击库元件,按下OK 即可。

c 、如果安放相同的元件,只要按住Ctrl 键,同时用鼠标按左键拖动该元件复制即可。

d 、一个完整的电路包括:输入端口input 、电路元件集合、输出端口output 。

e 、图1.1-5为3-8译码器元件安放结果。

2)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

3-8译码器原理图连线后如图1.1-6所示。

3)标记输入/输出端口属性分别双击输入端口的“PINNAME ”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似。

本译码器的三输入端分别标记为:A 、B 、C ;其八输出端分别为:D0、D1、D2、D3、D4、D5、D6、D7。

如图1.1-7所示。

4)保存原理图单击保存按钮图表,对于新建文件,出现类似文件管理器图框,请选择保存路径/文件名称保存原理图,原理图的扩展名为.gdf ,本实验中取名为test1.gdf 。

EDA技术与应用讲义第章第节EDA设计流程及其工具QUARTUSII快速设计指南-V1

EDA技术与应用讲义第章第节EDA设计流程及其工具QUARTUSII快速设计指南-V1EDA技术与应用讲义是关于电子设计自动化技术(EDA)的一本权威教材,其中介绍了EDA设计流程及其工具QUARTUSII的快速设计指南。

本文将重点介绍第一章第节中关于EDA设计流程及其工具QUARTUSII的内容,并提供一些快速设计指南。

一、EDA设计流程EDA设计流程是EDA设计中不可缺少的重要步骤,它主要包括如下几个步骤:1.需求分析:需求分析是整个设计流程中非常关键的一步。

在这个阶段,设计师需要了解客户需求,制定出设计目标,明确设计范围,并且向客户提供关于设计方案的报告。

2.系统级设计:在系统级设计阶段中,设计师需要通过设计文档和模块图来描述整个系统的基本框架、模块间的通信方式和模块的功能特性等。

在这一阶段需要并且经常使用的工具包括:Microsoft Office、Mindmap、XMind等。

3.算法设计与仿真:在这个阶段,设计师通过各种仿真工具对系统进行算法的仿真和验证。

在这一过程中,设计师需要熟练掌握仿真和验证工具,比如MATLAB、Verilog等。

4.电路级设计:电路级设计是EDA设计流程的重要步骤。

设计师需要在此阶段使用EDA工具来实现电路的设计,并进行SPICE仿真。

常用的工具包括SPICE仿真器、电路设计与验证工具等。

5.物理设计:在物理设计阶段中,设计师需要对电路进行物理实现和布局。

可以使用EDA工具中的Autoplacer和Autorouter等工具。

二、QUARTUSII快速设计指南QUARTUSII是EDA设计中广泛使用的FPGA开发工具,它可以从高层次的RTL代码到底层的逻辑等级进行仿真和综合,最终生成bitstream文件上传到FPGA中实现电路的设计。

QUARTUSII的快速设计指南包括:1.了解quartus ii软件:在使用QUARTUSII之前,首先需要熟悉软件的基本操作和使用流程。

EDA实验讲义

实验一十进制计数器的设计一、实验目的熟悉QuartusⅡ的Verilog HDL文本设计流程全过程,学习计数器的设计、仿真和硬件测试。

二、实验原理实验程序为例3-22,实验原理参考3.3节,设计流程参考4.1,4.2节。

三、实验内容编写Verilog程序描述一个电路,实现以下功能:设计带有异步复位、同步计数使能和可预置型的十进制计数器。

具有5个输入端口(CLK、RST、EN、LOAD、DATA)。

CLK输入时钟信号;RST 起异步复位作用,RST=0,复位;EN是时钟使能,EN=1,允许加载或计数;LOAD 是数据加载控制,LOAD=0,向内部寄存器加载数据;DATA是4位并行加载的数据。

有两个输出端口(DOUT和COUT)。

DOUT的位宽为4,输出计数值,从0到9;COUT是输出进位标志,位宽为1,每当DOUT为9时输出一个高电平脉冲。

四、实验步骤1、启动Quartus II软件,建立工程,文件夹CNT10B。

2、编写Verilog程序,存盘CNT10.V,编译。

器件选择Cyclone系列中的EP1C6Q240C8。

3、通过编译后,建立波形文件CNT10.vwf,设置仿真输入信号,存盘。

4、进行仿真(仿真时间50цS),分析结果。

5、进行引脚锁定,重新编译。

选用实验电路结构图NO.5。

6、下载到EDA实验系统上的FPGA中,进行实际测试。

7、使用SignalTap II对此计数器进行实时测试,流程与要求参考4.3节。

四、实验报告要求实验目的,实验内容,设计的Verilog程序,实验结果,结果分析,心得与体会。

思考题:在例3-22中是否可以不定义信号 CQI,而直接用输出端口信号完成加法运算,即:CQ <= CQ + 1?为什么?实验二四选一多路选择器的设计一、实验目的进一步熟悉QuartusⅡ的Verilog HDL文本设计流程,学习组合电路的设计、仿真和硬件测试。

二、实验原理实验程序为例3-5,实验原理参考3.1节,设计流程参考4.1,4.2节。

EDA实验讲义

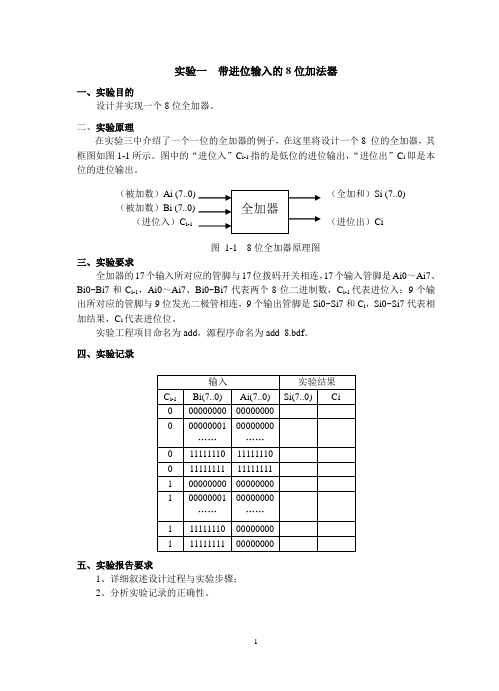

实验一 带进位输入的8位加法器一、实验目的设计并实现一个8位全加器。

二、实验原理在实验三中介绍了一个一位的全加器的例子,在这里将设计一个8 位的全加器,其框图如图1-1所示。

图中的“进位入”C i-1指的是低位的进位输出,“进位出”C i 即是本位的进位输出。

图 1-1 8位全加器原理图三、实验要求全加器的17个输入所对应的管脚与17位拨码开关相连,17个输入管脚是Ai0~Ai7、Bi0~Bi7和C i-1,Ai0~Ai7、Bi0~Bi7代表两个8位二进制数,C i-1代表进位入;9个输出所对应的管脚与9位发光二极管相连,9个输出管脚是Si0~Si7和C i ,Si0~Si7代表相加结果,C i 代表进位位。

实验工程项目命名为add ,源程序命名为add_8.bdf 。

四、实验记录五、实验报告要求1、详细叙述设计过程与实验步骤;2、分析实验记录的正确性。

(被加数)(被加数)(进位入)C i-1(全加和)Si (7..0)(进位出)Ci实验二多路数据选择器一、实验目的设计并实现一个16选1多路数据选择器。

二、实验原理在VHDL语言中描述一个2选一多路选择器的方法有多种,推荐使用when else构造,这样在VHDL代码中只用1行就可以描述2选1多路选择器。

例如:library ieee;use ieee.std_logic_1164.all;entity mux2 isport(a,b,sel: in std_logic;q: out std_logic);end;architecture a of mux2 isbeginq <= a when sel=’0’ else b;end;但我们在描述一个16选1的多路选择器时,若采用同样的方法,则就需要许多行VHDL代码,此时我们可以在进程中使用case语句会很清晰,不论使用哪一种描述方法,得到的结果应该是相同的。

16选1多路选择器结构图如图2-1所示。

EDA技术实验讲义

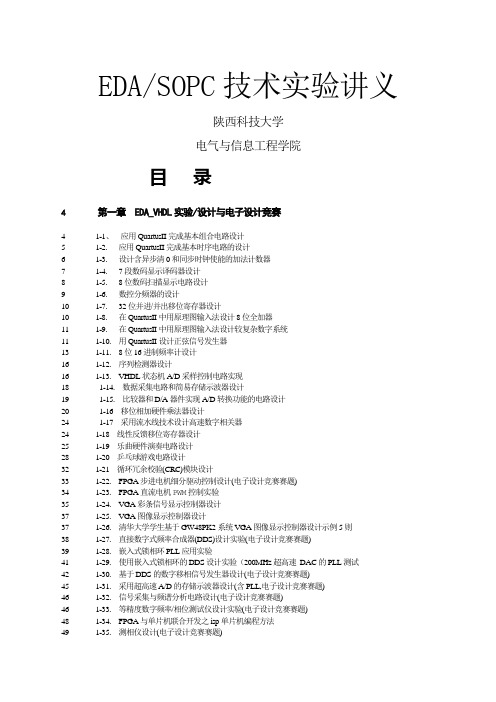

EDA/SOPC技术实验讲义陕西科技大学电气与信息工程学院目录4第一章 EDA_VHDL实验/设计与电子设计竞赛4 1-1、应用QuartusII完成基本组合电路设计5 1-2. 应用QuartusII完成基本时序电路的设计6 1-3. 设计含异步清0和同步时钟使能的加法计数器7 1-4. 7段数码显示译码器设计8 1-5. 8位数码扫描显示电路设计9 1-6. 数控分频器的设计10 1-7. 32位并进/并出移位寄存器设计10 1-8. 在QuartusII中用原理图输入法设计8位全加器11 1-9. 在QuartusII中用原理图输入法设计较复杂数字系统11 1-10. 用QuartusII设计正弦信号发生器13 1-11. 8位16进制频率计设计16 1-12. 序列检测器设计16 1-13. VHDL状态机A/D采样控制电路实现18 1-14. 数据采集电路和简易存储示波器设计19 1-15. 比较器和D/A器件实现A/D转换功能的电路设计20 1-16 移位相加硬件乘法器设计24 1-17 采用流水线技术设计高速数字相关器24 1-18 线性反馈移位寄存器设计25 1-19 乐曲硬件演奏电路设计28 1-20 乒乓球游戏电路设计32 1-21 循环冗余校验(CRC)模块设计33 1-22. FPGA步进电机细分驱动控制设计(电子设计竞赛赛题)34 1-23. FPGA直流电机PWM控制实验35 1-24. VGA彩条信号显示控制器设计37 1-25. VGA图像显示控制器设计37 1-26. 清华大学学生基于GW48PK2系统VGA图像显示控制器设计示例5则38 1-27. 直接数字式频率合成器(DDS)设计实验(电子设计竞赛赛题)39 1-28. 嵌入式锁相环PLL应用实验41 1-29. 使用嵌入式锁相环的DDS设计实验(200MHz超高速DAC的PLL测试42 1-30. 基于DDS的数字移相信号发生器设计(电子设计竞赛赛题)45 1-31. 采用超高速A/D的存储示波器设计(含PLL,电子设计竞赛赛题)46 1-32. 信号采集与频谱分析电路设计(电子设计竞赛赛题)46 1-33. 等精度数字频率/相位测试仪设计实验(电子设计竞赛赛题)48 1-34. FPGA与单片机联合开发之isp单片机编程方法49 1-35. 测相仪设计(电子设计竞赛赛题)50 1-36. PS/2键盘鼠标控制电子琴模块设计50 1-37. PS/2鼠标与VGA控制显示游戏模块设计50 1-38. FPGA_单片机_PC机双向通信测频模块设计50 1-39. 10路逻辑分析仪设计(电子设计竞赛赛题)51 1-40. IP核:数控振荡器NCO应用设计52 1-41. IP核:FIR数字滤波器应用设计53 1-42. IP核:FFT应用设计53 1-43. IP核:CSC VGA至电视色制互转模块应用设计54 1-44. IP核:嵌入式逻辑分析仪SignalTapII调用55 1-45. USB与FPGA通信实验56第二章 SOPC/EDA设计实验I56 2-1 用逻辑锁定优化技术设计流水线乘法器实验57 2-2 用逻辑锁定优化技术设计16阶数字滤波器实验59 2-3 基于DSP Builder的FIR数字滤波器设计实验60 2-4 基于DSP Builder的IIR数字滤波器设计实验60 2-5 基于DSP Builder的DDS与数字移相信号发生器设计实验62 2-6 m序列伪随机序列发生器设计实验63 2-7 巴克码检出器设计实验65 2-8 RS码编码器设计实验65 2-9 正交幅度调制与解调模型设计实验67 第三章 SOPC/EDA设计实验II67 3-1 基于MATLAB/DSP Builder DSP可控正弦信号发生器设计72 3-2 32位软核嵌入式处理器系统Nios开发实验73 3-3 设计一个简单的SOPC系统74 3-4 简单测控系统串口接收程序设计74 3-5 GSM短信模块程序设计75 3-6 基于SOPC的秒表程序设计77 3-7 Nios Avalon Slave外设(PWM模块)设计78 3-8 Nios Avalon Slave外设(数码管动态扫描显示模块)设计79 3-15 DMA应用和俄罗斯方块游戏设计79第四章 SOPC/EDA设计实验III ( NiosII系统设计 ) 79 4-1、建立NIOSII嵌入式处理器硬件系统87 4-2、NIOSII软件设计与运行流程94 4-3、加入用户自定义组件设计100 4-4、加入用户自定义指令设计103 4-5、FLASH编程下载104 4-6、设计DSP处理器功能系统104 4-7、AM调制电路设计105第五章液晶接口实验105 5-1 GDM12864A液晶显示模块接口开发111 5-2 HS162-4液晶显示模块与单片机的接口114 5-3 G240-128A液晶显示模块的接口115第六章 CPU及其结构组件设计实验115 6-1 复杂指令CPU设计122 6-2 8051/89C51单片机核于FPGA中实现实验124第七章模拟EDA实验124 7-1 模拟EDA实验及其设计软件使用向导(PAC _Designer使用)124 7-2 基于ispPAC80的5阶精密低通滤波器设计126 7-3 基于ispPAC10的直流增益为9的放大器设计129附录:GW48 EDA/SOPC主系统使用说明129 第一节:GW48教学系统原理与使用介绍,132 第二节:实验电路结构图137 第三节:超高速A/D、D/A板GW-ADDA说明138 第四节:步进电机和直流电机使用说明138 第五节:SOPC适配板使用说明139 第六节:GWDVPB电子设计竞赛应用板使用说明141 第七节:GWCK/PK2/PK3系统万能接插口与结构图信号/与芯片引脚对照表第一章EDA_VHDL实验/设计与电子设计竞赛1-1. 应用QuartusII完成基本组合电路设计(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

EDA实验讲义

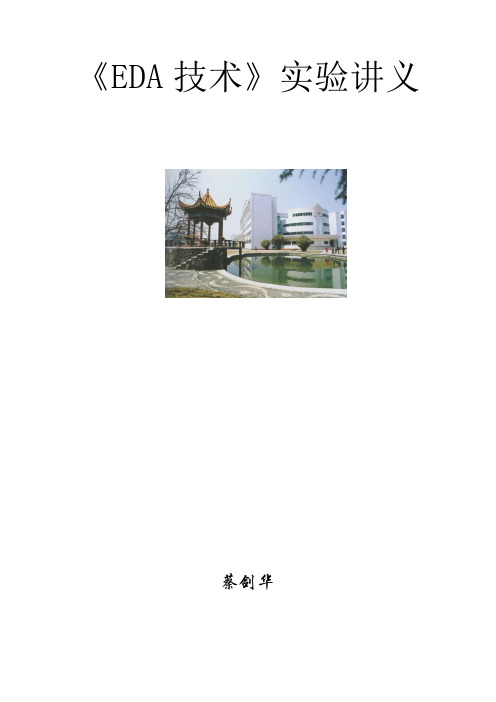

第一篇基础实验5-1. 时序电路的设计(1) 实验目的:熟悉MAX+PLUSII的VHDL文本设计过程。

(2)学习简单时序电路的设计、仿真和测试。

MAX+PLUSII设计导向(以十进制计数器为例)(一)设计输入(以文本设计输入方法为例)1、建立新文件(1)执行 File\New。

(2)在New对话框中选择text Editor File项,然后按下OK按钮, 将会出现一个无标题的文本编辑器窗口。

(3)执行file\save as(或工具3),在file name设置文件名cnt10.vhd(与实体名一致); automatic extension栏选择.vhd;Directories栏设置存储路径如e:﹨xsw﹨ (注意:一定要存放在一个文件夹里)。

2、在编辑窗口文本文件在文本编辑器窗口的空白处用VHDL语言编写程序。

3、指定设计项目名称并设为当前文件(1)执行File\Project﹨ Name项(或工具16),(2) 在Project Name框内键入你的设计项目名cnt10.vhd(注意:项目名与设计文件名一致)(3)执行File\Project \set project to current file项(或工具17),即设为当前文件。

4、检查并保存文件执行file\project\save&check(或工具19)。

如果有错则修改之。

(二)编译(1)执行MAX+PLUS II\COMPILER(或工具12),打开编译器。

(2)点击Assign\Device菜单,选用ACEX1K系列中的EP1K100QC208-3(3)执行Processing\Design Doctor项,执行Processing\Design Doctor Setting项,FPGA芯片选择FLEX rules。

(4)选中Timing SNF Extractor (时序仿真)。

(5)执行Interfaces/VHDL Netlist reader settings,选中VHDL 1987版本。

EDA电子设计实验讲义

MAX+PLUS II 操作指南自动化学院电工电子技术中心“电子技术基础”课程教学组第一部分原理图输入设计方法利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。

MAX+plusII提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。

但更为重要的是,MAX+plusII还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。

以传统的数字电路实验相比为例,MAX+plusII提供原理图输入设计功能具有显著的优势:∙能进行任意层次的数字系统设计。

传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计;∙对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1ns ,因此能发现一切对系统可能产生不良影响的竞争冒险现象;∙通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正;∙能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件;∙通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。

∙如果使用FPGA和配置编程方式,将不会有如何器件损坏和损耗;∙符合现代电子设计技术规范。

传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。

以下将详细介绍原理图输入设计方法,但读者应该更多地关注设计流程,因为除了最初的图形编辑输入外,其它处理流程都与文本(如VHDL文件)输入设计完全一致。

EDA实验讲义

实验一简单逻辑电路设计与仿真一.实验目的1.学习并掌握MAX+PLUSⅡ及CPLD/FPGA实验开发系统的基本操作。

2.学习在MAX+PLUSⅡ下设计简单逻辑电路与功能仿真的方法。

二.实验仪器设备1.PC机一台2.KHF-1/KHF-2/KHF-3/KHF-4/KHF-5 CPLD/FPGA实验开发系统一套。

三.实验要求1.预习教材中的相关内容。

2.阅读并熟悉本次实验的内容。

3.用图形输入方式完成电路设计。

4.分析器件的延时特性。

四.实验内容及参考实验步骤1.用D触发器设计一个4进制加法计数器并进行功能仿真。

(1)开机,进入MAX+PLUSⅡ软件系统。

(2)点击File菜单Project子菜单之Name项,出现Project Name 对话框。

为当前的实验选择恰当的路径并创建项目名称(注意MAX+PLUSⅡ不识别中文路径)。

(3)点击File菜单之New项,出现对话框,为选择输入方式,这儿我们选择Graphic Editor File。

出现图形编辑窗口(注意界面发生了一定变化)。

(4)双击空白编辑区,出现Enter Symbol 对话框(或点击Symbol 菜单Enter Symbol 项)从Symbol Libraries项中选择mf子目录(双击),然后在Symbol File 中选择7474元件(双D触发器);在prim子目录中选择输入脚input 和输出引脚output(或直接Symbol Name 中输入所需元件的名称回车亦可)。

(5)在图形编辑窗口中的左侧点击连线按钮(draws a horizontal or vertical line),并完成对电路的连线(参考电路如图3-1)。

图3-1 4 进制加法计数器(6)在引脚的PIN_NAME处左键双击使之变黑,键入引脚名称。

(7)点击工具栏中的“change the project name to the name of the current file”按钮,使项目名称与当前设计文件相同。

EDA实验讲义(2012版)

《EDA技术》实验讲义蔡剑华湖南文理学院物电系电子技术教研室第一部分硬件资源说明1)PORT A信号分配注意:从FPGA引出到PORT A、PORT B的所有信号线,在适配器板上均有其它器件复用,使用时一定要注意,请查看《E-Play-SOPC适配器原理图》或查看前面FPGA对其它芯片的管脚分配表。

2)PORT B信号分配3)系统复位及系统时钟分配:4)模式分配16个用户IO单元IO1-IO16都是通过PORTB从FPGA直接引出,供用户二次开发使用,具体定义请参照PORTB的接口定义。

16个拨码开关,16个按键,12个交通灯和蜂鸣器四周4个灯,8位数码管,4x4矩阵键盘,16x16点阵LED均是从底板的两片CPLD引出的,这些资源有IO方式和总线操作两种控制方式。

当采用IO控制方式时,通过PORTB的41-44 四位设置不同的值来选择不同的资源。

4位功能管脚说明:PORT B 对应标识41 M[0]42 M[1]43 M[2]44 M[3]M[3..0] 0001 16位拨码开关接到16位数据总线上0011 16位按键接到16位数据总线上0111 12个交通灯和蜂鸣器四周4个灯接到16位数据总线上0010 8个数码管,低8位为7位段总加小数点选取位,高8位为8个数码管com端选取,即如果要选取数码管0,则发送总线值为:1111 1110 1111 1111,如要选取数码管1,则发送总线值为:1111 1101 1111 1111.此时所选数码管7段和DP位将全部亮.0101 4X4键盘功能选取,此时只有最低的8位有效,高4位为键盘的4位行扫描输出,低4位为键盘的4位列查询输入0110 16X16 LED点阵显示功能选取,16位数据总线作为点阵的行值,4位地址对应列值编码,(底板上已经过译码).4位地址分别对应E-PLAY-SOPC主适配器上外扩总线地址的ADDRESS[4..1]在做基本的数字逻辑实验时,如果用到底板的资源时,一定要设置M[3..0]4位功能位,并且设置值一定要与上述功能对应,如不对应有可能对硬件造成损伤.当实验用到的拨码,按键,LED小于5位时,可以使用E-PLAY-SOPC适配器上的资源,当实验中仅使用到E-PLAY-SOPC适配器就可以完成时,可以不设置M[3..0]特别注意在做Quartus II工程时必须将未分配的管脚置为三态输入。

EDA实验讲义v1[1].0

![EDA实验讲义v1[1].0](https://img.taocdn.com/s3/m/b29ad3335a8102d276a22ff9.png)

EDA实验指导书浙江师范大学数理与信息工程学院电工电子实验教学中心二〇〇八年九月目 录第一章 EDA技术实验基本要求 (1)1.1 EDA技术实验的预习要求 (1)1.2 EDA技术实验的基本步骤 (1)1.3 EDA技术实验的报告要求 (1)第二章 爱迪克EDA实验箱使用手册 (2)2.1 系统组成 (2)2.2 AEDK-EDA实验机布局图 (3)2.3 实验模块 (4)1.调压电路 (4)2.A/D转换 (4)3.参考电源 (5)4.电压比较 (5)5.D/A转换 (5)6.RAM (6)7.ROM (6)8.输出驱动 (7)9.继电器模块 (7)10.蜂鸣器 (8)11.交通灯实验 (8)12.输出指示 (9)13.骰子实验 (9)14.液晶模块 (10)15.RESET (10)16.CPU (10)17.脉冲和上下沿 (11)18.脉冲源 (11)19.LED点阵 (12)20.串口通讯 (12)21.输入端子 (13)22.开关设置 (13)23.设置跳接 (13)24.键盘显示 (14)2.4 EDA-A2适配卡信号表(ALTERA EPF10K10 10K20) (15)第三章 EDA实验内容 (17)实验1 MAX+PLUS软件的使用 (17)实验2 简单组合逻辑电路设计 (32)实验3 三—八译吗码器电路设计 (33)实验4 四选一数据选择器电路设计 (35)实验5 全加器电路设计 (36)实验6 交通灯电路设计 (37)实验7 骰子实验 (39)实验8 计数时钟综合实验 (41)第一章 EDA技术实验基本要求1.1 EDA技术实验的预习要求每次实验前,先阅读该实验的实验指导,并完成实验要求中的如下内容:(1)进行系统的分析建模,画出原理框图,并说明系统各模块的功能;(2)各个VHDL 源程序的设计;(3)波形仿真文件中各个输入信号的设置;(4)实验芯片的选择(教师可事先给定)、管脚锁定文件的编制以及进行硬件验证方案的制定。

EDA讲义

第一章CPLD/FPGA数字实验开发系统使用说明GXUEDA-98C实验开发系统设计原理和使用方法GXUEDA-98C型CPLD/FPGA实验开发系统是一种多功能、高配臵的EDA教学与开发设备,适合用于大学本科EDA教学、课程设计和毕业设计。

也适合于大专院校、科研所做项目开发之用。

该系统采用单片机控制整个实验系统的独特技术,在单片机的控制下,系统可以产生不同的实验模式,构成了以CPLD+MPU双系统为主要特征的复合型综合电子实验平台。

除了适用基于数字逻辑电路的电子设计自动化EDA,数字系统设计硬件描述语言(VHDL、Verilog HDL),数字系统设计等相关课程教学实验平台,还适用基于单片机的学生电子创新设计平台。

系统配有RS232、AD0809、DAC0832、RAM62256、LED点阵、SST89E564RD单片机等功能模块器件和接口,所构成的综合系统完全是由用户根据题意所设定,最典型的组合模式有13种,极为灵活(每种模式功能参见说明书)。

同时,该系统扩展灵活,完全可以根据用户需要改变电路结构,为高年级学生做创新性实验课题、综合电子设计、毕业设计、电子设计竞赛的训练以及为教师的科研工作提供了实验环境。

例如可利用此平台完成基于LED点阵的汉字显示、100MHz范围内自适应频率计等大型课题的设计。

该系统的实验电路结构是可控的,即可通过模式选择键SW17,使电路改变连接方式以适应不同的实验需要。

从物理结构上看,实验板的电路结构是固定的,但其内部的信息流在主控单片机的控制下,电路结构将发生变化,这种“多任务重配臵”(Multi-task Reconfiguring)是目前最先进的数字电子系统设计思想,本设计方案的优点体现在:1.适应更多的实验与开发项目;2. 兼容更多的PLD公司的器件;3. 兼容不同封装的CPLD和FPGA器件;4.减少连线的麻烦,增加了系统的可靠性和稳定性;5.用户可支配系统资源非常多。

EDA实验讲义

EDA 实验

根据式 1-1,可以得出, So 为两个输入信号的异或( xor 门) , Co 为两个

实验一

一、实验目的

加法器

信号的与( and 门) 。 三、实验步骤 步骤 1:为本项设计建立文件夹 任何一项设计都是一项工程( Project) , Quartus II 以工程方式对设计过程 进行管理,工程中存放创建 FPGA 配置文件需要的所有设置和设计文件。设计 前一般首先为此工程建立一个放置与此工程相关的所有文件的文件夹,此文件 夹将被 EDA 软件默认为工作库( Work Library) 。一般不同的设计项目最好放 在不同的文件夹中,便于以后的管理,即使有些硬件描述语言程序原来已经完 成,建议最好把相关文件拷贝到新工程文件夹下,否则以后工程拷贝时可能不 完整,造成不必要的麻烦。 为了区分方便起见,每位实验者在硬盘建立一个以自己学号命名或英文名 字的一级文件夹,一级文件夹下建立二级文件夹,每个实验或工程对应一个耳 机 文 件 夹 , 二 级 文 件 夹 的 名 字 为 exp_1 , 第 二 个 实 验 的 二 级 文 件 夹 为 exp_2, ……,或者二级文件夹的名字和工程功能有关,便于以后的管理。 注意:Quartus II 为英文软件,早期的版本不支持全角字符,故文件夹不能 用中文(包括放在“桌面”文件夹下) ,也不能带空格;不要将文件夹设在计算 机已有的安装目录下,更不要将工程文件直接放在安装目录下。 步骤 2:建立设计工程 1. 点击桌面的 Quartus II 的快捷方式图标 QuartusⅡ8.0 软件。 如果第一次使用 Quartus II 软件,需要安装 License。此略

Co 0 0 0 1

示。

根据真值表,我们可以得出输出和输入之间的关系,如实验式 1-1 所示。

EDA课程实验讲义

实验一基本组合逻辑电路设计一、实验目的1. 熟悉Quartus Ⅱ软件基本使用方法;2.掌握电路的基本设计方法;3.掌握电路的基本仿真方法;4.掌握电路的基本下载方法。

二、实验内容用VHDL语言和原理图分别完成设计、仿真和下载基本逻辑门电路半加器的过程:输入:a,b;输出:求和sum,进位c;三、实验设备1. KH-31001 主机;2. KH-33001/2/3 下载板(或KH-33004 下载板或KH-33005下载板);四、实验步骤1. 新建文本文件在Quartus Ⅱ管理器界面中选择File/New.., 菜单,出现New对话框,如图1.1所示。

在对话框中选择VHDL File,点击OK,打开文本编辑器,输入半加器的VHDL语言程序,如图1.2所示。

然后保存文件halfadd.vhd。

需要注意的是,文件名与模块名必须一致。

图1.1 Quartus Ⅱ新建文本文件界面图1.2 输入半加器的VHDL语言程序图1.3保存文件2.建立工程项目(1)在管理器窗口中选择File/New Project Wizard...菜单,出现新建项目向导New ProjectWizard 对话框,输入项目目录(r:\test)、项目名称(halfadd)和顶层实体(halfadd),如图1.4所示,顶层实体名可以与项目名不同。

图1.4 建立工程项目(2)点击Next,添加文件对话框。

点击按钮“…”,添加与该项目有关的所有文件到当前项目,如图1.5所示。

本例只有一个文件halfadd.vhd,所以不用添加其它器件。

图1.5图1.6图1.7 添加项目有关的文件(3)点击Next按钮,再点击Next选择目标器件系列ACEX1K,选择目标器件封装形式,引脚数目和速度级别。

如图1.8所示,点击NEXT。

图1.8 选择目标器件(4)点击FINISH按钮,项目halfadd出现在项目导航窗口中,如图1.9所示。

双击文件名,即可打开文件。

EDA实验讲义

实验一离散傅里叶变换的性质及应用一、实验目的1、了解DFT的性质及应用。

2、熟悉MATLAB编程的特点。

二、实验内容1、用三种不同的DFT程序计算x(n)=R8(n)的傅里叶变换X(e jw),并比较三种程序计算机运行时间。

(1) 用for loop 语句的M函数文件dft1.m,用循环变量逐点计算X(k);(2) 编写用MATLAB矩阵运算的M函数文件dft2.m,完成上述运算;(3) 编写函数dft3.m,调用FFT库函数,直接计算X(k);(4) 分别利用上述三种不同方式编写的DFT程序计算序列x(n)的傅立叶变换X(e jw),并画出相应的幅频和相频特性,再比较各个程序的计算机运行时间。

M函数文件如下:dft1.m:function[Am,pha]=dft1(x)N=length(x);w=exp(-j*2*pi/N);for k=1:Nsum=0;for n=1:Nsum=sum+x(n)*w^((k-1)*(n-1));endAm(k)=abs(sum);pha(k)=angle(sum);enddft2.m:function[Am,pha]=dft2(x)N=length(x);n=[0:N-1];k=[0:N-1];w=exp(-j*2*pi/N);nk=n'*k;wnk=w.^(nk);Xk=x*wnk;Am=abs(Xk);pha=angle(Xk);dft3.m:function[Am,pha]=dft3(x)Xk=fft(x);Am=abs(Xk);pha=angle(Xk);源程序及运行结果:(1) x=[ones(1,8),zeros(1,248)];t=cputime;[Am1,pha1]=dft1(x);t1=cputime-tn=[0:(length(x)-1)];w=(2*pi/length(x))*n;figure(1)subplot(2,1,1), plot(w,Am1,'b'); grid;title('Magnitude part');xlabel('frequency in radians');ylabel('|X(exp(jw))|');subplot(2,1,2), plot(w,pha1,'r'); grid;title('Phase Part');xlabel('frequency in radians');ylabel('argX[exp(jw)]/radians');(2) x=[ones(1,8),zeros(1,248)];t=cputime;[Am2,pha2]=dft2(x);t2=cputime-tn=[0:(length(x)-1)];w=(2*pi/length(x))*n;figure(2)subplot(2,1,1), plot(w,Am2,'b'); grid;title('Magnitude part');xlabel('frequency in radians');ylabel('|X(exp(jw))|');subplot(2,1,2), plot(w,pha2,'r'); grid;title('Phase Part');xlabel('frequency in radians');ylabel('argX[exp(jw)]/radians');(3) x=[ones(1,8),zeros(1,248)];t=cputime;[Am3,pha3]=dft3(x);t3=cputime-t;n=[0:(length(x)-1)];w=(2*pi/length(x))*n;figure(3)subplot(2,1,1), plot(w,Am3,'b'); grid;title('Magnitude part');xlabel('frequency in radians');ylabel('|X(exp(jw))|');subplot(2,1,2), plot(w,pha3,'r'); grid;title('Phase Part');xlabel('frequency in radians');ylabel('argX[exp(jw)]/radians')从以上运行结果可以看出,调用FFT库函数直接计算X(k)速度最快,矩阵运算次之,用循环变量逐点计算运行速度最慢。

EDA实验指导讲义(自编)

实验注意事项1.启动计算机,进入2000系统(98系统可以直接进行硬件编程下载,其它系统需装驱动)。

2.打开Quartus II软件,注意软件有没有安装Lisence,若没有请自己安装。

3.在Quartus II中进行设计的输入、编译和仿真,若正确后可进行下一步。

4.检查实验箱的数据线有无连接到计算机的并口(轻插轻拔),电源线有无接上,若均有,则给实验箱上电(开关在实验箱后面)。

5.确认你所需要的实验模式,选中此种模式后,建议按一下右侧的复位键,以便使系统进入该结构模式工作。

6.在Quartus II中进行引脚的锁定后,重新编译一次,然后再下载到实验箱上,接着在实验箱上进行硬件验证。

需要修改代码的话,重复3~6部分。

7.注意在实验中不可带电插拔实验箱上的任何芯片。

8.不可随意搬动实验箱,若确实需要移动,需老师在场,且同意。

9.不可将水、饮料等其它液体洒到实验箱上面。

10.离开实验室时不可带走任何实验室的东西,比如实验说明书等。

11.闲置不用实验箱时,关闭实验箱后面的开关,注意不要拔掉数据线(后续实验还要用),将数据线放平,实验箱的盖子轻轻盖上,不必上锁扣!!!实验的一般步骤1.原理图或VHDL程序代码输入2.检查有无语法错误,编译通过3.建立波形仿真文件4.进行时序仿真,观察逻辑关系是否正确5.管脚分配与锁定6.重新编译适配,产生下载文件7.检查实验箱的电源接上否?并行下载线是否正确联接?拨码开关4为ON,其它为OFF?8.打开实验箱电源,选择合适的模式,复位系统9.编程下载,选择JTAG并行下载方式10.硬件仿真实验课的上课纪律:1.珍惜做实验的时间,禁止在电脑上玩游戏2.实行点名制度,须经老师在实验箱上进行硬件验证,若正确才算完成实验。

3.平时实验的成绩占期末考的30%~40%。

实验报告的撰写格式:实验名称一、实验目的二、实验内容三、实验条件(1)、开发软件Max+Plus II 或者Quartus II 5.0/7.2(2)、实验设备 GW-48系列EDA实验开发系统(3)、所用芯片Altera公司ACEX1K系列的EP1K30TC144-3芯片四、实验设计(1)、系统的原理框图(2)、原理图/VHDL源程序(3)、仿真波形(4)、管脚锁定情况五、实验结果及总结(1)、系统仿真情况(2)、硬件验证情况(3)、实验过程中出现的问题及解决的办法注:除仿真波形可用截图方式打印外,其余要求用手写。

EDA电子制图实验讲义-推荐下载

实验一软件基本操作该练习就是建立名为MYPRO的文件夹,并在该文件夹内建立MYFIRST的设计文件[练习1] 启动Protel99SE,建立名为MYPRO的文件夹,并在文件夹中建立名为MYFIRST的设计数据库文件。

提示:单击桌面上的Protel99SE快捷图标,进入Protel99SE设计环境。

若环境中已经有设计数据库文件,就执行菜单File/Close Design将其关闭。

若环境中没有设计数据库文件,就执行菜单File/New,在弹出的窗口中,单击Browse按钮,在弹出的文件名输入窗口中建立MYPRO的文件夹,并在文件夹中建立MYFIRST的设计文件。

[练习2] 在练习1的基础上,建立名为FIRSCH的原理图文件,并进入原理图设计窗口。

提示:执行File/New菜单,在弹出的窗口中选择Schematic Document图标。

[练习3] 1、设置原理图的图纸尺寸为A0,去掉可视栅格,去掉标题栏。

2、显示可视栅格,标题栏提示:在原理图设计环境中,执行菜单Design/Options,在弹出的窗口中选择Sheet Options页面,在页面右上角的Standard Styles下拉框中选择A0。

现在的原理图文件没有可视栅格,图幅为A0[练习4] 把光标设置成大十字,并把光标移动到图纸边沿时的移动速度设置为Auto Pan Recenter。

提示:设置光标:在原理图设计环境中,执行菜单Tools/Preferences,在弹出的窗口中选择Graphical Editing 页面,然后在该页面Cursor/Grid Options 区域的Cursor Type下拉列表框中选择Large Cursor 90。

设置光标移动:在原理图设计环境中,执行菜单Tools/Preferences,在弹出的窗口中选择Graphical Editing页面,然后在该页面Autopan Options 区域的Style下拉列表框中选择Auto Pan ReCenter。

综合实验讲义(EDA)

二、开发环境介绍

设计输入(Design Entry)

• 硬件描述语言 硬件描述语言用于文本形式描述设计, 又可分为普通的硬件描述语言和行为描述语言。 普通的硬件描述语言,如ABEL—HDL、CUPL和 MINC—HDL。它们支持布尔方程、真值表、状态机 等逻辑表达式,适合对计数器、译码器和状态机 等逻辑功能的描述。行为描述语言,如VHDL和 Verilog –HDL。行为描述语言类似于C语言,在描 述复杂设计时非常简洁,具有很强的逻辑描述和 仿真功能,是未来硬件描述语言的主流。

二、开发环境介绍

下载线原理图

JP1接目标板JTAG口,J1接计算机并口

二、开发环境介绍

可编程器件设计流程

CPLD或FPGA器件的设计一般可分为设计 输入、设计实现和编程三个设计步骤,及 相应的前仿真(功能仿真)、后仿真(时 序仿真)和测试三个设计验证过程。

二、开发环境介绍

设计输入(Design Entry)

本课程要学习的pld设计eda工具软件quartus?美国altera公司自行设计的第四代pld开发软件?可以完成pld的设计输入逻辑综合布局可以完成pld的设计输入逻辑综合布局与布线仿真时序分析器件编程的全过程?同时还支持sopc可编程片上系统设计开发6quartus简介quartus提供了方便的设计输入方式快速的编译和直接易懂的器件编程

二、开发环境介绍

建立原理图文件

在原理图的空白处双击 鼠标右键,出现下图。在 symbol name栏内,键入dff, 选ok即可。在不知道器件的 名称时,双击相应符号库目 录,在符号文件框内选择也 可以。在本例中,是双击库 目录; d;\max2work\max2lib\prim, 再选出dff。用同样的方法 可以依次键入input output 和vcc等。

EDA实验指导-VHDL实验讲义

目录第一章EDA_VHDL 实验设计1-1、应用 QuartusII 完成基本组合电路设计1-2. 应用 QuartusII 完成基本时序电路的设计1-3. 设计含异步清 0 和同步时钟使能的加法计数器1-4. 7 段数码显示译码器设计1-5. 8 位数码扫描显示电路设计1-6. 数控分频器的设计1-7. 在 QuartusII 中用原理图输入法设计 8 位全加器1-8. 在 QuartusII 中用原理图输入法设计较复杂数字系统1-9. 用 QuartusII 设计正弦信号发生器1-10. 8 位 16 进制频率计设计1-11. 序列检测器设计1-12. VHDL 状态机 A/D 采样控制电路实现1-13. 数据采集电路和简易存储示波器设计1-14. 比较器和 D/A 器件实现 A/D 转换功能的电路设计1-15 移位相加硬件乘法器设计1-16 采用流水线技术设计高速数字相关器1-17 线性反馈移位寄存器设计1-18 循环冗余校验(CRC)模块设计附录:GW48 EDA/SOPC 主系统使用说明第一节:GW48 教学系统原理与使用介绍,第二节:实验电路结构图第三节:步进电机和直流电机使用说明第四节:SOPC 适配板使用说明第五节:GWCK/PK2/PK3 系统万能接插口与结构图信号/与芯片引脚对照表第一章 EDA_VHDL 实验设计1-1. 应用QuartusII完成基本组合电路设计(1) 实验目的:熟悉QuartusⅡ的VHDL 文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

(2) 实验内容1:首先利用QuartusⅡ完成2 选1 多路选择器(例1-1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出图3-3 所示的仿真波形。

最后在实验系统上进行硬件测试,验证本项设计的功能。

(3) 实验内容2:将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图1-1,并将此文件放在同一目录中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

学习使人进步实验一十进制计数器的设计一、实验目的熟悉QuartusⅡ的Verilog HDL文本设计流程全过程,学习计数器的设计、仿真和硬件测试。

二、实验原理实验程序为例3-22,实验原理参考3.3节,设计流程参考4.1,4.2节。

三、实验内容编写Verilog程序描述一个电路,实现以下功能:设计带有异步复位、同步计数使能和可预置型的十进制计数器。

具有5个输入端口(CLK、RST、EN、LOAD、DATA)。

CLK输入时钟信号;RST 起异步复位作用,RST=0,复位;EN是时钟使能,EN=1,允许加载或计数;LOAD 是数据加载控制,LOAD=0,向内部寄存器加载数据;DATA是4位并行加载的数据。

有两个输出端口(DOUT和COUT)。

DOUT的位宽为4,输出计数值,从0到9;COUT是输出进位标志,位宽为1,每当DOUT为9时输出一个高电平脉冲。

四、实验步骤1、启动Quartus II软件,建立工程,文件夹CNT10B。

2、编写Verilog程序,存盘CNT10.V,编译。

器件选择Cyclone系列中的EP1C6Q240C8。

3、通过编译后,建立波形文件CNT10.vwf,设置仿真输入信号,存盘。

4、进行仿真(仿真时间50цS),分析结果。

5、进行引脚锁定,重新编译。

选用实验电路结构图NO.5。

6、下载到EDA实验系统上的FPGA中,进行实际测试。

7、使用SignalTap II对此计数器进行实时测试,流程与要求参考4.3节。

四、实验报告要求实验目的,实验内容,设计的Verilog程序,实验结果,结果分析,心得与体会。

思考题:在例3-22中是否可以不定义信号 CQI,而直接用输出端口信号完成加法运算,即:CQ <= CQ + 1?为什么?实验二四选一多路选择器的设计一、实验目的进一步熟悉QuartusⅡ的Verilog HDL文本设计流程,学习组合电路的设计、仿真和硬件测试。

二、实验原理实验程序为例3-5,实验原理参考3.1节,设计流程参考4.1,4.2节。

三、实验内容编写Verilog程序描述一个电路,实现以下功能:具有6个输入端口 A、B、C、D、S1、SO,A、B、C、D均为输入端口,位宽为1;Sl、S0为通道选择控制信号端,位宽为1;Y为输出端口,位宽为1。

当S1S0为“00”时,A的数据从Y输出,S1S0为“01”时,B的数据从Y输出,S1S0为“10”时,C的数据从Y输出,S1S0为“11”时,D的数据从Y输出。

四、实验步骤1、启动Quartus II软件,建立工程。

器件选择Cyclone系列中的EP1C6Q240C8。

2、编写Verilog程序,存盘编译。

3、通过编译后,建立波形文件,设置仿真输入信号,存盘。

4、进行仿真,分析结果。

5、进行引脚锁定,重新编译。

选用实验电路结构图NO.5。

6、下载到EDA实验系统上的FPGA中,进行实际测试。

四、实验报告要求实验目的,实验内容,设计的Verilog程序,实验结果,结果分析,心得与体会。

实验三原理图输入法设计8位全加器一、实验目的熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二、实验原理一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接。

而一个1位全加器可以由半加器来构成。

三、实验内容1、按照1-1、1-2图完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个硬件符号入库。

键1、键2、键3(PIO0/1/2)分别接ain、bin、cin;发光管D2、D1(PIO9/8)分别接sum和cout。

1-1 半加器原理图1-2 全加器原理图2、建立一个更高层次的原理图设计,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真和硬件下载(JTAG模式下载SOF文件)测试。

建议选择电路模式1;键2、键1输入8位加数;键4、键3输入8位被加数;数码6/5显示加和;D8显示进位cout。

引脚分配如下:a[7..0]对应的是PIO[15..8],,引脚分别是12、8、7、6、4、3、2、1。

b[7..0]对应的是PIO[7..0],,引脚分别是240、239、238、237、236、235、234、233。

cin对应的是PIO49,引脚是173。

sum[7..0]对应的是PIO[23..16],,引脚分别是20、19、18、17、16、15、14、13。

cout对应的是PIO39,引脚是160。

结构如图1-3。

1-3 8位加法器原理图4、要求全程编译后生成用于配置器件EPCS4编程的压缩POF文件,并使用USB-Blaster,通过AS模式对实验板上的EPCS4进行编程,最后进行验证。

(6) 实验报告:详细叙述8位加法器的设计流程;给出各层次的原理图及其对应的仿真波形图;给出加法器的时序分析情况;最后给出硬件测试流程和结果。

实验七原理图输入法设计频率计一、实验目的熟悉原理图输入法中74系列等宏功能元件的使用方法,掌握更复杂的原理图层次化设计技术和数字系统设计方法。

完成8位十进制频率机的设计。

二、实验原理利用4.5.2节介绍的2位计数器模块,连接它们的计数进位,用4个计数模块就能完成一个8位有时钟使能的计数器;对于测频控制器的控制信号,在仿真过程中应该注意它们可能的毛刺现象。

最后按照4.5.2节中的设计流程和方法即可完成全部设计。

三、实验内容首先完成2位频率计的设计,然后进行硬件测试,建议选择电路模式2;数码2和1显示输出频率值,待测频率F_IN接clock0;测频控制时钟CLK接clock2,若选择clock2 = 8Hz,门控信号CNT_EN的脉宽恰好为1秒。

然后建立一个新的原理图设计层次,在此基础上将其扩展为8位频率计,仿真测试该频率计待测信号的最高频率,并与硬件实测的结果进行比较。

四、实验报告给出各层次的原理图、工作原理、仿真波形图和分析,详述硬件实验过程和实验结果。

实验四正弦信号发生器设计实验五 8位数码显示频率计设计实验六序列检测器设计附加实验:(可加分)实验七原理图输入法设计频率计实验八实验九实验十实验十一实验十二实验十三实验十四实验十五附录一 实验电路结构图CLOCK0CLOCK2CLOCK5CLOCK9目标芯片F PG A /C P L D HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8NO.0S P E A K E R 扬声器实验电路结构图译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16图3-1 电路结构图NO.0CLOCK9CLOCK5CLOCK2CLOCK0SPEAKER扬声器NO.1PIO11-PIO8PIO15-PIO12PIO48PIO49D15D16HEX HEXPIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39D1D2D3D4D5D6D7D8实验电路结构图译码器译码器译码器译码器FPGA/CPLD 目标芯片12345678PIO3-PIO0PIO7-PIO4HEX HEX 键1键2键3键4键5键6键7键8PIO39-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16图3-2 电路结构图NO.1CLOCK9CLOCK5CLOCK2CLOCK0PIO48PIO49D10D912345678NO.2实验电路结构图FPGA/CPLD 直接与7段显示器相接PIO46-PIO40PIO38-PIO32PIO30-PIO24PIO22-PIO16PIO46-PIO40 接 g, f, e , d, c, b, a PIO38-PIO32 接 g, f, e , d, c, b, aPIO30-PIO24 接 g, f, e , d, c, b, a 七段PIO22-PIO16 接 g,f,e,d ,c,b,aPIO15-PIO12PIO11-PIO8PIO7-PIO4PIO3-PIO0目标芯片键1键2键3键4键5键6键7键8译码器译码器译码器译码器图3-3 电路结构图NO.2CLOCK9CLOCK5CLOCK2CLOCK0实验电路结构图NO.3译码器译码器译码器译码器译码器译码器译码器译码器D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E R扬声器12345678目标芯片FPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16图3-4 电路结构图NO.3CLOCK9CLOCK5CLOCK2CLOCK0实验电路结构图NO.4目标芯片FPGA/CPLD 12345678D16D15D14PIO3-PIO0PIO7-PIO4PIO15-PIO12HEX HEX HEX单脉冲单脉冲键1键2键3键4键5键6键7键8PIO11PIO9PIO8PIO10PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32串行 输出显示串行输出CLEARCLOCKLOAD时钟计数器D1D2D3D4D5D6D7D8译码器译码器译码器译码器图3-5 电路结构图NO.4CLOCK9CLOCK5CLOCK2CLOCK0D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器图3-6 电路结构图NO.7CLOCK9CLOCK5CLOCK2CLOCK0FPGA/CPLD PIO10串行输入脉冲D16D15D1487654321NO.8实验电路结构图SPEAKER 扬声器目标芯片PIO39-PIO36PIO43-PIO40PIO47-PIO44预置串行输入数DCBADCBAD1D2D3D4D5D6D7D8译码器译码器译码器单脉冲HEX HEX HEX单脉冲PIO9PIO11PIO8PIO15-12PIO7-4PIO3-0HEX HEX 键1键2键3键4键5键6键7键8图3-7 电路结构图NO.8CLOCK9CLOCK5CLOCK2CLOCK0NO.9实验电路结构图目标芯片FPGA/CPLD S P E A K E R扬声器87654321D1D2D3D4D5D6D7D8D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16PIO15-PIO8PIO15PIO14PIO13PIO12PIO11PIO10PIO9PIO8译码器译码器译码器译码器译码器译码器译码器译码器单脉冲单脉冲单脉冲单脉冲单脉冲单脉冲单脉冲单脉冲PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8图3-8 电路结构图NO.9CLOCK0CLOCK2CLOCK5CLOCK9目标芯片F PG A /C P L D 拨码开关滤波1A /D 使能比较器5t h 使能R O M 使能ON87654321转换结束D S 8使能拨码1:ROM/RAM 使能,即它们的CS1接地拨码8:DAC0832输出滤波使能拨码7:ADC0809使能,默认关闭,见左图拨码6:ADC0809转换结束使能,见左图拨码5:应用LM311使能,见下图拨码4:8数码管显示开关,默认打开拨码2:默认关闭 向上拨,由厂家通知升级VS (PIO65)HS (PIO64)B (PIO63)G (PIO61)R (PIO60)1054876321 视频接口VGA J6R78 200R77 200R76 2001413PIO77PIO76PS/2下接口PS/2上接口VCCGNDPIO45PIO46513J74VCCGND5134PIN31->A15 )PIN29->WE ,29C040(PIN31->WE,PIN1->A18,P29->A14)27010(PIN30->VCC,PIN3->A15,PIN29->A14)27020(PIN30->A17,PIN3->A15,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN30->A17,PIN3->A15,PIN29->A14)注意,PIO62 同时是键11的信号线PIO62RAM/ROM 使能A I N 1VCC10K VR1拨码7拨码6A I N 0P I O 8(23)(24)1216272610C L O C K 750K H Z A 021+5V r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T(拨码1:“ROM 使能 ON”即将CS1接地)628128(PIN30->VCC,PIN3->A14,(拨码8:“滤波1 ON”即连接滤波电容)滤波1103连接PIO37与COMP )(拨码5:“比较器ON”即7.2K PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+551pFC27COMPLM311VCC10K -12+124823TL082/1AIN0AOUT5.1KR72765TL082/2841+12-12COMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CSWR2XFERA GNDD GND VREF8VCC20VCCD1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8GNDVCCPIO49RAM/ROMA18/A19A18/A15/WE PIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCCA17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GNDD2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A16图3-9 电路结构图NO.5CLOCK9CLOCK5CLOCK2CLOCK0PIO8D11D12PIO9D13PIO10D14PIO11D15PIO12PIO13D16D6D5D4D3D2D1D7D8)(12345678实验电路结构图NO.6目标芯片FPGA/CPLD 扬声器S P E A K E RPIO3-PIO0PIO7-PIO4HEX HEXPIO16PIO13-PIO8PIO23PIO22PIO21PIO20PIO19PIO18PIO17直接与7段显示器相接PIO46-PIO40PIO38-PIO32PIO30-PIO24PIO22-PIO16PIO46-PIO40 接 g, f, e , d, c, b, aPIO38-PIO32 接 g, f, e , d, c, b, aPIO30-PIO24 接 g, f, e , d, c, b, a 七段PIO22-PIO16 接 g,f,e,d,c,b,a键1键2键3键4键5键6键7键8图3-10 电路结构图NO.6图3-11 8位数码管扫描式显示电路(输入信号高电平有效)D+(PIO65)D-(PIO64)GNDVCCSLAVEUSB PIO65PIO64OO O O选择开关T O F P G A T O M C U键复位接PC 机串行通讯接口接口电路235RS-232B4P27P26P25P24P23P22P21P20PSEN ALE EA P07P06P05P04P03P02P01P00VCC A T 89C 5140393837363534333231302928272625242223212019181716151413121110987654321GNDX1X2PIO66PIO67PIO77PIO76PIO79PIO78P31P30RESET PIO75PIO74PIO73PIO72PIO71PIO70PIO69PIO68LCD液晶显示屏VCC GND P22P21P20P00P01P02P03P04P05P06P07P23P241234567891011121314151617181920图3-12 液晶与单片机以及FPGA 的I/O 口的连接P82P62P61P59P57P55P53P28P26EP1C3目标板插座EP1C6/12目标板插座P100P124P126P128P130P123P125P127P94P91P79P60P58P56P54P31P27PIO26PIO28PIO30PIO32PIO34PIO36PIO38目标板插座22423PIO27PIO29PIO31PIO33PIO35PIO37GND NC clk0+12V -12V NC 2423GND VCC VCCIO 21o o o o o o o o o o o o oo o o o o o o o o o o 21o o o o o o o o o o o o o o o o o o o o o o o o PIO26PIO28PIO30PIO32PIO34PIO36PIO38PIO39PIO40PIO42PIO44PIO462423PIO27PIO29PIO31PIO33PIO35PIO37GND NC PIO41PIO43PIO45clk0+12V -12V P177P144P143P175NC P156P193P194P207P2082423GND VCC VCCIO P5P23P11P178P179P213P214P227P22821o o o o o o o o o o o o oo o o o o o o o o o o 21o o o o o o o o o o o o o o o o o o o o o o o o图3-13 GW_ADDA 板插座引脚ASDODATA0nCONFIG CONF_DONEDCLKGNDnCSO nCE VCCIO ByteBlast II 在线编程座GND o o o o ooo o o o 在线编程座ByteBlast(MV)SEL1SEL0GNDTDInSTA TMS TDO TCK o o o o ooo o o o 主板右数第2、3列“目标板插座”信号相同2.5V3.3V 1.8V -12V +12V PIO79PIO78PIO75PIO74PIO73PIO72PIO71PIO70PIO69PIO68CON2CON1PIO77PIO76PIO67PIO66PIO65PIO64PIO63PIO62PIO61PIO60oo o o o o o o o o oo o o o o o o o o SEL1SEL0o o o o o o o o o o 目标板插座14039PIO24PIO22PIO20PIO18PIO16PIO14PIO12PIO10PIO8PIO6PIO4nSTA PIO0PIO2VCCPIO25PIO23PIO21PIO19PIO7PIO17PIO15PIO13PIO11PIO9PIO5PIO3PIO1o o o o o o o o o o o o o o o o o o o o o o o o o GND TCK TDO TMS TDI o o o o o 目标板插座24039PIO27PIO26PIO29PIO31PIO33PIO35PIO37PIO39PIO41PIO43PIO45PIO47PIO49CLOCK0CLOCK2GND PIO28PIO30PIO32PIO34PIO36PIO38PIO40PIO42PIO44PIO46PIO48SPEAKER CLOCK5CLOCK9VCC ooo o o o o o o o o o o o o o o o o o o o o o o o o o o o o o oo oo oo o o图3-14 目标芯片万能适配座CON1/2图3-15 编程下载接口附录二 超高速A/D 、D/A 板GW_ADDA 说明GW_ADDA 板含两片10位超高速DAC (转换速率最高150MHz )和一片8位ADC (转换速率最高50MHz ),另2片3dB 带宽大于260MHz 的高速运放组成变换电路。