k60核心板调试引脚连接说明

K60-02节

K60系列的存储器空间地址映像(一)

地址范围 0x0000_0000~0x0FFF_FFFF 0x1000_0000~0x13FF_FFFF 大小 实际的物理对象 256MB 可编程flash和只读数据(包括一开始1024字节的异常中 断向量) 64MB 对MK60N256VLQ100芯片:未使用 对MK60X256VLQ100芯片:FlexNVM 对MK60N512VLQ100芯片:未使用 对MK60N256VMD100芯片:未使用 对MK60X256VLQ100芯片:FlexNVM 对MK60N512VMD100芯片:未使用

256

512 512

256

256 512

—

4 —

64

64 128

100

100 100

2.4 K60系列微控制器的存储器映像与编程结构

2.4.2 K60系列存储器映像 ARM Cortex-M4为32位处理器内核。内部的数据是32位 的,寄存器是32位的,存储器接口也是32位的。

CPU频 率 (MHz) 100 100 100 120 150 120 150 闪存 (KB) 256 512 256 512 512 1024 1024 FlexNV M (KB) — — 256 512 512 — — SRAM (KB) 64 128 64 128 128 128 128 FlexRA M (KB) — — 4 16 16 — — 100 LQFP 14× 14 + + + — — — — 104 BGA 8× 8 + + + — — — — 144 LQFP 20× 20 + + + + + + + 144 BGA 13× 13 + + + + + + + 196 BGA 15× 15 — — — + + + + 256 BGA 17× 17 — — — + + + +

K60(Rev6-Ch38-PDB)(中文)

第38章可编程延时模块(Programmable Delay Block,PDB)注意:有关此模块的特定芯片的实现详细信息实例,请参阅芯片配置一章。

38.1 概述PDB可以为内部或外部触发源提供可控制的延时,可以为ADC的硬件触发输入或为DAC的产生提供可编程的间隔。

这样就可以为ADC转换和DAC输出的完成提供精确的时间。

PDB模块还可以提供脉冲输出,就跟CMP模块中的采样窗口一样。

38.1.1 特性1.多达15种输入触发中断源和软件触发中断源2.多达8路的可配置PDB通道一个PDB模块对应一个ADC为每个PDB 通道ADC 触发器选择一个触发器输出的ADC 硬件触发器和多达8 个预输出每个输出有一个16位的延时寄存器可选的旁路电阻运行模式有单次触发模式和连续模式背靠背模式,可以使得ADC转换完成后触发下个PDB通道可编程的延时中断顺序错误中断每个触发器有一个通道标志和一个顺序错误标志支持DMA3.高达8路的DAC内部触发源每个DAC模块有一个内部触发输出每个DAC触发输出有一个16位的内部延时寄存器可选旁路延迟时间间隔触发寄存器可选的外部触发源4.高达8路的脉冲输出脉冲输出可以独立的使能或禁止脉宽可调注意:PDB 的数量的输入和输出出发是与特定芯片有关的。

详细信息请参阅芯片配置信息。

38.1.2 实现下面的字母表示触发数量:1.N-总的可用的PDB通道数2.n-PDB通道号,范围0~N-13.M-每个PDB通道的总得可用的触发器4.m-触发号,范围0~M-15.X-总的DAC内部触发数量6.x-DAC内部触发号,范围0~X-17.Y-总的脉冲输出8.y-脉冲输出号,范围0-Y-1注意:模块输出的数量触发的核心是与特定芯片的。

输出触发执行的核心模块,请参阅芯片配置信息。

38.1.3 背靠背的确认连接PDB背靠背操作确认连接是与具体芯片有关的。

关于实现,参考芯片配置说明。

38.1.4 DAC外部触发输入连接DAC的外部触发输入连接的实现是与具体芯片有关的。

K60功能介绍

一、超低功耗:1. 10 种带有功率和时脉闸控的低功耗模式,可优化外围设备活动和恢复时间。

停止电流<500 nA,运行电流<200 uA/MHz,停止模式唤醒时间4μs。

2. 完整内存,模拟运行可降至1.71V,令电池寿命延长。

3. 低漏电唤醒单元,可带有8 个内置模块和16 个引脚,作为低漏电停止(LLS)/超低漏电停止(VLLS) 模式的唤醒源。

4. 低功耗定时器支持在低功耗状态下系统的持续运行。

二、闪存、SRAM和FlexMemory5. 256 KB-1 MB闪存。

快速接入、高可靠性具备四级安全保护6. 64 KB-128 KB SRAM7. FlexMemory:32 字节- 16 KB 用户可分段的字节写入/清除EEPROM,适用于数据表/系统数据。

EEPROM 具有超过10M 的周期和70 μsec 写入时间的闪存(出现电力故障时不会发生数据丢失或损坏)。

没有用户或系统干预便可完成编程和清除功能,完全运行状态下可降至 1.71V。

此外,从256KB-512KB 的FlexNVM 还适用于额外编程代码、数据或EEPROM 备份三、混合信号功能:8. 多达四种可配置分辨率的高速16位ADC。

可采用单路或差分输出模式改善噪声抑制。

可编程延迟块触发功能转换时间可达500 ns9. 多达两个12位DAC可用于音频应用模拟波形生成10. 具有3 个高速比较器,通过将PWM 保持在安全状态,提供快速准确的电机过电流保护。

11. 多达四个64倍可编程增益放大器用于小型振幅信号转换12. 模拟基准电压为模拟块、ADC 和DAC 提供精确的基准值,可以替换外部基准电压,降低系统成本。

四、性能:13. ARM Cortex-M4 内核+ DSP。

100-180MHz、单周期MAC、单指令多数据(SIMD) 扩展、可选的单精度浮点单元。

14. 具有32 通道的DMA 适用于外围设备和内存,可降低CPU 负载,实现更快的系统吞吐量。

K60(Rev6-Ch11-PORT)(中文)

第54章通用输入输出(GPIO)54.1 引言处理器使用零等待方式,以最高性能访问通用输入输出(General Purpose Input and Output,GPIO)模块接口。

GPIO寄存器支持任意长度的数据访问。

当引脚被配置为GPIO功能时,GPIO数据方向寄存器与输出数据寄存器控制每个引脚的方向及输出数据。

当GPIO引脚被配置为任意数字功能时,GPIO输入数据寄存器在每个引脚上显示逻辑值,提供相应的端口控制和对有效引脚的中断模块。

通过对于每个端口输出数据寄存器的额外设置、清除和触发写寄存器,通用输出的有效位被支持。

54.1.1 特点●快速的通用输入输出⏹在所有数字引脚重用模式中,输入数据寄存器引脚可见。

⏹带有相应的设置/清除/触发寄存器的输入数据寄存器引脚⏹数据方向寄存器引脚⏹以零等待状态访问GPIO寄存器54.1.2 操作模式54.1.2.1 运行模式在运行模式,GPIO正常运行。

54.1.2.2等待模式在等待模式,GPIO正常运行。

54.1.2.3停止模式在停止模式中,GPIO无效,尽管引脚仍然保持它们的状态。

54.1.2.4 调试模式在调试模式中,GPIO正常运行。

54.1.3 GPIO引脚描述表54-1 GPIO信号描述注:并不是每个设备的每个端口上的所有引脚都是可用的。

54.1.3.1 详细的GPIO引脚说明表54-2 GPIO详细的接口信号描述54.2 内存映射与寄存器定义任何对GPIO内存空间以外的合法空间地址的任意读写访问都将会导致总线错误。

带有零等待状态的所有寄存器访问完成,除了带有一个等待状态的错误访问。

GPIOx_PDOR域描述54.2.2 端口设置输出寄存器(GPIOx_PSOR)GPIOx_PCOR域描述54.2.4 端口触发输出寄存器(GPIOx_PTOR)GPIOx_PDIR域描述54.2.6 端口数据方向寄存器(GPIOx_PDDR)PDDR配置个别的端口引脚来作为输入或者输出。

(完整word版)k60单片机最小系统引脚介绍

野火k60学习——IO口的编程2013-03-03 20:06:20| 分类: 【飞思卡尔】Free|举报|字号订阅GPIO的含义查阅技术手册Chapter 55——General-Purpose Input/Output (GPIO)通用输入/输出iar如何做仿真要使用仿真调试, 首先就要在选项里设置调试器为软件仿真:软件仿真工程右键选项调试器驱动改为仿真即可另外还要禁止锁相环时钟设置和串口发送, 不然仿真的时候, 会卡在死循环里, 不能继续调试。

实验中, 卡死在CPSIE i ; Unmask interrupts 关中断由于不知道如何禁止锁相环时钟设置和串口发送, 故先暂时放下。

GPIO模块函数说明:初始化, 哪个管脚, 输入输出, 高低(低为亮)gpio_init (PORTx, n, GPO/GPO, HIGH/LOW);gpio_set(PORTD, 14, level);level = gpio_get(PORTD, 15);gpio_turn(PORTD, 13);其他查阅头文件define 后面不区分大小写?#define GPIO_SET(PORTx,n,x) GPIO_SET_##x((PORTx),(n))//设置输出电平x, x为0或1 例如GPIO_SET(PORTA,1,1) PA1输出高电平#define GPIO_TURN(PORTx,n)(GPIO_PDOR_REG(GPIOx[(PORTx)]) ^= (1<<(n))) //翻转输出电平#define GPIO_Get(PORTx,n)((GPIO_PDIR_REG(GPIOx[(PORTx)])>>(n))&0x1) //读取引脚输入状态例程学习闪烁LED初始化, 哪个管脚, 输入输出, 高低(低为亮)gpio_init (PORTx, n, GPO/GPO, HIGH/LOW);高低切换, 为何不用turn函数, 取反、延时更简单while(1){PTD15_OUT = 0; //低电平点亮LED3time_delay_ms(500); //延时500msPTD15_OUT = 1; //高电平熄灭LED3time_delay_ms(500); //延时500ms}读写测试/************************************************************************* * 野火嵌入式开发工作室* GPIO实验并行读写测试* 实验说明: 野火GPIO实验, 利用LED来显示电平高低** 实验操作: PTD15和PTD13短接, PTD14和PTD12短接** 实验效果: LED0、LED2和LED1.LED3 轮流间隔500ms 闪烁** 实验目的: 明白如何并行读写数据** 修改时间: 2012-3-6 已测试** 备注: 野火Kinetis开发板的LED0~3 , 分别接PTD12~PTD15 , 低电平点亮*************************************************************************/ void main(void){u32 value; //保存读取PTD12~PTD15 的值gpio_init (PORTD, 15, GPO, HIGH); //初始化PTD15 : 输出高电平,即初始化LED3, 灭gpio_init (PORTD, 14, GPO, LOW); //初始化PTD14 :输出高电平,即初始化LED2, 灭gpio_init (PORTD, 13, GPI, HIGH); //初始化PTD13 : 输入gpio_init (PORTD, 12, GPI, HIGH); //初始化PTD12 : 输入while(1){value = GPIO_GET_2bit(PORTD, 12); //读取PTD13~PTD12的值if(value & (~0x0f))while(1); //如果高位非0, 则死循环。

K60各模块入门培训教程

北京理工大学智能车俱乐部程序培训K60各模块入门前言这个小文档是对k60单片机的各模块进行了初步的介绍,以便大家在之后车队的k60实际培训演示中能更好地理解,能更快的上手单片机,另外说一下车队用的K60单片机型号是MK60DN512ZVLL10,不同型号的k60单片机各模块基本操作有些小区别。

本文档是基于给大家实际演示的各模块功能来撰写的,里面讲的各个模块在以后的做车过程中基本上都会用到。

实际上一个智能车上所实现的功能都是由这些最基本的小模块组合而成的,把这些小模块各个击破了,都理解了,以后看智能车的整体程序也就容易得多了~另外注意:在我没实际操作讲解之前,大家看这些模块的时候可以不用纠结一些细节的问题,大致有个概念即可~在我讲的时候好好听我讲各个模块的例程,做好笔记,然后看实验现象,进行进一步的理解。

之后自己再回去仔细看例程、笔记和这个文档,并且自己可以对程序进行一些改动,然后烧写程序看现象仔细研究。

PS:我们第十届包括之前的学长们都没有进行这样专门的比较系统的单片机各模块的培训,也没有学长们亲自给我们写这些入门的学习文档,基本都是自己去查资料学习,所以你们这一届算是很走运的了!不要错失良机不好好学习哦~话说回来,毕竟车队是一年比一年进步嘛,培训会慢慢地变得更加有条理!还有你们明年培训下一届的时候也是哦学完了单片机各个模块后,以后你们要是想对车进行哪个模块的调试不会出现不知道程序在哪、不知道怎样去调试这些最基本、较Low的问题~你们对各个模块理解透了,智能车整体的程序架构你们会轻而易举的掌握。

以后想调那个模块调哪个,整个程序也不会乱,以后要在车上增加新模块新功能也会容易得多!所以......仓鼠们打起精神~好好学吧!!!第十届摄像头游清目录一、GPIO模块 (5)1、GPIO概述 (5)2、I/O口的使用方法 (6)二、FTM占空比(PWM)模块 (9)1、PWM概述 (9)2、PWM程序讲解 (10)三、中断模块 (13)1、中断概述 (13)2、GPIO(I/O)口外部中断 (13)2.1I/O口外部中断概述 (13)2.2I/O口外部中断程序讲解 (14)3、PIT定时器中断 (16)3.1PIT定时器中断概述 (16)3.2PIT定时器中断程序讲解 (16)四、A/D(模数)转换模块 (18)1、A/D模块概述 (18)2、A/D模块程序讲解 (19)五、串口通信(UART)模块 (21)1、串口(UART)模块概述 (21)1、串口(UART)模块程序讲解 (22)后记 (25)一、GPIO模块车队用的K60单片机有100个引脚,如下图:其中大部分引脚有GPIO模块的功能,GPIO模块可以输出指定的高低电平,或读入输入电平,在实际智能车上可以用于调试用的小灯、蜂鸣器、拨码开关和摄像头信号数据采集及外部中断等。

K60 SPI

32

存器(主机模式)

(SPI2_CTAR1)

400A_C02C

DSPI 状 态 寄 存 器

32

(SPI2_SR)

400A_C030

DSPI DMA/中断请求选择

32

与使能寄存器(SPI2_RSER)

400A_C034

DSPI PUSH发送队列寄存

32

器(主机模式)(SPI2_PUSHR)

400A_C034

第49章 SPI(DSPI)

49.1 导言

串行设备接口(serial peripheral interface ,SPI)模块包含一个在 MCU 和一个外 部设备之间进行通信的同步串行总线。

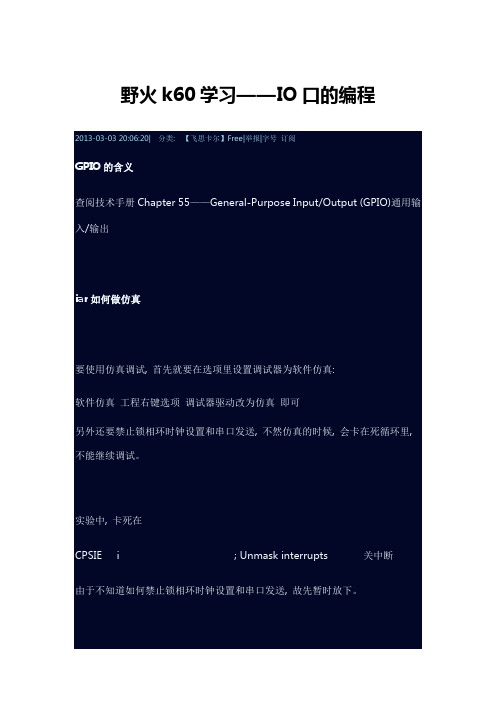

49.1.1 框图

SPI(DSPI)的框图如下所示:

图 49-1 DSPI框图

49.1.2 特性

DSPI 支持三种 SPI 特性: •全双工,三线同步传输 •主机与从机模式

(SPI1_RXFR1)

4002_D088

DSPI 接 收 队 列 寄 存 器

32

(SPI1_RXFR3)

R

0000_0000

R

0000_0000

R/W

0000_4001

R/W

0000_0000

R/W

7800_0000

R/W

7800_0000

R/W

7800_0000

R/W

0000_0000

R/W

0000_0000

(SPI0_TCR)

4002_C00C

DSPI 时钟与 传输 属性 寄

32

R/W

7800_0000

存器(主机模式)

(SPI0_CTAR0)

k60单片机最小系统引脚介绍

野火k60学习——IO口的编程2013-03-03 20:06:20| 分类:【飞思卡尔】Free|举报|字号订阅GPIO的含义查阅技术手册Chapter 55——General-Purpose Input/Output (GPIO)通用输入/输出iar如何做仿真要使用仿真调试,首先就要在选项里设置调试器为软件仿真:软件仿真工程右键选项调试器驱动改为仿真即可另外还要禁止锁相环时钟设置和串口发送,不然仿真的时候,会卡在死循环里,不能继续调试。

实验中,卡死在CPSIE i ; Unmask interrupts 关中断由于不知道如何禁止锁相环时钟设置和串口发送,故先暂时放下。

GPIO模块函数说明:初始化,哪个管脚,输入输出,高低(低为亮)gpio_init (PORTx, n, GPO/GPO, HIGH/LOW);gpio_set(PORTD, 14, level);level = gpio_get(PORTD, 15);gpio_turn(PORTD, 13);其他查阅头文件define 后面不区分大小写?#define GPIO_SET(PORTx,n,x) GPIO_SET_##x((PORTx),(n))//设置输出电平x,x为0或1 例如GPIO_SET(PORTA,1,1) PA1输出高电平#define GPIO_TURN(PORTx,n)(GPIO_PDOR_REG(GPIOx[(PORTx)]) ^= (1<<(n))) //翻转输出电平#define GPIO_Get(PORTx,n)((GPIO_PDIR_REG(GPIOx[(PORTx)])>>(n))&0x1) //读取引脚输入状态例程学习闪烁LED初始化,哪个管脚,输入输出,高低(低为亮)gpio_init (PORTx, n, GPO/GPO, HIGH/LOW);高低切换,为何不用turn函数,取反、延时更简单while(1){PTD15_OUT = 0; //低电平点亮LED3time_delay_ms(500); //延时500msPTD15_OUT = 1; //高电平熄灭LED3time_delay_ms(500); //延时500ms}读写测试/************************************************************************* * 野火嵌入式开发工作室* GPIO实验并行读写测试* 实验说明:野火GPIO实验,利用LED来显示电平高低** 实验操作:PTD15和PTD13短接,PTD14和PTD12短接** 实验效果:LED0、LED2和LED1、LED3 轮流间隔500ms 闪烁** 实验目的:明白如何并行读写数据** 修改时间:2012-3-6 已测试** 备注:野火Kinetis开发板的LED0~3 ,分别接PTD12~PTD15 ,低电平点亮*************************************************************************/ void main(void){u32 value; //保存读取PTD12~PTD15 的值gpio_init (PORTD, 15, GPO, HIGH); //初始化PTD15 :输出高电平,即初始化LED3,灭gpio_init (PORTD, 14, GPO, LOW); //初始化PTD14 :输出高电平,即初始化LED2,灭gpio_init (PORTD, 13, GPI, HIGH); //初始化PTD13 :输入gpio_init (PORTD, 12, GPI, HIGH); //初始化PTD12 :输入while(1){value = GPIO_GET_2bit(PORTD, 12); //读取PTD13~PTD12的值if(value & (~0x0f))while(1); //如果高位非0,则死循环。

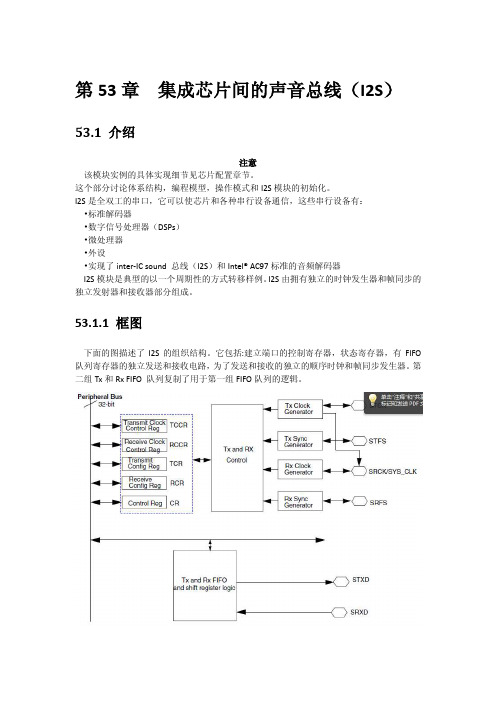

K60(Rev6-Ch53-I2S)(中文)

应用

异步

连续

正常

多个同步编解码器

异步

连续

网络

TDM 编解码器或 DSP 网络

同步

连续

正常

多个同步编解码器

同步

连续

网络

TDM 编解码器或 DSP 网络

同步

门控

正常

SPI 类型设备:DSP 到 MCU

列可以用于网络模式从而为发送和接收提供两个独立的通道 •可编程数据接口模式,例如 I2S, lsb- and msb-aligned •可编程单词长度(8, 10, 12, 16, 18, 20, 22 or 24 位) •用于帧同步和时钟发生器的编程选项 •可编程的 I2S 模式(主,从,正常) •在 I2S 的主模式下过采样时钟作为 SRCK 的输出 •AC97 支持 •用于发送和接收部分的完全独立的时钟和帧同步选择。在 AC97 标准中时钟来自外部

53.2 I2S 的信号说明

表 53-2 I2S 的信号说明

信号

说明

I/O

SRCK

串行接收时钟。SRCK 可被用于输入或输出:

I/O

•在异步模式下,接收器使用这个时钟信号,它总是连续的

•在同步模式下,STCK 端口用来代替时钟数据

信号 SRFS

说明

I/O

串行接收帧同步。SRFS 端口可用于输入或输出。接收器使用帧同步来同步数 I/O

寄存器位的详细信息和字段功能以位顺序紧跟寄存器图表。

I2S 内存映射

绝 对 地 址 寄存器名

宽 度 访 问 复位值

段/页

(hex)

(位) 权限

K60核心板说明与扩展板_SD-Ex-D_对接说明

K60核心板说明与扩展板(SDExD)对接说明 1、核心板引脚说明K60一共有100个GPIO口,还有其他为复用的非GPIO口,如USB、ADC 等引脚。

核心板引出了所有的GPIO和其他非K60最小系统的引脚。

具体的引脚如下。

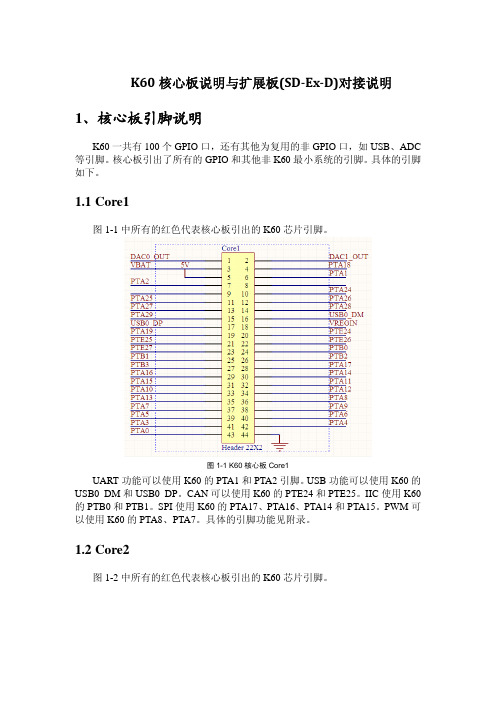

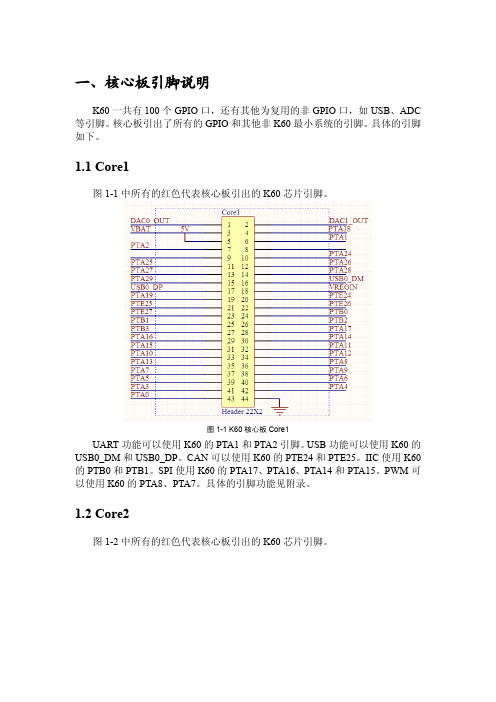

1.1 Core1图1-1中所有的红色代表核心板引出的K60芯片引脚。

图1-1 K60核心板Core1UART功能可以使用K60的PTA1和PTA2引脚。

USB功能可以使用K60的USB0_DM和USB0_DP。

CAN可以使用K60的PTE24和PTE25。

IIC使用K60的PTB0和PTB1。

SPI使用K60的PTA17、PTA16、PTA14和PTA15。

PWM可以使用K60的PTA8、PTA7。

具体的引脚功能见附录。

1.2 Core2图1-2中所有的红色代表核心板引出的K60芯片引脚。

图1-2 K60核心板Core2可以使用K60的ADC1_SE16和ADC0_SE16。

具体的引脚功能见附录。

1.3 Core3图1-3中所有的红色代表核心板引出的K60芯片引脚。

图1-3 K60核心板Core3具体的引脚功能见附录。

2、核心板与大板对接在设计电路时,考虑到与旧的扩展板兼容,做了如下设计,保证K60核心板与扩展板兼容。

以下图片中的蓝色表示大板的功能,红色代表核心板引出引脚。

2.1 Core1图2-1 Core1引脚定义2.2 Core2LCD使用K60的PTE可以实现,具体功能见参考代码。

图2-2 Core2引脚定义AD5和AD9分别接K60的ADC1_SE16和ADC0_SE16。

2.3 Core3可以使用K60的PTC口实现LED功能,具体实现见参考代码。

图2-3 Core3引脚定义3、附录:144引脚资源简明表3.1 硬件最小系统引脚K60N512VM100芯片电源类引脚,BGA封装22个,LQFP封装27个,其中BGA 封装的芯片有五个引脚未使用(A10、B10、C10、M5和L5)。

K60核心板说明与扩展板(SD-Ex-D)对接说明

一、核心板引脚说明K60一共有100个GPIO口,还有其他为复用的非GPIO口,如USB、ADC 等引脚。

核心板引出了所有的GPIO和其他非K60最小系统的引脚。

具体的引脚如下。

1.1 Core1图1-1中所有的红色代表核心板引出的K60芯片引脚。

图1-1 K60核心板Core1UART功能可以使用K60的PTA1和PTA2引脚。

USB功能可以使用K60的USB0_DM和USB0_DP。

CAN可以使用K60的PTE24和PTE25。

IIC使用K60的PTB0和PTB1。

SPI使用K60的PTA17、PTA16、PTA14和PTA15。

PWM可以使用K60的PTA8、PTA7。

具体的引脚功能见附录。

1.2 Core2图1-2中所有的红色代表核心板引出的K60芯片引脚。

图1-2 K60核心板Core2可以使用K60的ADC1_SE16和ADC0_SE16。

具体的引脚功能见附录。

1.3 Core3图1-3中所有的红色代表核心板引出的K60芯片引脚。

图1-3 K60核心板Core3具体的引脚功能见附录。

二、核心板与大板对接在设计电路时,考虑到与旧的扩展板兼容,做了如下设计,保证K60核心板与扩展板兼容。

以下图片中的蓝色表示大板的功能,红色代表核心板引出引脚。

2.1 Core1图2-1 Core1引脚定义2.2 Core2LCD使用K60的PTE可以实现,具体功能见参考代码。

图2-2 Core2引脚定义AD5和AD9分别接K60的ADC1_SE16和ADC0_SE16。

2.3 Core3可以使用K60的PTC口实现LED功能,具体实现见参考代码。

图2-3 Core3引脚定义。

K60 Nano核心板用户手册

K60 Nano核心板用户手册版本0.1用户手册目录1.K60 Nano板整体介绍 (3)1.1.板载资源 (3)1.2.核心板引脚 (5)2.第一次测试Nano板 (6)2.1.上电测试 (6)2.2.观察LED灯 (7)2.3.观察串口信息 (7)3.快速开发指南 (7)3.1.开发包目录说明 (8)3.2.运行一个示例工程 (9)3.3.更改内核频率 (11)3.4.用模板新建一个工程 (11)4.利用Bootloader给Nano板下载 (13)1.K60 Nano板整体介绍“K60 Nano板”是拉普兰德电子技术独家设计的一款专门应用于飞思卡尔智能车竞赛的最小系统板。

之所以命名为“ Nano板”,是因为他是目前市场上同类产品中尺寸最小的产品,大小仅为5.5cm*3.5cm的PCB板上板载了LQFP-144封装的K60单片机!该核心板不仅在尺寸上占有优势,更集成了其他核心板不具有的功能,如Micro-SD卡座、USB接口等等!K60 Nano核心板整体采用白色PCB板与白色塑胶插针组合,焊盘均为沉金工艺!使得该板不仅在功能上领先同类,更在外观上出类拔萃!该最小系统板的整体照片如图1所示。

该最小系统板的原理图请见文档“K60 Nano核心板原理图”。

图1. K60 Nano板整体概览1.1.板载资源K60 Nano板具有一个JTAG 10Pin仿真/下载接口,引脚数为2x5个,插针距离为标准的100Mil(2.54mm)排针间距。

用户可以使用J-Link V8下载器配合转接板给核心板下载程序。

注意,如果用户需要给Nano板下载程序,必须给板子供电,因为Jlink下载器在默认情况下不能为目标板输出电源。

JTAG接口原理图如图2所示。

小提示:由于采用复合插针,因此该JTAG引脚奇偶对调。

图2. JTAG接口K60 Nano板搭载了4个LED灯,方便开发者调试时指示各种状态,或测试IO口。

这8个LED灯分别与K60芯片的PTA4、PTA6、PTA8和PTA10相连,当IO口为低电平时,对应的LED点亮。

Kinetis K60核心板套件用户手册V2.0

通联物网Kinetis K60 Cortex ™-M4 核心板+扩展板用户手册(ARM ® Cortex ™-M4 V2.0)北京通联物网教育咨询有限公司更新说明1、本次更新为2.0版本2、本次更新了K60套板的全部基础案例,共计59个案例。

后续基于KL04的传感器模块基础实验会不断更新到本文档目录更新说明 (2)目录 (3)一、Kinetis K60 Cortex ™-M4 (4)二、产品介绍 (6)1、产品简介 (6)2、开发板硬件资源 (10)2.1、核心开发板硬件资源 (10)2.2、通用扩展开发板硬件资源 (11)2.3 K60 核心板+通用扩展板配套光盘资料 (12)2.4 K60 核心板+扩展板C语言代码实验案例 (13)三、实验案例操作方法 (13)3.1搭建开发环境 (13)3.2安装串口转USB接口驱动 (15)3.3建立实验调试“超级终端”环境 (15)3.4注意事项及建立IAR6.3调试环境 (18)3.5基础案例 (23)一、Kinetis K60 Cortex ™-M4核心板+扩展板及配件照片:图1-1 K60/K10 核心板(正面)图1-2 K60/K10 核心板(反面)图1-3 K60 完全版扩展板(正面)图1-4 K60/K10 核心板+简化扩展板+JLINK 仿真器连接图图1-5 JLINK V8 仿真器二、产品介绍1、产品简介Cortex-M 系列内核是ARM 公司针对低功耗和高性能的嵌入式控制市场而开发的内核。

Cortex-M0 和Cortex-M3 系列芯片广泛的应用于智能仪表、智能卡、智能家电、智能玩具、短距离联网应用(Zigbee 和NFC)、汽车电子和高效电机控制等领域。

ST、TI、NXP、Atmel 和东芝等芯片设计公司都已经推出Cortex-M3 的MCU。

Cortex-M4 是ARM 公司于2009 年下半年推出的内核,其性能比Cortex-M3 提高20%。

野火K60 测试说明书

野火K60核心板和调试板测试说明书欢迎使用野火 K60 核心板,现在让我们走近K60……目录野火K60核心板和调试板测试说明书 (1)1.K60 核心板资源介绍 (2)2.供电方式 (2)排针供电 (2)USB供电 (3)Jlink供电 (4)3.J-Flash下载固件 (7)4.野火鹰眼软排线转接板 (11)5.测试方案 (13)LED测试 (13)USB测试 (14)摄像头无线发送模式 (18)调试板测试模式 (20)1. K60 核心板资源介绍首先,拿到我们的野火K60核心板,先来熟悉我们的板载资源:图 1 野火核心板正面 图 2野火核心板背面2. 供电方式 排针供电野火K60核心板的排针,有专门的5V 电源输入和3.3V 电源输入管脚,两者可任意选择其中一个来进行供电。

如果是采用5V 供电,则通过板载的LDO 芯片转换为3.3V ,供控制器、无线模块、摄像头使用。

建议采用 5V 供电,板载专用的低压差线性LDO 更能保证电源的稳定。

LED 1~4 野火摄像头排线接口复位按钮NRF24L01+无线模块接口Micro USB 接口V5V 转3.3V50MHz晶振 预留给USB 转TTL 接口KEY 1 & 2 电源指示灯KEY 1 & 2 JLink 接口LED 1~43.3V 管脚 3.3V和5V 管脚供电后,此电源灯会亮图 3 核心板排针供电指示注意:不要把5V电源插入 3.3V 的排针座内!!!USB供电用micro USB 数据线(现在绝大部分的智能机都是用这类的数据线),一头接入核心板,另外一头接入电脑的USB口或者5V供电的带USB口充电器的口上。

比mini USB更加扁平的图 4 micro USB数据线图 5野火K60核心板USB 供电方式Jlink 供电野火K60 核心板使用标准的10PIN 插头,Jlink 默认不支持供电,但Jlink 虽然支持使用power on 和 power off 命令来实现供电,但仅仅适用于5V 供电,而且不适用于 10PIN 管脚。

K60(Rev6-Ch11-PORT)(中文)

11端口控制与中断11.1 简介有关此模块的特定芯片的应用详细信息实例,请参阅芯片配置章节。

11.1.1 概述端口控制与中断(PORT)模块支持外部中断、数字滤波和端口控制功能。

对于32位的端口的每个引脚都可以单独的配置其功能,大多数功能都能直接影响端口,而无需考虑多路复用状态。

本章描述是PORT模式的每个引脚的使用实例。

不是每个端口的所有引脚都在专用的设备上实现了这些功能。

11.1.2 特性1)引脚中断:(1)每个引脚有对应的中断标志位和使能寄存器;(2)可配置每个引脚为边沿触发(上升沿,下降沿)或电平触发(高电平,低电平)(3)支持配置每个引脚的中断和DMA请求;(4)支持低功耗模式下的异步唤醒;(5)在所有数字引脚的复用模式中可以使用引脚中断;2)数字输入滤波器:(1)每个引脚的数字滤波器可以被任何数组外围复用引脚使用;(2)每个引脚有独立的使能或屏蔽控制位;(3)数字输入滤波器的5位的可选时钟源决定滤波大小;(4)在所有数字引脚的复用模式的数字滤波器有效3)端口控制(1)独立的上拉电阻控制寄存器,选择上拉、下拉、不上拉;(2)独立的驱动能力寄存器,选择高驱动或低驱动;(3)独立的斜率寄存器,选择快速变化或缓慢变化;(4)独立的输入被动的过滤器寄存器,选择使能或禁止;(5)独立的开环寄存器,选择使能或禁止;(6)独立的复用控制功能寄存器,选择模拟量输入,GPIO等最多6个特殊的数字功能;(7)在所有数字引脚的复用模式中可以选择使用功能配置寄存器。

11.1.3 操作模式11.1.3.1 运行模式在运行模式下,PORT能正常工作。

11.1.3.2 等待模式在等待模式下,PORT仍正常工作。

而当检测到使能的中断时,可被配置退出低功耗模式。

DMA请求在等待模式下仍会产生,但不会退出低功耗模式。

11.1.3.3 停止模式在停止模式下,除非被配置成使用1kHz的LPO时钟源运行,否则数字输入过滤器功能将被屏蔽。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

黑龙江工业学院

电子设计工作室

飞思卡尔智能车竞赛经验总结

K60核心板与J-Link引脚连接说明。

下图为jlink引脚引脚功能表

(注意:jlink可以直接为核心板供电,2引脚提供3.3v电源,19引脚提供5v电源。

两个电源只能选择一个,通过将jlink的外壳打开里边有一个跳线帽来选择。

5v电源需要通过指令开启:power on开power off关)

K60的JTAG对应芯片引脚TMS—PtA3,TCK—PAT0,TDO—PTA2,TDI—PTA1,RESET--RESET。

Jlink与k60连接图

SW模式连接(强烈推荐)

Jlink引脚JTAG引脚(核心板已经引出对应下面原理图)

1 1 (核心板3.3V引脚)

7 2 (TMS)

9 4 (TCK)

15 10 (RESET)

GND(随便一个)9

JTAG模式

将剩下两个引脚连接到jlink对应引脚就行

软件调试界面看《IAR使用详解》文档。

IAR配置方法见《JLINK V8新用户手册中文版》的第18页说明。