MCP7383XEV-DIBC;中文规格书,Datasheet资料

3933中文资料

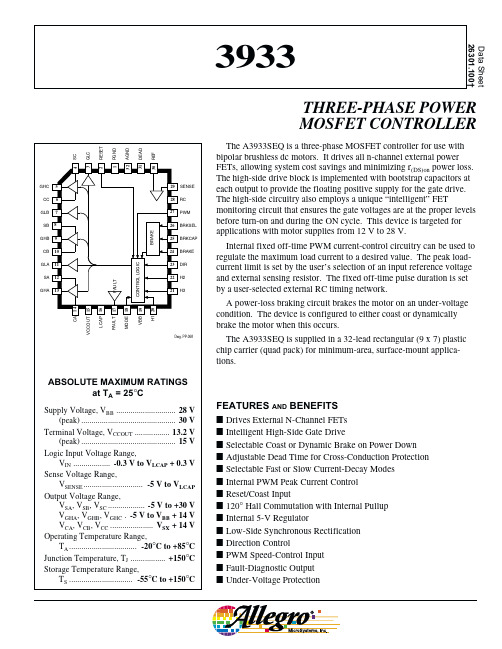

Data Sheet 26301.100†The A3933SEQ is a three-phase MOSFET controller for use with bipolar brushless dc motors. It drives all n-channel external power FETs, allowing system cost savings and minimizing r (DS)on power loss.The high-side drive block is implemented with bootstrap capacitors at each output to provide the floating positive supply for the gate drive.The high-side circuitry also employs a unique “intelligent” FETmonitoring circuit that ensures the gate voltages are at the proper levels before turn-on and during the ON cycle. This device is targeted for applications with motor supplies from 12 V to 28 V.Internal fixed off-time PWM current-control circuitry can be used to regulate the maximum load current to a desired value. The peak load-current limit is set by the user’s selection of an input reference voltage and external sensing resistor. The fixed off-time pulse duration is set by a user-selected external RC timing network.A power-loss braking circuit brakes the motor on an under-voltage condition. The device is configured to either coast or dynamically brake the motor when this occurs.The A3933SEQ is supplied in a 32-lead rectangular (9 x 7) plasticchip carrier (quad pack) for minimum-area, surface-mount applica-tions.3933FEATURES AND BENEFITSI Drives External N-Channel FETs I Intelligent High-Side Gate DriveI Selectable Coast or Dynamic Brake on Power Down I Adjustable Dead Time for Cross-Conduction Protection I Selectable Fast or Slow Current-Decay Modes I Internal PWM Peak Current Control I Reset/Coast InputI 120° Hall Commutation with Internal Pullup I Internal 5-V RegulatorI Low-Side Synchronous Rectification I Direction ControlI PWM Speed-Control Input I Fault-Diagnostic Output IUnder-Voltage ProtectionTHREE-PHASE POWER MOSFET CONTROLLER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-********THREE-PHASE POWER MOSFET CONTROLLERCopyright © 1999, Allegro MicroSystems, Inc.Functional Block DiagramRECOMMENDED OPERATING CONDITIONSSupply Voltage, V BB ...................................... 15 V to 28 Vor, if V BB = V CCOUT ................................... 12 V ±10%Logic Input Voltage Range, V IN .............. -0.3 V to +4.8 V Sense Voltage Range, V SENSE ........................ -1 V to +1 V RC Resistance.......................................... 10 k Ω to 100 k ΩPWM Frequency, f PWM ....................... 20 kHz to 100 kHzLOW-SIDE Dwg. FP-045V 1 OF 3 HIGH-SIDE DRIVERSTO 1 OF 3MOTOR PHASES TO LCAP3933THREE-PHASE POWER MOSFET CONTROLLERELECTRICAL SPECIFICATIONS at T A = 25°C, V BB = V CCOUT = 12 V, C load = 1000 pF, C boot = 0.047 µF (unless noted otherwise).LimitsParameterSymbolConditionsMinTypMaxUnitsSupply CurrentQuiescent Current I BB RESET low, f PWM = 40 kHz –1619mA RESET high–1517mA Reference Voltage V LCAP4.755.0 5.25V Ref. Volt. Load Regulation ∆V LCAP(∆ILCAP)I LCAP = 0 to -2 mA –1025mV Output VoltageV CCOUTV BB = 28 V10.81213.2V Output Voltage Regulation∆V CCOUT(∆ICCOUT)V BB = 28 V, I CCOUT = 0 to -10 mA––25mV Digital Logic LevelsLogic Input Voltage V IH 2.0––V V IL ––0.8V Logic Input CurrentI IH V IH = 2 V –<1.010µA I ILV IL = 0.8 V-70–-130µA Gate DriveLow-Side Output Voltage V GLxH 9.510.511.5V V GLxL I GLx = 1 mA––0.30V High-Side Output Voltage V GHxH 9.010.511.5V V GHxL I GHx = 1 mA ––0.25V Low-Side Output t rGLx 1 V to 8 V –50–ns Switching Time t fGLx 8 V to 1 V –40–ns High-Side Output t rGHx 1 V to 8 V –100–ns Switching Time t fGHx 8 V to 1 V –100–ns DEAD Timet DEADI DEAD = 10 µA –3000–ns (Source OFF to Sink ON)I DEAD = 215 µA –180–nsContinued —NOTES: 1.Typical Data is for design information only.2.Negative current is defined as coming out of (sourcing) the specified device terminal.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003933THREE-PHASE POWER MOSFET CONTROLLERELECTRICAL SPECIFICATIONS at T A = 25°C, V BB = V CCOUT = 12 V, C load = 0.001 µF, C boot = 0.047 µF (unless noted otherwise), continued.LimitsParameterSymbolConditions MinTypMaxUnitsBootstrap CapacitorBootstrap Charge Current I Cx 50100150mA Bootstrap Output Voltage V Cx Reference Sx9.510.511.5V Leakage CurrentI Cx High side switched high, Sx = V BB–1520µA Current LimitOffset Voltage V io –0±5.0mV Input bias current I SENSE ––-1.0µA RC Charge Current I RC 8509451040µA RC Voltage Threshold V RCL 1.0 1.1 1.2V V RCH 2.73.0 3.2V PWM frequency Rangef PWM Operating 20–100kHz Protection CircuitryUndervoltage Threshold UVLO Increasing V BB 9.710.210.7V Decreasing V BB 9.35–10.35V Boot-Strap Capacitor Volt.V CxSx V BB = 12 V 9.5––V High-Side Gate-Source Volt.V GHxSx – 6.3–V Fault Output VoltageV FAULT I O = 1 mA––0.8V Brake FunctionBrake Cap. Supply Current I BRKCAP V BB = 8 V, BRKSEL ≥ 2 V –30–µA Low-Side Gate VoltageV GLxHV BB = 0, BRKCAP = 8 V–6.6–VNOTES: 1.Typical Data is for design information only.2.Negative current is defined as coming out of (sourcing) the specified device terminal.3933THREE-PHASE POWER MOSFET CONTROLLERTerminalName1PGND 2RESET 3GLC 4SC 5GHC 6CC 7GLB 8SB 9GHB 10CB 11GLA 12SA 13GHA 14CA 15V CCOUT 16LCAP 17FAULT 18MODE 19V BB 20H121H322H223DIR 24BRAKE 25BRKCAP 26BRKSEL 27PWM 28RC 29SENSE 30REF 31DEAD 32AGNDRESET — A logic input used to enable the device, internally pulled up to V LCAP (+5 V). A logic HIGH will disable the device and force all gate drivers to 0 V, coasting the motor. A logic LOW allows the gate drive to follow commutation logic.This input overrides BRAKE.GLA/GLB/GLC — Low-side, gate-drive outputs for external NMOS drivers. External series-gate resistors (as close aspossible to the NMOS gate) can be used to control the slew rate seen at the power-driver gate, thereby controlling the di/dt and dv/dt of the SA/SB/SC outputs. Each output is designed and specified to drive a 1000 pF load with a rise time of 50 ns.SA/SB/SC — Directly connected to the motor, these terminals sense the voltages switched across the load. These terminals are also connected to the negative side of the bootstrap capaci-tors and are the negative supply connections for the floating high-side drive.GHA/GHB/GHC — High-side, gate-drive outputs for external NMOS drivers. External series-gate resistors (as close aspossible to the NMOS gate) can be used to control the slew rate seen at the power-driver gate, thereby controlling the di/dt and dv/dt of the SA/SB/SC outputs. Each output is designed and specified to drive a 1000 pF load with a rise time of 100 ns.CA/CB/CC — High-side connections for the bootstrap capaci-tors, positive supply for high-side gate drive. The bootstrap capacitor is charged to approximately V CCOUT when theassociated output SA/SB/SC terminal is low. When the output swings high, the voltage on this terminal rises with the output to provide the boosted gate voltage needed for n-channel power FETs.Terminal Descriptionscontinued next page115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003933THREE-PHASE POWER MOSFET CONTROLLERFAULT — Open-drain output to indicate fault condition; will go active high for any of the following:1 – invalid HALL input code,2 – high-side, gate-source voltage less than 7 V,3 – bootstrap capacitor not sufficiently charged, or4 – under-voltage condition detected at V CCOUT .The fault state for gate-source and bootstrap monitors are cleared at each commutation. If the motor has stalled, then the fault can only be cleared by toggling the RESET terminal or power-up sequence.MODE — A logic input to set current-decay method, internally pulled up to V LCAP (+5 V). When in slow-decay mode (logic HIGH), only the high-side FET is switched open during a PWM OFF cycle. The fast-decay mode (logic LOW) switches both the source and sink FETs.H1/H2/H3 — Hall-sensor inputs; internally pulled up to V LCAP (+5 V). Configured for 120° electrical spacing.DIR — A logic input to reverse rotation, see commutation logic table. Internally pulled up to V LCAP (+5 V).BRAKE — A logic input to short out the motor windings for a braking function. A logic HIGH will turn ON the low-side FETs, turn OFF the high-side FETs. Internally pulled up to V LCAP (+5 V). The braking torque applied will depend on the speed.BRKCAP — Connection for reservoir capacitor. This terminal is used to provide a positive power supply for the sink-drive outputs for a power-down condition. This will allow predict-able braking, if desired. A blocking diode to V CCOUT is re-quired. A 4.7 µF capacitor will provide 6.5 V gate drive for 300 ms. If a power-down braking option is not needed(BRKSEL = LOW) then this terminal should be tied to V CCOUT .BRKSEL — A logic input to enable/disable braking on power-down condition. Internally pulled up to V LCAP (+5 V). If held low, the motor will coast on a power-down condition.PWM — Speed control input, internally pulled up to V LCAP(+5 V). A logic LOW turns OFF all drivers, a logic HIGH will turn ON selected drivers as determined by H1/H2/H3 input logic. Holding the terminal high allows speed/torque control solely by the current-limit circuit via REF analog voltage command.RC — An analog input used to set the fixed off time with an external resistor (R T ) and capacitor (C T ). The t blank time is controlled by the value of the external capacitor (see Applica-tions Information). As a rule, the fixed off time should not be less than 10 µs. The resistor should be in the range of 10 k Ω to 100 k Ω.SENSE — An analog input to the current-limit comparator.A voltage representing load current appears on this terminal during ON time, when it reaches REF voltage, the comparator trips and load current decays for the fixed off-time interval.Voltage transients seen at this terminal when the drivers turn ON are ignored for time t blank .REF — An analog input to the current-limit comparator.Voltage applied here sets the peak load current.I peak = V REF /R S .V CCOUT — A regulated 12 V output; supply for low-side gate drive and bootstrap capacitor charge circuits. It is good practice to connect a decoupling capacitor from this terminal to AGND,as close to the device terminals as possible. The terminal should be shorted to V BB for 12 V applications.V BB — The A3933 supply voltage. It is good practice toconnect a decoupling capacitor from this terminal to AGND, as close to the device terminals as possible. This terminal should be shorted to V CCOUT for 12 V applications.LCAP — Connection for decoupling capacitor for the internal 5 V reference. This terminal can source no more than 2 mA.DEAD — An analog input. A resistor between DEAD and LCAP is selected to adjust turn-off to turn-on time. This delay is needed to prevent shoot-through in the external power FETs.The allowable resistor range is 20 k Ω to 430 k Ω, whichconverts to deadtime of 210 ns to 2.1 µs, using the following equation:t DEAD = (6.75 x 10-12 x R DEAD ) + (75 x 10-9).AGND — The low-level (analog) reference point for the A3933.PGND — The reference point for all low-side gate drivers.Terminal Descriptions (cont’d)3933 THREE-PHASE POWER MOSFET CONTROLLER Commutation Truth TableLogic Inputs Driver OutputsH1H2H3DIR GLA GLB GLC GHA GHB GHC SA SB SCH L H H L L H H L L H Z L H L L H L L H L H L Z H L H H L H H L L L H L L H Z L H L H H L L L L H L Z H L H H H L H L L L H Z L H L L H H L H L H L L H L Z H L H L H L L L L H L Z H H L L L L H L L L H Z L H H H L L L H L H L L H L Z L H L L L L H H L L H Z L L H H L L L H L H L Z H L L L H L H L L L H L L H ZInput LogicMODE PWM RESET Mode OperationL L L Fast decay PWM chop mode, current decayL H L Fast decay Peak current limit, selected drivers ONH L L Slow decay PWM chop mode. current decayH H L Slow decay Peak current limit, selected drivers ONX X H Coast All gate drive outputs OFF, clear fault logicBrake ControlBRAKE BRKSEL Normal Operation Under Voltage or Power Loss ConditionL L Normal run mode Coast, all gate drive outputs OFFL H Normal run mode Dynamic brake, all sink gate drives ONH L Dynamic brake, all sink gate drives ON Coast, all gate drive outputs OFFH H Dynamic brake, all sink gate drives ON Dynamic brake, all sink gate drives ONL = Low Level, H = High Level, X = Don’t Care, Z = High Impedance115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003933THREE-PHASE POWER MOSFET CONTROLLERApplications Informationbootstrap capacitor. When the bootstrap capacitor has been properly charged, the high side is turned back ON. The circuit will allow three faults of this type within one commutation cycle before signaling a fault and coast the motor (all gate outputs go low).2)Bootstrap Monitor. The bootstrap capacitor is charged whenever a sink-side MOSFET is ON, Sx output goes low, and the load current recirculates. This happens constantly during normal operation. A 60 µs timer is started at the beginning of this cycle and the capacitor is charged with typically 100 mA.The bootstrap capacitor voltage is clamped at approximately 87% of V CCOUT . If the capacitor is not charged to the clamp voltage in 60 µs, a fault is signaled and the motor will coast.3)Undervoltage. The internal V CCOUT regulator supplies the low-side gate driver and the bootstrap charge current. It is critical to ensure that the voltages are at a proper level before enabling any of the outputs. The undervoltage circuit is active during power up and will force a motor coast condition until V CCOUT is greater than approximately 10 V.4)Hall Invalid. Illegal codes for the HALL inputs (000 or 111) will force a fault and coast the motor.Faults are cleared at the beginning of each commutation. If a stalled motor results from a fault, the fault can only be cleared by toggling the RESET terminal or by a power-up sequence.Current Control. Internal fixed off-time PWM circuitry is implemented to limit load current to a desired value. The external sense resistor combined with the applied analog voltage to REF terminal will set the peak current level approximatelyI TRIP ≈ V REF /R S .After the peak level is reached, the sense comparator trips and the load current will decay for a fixed off time.An external resistor (R T ) and capacitor (C T ) are used to set the fixed off-time period (t off = R T x C T ). The t off should be in the range of 10 µs to 50 µs. Longer values for t off can result in audible noise problems.Torque control can be implemented by varying the REF input voltage as long as the PWM input stays high. If direct control of the torque/current is desired by PWM input, a voltage can be applied to the REF input to set an absolute maximum current limit.Bootstrap Capacitor Selection. The high-side bootstrap circuit operates on a charge-transfer principle. The gate charge (Q g ) specification of the external power MOSFET must betaken into consideration. The bootstrap capacitor must be large enough to turn on the MOSFET without losing significant gate voltage. If the bootstrap capacitor is too large, it would take too long to charge up during the off portion of the PWM cycle. The capacitor value must be selected with both of these constraints in mind.1)Minimum bootstrap capacitor value to transfer charge. The charge on the bootstrap capacitor should be 20x greater than the gate charge (Q g ) of the power MOSFET.Example: For Q g = 0.025 µC, selectC boot = 20 x Q g /10.5 V = 0.047 µF.Check for maximum V g drop at turn on: dq = C boot x dV g , where Q g = dq.dV g = dq/C boot = 0.025 µC/0.047 µF = 532 mV.2)Calculate minimum PWM “OFF” cycle with C boot = 0.047 µF.dt = r o x C boot x ln(0.036/[Q g /C boot + 0.036])where r o = 20 ohms, the equivalent internal series resistance of the bootstrap capacitor monitor circuit.The sink-side MOSFET will be held OFF for this minimum time such that the bootstrap capacitor can be recharged independently of the PWM input frequency.The above equation is valid for PWM cycles after the bootstrap capacitor has been charged once. For the first cycle after a motor phase commutates from Hi-Z to GHx ON, or during the first charging cycle at power-up, the circuit will ignore PWM signals until it has been charged.The time required to charge up at power up and at commutation change is approximately:t = C boot x 7 V/0.1 AProtection Circuitry. The A3933 will protect the external MOSFETs by shutting down the gate drive if any of the following conditions are detected:1)Gate Source Monitor (high side only). The voltage on the GHx terminals must stay 7 V higher than the source. If this voltage droops below the threshold, the high side turns OFF,and the low-side gate will turn ON in an attempt to recharge the3933 THREE-PHASE POWER MOSFET CONTROLLER Applications Information (cont’d)PWM Blank. The capacitor (C T) also serves as the means to set the blank time duration. After the off time expires, the selected gates are turned back ON. At this time, large current transients can occur during the reverse recovery time (t rr) of the intrinsic body diodes of the external MOSFETs. To prevent the current-sense comparator from thinking the current spikes are a real overcurrent event, the comparator is blanked:t blank = 1.9 x C T/(1 mA-2/R T)The user must ensure that C T is large enough to cover the current-spike duration.Load Current Recirculation. If MODE has been set for slow decay, the high-side (source) driver will turn OFF forcing the current to recirculate through the pair of sink MOSFETs. If MODE has been selected for fast decay, both the selected high-and low-side gates are turned OFF, which will force the current to recirculate through one sink MOSFET and the high-side clamp diode. Synchronous rectification (only on the low side) allows current to flow through the MOSFET, rather than the clamp diode, during the decay time. This will minimize power loss during the off period. It is important to take into account that, when switching, the intrinsic diodes will conduct during the adjustable deadtime.Braking. The A3933 will dynamically brake by forcing all sink-side MOSFETs ON. This will effectively short out the BEMF. During braking, the load current can be approximated by:I BRAKE = V BEMF/R LPower Loss Brake. The BRKCAP and BRKSEL terminals provide a power-down braking option. By applying a logic level to input BRKSEL, the system can control if the motor is dynamically braked or is allowed to coast during an undervoltage event. The reservoir capacitor on the BRKCAP terminal provides the power to hold the sink-side gates ON after supply voltage is lost. A logic high on BRKSEL will brake the motor, a logic low and it will coast.Layout. Careful consideration must be given to PCB layout when designing high-frequency, fast-switching, high-current circuits.1)The analog ground (AGND), the power ground (PGND), and the high-current return of the external MOSFETs (the negative side of the sense resistor) should return separately to the negative side of the motor supply filtering capacitor. This will minimize the effect of switching noise on the device logic and analog reference.2)Minimize stray inductances by using short, wide copper runs at the drain and source terminals of all power MOSFETs. This includes motor lead connections, the input power buss, and the common source of the low-side power MOSFETs. This will minimize voltages induced by fast switching of large load currents.3)Kelvin connect the SENSE terminal PC trace to the positive side of the sense resistor.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50003933THREE-PHASE POWER MOSFET CONTROLLERDimensions in Inches(controlling dimensions)Dwg. MA-006-32 in5NOTES: 1. Lead spacing tolerance is non-cumulative.2. Exact body and lead configuration at vendor’s option within limits shown3933THREE-PHASE POWER MOSFET CONTROLLERDimensions in Millimeters(for reference only)Dwg. MA-006-32 mm5201413NOTES: 1. Lead spacing tolerance is non-cumulative.2. Exact body and lead configuration at vendor’s option within limits shownThe products described here are manufactured under one or more U.S.patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time totime, such departures from the detail specifications as may be required topermit improvements in the performance, reliability, or manufacturabilityof its products. Before placing an order, the user is cautioned to verify thatthe information being relied upon is current.Allegro products are not authorized for use as critical components inlife-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable.However, Allegro MicroSystems, Inc. assumes no responsibility for its use;nor for any infringement of patents or other rights of third parties whichmay result from its use.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-********THREE-PHASE POWER MOSFET CONTROLLERMOTOR DRIVERS FunctionOutput Ratings*Part Number †INTEGRATED CIRCUITS FOR BRUSHLESS DC MOTORS3-Phase Power MOSFET Controller —28 V 39333-Phase Power MOSFET Controller —50 V 39323-Phase Power MOSFET Controller —50 V 76002-Phase Hall-Effect Sensor/Driver 400 mA 26 V 3626Bidirectional 3-Phase Back-EMF Controller/Driver ±600 mA 14 V 89062-Phase Hall-Effect Sensor/Driver 900 mA 14 V 36253-Phase Back-EMF Controller/Driver ±900 mA 14 V 8902–A3-Phase Controller/Drivers ±2.0 A 45 V 2936 & 2936-120INTEGRATED BRIDGE DRIVERS FOR DC AND BIPOLAR STEPPER MOTORSDual Full Bridge with Protection & Diagnostics ±500 mA 30 V 3976PWM Current-Controlled Dual Full Bridge ±650 mA 30 V 3966PWM Current-Controlled Dual Full Bridge ±650 mA 30 V 3968PWM Current-Controlled Dual Full Bridge ±750 mA 45 V 2916PWM Current-Controlled Dual Full Bridge ±750 mA 45 V 2919PWM Current-Controlled Dual Full Bridge ±750 mA 45 V 6219PWM Current-Controlled Dual Full Bridge ±800 mA 33 V 3964PWM Current-Controlled Full Bridge ±1.3 A 50 V 3953PWM Current-Controlled Dual Full Bridge ±1.5 A 45 V 2917PWM Current-Controlled Dual Full Bridge ±1.5 A 45 V 2918PWM Current-Controlled Microstepping Full Bridge ±1.5 A 50 V 3955PWM Current-Controlled Microstepping Full Bridge ±1.5 A 50 V 3957PWM Current-Controlled Dual DMOS Full Bridge ±1.5 A 50 V 3972Dual Full-Bridge Driver ±2.0 A 50 V 2998PWM Current-Controlled Full Bridge ±2.0 A 50 V 3952DMOS Full Bridge PWM Driver ±2.0 A 50 V 3958Dual DMOS Full Bridge ±2.5 A 50 V 3971UNIPOLAR STEPPER MOTOR & OTHER DRIVERSVoice-Coil Motor Driver ±500 mA 6 V 8932–A Voice-Coil Motor Driver ±800 mA 16 V 8958Unipolar Stepper-Motor Quad Drivers 1 A 46 V 7024 & 7029Unipolar Microstepper-Motor Quad Driver 1.2 A 46 V 7042Unipolar Stepper-Motor Translator/Driver 1.25 A 50 V 5804Unipolar Stepper-Motor Quad Driver 1.8 A 50 V 2540Unipolar Stepper-Motor Quad Driver 1.8 A 50 V 2544Unipolar Stepper-Motor Quad Driver 3 A 46 V 7026Unipolar Microstepper-Motor Quad Driver 3 A 46 V 7044*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits or over-current protection voltage limits. Negative current is defined as coming out of (sourcing) the output.†Complete part number includes additional characters to indicate operating temperature range and package style.Also, see 3175, 3177, 3235, and 3275 Hall-effect sensors for use with brushless dc motors.。

ZSSC3135AA2T中文资料(ZMDI)中文数据手册「EasyDatasheet - 矽搜」

数据表

修订1.00 2011 /月

ZSSC3135

传感器信号调理器,用于压阻式桥传感器

芯片中文手册,看全文,戳

ZSSC3135

传感器信号调理器,用于压阻式桥传感器

简 要 描 述 ;简 介

所述ZSSC3135是ZSSC313x成员 CMOS产品系列集成电路 专为汽车/工业传感器应用 系统蒸发散.所有家人都非常适合highly-

2电路描述....................................................................................................................................... 11 2.1.信号流........................................................................................................................................... 11 2.2.应用模式................................................................................................................................ 12 2.3.模拟前端(AFE) ....................................................................................................................... 12 2.3.1.可编程增益放大器(PGA)............................................ ................................................. 12 2.3.2.偏移补偿..................................................................................................................... 13 2.3.3.测量周期....................................................................................................................... 13 2.3.4.模拟 - 数字转换器............................................................................................................ 15 2.4.温度测量.................................................................................................................. 16 2.5.系统控制和调节计算............................................. ......................................... 16 2.5.1.操作Modes............................................................................................................................ 16 2.5.2.启动阶段................................................................................................................................ 16 2.5.3.空调计算................................................................................................................ 17 2.6.模拟输出AOUT ............................................................................................................................ 17 2.7.串行数字接口.......................................................................................................................... 18 2.8.故障防护护功能,看门狗和错误检测........................................... .................................... 18 2.9.高电压,反向极性防护护和短路防护护......................................... ...................... 18

MCP73871中文文档

18, 19 2 6

CE

IN

IN

IN

OUT

系统 负载

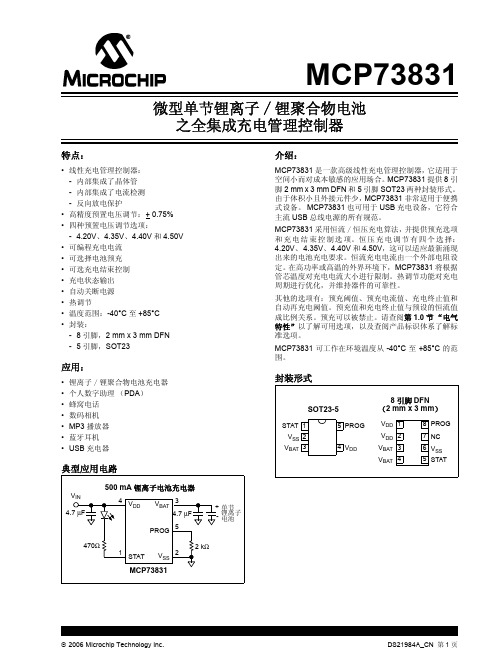

7 STAT2 8 3 STAT1 LBO SEL PROG2 TE CE

单节 锂离子电池

低 低 低 低

高 4 高 高 高 9 17

PROG3

12 RPROG3

VSS 10, 11, EP

DS22090A_CN 第 2 页

2009 Microchip Technology Inc.

2009 MicrochiБайду номын сангаас Technology Inc.

DS22090A_CN 第 1 页

MCP73871

封装类型

MCP73871 20 引脚 QFN VBAT_SENSE 15 VBAT 外露的金属 焊盘 VSS 14 VBAT 13 PROG1 12 PROG3 11 VSS 6 PG 7 STAT2 8 STAT1 / LBO 9 TE 10 VSS

VREG + 0.25V VREG + 0.17V — 4.121 4.221 4.372 4.422 +0.5 +0.75 0.20 0.18 — — 110 1100 100 500

V V mV V V V % % %/V % dB dB mA mA mA mA

VDD=[VREG( 典型值 )+1V] IOUT=10 mA TA=-5°C 至 +55°C TA= +25°C TA= -5°C 至 +55°C VDD=[VREG( 典型值 )+1V] 至 6V IOUT=10 mA IOUT=10 mA 至 150 mA VDD= [VREG( 典型值 )+1V] IOUT=10 mA, 1 kHz IOUT=10 mA, 10 kHz PROG1 = 10 kΩ PROG1 = 1 kΩ, TA=-5°C 至 +55°C, SEL = 高 PROG2 = 低, SEL = 低, (注 2) PROG2 = 高, SEL = 低, (注 2) TA= -5°C 至 +55°C

7383-G1C3-ATVA中文资料

元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSFeatures˙Popular T-1 3/4 diameter package. ˙Choice of various viewing angles. ˙Available on tape and reel. ˙Reliable and robust. ˙ESD-withstand voltage: up to 4KV. ˙The product itself will remain within RoHS compliant version. ˙UV resistant epoxyDescriptions˙The series is specially designed for applications requiring higher brightness. ˙The LED lamps are available with different colors, intensities, epoxy colors, etc. ˙Superior performance in outdoor environmentApplications˙Color Graphic Signs ˙Message boards ˙Variable message signs (VMS) ˙Commercial outdoor advertisingDevice Selection GuideLED Part No.7383/G1C3-ATVA/MS 7383/G1C3-ATVA/P/MSChip Mterial InGaN InGaNEmitted Color Super Green Super GreenLens Color Water Clear Water ClearStopper No YesEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 1 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSPackage DimensionsStopper type No Stopper typeNotes: ˙All dimensions are in millimeters, tolerance is 0.25mm except being specified. ˙Lead spacing is measured where the lead emerges from the package. ˙Protruded resin under flange is 1.5mm Max LED.Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 2 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSAbsolute Maximum Ratings (Ta=25℃)Parameter Forward Current Pulse Forward Current*1 Operating Temperature Storage Temperature Electrostatic Discharge*2Symbol IF IFP Topr Tstg ESD Tsol Pd Iz VRRating 30 100 -40 ~ +85 -40 ~ +100 4K 260 ±5 120 100 5Units mA mA ℃ ℃ V ℃ mW mA VSoldering Temperature Power Dissipation Zener Reverse Current Reverse VoltageNotes: *1:IFP Conditions--Pulse Width≦10msec and Duty≦1/10. *2:Soldering time≦5 seconds.Electro-Optical Characteristics (Ta=25℃)Parameter Forward Voltage Zener Reverse Voltage Luminous Intensity Viewing Angle Peak Wavelength Dominant Wavelength Spectrum Radiation Bandwidth Reverse Current Symbol VF Vz IV 2θ1/2 λp λd Δλ IR Condition IF=20mA IZ=5mA IF=20mA IF=20mA IF=20mA IF=20mA IF=20mA VR=5V Min. 2.8 5.2 7150 ----524 --Typ. ---30 518 528 35 -Max. 3.6 -14250 ----532 -50 Units V V mcd deg nm nm nm μAEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 3 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSRank Combination (IF=20mA)Rank Luminous Intensity T 7150~9000 U 9000~11250 V 11250~14250Unit: :mcd*Measurement Uncertainty of Luminous Intensity: ±15%Rank Forward Voltage0 2.8~3.01 3.0~3.22 3.2~3.43 3.4~3.6Unit:V*Measurement Uncertainty of Forward Voltage: ±0.1VRank Dominant Wavelength12Unit:nm524~528 528~532 *Measurement Uncertainty of Dominant Wavelength ±1.0nm*The quantity ratio of the ranks is decided by EVERLIGHT.Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 4 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSTypical Electro-Optical Characteristics CurvesEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 5 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSPacking Quantity Specification1.500PCS/1Bag,5Bags/1Box 2.10Boxes/1CartonLabel Form SpecificationEVERLIGHT CPN: P/N: 7383/G1C3-ATVA/X/MS QTY: CAT: HUE: LOT NO: REF: MADE IN TAIWAN CPN: Customer’s Production Number P/N : Production Number QTY: Packing Quantity CAT: Ranks of Luminous Intensity and Forward Voltage HUE: Ranks of Dominant Wavelength REF: Reference LOT No: Lot Number MADE IN TAIWAN: Production PlaceEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 6 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSNotes 1. Above specification may be changed without notice. EVERLIGHT will reserve authority on material change for above specification. 2. When using this product, please observe the absolute maximum ratings and the instructions for using outlined in these specification sheets. EVERLIGHT assumes no responsibility for any damage resulting from use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets. 3. These specification sheets include materials protected under copyright of EVERLIGHT corporation. Please don’t reproduce or cause anyone to reproduce them without EVERLIGHT’s consent. 4. Below the zener reference voltage Vz, all the current flows through LED and as the voltage rises to Vz, the zener diode “breakdown." If the voltage tries to rise above Vz current flows through the zener branch to keep the voltage at exactly Vz. 5. When the LED is connected using serial circuit, if either piece of LED is no light up but current can’t flow through causing others to light down. In new design, the LED is parallel with zener diode. if either piece of LED is no light up but current can flow through causing others to light up.Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 7 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MS6. Soldering ConditionCareful attention should be paid during soldering. When soldering, leave more then 3mm from solder joint to case, and soldering beyond the base of the tie bar is recommended. Avoiding applying any stress to the lead frame while the LEDs are at high temperature particularly when soldering. Recommended soldering conditions: Hand Soldering Temp. at tip of iron Soldering time Distance 400℃ Max. (30W Max.) 3 sec Max. 3mm Min.(From solder joint to case) Preheat temp. Bath temp. Bath time. Distance DIP Soldering 100℃ Max. (60 sec Max.) 265 Max. 5 sec Max. 3mm Min.EVERLIGHT ELECTRONICS CO., LTD. Office: No 25, Lane 76, Sec 3, Chung Yang Rd, Tucheng, Taipei 236, Taiwan, R.O.CTel: 886-2-2267-2000, 2267-9936 Fax: 886-2267-6244, 2267-6189, 2267-6306 http:\\Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 8 of 8Prepared : Grace Shen。

TDA7385,E-TDA7385,TDA7385H, 规格书,Datasheet 资料

This is information on a product in full production.July 2012Doc ID 8160 Rev 51/17TDA73854 x 42 W quad bridge car radio amplifierDatasheet − production dataFeatures■High output power capability:– 4 x 42 W / 4 Ω max.– 4 x 23 W / 4 Ω @ 14.4 V , 1 kHz, 10 %■Clipping detector ■Low distortion ■Low output noise ■Standby function ■Mute function■Automute at min. supply voltage detection ■Diagnostics facility for: –Clipping–Out to GND short –Out to V S short –Thermal shutdown■Low external component count:–Internally fixed gain (26 dB)–No external compensation –No bootstrap capacitors■Protections:–Output short circuit to GND, to V S , across the load–Very inductive loads–Overrating chip temperature with soft thermal limiter–Load dump voltage –Fortuitous open GND–ESDDescriptionThe TDA7385 is an AB class audio poweramplifier, packaged in Flexiwatt 25 and designed for high end car radio applications.Based on a fully complementary PNP/NPN configuration, the TDA7385 allows a rail to rail output voltage swing with no need of bootstrap capacitors. The extremely reduced boundary components count allows very compact sets.The on-board clipping detector simplifies gain compression operations. The fault diagnostics makes it possible to detect mistakes during car-radio assembly and wiring in the car.Table 1.Device summaryOrder code Package Packing TDA7385Flexiwatt25Tube E-TDA7385(1)1.Device in ECOPACK® package (see Section 4: Package information on page 15).Flexiwatt25TubeContents TDA7385Contents1Block and pin connection diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.1Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.2Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.3Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.4PCB and component layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82.5Electrical characteristic curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93Application hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.1Biasing and SVR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.2Input stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.3Standby and muting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.4Diagnostics facility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.5Stability and layout considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 4Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 5Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162/17Doc ID 8160 Rev 5TDA7385List of tables List of tablesTable 1.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 3.Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 4.Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 5.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16Doc ID 8160 Rev 53/17List of figures TDA7385 List of figuresFigure 1.Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 2.Pin connection (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3.Standard test and application circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure ponents and top copper layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5.Bottom copper layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6.Quiescent current vs. supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7.Quiescent output voltage vs. supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8.Output power vs. supply voltage (4Ω). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 9.Distortion vs. output power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10.Distortion vs. frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 11.Supply voltage rejection vs. frequency by varying C6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 12.Output noise vs. source resistance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 13.Power dissipation and efficiency vs. output power. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 14.Input/output biasing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 15.Diagnostics circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16.Clipping detection waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 17.Diagnostics waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18.Fault detection circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 19.Flexiwatt25 mechanical data and package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 4/17Doc ID 8160 Rev 5TDA7385Block and pin connection diagrams 1 Block and pin connection diagramsDoc ID 8160 Rev 55/17Electrical specifications TDA73856/17Doc ID 8160 Rev 52 Electrical specifications2.1Absolute maximum ratings2.2 Thermal data2.3 Electrical characteristicsV S = 14.4 V; f = 1 kHz; R g = 600 Ω; R L = 4 Ω;T amb = 25 °C; Refer to the test and applicationdiagram (Figure 3), unless otherwise specified.Table 2.Absolute maximum ratingsSymbol ParameterValue Unit V S Operating supply voltage 18V V S (DC)DC supply voltage28V V S (pk)Peak supply voltage (t = 50 ms)50V I O Output peak current:Repetitive (duty cycle 10 % at f = 10 Hz)Non repetitive (t = 100 µs) 4.55.5A A P tot Power dissipation, (T case = 70 °C)80W T j Junction temperature 150°C T stgStorage temperature– 55 to 150°CTable 3.Thermal dataSymbol ParameterValue Unit R th j-caseThermal resistance junction-to-casemax.1°C/WTable 4.Electrical characteristicsSymbol ParameterTest conditionMin.Typ.Max.Unit I q1Quiescent current --180300mA V OS Output offset voltage ---100mV G vVoltage gain-252627dBP oOutput power THD = 10%THD = 1%THD = 10%; V S = 13.2 V THD = 1%; V S = 13.2 V 2116.5171423192016-WP o max.Max. output power (1)V S = 14.4 V 3335-W V S = 15.2 V -42-W THDDistortionP o = 4 W-0.040.3%TDA7385Electrical specificationsDoc ID 8160 Rev 57/17e No Output noise"A" WeightedBw = 20 Hz to 20 kHz -5065-150μV μV SVR Supply voltage rejection f = 100 Hz 5065-dB f cl Low cut-off frequency --20-Hz f ch High cut-off frequency -75-kHz R i Input impedance -70100-k ΩC T Cross talk f = 1 kHz 5070-dB I SB Standby current consumptionVs tandby =0 V --15µA V SB out Standby out threshold voltage(Amp: on)3.5--V V SB IN Standby in threshold voltage (Amp: off)-- 1.5V A M Mute attenuationV O = 1Vrms 8090-dB V M out Mute out threshold voltage (Amp: play) 3.5--V V M in Mute in threshold voltage (Amp: mute)-- 1.5V I m (L)Muting pin currentV MUTE = 1.5V (source current)51016μA I CDOFF Clipping detector "off" outputaverage currentTHD = 1% (1)-100-μA I CDONClipping detector "on" outputaverage currentTHD = 10% (1)100240350μA1.Diagnostics output pulled-up to 5 V with 10 k Ω series resistor.Table 4.Electrical characteristics (continued)Symbol ParameterTest conditionMin.Typ.Max.UnitElectrical specifications TDA73858/17Doc ID 8160 Rev 52.4 PCB and component layoutReferred to Figure 3: Standard test and application circuit .Figure 4.Components and top copper layerFigure 5.Bottom copper layerTDA7385Electrical specificationsDoc ID 8160 Rev 59/172.5Electrical characteristic curvesFigure 6.Quiescent current vs. supplyFigure 7.Quiescent output voltage vs. Figure 8.Output power vs. supply voltageFigure 9.Distortion vs. output powerFigure 10.Distortion vs. frequencyFigure 11.Supply voltage rejection vs.Electrical specifications TDA7385 Figure 12.Output noise vs. source resistance Figure 13.Power dissipation and efficiency10/17Doc ID 8160 Rev 5TDA7385Application hintsDoc ID 8160 Rev 511/173 Application hintsReferred to the circuit of Figure 3.3.1 Biasing and SVRAs shown by Figure 14, all the TDA7385’s main sections, such as Inputs, Outputs AND AC-GND (pin 16) are internally biased at half supply voltage level (Vs/2), which is derived fromthe Supply Voltage Rejection (SVR) block. In this way no current flows through the internal feedback network. The AC-GND is common to all the 4 amplifiers and represents the connection point of all the inverting inputs.Both individual inputs and AC-GND are connected to Vs/2 (SVR) by means of 100 k Ω resistors.To ensure proper operation and high supply voltage rejection, it is of fundamentalimportance to provide a good impedance matching between Inputs and AC-GROUND terminations. This implies that C 1, C 2, C 3, C 4, C 5 capacitors have to carry the same nominal value and their tolerance should never exceed ± 10 %.Besides its contribution to the ripple rejection, the SVR capacitor governs the turn ON/OFF time sequence and, consequently, plays an essential role in the pop optimization during ON/OFF transients. To conveniently serve both needs, its minimum recommended value is 10µF .3.2 Input stageThe TDA7385’s inputs are ground-compatible and can stand very high input signals(± 8 Vpk) without any performances degradation.If the standard value for the input capacitors (0.1 µF) is adopted, the low frequency cut-off will amount to 16 Hz.Application hints TDA738512/17Doc ID 8160 Rev 53.3 Standby and mutingStandby and muting facilities are both CMOS-compatible. If unused, a straight connection toVs of their respective pins would be admissible. Conventional low-power transistors can be employed to drive muting and stand-by pins in absence of true CMOS ports ormicroprocessors. R-C cells have always to be used in order to smooth down the transitions for preventing any audible transient noises.Since a DC current of about 10 µA normally flows out of pin 22, the maximum allowable muting-series resistance (R 2) is 70 k Ω, which is sufficiently high to permit a muting capacitor reasonably small (about 1µF).If R 2 is higher than recommended, the involved risk will be that the voltage at pin 22 may rise to above the 1.5 V threshold voltage and the device will consequently fail to turn OFF when the mute line is brought down.About the stand-by, the time constant to be assigned in order to obtain a virtually pop-free transition has to be slower than 2.5V/ms.3.4 Diagnostics facilityThe TDA7385 is equipped with a diagnostics circuitry able to detect the following events:●Clipping in the output stage●overheating (thermal shut-down proximity)●Output misconnections (OUT -GND and OUT -V S shorts)Diagnostics information is available across an open collector output located at pin 25(Figure 15) through a current sinking whenever at least one of the above events is recognized.Among them, the Clipping Detector acts in a way to output a signal as soon as one or more power transistors start being saturated.As a result, the clipping-related signal at pin 25 takes the form of pulses, which are perfectly synchronized with each single clipping event in the music program and reflect the same duration time (Figure 16). Applications making use of this facility usually operate afiltering/integration of the pulses train through passive R-C networks and realize a volume (or tone bass) stepping down in association with microprocessor-driven audioprocessors. The maximum load that pin 25 can sustain is 1 k Ω.Due to its operating principles, the clipping detector has to be viewed mainly as a power-dependent feature rather than frequency-dependent. This means that clipping state will be immediately signaled out whenever a fixed power level is reached, regardless of the audioTDA7385Application hints frequency. In other words, this feature offers the means to counteract the extremely sound-damaging effects of clipping, caused by a sudden increase of odd order harmonics andappearance of serious inter-modulation phenomena.Another possible kind of distortion control could be the setting of a maximum allowable THDlimit (e.g. 0.5%) over the entire audio frequency range. Besides offering no practicaladvantages, this procedure cannot be much accurate, as the non-clipping distortion is likelyto vary over frequency.In case of Overheating, pin 25 will signal out the junction temperature proximity to thethermal shut-down threshold. This will typically start about 2°C before the thermal shut-down threshold is reached.As various kind of diagnostics information is available at pin 25 (clipping, shorts andoverheating), it may be necessary to operate some distinctions on order to treat each eventseparately. This could be achieved by taking into account the intrinsically different timing ofthe diagnostics output under each circumstance.In fact, clipping will produce pulses normally much shorter than those present under faultyconditions. An example of circuit able to distinguish between the two occurrences is shownby Figure18.3.5 Stability and layout considerationsIf properly layouted and hooked to standard car-radio speakers, the TDA7385 will beintrinsically stable with no need of external compensations such as output R-C cells. Due tothe high number of channels involved, this translates into a very remarkable componentssaving if compared to similar devices on the market.To simplify pc-board layout designs, each amplifier stage has its own power groundexternally accessible (pins 2,8,18,24) and one supply voltage pin for each couple of them.Even more important, this makes it possible to achieve the highest possible degree ofseparation among the channels, with remarkable benefits in terms of cross-talk anddistortion features.About the layout grounding, it is particularly important to connect the AC-GND capacitor (C5)to the signal GND, as close as possible to the audio inputs ground: this will guarantee highrejection of any common mode spurious signals.The SVR capacitor (C6) has also to be connected to the signal GND.Supply filtering elements (C7, C8) have naturally to be connected to the power-ground andlocated as close as possible to the Vs pins.Doc ID 8160 Rev 513/17Application hints TDA7385 Pin 1, which is mechanically attached to the device’s tab, needs to be tied to the cleanestpower ground point in the pc-board, which is generally near the supply filtering capacitors.14/17Doc ID 8160 Rev 5TDA7385Package informationDoc ID 8160 Rev 515/174 Package informationIn order to meet environmental requirements, ST offers these devices in different grades ofECOPACK ® packages, depending on their level of environmental compliance. ECOPACK ® specifications, grade definitions and product status are available at: .ECOPACK ® is an ST trademark.Revision history TDA738516/17Doc ID 8160 Rev 55 Revision historyTable 5.Document revision historyDate RevisionChanges10-Mar-20011Initial release.13-Nov-20082Document reformatted.Added Features on page 1.Updated Table 4: Electrical characteristics on page 6.Updated Section 4: Package information on page 15.09-Jan-20123Modified Features on page 1;Updated Table 4: Electrical characteristics .14-Jun-20124Updated Features on page 1;Updated Table 4: Electrical characteristics .26-Jul-20125Updated Figure 17: Diagnostics waveforms on page 14.TDA7385Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNL ESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SAL E ST DISCL AIMS ANY EXPRESS OR IMPL IED WARRANTY WITH RESPECT TO THE USE AND/OR SAL E OF ST PRODUCTS INCL UDING WITHOUT L IMITATION IMPL IED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNL ESS EXPRESSL Y APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2012 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of AmericaDoc ID 8160 Rev 517/17。

IRF7389TRPBF;IRF7389PBF;中文规格书,Datasheet资料

Min. Typ. Max. Units

Conditions

N-Ch 30 P-Ch -30

V

VGS = 0V, ID = 250µA VGS = 0V, ID = -250µA

N-Ch P-Ch

0.022 0.022

V/°C

Reference to 25°C, ID = 1mA Reference to 25°C, ID = -1mA

IDSS

IGSS Qg Qgs Qgd td(on) tr td(off) tf Ciss Coss Crss

Drain-to-Source Leakage Current

Gate-to-Source Forward Leakage Total Gate Charge Gate-to-Source Charge Gate-to-Drain ("Miller") Charge Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Input Capacitance Output Capacitance Reverse Transfer Capacitance

P-Ch -2.5 A

N-Ch 30

ISM

Pulsed Source Current (Body Diode)

P-Ch -30

VSD

Diode Forward Voltage

N-Ch 0.78 1.0 P-Ch -0.78 -1.0

V

TJ = 25°C, IS = 1.7A, VGS = 0V TJ = 25°C, IS = -1.7A, VGS = 0V

PIC下载地址

PIC18F87J10系列(128K字节Flash)中文数据手册:

/downloads/en/DeviceDoc/39663b_cn.pdf

PIC16F627A/628A/648A中文数据手册:

/downloads/en/DeviceDoc/40044d_cn.pdf

Section 17. 10-Bit A/D Converter

/downloads/en/DeviceDoc/39705a_cn.pdf

Section 19. Comparator Module

/downloads/en/DeviceDoc/39710a_cn.pdf

电池电量管理芯片PS810中文数据手册:

/downloads/en/DeviceDoc/21904b_cn.pdf

PIC24系列参考手册部分章节中文翻译

Section 7. Reset

/downloads/en/DeviceDoc/39712a_cn.pdf

PIC18F45J10系列中文数据手册

/downloads/en/devicedoc/39682a_cn.pdf

PICKIT2 在线编程器中文使用说明书

/downloads/en/DeviceDoc/51553a_cn.pdf

PIC16F785/HV785中文数据手册(更新版本)

/downloads/en/DeviceDoc/41249d_cn.pdf

PIC18F2450/4450带有全速USB的单片机中文数据手册

/downloads/en/DeviceDoc/39760a_cn.pdf

MCP2515 SPI接口的CAN控制器中文数据手册

FAN7384MX;FAN7384M;中文规格书,Datasheet资料

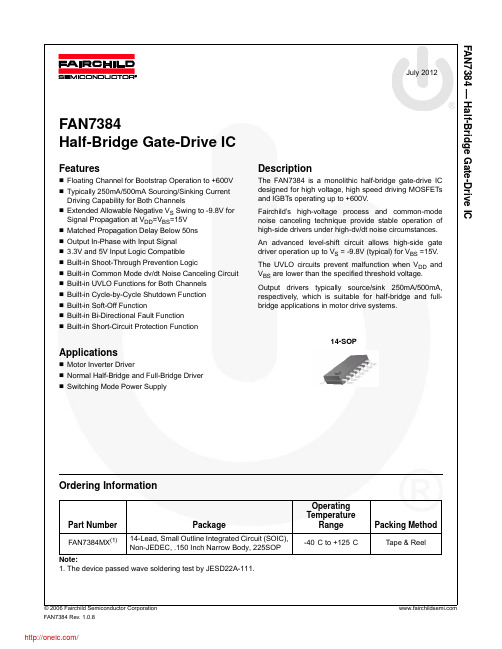

Symbol

VS VB VHO VDD VIN VCSC VFO dVS/dt PD(2)(3)(4) JA TJ TS Notes:

Parameter

High-side offset voltage VS High-side floating supply voltage VB High-side floating output voltage Low-side and logic-fixed supply voltage Logic input voltage (HIN, LIN, SD) Current sense input voltage Fault output voltage Allowable offset voltage slew rate Power dissipation Thermal resistance, junction-to-ambient Junction temperature Storage temperature

14-SOP

Applications

Motor Inverter Driver Normal Half-Bridge and Full-Bridge Driver Switching Mode Power Supply

1

Ordering Information

Operating Temperature Range

FAN7384 — Half-Bridge Gate-Drive IC

Pin Configuration

LIN SD HIN VDD FO CSC GND

1 2 3 4 5 6 7

14 13 12 11 10 9 8

VB HO VS NC NC LO VSL

TDA7385中文资料

2/12

25

D94AU117B

Max.

Value 1

Unit °C/W

元器件交易网

TDA7385

ELECTRICAL CHARACTERISTICS (VS = 14.4V; f = 1KHz; Rg = 600Ω; RL = 4Ω; Tamb = 25°C; Refer to the Test and application circuit (fig.1), unless otherwise specified.)

The on-board clipping detector simplifies gain

compression operations. The fault diagnostics makes it possible to detect mistakes during CarRadio assembly and wiring in the car.

30

W

33

35

W

0.04 0.3

%

50

µV

65

150

µV

50

65

dB

20

Hz

75

KHz

70

100

KΩ

50

70

dB

100

µA

3.5

V

1.5

V8090dB3.5V

1.5

V

5

10

16

µA

100

µA

100 240 350

µA

(*) Saturated square wave output. (**) Diagnostics output pulled-up to 5V with 10KΩ series resistor.

MAX738AEWE中文资料