PAD_A13_STD_V1_24

micropython hx711方法

micropython hx711⼀、引⾔随着物联⽹技术的快速发展,微控制器在各种应⽤中发挥着越来越重要的作⽤。

其中,micropython作为⼀种轻量级的Python语⾔,在微控制器领域得到了⼴泛的应⽤。

hx711是⼀款⾼精度的24位ADC(模数转换器),⼴泛应⽤于各种传感器数据的采集。

本⽂将介绍如何使⽤micropython控制hx711,并详细介绍其基本⽅法。

⼆、hx711简介hx711是⼀款24位ADC芯⽚,具有⾼精度、低噪声、低功耗等优点。

它采⽤SPI(串⾏外设接⼝)或I2C(双向串⾏总线)通信⽅式,与微控制器连接。

通过读取hx711的寄存器,可以获取传感器的模拟信号值。

三、micropython控制hx711⽅法下⾯介绍如何使⽤micropython控制hx711:步骤⼀:安装micropython库在micropython中,需要安装hx711库才能使⽤hx711模块。

可以使⽤upip 库来安装hx711库。

在micropython的命令⾏界⾯中输⼊以下命令:import upipupip.install('hx711')步骤⼆:导⼊hx711模块在micropython中导⼊hx711模块,可以使⽤以下代码:from machine import I2C,Pinfrom hx711import HX711步骤三:初始化hx711初始化hx711时,需要指定通信⽅式(SPI或I2C)、通信端⼝号以及设备地址等参数。

以下是使⽤I2C通信⽅式初始化的示例代码:i2c=I2C(scl=Pin(22),sda=Pin(21),freq=400000)#初始化I2C通信⽅式,scl和sda分别接在了数字引脚22和21上,频率为400kHzhx711=HX711(i2c)#创建HX711对象,与I2C通信⽅式关联起来步骤四:设置hx711增益值和偏置值在使⽤hx711之前,需要设置增益值和偏置值。

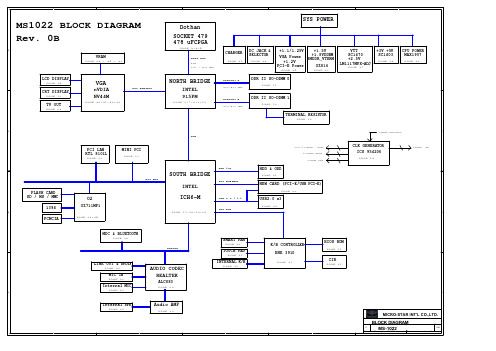

MSI MS-1022 - REV 0B

Cap must close to thermal sensor

THERMDC 31 T_CRIT_CPUT_CRIT_CPUTHERMTRIPRB37 RB35 0_NC 0

CB63 2200PF T_CRIT_A_CPU-

2 3 4

D

LM86_MSOP8 CB66 0.1UF_0402

D

Close to CPU socket

Full ON S1M(Power On Suspend)

A

HIGH HIGH LOW LOW LOW

HIGH HIGH HIGH LOW LOW

HIGH HIGH HIGH HIGH LOW

ON ON ON ON ON

ON ON ON ON ON

ON ON OFF OFF OFF

keep high

U2EB5B #D0 #D1 #D2 #D3 #D4 #D5 #D6 #D7 #D8 #D9 #D10 #D11 #D12 #D13 #D14 #D15 DSTBN0# DSTBP0# DINV0# #D16 #D17 #D18 #D19 #D20 #D21 #D22 #D23 #D24 #D25 #D26 #D27 #D28 #D29 #D30 #D31 DSTBN1# DSTBP1# DINV1# PSI# BSEL0 BSEL1 NC1 NC2 RSVD2 RSVD3 RSVD [GTLREF3] RSVD [GTLREF1] GTLREF0 #D32 #D33 #D34 #D35 #D36 #D37 #D38 #D39 #D40 #D41 #D42 #D43 #D44 #D45 #D46 #D47 DSTBN2# DSTBP2# DINV2# #D48 #D49 #D50 #D51 #D52 #D53 #D54 #D55 #D56 #D57 #D58 #D59 #D60 #D61 #D62 #D63 DSTBN3# DSTBP3# DINV3# COMP0 COMP1 COMP2 COMP3 Y26 AA24 T25 U23 V23 R24 R26 R23 AA23 U26 V24 U25 V26 Y23 AA26 Y25 W25 W24 T24 AB25 AC23 AB24 AC20 AC22 AC25 AD23 AE22 AF23 AD24 AF20 AE21 AD21 AF25 AF22 AF26 AE24 AE25 AD20 P25 P26 AB2 AB1 G1 B7 C19 E4 A6 C5 F23 HD-32 HD-33 HD-34 HD-35 HD-36 HD-37 HD-38 HD-39 HD-40 HD-41 HD-42 HD-43 HD-44 HD-45 HD-46 HD-47 HDSTBN-2 HDSTBP-2 DBI-2 HD-48 HD-49 HD-50 HD-51 HD-52 HD-53 HD-54 HD-55 HD-56 HD-57 HD-58 HD-59 HD-60 HD-61 HD-62 HD-63 HDSTBN-3 HDSTBP-3 DBI-3 HCOMP0 HCOMP1 HCOMP2 HCOMP3 H_DPRSTPH_DPSLPH_DPWRCPU_PWRGD CPUSLPRB31 RB24 1K_NC 1K_NC VTT

全志A13标案原理图

CSI_D3/SDC2_D3 121

CSI_D2/SDC2_D2 120

CSI_D1/SDC2_D1 119

CSI_D0/SDC2_D0 118

CSI_VSYNC/SPI2_MISO 117

LCD-D21 5 LCD-D22 5 LCD-D23 5 LCD-CLK 5 LCD-DE 5 LCD-HSYNC 5 LCD-VSYNC 5 CSI-D7 6 CSI-D6 6 CSI-D5 6 CSI-D4 6 CSI-D3 6 CSI-D2 6 CSI-D1 6 CSI-D0 6 CSI-VSYNC 6 CSI-HSYNC 6 CSI-MCLK 6 CSI-PCLK 6 SD0-D2 4 SD0-D3 4 SD0-CMD 4 SD0-CLK 4 SD0-D0 4 SD0-D1 4 TWI1-SDA 5,6 TWI1-SCK 5,6 PWM0 5 TWI0-SDA 3 TWI0-SCK 3 DP1 6 DM1 6 DP0 6 DM0 6

TPY1 5 TPX1 5

SZQ

17

CSI_HSYNC/SPI2_MOSI 116

SVREF

18

CSI_MCLK/SPI2_CLK/EINT15 115

SDQ1

19

CSI_PCLK/SPI2_CS0/EINT14 114

SDQ3

20

SDC0_D2 113

SDQ7

21

SDC0_D3 112

SDQ5

22

CSI-STY TWI1

TWI2

PG0 PG1

PG2

PG3

B

PG4

PG9

PG10

PG11

PG12

INPUT GPIO-IN GPIO-IN GPIO-OUT GPIO-OUT GPIO-OUT GPIO-OUT EINT GPIO-OUT

PI3EQXDP1201 ActiveEye DisplayPort ReDriver with A

ActiveEye TM DisplayPort1.2 ReDriver TM with AUX ListenerPI3EQXDP1201Features∙VESA DisplayPort 1.1a and 1.2 standard compliant for RBR 1.62Gbps, HBR 2.7Gbps /HBR2 5.4Gbps data rate∙ Full Auto and M anual DP1.2 test mode support for the user friendly system diagnosis∙ FAUX signal pass-through with low signal degrada-tion∙AUX listener supports link training, output level and pre-emphasis configuration during the link initializa-tion with "Sink Request Test Mode"∙ Fixed and Dynamic EQ configuration based on AUX link training requirement∙ Auto equalization based on signal and pre-emphasis level in AUX configuration register∙ Support Hot Plug and Cable Detection function ∙ AUX/DDC combo switch∙Individual lane power down state automatically to enter low power mode when no DP signal is present or no sink device is inserted∙ Support dedicated pins or SM Bus control mode for Equalization (EQ) setting control∙ Internally Biased AC coupled in AUX channel ∙Single 3.3V or Dual 1.5V/3.3V power sources∙ Integrated ESD protection Independent squelch per lane (auto power down) ∙48-contact TQFN, 7mm x 7mmDescriptionPI3EQXDP1201 is the Pericom’s latest DisplayPort1.2 compliant ReDriver (Repeater) to support signal jitter re-duction caused by noisy transmission line effects in the high speed DisplayPort 5.4Gbps data.It has DisplayPort Aux decoder, decipher the link training message and automatically configure the signal outputs with the optimum pre-emphasis and output swing level. In pin control, Auto EQ mode 1/2/3 and 2 bit of pre-emphasis setting provide 12 EQ steps. Programmable SMBus mode provides 16 EQ steps.PI3EQXDP1201 is intended for use in any DP signal com-pliance system including notebook PC and docking sta-tions, graphic cards and other high-speed AC-coupled dig-ital video system.Applications∙ Notebook computers ∙ PC docking station ∙ Dongle, switch boxes ∙Long DisplayPort cablesFig. 1. PI3EQXDP1201 Functional Block DiagramFig. 2. Output Eye Opening at 5.4Gbps, 12-in FR4 input and 36-in Coaxial cable. Auto EQ mode. 1200mV Swing. 0dB Pre-emphasisINFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH PERICOM PRODUCT. NO LIN-CENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN PERICOM’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PAR-TICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENR, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.Pericom may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. Pericom re-serves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specification. Current characterized errata are available on request.Contact your local Pericom Sales office or your distributor to obtain the latest specifications and before placing your product order.Copyright 2012 Pericom Corporation. All rights reserved. Pericom and the Pericom logo are trademarks of PericomCorporation in the U.S. and other countries.PI3EQXDP1201ActiveEyeTMDisplayPort1.2 ReDriver TM with Aux ListenerOrdering InformationNotes:1. Thermal characteristics can be found on the company web site at /packaging/2. “E” = Pb-free and Green, Adding an “X” suffix = Tape/ReelRelated ProductsPart NumberProduct DescriptionPI3VDP1430 ActiveEye TM Dual Mode DisplayPort to HDMI Level Shifter and Re-driver PI3HD M I412AD ActiveEye TM 1:2 HDMI1.4 compliant Splitter/Re-driverPI3HD M I336 ActiveEye TM 3:1 HDMI1.4 Switch/Re-driver with I2C control and ARC PI3HD M I511 ActiveEye TM HDMI1.4 ReDriver for Source-side application PI3HD M I611 ActiveEye TM HDMI1.4 ReDriver for Sink-side application PI3HDMI521 ActiveEye TM 2:1 HDMI1.4 Switch/Re-driver with ARC and Fast Switching support for Source-sideApplicationPI3HDMI621 ActiveEye TM 2:1 HDMI1.4 Switch/Re-driver with ARC and Fast Switching support for Sink-side ApplicationPI3VDP3212 2-Lane DisplayPort1.2 Compliant Switch PI3VDP124124-Lane DisplayPort1.2 Compliant SwitchOrdering CodePackage Code Package Desc r iptionPI3EQXDP1201ZBE ZBPb-free & Green, 48-pin TQFN。

S32K3X4EVB-Q172 通用汽车应用开发板说明书

Belt-Driven Starter Generator (BSG), Turbo Charger, Fan/Pump ControllerHero SpecsS32K3 FAMILY FEATURESFS26 Safety System Basis Chip[+5 V, +3.3V and +1.5V]MCU Current Monitoring forVDD_HV_A and VDD_HV_B64Mb QSPI Serial NOR FlashMII/RMII Ethernet Interface— SABRE Connector10/100TBase Ethernet— RJ45 ConnectorTJA1043 CAN InterfacesTJA1021 LIN InterfacesMicrocontroller (MCU)32-bit Arm Cortex-M7-based S32K344 (/products/processors-and-microcontrollers/arm-microcontrollers/s32k-automotive-mcus/s32k3-microcoK26 (/products/processors-and-microcontrollers/arm-microcontrollers/general-purpose-mcus/k-series-cortex-m4/k2x-usb/kinetis-k26-180-mhz-Safety System Basis Chip (SBC)FS26 (/products/power-management/pmics-and-sbcs/safety-sbcs/safety-system-basis-chip-sbc-with-low-power-fit-for-asil-d:FS26): Safety syst Transceivers TJA1021 (/products/interfaces/automotive-lin-solutions/lin-2-1-sae-j2602-transceiver:TJA1021): LIN 2.1/SAE J2602 transceiverTJA1043 (/products/interfaces/can-transceivers/can-with-flexible-data-rate/high-speed-can-transceiver-with-standby-and-sleep-mode:TJA1043Hardware Features 64 Mb QSPI NOR flash100 Mbit Ethernet physical LayerPower supply switchMCU voltage/current measurementUser RGB LED2x user push-buttonsADC rotary potentiometer2x touch pad electrodeSoftware Features Free of charge S32 Design Studio IDE (/design/software/development-software/s32-design-studio-ide:S32-DESIGN-STUDIO-IDE) (Eclipse, GFree of charge (/design/automotive-software-and-tools/real-time-drivers-rtd:AUTOMOTIVE-RTD)Real Time Drivers for AUTOSAR and non-AUConfiguration tools for both AUTOSAR and non-AUTOSAR usersFree of charge security firmware: SHE+ compliant NXP supplied, designed for ISO 21434S32 Safety Software Framework (/design/automotive-software-and-tools/s32-safety-software-framework-saf:SAF) (SAF): Six fault detection anFree of charge Safety Peripheral Drivers (SPD)Structural Core Self Test (/docs/en/product-brief/S32K3xx-SCST-PB.pdf) (SCST)Free of charge inter-platform communication framework (/design/automotive-software-and-tools/inter-platform-communication-framework-ipcf:Free of charge Model-Based Design Toolbox (/design/automotive-software-and-tools/model-based-design-toolbox-mbdt:MBDT) for MATLAB :Programing Debug interfaces On-board S32K3 debug interface20-Pin Cortex debug + ETM connectorCompatibility Arduino UNO pint-out compatible with expansion “shield” supportInterfaces On-board HS-CAN2x on-board LINEthernet 100 Mbit Physical Layer with RJ-45 connector for fast prototypingSWD/JTAG debug interface for S32K3 debugger®®BuyS32K3X4EVB-Q172 (/part/S32K3X4EVB-Q172) S32K3X4EVB-Q172 Evaluation and Development Board for General Purpose(/design/automotive-(/design/software/development-(/design/software/development-Design ResourcesGet Started1. Review this Getting Started guide to get familiar with the hardware specifications.Getting StartedGetting Started with the S32K3X4EVB-Q172 Evaluation Board (/document/guide/getting-started-with-the-s32k3x4evb-q172-evaluation-board:GS-S32K3X4EVB-Q172)HTML Oct 6, 2021 GS-S32K3X4EVB-Q1722. Review this user manual to get familiar with the board.User ManualS32K3X4EVB-Q172 Evaluation Board – HW User Manual (/webapp/Download?colCode=S32K3X4EVB-Q172_HW-UM)PDF Rev A Oct 20, 2021 S32K3X4EVB-Q172_HW-UM EnglishDOCUMENTS ( 8 )DESIGN RESOURCES ( 4 )SOFTWARE ( 7 )Reference Manual ( 1 )User Guide ( 1 )Brochure ( 1 )Errata ( 1 )Product Brief ( 4 )Design Tools & Files ( 4 )Embedded Software ( 3 )Development Software ( 4 )DocumentsReference Manual ( 1 )S32K3X4EVB-Q172 Evaluation Board – HW User Manual (/webapp/Download?colCode=S32K3X4EVB-Q172_HW-UM)Hardware User Manual for the S32K3X4EVB-Q172 Evaluation Board.PDF Rev A Oct 20, 2021 S32K3X4EVB-Q172_HW-UM EnglishUser Guide ( 1 )Getting Started with the S32K3X4EVB-Q172 Evaluation Board (/document/guide/getting-started-with-the-s32k3x4evb-q172-evaluation-board:GS-S32K3X4EVB-Q172)This page will help guide you through the process of learning about your S32K3X4EVB-Q172 evaluation boardHTML Oct 6, 2021 GS-S32K3X4EVB-Q172 EnglishBrochure ( 1 )S32K3 Arm Cortex-M7-based Automotive MCUs – Brochure (/docs/en/brochure/S32KBRA4.pdf)The S32K3 family includes scalable 32-bit Arm Cortex-M7 based MCUs in single, dual and Lockstep core configurations supporting up to ASIL D level safety.Features include a hardware security subsystem with NXP firmware, support for firmware over-the-air (FOTA) updates, and ISO 26262 compliant Real-Time Drivers (RTD) software package for AUTOSARTM and non-AUTOSAR.PDF Rev 0 Oct 19, 2021 S32KBRA4 EnglishErrata ( 1 )Mask Set Errata for Mask 0P55A/1P55A - Errata (/webapp/Download?colCode=S32K3X4-0P55A-1P55A-ERRATA)This report applies to mask 0P55A/1P55A for these products S32K344, S32K324 and S32K314PDF Rev 14 Oct 14, 2021 S32K3X4-0P55A-1P55A-ERRATA EnglishProduct Brief ( 4 )S32 Safety Software Framework (SAF) for S32K3xx Microcontrollers - Product Brief (/docs/en/product-brief/S32K3xx-SAF-PB.pdf)The S32 Safety Software Framework (SAF) is a software product containing software components for establishing the safety foundation for customer’s safety applications compliant with ISO 26262 functional safety.PDF Rev 1 Sep 30, 2021 858.4 KB S32K3xx-SAF-PB EnglishStructural Core Self-Test Library (SCST) for S32K3xx Microcontrollers - Product Brief (/docs/en/product-brief/S32K3xx-SCST-PB.pdf)The SCST (Structural Core Self-Test) Library is the software product used for the runtime detection of permanent HW faults in the MCU core.PDF Rev 1 Oct 14, 2021 S32K3xx-SCST-PB EnglishReal-Time Drivers (RTD) for S32K3xx Microcontrollers – Product Brief (/docs/en/product-brief/RTD-S32K3-PB.pdf)S32-based platform products offer Real-Time Drivers (RTD) software supporting both AUTOSAR and non-AUTOSAR (similar to traditional SDKs) applications.PDF Rev 1.5 Nov 11, 2021 397.5 KB RTD-S32K3-PB EnglishInter-Platform Communication Framework (IPCF) - Product Brief (/docs/en/product-brief/IPCFPB.pdf)Inter-Platform Communication Framework (IPCF) is a subsystem which enables applications, running on multiple homogenous or heterogenous processing cores, located on the same chip or different chips, running on different operating systems (AUTOSAR, FreeRTOS etc.), to communicate over various transport interfaces (Shared Memory, etc.).PDF Rev 1 Oct 13, 2021 441.4 KB IPCFPB EnglishDesign ResourcesDesign Tools & Files ( 4 )Printed Circuit Boards and Schematics ( 3 )S32K3X4EVB-Q172 Evaluation Board – REV A Design Files (/webapp/Download?colCode=S32K3X4EVBQ172_CAD_FILES_REVA)Design Files REV A for the S32K3X4EVB-Q172 Evaluation Board.ZIP Rev A Oct 20, 2021 S32K3X4EVBQ172_CAD_FILES_REVAS32K3X4EVB-Q172 Evaluation Board – REV A Schematics (/webapp/Download?colCode=S32K3X4EVB-Q172_SCH)Schematics REV A for the S32K3X4EVB-Q257 Evaluation Board.PDF Rev A Oct 20, 2021 S32K3X4EVB-Q172_SCHDOWNLOAD (/WEBAPP/DOWNLOAD?COLCODE=S32K3X4EVBQ172_CAD_FILES_REVA)DOWNLOAD (/WEBAPP/DOWNLOAD?COLCODE=S32K3X4EVB-Q172_SCH)S32K3 MCUs for General Purpose – REV A Hardware Design Package (/webapp/Download?colCode=S32K3_HW-DesignPackage)Hardware considerations for the S32K3xx MCUs, covering power considerations, bulk/bypass and decoupling required capacitors, reset, crystal, Ethernet and QSPI configurations, and PCB layout recommendations.ZIP Rev A Sep 29, 2021 8.6 MB S32K3_HW-DesignPackageCalculators ( 1 )S32K Power Estimation Tool (PET) (/design/automotive-software-and-tools/s32k-power-estimation-tool-pet:S32K-PET)S32K PET provides a user interface to generate a power profile for an application use case quickly; it also helps calculate a first estimate of the average power consumption for developing automotive battery-operated applicationsDOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/S32K-POWER-ESTIMATION-TOOL-PET:S32K-PET?TAB=DESIGN_TOOLS_TAB)SoftwareEmbedded Software ( 3 )Embedded Software ( 3 )S32 Safety Software Framework (SAF) (/design/automotive-software-and-tools/s32-safety-software-framework-saf:SAF)The S32 Safety Software Framework (SAF) is a software product containing software components for establishing the safety foundation for customer’s safety applications compliant with ISO 26262 functional safety.DOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/S32-SAFETY-SOFTWARE-FRAMEWORK-SAF:SAF?TAB=DESIGN_TOOLS_TAB)Automotive Math and Motor Control Library (AMMCLib) (/design/automotive-software-and-tools/automotive-math-and-motor-control-library-ammclib:AMMCLIB)The Automotive Math and Motor Control Library (AMMCLib) set is a collection of production-ready, easy-to-use, software libraries for rapid development of motor control and other real-time embedded systems.DOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/AUTOMOTIVE-MATH-AND-MOTOR-CONTROL-LIBRARY-AMMCLIB:AMMCLIB?TAB=DESIGN_TOOLS_TAB)Model-Based Design Toolbox (MBDT) (/design/automotive-software-and-tools/model-based-design-toolbox-mbdt:MBDT)The NXP Model-Based Design Toolbox (MBDT) is a comprehensive collection of tools that plug into the MATLAB and Simulink model-based designenvironment to support fast prototyping, verification, and validationDOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/MODEL-BASED-DESIGN-TOOLBOX-MBDT:MBDT?TAB=DESIGN_TOOLS_TAB)Development Software ( 4 )IDE and Build Tools ( 2 )S32 Design Studio for S32 Platform (/design/software/development-software/s32-design-studio-ide/s32-design-studio-for-s32-platform:S32DS-S32PLATFORM)The S32 Design Studio is a tool suite for developing your applications for NXP Automotive and Ultra-Reliable MicrocontrollersDOWNLOAD OPTIONS (/DESIGN/SOFTWARE/DEVELOPMENT-SOFTWARE/S32-DESIGN-STUDIO-IDE/S32-DESIGN-STUDIO-FOR-S32-PLATFORM:S32DS-S32PLATFORM?TAB=DESIGN_TOOLS_TAB)S32K3 Standard Software (/webapp/swlicensing/sso/downloadSoftware.sp?catid=SW32K3-STDSW-D)S32K3 Standard Software includes Real Time Drivers for AUTOSAR® and non-AUTOSAR operating systems, Standard HSE Security firmware, SafetyPeripheral Drivers, an Inter-Platform Communication Framework (IPCF) for communications between the Cortex-M7 cores. Additionally user also get access to Real Time Driver of FS26 SBC, S32 Design Studio IDE and EB tresos Studio.EXTERNAL Rev 0 Sep 30, 2021 null KB SW32K3-STDSW-DDOWNLOAD (/WEBAPP/SWLICENSING/SSO/DOWNLOADSOFTWARE.SP?CATID=SW32K3-STDSW-D)Test, Debug and Analyzer Software ( 1 )FreeMASTER Run-Time Debugging Tool (/design/software/development-software/freemaster-run-time-debugging-tool:FREEMASTER)Graphical PC host tool to control and debug embedded applications in run-time.DOWNLOAD OPTIONS (/DESIGN/SOFTWARE/DEVELOPMENT-SOFTWARE/FREEMASTER-RUN-TIME-DEBUGGING-TOOL:FREEMASTER?TAB=DESIGN_TOOLS_TAB)Host Device Drivers ( 1 )Inter-Platform Communication Framework (IPCF) (/design/automotive-software-and-tools/inter-platform-communication-framework-ipcf:IPCF)DOWNLOAD (/WEBAPP/DOWNLOAD?COLCODE=S32K3_HW-DESIGNPACKAGE)Get HelpInter-Platform Communication Framework (IPCF) is a subsystem which enables applications, running on multiple homogenous or heterogenous processing cores, located on the same chip or different chips, running on different operating systems (AUTOSAR, FreeRTOS etc.), to communicate over various transport interfaces (Shared Memory, etc.).DOWNLOAD OPTIONS (/DESIGN/AUTOMOTIVE-SOFTWARE-AND-TOOLS/INTER-PLATFORM-COMMUNICATION-FRAMEWORK-IPCF:IPCF?TAB=DESIGN_TOOLS_TAB)RECOMMENDED COMMUNITIESS32K S32 Design Studio MBDT Community Articles FreeMASTERSUGGESTED LINKSFunctional Safety documents AVAILABLE | Require access to the SafeAssure NDA group(//)ABOUT NXP (///COMPANY/OUR-COMPANY/ABOUT-NXP:ABOUT-NXP)CAREERS (///ABOUT/CAREERS-AT-NXP:CAREERS)INVESTORS (///)MEDIA (//)CONTACT (///COMPANY/ABOUT-NXP/CONTACT-US:CONTACTUS)SUBSCRIBE (///SUBSCRIPTION-CENTER)(///NXP)(///company/nxp-semiconductors)(///NXPsemi)Privacy (///about/privacy:PRIVACYPRACTICES)Terms of Use (///about/terms-of-use:TERMSOFUSE)Terms of Sale (///about/our-standard-terms-and-conditions-of-sale-counter-offer:TERMSCONDITIONSSALE)Slavery and Human Trafficking Statement (///company/about-nxp/sustainability/social-responsibility/labor-and-human-rights:LABOR-AND-HUMAN-RIGHTS)Accessibility (///company/our-company/about-nxp/accessibility:ACCESSIBILITY)©2006-2022 NXP Semiconductors. All rights reserved.Search NXP Community SEARCH (HTTPS:///T5/FORUMS/SEARCHPAGE/TAB/MESSAGE?Q=) News Jan 4, 2022 | Read More (https:///news-releases/news-release-details/nxp-advances-iot-connectivity-industrys-first-secure-tri-radio)。

PY32F030系列32位ARM

1.产品特性◼内核—32位ARM®Cortex®-M0+—最高48MHz工作频率◼存储器—最大64Kbytes flash存储器—最大8Kbytes SRAM◼时钟系统—内部4/8/16/22.12/24MHz RC振荡器(HSI)—内部32.768KHz RC振荡器(LSI)—4~32MHz晶体振荡器(HSE)—32.768KHz低速晶体振荡器(LSE)—PLL(支持对HSI或者HSE的2倍频)◼电源管理和复位—工作电压:1.7V~5.5V—低功耗模式:Sleep和Stop—上电/掉电复位(POR/PDR)—掉电检测复位(BOR)—可编程的电压检测(PVD)◼通用输入输出(I/O)—多达30个I/O,均可作为外部中断—驱动电流8mA—4个GPIO支持超强灌电流,可配置为80mA/60mA/40mA/20mA◼3通道DMA控制器◼1x12-bit ADC—支持最多10个外部输入通道PY32F030系列32位ARM®Cortex®-M0+微控制器数据手册—输入电压转换范围:0~VCC◼定时器—1个16bit高级控制定时器(TIM1)—4个通用的16位定时器(TIM3/TIM14/TIM16/TIM17)—1个低功耗定时器(LPTIM),支持从stop模式唤醒—1个独立看门狗定时器(IWDT)—1个窗口看门狗定时器(WWDT)—1个SysTick timer—1个IRTIM◼RTC◼通讯接口—2个串行外设接口(SPI)—2个通用同步/异步收发器(USART),支持自动波特率检测—1个I2C接口,支持标准模式(100kHz)、快速模式(400kHz),支持7位寻址模式◼支持4位7段共阴极LED数码管—可循环扫描1位、2位、3位、4位数字◼硬件CRC-32模块◼2个比较器◼唯一UID◼串行单线调试(SWD)◼工作温度:-40~85℃◼封装LQFP32,QFN32,TSSOP20,QFN20目录1.产品特性 (1)2.简介 (4)3.功能概述 (6)3.1.Arm®Cortex®-M0+内核 (6)3.2.存储器 (6)3.3.Boot模式 (6)3.4.时钟系统 (7)3.5.电源管理 (7)3.5.1.电源框图 (7)3.5.2.电源监控 (8)3.5.3.电压调节器 (9)3.5.4.低功耗模式 (10)3.6.复位 (10)3.6.1.电源复位 (10)3.6.2.系统复位 (10)3.7.通用输入输出GPIO (10)3.8.DMA (10)3.9.中断 (10)3.9.1.中断控制器NVIC (11)3.9.2.扩展中断EXTI (11)3.10.模数转换器ADC (11)3.11.定时器 (12)3.11.1.高级定时器 (12)3.11.2.通用定时器 (12)3.11.3.低功耗定时器 (13)3.11.4.IWDG133.11.5.WWDG (13)3.11.6.SysTick timer (13)3.12.实时时钟RTC (13)3.13.I2C接口 (14)3.14.通用同步异步收发器USART (14)3.15.串行外设接口SPI (16)3.16.SWD (16)4.引脚配置 (17)4.1.端口A复用功能映射 (31)4.2.端口B复用功能映射 (32)4.3.端口F复用功能映射 (33)5.存储器映射 (34)6.电气特性 (38)6.1.测试条件 (38)6.1.1.最小值和最大值 (38)6.1.2.典型值 (38)6.2.绝对最大额定值 (38)6.3.工作条件 (39)6.3.1.通用工作条件 (39)6.3.2.上下电工作条件 (39)6.3.3.内嵌复位和LVD模块特性 (39)6.3.4.工作电流特性 (40)6.3.5.低功耗模式唤醒时间 (41)6.3.6.外部时钟源特性 (42)6.3.7.内部高频时钟源HSI特性 (44)6.3.8.内部低频时钟源LSI特性 (44)6.3.9.锁相环PLL特性 (44)6.3.10.存储器特性 (45)6.3.11.EFT特性 (45)6.3.12.ESD&LU特性 (45)6.3.13.端口特性 (45)6.3.14.NRST引脚特性 (46)6.3.15.ADC特性 (46)6.3.16.比较器特性 (47)6.3.17.温度传感器特性 (48)6.3.18.定时器特性 (48)6.3.19.通讯口特性 (49)7.封装信息 (53)7.1.LQFP32封装尺寸 (53)7.2.QFN32封装尺寸 (54)7.3.QFN20封装尺寸 (55)7.4.TSSOP20封装尺寸 (56)8.订购信息 (57)9.版本历史 (58)2.简介PY32F030系列微控制器采用高性能的32位ARM®Cortex®-M0+内核,宽电压工作范围的MCU。

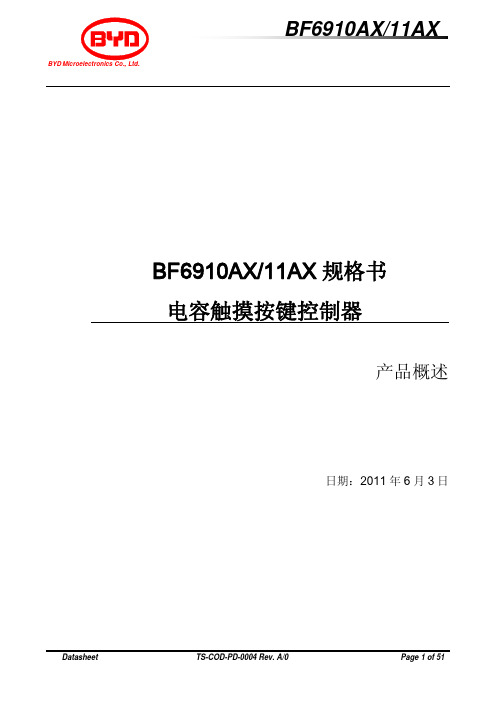

BF6910(BF6911)ASXX规格书

3.1 引脚图 ....................................................................................................................................................... 6 3.2 引脚描述 ................................................................................................................................................... 6

A31原理图

PH9 TMS PH10 TCK PH11 TDO

DEBUG

PL7 STDO PL8 STDI

DEBUG

PM0 BB-WAKE-HOST BB

PA12 LS-INT

PC4 N0CE0

PD12 LCD0-D12

PH12 TDI

PM1

PA13 USB0-DRV

PC5 N0RE

PD13 LCD0-D13

PH13 LCD-PWM

PH18 TWI2-SCK

Sensors PM7 CK32KO

CLOCK

PA19 LCD-SDA PA20 LCD-SCL PA21 FLASH-MODE PA22 FLASH-EN

LCD-eDP PC11 N0DQ3/eMMC-D3 PC12 N0DQ4/eMMC-D4

FLASH LED PC13 N0DQ5/eMMC-D5 PC14 N0DQ6/eMMC-D6

A

A

AllWinner Technology Co.,Ltd

Design Name

PAD_APP4_STD

Size Page Name

Rev

A3 BLOCK

Date:

Friday, March 01, 2013

Sheet

2

of 16

5

4

3

2

1

5

4

3

2

1

POWER TREE

3.5V~5V@2A

PS

AXP

CPUS VDD 1.1V for SOC (ON)

3.0V@30mA

VCC-RTC

RTC VCC 3.0V for SOC (ON)

ALDO1

3.3V@300mA

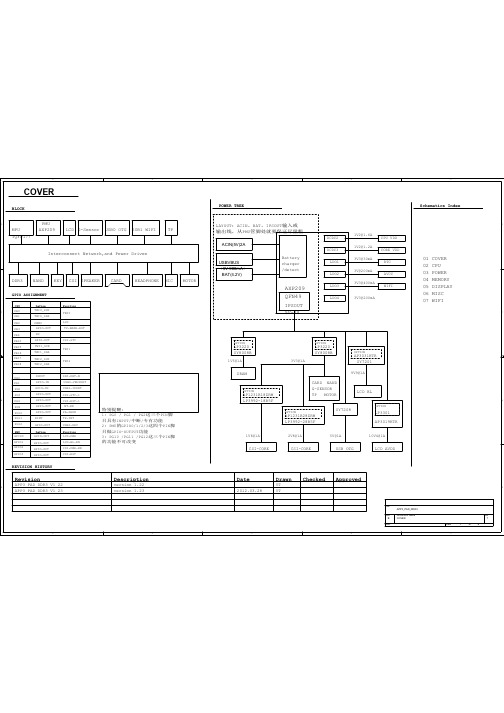

全志A31 平板原理图2014 05 07

VCC-PLL

VCC-PLL VCC-RTC VIO-RTC

RTC/PLL PWR GND-PLL

V19 R21 T19 RTC-VIO C65 4.7uF V18 C0603

VCC-RTC=3.0V VCC-PLL=3.0V

C63 104 C0402 GND UBOOT

MIPI CSI

TP2 TP4 TP5 TP6

STMS STCK STDO STDI

VDD-SYS

SW 3 sw_2p_4x3_h2

CPUS-TDI

1

CPUS Debug

A

Value Can Not be Changed.

1

C77 C78 10uF/25V 1uF C0805 C0402

A31-BGA609i VDD-CPUS U1B

GTXD0 GTXD1 GTXD2 GTXD3 UART1-TX UART1-RX UART1-RTS UART1-CTS SD0-DET GTXEN GTXCLK GRXD0 GRXD1 GRXD2 GRXD3 USB0-IDDET USB0-VBUSDET USB0-DRVVBUS USB-ICTRL GRXDV GRXCLK ETXRR 3G-IO-PW RON TP-INT TP-W AKEUP GCLKIN GMDC GMDIO

5

4

3

2

1

VCC-PA

VCC-PA=3.0V

C61 104 C0402 GND

CPU

VCC-HDMI=3.0V

U1A VCC-HDMI U1M

U1E

VCC-USB=3.0V

VCC-USB

GMAC LCD13.3V MISC

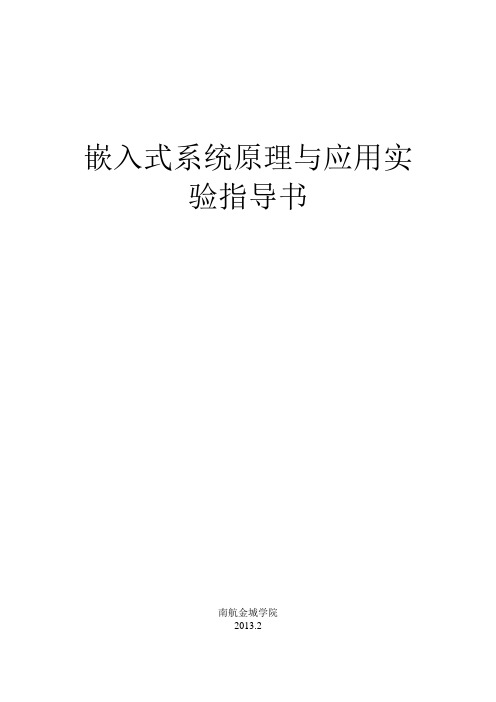

嵌入式系统原理与应用实验指导书(合稿+习题)

嵌入式系统原理与应用实验指导书南航金城学院2013.2目录目录 (1)第一部分试验箱硬件结构 (2)第二部分实验 (11)实验一ADS1.2集成开发环境练习 (11)实验二汇编指令实验1 (17)实验三汇编指令实验2 (20)实验四汇编指令实验3 (23)实验五ARM微控制器工作模式实验 (28)实验六 C语言程序实验 (33)实验七 C语言调用汇编程序实验 (36)实验八GPIO输出控制实验 (39)实验九GPIO输入实验 (46)实验十外部中断实验 (50)实验十一UART通讯实验 (56)实验十二I2C接口实验 (64)实验十三定时器实验 (75)实验十四PWM DAC实验 (81)实验十五ADC实验 (87)实验十六RTC实验 (94)实验十七步进电机控制实验 (101)实验十八直流电机控制实验 (105)附录1 DeviceARM2410 专用工程模板 ..................................................... 错误!未定义书签。

第一部分试验箱硬件结构MagicARM2410教学实验开发平台是一款可使用μC/OS-II、Linux和WinCE操作系统、支持QT、MiniGUI图形系统、集众多功能于一身的ARM9教学实验开发平台。

采用Samsung公司的ARM920T内核的S3C2410A微处理器,扩展有充足的存储资源和众多典型的嵌入式系统接口。

MagicARM2410实验箱参考如图1.1所示。

图1.1 MagicARM2410实验箱外观图MagicARM2410实验箱功能框图如图1.2所示。

图1.2 MagicARM2410实验箱功能框图1.1 S3C2410A芯片简介S3C2410A是Samsung公司推出的16/32位RISC处理器(ARM920T内核),适用于手持设备、POS机、数字多媒体播放设备等等,具有低价格、低功耗、高性能等特点。

智能家居毕业设计论文

智能家居毕业设计论文【篇一:智能家居毕业设计】某别墅智能家居系统设计摘要随着计算机网络技术和信息技术的进步,智能家居得到了前所未有的发展,居民对住宅的功能以及质量提出了更多、更高的要求,智能化住宅以其安全舒适、信息通畅、服务完善而深受住户们的喜爱,智能住宅成为现代化住宅的必然发展趋势。

因此研究并开发出适合人们要求的智能化产品具有很重要的意义。

怎样把电气智能化,怎样安排家居格局,我们就涉及到了家居布线系统。

家居布线系统就是把电话、有线电视、电脑网络、影音系统、家庭自动化控制系统的布线统一规划、布局、集中管理,为实现家具智能化提供网路平台。

采用综合布线方式,使得家庭内部布线系统具有良好的扩展性和可升级性,满足不同用户现在和未来的需求。

本论文设计的智能家居布线系统能充分实现以下功能:1.将住宅内的控制系统、安防系统等系统连接起来,并让它们能够正常的工作;2.新型的布线系统让住宅更加的美观;3.让我们的住宅时刻处于一个安全的状态。

智能家居布线系统须遵循 tia/eia 570-a 家居电信布线的国家标准。

布线系统是实现连接功能是由配线箱进行连接,然后再分配到各个功能模块,让功能模块发挥自己的功能。

关键词:智能家居自动化,自动控制 ,信息化和智能化 ,家具综合布线abstractalong with the computer network technology and information technology progress,intelligent household got unprecedented development,residents of residential functionand quality put forward more and higher demand,intelligent residential to its safe andcomfortable,information unobstructed,and perfect serviceand favored by residents of the love,intelligent residentialbecome modern residential trend.so the research and the development of a suitable for people to requirements of the intelligent product has important significance.household telephone wiring system,cable tv,computernetwork,audio-visual systems,the family of the automaticcontrol system of unified planning,layout and wiring forrealizing the centralized management,providing a networkplatform,intelligent ing the comprehensivewiring,internal cabling system has good family theexpansibility and scalability,meet different users of thepresent and future needs.in domestic and abroad existing intelligent home controlsystem are studied andanalyzed,the combination of domestic intelligence changes household to actual requirements standards,puts forward aset of multifunctional smart home wiring system designscheme. this thesis design intelligent household wiring systemcan fully realize the following functions:1.will inside the residence control system,secutity linksup and allow them to normal work;2.type of wiring system to make the house more beautiful;3.make our housing moment in a safe condition.intelligence lives in wiring system must follow tia/eia 570-ahouseholdtelecommunication wiring national standards.wiring systemis to realize the connect function is connected by wiring kit isincluded as standard,then assigned to each functionmodule,make function module play to ones own function.keyword:intelligent household automation;automaticcontrol;information and intelligence;household wiring system.目录第一章、绪论 ....................................................................... 11.1 选题意义、价值和目标 ........................................................ 11.2 课题研究方案 ................................................................ 1第二章智能家居的初步介绍 ...........................................................32.1 智能家居的发展概况 .......................................................... 32.1.1 国外智能家居的发展概况 ................................................ 32.1.2 国内智能家居的发展概况 ................................................ 32.2 智能家居系统的组成 .......................................................... 32.2.1 弱电子系统 ............................................................ 32.2.2 综合布线系统 .......................................................... 32.3 家庭信息接入箱 .............................................................. 32.3.2 近程访问 /控制 ......................................................... 42.3.3 中央控制器功能实现 .................................................... 42.3.4 交换机的工作原理 ...................................................... 4第三章智能家居各模块简单介绍 .......................................................53.1 娱乐 ........................................................................ 53.1.1 全宅音响模块 .......................................................... 53.2 安防 ........................................................................ 53.2.1 门磁、窗磁防盗报警模块 ................................................ 53.2.2 感烟探测报警模块 ...................................................... 53.2.3 煤气泄露报警模块 ...................................................... 6 3.2.4 报警及联动模块 ........................................................ 73.2.5 紧急求助模块 .......................................................... 73.3 便民 ........................................................................ 73.3.1 智能照明控制模块 ...................................................... 73.3.2 感应开关模块 .......................................................... 7第四章智能家居布线系统 .............................................................84.1 智能家居布线系统设计 ........................................................ 84.1.1 布线标准 .............................................................. 84.1.2 系统的需求分析 ........................................................ 84.2 智能家居布线硬件结构设计 .................................................... 84.2.1 综合布线的基本概念 .................................................... 84.2.2 系统硬件结构及特点 .................................................... 84.2.3 配线箱的工作原理 ...................................................... 94.2.4 具体施工方案 .......................................................... 94.3 布线系统的管理与维护 ........................................................ 94.3.1 布线的管理标准与措施 .................................................. 94.3.2 故障诊断 ............................................................ 10第五章云计算在安防系统中的前景与应用 ............................................. 115.1 云计算的运用前景..........................................................115.2 云计算的应用特性..........................................................115.2.1 安全性 .............................................................. 115.2.2 便携性 .............................................................. 115.2.3 性能的可用性 ........................................................ 115.2.4 数据访问 ............................................................ 11致谢 ............................................................................. 13参考文献 ......................................................................... 14附录 1智能家居施工图 ............................................................. 15第一章、绪论1.1 选题意义、价值和目标计算机、自动控制、通信技术以及数字化技术自20 世纪 90 年代后期以来,取得了迅猛的发展并日益渗透到各个领域。

DB_PCap01Ax_0301_电容测试芯片

RMS 噪声和精度 vs. 输出数据频率.......................................................................................................... 2-3

2.2.2

RMS 噪声 vs. 供电电压............................................................................................................................... 2-5

1.2 典型应用

湿度传感器 位移传感器 压力传感器 力学传感器 加速度传感器 倾角传感器 角度传感器 无线应用 夜位开关传感器 麦克风 MEMS 传感器

acam-messelectronic gmbh - Am Hasenbiel 27 - D-76297 Stutensee-Blankenloch - Germany - www.acam.de

3 转换器前端

3.1 CDC 测量原理 3.2 重要 CDC 参数 3.3 CDC 外部电路 3.4 连接电容传感器 3.5 选择放电电阻 3.6 补偿测量

4.1 串行通信

4 接口 (串行通信和 Pulse-Density通信) 4.2 PDM/PWM 和 GPIO

5 读 & 写寄存器 6 DSP, 存储 & 固件

1-1

4

1.3 内部结构原理图

图 1-1: 内部结构原理图

PCapØ1Ax-0301

1-2

acam-messelectronic gmbh - Am Hasenbiel 27 - D-76297 Stutensee-Blankenloch - Germany - www.acam.de

TG7100C 开发板用户手册说明书

《xxx芯片数据手册》文档版本发布日期TG7100C开发板用户手册版本:1.0版权@2020Contents1环境配置 (3)2代码编译 (5)3下载运行 (6)3.1芯片选择 (6)3.2配置程序下载方式 (7)3.3配置下载参数 (8)3.4下载程序 (9)1环境配置aos-cube是AliOS Things基于命令行的开发管理工具,主要功能包括:工程配置与编译、Image下载调试、组件生成、组件安装管理、设备管理、代码审查、OTA工具等功能。

它依赖于Python(64bits,2.7.14和3.5已验证)。

Linux 下AliOS-Things开发环境的搭建主要分为两部分:python和pip安装、基于pip安装aos-cube及相关的依赖包。

1.安装python、pip和git:$sudo apt-get install-y python python-pip git#完成python和pip安装后,再安装依赖库和aos-cube,步骤如下:$python-m pip install setuptools wheel aos-cube注解:如果在安装过程中遇到网络问题可以使用国内镜像。

###安装/升级pip$python-m pip install–trusted-host=-i https:///pypi/simple/–upgrade pip###基于pip依次安装第三方包和aos-cube$pip install–trusted-host=-i https:///pypi/simple/setuptools$pip install–trusted-host=-i https:///pypi/simple/wheel$pip install–trusted-host=-i https:///pypi/simple/aos-cube###如需要使用doubanio作备用源$pip install–trusted-host -i /simple/aos-cube###如需指定版本,可改成如aos-cube==0.2.50因涉及多种开发环境和具体版本的依赖,针对开发者的实际情况,还给出一种简单方便且不影响当前系统环境的方法—-基于虚拟环境virtualenv的方法,作为备用。

21.5寸M215HW03 V1

document version 1.1

2

Product Specification

N

Record of Revision

M215HW03 V1

Version and Date 0.1 2010/12/21 0.2 2011/2/10

1.0 2011/3/22

6.4 Timing Characteristics ................................................................................................................... 19

89117..01.000..7776670......2RSPC12561..ChMTTao11PeoiFomcniPSlneTpiwiikninangnceeLpnigAcberhCnatisoOldincDasCgrlfiiNtaioggnooMtorgn/nSnOyirmoLrLBcfapEFdidemaaaTD&uFenceblle.ktelncS.i.l.geCP..istei...gih...fatql..h.hit..i.ltn..u...c..baF.....Ue...aa....o.nrAn....r...tric.....at..c.s..ie...S.o...c..o....sn.......Tt.....n..ni.....A....e..g....e.........R...c.r....n.....t.......i.....oI........m s....nr..........t.......t......e.........ei......c...r..........n...n......s.........a......t.............l.....................U.....................s......................e............................O..............................n.................l...........y............................/...................2......................0.................1.....................1....................../...........9...................../...........1.................3..................................................................................................................................................................................................................................................................................................................................................................22222..........22222262854230123 AUO

64位加法器设计解析

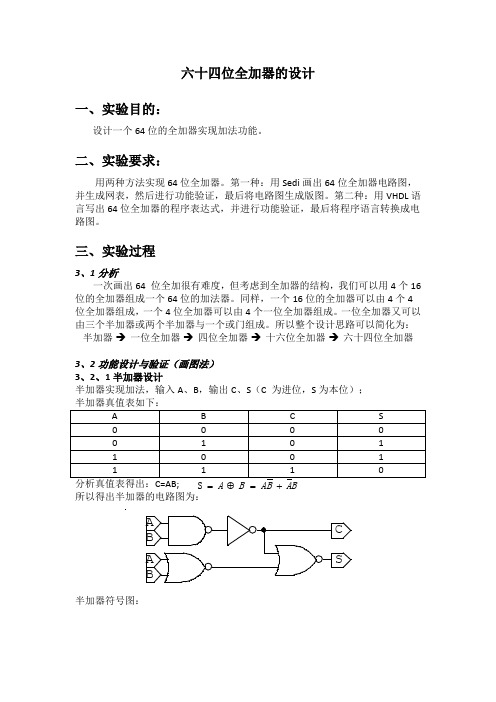

六十四位全加器的设计一、实验目的:设计一个64位的全加器实现加法功能。

二、实验要求:用两种方法实现64位全加器。

第一种:用Sedi画出64位全加器电路图,并生成网表,然后进行功能验证,最后将电路图生成版图。

第二种:用VHDL语言写出64位全加器的程序表达式,并进行功能验证,最后将程序语言转换成电路图。

三、实验过程3、1分析一次画出64 位全加很有难度,但考虑到全加器的结构,我们可以用4个16位的全加器组成一个64位的加法器。

同样,一个16位的全加器可以由4个4位全加器组成,一个4位全加器可以由4个一位全加器组成。

一位全加器又可以由三个半加器或两个半加器与一个或门组成。

所以整个设计思路可以简化为:半加器→一位全加器→四位全加器→十六位全加器→六十四位全加器3、2功能设计与验证(画图法)3、2、1半加器设计半加器实现加法,输入A、B,输出C、S(C 为进位,S为本位);所以得出半加器的电路图为:半加器符号图:SS C CB B A A 半加器()()()与非门 或非门 非门 3 、2、2一位全加器设计一位全加器可由三个半加器组成电路图如下:A B C iSC 半加器A B CS半加器A B CS半加器A B CS一位全加器的电路图符号如下:SSC iC iCCBBAA全加器3、2、3四位全加器的设计四位全加器可由四个一位全加器组成,四位全加器电路图如下:B 0A 0CS 3S 2S 1S 0C iB 3A 3B 2A 2B 1A 1全加器AB CC i S全加器A B CC i S全加器AB C C iS全加器A B CC i S四位全加器符号图如下:S 3S 3S 2S 2S 1S 1S 0S 0C iC iCC B 3B 3B 2B 2B 1B 1B 0B 0A 3A 3A 2A 2A 1A 1A 0A 0四位全加网表输入如下: 1、添加工作电压; Vvdd vdd GND 52、添加模型文件;.include "D:\iceda\TannerPro9\TSpice7.0\models\ml2_125.md" 3、添加输入信号;VA0 A0 GND PULSE (0 5 0 5n 5n 50n 100n) VA1 A1 GND PULSE (0 5 0 5n 5n 100n 200n) VA2 A2 GND PULSE (0 5 0 5n 5n 150n 300n) VA3 A3 GND PULSE (0 5 0 5n 5n 120n 240n) VB0 B0 GND PULSE (0 5 0 5n 5n 50n 100n) VB1 B1 GND PULSE (0 5 0 5n 5n 100n 200n) VB2 B2 GND PULSE (0 5 0 5n 5n 150n 300n) VB3 B3 GND PULSE (0 5 0 5n 5n 120n 240n) VCi Ci GND PULSE (0 5 0 5n 5n 50n 100n) 4、添加参数设置; .param l=0.5u5、输出设置;.print tran v(A0) v(A1) v(A2) v(A3) v(B0) v(B1) v(B2) v(B3) v(Ci) v(S0) v(S1) v(S2) v(S3) v(C) 6、设置分析;.tran/op 1n 400n method=bdf 总网表如下.include "D:\iceda\TannerPro9\TSpice7.0\models\ml2_125.md" Vvdd vdd GND 5VA0 A0 GND PULSE (0 5 0 5n 5n 50n 100n) VA1 A1 GND PULSE (0 5 0 5n 5n 100n 200n) VA2 A2 GND PULSE (0 5 0 5n 5n 150n 300n) VA3 A3 GND PULSE (0 5 0 5n 5n 120n 240n) VB0 B0 GND PULSE (0 5 0 5n 5n 50n 100n) VB1 B1 GND PULSE (0 5 0 5n 5n 100n 200n) VB2 B2 GND PULSE (0 5 0 5n 5n 150n 300n) VB3 B3 GND PULSE (0 5 0 5n 5n 120n 240n) VCi Ci GND PULSE (0 5 0 5n 5n 50n 100n) .param l=0.5u.tran/op 1n 400n method=bdf.print tran v(A0) v(A1) v(A2) v(A3) v(B0) v(B1) v(B2) v(B3) v(Ci) v(S0) v(S1) v(S2) v(S3) v(C) (由于步骤相同,以此为例,后面网表添加均简写)仿真结果:(四位全加器仿真图)3、2、4十六位全加器的设计十六位全加器可由四个四位全加器组成,十六位全加器电路图如下:A0A 1A 2A3A4A 5A 6A7A 8A 9A 10A11A12A 13A 14A15B0B 1B 2B3B4B 5B 6B7B8B 9B 10B11B12B 13B 14B15Ci S0S 1S 2S3S4S 5S 6S7S8S 9S 10S11S12S 13S 14S15C四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3四位全加A0A1A2A3B0B1B2B3C CiS0S1S2S3十六位全加器符号图如下:S 15S 15S 14S 14S 13S 13S 12S 12S 11S 11S 10S 10S 9S 9S 8S 8S 7S 7S 6S 6S 5S 5S 4S 4S 3S 3S 2S 2S 1S 1S 0S 0C iC iCCB 15B 15B 14B 14B 13B 13B 12B 12B 11B 11B 10B 10B 9B 9B 8B 8B 7B 7B 6B 6B 5B 5B 4B 4B 3B 3B 2B 2B 1B 1B 0B 0A 15A 15A 14A 14A 13A 13A 12A 12A 11A 11A 10A 10A 9A 9A 8A 8A 7A 7A 6A 6A 5A 5A 4A 4A 3A 3A 2A 2A 1A 1A 0A 0十六位全加器网表输入: 仿真图如下:3、2、5 六十四位全加器的设计六十四全加器可由四个十六位全加器组成,六十四位全加器电路图如下:CA48A49A 50A51A52A 53A54A 55A56A 57A58A59A60A61A62A63B48B 49B50B 51B52B 53B54B 55B56B57B 58000A32A 33A34A35A 36A37A 38A39A 40A41A 42A43A44A45A46A47B32B33B 34B35B 36B37B 38B39B40B 41B42B43B44B45B46B470A16A17A18A 19A20A 21A22A 23A24A 25A26A27A28A29A30A31B16B 17B18B 19B20B 21B22B23B 24B25B 26B27B28B29B30B3100A0A1A2A3A4A5A6A7A8A9A 10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B1500Ci 十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15C CiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15CCiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15CCiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15十六位全加器A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15B0B1B2B3B4B5B6B7B8B9B10B11B12B13B14B15CCiS0S1S2S3S4S5S6S7S8S9S10S11S12S13S14S15六十四位全加器符号图如下:S63S62S61S60S59S58S57S56S55S54S53S52S51S50S49S48S47S46S45S44S43S42S41S40S39S38S37S36S35S34S33S32S31S30S29S28S27S26S25S24S23S22S21S20S19S18S17S16S15S14S13S12S11S10S9S8S7S6S5S4S3S2S1S0CiC B63B62B61B60B59B58B57B56B55B54B53B52B51B50B49B48B47B46B45B44B43B42B41B39B40B38B37B36B35B34B33B32B31B30B29B28B27B26B25B24B23B22B21B20B19B18B17B16B15B14B13B12B11B10B9B8B7B6B5B4B3B2B1B0A63A62A61A60A59A58A57A56A55A54A53A52A51A50A49A48A47A46A45A44A43A42A41A40A39A38A37A36A35A33A34A32A31A30A29A28A27A26A25A24A23A22A21A20A19A18A17A16A15A14A13A12A11A10A9A8A7A6A5A4A3A2A1A0Ci 00000000000000C0000000网表添加如:六十四位全加器仿真图:六十四位全加器生成版图: 1、加压焊块将设计好的六十四位全加器的电路图例化进新的module 中,然后引用PAD 模块和端口。

Orient Display AFY1024600A0-7.0INTH-R LCD模块说明书

Specification for LCD ModuleAFY1024600A0-7.0INTH-RRevision DA Orient DisplayFY TFT Type1024600 Resolution 1024 x 600A0 Serial A07.0 7.0”, Module Dimension 164.80 x 99.80 x 6.75 mmI IPS DisplayN Top: -20~+70°C; Tstr: -30~+80°CT TransmissiveH High Brightness, 800 cd/m2R Resistive Touch Panel/ Controller EK79001HN+EK73215BCGA Or Compatible / LVDS InterfaceREVISION RECORDREV NO. REV DATE CONTENTS REMARKS O 2019-11-28 First release PreliminaryA 2020.2.12 CHANGED BACKLIGHT. Detia a pagel of 9.B 2020-03-16 Update EXTERNAL DIMENSIONS Detia apagel of 6C 2020-04-10 Update Module power consumption ANDLED power consumption Detia as pagel of 4D2020-05-04 Update EXTERNAL DIMENSION in page 5CONTENTS1. GENERAL INFORMATION (4)2. ABSOLUTE MAXIMUM RATINGS (4)3. ELECTRICAL CHARACTERISTICS (4)4. BACKLIGHT CHARACTERISTICS (4)5. EXTERNAL DIMENSIONS (5)6. ELECTRO-OPTICAL CHARACTERISTICS (6)7. INTERFACE DESCRIPTION......................................................... (9)8. LVDS CHARACTERISTICS (10)9. POWER SEQUENCE............................................................... .. (15)10. RELIABILITY TEST CONDITIONS (16)11. INSPECTION CRITERION (17)12. HANDLING PRECAUTIONS (17)13. PRECAUTION FOR USE (18)14. PACKING SPECIFICATION (18)No. ItemContentsUnit 1 LCD size 7.0 inch (Diagonal)/ 2 LCD typeIPS/NormallyBlack/TRANSMISSIVE(ANTI-GLARE) / 3 Viewing direction(eye) Free/ 4 Resolution(H*V)1024*600 Pixels / 5 Module size (L*W*H) 164.8*99.8*6.75 mm 6 Active area (L*W) 154.21*85.92 mm 7 Pixel pitch (L*W) 0.1506* 0.1432 mm 8 Interface typeLVDS Interface / 9 Module power consumption 4.905W 10 Back light type White LED/ 11 Driver IC EK79001HN+EK73215BCGA or compatible / 12WeightTBDg 2.ABSOLUTE MAXIMUM RATINGSItemSymbol Min Max Unit Power supply input voltage (LCM) VDD -0.5 5.0 V Backlight current (normal temp.) ILED - 600 mA Operation temperature Top -20 70 °C Storage temperature Tst -30 80°C HumidityRH-90%(Max60°)RH3. ELECTRICAL CHARACTERISTICSDC CHARACTERISTICS (at Ta=25°C )ItemSymbol Min Typ Max Uni t NotePower supply input voltage (LCM) VDD 2.7 3.3 3.6 V I/O logic voltageVDDIO N/A N/A N/A V =VDD Input voltage 'H' level VIH 0.7VDD - VDD V Input voltage 'L' level VIL 0 - 0.3VDDV Power supply current IVDD - 90 - mA TFT gate on voltage GH N/A N/A N/A V Built in LCMTFT gate off voltageVGL N/A N/A N/A V Analog power supply voltageAVDD N/A N/A N/A V Differential input common mode voltageVcomN/AN/AN/AV4. BACKLIGHT CHARACTERISTICS(at Ta=25°C ,RH=60%)Item Symbol Min. Typ. Max. Unit NoteLED forward voltage VF 8.7 9.6 10.5 V LED forward current IF - 480 - mA LED power consumption PLED - 4.608 - W Note1 Number of LED - 24 PCS Connection mode - 3 in series *8 in parallel / LED life-time - 20000 - - Hrs Note2 Note1.Calculator Value for reference: IF*VF = PLEDNote2.The LED Life-time define as the estimated time to 50% degradation of initial brightness at Ta=25℃ and IF =480mA. The LED lifetime could be decreased if operating IF is larger than 480mA6. ELECTRO-OPTICAL CHARACTERISTICSNote1.Definition of contrast ratioContrast Ratio(CR) is defined mathematically by the following formula. For more information see FIG.2Average Surface Luminance with all white pixels (P1, P2, P3, P4, P5,P6,P7,P8,P9) Average Surface Luminance with all black pixels (P1, P2, P3, P4, P5,P6,P7,P8,P9) Note2.Definition of surface luminanceSurface luminance is the LCD surface from the surface with all pixels displaying white. For more information see FIG.2Lv = Average Surface Luminance with all white pixels(P1, P2, P3, P4, P5,P6,P7,P8,P9) Note3.Definiton of luminance uniformityThe luminance uniformity in surface luminance (δ WHITE ) is determined by measuring luminance at each test position 1 through 9, and then dividing the maximum luminance of 9 points luminance by minimum luminance of 9 points luminance. For more information see FIG.2Minimum Surface Luminance with all white pixels (P1, P2, P3, P4, P5,P6,P7,P8,P9) Maximum Surface Luminance with all white pixels (P1, P2, P3, P4, P5,P6,P7,P8,P9) Note4. Definition of Response timeThe response time is defined as the LCD optical switching time interval between “White” state and“Black”state.Rise time (T ON ) is the time between photo detector output intensity changed from 90% to 10%. And fall time (T OFF ) is the time between photo detector output intensity changed from 10% to 90%.For additional information see FIG1.Note5. Definition of color chromaticity (CIE1931)CIE (x, y) chromaticity ,The x,y value is determined by screen active area center position P5,For more information see FIG.2 Item Symbol ConditionMin Typ Max Unit Remark NoteResponse time Tr+ Tf - - 25 50 ms FIG.1 Note 4 Contrast ratio Cr 400 500 - --- FIG.2 Note 1 Surface Luminance Lv θ=0︒ 650 800 - cd/m2 FIG.2 Note 2 Luminance uniformity - θ=0︒ 75 80 - % FIG.2 Note 3 NTSC -θ=0︒ - 50 - % FIG.2 Note 5 Viewing angle rangeθ∅ = 90︒ 70 80 - deg FIG.3 Note 6∅ = 270︒ 70 80 - deg FIG.3 ∅ = 0︒ 70 80 - deg FIG.3 ∅ = 180︒7080 -deg FIG.3CIE (x, y) chromaticityRed x θ=0︒ ∅=0︒ Ta=25℃Typ -0.04 TBD Typ +0.04-FIG.2 CIE1931Note 5Red y TBD - Green x TBD - Green y TBD - Blue x TBD - Blue y TBD - White x TBD - White yTBD-Contrast Ratio = Yu=Note6. Definition of Viewing angleViewing angle is the angle at which the contrast ratio is greater than 10. angles are determined for thehorizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG.3For Viewing angle and response time testing, the testing data is base on Autronic-Melchers’s ConoScope or DMS series Instruments or compatible. For contrast ratio, Surface Luminance, Luminance uniformity and CIE,the testing data is base on TOPCON’s BM -5or BM-7 photo detector or compatible.Note: For TFT module, Gray scale reverse occurs in the direction of panel viewing angle.The definition of Response TimeFIG.1. Measuring method for Contrast ratio, surface luminance,Luminance uniformity, CIE (x, y) chromaticitySize:S≤5”(see Figure a) A : 5 mm B : 5 mm H,V : Active AreaLight spot size ∅=5mm(BM-5) or ∅=7.7 (BM-7)50cm distance orcompatible distance from the LCD surface to detector lens. test spot position :see Figure a.measurement instrument : TOPCON’s luminanc e meter BM-5 orFigure aBM-7 or compatible (see Figure c)AAP1P2P4P3P5HBB VSize:5”<S≤12.3”(see Figure b) H,V : Active AreaLight spot size ∅=5mm(BM-5) or ∅=7.7mm (BM-7)50cm distance or compatible distance from the LCD surface to detector lens test spot position :see Figure bmeasurem ent instrument : TOPCON’s luminance meter BM -5 or BM-7 or compatible (see Figure c)Figure bFigure cFIG.2. The definition of viewing angleDown Φ=270(6:00)θ=0UpΦ=90(12:00)Left Φ=180(9:00)θΦRight Φ=0(3:00)x zyBM-5/BM-77. LCM INTERFACE DESCRIPTIONInterface NO. PIN NAME I/O DESCRIPTION1 N/C Float No connection,Please float it2-3 VDD P Power supply for digital4 NC I Dither="L" , to enable internal dithering function; DITHB="H" , to disable internal dithering function;5 REST I Global reset pin. Active Low. Normally pull high.6 STBYB I Display on/off swich,”H” display off7 GND P Ground8 RXIN0- I/O LVDS data lane 0-9 RXIN0+ I/O LVDS data lane 0+10 GND P Ground11 RXIN1- I/O LVDS data lane 1-12 RXIN1+ I/O LVDS data lane 1+13 GND P Ground14 RXIN2- I/O LVDS data lane 2-15 RXIN2+ I/O LVDS data lane 2+16 GND P Ground17 RXCLKIN- I/O LVDS clk lane -18 RXCLKIN+ I/O LVDS clk lane +19 GND P Ground20 RXIN3- I/O LVDS data lane 3-21 RXIN3+ I/O LVDS data lane 3+22 GND P Ground23 NC Float No connection,Please float it24 BIST I SELB="L" for 8-bit LVDS;SELB="H" for 6-bit LVDS;25 INSEL Float SELB="L" for TTL Interface;SELB="H" for LVDS Interface;26 NC Float No connection,Please float it27 GND P Ground28 NC Float No connection,Please float it29 L/R I L/R="L" Scan direction from right to left;L/R="H" Scan direction from left to right;30 U/D I U/D="L" Scan direction from down to up;U/D="H" Scan direction from up to down;31 NC Float No connection,Please float it32-33 LEDK P LED Cathode for BL34 NC Float No connection,Please float it35-36 LEDA P LED ANODE for BL37 XR(NC) I X-Right38 YD(NC) I Y-Up39 XL(NC) I X-Left40 YU(NC) I Y-Bottom8.Lvds CHARACTERISTCiS8.1 Absolute maximum rating(GND=AGND=0V)T able 8.1 Absolute maximum rating8.2 Lvds mode DC electrical characteristicsT able 8.2 Lvds mode DC electrical characteristics 8.3PWM power tableTable 8.3 Power table8.4 Lvds mode AC electrical characteristicsTable 8.4 Lvds mode AC electrical characteristics 8.5Lvds FigureTable 8.5 Lvds Figure8.6Lvds mode data input format8.6.1 6 bit Lvds inputFigure 8.1 6 bit Lvds input 8.6.2 8 bit Lvds inputFigure 8.2 8 bit Lvds data input8.7 SDRRS TIMING DIAGRAMSDRRS(seamless display refresh rate switching)9.POWER SEQUENCE9.1. Power On/Off SequenceIn order to prevent IC from power on reset fail, the rising time (TPOR) of the digital power supply VDD should be maintained within the given spe cifications. Refer to “AC Characteristics” for more detail on timing.9.2. Power-On/Off Timing Sequence10. RELIABILITY TEST CONDITIONSNo. Test ItemTest ConditionInspection after test 1 High Temperature Storage +80C/240 hours Inspection after2~4hours storage at room temperature, the sample shall be free from defects:1.Current changing value before test andafter test is 50% larger ; 2. functiondefect:Non-display ,abn ormal-display,missing lines,Short lines ,ITOcorossion ; 3.visual defect:Air bubble in theLCD,Sealleak,Glass crack 。

播放器 全志A31原理图

D

P01: P02: P03: P04: P05: P06: P07: P08: P09: P10: P11: P12: P13:

C

REVISION HISTORY BLOCK POWER TREE GPIO ASSIGNMENT DRAM DRAM CPU PMU NAND CARD-USB-HDMI CAMERA&LCD&SDIO&BASEBAND WIFI&HOST MIC&KEY&IR

SATA_22P

1 2 3 4 5 6 7 8 9 10 11 12

GND1 GPIO0 GPIO3 PIO3 HRST CVDD1 VDD1 GND2 TEST PIO0 PIO1 CVDD2

P15 P14 P13 P12 P11 P10 P9 P8 P7 P6 P5 P4 P3 P2 P1 S7 S6 S5 S4 S3 S2 S1

2

B

ACIN

KEY 1_8V C196 C201 C205 C211 0.01u 0.01u 0.01u 0.01u RXP RXN TXN TXP

GPIO4 PIO1 R114 0R PIO2 PIO4 R110 R113 R111 4.7K

GPIO3 R109 0R USB_DET R107 7.5K ACIN

~

AC Line M GPS MOTO Battery Voltage Supply 3.55V-4.20V

24MHz

32768Hz

G-Sensor Grycroscope Compass Light Sensor

A

A

AllWinner Technology Co.,Ltd

Design Name

A33