L7386A中文资料

HT7136A中文资料

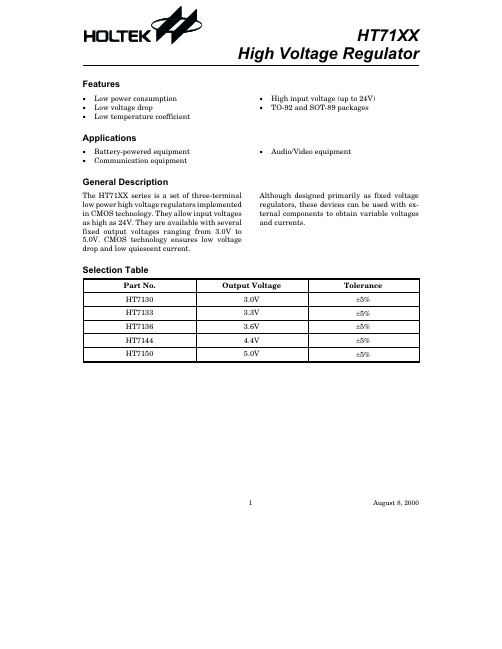

HT71XXHigh Voltage RegulatorSelection TablePart No.Output VoltageToleranceHT7130 3.0V ±5%HT7133 3.3V ±5%HT7136 3.6V ±5%HT7144 4.4V ±5%HT71505.0V±5%1August 8,2000Features·Low power consumption ·Low voltage drop·Low temperature coefficient·High input voltage (up to 24V)·TO-92and SOT-89packagesApplications·Battery-powered equipment ·Communication equipment·Audio/Video equipmentGeneral DescriptionThe HT71XX series is a set of three-terminal low power high voltage regulators implemented in CMOS technology.They allow input voltages as high as 24V.They are available with several fixed output voltages ranging from 3.0V to 5.0V.CMOS technology ensures low voltage drop and low quiescent current.Although designed primarily as fixed voltage regulators,these devices can be used with ex-ternal components to obtainvariable voltages and currents.Block DiagramPin AssignmentPad Assignment Pad CoordinatesUnit:m m Pad No.X Y 1-480.00-451.50287.50-444.503482.00-444.50Chip size:1374´1294(m m)2*The IC substrate should be connected to VDD in the PCB layout artwork.2August 8,2000Absolute Maximum RatingsSupply Voltage..............................-0.3V to28V Storage Temperature................-50°C to125°C Power Consumption.............................200mW Operating Temperature.................0°C to70°CNote:These are stress ratings only.Stresses exceeding the range specified under Absolute Maxi-mum Ratings may cause substantial damage to the device.Functional operation of this de-vice at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.Electrical CharacteristicsHT7130,+3.0V output typeHT7133,+3.3V output type Ta=25°C3August8,2000HT7144,+4.4V output type Ta=25°C4August8,2000Application CircuitsBasic circuits5August8,2000High output current positive voltage regulatorShort-Circuit protection by Tr1Circuit for increasing output voltageV V (1+R2R1)I R2OUT XX SS =+HT71XX6August 8,2000Circuit for increasing output voltageV OUT=V XX+V D1 Constant current regulatorI VR IOUTXXA SS=+Dual supply7August8,20008August 8,2000Copyright Ó2000by HOLTEK SEMICONDUCTOR INC.The information appearing in this Data Sheet is believed to be accurate at the time of publication.However,Holtek assumes no responsibility arising from the use of the specifications described.The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification,nor recommends the use of its products for application that may pres-ent a risk to human life due to malfunction or otherwise.Holtek reserves the right to alter its products without prior notification.For the most up-to-date information,please visit our web site at .Holtek Semiconductor Inc.(Headquarters)No.3Creation Rd.II,Science-based Industrial Park,Hsinchu,Taiwan,R.O.C.Tel:886-3-563-1999Fax:886-3-563-1189Holtek Semiconductor Inc.(Taipei Office)5F,No.576,Sec.7Chung Hsiao E.Rd.,Taipei,Taiwan,R.O.C.Tel:886-2-2782-9635Fax:886-2-2782-9636Fax:886-2-2782-7128(International sales hotline)Holtek Semiconductor (Hong Kong)Ltd.RM.711,Tower 2,Cheung Sha Wan Plaza,833Cheung Sha Wan Rd.,Kowloon,Hong Kong Tel:852-2-745-8288Fax:852-2-742-8657。

ST L7800AB AC SERIES 说明书

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!L7800AB/ACSERIESPRECISION 1A REGULATORS®November 1999s OUTPUT CURRENT IN EXCESS OF 1AsOUTPUT VOLTAGESOF 5;6;8;9;12;15;18;20;24Vs THERMAL OVERLOAD PROTECTIONs OUTPUT TRANSITION SOA PROTECTION s 2%OUTPUT VOLTAGE TOLERANCE sGUARANTEED IN EXTENDED TEMPERATURE RANGEDESCRIPTIONThe L7800A series of three-terminal positive regulators is available in TO-220and D 2PAK packages and several fixed output voltages,making it useful in a wide range of applications.These regulators can provide local on-card regulation,eliminating the distribution problems associated with single point regulation.Each type employs internal current limiting,thermal shut-down and safe area protection,making it essentially indestructible.If adequate heat sinking is provided,they can deliver over 1A output current.Although designed primarily as fixed voltage regulators,these devices can be used with external components to obtain adjustable voltages and currents.TO-220D 2PAKBLOCK DIAGRAM1/17CONNECTION DIAGRAM AND ORDERING NUMBERS (top view)TO-220D 2PAKTHERMAL DATASymbolParameterD 2PAK TO-220UnitR thj-ca se R thj-amb Thermal Resistance Junction-case Max Thermal Resistance Junction-ambient Max362.5350o C/W oC/WTypeTO-220D 2PAK (*)Output VoltageL7805AB L7805AC L7806AB L7806AC L7808AB L7808AC L7809AB L7809AC L7812AB L7812AC L7815AB L7815AC L7818AB L7818AC L7820AB L7820AC L7824AB L7824ACL7805ABV L7805ACV L7806ABV L7806ACV L7808ABV L7808ACV L7809ABV L7809ACV L7812ABV L7812ACV L7815ABV L7815ACV L7818ABV L7818ACV L7820ABV L7820ACV L7824ABV L7824ACVL7805ABD2T L7805ACD2T L7806ABD2T L7806ACD2T L7808ABD2T L7808ACD2T L7809ABD2T L7809ACD2T L7812ABD2T L7812ACD2T L7815ABD2T L7815ACD2T5V 5V 6V 6V 8V 8V 9V 9V 12V 12V 15V 15V 18V 18V 24V 24V(*)AVAILABLE IN TAPE AND REEL WITH ”-TR”SUFFIXABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V i DC Input Voltage (for V O =5to 18V)(for V O =20,24V)3540V VI o Output Current Internally limited P tot Power DissipationInternally limitedT op Operating Junction Temperature Range (for L7800AC )(for L7800AB )0to 150-40to 125o C o C T st gStorage Temperature Range-65to 150oCL7800AB/AC2/17L7800AB/AC APPLICATION CIRCUITSCHEMATIC DIAGRAM3/17TEST CIRCUITSFigure3:Ripple Rejection.Figure2:Load Regulation.Figure1:DC Parameter L7800AB/AC4/17*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.ELECTRICAL CHARACTERISTICS FOR L7805A (V i =10V,I o =1A,T j =0to 125o C (L7805AC),T j =-40to 125o C (L7805AB)unless otherwise specified)Symbol ParameterTest ConditionsMin.Typ.Max.Unit V o Output Voltage T j =25o C 4.95 5.1V V o Output Voltage I o =5mA to 1A P o ≤15W V i =7.5to 20V 4.85 5.2V ∆V o *Line RegulationV i =7.5to 25V I o =500mA V i =8to 12V V i =8to 12V T j =25o C V i =7.3to 20VT j =25o C710275052550mV mV mV mV ∆V o *Load RegulationI o =5mA to 1AI o =5mA to 1.5A T j =25o C I o =250to 750mA 2530810010050mV mV mV I d Quiescent Current T j =25oC4.366mA ∆I dQuiescent Current ChangeV i =8to 25V I o =500mAV i =7.5to 20VT j =25o C I o =5mA to 1A 0.80.80.5mA mA mA SVR Supply Voltage Rejection V i =8to 18V f =120HzI o =500mA 68dB V d Dropout Voltage I o =1AT j =25o C2V e N Output Noise Voltage B =10Hz to 100KHz T j =25oC10µV/V o R o Output Resistance f =1KHz 17m ΩI s c Short Circuit Current V i =35V T amb =25o C0.2A I scp Short Circuit Peack Current T j =25o C2.2A ∆V o∆TOutput Voltage Drift-1.1mV/o CL7800AB/AC5/17ELECTRICAL CHARACTERISTICS FOR L7806A(V i=11V,I o=1A,T j=0to125o C(L7806AC),T j=-40to125o C(L7806AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C 5.886 6.12V V o Output Voltage I o=5mA to1A P o≤15WV i=8.6to21V5.7666.24V∆V o*Line Regulation V i=8.6to25V I o=500mAV i=9to13VV i=9to13V T j=25o CV i=8.3to21V T j=25o C9113960603060mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.366mA∆I d Quiescent Current Change V i=9to25V I o=500mAV i=8.6to21V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=9to19V f=120HzI o=500mA65dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz17mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-0.8mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.L7800AB/AC6/17ELECTRICAL CHARACTERISTICS FOR L7808A(V i=14V,I o=1A,T j=0to125o C(L7808AC),T j=-40to125o C(L7808AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C7.8488.16V V o Output Voltage I o=5mA to1A P o≤15WV i=10.6to23V7.788.3V∆V o*Line Regulation V i=10.6to25V I o=500mAV i=11to17VV i=11to17V T j=25o CV i=10.4to23V T j=25o C 121551280804080mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.366mA∆I d Quiescent Current Change V i=11to25V I o=500mAV i=10.6to23V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=11.5to21.5V f=120HzI o=500mA62dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz18mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-0.8mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.L7800AB/AC7/17ELECTRICAL CHARACTERISTICS FOR L7809A(V i=15V,I o=1A,T j=0to125o C(L7809AC),T j=-40to125o C(L7809AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C8.8299.18V V o Output Voltage I o=5mA to1A P o≤15WV i=10.6to23V8.6599.35V∆V o*Line Regulation V i=10.6to25V I o=500mAV i=11to17VV i=11to17V T j=25o CV i=10.4to23V T j=25o C 121551290904590mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.366mA∆I d Quiescent Current Change V i=11to25V I o=500mAV i=10.6to23V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=11.5to21.5V f=120HzI o=500mA61dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz18mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-0.8mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.L7800AB/AC8/17ELECTRICAL CHARACTERISTICS FOR L7812A(V i=19V,I o=1A,T j=0to125o C(L7812AC),T j=-40to125o C(L7812AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C11.751212.25V V o Output Voltage I o=5mA to1A P o≤15WV i=14.8to27V11.51212.5V∆V o*Line Regulation V i=14.8to30V I o=500mAV i=16to22VV i=16to22V T j=25o CV i=14.5to27V T j=25o C 131661312012060120mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.466mA∆I d Quiescent Current Change V i=15to30V I o=500mAV i=14.8to27V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=15to25V f=120HzI o=500mA60dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz18mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-1mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.L7800AB/AC9/17ELECTRICAL CHARACTERISTICS FOR L7815A(V i=23V,I o=1A,T j=0to125o C(L7815AC),T j=-40to125o C(L7815AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C14.71515.3V V o Output Voltage I o=5mA to1A P o≤15WV i=17.9to30V14.41515.6V∆V o*Line Regulation V i=17.9to30V I o=500mAV i=20to26VV i=20to26V T j=25o CV i=17.5to30V T j=25o C 131661315015075150mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.466mA∆I d Quiescent Current Change V i=17.5to30V I o=500mAV i=17.5to30V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=18.5to28.5V f=120HzI o=500mA58dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz19mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-1mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.L7800AB/AC10/17ELECTRICAL CHARACTERISTICS FOR L7818A(V i=27V,I o=1A,T j=0to125o C(L7818AC),T j=-40to125o C(L7818AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C17.641818.36V V o Output Voltage I o=5mA to1A P o≤15WV i=21to33V17.31818.7V∆V o*Line Regulation V i=21to33V I o=500mAV i=24to30VV i=24to30V T j=25o CV i=20.6to33V T j=25o C 252810518018090180mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.566mA∆I d Quiescent Current Change V i=21to33V I o=500mAV i=21to33V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=22to32V f=120HzI o=500mA57dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz19mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-1mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.11/17ELECTRICAL CHARACTERISTICS FOR L7820A(V i=28V,I o=1A,T j=0to125o C(L7820AC),T j=-40to125o C(L7820AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C19.62020.4V V o Output Voltage I o=5mA to1A P o≤15WV i=23to35V19.22020.8V∆V o*Line Regulation V i=23to35V I o=500mAV i=26to32VV i=26to32V T j=25o CV i=23to32V T j=25o C 200200100200mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.566mA∆I d Quiescent Current Change V i=23to35V I o=500mAV i=23to35V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=24to35V f=120HzI o=500mA56dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz20mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-1mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.12/17ELECTRICAL CHARACTERISTICS FOR L7824A(V i=33V,I o=1A,T j=0to125o C(L7824AC),T j=-40to125o C(L7824AB)unless otherwise specified)Symbol Parameter Test Conditions Min.Typ.Max.Unit V o Output Voltage T j=25o C23.52424.5V V o Output Voltage I o=5mA to1A P o≤15WV i=27.3to38V232425V∆V o*Line Regulation V i=27to38V I o=500mAV i=30to36VV i=30to36V T j=25o CV i=26.7to38V T j=25o C 31351431240240120240mVmVmVmV∆V o*Load Regulation I o=5mA to1AI o=5mA to1.5A T j=25o CI o=250to750mA 25301010010050mVmVmVI d Quiescent Current T j=25o C 4.666mA∆I d Quiescent Current Change V i=27.3to38V I o=500mAV i=27.3to38V T j=25o CI o=5mA to1A 0.80.80.5mAmAmASVR Supply Voltage Rejection V i=28to38V f=120HzI o=500mA54dB V d Dropout Voltage I o=1A T j=25o C2Ve N Output Noise Voltage B=10Hz to100KHz T j=25o C10µV/V oR o Output Resistance f=1KHz20mΩI s c Short Circuit Current V i=35V T amb=25o C0.2AI scp Short Circuit Peack Current T j=25o C 2.2A∆V o∆TOutput Voltage Drift-1.5mV/o C*Load and line regulation are specified at constant junction temperature.Changes in V o due to heating effects must be taken into account separately.Pulse testing with low duty cycle is used.13/17APPLICATIONS INFORMATIONDESIGN CONSIDERATIONSThe L7800A Series of fixed voltage regulators are designed with Thermal Overload Protection that shuts down the circuit when subjected to an excessive power overload condition,Internal Short-circuit Protection that limits the maximum current the circuit will pass,and Output Transistor Safe-Area Compensation that reduces the output short-circuit current as the voltage across the pass transistor is increased.In many low current applications,compensation capacitors are not required.However,it is recommended that the regulator input be bypassed with a capacitor if the regulator is connected to the power supply filter with long wire lengths,or if the output load capacitance is large.An input bypass capacitor should be selected to provide good high-frequency characteristics to insure stable operation under all load conditions.A 0.33µF or larger tantalum,mylar,or other capacitor having low internal impedance at high frequencies should be chosen.The bypass capacitor should be mounted with the shortest possible leads directly across the regulators input terminals.Normally good construction techniques should be used to minimize ground loops and lead resistance drops since the regulator has no external sense lead.Figure 4:Current Regulator.Figure 5:Adjustable Output Regulator.Figure 6:Current Boost Regulator.Figure 7:Short-circuit Protection.V O ,7.0V to 20V V i –V O ≥2.0VThe addition of an operational amplifier allows adjustment to higher or intermediate values while retaining regulation characteristics.The minimum voltage obtainable with this arrangement is 2.0V greater than the regulator voltage.The circuit of figure 6can be modified to provide supply protection against short circuit by adding a short-circuit sense resistor,R sc ,and an additional PNP transistor.The current sensing PNP must be able to handle the short-circuit current of the three-terminal regulator.Therefore,a four-ampere plastic power transistor is specified.R 1=V BEQ 1I REQ −I Q 1βQ 1I O =IREG+Q 1(I REG −V BEQ 1R 1)I O =V XXR 1+I d 14/17DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 4.40 4.600.1730.181C 1.23 1.320.0480.051D 2.402.720.0940.107D1 1.270.050E 0.490.700.0190.027F 0.610.880.0240.034F1 1.14 1.700.0440.067F2 1.14 1.700.0440.067G 4.95 5.150.1940.203G1 2.4 2.70.0940.106H210.010.400.3930.409L216.40.645L413.014.00.5110.551L5 2.65 2.950.1040.116L615.2515.750.6000.620L7 6.2 6.60.2440.260L9 3.5 3.930.1370.154DIA.3.75 3.850.1470.151L6ACDED 1FGL7L2Dia.F 1L5L4H 2L9F 2G 1TO-220MECHANICAL DATAP011C15/17DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 4.4 4.60.1730.181A1 2.49 2.690.0980.106B 0.70.930.0270.036B2 1.14 1.70.0440.067C 0.450.60.0170.023C2 1.23 1.360.0480.053D 8.959.350.3520.368E 1010.40.3930.409G 4.88 5.280.1920.208L 1515.850.5900.624L2 1.27 1.40.0500.055L31.41.750.0550.068L2L3LB2B GEAC2DCA1DETAIL”A”DETAIL”A”A 2P011P6/FTO-263(D 2PAK)MECHANICAL DATA16/17Information furnished is believed to be accurate and reliable.However,STMicroelectroni c s assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectroni c s.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all informati o n previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems withoutexpress written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics©1999STMicroelectronics–Printed in Italy–All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-China-Finland-France-Germany-Hong Kong-India-Italy-Japan-Malaysia-Malta-MoroccoSingapore-Spain-Sweden-Switzerland-United Kingdom-U.S.A..17/17。

A67L8316资料

A67L8316/A67L8318/ A67L7332/A67L7336 Series

256K X 16/18, 128K X 32/36 Preliminary

Features

n Fast access time: 4.5/5.0/6.0 ns (117/100/83MHz) n Direct Bus Alternation between READ and WRITE cycles allows 100% bus utilization n Signal +3.3V ± 5% power supply n Individual Byte Write control capability n Clock enable ( CEN ) pin to enable clock and suspend operations n Clock-controlled and registered address, data and control signals n Registered output for pipelined applications n Three separate chip enables allow wide range of options for CE control, address pipelining n Internally self-timed write cycle n Selectable BURST mode (Linear or Interleaved) n SLEEP mode (ZZ pin) provided n Available in 100 pin LQFP package

元器件交易网

A67L8316/A67L8318/ A67L7332/A67L7336 Series

AN7384N中文资料

4 13

1.8kΩ

5

30µA

元器件交易网

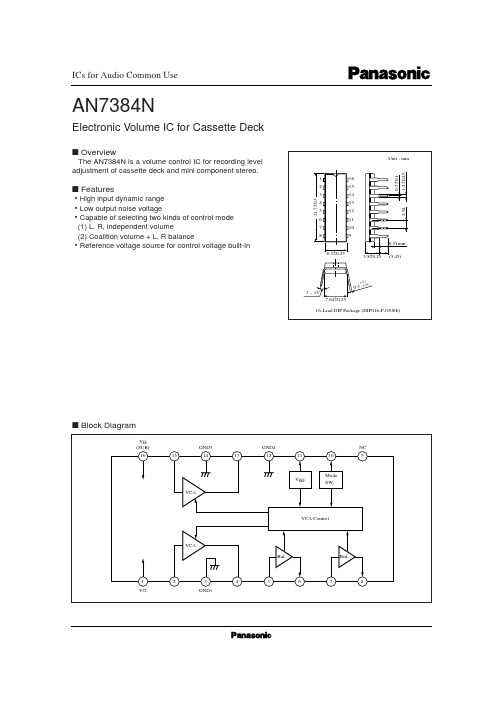

AN7384N

s Pin Descriptions (Cont.)

Pin No.

Pin Name

Description

6

A-ch. Control Voltage Output

Control DC voltage buffer output pin

Tstg

ICs for Audio Common Use

Rating

Unit

±12

V

30

mA

800

mW

–20 ~ + 70

˚C

–55 ~ +150

˚C

s Recommended Operating Range (Ta = 25˚C)

Parameter Operating Supply Voltage Range

10

Volume Mode/Balance Low – independent volume control

Mode Switching

High – coalition volume balance control

mode

10

Vref 2

11

Reference Voltage Output

Reference voltage output pin

Negative Side Circuit Current Attenuation – 1 Attenuation – 2 Channel Balance – 1 Distortion Rate – 1 Distortion Rate – 2 Noise Output Voltage – 1 Noise Output Voltage – 2 Channel Balance – 2 Max. Input Voltage Max. Output Voltage Control Voltage Range

7383-G1C3-ATVA中文资料

元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSFeatures˙Popular T-1 3/4 diameter package. ˙Choice of various viewing angles. ˙Available on tape and reel. ˙Reliable and robust. ˙ESD-withstand voltage: up to 4KV. ˙The product itself will remain within RoHS compliant version. ˙UV resistant epoxyDescriptions˙The series is specially designed for applications requiring higher brightness. ˙The LED lamps are available with different colors, intensities, epoxy colors, etc. ˙Superior performance in outdoor environmentApplications˙Color Graphic Signs ˙Message boards ˙Variable message signs (VMS) ˙Commercial outdoor advertisingDevice Selection GuideLED Part No.7383/G1C3-ATVA/MS 7383/G1C3-ATVA/P/MSChip Mterial InGaN InGaNEmitted Color Super Green Super GreenLens Color Water Clear Water ClearStopper No YesEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 1 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSPackage DimensionsStopper type No Stopper typeNotes: ˙All dimensions are in millimeters, tolerance is 0.25mm except being specified. ˙Lead spacing is measured where the lead emerges from the package. ˙Protruded resin under flange is 1.5mm Max LED.Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 2 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSAbsolute Maximum Ratings (Ta=25℃)Parameter Forward Current Pulse Forward Current*1 Operating Temperature Storage Temperature Electrostatic Discharge*2Symbol IF IFP Topr Tstg ESD Tsol Pd Iz VRRating 30 100 -40 ~ +85 -40 ~ +100 4K 260 ±5 120 100 5Units mA mA ℃ ℃ V ℃ mW mA VSoldering Temperature Power Dissipation Zener Reverse Current Reverse VoltageNotes: *1:IFP Conditions--Pulse Width≦10msec and Duty≦1/10. *2:Soldering time≦5 seconds.Electro-Optical Characteristics (Ta=25℃)Parameter Forward Voltage Zener Reverse Voltage Luminous Intensity Viewing Angle Peak Wavelength Dominant Wavelength Spectrum Radiation Bandwidth Reverse Current Symbol VF Vz IV 2θ1/2 λp λd Δλ IR Condition IF=20mA IZ=5mA IF=20mA IF=20mA IF=20mA IF=20mA IF=20mA VR=5V Min. 2.8 5.2 7150 ----524 --Typ. ---30 518 528 35 -Max. 3.6 -14250 ----532 -50 Units V V mcd deg nm nm nm μAEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 3 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSRank Combination (IF=20mA)Rank Luminous Intensity T 7150~9000 U 9000~11250 V 11250~14250Unit: :mcd*Measurement Uncertainty of Luminous Intensity: ±15%Rank Forward Voltage0 2.8~3.01 3.0~3.22 3.2~3.43 3.4~3.6Unit:V*Measurement Uncertainty of Forward Voltage: ±0.1VRank Dominant Wavelength12Unit:nm524~528 528~532 *Measurement Uncertainty of Dominant Wavelength ±1.0nm*The quantity ratio of the ranks is decided by EVERLIGHT.Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 4 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSTypical Electro-Optical Characteristics CurvesEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 5 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSPacking Quantity Specification1.500PCS/1Bag,5Bags/1Box 2.10Boxes/1CartonLabel Form SpecificationEVERLIGHT CPN: P/N: 7383/G1C3-ATVA/X/MS QTY: CAT: HUE: LOT NO: REF: MADE IN TAIWAN CPN: Customer’s Production Number P/N : Production Number QTY: Packing Quantity CAT: Ranks of Luminous Intensity and Forward Voltage HUE: Ranks of Dominant Wavelength REF: Reference LOT No: Lot Number MADE IN TAIWAN: Production PlaceEverlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 6 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MSNotes 1. Above specification may be changed without notice. EVERLIGHT will reserve authority on material change for above specification. 2. When using this product, please observe the absolute maximum ratings and the instructions for using outlined in these specification sheets. EVERLIGHT assumes no responsibility for any damage resulting from use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets. 3. These specification sheets include materials protected under copyright of EVERLIGHT corporation. Please don’t reproduce or cause anyone to reproduce them without EVERLIGHT’s consent. 4. Below the zener reference voltage Vz, all the current flows through LED and as the voltage rises to Vz, the zener diode “breakdown." If the voltage tries to rise above Vz current flows through the zener branch to keep the voltage at exactly Vz. 5. When the LED is connected using serial circuit, if either piece of LED is no light up but current can’t flow through causing others to light down. In new design, the LED is parallel with zener diode. if either piece of LED is no light up but current can flow through causing others to light up.Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 7 of 8Prepared : Grace Shen元器件交易网EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 7383/G1C3-ATVA/X/MS6. Soldering ConditionCareful attention should be paid during soldering. When soldering, leave more then 3mm from solder joint to case, and soldering beyond the base of the tie bar is recommended. Avoiding applying any stress to the lead frame while the LEDs are at high temperature particularly when soldering. Recommended soldering conditions: Hand Soldering Temp. at tip of iron Soldering time Distance 400℃ Max. (30W Max.) 3 sec Max. 3mm Min.(From solder joint to case) Preheat temp. Bath temp. Bath time. Distance DIP Soldering 100℃ Max. (60 sec Max.) 265 Max. 5 sec Max. 3mm Min.EVERLIGHT ELECTRONICS CO., LTD. Office: No 25, Lane 76, Sec 3, Chung Yang Rd, Tucheng, Taipei 236, Taiwan, R.O.CTel: 886-2-2267-2000, 2267-9936 Fax: 886-2267-6244, 2267-6189, 2267-6306 http:\\Everlight Electronics Co., Ltd. Device Number : DLE-738-037http\\: Prepared date:05-26-2006Rev :1Page: 8 of 8Prepared : Grace Shen。

LS7366中文资料

GENERAL FEATURES:• Operating voltage: 3.0V to 5.5V (V DD - V SS )• 5V count frequency: 40MHz • 3V count frequency: 20MHz • 32-bit counter (CNTR).• 32-bit data register (DTR) and comparator.• 32-bit output register (OTR).• Two 8-bit mode registers (MDR0, MDR1) for programmable functional modes.• 8-bit instruction register (IR).• 8-bit status register (STR).• Latched Interrupt output on Carry or Borrow or Compare or Index.• Index driven counter load, output register load or counter reset.• Internal quadrature clock decoder and filter.• x1, x2 or x4 mode of quadrature counting.• Non-quadrature up/down counting.• Modulo-N, Non-recycle, Range-limit or Free-running modes of counting• 8-bit, 16-bit, 24-bit and 32-bit programmable configuration synchronous (SPI) serial interface• LS7366 (DIP); LS7366-S (SOIC); LS7366-TS (TSSOP) - See Figure 1-SPI/MICROWIRE (Serial Peripheral Interface):• Standard 4-wire connection: MOSI, MISO, SS/ and SCK. • Slave mode only.GENERAL DESCRIPTION:LS7366 is a 32-bit CMOS counter, with direct interface for quadra-ture clocks from incremental encoders. It also interfaces with the index signals from incremental encoders to perform variety of marker functions.For communications with microprocessors or microcontrollers, it provides a 4-wire SPI/MICROWIRE bus.The four standard bus I/Os are SS/, SCK, MISO and MOSI. The data transfer between a micro-controller and a slave LS7366 is synchronous. The synchronization is done by the SCK clocks supplied by the microcontroller.Each transmission is organized in blocks of 1 to 5 bytes of data. A transmission cycle is intitiated by a high to low transition of the SS/ input. The first byte received in a transmission cycle is always an instruction byte, whereas the second through the fifth bytes are always interpreted as data bytes. A transmission cycle is terminated with the low to high transition of the SS/ input. Received bytes are shifted in at the MOSI input, MSB first, with the leading edges (high transition) of the SCK clocks. Output data are shifted out on the MISO output, MSB first, with the trailing edges (low transition) of the SCK clocks.32-BIT QUADRATURE COUNTER WITH SERIAL INTERFACE1234567891011121314Vss V DD B A INDEX LFLAG/SS/SCK LS7366MISO MOSIf CKi f CKO PIN ASSIGNMENT TOP VIEWCNT_EN DFLAG/FIGURE 1LSI/CSILSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405LS7366U L®A3800January 2005Read and write commands cannot be combined.For example, when the device is shifting out read data on MISO output, it ignores the MOSI input,even though the SS/ input is active. SS/ must be terminated and reasserted before the device will accept a new command.The counter can be configured to operate as a 1, 2, 3 or 4-byte counter. When configured as a n-byte counter, the CNTR, DTR and OTR are all configured as n-byte registers, where n = 1, 2, 3 or 4. The content of the instruction/data identity is automatically adjusted to match the n-byte configu-ration. For example, if the counter is configured as a 2-byte counter, the instruction “write to DTR”expects 2 data bytes following the instruction byte.If the counter is configured as a 3-byte counter, the same instruction will expect 3 bytes of data follow-ing the instruction byte.Following the transfer of the appropriate number of bytes any further attempt of data transfer is ignored until a new instruction cycle is started by switching the SS/ input to high and then low.The counter can be programmed to operate in a number of different modes, with the operating characteristics being written into the two mode registers MDR0 and MDR1. Hardware I/Os are provided for event driven operations, such as processor interrupt and index related functions.I/O Pins:Following is a description of all the input/output pins.A (Pin 12)B (Pin 11)Inputs. A and B quadrature clock outputs from incremental encoders are directly applied to the A and B inputs of the LS7366. These clocks are ideally 90 degrees out-of-phase signals. A and B inputs are validated by on-chip digital filters and then decoded for up/down direction and count clocks.In non-quadrature mode, A serves as the count input andB serves as the direction input (B = high enables up count, B = low enables down count). In non-quadrature mode,the A and B inputs are not filtered internally, and are instantaneous in nature.INDEX (Pin 10)Input. The INDEX is a programmable input that canbe driven directly by the Index output of an incremental encoder. It can be programmed via the MDR to functionas one of the following:LCNTR (load CNTR with data from DTR), RCNTR(reset CNTR), or LOTR (load OTR with data from CNTR). Alternatively, the INDEX input can be masked out for"no functionality".In quadrature mode, the INDEX input is validated with the filter clock in order to synchronize with the quadrature inputs A and B. To be valid, the INDEX signal in quadrature mode must overlap the condition in which both A and B are low or both A and B are high. In non-quadrature mode, however, the INDEX input is instantaneous in nature and totally independent of A and B.f CK i (Pin 2), f CK0 (Pin 1)Input, Output. A crystal connected between these 2 pins generates the basic clock for filtering the A, B and INDEX inputs in the quadrature count mode. Instead of a crystal the f CKi input may also be driven by an external clock.The frequency at the f CKi input is either divided by 2(if MDR0 <B7> = 1) or divided by 1 (if MDR0 <B7> = 0)for the filter circuit. For proper filtering of the A, B andthe Index inputs the following condition must be satisfied:f f≥ 4f QAWhere f f is the internal filter clock frequency derived from the fCKi in accordance with the status of MDR0 <B7> and f QA is the maximum frequency of Clock A in quadrature mode.In non-quadrature count mode, f CKi is not used and should be tied off to any stable logic state.SS/ (Pin 4)A high to low transition at the SS/ (Slave Select) input selects the LS7366 for serial bi-directional data transfer;a low to high transition disables serial data transferand brings the MISO output to high impedance state.This allows for the accommodation of multiple slave units on the serial I/O.CNT_EN (Pin 12)Input. Counting is enabled when CNT_EN input is high; counting is disabled when this input is low.There is an internal pull-up resistor on this input.LFLAG/ (Pin 8), DFLAG/ (Pin 9)Outputs. LFLAG/ and DFLAG/ are programmable outputs to flag the occurences of Carry (counter overflow), Borrow (counter underflow), Compare (CNTR = DTR) and INDEX. The LFLAG/ is an open drain latched output. In contrast, the DFLAG/ is a push-pull instantaneous output. The LFLAG/ can be wired in multi-slave configuration, forming a single processor interrupt line. When active LFLAG/ switches to logic 0 and can be restored to the high impedence state only by clearing the status register, STR. In contrast, the DFLAG/ dynamically switches low with occurences of Carry, Borrow, Compare and INDEX conditions. The configuration of LFLAG/ and DFLAG/ are made through the control register MDR1. In free-running count mode LFLAG/ and DFLAG/ output the same status information in latched and dynamic form, respectively. In single-cycle mode the DFLAG/ outputs CY and BW signals independent of the MDR1 configura-tion. In range-limit and modulo-n modes, DFLAG/ outputs CMP signal in count-up direction (at CNTR = DTR) and BW signal when CNTR underflows independent of the MDR1 configuration. In effect, DFLAG/ generates mode-relevant marker signals in all modes, excepting the free-running count mode wherein MDR1 configures the output signal selection.MOSI (RXD) (Pin 7)Input. Serial output data from the host processor is shifted into the LS7366 at this input.MISO (TXD) (Pin 6)Output. Serial output data from the LS7366 is shifted out on the MISO (Master In Slave Out) pin. The MISO output goes into high impedance state when SS/ input is at logic high, providing multiple slave-unit serial outputs to be wire-ORed.SCK (Pin 5)Input. The SCK input serves as the shift clock input for transmit-ting data in and out of LS7366 on the MOSI and the MISO pins, respectively. Since the LS7366 can operate only in the slave mode, the SCK signal is provided by the host processor as a means for synchronizing the serial transmission between itself and the slave LS7366.REGISTERS:The following is a list of LS7366 internal registers:Upon power-up the registers DTR, CNTR, STR, MDR0 and MDR1 are reset to zero.DTR. The DTR is a software configurable 8, 16, 24 or 32-bit input data register which can be written into directly from MOSI, the serial input. The DTR data can be transferred into the 32-bit counter (CNTR) under program control or by hardware index signal. The DTR can be cleared to zero by software control.In certain count modes, such as modulo-n and range-limit,DTR holds the data for "n" and the count range, respectively.In compare operations, whereby compare flag is set, the DTR is compared with the CNTR.STR. The STR is an 8-bit status register which stores count related status information.CY BW CMP IDX CEN PLS U/D S 7 6 5 4 3 2 1 0CY: Carry (CNTR overflow) latchBW: Borrow (CNTR underflow) latch CMP: Compare (CNTR = DTR) latch IDX: Index latchCEN: Count enable status: 0: counting disabled, 1: counting enabled7366-012405-3IR . The IR is an 8-bit register that fetches instruction bytes from the received data stream and executes them to perform such functions as setting up the operating mode for the chip (load the MDR) and data transfer among the various registers.B7 B6 B5 B4 B3 B2 B1 B0B2 B1 B0 = XXX (Don’t care)B5 B4 B3 = 000: Select none= 001: Select MDR0 = 010: Select MDR1= 011: Select DTR = 100: Select CNTR = 101: Select OTR = 110: Select STR = 111: Select noneB7 B6 = 00: CLR register= 01: RD register = 10: WR register = 11: LOAD register The actions of the four functions, CLR, RD, WR and LOAD are elaborated in Table 1.TABLE 1Number of Bytes OP Code Register OperationMDR0Clear MDR0 to zero MRD1Clear MDR1 to zero1 CLR DTR NoneCNTR Clear CNTR to zero OTR None STR Clear STR to zero MDR0Output MDR0 serially on TXD (MISO)MDR1Output MDR1 serially on TXD (MISO)2 to 5 RD DTR NoneCNTR Transfer CNTR to OTR, then output OTR seriallyon TXD (MISO)OTR Output OTR serially on TXD (MISO)STR Output STR serially on TXD (MISO)MDR0Write serial data at RXD (MOSI) into MDR0MDR1Write serial data at RXD (MOSI) into MDR12 to 5 WR DTR Write serial data at RXD (MOSI) into DTRCNTR None OTR None STR None MDR0None MDR1None1 LOAD DTR NoneCNTR Transfer DTR to CNTR in “parallel”OTR Transfer CNTR to OTR in “parallel”CNTR. The CNTR is a software configurable 8, 16, 24 or 32-bit up/down counter which counts the up/down pulses resulting from the quadrature clocks applied at the A and B inputs, or alternatively, in non-quadrature mode, pulses applied at the A input. By means of IR intructions the CNTR can be cleared, loaded from the DTR or in turn, can be transferred into the OTR. The “clear CNTR”and the “load CNTR” commands in the ”range-limit” mode, however have limitations. In this mode when the CNTR is frozen in up count direction at CNTR = DTR, a “clear CNTR” command will only function if the count direction is reversed from up to down. Similarly, in the down direction at CNTR = 0, a “load CNTR” command will only function if the direction is reversed from down to up.OTR. The OTR is a software configuration 8, 16, 24 or 32-bit register which can be read back on the MISO output. Since instantaneous CNTR value is often needed to be read while the CNTR continues to count, the OTR serves as a convenient dump site for instantaneous CNTR data which can then be read without interfering with the counting process.PLS: Power loss indicator latch; set upon power upU/D: Count direction indicator: 0: count down, 1: count up S: Sign bit. 1: negative, 2: positiveA “CLR STR” command to IR resets all status bits except CEN and U/D. In quadrature mode, if the quadrature clocks have been halted, the status bits CY, BW and CMP are not affected by a “CLR STR” command under the following conditions: CY: If CNTR = FFFFFFFF with status bit U/D = 1 BW: If CNTR = 0 with status bit U/D = 0 CMP: If CNTR = DTRIn non-quadrature mode the same rules apply if input A is held at logic low.7366-112204-4ABSOLUTE MAXIMUM RATINGS: (All voltages referenced to Vss)Parameter Symbol Values Unit DC Supply Voltage V DD +7.0V Voltage V IN Vss - 0.3 to V DD + 0.3 VOperating Temperature T A -25 to +85o C Storage Temperature T STG -65 to +150o C MDR1. The MDR1 (Mode Register 1) is an 8-bit read/write register which is appended to MDR0 for additional modes. Upon power-up MDR1 is cleared to zero.B7 B6 B5 B4 B3 B2 B1 B0B1 B0 = 00: 4-byte counter mode = 01: 3-byte counter mode = 10: 2-byte counter mode. = 11: 1-byte counter mode B2 = 0: Enable counting = 1: Disable counting B3 = : not used B4 = 0: NOP= 1: FLAG on IDX (B4 of STR) B5 = 0: NOP= 1: FLAG on CMP (B5 of STR) B6 = 0: NOP= 1: FLAG on BW (B6 of STR) B7 = 0: NOP= 1: FLAG on CY (B7 of STR)MDR0. The MDR0 (Mode Register 0) is an 8-bit read/write register that sets up the operating mode for the LS7366. The MDR0 is written into by executing the "write-to-MDR0" instruction via the instruction register. Upon power up MDR0 is cleared to zero. The following is a breakdown of the MDR bits:B7 B6 B5 B4 B3 B2 B1 B0B1 B0 = 00: non-quadrature count mode. (A = clock, B = direction). = 01: x1 quadrature count mode (one count per quadrature cycle). = 10: x2 quadrature count mode (two counts per quadrature cycle). = 11: x4 quadrature count mode (four counts per quadrature cycle).B3 B2 = 00: free-running count mode.= 01: single-cycle count mode (counter disabled with carry or borrow, re-enabled with reset or load). = 10: range-limit count mode (up and down count-ranges are limited between DTR and zero, respectively; counting freezes at these limits but resumes when direction reverses). = 11: modulo-n count mode (input count clock frequency is divided by a factor of (n+1), where n = DTR, in both up and down directions).B5 B4 = 00: disable index.= 01: configure index as the "load CNTR" input (transfers DTR to CNTR). = 10: configure index as the "reset CNTR" input (clears CNTR to 0). = 11: configure index as the "load OTR" input (transfers CNTR to OTR). B6 = 0: Negative index input = 1: Positive index inputB7 = 0: Filter clock division factor = 1 = 1: Filter clock division factor = 2NOTE: Applicable to both LFLAG/ and DFLAG/DC Electrical Characteristics. (T A = -25˚C to +85°C)Parameter Symbol Min. TYP Max. Unit RemarksSupply Voltage V DD 3.0- 5.5V-Supply Current I DD300400450µA V DD = 3.0VI DD700800950µA V DD = 5.0VInput Voltagesf CK i, Logic high V CH- 2.1 2.3V V DD = 3.0VV CH- 3.5 3.7V V DD = 5.0Vf CKi, Logic Low V CL0.70.9-V V DD = 3.0VV CL 1.3 1.5-V V DD = 5.0VAll other inputs, Logic High V AH- 1.9 2.1V V DD = 3.0VV AH- 3.2 3.5V V DD = 5.0VAll other inputs, Logic Low V AL0.50.7-V V DD = 3.0VV AL 1.0 1.2-V V DD = 5.0VInput Currents:CNT_EN Low I IEL- 3.0 5.0µA V AL = 0.7V, V DD = 3.0VI IEL-10.015.0µA V AL = 1.2V, V DD = 5.0V CNT_EN High I IEH- 1.0 3.0µA V AH = 1.9V, V DD = 3.0VI IEH- 4.0 6.0µA V AH = 3.2V, V DD = 5.0V All other inputs, High or Low--00µA-Output Currents:FLAG Sink I OFL-1.3-2.0-mA V OUT = 0.5V, V DD = 3.0VI OFL-3.2-4.0-mA V OUT = 0.5V, V DD = 5.0V FLAG Source- 0 0-mA Open Drain Outputf CKO Sink I OCL-1.3-2.0-mA V OUT = 0.5V, V DD = 3.0VI OCL-3.2-4.0-mA V OUT = 0.5V, V DD = 5.0V f CKO Source I OCH 1.3 2.0-mA V OUT = 2.5V, V DD = 3.0VI OCH 3.2 4.0-mA V OUT = 4.5V, V DD = 5.0V TXD/MISO:Sink I OML-1.5-2.4-mA V OUT = 0.5V, V DD = 3.0VI OML-3.8-4.8-mA V OUT = 0.5V, V DD = 5.0V Source I OMH 1.5 2.4-mA V OUT = 0.5V, V DD = 3.0VI OMH 3.8 4.8-mA V OUT = 0.5V, V DD = 5.0V Transient Characteristics. (T A = -25˚C to +85˚C, V DD = 5V ± 10%)Parameter Symbol Min. Value Max.Value Unit Remarks(See Fig. 2 & 3)SCK High Pulse Width t CH100-ns-SCK Low Pulse Width t CL100-ns-SS/ Set Up Time t CSL100-ns-SS/ Hold Time t CSH100-ns-Quadrature Mode(See Fig. 4, 6 & 7)f CKI High Pulse Width t112-ns-f CKI Pulse Width t212-ns-f CKI Frequency f FCK-40MHz-Effective Filter Clock fF Period t325-ns t3 = t1+t2, MDR0 <7> = 0t350-ns t3 = 2(t1+t2), MDR0 <7> = 1 Effective Filter Clock f F frequency f F-40MHz f F = 1/ t3Quadrature Separation t426-ns t4 > t3Quadrature Clock Pulse Width t552-ns t5≥ 2t3Quadrature Clock frequency f QA, f QB-9.6MHz f QA = f QB < 1/4t3 Quadrature Clock to Count Delay t Q14t35t3--x1 / x2 / x4 Count Clock Pulse Width t Q212-ns t Q2 = (t3)/2Index Input Pulse Width ti d32-ns t id > t4Index Set Up Time ti s-5ns-Index Hold Time ti h-5ns-Quadrature clock to t fl 4.5t3 5.5t3ns-DFLAG/ or LFLAG/ delayDFLAG/ output width t fw26-ns t fw = t4Parameter Symbol Min. Value Max.Value Unit RemarksNon-Quadrature Mode(See Fig. 5 & 8)Clock A - High Pulse Width t612-ns-Clock A - Low Pulse Width t712-ns-Direction Input B Set-up Time t8S12-ns-Direction Input B Hold Time t8H10-ns-Clock Frequency (non-Mod-N)f A-40MHz f A = (1/(t6 + t7))Clock to DFLAG/ or t920-ns-LFLAG/ delayDFLAG/ output width t1012-ns t10 = t7Transient Characteristics. (T A = -25˚C to +85˚C, V DD = 3.3V ± 10%)Parameter Symbol Min. Value Max.Value Unit Remarks(See Fig. 2 & 3)SCK High Pulse Width t CH120-ns-SCK Low Pulse Width t CL120-ns-SS/ Set Up Time t CSL120-ns-SS/ Hold Time t CSH120-ns-Quadrature Mode(See Fig. 4, 6 & 7)f CKI High Pulse Width t124-ns-f CKI Pulse Width t224-ns-f CKI Frequency f FCK-20MHz-Effective Filter Clock fF Period t350-ns t3 = t1+t2, MDR0 <7> = 0t3100-ns t3 = 2(t1+t2), MDR0 <7> = 1 Effective Filter Clock f F frequency f F-20MHz f F = 1/t3Quadrature Separation t452-ns t4 > t3Quadrature Clock Pulse Width t5105-ns t5≥ 2t3Quadrature Clock frequency f QA, f QB- 4.5MHz f QA = f QB < 1/4t3 Quadrature Clock to Count Delay t Q14t35t3--x1/x2/x4 Count Clock Pulse Width t Q225-ns t Q2 = (t3)/2Index Input Pulse Width t id60-ns t id > t4Index Set Up Time t is-10ns-Index Hold Time t ih-10ns-Quadrature clock to t fl 4.5t3 5.5t3ns-DFLAG/ or LFLAG/ delayDFLAG/ output width t fw52-ns t fw = t4Non-Quadrature Mode(See Fig. 5 & 8)Clock A - High Pulse Width t624-ns-Clock A - Low Pulse Width t724-ns-Direction Input B Set-up Time t8S24-ns-Direction Input B Hold Time t8H24-ns-Clock Frequency (non-Mod-N)f A-40MHz f A = (1/(t6 + t7))Clock to DFLAG/or t940-ns-LFLAG/ delayDFLAG/ output width t1024-ns t10 = t7。

LA76810功能参数

LA76810LA76810是三洋公司于99年开发成功的用于PAL/NTSC 制彩色电视信号处理的大规模集成电路单片可完成图像伴音的解调色解码亮度处理同步及行场小信号的处理LA76810集成度高外围元件少用于替代三洋A6机芯的LA7687A 单片被称为A12机芯LA76810具有以下特点单片多制式适用于处理PAL/NTSC 视频信号配合免调试SECAM 解码电路可实现全制式解码采用PLL 图像和伴音解调采用单晶体完成PAL NTSC 制信号解调内藏一行基带延迟线亮度延迟线不需外接各种带通滤波器陷波器内置伴音和视频选择开关50/60Hz 场频自动识别I 2C 总线控制等芯片还内置了峰化清晰度改善电路挖芯降噪处理电路黑电平延伸电路对比度改善电路等A12机芯电视整机线路比较简单外接元件也很少便于生产与维修海信电器股份有限公司在2000年研制投产了A12单片机芯并在升级彩电系列休闲系列及环保二代系列产品中大量使用其主要机型有TC1410L TC1423TC2102G TC2110L TC2166L TC2175G TC2181F TC2199A TC2505TC2540AM TC2588D TC2961L TC2975DL TC2999L TF2110D 等对地阻值k 引脚序号标 号 功 能 电压值V 黑笔接地 红笔接地1 AUDIO OUT 伴音输出 2.25 8.5 9.12 FM OUT 伴音调频解调 2.37 9.4 11.03 PIF AGC 中放AGC 滤波 2.40 9.8 11.4 4 RF AGC OUT 高放AGC 输出 3.50 9.4 33.05 PIF IN 中频输入 2.85 9.5 9.96 PIF IN 中频输入 2.85 9.5 9.97 IF GND 中频电路地 0 0 08 VCC(VIF) 图像中频供电 4.90 1.4 1.49 FM FIL 调频解调滤波 2.20 9.8 12.2 10 AFT OUT AFT 信号输出 2.40 7.5 10.5 11 BUS DATA 总线数据线 4.50 8.0 12.5 12 BUS CLOCK 总线时钟线 4.48 7.9 12.5 13 ABL 自动亮度限制输入 2.21 6.4 8.0 14 R IN 字符红信号输入 0.02 9.4 10.8 15 G IN 字符绿信号输入 0.02 9.4 10.8 16 B IN 字符蓝信号输入 0.02 9.4 10.8 17 BL IN 字符消隐信号输入 0.80 3.3 3.3 18 VCC(RGB) RGB 电路供电 8.24 1.0 0.9 19 R OUT 红信号输出 2.46 9.0 8.5 20 G OUT 绿信号输出 2.50 9.1 8.5 21 B OUT 蓝信号输出 2.55 9.3 8.5 22 SYNC 同步信号输出 0.37 7.3 10.6 23 V OUT 场激励信号输出 2.60 2.0 2.0 24 V RAMP ALC FIL 场信号形成滤波 2.07 9.5 11.0 25 VCC(H/D) 行场激励信号电路供电 5.10 1.0 1.026 AFC FIL AFC 滤波 2.56 9.5 11.5 27 H.OUT 行激励信号输出 0.64 2.2 2.2 28 FBP IN 反馈脉冲输入 1.12 9.2 10.1REF行振荡参考输入 1.63 4.7 4.729 IOUT 行振荡信号输出 0.64 6.6 11.630 CLOCK1.4 1.431 1 HDL VCC 1行延迟线供电 4.5032 1 HDL VCC OUT 1行延迟线自举升压 8.30 633 GND 1行延迟/行电路地 0 0 034 SECAM B-Y IN SECAM蓝色差输入 2.50 9.6 10.735 SECAM R-Y IN SECAM红色差输入 2.50 9.6 10.711.236 C AFC2 FIL 彩色AFC2滤波 3.9010.011.79.8OUT SECAM制使用 2.6337 FSC9.911.1 38 XTAL 晶振 3.789.5 10.639 C AFC1 FIL 彩色AFC1滤波 3.30V.OUT 视频信号选择输出 2.20 9.5 11.440 SELECT41 GND(V/C/D) 地 0V.IN 外部视频信号输入 2.50 9.6 11.242 EXT1.4 43 VCC(V/C/D) 供电 5.031.4V.IN 内部视频信号输入 2.80 9.5 11.544 INTSTR 黑电平延伸滤波 2.60 8.0 8.645 BLACK1.2 1.2OUT 视频信号输出 2.7046 VIDEOFIL 38MHz解调APC滤波 3.95 9.5 11.647 APC1.8 1.848 VCOCOIL 中频解调中周 4.201.8 1.8COIL 中频解调中周 4.2049 VCOFIL 压控振荡器滤波 2.40 9.1 11.050 VCO51 EXT AUDIO IN 外部音频信号输入 2.10 9.5 11.111.59.152 SIFOUT 伴音中频输出 1.9053 SIF APC FIL 伴音解调APC滤波 2.20 9.4 11.511.69.654 SIFIN 伴音中频输入 3.10说明测量机型为海信TC2199A采用MF10B型万用表在线电阻采用R1k挡。

AN13300A资料

7 8

Note) *:

Supply current Power dissipation

ICC PD

mA W

Expect for the operating ambient temperature and storage temperature , all ratings are for Ta = 25°C.

DATA SHEET

Part No. Package Code No.

AN13300A

*SOP022 - P - 0375C

SEMICONDUCTOR COMPANY MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD.

Publication date: January 2005

2003 SEP

SDF00039AEB

1

AN13300A Contents

Features …………………………………………………………………………………………………………… 3 Applications ………………………………………………………………………………………………………… 3 Package ……………………………………………………………………………………………………………. 3 Block Diagram ………………………………………………………………………………………………………. 4 Pin Descriptions …………………………………………………………………………………………………… 4 Absolute Maximum Ratings ………………………………………………………………………………………. 5 Operating Supply Voltage Range ………………………………………………………………………………. 5

AU6366中文资料

AU6366USB2.0 Single LUNMultiple Flash Card Reader Controller Technical Reference ManualAU6366USB2.0 Single LUN Multiple Flash Card Reader ControllerC o p y r i g h tCopyright © 1997 - 2007. Alcor Micro, Corp. All Rights Reserved. No part of this data sheet may be reproduced, transmitted, transcribed, stored in a retrieval system or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without prior written permission from Alcor Micro, Corp.T r a d e m a r k A c k n o w l e d g e m e n t sThe company and product names mentioned in this document may be the trademarks or registered trademarks of their manufacturers.D i s c l a i m e rAlcor Micro, Corp. reserves the right to change this product without prior notice. Alcor Micro, Corp. makes no warranty for the use of its products and bears no responsibility for any error that appear in this document. Specifications are subject to change without prior notice.R e v i s i o n H i s t o r yDate Revision DescriptionJan 2006 1.00W Official ReleaseAug 2006 1.01W Update new address of Los Angeles OfficeNov 2006 1.02W Modify “1.2 Features”July 2007 1.03W Modify “5.6 Power Switch Feature”C o n t a c t I n f o r m a t i o n:Web site: /Taiwan China ShenZhen OfficeAlcor Micro, Corp. Rm.2407-08, Industrial Bank Building 4F, No 200 Kang Chien Rd., Nei Hu, No.4013, Shennan Road,Taipei, Taiwan, R.O.C. ShenZhen,China. 518026Phone: 886-2-8751-1984 Phone: (0755) 8366-9039Fax: 886-2-2659-7723 Fax: (0755) 8366-9101Santa Clara Office Los Angeles Office2901 Tasman Drive, Suite 206 9070 Rancho Park CourtSanta Clara, CA 95054 Rancho Cucamonga, CA 91730USA USA Phone: (408) 845-9300 Phone: (909) 483-9900Fax: (408) 845-9086 Fax: (909) 944-0464<Memo>Table of Contents1. Introduction (1)1.1 Description (1)1.2 Features (1)2. Application Block Diagram (2)3. Pin Assignment (3)4. System Architecture and Reference Design (6)4.1 AU6366 Block Diagram (6)5. Electrical Characteristics (7)5.1 Absolute Maximum Ratings (7)5.2 Recommended Operating Conditions (7)5.3 General DC Characteristics (7)5.4 DC Electrical Characteristics of 3.3V I/O Cells (8)5.5 USB Transceiver Characteristics (8)5.6 Power Switch Feature (12)6. Mechanical Information (13)7. Abbreviations (14)iList of FiguresFigure 2.1 Block Diagram (2)Figure 3.1 Pin Assignment Diagram (3)Figure 4.1 AU6366 Block Diagram (6)Figure 5.1 Built-in card power switch I-V curve (12)Figure 5.2 Card Detect Power-on Timing (12)Figure 6.1 Mechanical Information Diagram (13)List of TablesTable 3.1 Pin Descriptions (4)Table 5.1 Absolute Maximum Ratings (7)Table 5.2 Recommended Operating Conditions (7)Table 5.3 General DC Characteristics (7)Table 5.4 DC Electrical Characteristics of 3.3V I/O Cells (8)Table 5.5 Electrical characteristics (8)Table 5.6 Static characteristic:Digital pin (9)Table 5.7 Static characteristic:Analog I/O pins(DP/DM) (9)Table 5.8 Dynamic characteristic:Analog I/O pins(DP/DM) (10)ii1. Introduction1.1D e s c r i p t i o nThe AU6366 is a single chip integrated USB 2.0 multimedia card reader controller that enables PC/DVD/Printer to read/write various type of flash media cards. Flash media cards such as CF, SMC, XD, SD, MMC, Memory Stick are widely used in digital camera, cell phone, PDA and MP3 player to store digital photos and compressed music.Performance of AU6366 is maximized by implementing the latest and fastest card specification available form the industry.The AU6366 is designed in shared pin architecture to meet cost and space regulate for Notebook end reunite.1.2F e a t u r e sSupport USB V2.0 specification and USB Device Class Definition for Mass Storage, Bulk-Transport V1.0Support CF/MD/SD/MMC/MS/MS_Pro/MS_Duo/xD/SMC compatible flash cardSupport the latest flash card specification: CF 3.0 (16-bit IDE mode), SD1.1 (HS-SD), MMC4.0 (8-bit), MSPro parallel mode (4-bit), xD 1.2 Hardware DMA engine integrated for performance enhancementWork with default driver from Windows ME/2000/XP and Mac OS X; Windows 98/2000(SP1/SP2) and Mac OS 9 are supported by vendor driver fromAlcor.Ping-pong FIFO implementation for concurrent bus operationSupport multiple sectors transfer optimize performanceSupport slot-to-slot read/write operationSupport Dynamic Icon UtilitySupport LED for bus operating indicationPower switch integrated to reduce production BOM cost30MHz 8051 CPUBuilt in 3.3V to 2.5V regulatorRun at 12MHz crystalAvailable in 48-pin LQFP packageAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 12. Application Block DiagramThe following application drawing demonstrates a typical card reader block diagram using AU6366. By connecting one card reader to a desktop or notebook PC through USB bus, the AU6366 becomes a bus-powered, high speed USB card reader, which can be used as a bridge for data transfer between Desktop PC and Notebook PC.Figure 2.1 Block DiagramSMC/SD/MMCAU6366AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 2AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W33. Pin AssignmentThe AU6366 is delivered in 48pin LQFP form factor. Documented below is a figure shows signal names of each pin and a table in the following page describes each pin in more details.Figure 3.1 Pin Assignment DiagramCARDDATA15CFWTN CLEDCHIPRESETN GNDAVDDARPUAVDD DPDMAVSS RREFXDCDNCONTROLOUT5CONTROLOUT4CONTROLOUT3CONTROLOUT2CONTROLOUT1CONTROLOUT0VDDCARDDATA1CARDDATA2GNDCARDDATA0SDCDNVSSHCPWR_V33SMCDNCFCDNMSINSVDD25VPVSSPVDDXOVDDHXICARDDATA3CARDDATA4CARDDATA5CARDDATA6CARDDATA7CARDDATA8CARDDATA9CARDDATA10CARDDATA11CARDDATA12CARDDATA14CARDDATA13AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W4Table 3.1 Pin DescriptionsPin #Pin NameI/ODescription1 CARDDATA15 I/O CF Data15/xD Data72 CFWTN I CF WAITN3 CLED O Card Operating LED4 CHIPRESETNI Chip Reset, Pull up with RC 5 GNDA PLL Ground 6 VDDA I PLL VDD 2.5V7 RPU I Connected with an 1.5k pull up resistor to 3.3 VDD 8 AVDD I Analog Power 3.3V 9 DP I/O DP 10 DM I/O DM11 AVSS Analog Ground12 RREF I Connected an 1k resistor to GND for impedance match13 PVDD I OSC Power 3.3V 14 XI I 12 MHz crystal input. 15 XO O 12 MHz crystal output. 16 PVSS OSC Ground 17 VDD25V O Core Power 2.5V 18 VDDH I 3.3V for IO pad 19 CPWR_V33 O Card Power 3.3V 20 VSSH Power Ground 21 MSINS I MS INS22 SMCDN I SMC Card Detect 23 CFCDN I CF Card Detect 24 SDCDN I SD Card Detect 25 XDCDN I xD Card Detect26 CONTROLOUT5 O CFRESETN and SMWRN/XDWRN 27 CONTROLOUT4 O CFWRN and SMRDN/XDRDN 28 CONTROLOUT3 O CFRDN and XDCEN/SMCEN 29CONTROLOUT2OCFAD2 and SMALE/XDALEAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W5Pin #Pin NameI/ODescription30 CONTROLOUT1 O CFAD1, MSCLK and SMCLE/XDCLE 31 CONTROLOUT0O CFAD0, SDCLK and MSBS 32 VDD I Core power 2.5V 33 GND Core Ground34 CARDDATA0 I/O CFDATA0, MSDATA0,and SDCMD 35 CARDDATA1 I/O CFDATA1,MSDATA1,XDWPN,and SMWPN 36 CARDDATA2 I/O CFDATA2,MSDATA2,and SDWP37 CARDDATA3 I/O CFDATA3,MSDATA3,SMRBN,and XDRBN 38 CARDDATA4 I/O CFDATA4 and SDDATA0 39 CARDDATA5 I/O CFDATA5 and SDDATA1 40 CARDDATA6 I/O CFDATA6 and SDDATA2 41 CARDDATA7 I/O CFDATA7 and SDDATA342 CARDDATA8 I/O CFDATA8,XDDATA0, and SDDATA4 43 CARDDATA9 I/O CFDATA9,XDDATA1, and SDDATA5 44 CARDDATA10 I/O CFDATA10,XDDATA2, and SDDATA6 45 CARDDATA11 I/O CFDATA11,XDDATA3, and SDDATA7 46 CARDDATA12 I/O CFDATA12 and XDDATA4 47 CARDDATA13 I/O CFDADA13 and XDDATA5 48CARDDATA14I/OCFDATA14 and XDDATA64. System Architecture and Reference Design4.1 A U 6366 B l o c k D i a g r a mFigure 4.1 AU6366 Block DiagramCF MD SMC SD MMC MS xDUSB Upstream PortAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W65. Electrical Characteristics5.1A b s o l u t e M a x i m u m R a t i n g sTable 5.1 Absolute Maximum RatingsSYMBOL PARAMETER RATING UNITS V DDH Power Supply -0.3 to V DDH +0.3 VV IN Input Signal Voltage -0.3 to 3.6 VV OUT Output Signal Voltage-0.3 to V DDH +0.3 VT STG Storage Temperature-40 to 150 O C5.2 Recommended Operating ConditionsTable 5.2 Recommended Operating ConditionsSYMBOL PARAMETER MIN TYP MAX UNITS V DDH Power Supply 3.0 3.3 3.6 V V DD Digital Supply 2.25 2.5 2.75 V V IN Input Signal Voltage 0 3.3 3.6 V T OPR Operating Temperature 0 70 O C 5.3G e n e r a l D C C h a r a c t e r i s t i c sTable 5.3 General DC CharacteristicsSYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITSI IN Input current No pull-up orpull-down-10 ±1 10 µAI OZ Tri-state leakage current-10 ±1 10 µA C IN Input capacitance Pad Limit 2.8 ρF C OUT Output capacitance Pad Limit 2.8 ρFC BID Bi-directional buffercapacitancePad Limit 2.8 ρFAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 75.4D C E l e c t r i c a l C h a r a c t e r i s t i c s o f3.3V I/O C e l l sTable 5.4 DC Electrical Characteristics of 3.3V I/O CellsLimitsSYMBOL PARAMETER CONDITIONSMIN TYP MAXUNIT V DDH Power supply 3.3V I/O 3.0 3.3 3.6 V V il Input low voltage 0.8 VV ih Input high voltage LVTTL2.0 VV ol Output low voltage ∣I ol∣=2~16mA 0.4 V V oh Output high voltage ∣I oh∣=2~16mA 2.4 V R pu Input pull-up resistance PU=high, PD=low55 75 190 KΩR pd Input pull-down resistance PU=low, PD=high40 75 190 KΩI in Input leakage current V in= V DDH or 0 -10 ±1 10 μAI oz Tri-state output leakagecurrent-10 ±1 10 μA5.5U S B T r a n s c e i v e r C h a r a c t e r i s t i c sTable 5.5 Electrical characteristicsSymbol Parameter Conditions Min.Typ. Max.Unit VD33 Analog supply Voltage 3.0 3.3 3.6 V VDDUVDDADigital supply Voltage 2.25 2.5 2.75 VI CC Operating supply current High speed operatingat 480 MHz73mAI CC (susp)Suspend supply currentIn suspend mode,current with 1.5kΩpull-up resistor on pinRPU disconnected120µAAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 8Table 5.6 Static characteristic:Digital pinSymbol Parameter Conditions Min. Typ. Max. UnitInput levelsV IL Low-level input voltage 0.8 V V IH High-level input voltage 2.0 VOutput levelsV OL Low-level output voltage 0.2 V V OH High-level output voltage VDDH-0.2V Table 5.7 Static characteristic:Analog I/O pins(DP/DM)Symbol Parameter Conditions Min.Typ. Max. UnitUSB2.0 Transceiver(HS)Input Levels(differential receiver)V HSDIFF High speed differentialinput sensitivity∣V I(DP)-V I(DM)∣measured at theconnection asapplication circuit300 mVV HSCM High speed data signalingcommon mode voltagerange-50 500mVSquelch detected 100 mVV HSSQ High speed squelchdetection threshold No squelch detected150 mVDisconnectiondetected625 mVV HSDSC High speed disconnectiondetection threshold Disconnection notdetected525mVOutput LevelsV HSOIHigh speed idle leveloutput voltage(differential)-10 10mVV HSOLHigh speed low leveloutput voltage(differential)-10 10mVV HSOHHigh speed high leveloutput voltage(differential)-360 400mVV CHIRPJ Chirp-J output voltage(differential)700 1100mVV CHIRPK Chirp-K output voltage(differential)-900 -500mVResistanceR DRV Driver output impedance Equivalent resistanceused as internal chiponly3 6 9 ΩAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 9Overallresistanceincluding externalresistor40.5 45 49.5 TerminationV TERM Termination voltage forpull-up resistor on pinRPU3.0 3.6V USB1.1 Transceiver(FS/LS)Input Levels(differential receiver)V DI Differential inputsensitivity∣V I(DP)-V I(DM)∣0.2 VV CM Differential commonmode voltage0.8 2.5V Input Levels(single-ended receivers)V SE Single ended receiverthreshold0.8 2.0VOutput levelsV OL Low-level output voltage0 0.3 V V OH High-level output voltage 2.8 3.6 VTable 5.8 Dynamic characteristic:Analog I/O pins(DP/DM)Symbol Parameter Conditions Min.Typ. Max. UnitDriver CharacteristicsHigh-Speed Modet HSR High-speed differentialrise time500 pst HSF High-speed differential falltime500 psFull-Speed Modet FR Rise time CL=50pF;10 to 90﹪of∣V OH-V OL∣;4 20nst FF Fall time CL=50pF;90 to 10﹪of∣V OH-V OL∣;4 20nst FRMA Differential rise/fall timematching(t FR / t FF)Excluding the firsttransition from idlemode90 110 %V CRS Output signal crossovervoltageExcluding the firsttransition from idlemode1.32.0 VLow-Speed Modet LR Rise time CL=200pF-600pF;10 to 90﹪of∣V OH-V OL∣;75 300nsAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 10t LFFall timeCL=200pF-600pF ;90 to 10﹪of ∣V OH -V OL ∣; 75 300 nst LRMA Differential rise/fall timematching (t LR / t LF )Excluding the firsttransition from idlemode80 125 % V CRS Output signal crossovervoltageExcluding the firsttransition from idlemode 1.3 2.0 V V OHHigh-level output voltage2.83.6VAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W115.6 P o w e r S w i t c h F e a t u r eFigure 5.1 Built-in card power switch I-V curve3.3V+/- 0.3V1ms to 10ms ( Depend Load Capacitor )CARD_POWERCARD_DETECT100ms + System Polling timingFigure 5.2 Card Detect Power-on TimingAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W126. Mechanical InformationFigure 6.1 Mechanical Information DiagramGAUGE PLANE SEATING PLANE1.60.15 1.45 0.16 BSC BSC BSC BSC BSC 0.270.75 REF1.JEDEC OUTLINE: MS-026 BBC2. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION.ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. D1 AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS IMCLUDING MOLD MISMATCH.3. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM b DIMENSION BY MORE THAN 0.08mmAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W137. AbbreviationsIn this chapter some of the terms and abbreviations used throughout the technical reference manual are listed as follows.SIE Serial Interface EngineCF Compact FlashMD Micro DriveSMC SmartMedia CardMS Memory StickSD Secure DigitalMMC Multimedia CardUTMI USB Transceiver Macrocell InterfaceAbout Alcor Micro, Corp.Alcor Micro, Corp. designs, develops and markets highly integrated and advanced peripheral semiconductor, and software driver solutions for the personal computer and consumer electronics markets worldwide. We specialize in USB solutions and focus on emerging technology such as USB and IEEE 1394. The company offers a range of semiconductors including controllers for USB hub, integrated keyboard/USB hub and USB Flash memory card reader…etc. Alcor Micro, Corp. is based in Taipei, Taiwan, with sales offices in Taipei, Japan, Korea and California. Alcor Micro is distinguished by its ability to provide innovative solutions for spec-driven products. Innovations like single chip solutions for traditional multiple chip products and on-board voltage regulators enable the company to provide cost-efficiency solutions for the computer peripheral device OEM customers worldwide.AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 14。

AD7386四路16位双取样解决方案

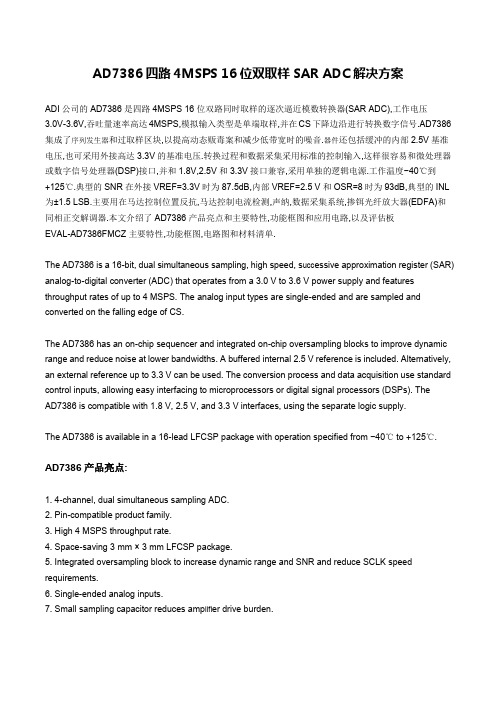

AD7386四路4MSPS 16位双取样SAR ADC解决方案ADI公司的AD7386是四路4MSPS 16位双路同时取样的逐次逼近模数转换器(SAR ADC),工作电压3.0V-3.6V,吞吐量速率高达4MSPS,模拟输入类型是单端取样,并在CS下降边沿进行转换数字信号.AD7386集成了序列发生器和过取样区块,以提高动态贩毒案和减少低带宽时的噪音.器件还包括缓冲的内部2.5V基准电压,也可采用外接高达3.3V的基准电压.转换过程和数据采集采用标准的控制输入,这样很容易和微处理器或数字信号处理器(DSP)接口,并和1.8V,2.5V和3.3V接口兼容,采用单独的逻辑电源.工作温度−40℃到+125℃.典型的SNR在外接VREF=3.3V时为87.5dB,内部VREF=2.5 V和OSR=8时为93dB,典型的INL 为±1.5 LSB.主要用在马达控制位置反抗,马达控制电流检测,声纳,数据采集系统,掺铒光纤放大器(EDFA)和同相正交解调器.本文介绍了AD7386产品亮点和主要特性,功能框图和应用电路,以及评估板EVAL-AD7386FMCZ主要特性,功能框图,电路图和材料清单.The AD7386 is a 16-bit, dual simultaneous sampling, high speed, s ucc essive approximation register (SAR) analog-to-digital converter (ADC) that operates from a 3.0 V to 3.6 V power supply and features throughput rates of up to 4 MSPS. The analog input types are single-ended and are sampled and converted on the falling edge of CS.The AD7386 has an on-chip sequencer and integrated on-chip oversampling blocks to improve dynamic range and reduce noise at lower bandwidths. A buffered internal 2.5 V reference is included. Alternatively, an external reference up to 3.3 V can be used. The conversion process and data acquisition use standard control inputs, allowing easy interfacing to microprocessors or digital signal processors (DSPs). TheAD7386 is compatible with 1.8 V, 2.5 V, and 3.3 V interfaces, using the separate logic supply.The AD7386 is available in a 16-lead LFCSP package with operation specified from −40℃ to +125℃. AD7386产品亮点:1. 4-channel, dual simultaneous sampling ADC.2. Pin-compatible product family.3. High 4 MSPS throughput rate.4. Space-saving 3 mm × 3 mm LFCSP package.5. Integrated oversampling block to increase dynamic range and SNR and reduce SCLK speed requirements.6. Single-ended analog inputs.7. Small sampling capacitor reduces amp lifi er drive burden.AD7386主要特性:16-bit dual simultaneous sampling SAR ADC Single-ended analog inputsQuad channel with 2:1 multiplexersChannel sequencer modeHigh throughput rate of up to 4 MSPSOn-chip oversampling functionsSNR (typical)87.5 dB, VREF = 3.3 V external93 dB with OSR = 8, VREF = 2.5 V internalINL (typical): ±1.5 LSBsResolution boost function2.5 V internal reference at 10 ppm/℃(maximum) Alert function−40℃ to +125℃ temperature range16-lead LFCSP, 3 mm×3 mmAD7386应用:Motor control position feedbackMotor control current senseSonarsPower qualityData acquisition systemsErbium doped fiber amplifier (EDFA) applications Inphase and quadrature demodulation图1.AD7386功能框图图2.AD7386典型应用电路图评估板EVAL-AD7386FMCZEvaluating the AD7386 4-Channel 16-bit, Dual Simultaneous Sampling, SAR ADCThe EVAL-AD7386FMCZ is a full featured evaluation board designed to evaluate all features of theAD7386 analog-to-digital converters (ADCs). The evaluation board can be controlled by theEVAL-SDP-CH1Z via the 160-way system demonstration platform (SDP) connector, P7. TheEVAL-SDP-CH1Z board controls the evaluation boards through a USB port of a PC using the analysis control evaluation (ACE) software, which is available for download from the ACE software page. Complete specifications for the AD7386 are provided in the AD7386 data sheet. Consult these specifications in conjunction with this user guide when using the evaluation board. Full details on the EVAL-SDP-CH1Z are available on the SDP-H1 product page. The comprehensive ACE user guide is available on the ACE software page.评估板EVAL-AD7386FMCZ主要特性:Full featured evaluation board multichannel, simultaneous sampling ADCOn-board reference, reference buffer, and ADC driverOn-board power suppliesBoard-compatible high speed system demonstration platform (SDP-H1) controller PC software for control and data analysis评估板EVAL-AD7386FMCZ包括:EVAL-AD7386FMCZ evaluation boardInstructions to download software图3.评估板EVAL-AD7386FMCZ(左)连接到EVAL-SDP-CH1Z(右)图3.评估板EVAL-AD7386FMCZ(左)连接到EVAL-SDP-CH1Z(右)设定图图4.评估板EVAL-AD7386FMCZ功能框图图5.ADC评估板,ADC驱动器和ADC图6.ADC评估板,共模和基准缓冲器图7.ADC评估板,电源评估板EVAL-AD7386FMCZ材料清单:。

A416316AV-35L中文资料

A416316A Series

Preliminary

Document Title 64K X 16 CMOS DYNAMIC RAM WITH FAST PAGE MODE Revision History

Rev. No.

0.0 0.1

64K X 16 CMOS DYNAMIC RAM WITH FAST PAGE MODE

A0 – A7 I/O0 - I/O15

RAS

PRELIMINARY

A416316AS

(October, 1999, Version 0.1)

A416316AV

UCAS

LCAS

WE OE

VCC VSS NC

1

AMIC Technology, Inc.

元器件交易网

A416316A Series

RAS

UCAS

H L H

LCAS

H L L

WE

OE

Address L Row/Col. Row/Col.

I/Os L Data Out I/O0-7 = Data Out I/O8-15 = High-Z I/O0-7 = High-Z I/O8-15 = Data Out Data In I/O0-7 = Data In I/O8-15 = X I/O0-7 = X I/O8-15 = Data In Data Out → Data In Data Out Data Out Data In Data In Data In Data In Data Out Data In → High-Z High-Z X L

Preliminary

Features

n Organization: 65,536 words X 16 bits n Part Identification: - A416316A - A416316A-L (with self-refresh mode) n High speed - 30/35/40 ns RAS access time - 16/18/20 ns column address access time - 10/11/12 ns CAS access time n Low power consumption - Operating: 75mA (-30 max) - Standby: 3 mA (TTL) Separate CAS ( UCAS , LCAS ) for byte selection Self refresh mode 256 refresh cycles, 4 ms refresh interval Read-modify-write, RAS -only, CAS -before- RAS , Hidden refresh capability n TTL-compatible, three-state I/O n JEDEC standard packages - 400mil, 40-pin SOJ - 400mil, 40/44 TSOP type II package n Single 5V power supply/built-in VBB generator n n n n

CS5463A中文资料手册pdf

mcp73833 73834中文手册

0.10

58 47 25

100 1000

3000 300 300

100

3.7 3.6 —

4.232 4.382 4.433 4.533 0.30

0.30

— — —

110 1100

最大输出电流限制

IMAX

—

1200

—

µA 充电中

µA 充电结束

µA 待机 (没有接电池或 PROG 悬空)

MCP73833/4

独立线性锂离子 / 锂聚合物电池 充电管理控制器

特点

• 完整的线性充电管理控制器 - 内部集成了功率晶体管 - 内部集成了电流检测 - 内部集成了反向阻断保护

• 可进行热调节的恒流 / 恒压控制 • 高精度预置稳压:

- 4.2V, 4.35V, 4.4V 或 4.5V, +0.75% • 可编程充电电流:最大 1A • 对深度放电的电池进行预充

电流 + 限制 -

111 kΩ

+ - 预充

+ - 终止 + - 充电

+ CA 10 kΩ

470.6 kΩ 48 kΩ

+ VA -

充电控制 定时器 状态逻辑

VBAT

STAT1 STAT2 PG (TE)

DS22005A_CN 第 2 页

2007 Microchip Technology Inc.

MCP73833/4

晶体管导通电阻 导通电阻

VPTH / VREG VPHYS

ITERM / IREG

VRTH / VREG RDSON

— 64 69 —

3.75 5.6 7.5 15

AT738资料

90° 120°

180° DC

3000

4000

5000

IF(AV) [A]

PF(AV) [W] 7000 6000 5000

60° 90° 120° 180° DC

4000

30°

3000 2000 1000 0 0 1000 2000 3000 4000 5000 IF(AV) [A]

元器件交易网

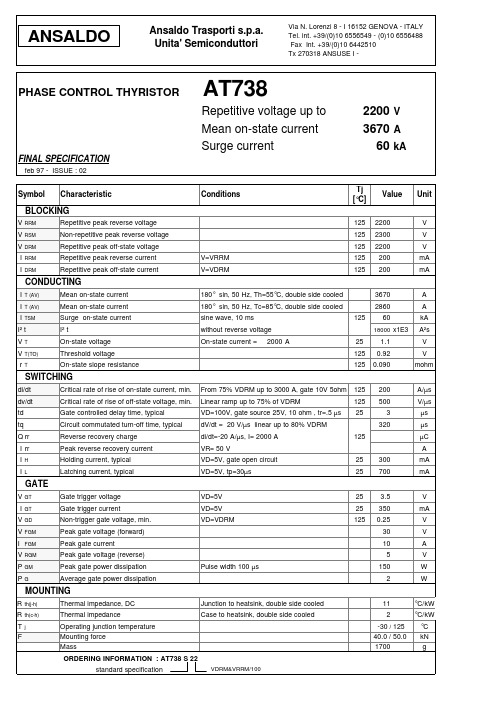

AT738 PHASE CONTROL THYRISTOR

FINAL SPECIFICATION feb 97 - ISSUE : 02

ANSALDO

ON-STATE CHARACTERISTIC Tj = 125 °C 12000 60

SURGE CHARACTERISTIC Tj = 125 °C

Junction to heatsink, double side cooled Case to heatsink, double side cooled

11 2 -30 / 125 40.0 / 50.0 1700

°C/kW °C/kW °C kN g

VDRM&VRRM/100

元器件交易网

PHASE CONTROL THYRISTOR

AT738

Repetitive voltage up to Mean on-state current Surge current 2200 V 3670 A 60 kA

FINAL SPECIFICATION

feb 97 - ISSUE : 02

Symbol

2200 2300 2200 200 200

V V V mA mA

125 125

CONDUCTING

A43L2616AV-6中文资料