基于FPGA的信号发生器设计

基于FPGA方波信号发生器的设计

基于FPGA方波信号发生器设计一.实验目的:1.进一步熟悉QuartusII及其LPM_ROM与FPGA硬件资源的使用方法。

2.加深对电路理论概念的理解3.进一步熟悉常用仪器的使用及调试4.加深计算机辅助分析及设计的概念5.了解及初步掌握对电路进行计算机辅助分析的过程6.培养学生发现问题、分析问题的创新能力7.锻炼学生搜集资料、分析综合资料的能力二.实验原理:方波波信号发生器由四部分组成:计数器或地址发生器(这里选择6位)。

方波信号数据ROM(6位地址线、8位数据线),含有64个8位数据(一个周期)。

VHDL顶层设计。

8位D/A(实验中用DAC0832代替)。

图1所示的信号发生器结构框图中,顶层文件singt.vhd在FPGA中实现,包含两个部分:ROM的地址信号发生器,由6位计数器担任;一个方波数据ROM,由LPM_ROM模块构成。

LPM_ROM底层是FPGA中的EAB、ESB或M4K等模块。

地址发生器的时钟CLK的输入频率f0与每周期的波形数据点数(在此选择64点),以及D/A输出的频率f的关系是:f = f0/64。

图1 方波信号发生器结构框图三.实验内容:1.新建一个文件夹。

利用资源管理器,新建一个文件夹,如:e : \SIN_GNT 。

注意,文件夹名不能用中文。

2.输入源程序。

打开QuartusII,选择菜单“File” “New”,在New 窗中的“Device Design Files”中选择编译文件的语言类型,这里选“VHDL Files”。

然后在VHDL 文本编译窗中键入VHDL 程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity square isport(clk,clr:in std_logic;q:out integer range 0 to 255);end entity;architecture behav of square issignal a:bit;beginprocess(clk,clr) --计数分频variable cnt:integer range 0 to 32; beginif(clr='0') thena<='0';elsif clk'event and clk='1' thenif cnt<31 then --进行32分频cnt:=cnt+1;elsecnt:=0;a<=not a;end if;end if;end process;process(clk,a) --信号输出beginif clk'event and clk='1' thenif a='1' thenq<=255;elseq<=0;end if;end if;end process;end behav;3. 建立.mif格式文件首先选择ROM 数据文件编辑窗,即在File 菜单中选择“New”,并在New 窗中选择“Other files”项,并“Memory Initialization File”(图3-11),点击OK 后产生ROM 数据文件大小选择窗。

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

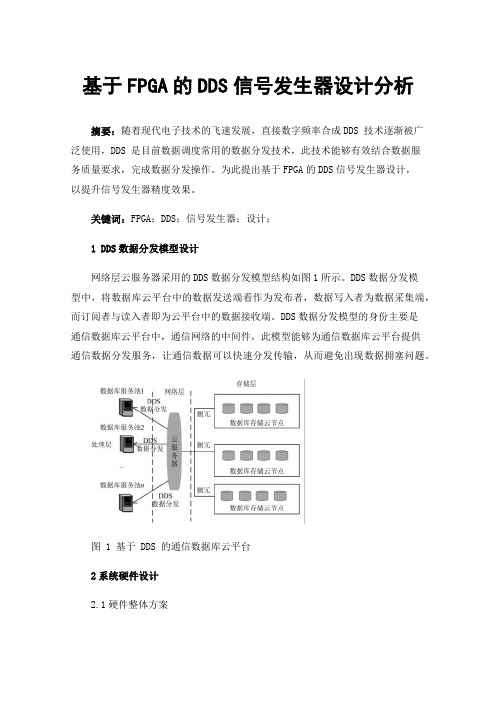

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

(完整word版)基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计摘要:利用FPGA芯片及D/A转换器,采用直接数字频率合成技术,设计并实现了一个频率、幅值可调的信号发生器,同时阐述了该信号发生器的工作原理、电路结构及设计思路。

经过电路调试,输出波形达到技术要求,证明了该信号发生器的有效性和可靠性。

0 引言信号发生器作为一种基本电子设备广泛的应用于教学、科研中,因此从理论到工程对信号的发生进行深入研究,有着积极的意义.随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本文研究了基于FPGA 的DDS信号发生器设计,实现了满足预定指标的多波形输出。

可产生不同频率、幅度的正弦波、三角波、矩形波信号,仿真和实测结果均证实了其灵活性和可靠性。

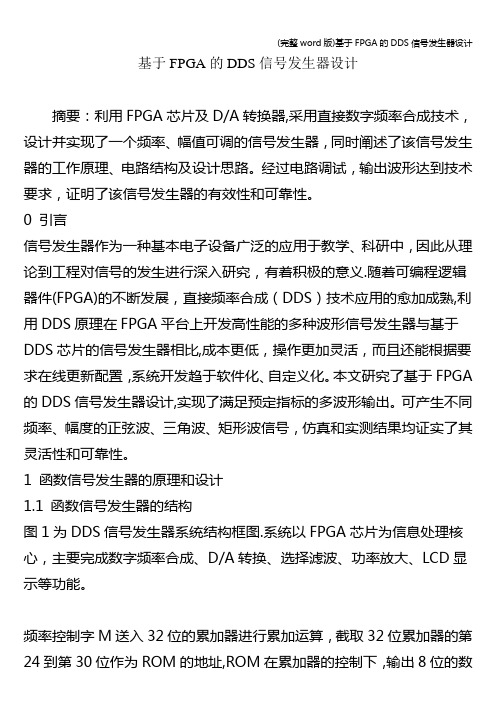

1 函数信号发生器的原理和设计1.1 函数信号发生器的结构图1为DDS信号发生器系统结构框图.系统以FPGA芯片为信息处理核心,主要完成数字频率合成、D/A转换、选择滤波、功率放大、LCD显示等功能。

频率控制字M送入32位的累加器进行累加运算,截取32位累加器的第24到第30位作为ROM的地址,ROM在累加器的控制下,输出8位的数字波形数据,经过DAC0832转换为模拟量,因为DAC0832输出的是电流的形式,所以通过电压转电流电路转换为电压形式的模拟波形,但其中还含有大量的高频成分,为了输出频率纯净的信号波形,再通过一个二阶的有源低通滤波器。

最后为了调节输出信号的峰峰值,再引入一个幅度调节电路。

根据直接数字频率合成理论将系统的频率分辨率及输出频率写为:其中fclk和N为系统时钟和位宽,M为频率控制字,利用信号相位与时间成线性关系的特性,直接对所需信号进行抽样、量化和映射,输出频率可调的信号波形。

基于FPGA的信号发生器设计

基于FPGA的信号发生器设计1 引言电子产业瞬息万变,越来越多的设计开始以ASIC转向FPGA(现场可编程门阵列),FPGA正以各种电子产品的形式进入了我们日常生活的各个角落。

随着新一代FPGA芯片工艺和设计方法的进步及新的应用领域和市场需求的变化, EDA技术有了突飞猛进的发展,数字系统设计也有了革命性的变化。

芯片的复杂程度越来越高,人们对数万门乃至数百万门设计的需求也越来越多,采用硬件描述语言VHDL的设计方式就应运而生,设计工作从行为、功能级开始,并向着设计的高层次发展。

VHDL具有多层次描述系统硬件功能的能力,支持自顶向下和基于库的设计的特点,从系统设计入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的FPGA器件中去,可以实现可编程的专用集成电路(ASIC)的设计。

在电子技术飞速发展的今天,信号发生器在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,或者电路实验和设备检测中具有十分广泛的用途。

基于FPGA的信号发生器的设计,以简单、廉价的元器件构筑,能够产生高精度的正弦波、方波、三角波、锯齿波,同时可以实现波形自由选择。

本设计以花费小、集成度高、性能稳定、使用方便为指导,在功能上力求完善实用,同时兼顾商业价值与应用价值的体现。

2 设计方案2.1 方案介绍正弦波和方波使用MegaWizard Plug-In Manager定制宏功能模块,然后在顶层文件中例化。

锯齿波和三角波采用VHDL语言编程的文本输入方式。

使用分频器将输入的高频脉冲降频得到各模块所需的低频脉冲,使用四选一数据选择器选择波形的输出。

对程序进行编译仿真,成功后下载文件到FPGA实验箱来测试。

通过FPGA软件扫描方式将波形数据读出传输给DAC0832,通过外接示波器显示波形输出。

基于FPGA的信号发生器设计

目录一、设计要求 (3)1. 基本要求 (3)二、设计方案 (3)三、系统基本原理 (4)3.1函数信号发生器的几种实现方式 (4)3.1.1程序控制输出方式 (4)3.1.2 DMA输出方式 (5)3.1.3可变时钟计数器寻址方式 (5)3.1.4直接数字频率合成方式 (6)3.2频率合成器简介 (6)3.2.1频率合成技术概述 (6)3.2.2频率合成器主要指标 (7)2.3 DDS原理 (8)3.3.1相位累加器 (8)3.3.2波形ROM (10)3.3.3 DDS频率合成器优缺点 (10)四、单元模块设计 (11)4.1系统框图 (11)4.2相位累加器与相位寄存器的设计 (12)4.3波形ROM的设计 (13)4.4频率控制模块的设计 (16)4.5 D/A转换器 (17)4.6滤波模块 (19)五、系统源程序 (19)5.1 Verilog HDL 源程序: (19)5.2 STM32 源程序: (23)摘要直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。

与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率高、相位可连续变化和输出波形灵活等优点,因此,广泛应用于教学科研、通信、雷达、自动控制和电子测量等领域。

该技术的常用方法是利用性能优良的DDS专用器件,“搭积木”式设计电路,这种“搭积木”式设计电路方法虽然直观,但DDS专用器件价格较贵,输出波形单一,使用受到一定限制,特别不适合于输出波形多样化的应用场合。

随着高速可编程逻辑器件FPGA的发展,电子工程师可根据实际需求,在单一FPGA上开发出性能优良的具有任意波形的DDS系统,极大限度地简化设计过程并提高效率。

本文在讨论DDS的基础上,介绍利用FPGA设计的基于DDS 的信号发生器。

关键字:FPGA;DDS;函数信号发生器;一、设计要求1. 基本要求(1)信号发生器能产生正弦波、方波和三角波三种周期性波形;(2)将输出信号频率范围为10Hz ~10MHz ,输出信号频率可分段调节:在10Hz ~100kHz 范围内步进间隔为10Hz ;在100kHz ~1MHz范围内步进间隔为100Hz ;在1MHz ~10MHz 范围内步进间隔为1kHz 。

基于FPGA的信号发生器设计

基于FPGA的函数信号发生器设计摘要在信号发生器的设计中,传统的用分立元件或通用数字电路元件设计电子线路的方法设计周期长,花费大,可移植性差。

本设计是利用EDA技术设计的电路,该信号发生器可以输出四种信号,分别是正玄波、方波、三角波、锯齿波,可以通过外部的按键选择波形并调节波形的幅度、相位和频率。

侧重叙述了用FPGA来完成直接数字频率合成器(DDS)的设计,通过调用四个ROM 里面的数据来实现,这里需要一个加法器和一个累加器来产生 ROM 的地址。

通过不断让地址累加,从而不断地从 ROM 中读取波形数据,然后将数据送往 DACTLC5615的驱动模块中,这样最终便输出模拟的波形,最后通过示波器演示仿真结果。

与传统的频率合成方法相比,DDS合成信号具有频率切换时间短、频率分辨率高、相位变化连续等诸多优点。

使用FPGA器件的高性能、高集成度相结合,可以克服传统DDS 设计中的不足,从而设计开发出性能优良的DDS系统。

关键词:FPGA;函数信号发生器;DDS;DAC;The design of function generator based on FPGAAbstractIn the signal generator design , the traditional method of using discrete long design cycle components or general purpose digital circuit component design of electronic circuits , expensive, poor portability . This design is the use of EDA technology designed circuit , the signal generator can output four signals , which are sine wave, square wave , triangle wave , sawtooth wave, you can select and adjust the waveform amplitude, phase and frequency of the waveform by an external button.Emphasis describes the use of FPGA to complete direct digital frequency synthesizer (DDS) design , by calling four ROM inside the data to achieve here need an adder and an accumulator to generate ROM address. By constantly make address accumulate, thereby continuously reads the waveform data from the ROM , and then the data is sent to DACTLC5615 drive module , so that the final output will be analog waveforms, and finally through the oscilloscope display simulation results.Compared with the conventional method of frequency synthesis , DDS frequency synthesized signal having a short switching time , high frequency resolution, and many other advantages of continuous phase change . FPGA devices using high-performance, highly integrated combination of design can overcome the shortcomings of traditional DDS , which designed and developed the excellent performance of the DDS system .Keywords: FPGA; function signal generator; DDS; DAC;目录第一章绪言 (1)1.1 课题背景 (1)1.2 课题研究的目的和意义 (1)1.3 国内外的研究状况 (2)1.3.1波形发生器的发展状况 (2)1.3.2 国内外波形发生器产品比较 (3)1.3.3 本课题在国内外的研究现状 (3)第二章信号发生器的方案设计 (4)2.1硬件组成部分 (4)2.1.1 FPGA实验板 (4)2.2外围电路 (6)2.2.1TLC5615芯片 (6)2.2.2 TLC5615工作原理 (8)2.3 RC低通滤波电路 (9)第三章直接数字合成技术(DDS) (11)3.1 直接数字合成技术(DDS) (11)3.2 DDS 的基本原理 (11)3.3 DDS 的性能分析 (12)3.3.1 DDS理想抽样频谱 (12)3.4 DDS 杂散频谱分析 (13)3.4.1相位截断对输出信号频谱的影响 (13)3.4.2 D/A 非理想特性及参考时钟相位噪声对输出信号频谱的影响 (13)3.5基于DDS的信号函数发生器 (14)3.5.1 整体框图及其说明 (14)3.5.2 按键消抖模块 (14)3.5.3 按键编码 (16)3.5.4 DDS 信号发生器 (18)3.5.5 RTL电路图 (20)第四章实验分析 (21)4.1 实验过程 (21)4.1.1 程序调试 (21)4.2 实验结果 (23)4.3 实验总结 (24)致谢 (24)参考文献 (25)第一章绪言1.1 课题背景在一些电子设备的电路板故障检测仪中,往往需要频率、幅度都能由计算机自动调节的信号源。

基于FPGA的多功能信号发生器的设计

电子电路设计与方案0 前言现场可编程门阵列具有运行速度快,修改灵活方便,并自带大量的输入输出端口等优点,通过FPGA实现该信号发生器的核心部件DDS模块,可以灵活地对信号发生器的参数进行调整,另外通过单片机的配合实现对其他外设电路的控制,实现信号发生器显示、参数调节等辅助的功能,通过数模转换电路和波形处理电路实现所需信号波形的输出。

本设计的主要指标为:(1)频率范围:0~1MHz,可通过键盘任意设置频率,步进1Hz。

(2)频率精度:±1%。

(3)幅值范围:±5V,可通过键盘任意设置幅度,步进100mV。

(4)幅值精度:±5%。

(5)用液晶显示所选波形名称,频率,幅值。

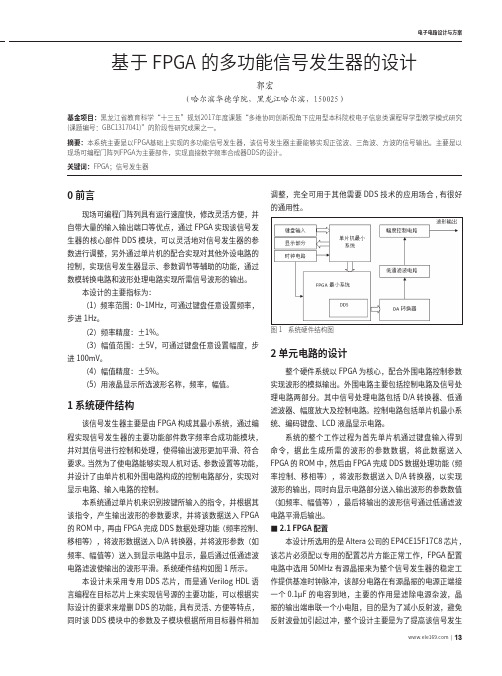

1 系统硬件结构该信号发生器主要是由FPGA构成其最小系统,通过编程实现信号发生器的主要功能部件数字频率合成功能模块,并对其信号进行控制和处理,使得输出波形更加平滑、符合要求。

当然为了使电路能够实现人机对话、参数设置等功能,并设计了由单片机和外围电路构成的控制电路部分,实现对显示电路、输入电路的控制。

本系统通过单片机来识别按键所输入的指令,并根据其该指令,产生输出波形的参数要求,并将该数据送入FPGA 的ROM中,再由FPGA完成DDS数据处理功能(频率控制、移相等),将波形数据送入D/A转换器,并将波形参数(如频率、幅值等)送入到显示电路中显示,最后通过低通滤波电路滤波使输出的波形平滑。

系统硬件结构如图1所示。

本设计未采用专用DDS芯片,而是通Verilog HDL语言编程在目标芯片上来实现信号源的主要功能,可以根据实际设计的要求来增删DDS的功能,具有灵活、方便等特点,同时该DDS模块中的参数及子模块根据所用目标器件稍加调整,完全可用于其他需要DDS技术的应用场合,有很好的通用性。

图1 系统硬件结构图2 单元电路的设计整个硬件系统以FPGA为核心,配合外围电路控制参数实现波形的模拟输出。

外围电路主要包括控制电路及信号处理电路两部分。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 7 ( 3 ) : 8 8 ~ 9 1

J u n . 2 0 1 5

6月

d o i : 1 0 . 3 9 6 9 6 . i s s n . 1 0 0 2 — 2 0 9 0 . 2 0 1 5 . 0 3 . 0 2 0

基于 F P GA 的信 号发 生器设 计

刘英楠 。 衣淑 娟 , 宫龙江

s q u a r e w a v e , t i r a n g l e w a v e a n d s a w t o o t h w a v e o f a d j u s t a b l e f r e q u e n c y . T h r o u g h t h e h a r d w a r e t e s t , t h e r e s u l t s s h o w e d t h a t t h e s y s t e m

( 1 . 黑龙江八一农垦大学信息技术 学院 , 大庆 1 6 3 3 1 9 ; 2 . 东北石油大学党委宣传部 ) 摘 要: 作为调试设 备 , 数字信号发生器是数字信号处理 中不可缺少 的一部分 , 广泛的应用在生产生活 当中。 由于 F P G A集密

度高 , 功耗低 , 体积小以及可靠性高等优点于一身 , 所 以采用 A h e r a 公 司生产 的 F P G A实现数字 信号发生器 的设计 , 该数 字信 号发生器能够产生可调频率 的正弦波 、 方波 、 三角 波和锯齿波 。通过硬件 系统测试 , 结果表 明: 系统精度较高 、 带负载 能力较

第 2 7卷 第 3期

2 0 1 5 年

黑 龙 江 八 一 农 垦 大 学 学 报

J o u r n a l o f H e i l o n g j i a n g B a y i A g r i c u l t u r a l U n i v e r s i t y

p r o d u c t i o n a n d l i f e . S i n c e F P GA a d v a n t a g e o f h i g h d e n s i t y ,l o w p o we r c o n s u mp t i o n,s ma l l v o l u me a n d h i g h r e l i a b i l i t y, F P GA o f Al t e r a c o mp a n y wa s u s e d t o r e li a z e he t d e s i g n o f d i g i t a l s i g n a l g e n e r a t o r , a n d t h e d i g i t a l s i g n a l g e n e r a t o r c o u l d g e n e r a t e s i n e wa v e ,

Ke y wo r d s : s i g n a l g e n e r a t o r ; D / A c o n v e r s i o n; F P GA

如今 , 现代电子技术迅猛发展 , 电子测量工作对 信号发生器的正弦信号源、 脉冲信号源 、 函数信号源 以及 高频 信 号 源等 性能 方 面有 了更 严 格 ,更 具体 的 要求。传统 的信号发生器具有成本高 , 操作不灵活等 缺点 已经远 远 满足 不 了现 代 电子测 量 的需 要 退 出 了

强、 运行稳 定。

关键词 : 信号发生器 ; D / A转换 ; F P G A

中 图分 类 号 : T P 2 7 3 文 献 标 识码 : A 文章编号 : 1 0 0 2 — 2 0 9 0 ( 2 0 1 5 ) 0 3 — 0 0 8 8 — 0 4

De s i g n o f S i g n a l Ge n e r a t o r Ba s e d o n FPGA

L i u Yi n g n a n 1 , Yi S h u j u a n 1 , Go n g L o n g j i a n g 2

( 1 . C o l l e g e o f I n f o r ma t i o Байду номын сангаас a n d T e c h n o l o g y , H e i l o n g j i a n g B a y i A g r i c u l t u r a l U n i v e si r t y , D a q i n g 1 6 3 3 1 9 ;

2 . P r o p a g a n d a D e p a r t m e n t , N o r t h e a s t P e t r o l e u m U n i v e si r t y )

Ab s t r a c t : As d e b u g g i n g e q u i p me n t , t h e d i g i t a l s i g n a l g e n e r a t o r wa s a n i n d i s p e n s a b l e p a r t i n d i g i t a l s i g n a l p r o c e s s i n g , a n d wa s u s e d i n