TSOP2830ON1中文资料

uln2803资料介绍

6

V

7

V

8

V

2.4

V

–2

25 pF –

1

µs –

1

µs –

50 µA 6 100 µA 6

2

V7

3/8

ULN2801A - ULN2802A - ULN2803A - ULN2804A - ULN2805A

TEST CIRCUITS Figure 1a.

Figure 1b.

Figure 2.

Figure 3.

MAX. 0.065

0.915

0.280 0.155 0.063

7/8

ULN2801A - ULN2802A - ULN2803A - ULN2804A - ULN2805A

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rig hts of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

上工申贝缝制机械产品说明书

SINCE 1965行业首家上市公司A股代码 600843 B股代码 900924上工申贝(集团)股份有限公司Shang Gong Group Co.,ltd.上工缝制机械(浙江)有限公司地址:中国 · 浙江省台州市黄岩区新前街道锦川路318号电话:0576-******** 4008-600-843传真:*************网址: 邮编:318020 邮箱:*********************Shang Gong Sewing Machinery (Zhejiang) Co., Ltd.ADD: 318 Jinchuan Road, Xinqian Street, Huangyan District, Taizhou City, Zhejiang Province, China TEL: 0086-576-84332256 4008-600-843FAX: 0086-576-84332258 website: Postcode:318020Email:*********************上工缝制官方微信号上工缝制官方抖音号上工缝制官方视频号MESSAGE FROM THE CHAIRMAN董事长致辞作为中国最早从事工业缝制设备专业化生产经营的大型骨干企业;在缝制机械行业第一家发行A 、B 股的上市公司;也是第一批响应国家“走出去”战略,实施跨国并购,进行国际化经营的国有控股企业之一,上工申贝走过了风雨兼程的50载。

回眸过去,展望未来,惜时勤业的上工申贝人从未放弃心中的梦—— 续写上工申贝的辉煌。

随着2005年跨国并购全球缝制机械行业的引领者——德国杜克普 · 爱华公司之后,公司全球化经营的战略不断深入,我们有着太多的经历和收获。

面对2008年全球金融危机对缝制设备行业的巨大冲击,众志成城的上工申贝人,以淡定从容的气度应对危机,积累了逆势飞扬、危中求机的资本和体验,从而在行业经济企稳回暖之时,率先走出困境,扭亏为盈。

拓斯达 辅机系统 高端智能装备产品说明书

作为中国整厂自动化第一品牌,拓斯达专注于高端智能装备,主张 的品牌价值,即随着技术不断进步与突破,用智能系统替代人工,开拓可替代的应用领域,推动产业进步助力企业发展,同时把制造业从劳动密集型带入完全的自动化,回归到自然,人性,和谐的状态。

新出现的文明与传统的旧工业文明有许多矛盾之处:它既有高度的科学技术,同时又是反工业化的。

As the top brand of complete factory automation in China, TOPSTAR focuses on high-end innovative equipment, proposes the brand value of. We initiate to replacelabor with intelligent systems, expand replaceable application areas and promote industrial progress to help enterprise developing, transform labor intensive type to full automation and return to a natural, human-oriented and harmonious status.Much in this emerging civilization contradicts the old traditional industrial civilization. It is, at one and the same time, highly technological and anti-industrial.摘自《第三次浪潮》——阿尔文·托夫勒from The Third Wave,Alvin Toffler企业简介Guangdong Topstar Technology Co., Ltd.(SZ.300607)is a National High-Tech Enterprise, focusing on the development of industrial robots, manufacturing and sales, dedicated to systems integration, products manufacturing and software development--three in one integration of industrial robot ecosystems and overall automation solution.Since the establishment in 2007, adhering to the brand advocate "Let Industrial Civilization Return To The Natural Beauty” and the core value "one year investment return for the automation solution", the business has maintained a rapid growth. In 2015, Topstar was named “China Industrial Automation Leading Enterprise” by the State Ministry of Information Industry Development Institute. We have served about 4000 customers in domestic and oversea market, including well-known companies from Global 500. Now our sales and service network are all over the country in China and the products have been exported to more than 30 countries in Asia, America, Europe, Africa, etc.In 2014, we were ranked on the 30th as "Potential 100 Non-Listed Chinese Enterprises" by Forbes. In 2015, we were named "China's Most Potential Enterprise" by Ernst & Young with Fudan University, at the same time won the Guangdong Provincial-level Enterprise Technical Center, the Rapid Growth of Small&Medium Enterprises of Guangdong Province, and as the only one robot enterprise selected in Guangdong Province Manufacturing 500, honored “2014 and 2015Annual Golden Globe” by GG Robots, etc. In 2016, was assessed as the first batch of robot key enterprises in Guangdong Province. Our enterprise is highly appreciated by national ministries , provincial and municipal leaders.At present, our shareholders include China Huarong, top PE Shenzhen Fortune Capital, Industrial Securities and Dongguan Sangem Group.Topstar has recruited top R&D experts from Canada, Korea and Taiwan, and carried out long-term research cooperation with Tsinghua University, Huazhong University of Science and Technology, South China University of Technology, Dongguan Institute of Technology and other research institutions and well-known colleges. We have achieved 100 national patents and 10 software copyrights.Three kinds of Robots with independent intellectual property were named Guangdong Provincial Famous Brand and five kinds of machines were named Guangdong High-Tech Products. Many machines have been certified by CE.Company profile广东拓斯达科技股份有限公司(SZ.300607)是国家级高新技术企业,专注于工业机器人的研发、制造、销售,致力于打造系统集成 + 本体制造 + 软件开发三位一体的工业机器人生态系统和整体自动化解决方案。

TSOP2830UH1中文资料

Document Number 82063 Rev. 3, 13-Jun-00

元器件交易网

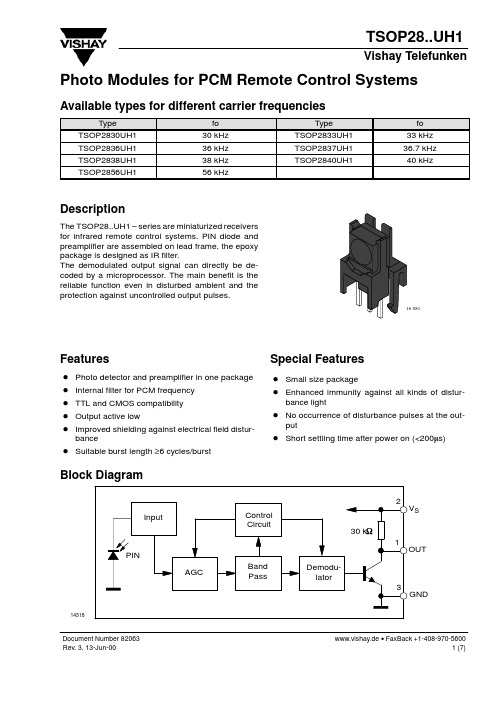

TSOP28..UH1

Vishay Telefunken Suitable Data Format

The circuit of the TSOP28..UH1 is designed in that way that unexpected output pulses due to noise or disturbance signals are avoided. A bandpassfilter, an integrator stage and an automatic gain control are used to suppress such disturbances. The distinguishing mark between data signal ( not suppressed) and disturbance signal (supressed) are carrier frequency, burst length and Signal Gap Time (see diagram below). The data signal should fullfill the following condition: • Carrier frequency should be close to center frequency of the bandpass (e.g. 38kHz). • Burst length should be 6 cycles/burst or longer. • After each burst a gap time of at least 10 cycles is neccessary. • The data format should not make a continuous signal transmission. There must be a Signal Gap Time (longer than 15ms) at least each 90ms (see Figure A). Some examples for suitable data format are: NEC Code (repetitive pulse), NEC Code (repetitive data), Toshiba Micom Format, Sharp Code, RC5 Code, RECS–80 Code, R–2000 Code. When a disturbance signal is applied to the TSOP28..UH1 it can still receive the data signal. However the sensitivity is reduced to that level that no unexpected pulses will occure. Some examples for such disturbance signals which are suppressed by the TSOP28..UH1 are: • DC light (e.g. from tungsten bulb or sunlight), • Continuous signal at 38kHz or at any other frequency, • Signals from fluorescent lamps (see Figure B). • Continuous IR signal (e.g. 1ms burst, 2ms pause)

SR2830A SR上海胜芯微电子有限公司

用了专利的恒流控制技术, 实现高精度的 LED 恒流 输出和优异的线电压调整率。 芯片工作在电感电流 临界模式, 输出电流不随电感量和 LED 工作电压的 变化而变化,实现优异的负载调整率。

SR2830A 具有多重保护功能,包括 LED 短路保护,

应用

LED 蜡烛灯 LED 球泡灯 其它 LED 照明

注 2:温度升高最大功耗一定会减小,这也是由 TJMAX, θJA,和环境温度 TA 所决定的。最大允许功耗为 PDMAX = (TJMAX - TA)/

θJA 或是极限范围给出的数字中比较低的那个值。

注 3:人体模型,100pF 电容通过 1.5KΩ 电阻放电。

推荐工作范围

符号 ILED 1 ILED2 ILED3 VLED min 参数 输出 LED 电流@ Vout=150V (输入电压 176V~265V) 输出 LED 电流@ Vout=72V (输入电压 176V~265V) 输出 LED 电流@ Vout=36V (输入电压 176V~265V) 最小负载 LED 电压 参数范围 60 75 90 >18 单位 mA mA mA V

t off

L IPK VLED

储能电感的计算公式为:

V (VIN V LED ) L LED f IPK VIN

其中, f 为系统工作频率。 SR2830A 的系统工作频率 和输入电压成正比关系,设置 SR2830A 系统工作频 率时,选择在输入电压最低时设置系统的最低工作 频率,而当输入电压最高时,系统的工作频率也最 高。

非隔离降压型 LED 恒流驱动芯片 概述

SR2830A是一款高精度降压型的 LED 恒流驱动芯

SR2830A

特点

P28F010-90资料

元器件交易网

28F010/28F020

E

CONTENTS

PAGE PAGE 4.5 DC Characteristics—28F020—TTL/NMOS Compatible—Commercial Products .......... 22 4.6 DC Characteristics—28F010—CMOS Compatible—Commercial Products .......... 24 4.7 DC Characteristics—28F020—CMOS Compatible—Commercial Products .......... 25 4.8 DC Characteristics—28F010—TTL/NMO Compatible—Extended Temperature Products ................................................... 27 4.9 DC Characteristics—28F020—TTL/NMO Compatible—Extended Temperature Products ................................................... 29 4.10 DC Characteristics—28F010—CMOS Compatible—Extended Temperature Products ................................................... 31 4.11 DC Characteristics—28F020—CMOS Compatible—Extended Temperature Products ................................................... 32 4.12 AC Characteristics—28F010—Read-Only Operation—Commercial and Extended Temperature Products .............................. 35 4.13 AC Characteristics—28F020—Read Only Operations—Commercial and Extended Temperature Products .............................. 36 4.14 AC Characteristics—28F010— Write/Erase/Program Only Operation— Commercial and Extended Temperature Products ................................................... 38 4.15 AC Characteristics—28F020— Write/Erase/Program Only Operation— Commercial and Extended Temperature Products ................................................... 39 4.16 AC Characteristics—28F010—Alternative CE#-Controlled Write—Commercial and Extended Temperature ............................. 44 4.17 AC Characteristics—28F020—Alternate CE# Controlled Writes—Commercial and Extended Temperature Products .............. 45 4.18 Erase and Programming Performance ..... 46 5.0 ORDERING INFORMATION ......................... 47 6.0 ADDITIONAL INFORMATION....................... 47

上润精密仪器 智能给定操作器 说明书

先按SET键不放再按增键,5秒钟后即可进入用户参数的设定。

用户参数设定如表四:

表四

符号 名 称 DE 通讯仪表设备号

仪表通讯 BT 波特率设定

设定范围

1~254 BT=0

BT=1 BT=2

BT=3 BT=4 BT=5

参数说明

在同一通讯网络设备号应唯一,出厂设为1

通讯波特率为300bps 通讯波特率为600bps

智能给定操作器

一、产品概述

智能给定操作器 具有万能分度号输入的位式控制表所有 特点,自动时测量值与给定值比较,决定操作器输出的正转或 反转,双屏数码管显示,上屏显示测量值,下屏显示给定值, 手 动时由按键操作决定正转或反转开关量输出,与电动执行机构 配合可控制系统的液位或温度等。

二、技术参数

±0.5%FS ±1(字) 数字显示:±1字;光柱显示:±1线 数字:-1999~9999 光柱:0 ~100% 0~50℃ ≤85% 无凝露避免强腐蚀气体 AC90V~265V (开关电源) ≤ 5W(AC 90V~265V开关电源) 。 操作信号输出正转、反转开关量,上、下限幅可设 定。 具有万能分度号输入的位式控制表所有特点。 可带RS485/RS232隔离通讯接口。

下限报警

N H L

T W

无报警(可省略) 上限报警

下限报警

AC220V 线 性 电 源(可 省 略 ) AC(90~265)V开关电源供电 DC24V供电

选型举例:WP-D855-012-03-HL;

-8-

智能给定操作器

七、安装与使用

本仪表采用标准卡入式结构,请将仪表轻轻推入表盘即可。 mm

5 6 7 8 PV

WP-70

外形尺寸:72×72× 115mm

TSOP34838;中文规格书,Datasheet资料

IR Receiver Modules for Remote Control SystemsMECHANICAL DATAPinning for TSOP348.., TSOP344..:1 = OUT, 2 = GND, 3 = V SPinning for TSOP322.., TSOP324..:1 = OUT, 2 = V S , 3 = GNDFEATURES•Very low supply current•Photo detector and preamplifier in one package •Internal filter for PCM frequency •Improved shielding against EMI •Supply voltage: 2.5 V to 5.5 V•Improved immunity against ambient light •Insensitive to supply voltage ripple and noise•Material categorization: For definitions of compliance please see /doc?99912DESCRIPTIONThese products are miniaturized receivers for infrared remote control systems. A PIN diode and a preamplifier are assembled on a lead frame, the epoxy package acts as an IR filter.The demodulated output signal can be directly decoded by a microprocessor. The TSOP348.., TSOP322.. are compatible with all common IR remote control data formats. The TSOP324.., TSOP344.. are optimized to suppress almost all spurious pulses from energy saving fluorescent lamps but will also suppress some data signals.This component has not been qualified according to automotive specifications.BLOCK DIAGRAMAPPLICATION CIRCUITPARTS TABLECARRIER FREQUENCY STANDARD APPLICATIONS(AGC2)VERY NOISY ENVIRONMENTS(AGC4)PINNING1 = OUT,2 = GND,3 = V S1 = OUT,2 = V S ,3 = GND1 = OUT,2 = GND,3 = V S1 = OUT,2 = V S ,3 = GND30 kHz TSOP34830TSOP32230TSOP34430TSOP3243033 kHz TSOP34833TSOP32233TSOP34433TSOP3243336 kHz TSOP34836TSOP32236TSOP34436TSOP3243638 kHz TSOP34838TSOP32238TSOP34438TSOP3243840 kHz TSOP34840TSOP32240TSOP34440TSOP3244056 kHzTSOP34856TSOP32256TSOP34456TSOP32456Note•Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect the device reliability.TYPICAL CHARACTERISTICS (T amb = 25 °C, unless otherwise specified)Fig. 1 - Output Active Low Fig. 2 - Pulse Length and Sensitivity in Dark AmbientABSOLUTE MAXIMUM RATINGSPARAMETER TEST CONDITIONSYMBOLVALUE UNIT Supply voltage V S - 0.3 to + 6V Supply current I S 3mA Output voltage V O - 0.3 to (V S + 0.3)V Output current I O 5mA Junction temperature T j 100°C Storage temperature range T stg - 25 to + 85°C Operating temperature range T amb- 25 to + 85°C Power consumption T amb ≤ 85 °C P tot 10mW Soldering temperaturet ≤ 10 s, 1 mm from caseT sd260°CELECTRICAL AND OPTICAL CHARACTERISTICS (T amb = 25 °C, unless otherwise specified)PARAMETER TEST CONDITION SYMBOLMIN.TYP.MAX.UNIT Supply current E v = 0, V S = 3.3 V I SD 0.270.350.45mA E v = 40 klx, sunlightI SH 0.45mA Supply voltage V S 2.55.5V Transmission distance E v = 0, test signal see fig. 1,IR diode TSAL6200,I F = 250 mA d 45m Output voltage low I OSL = 0.5 mA, E e = 0.7 mW/m 2,test signal see fig. 1V OSL 100mV Minimum irradiance Pulse width tolerance:t pi - 5/f 0 < t po < t pi + 6/f 0,test signal see fig. 1E e min.0.10.25mW/m 2Maximum irradiance t pi - 5/f 0 < t po < t pi + 6/f 0,test signal see fig. 1E e max.30W/m 2DirectivityAngle of half transmissiondistanceϕ1/2± 45degE eV O V VFig. 3 - Output Function Fig. 4 - Output Pulse Diagram Fig. 5 - Frequency Dependence of Responsivity Fig. 6 - Sensitivity in Bright AmbientFig. 7 - Sensitivity vs. Supply Voltage DisturbancesFig. 8 - Sensitivity vs. Electric Field DisturbancesEV O V V OL0.00.20.40.60.81.01.20.70.9 1.1 1.3f/f 0 - Relative Frequency16925E /E - R e l. R e s p o n s i v i t y e m i n.eFig. 9 - Max. Envelope Duty Cycle vs. Burst Length Fig. 10 - Sensitivity vs. Ambient TemperatureFig. 11 - Relative Spectral Sensitivity vs. WavelengthFig. 12 - Horizontal DirectivityFig. 13 - Sensitivity vs. Supply VoltageSUITABLE DATA FORMATThese products are designed to suppress spurious output pulses due to noise or disturbance signals. Data and disturbance signals can be distinguished by the devices according to carrier frequency, burst length and envelope duty cycle. The data signal should be close to the band-pass center frequency (e.g. 38 kH z) and fulfill the conditions in the table below.When a data signal is applied to the IR receiver in the presence of a disturbance signal, the sensitivity of the receiver is reduced to insure that no spurious pulses are present at the output. Some examples of disturbance signals which are suppressed are:•DC light (e.g. from tungsten bulb or sunlight)•Continuous signals at any frequency•Strongly or weakly modulated noise from fluorescent lamps with electronic ballasts (see figure 14 or figure 15)Fig. 14 - IR Signal from Fluorescent Lampwith Low ModulationFig. 15 - IR Signal from Fluorescent Lampwith High ModulationNote•For data formats with short bursts please see the datasheet for TSOP323.., TSOP325.., TSOP343.., TSOP345..0101520Time (ms)16920I R S i g n a l50101520Time (ms)16921I R S i g n a l5TSOP322.., TSOP348..TSOP324.., TSOP344..Minimum burst length10 cycles/burst 10 cycles/burst After each burst of lengtha minimum gap time is required of10 to 70 cycles ≥ 10 cycles 10 to 35 cycles ≥ 10 cycles For bursts greater thana minimum gap time in the data stream is needed of 70 cycles > 4 x burst length35 cycles> 10 x burst lengthMaximum number of continuous short bursts/second 18001500Recommended for NEC code yes yes Recommended for RC5/RC6 code yes yes Recommended for Sony codeyes no Recommended for Thomson 56 kHz codeyes yes Recommended for Mitsubishi code (38 kHz, preburst 8 ms, 16 bit)yes no Recommended for Sharp codeyesyesSuppression of interference from fluorescent lampsMost common disturbance signals are suppressedEven extreme disturbance signals are suppressedPACKAGE DIMENSIONS in millimetersLegal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.分销商库存信息: VISHAYTSOP34838。

TSDF52830YS_08中文资料

TSDF52830YSDocument Number 85178Rev. 1.2, 05-Sep-08Vishay Semiconductors1Not for new design, this product will be obsoleted soonDual - MOSMIC ®- two AGC Amplifiers for TV-Tuner Prestage CommentsMOSMIC - MOS M onolithic I ntegrated C ircuitDescriptionThe Dual-MOSMI C ® TSDF52830YS, assembled in the well-known SOT-363 plastic package, is a combi-nation of two different MOSMIC ® amplifiers with com-mon Source and common Gate 2 leads and an integrated switch. One of the MOSMIC stages is opti-mized for use in V HF applications, especially regard-ing cross modulation performance and noise figure at lower V HF frequencies, whereas the other stage is optimized for use in UHF applications regarding gain and noise figure performance at higher frequencies of UHF range. The integrated switch is operated by the Gate 1 bias of the UHF amplifier on Pin 1. All of the Gates are protected against excessive input voltage surges by integrated antiserial diodes between them-selves and Source.Features•Two differently optimized amplifiers in a single package. One of them has a fullyinternal self-biasing network on chip andthe other has a partly integrated bias foreasy Gate 1 switch-off with PNP switching transis-tors inside PLL -IC•Internal switch for saving lines on PCB layout as well as external components•Integrated gate protection diodes •Low noise figure, high gain•Typical forward transadmittance of 31 mS resp. 28 mS•Superior cross modulation at gain reduction •High AGC-range with soft slope•Main AGC control range from 3 V to 0.5 V •Lead (Pb)-free component•Component in accordance to RoHS 2002/95/EC and W EEE 2002/96/ECApplicationsLow noise gain controlled V HF and UHF input stages with 5 V supply voltage, such as in digital and analog T V tuners and in other multimedia and communica-tions equipment.Typical ApplicationMechanical DataCase: SOT-363 Plastic case Weight: approx. 6.0 mg V - V ishayY - Year, is variable for digit from 0 to 9Parts TablePartMarkingPackageTSDF52830YSW N5SOT -363元器件交易网 2Document Number 85178Rev. 1.2, 05-Sep-08TSDF52830YSVishay Semiconductors Absolute Maximum RatingsT amb = 25°C, unless otherwise specifiedAmplifier 1Following data are valid for operating amplifier 1 (pin 1, 3, 5, 2) which is optimized for UHF applicationsAmplifier 2Following data are valid for operating amplifier 2 (pin 6, 4, 5, 2) which is optimized for V HF applicationsMaximum Thermal Resistance1)on glass fibre printed board (25 x 20 x 1.5) mm 3 plated with 35 μm CuParameterTest conditionSymbol V alue Unit Drain - source voltage V DS 8V Drain currentI D 25mA Gate 1/Gate 2 - source peak current± I G1/G2SM 10mA Gate 1/Gate 2 - source voltage + V G1± V G2SM6V Gate 1 - source voltage - V G1SM 1.5V Total power dissipation T amb ≤ 60°CP tot 200m W Channel temperature T Ch 150°C Storage temperature rangeT stg- 55 to + 150°CParameterTest conditionSymbol V alue Unit Drain - source voltage V DS 8V Drain currentI D 30mA Gate 1/Gate 2 - source peak current± I G1/G2SM 10mA Gate 1/Gate 2 - source voltage + V G1/± V G2SM6V Gate 1 - source voltage - V G1SM 1.5V Total power dissipation T amb ≤ 60°CP tot 200m W Channel temperature T Ch 150°C Storage temperature rangeT stg- 55 to + 150°CParameterTest condition Symbol V alue Unit Channel ambient1)R thChA450K/WTSDF52830YSDocument Number 85178Rev. 1.2, 05-Sep-08Vishay Semiconductors3Electrical DC CharacteristicsT amb = 25°C, unless otherwise specifiedAmplifier 1Following data are valid for operating amplifier 1 (pin 1, 3, 5, 2) which is optimized for UHF applicationsAmplifier 2Following data are valid for operating amplifier 2 (pin 6, 4, 5, 2) which is optimized for V HF applicationsParameterT est conditionSymbol Min T yp.MaxUnit Drain - source breakdown voltageI D = 10 μA, V G2S = V G1S = 0V (BR)DSS15V Gate 1 - source breakdown voltage+ I G1S = 10 mA, V G2S = V DS = 0+ V (BR)G1SS 710V ± I G2S = 10 mA, V G1S = V DS = 0± V (BR)G2SS710V Gate 1 - source leakage current + V G1S = 5 V , V G2S = V DS = 0+ I G1SS 20nA Gate 2 - source leakage current ± V G2S = 5 V , V G1S = V DS = 0± I G2SS 20nA Drain - source operating current V DS = V RG1 = 5 V , V G2S = 4 V ,R G1 = 100 k ΩI DSO 81217mA Gate 1 - source cut-off voltage V DS = 5 V , V G2S = 4, I D = 20 μA V G1S(OFF)0.3 1.0V Gate 2 - source cut-off voltageV DS = V RG1 = 5 V , R G1 =100 k Ω, I D = 20 μAV G2S(OFF)0.31.2VParameterT est conditionSymbolMin T yp.Max Unit Gate 1 - source breakdown voltage+ I G1S = 10 mA, V G2S = V DS = 0+ V (BR)G1SS 710V Gate 2 - source breakdown voltage± I G2S = 10 mA, V G1S = V DS = 0± V (BR)G2SS710V Gate 1 - source leakage current + V G1S = 5 V , V G2S = V DS = 0+ I G1SS 50μA Gate 2 - source leakage current ± V G2S = 5 V , V G1S = V DS = 0± I G2SS 20nA Drain - source operating current V DS = V RG1 = 5 V , V G2S = 4 V ,Gate 1 = nc I DSP 81317mA Gate 2 - source cut-off voltageV DS = V RG1 = 5 V , Gate 1 = nc, I D = 20 μAV G2S(OFF)0.31.2V 4Document Number 85178Rev. 1.2, 05-Sep-08TSDF52830YSVishay Semiconductors Electrical AC CharacteristicsT amb = 25°C, unless otherwise specifiedAmplifier 1V DS = V RG1 = 5 V , V G2S = 4 V , R G1 = 100 k Ω, I D = I DSO, f = 1 MHz, T amb = 25°C, unless otherwise specified Following data are valid for operating amplifier 1 (pin 1, 3, 5, 2) which is optimized for UHF applicationsRemark on improving intermodulation behavior:By setting R G1 smaller than 100 k Ω, typical value of I DSO will raise and improved intermodulation behavior will be performed.ParameterTest conditionSymbol Min Typ.Max Unit Forward transadmittance |y 21s |273135mS Gate 1 input capacitance C issg1 1.7 2.1pF Feedback capacitance C rss 20fF Output capacitance C oss 0.9pF Power gainG S = 2 mS, B S = B Sopt , G L = 0.5 mS, B L = B Lopt , f = 200 MHzG ps33dBG S = 3.3 mS, B S = B Sopt , G L = 1 mS, B L = B Lopt , f = 400 MHzG ps30dBG S = 3.3 mS, B S = B Sopt , G L = 1 mS, B L = B Lopt , f = 800 MHzG ps25dBAGC range V DS = 5 V , V G2S = 0.5 to 4 V , f = 800 MHzG ps 4050dB Noise figureG S = G L = 20 mS, B S = B L = 0, f = 50 MHzF 5.07.0dBG S = 2 mS, G L = 0.5 mS, B S = B Sopt , f = 400 MHz F 1.0 1.5dB G S = 3.3 mS, G L = 1 mS, B S = B Sopt , f = 800 MHzF 1.32.0dB Cross modulationInput level for k = 1 % @ 0 dB AGC f w = 50 MHz, f unw = 60 MHz X mod90dB μVInput level for k = 1 % @ 40 dB AGC f w = 50 MHz, f unw = 60 MHzX mod100105dB μVTSDF52830YSDocument Number 85178Rev. 1.2, 05-Sep-08Vishay Semiconductors5Amplifier 2V DS = V RG1 = 5 V , V G2S = 4 V , Gate 1 = nc, I D = I DSP, f = 1 MHz, T amb = 25°C, unless otherwise specified Following data are valid for operating amplifier 2 (pin 6, 4, 5, 2) which is optimized for V HF applicationsParameterT est conditionSymbol Min T yp.Max Unit Forward transadmittance |y 21s |232833mS Gate 1 input capacitance C issg1 2.2 2.7pF Feedback capacitance C rss 20fF Output capacitance C oss 1.0pF Power gainG S = 2 mS, B S = B Sopt , G L = 0.5 mS, B L = B Lopt , f = 200 MHzG ps32dBG S = 2 mS, B S = B Sopt , G L = 1 mS, B L = B Lopt , f = 400 MHzG ps28dBG S = 3.3 mS, B S = B Sopt , G L = 1 mS, B L = B Lopt , f = 800 MHzG ps22dBAGC range V DS = 5 V , V G2S = 0.5 to 4 V , f = 200 MHzG ps 50dB Noise figureG S = G L = 20 mS, B S = B L = 0, f = 50 MHzF 4.5 6.0dBG S = 2 mS, G L = 1 mS, B S = B Sopt , f = 400 MHz F 1.0 1.6dB G S = 3.3 mS, G L = 1 mS, B S = B Sopt , f = 800 MHzF 1.52.3dB Cross modulationInput level for k = 1 % @ 0 dB AGC f w = 50 MHz, f unw = 60 MHz X mod90dB μVInput level for k = 1 % @ 40 dB AGC f w = 50 MHz, f unw = 60 MHzX mod105dB μV 6Document Number 85178 Rev. 1.2, 05-Sep-08TSDF52830YSVishay SemiconductorsPackage Dimensions in mm (Inches)TSDF52830YSDocument Number 85178Rev. 1.2, 05-Sep-08Vishay Semiconductors7Ozone Depleting Substances Policy StatementIt is the policy of V ishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. V arious national and international initiatives are pressing for an earlier ban on these substances.V ishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively.2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA.3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.V ishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.W e reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use V ishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify V ishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personaldamage, injury or death associated with such unintended or unauthorized use.V ishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyDocument Number: 91000Revision: 18-Jul-081DisclaimerLegal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

K9F2G08U0M中文资料

2

元器件交易网

K9F2G08Q0M K9F2G16Q0M K9F2G08U0M K9F2G16U0M

Preliminary FLASH MEMORY

256M x 8 Bit / 128M x 16 Bit NAND Flash Memory

PRODUCT LIST

Part Number K9F2G08Q0M-Y,P K9F2G16Q0M-Y,P K9F2G08U0M-Y,P K9F2G16U0M-Y,P 2.7 ~ 3.6V Vcc Range 1.70 ~ 1.95V Organization X8 X16 X8 X16 TSOP1 PKG Type

FEATURES

• Voltage Supply -1.8V device(K9F2GXXQ0M): 1.70V~1.95V -3.3V device(K9F2GXXU0M): 2.7 V ~3.6 V • Organization - Memory Cell Array -X8 device(K9F2G08X0M) : (256M + 8,192K)bit x 8bit -X16 device(K9F2G16X0M) : (128M + 4,096K)bit x 16bit - Data Register -X8 device(K9F2G08X0M): (2K + 64)bit x8bit -X16 device(K9F2G16X0M): (1K + 32)bit x16bit - Cache Register -X8 device(K9F2G08X0M) : (2K + 64)bit x8bit -X16 device(K9F2G16X0M) : (1K + 32)bit x16bit • Automatic Program and Erase - Page Program -X8 device(K9F2G08X0M) : (2K + 64)Byte -X16 device(K9F2G16X0M) : (1K + 32)Word - Block Erase -X8 device(K9F2G08X0M) : (128K + 4K)Byte -X16 device(K9F2G16X0M) : (64K + 2K)Word • Page Read Operation - Page Size - X8 device(K9F2G08X0M) : 2K-Byte - X16 device(K9F2G16X0M) : 1K-Word - Random Read : 25µs(Max.) - Serial Access : 50ns(Min.) 30ns(Min., K9F2G08U0M only) • Fast Write Cycle Time - Page Program time : 300µs(Typ.) - Block Erase Time : 2ms(Typ.) • Command/Address/Data Multiplexed I/O Port • Hardware Data Protection - Program/Erase Lockout During Power Transitions • Reliable CMOS Floating-Gate Technology - Endurance : 100K Program/Erase Cycles - Data Retention : 10 Years • Command Register Operation • Cache Program Operation for High Performance Program • Power-On Auto-Read Operation • Intelligent Copy-Back Operation • Unique ID for Copyright Protection • Package : - K9F2GXXX0M-YCB0/YIB0 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9F2GXXX0M-PCB0/PIB0 : Pb-FREE PACKAGE 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

28C16中文资料

M28C1616K (2K x 8)PARALLEL EEPROM with SOFTWARE DATA PROTECTIONNOT FOR NEW DESIGNNovember 19971/18This is information on a product still in production but not recommended for new design.AI01518B11A0-A10W DQ0-DQ7V CCM28C16GE V SS8RB *Figure 1.Logic DiagramA0-A10Address Input DQ0-DQ7Data Input /Output W Write Enable E Chip Enable G Output Enable RB Ready /Busy V CC Supply Voltage V SSGroundTable 1.Signal NamesFAST ACCESS TIME:90nsSINGLE 5V ±10%SUPPLY VOLTAGE LOW POWER CONSUMPTION FAST WRITE CYCLE:–64Bytes Page Write Operation–Byte or Page Write Cycle:3ms MaxENHANCED END OF WRITE DETECTION:–Data Polling –Toggle BitPAGE LOAD TIMER STATUS BITHIGH RELIABILITY SINGLE POLYSILICON,CMOS TECHNOLOGY:–Endurance >100,000Erase/Write Cycles –Data Retention >40YearsJEDEC APPROVED BYTEWIDE PIN OUT SOFTWARE DATA PROTECTION M28C16is replaced by the products described on the document M28C16A DESCRIPTIONThe M28C16is a 2K x 8low power Parallel EEPROM fabricatedwith SGS-THOMSON proprie-tary single polysilicon CMOS technology.The de-vice offers fast access time with low power dissipation and requires a 5V power supply.The circuit has been designed to offer a flexible micro-controller interface featuring both hardware and software handshakingwith Data Polling and Toggle Bit.The M28C16supports 64byte page write op-eration.A Software Data Protection (SDP)is also possible using the standard JEDEC algorithm.241PDIP24(P)PLCC32(K)TSOP28(N)8x13.4mm241SO24(MS)300mils Note:*RB function is offered only with TSOP28package.A1A0DQ0A7A4A3A2A6A5A10A8A9DQ7W G E DQ5DQ1DQ2DQ3V SSDQ4DQ6V CCAI01485M28C16812345679101112131416152423222120191817Figure 2A.DIP Pin ConnectionsAI01486CN CA8A10D Q 417A0NC DQ0D Q 1D Q 2D U D Q 3A6A3A2A1A5A49W A91N C NC DQ6A 7DQ732D U V C C M28C16N C NC D Q 5G E 25V S S Figure 2B.LCC Pin ConnectionsWarning:NC =Not Connected,DU =Don’t UseDQ0DQ1A3A0A2A1A10E DQ7G DQ5V CC DQ4A9W A4A7AI01519M28C16823456791011122221201918171615DQ2V SSA6A5DQ62423DQ31A81615Figure 2C.SO Pin Connections A1A0DQ0A5A2A4A3A9NC DQ7A8G E DQ5DQ1DQ2DQ3DQ4DQ6NC W NC A6RB V CC A7AI01175CM28C162812278141521V SS A10Figure 2D.TSOP Pin ConnectionsWarning:NC =Not Connected.2/18M28C16Symbol Parameter Value Unit T A Ambient Operating Temperature–40to125°C T STG Storage Temperature Range–65to150°C V CC Supply Voltage–0.3to6.5V V IO Input/Output Voltage–0.3to V CC+0.6V V I Input Voltage–0.3to6.5V V ESD Electrostatic Discharge Voltage(Human Body model)(2)4000V Notes:1.Except for the rating”Operating Temperature Range”,stresses above those listed in the T able”Absolute Maximum Ratings”may cause permanent damage to the device.These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied.Exposure to Absolute Maximum Ratingconditions for extended periods may affect device reliability.Refer also to the SGS-THOMSON SURE Program and otherrelevant quality documents.2.100pF through1500Ω;MIL-STD-883C,3015.7Table2.Absolute Maximum Ratings(1)PIN DESCRIPTIONAddresses(A0-A10).The address inputs select an8-bit memory location during a read or write operation.Chip Enable(E).The chip enable input must be low to enable all read/write operations.When Chip Enable is high,power consumption is reduced. Output Enable(G).The Output Enable input con-trols the data output buffers and is used to initiate read operations.Data In/Out(DQ0-DQ7).Data is written to or read from the M28C16through the I/O pins.Write Enable(W).The Write Enable input controls the writing of data to the M28C16.Ready/Busy(RB).Ready/Busy is an open drain output that can be used to detect the end of the internal write cycle.It is offered only with the TSOP28package.The readershould refer to the M28C17datasheet for more information about the Ready/Busy func-tion.OPERATIONIn order to prevent data corruption and inadvertent write operations an internal V CC comparator inhib-its Write operation if V CC is below V WI(see Table 7).Access to the memory in write mode is allowed after a power-up as specified in Table7.ReadThe M28C16is accessed like a static RAM.When E and G are low with W high,the data addressed is presented on the I/O pins.The I/O pins are high impedance when either G or E is high.WriteWrite operations are initiated when both W and E are low and G is high.The M28C16supports both E and W controlled write cycles.The Address is latched by the falling edge of E or W which ever occurs last and the Data on the rising edge of E or W which ever occurs first.Once initiated the write operation is internally timed until completion.Mode E G W DQ0-DQ7 Standby1X X Hi-ZOutput Disable X1X Hi-ZWrite Disable X X1Hi-ZRead001Data OutWrite010Data InChip Erase0V0Hi-ZNote: 1.0=V IL;1=V IH;X=V IL or V IH;V=12±5%.Table3.Operating Modes(1)3/18M28C16Page WritePage write allows up to 64bytes to be consecu-tively latched into the memory prior to initiating a programming cycle.All bytes must be located in a single page address,that is A6-A10must be the same for all bytes.The page write can be initiated during any byte write operation.Following the first byte write instruction the host may send another address and data with a mini-mum data transfer rate of 1/t WHWH (see Figure 13).If a transition of E or W is not detected within t WHWH ,the internal programming cycle will start.Chip EraseThe contents of the entire memory may be erased to FFh by use of the Chip Erase command by setting Chip Enable (E)Low and Output Enable (G)to V CC +7V.The chip is cleared when a 10ms low pulse is applied to the Write Enable pin.Microcontroller Control InterfaceThe M28C16provides two write operation status bits andone status pin that can be used to minimize the system write cycle.These signals are available on the I/O port bits DQ7or DQ6of the memory during programming cycle only.Data Polling bit (DQ7).During the internal write cycle,any attempt to read the last byte written will produce on DQ7the complementary value of the previously latched bit.Once the write cycle is fin-ished the true logic value appears on DQ7in the read cycle.Toggle bit (DQ6).The M28C16offers another way for determining when the internal write cycle is completed.During the internal Erase/Write cycle,DQ6will toggle from ”0”to ”1”and ”1”to ”0”(the first read value is ”0”)on subsequent attempts to read the memory.When the internal cycle is com-pleted the toggling will stop and the device will be accessible for a new Read or Write operation.Page Load Timer Status bit (DQ5).In the Page Write mode data may be latched by E or W.Up to 64bytes may be input.The Data output (DQ5)indicates the status of the internal Page Load Timer.DQ5may be read by asserting Output En-able Low (t PLTS ).DQ5Low indicates the timer is running,High indicates time-out after which the write cycle will start and no new data may be input.DQ7DQ6DQ5DQ4DQ3DQ2DQ1DQ0DPTBPLTS Hi-ZHi-ZHi-ZHi-ZHi-ZFigure 4.Status Bit AssignmentDP =Data Polling TB =Toggle BitPLTS =Page Load Timer StatusAI01520ADDRESS LATCHA6-A10(Page Address)X D E C O D ECONTROL LOGIC64K ARRAYADDRESS LATCHA0-A5Y DECODE V PP GENRESET SENSE AND DATA LATCHI/O BUFFERSEGWPAGE LOAD TIMER STATUS TOGGLE BIT DATA POLLINGDQ0-DQ7Figure 3.Block Diagram4/18M28C16Software Data ProtectionThe M28C16offers a software controlled write protection facility that allows the user to inhibit all write modes to the device including the Chip Erase instruction.This can be useful in protecting the memory from inadvertent write cycles that may occur due to uncontrolled bus conditions.The M28C16is shipped as standard in the ”unpro-tected”state meaning that the memory contents can be changed as required by the user.After the Software Data Protection enable algorithm is is-sued,the device enters the ”Protect Mode”of operation where no further write commands have any effect on the memory contents.The device remains in this mode until a valid Software Data Protection (SDP)disable sequence is received whereby the device reverts to its ”unprotected”state.The Software Data Protection is fully non-volatile and is not changed by power on/off se-quences.To enable the Software Data Protection (SDP)the device requires the user to write (with a Page Write)three specific data bytes to three specific memory locations as per Figure 5.Similarly to disable the Software Data Protection the user has to write specific data bytes into six differentlocations asper Figure 6(with a Page Write).This complex series ensures that the user will never enable or disable the Software Data Protection accidentally .AI01509BWRITE AAh in Address 555hWRITE 55h in Address 2AAh WRITE A0h in Address 555h SDP is setWRITE AAh in Address 555h WRITE 55h in Address 2AAh WRITE A0h in Address 555hWrite Page (1up to 64bytes)WRITE IN MEMORY WHEN SDP IS SETSDP ENABLE ALGORITHMPage Write Instruction (Note 1)Page Write Instruction (Note 1)WRITE is enabledFigure 5.Software Data Protection Enable Algorithm and Memory WriteAI01510WRITE AAh in Address 555h WRITE 55h in Address 2AAh WRITE 80h in Address 555h Unprotected StateWRITE AAh in Address 555h WRITE 55h in Address 2AAh WRITE 20h in Address 555h Page Write InstructionFigure 6.Software Data Protection Disable AlgorithmNote:1.MSB Address bits (A6to A10)differ during these specific Page Write operations.5/18M28C16Symbol ParameterTest ConditionMinMax Unit C IN Input Capacitance V IN =0V 6pF C OUTOutput CapacitanceV OUT =0V12pFNote: 1.Sampled only,not 100%tested.Table 5.Capacitance (1)(T A =25°C,f =1MHz )Symbol ParameterTest Condition Min Max Unit I LI Input Leakage Current 0V ≤V IN ≤V CC 10µA I LO Output Leakage Current 0V ≤V IN ≤V CC10µA I CC (1)Supply Current (TTL inputs)E =V IL ,G =V IL ,f =5MHz 30mA Supply Current (CMOS inputs)E =V IL ,G =V IL ,f =5MHz25mA I CC1(1)Supply Current (Standby)TTL E =V IH 1mA I CC2(1)Supply Current (Standby)CMOS E >V CC –0.3V100µA V IL Input Low Voltage –0.30.8V V IH Input High Voltage 2V CC +0.5V V OL Output Low Voltage I OL =2.1mA 0.4V V OHOutput High VoltageI OH =–400µA2.4VNote: 1.All I/O’s open circuit.Table 6.Read Mode DC Characteristics (T A =0to 70°C or –40to 85°C;V CC =4.5V to 5.5V)Symbol ParameterMin MaxUnit t PUR Time Delay to Read Operation1µs t PUW Time Delay to Write Operation (once V CC ≥ 4.5V )10ms V WIWrite Inhibit Threshold3.04.2VNote: 1.Sampled only,not 100%tested.Table 7.Power Up Timing (1)(T A =0to 70°C or –40to 85°C;V CC = 4.5V to 5.5V)Input Rise and Fall Times ≤20ns Input Pulse Voltages0.4V to 2.4V Input and Output Timing Ref.Voltages0.8V to 2.0VNote that Output Hi-Z is defined as the point where data is no longer driven.Table 4.AC Measurement ConditionsAI008262.4V0.4V2.0V 0.8VFigure 7.AC Testing Input Output WaveformsAI011291.3VOUTC L =30pFC L includes JIG capacitance3.3k Ω1N914DEVICE UNDER TESTFigure 8.AC Testing Equivalent Load Circuit6/18M28C16SymbolAltParameterTest ConditionM28C16Unit-90-120-150minmax minmax minmax t AVQ V t ACC Address Valid to Output Valid E =V IL ,G =V IL 90120150ns t ELQV t CE Chip Enable Low to Output Valid G =V IL 90120150ns t GLQV t OE Output Enable Low to Output Valid E =V IL 404550ns t EHQZ(1)t DF Chip Enable High to Output Hi-Z G =V IL 040045050ns t GHQZ (1)t DF Output Enable High to Output Hi-Z E =V IL 040045050ns t AXQXt OHAddress Transition to Output TransitionE =V IL ,G =V IL00ns Note:1.Output Hi-Z is defined as the point at which data is no longer driven.Table 8.Read Mode AC Characteristics(T A =0to 70°C or –40to 85°C;V CC =4.5V to 5.5V)AI01511BVALIDtAVQVtAXQXtGLQVtEHQZtGHQZDATA OUTA0-A10EGDQ0-DQ7tELQVHi-ZFigure 9.Read Mode AC WaveformsNote:Write Enable (W)=High7/18M28C16Symbol Alt ParameterTest Condition Min MaxUnit t AVW L t AS Address Valid to Write Enable Low E =V IL ,G =V IH 0ns t AVEL t AS Address Valid to Chip Enable Low G =V IH ,W =V IL0ns t ELWL t CES Chip Enable Low to Write Enable Low G =V IH 0ns t GHWL t OES Output Enable High to Write Enable LowE =V IL 0ns t GHEL t OES Output Enable High to Chip Enable Low W =V IL 0ns t WLEL t WES Write Enable Low to Chip Enable Low G =V IH0ns t WLAX t AH Write Enable Low to Address Transition 50ns t ELAX t AH Chip Enable Low to Address Transition 50ns t WLDV t DV Write Enable Low to Input Valid E =V IL ,G =V IH 1µs t ELDV t DV Chip Enable Low to Input Valid G =V IH ,W =V IL1µs t ELEH t WP Chip Enable Low to Chip Enable High 50ns t WHEH t CEH Write Enable High to Chip Enable High 0ns t WHGL t OEH Write Enable High to Output Enable Low0ns t EHGL t OEH Chip Enable High to Output Enable Low 0ns t EHWH t WEH Chip Enable High to Write Enable High 0ns t WHDX t DH Write Enable High to Input Transition 0ns t EHDX t DH Chip Enable High to Input Transition 0ns t WHWL t WPH Write Enable High to Write Enable Low 50ns t WLWH1t WP Write Enable Low to Write Enable High 50ns t WHWH t BLC Byte Load Repeat Cycle Time 0.15100µs t WHRH t WC Write Cycle Time3ms t DVWH t DS Data Valid before Write Enable High 50ns t DVEHt DSData Valid before Chip Enable High50nsTable 9.Write Mode AC Characteristics(T A =0to 70°C or –40to 85°C;V CC =4.5V to 5.5V)8/18M28C16AI01207VALIDtAVWLA0-A10EGDQ0-DQ7DATA INWtWLAXtELWLtGHWLtWLDVtWHEHtWHGLtWLWH1tWHWLtWHDXtDVWHFigure 10.Write Mode AC Waveforms -Write Enable ControlledAI01522VALIDtAVELA0-A10EGDQ0-DQ7DATA IN WtELAXtGHELtWLELtELDVtEHGLtEHDXtDVEHtELEHtEHWHFigure 11.Write Mode AC Waveforms -Chip Enable Controlled9/18M28C16AI01523A0-A10EGDQ0-DQ7WtWHWH Addr 0DQ5Addr 1Addr 2Addr ntWHWH tWHRHtWLWHtWHWLtPLTSByte 0Byte 1Byte 2Byte nByte nFigure 12.Page Write Mode AC Waveforms -Write Enable ControlledAI01515A0-A5EGDQ0-DQ7WtWLWHtDVWHByte 0tWHWL A6-A10tWLAXtWHWHtWHDXtAVEL555h2AAh 555h Byte 62Byte 63AAh55hA0hByte AddressPage AddressFigure 13.Software Protected Write Cycle WaveformsNote:A6through A10must specify the same page address during each high to low transition of W (or E)after the software code has been entered.G must be high only when W and E are both low.10/18M28C16AI01516A0-A10EGDQ7WDQ7DQ7DQ7DQ7DQ7READYLAST WRITE INTERNAL WRITE SEQUENCE Address of the last byte of the Page Write instructionFigure 14.Data Polling Waveform SequenceAI01517A0-A10EGDQ6WREADYLAST WRITEINTERNAL WRITE SEQUENCE(1)TOGGLEFigure 15.Toggle Bit Waveform SequenceNote:1.First Toggle bit is forced to ’0’11/18AI01484BEGWtWLWH2tELWLtGLWHtWHRHtWHEHFigure 16.Chip Erase WavformsSymbol ParameterTest Condition Min MaxUnit t ELWL Chip Enable Low to Write Enable Low G =V CC +7V 1µs t WHEH Write Enable High to Chip Enable High G =V CC +7V 0ns t WLWH2Write Enable Low to Write Enable High G =V CC +7V 10ms t GLWH Output Enable Low to Write Enable High G =V CC +7V 1µs t WHRHWrite Enable High to Write Enable LowG =V CC +7V3msTable 10.Chip Erase AC Characteristics(T A =0to 70°C or –40to 85°C;V CC =4.5V to 5.5V)12/18ORDERING INFORMATION SCHEMENotes:1.The M28C16in TSOP28package has a Ready/Busy output on pin 1.2.Packages available on request only.Devices are shipped from the factory with the memory content set at all ”1’s”(FFh).For a list of available options (Package,etc...)or for further information on any aspect of this device,please contact the SGS-THOMSON Sales Office nearest to you.Speed-9090ns -120120ns -150150nsPackage P(2)PDIP28KPLCC32MS (2)SO28300mils N (1)TSOP288x 13.4mmTemperature Range 10to 70°C 6–40to 85°COption TTape &Reel PackingExample:M28C16-90K1T13/18PDIPA2A1A LB1B e1D SE1EN1CαeASymbmm inches TypMin Max TypMin Max A 3.94 5.080.1550.200A10.38 1.780.0150.070A2 3.56 4.060.1400.160B 0.380.560.0150.021B1 1.14 1.780.0450.070C 0.200.300.0080.012D 32.261.270E 14.8016.260.5830.640E112.5013.970.4920.550e1 2.54––0.100––eA 15.2017.780.5980.700L 3.05 3.820.1200.150S 1.02 2.290.0400.090α0°15°0°15°N2424PDIP24Drawing is not to scale.PDIP24-24pin Plastic DIP,600mils width14/18PLCCD NeE1E 1ND1NdCPBD2/E2eB1A1AjSymbmm inches TypMin Max TypMin Max A 2.54 3.560.1000.140A1 1.52 2.410.0600.095B 0.330.530.0130.021B10.660.810.0260.032D 12.3212.570.4850.495D111.3511.560.4470.455D29.9110.920.3900.430E 14.8615.110.5850.595E113.8914.100.5470.555E212.4513.460.4900.530e 1.27––0.050––j 0.89––0.035––N 3232Nd 77Ne 99CP0.100.004PLCC32Drawing is not to scale.PLCC32-32lead Plastic Leaded Chip Carrier,rectangular15/18SO-bENCPBe A2DCLA1α1HASymbmm inches TypMin Max TypMin Max A 2.46 2.640.0970.104A10.130.290.0050.011A2 2.29 2.390.0900.094B 0.350.480.0140.019C 0.230.320.0090.013D 15.2015.600.5980.614E 7.427.590.2920.299e 1.27––0.050––H 10.1610.410.4000.410L 0.61 1.020.0240.040α0°8°0°8°N 2424CP0.100.004SO24Drawing is not to scale.SO24-24lead Plastic Small Outline,300mils body width16/18TSOP-cD1E78CPBeA2A22DDIECLA1α21281Symbmm inches TypMinMax TypMinMax A 1.250.049A10.200.008A20.95 1.150.0370.045B 0.170.270.0070.011C 0.100.210.0040.008D 13.2013.600.5200.535D111.7011.900.4610.469E 7.908.100.3110.319e 0.55––0.022––L 0.500.700.0200.028α0°5°0°5°N 2828CP0.100.004TSOP28Drawing is not to scale.TSOP28-28lead Plastic Small Outline,8x 13.4mm17/18Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorize d for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.©1997SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A.18/18。

AT28BV256-20中文资料

Features•Single 2.7V - 3.6V Supply•Fast Read Access Time – 200 ns •Automatic Page Write Operation –Internal Address and Data Latches for 64 Bytes –Internal Control Timer •Fast Write Cycle Times–Page Write Cycle Time: 10 ms Maximum –1- to 64-byte Page Write Operation •Low Power Dissipation –15 mA Active Current–20 µA CMOS Standby Current•Hardware and Software Data Protection •DATA Polling for End of Write Detection •High Reliability CMOS Technology –Endurance: 10,000 Cycles –Data Retention: 10 Years•JEDEC Approved Byte-wide Pinout•Commercial and Industrial Temperature RangesDescriptionThe A T28BV256 is a high-performance Electrically Erasable and Programmable Read Only Memory. Its 256K of memory is organized as 32,768 words by 8 bits. Manufac-tured with Atmel’s advanced nonvolatile CMOS technology, the device offers access times to 200 ns with power dissipation of just 54 mW. When the device is deselected, the CMOS standby current is less than 200 µA.PLCC – Top ViewPin ConfigurationsPin Name Function A0 - A14Addresses CE Chip Enable OE Output Enable WE Write Enable I/O0 - I/O7Data Inputs/Outputs NC No Connect DCDon’t ConnectPDIP , SOIC – Top ViewNote:1.Note: PLCC package pins 1 and 17are DON’T CONNECT.TSOP – Top View2AT28BV2560273H–PEEPR–10/04The AT28BV256 is accessed like a Static RAM for the read or write cycle without the need for external components. The device contains a 64-byte page register to allow writing of up to 64 bytes simultaneously. During a write cycle, the addresses and 1 to 64 bytes of data are inter-nally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the device will automatically write the latched data using an internal control write cycle has been detected a new access for a read or w rite c an begin.Atmel’s AT28BV256 has additional features to ensure high quality and manufacturability. The device utilizes internal error correction for extended endurance and improved data retention characteristics. An optional software data protection mechanism is available to guard against inadvertent writes. The device also includes an extra 64 bytes of EEPROM for device identifi-cation or tracking.Block DiagramAbsolute Maximum Ratings*Temperature under Bias ................................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityStorage Temperature.....................................-65°C to +150°C All Input Voltages (including NC Pins)with Respect to Ground...................................-0.6V to +6.25V All Output Voltageswith Respect to Ground.............................-0.6V to V CC + 0.6V Voltage on OE and A9with Respect to Ground...................................-0.6V to +13.5V3AT28BV2560273H–PEEPR–10/04Device OperationREAD:high, the data stored at the memory location determined by the address pins is asserted on This dual-line control gives designers flexibility in preventing bus contention in their system.BYTE WRITE:been started, it will automatically time itself to completion. Once a programming operation has been initiated and for the duration of t WC , a read operation will effectively be a polling operation.PAGE WRITE: The page write operation of the AT28BV256 allows 1 to 64 bytes of data to be written into the device during a single internal programming period. A page write operation is initiated in the same manner as a byte write; the first byte written can then be followed by 1 to 63 additional bytes. Each successive byte must be written within 150 µs (t BLC ) of the previous byte. If the t BLC limit is exceeded the AT28BV256 will cease accepting data and commence the internal programming operation. All bytes during a page write operation must reside on the during the page write operation, A6 - A14 must be the same.The A0 to A5 inputs are used to specify which bytes within the page are to be written. The bytes may be loaded in any order and may be altered within the same load period. Only bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not occur.During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data to be presented on I/O7. Once the write cycle has been com-begin at anytime during the write cycle.TOGGLE BIT:determining the end of a write cycle. During the write operation, successive attempts to read data from the device will result in I/O6 toggling between one and zero. Once the write has completed, I/O6 will stop toggling and valid data will be read. Reading the toggle bit may begin at any time during the write cycle.DATA PROTECTION: If precautions are not taken, inadvertent writes may occur during transi-tions of the host system power supply. Atmel has incorporated both hardware and software features that will protect the memory against inadvertent writes.HARDWARE PROTECTION: Hardware features protect against inadvertent writes to the AT28BV256 in the following ways: (a) V CC power-on delay – once V CC has reached 1.8V (typ-ical) the device will automatically time out 10 ms (typical) before allowing a write; (b) write SOFTWARE DATA PROTECTION: A software-controlled data protection feature has been implemented on the AT28BV256. Software data protection (SDP) helps prevent inadvertent writes from corrupting the data in the device. SDP can prevent inadvertent writes during power-up and power-down as well as any other potential periods of system instability.The AT28BV256 can only be written using the software data protection feature. A series of three write commands to specific addresses with specific data must be presented to the device before writing in the byte or page mode. The same three write commands must begin each write operation. All software write commands must obey the page mode write timing4AT28BV2560273H–PEEPR–10/04specifications. The data in the 3-byte command sequence is not written to the device; the address in the command sequence can be utilized just like any other location in the device.Any attempt to write to the device without the 3-byte sequence will start the internal write tim-ers. No data will be written to the device; however, for the duration of t WC , read operations will effectively be polling operations.DEVICE IDENTIFICATION: An extra 64 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12V ± 0.5V and using address locations 7FC0H to 7FFFH the additional bytes may be written to or read from in the same manner as the regular memory array.Notes:1.X can be V IL or V IH .2.Refer to AC programming waveforms.3.V H = 12.0V ± 0.5V .DC and AC Operating RangeAT28BV256-20AT28BV256-25Operating Temperature (Case)Com.0°C - 70°C 0°C - 70°C Ind.-40°C - 85°C -40°C - 85°C V CC Power Supply2.7V -3.6V2.7V -3.6VOperating ModesMode CE OE WE I/O Read V IL V IL V IH D OUT Write (2)V IL V IH V IL D IN Standby/Write Inhibit V IH X (1)X High ZWrite Inhibit X X V IH Write Inhibit X V IL X Output Disable X V IH X High Z Chip Erase V ILV H (3)V ILHigh Z DC CharacteristicsSymbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0V to V CC + 1V 10µA I LO Output Leakage Current V I/O = 0V to V CC10µA I SB V CC Standby Current CMOS CE = V CC - 0.3V to V CC + 1V Com.20µA Ind.50µA I CC V CC Active Current f = 5 MHz; I OUT = 0 mA15mA V IL Input Low Voltage 0.6V V IH Input High Voltage 2.0V V OL Output Low Voltage I OL = 1.6 mA 0.3V V OHOutput High VoltageI OH = -100 µA2.0V5AT28BV2560273H–PEEPR–10/04AC Read Waveforms (1)(2)(3)(4)Notes:1.ACC - t CE after the address transition without impact on t ACC .2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE or by t ACC - t OE after an address changewithout impact on t ACC .3.t DF is specified from OE or CE whichever occurs first (C L = 5 pF).4.This parameter is characterized and is not 100% tested.AC Read CharacteristicsSymbol ParameterAT28BV256-20AT28BV256-25Units MinMax MinMax t ACC Address to Output Delay 200250ns t CE (1)CE to Output Delay 200250ns t OE (2)OE to Output Delay 0800100ns t DF (3)(4)CE or OE to Output Float055060ns t OHOutput Hold from OE, CE or Address, whichever occurred first00ns6AT28BV2560273H–PEEPR–10/04Input Test Waveforms and Measurement LevelOutput Test LoadNote:1.This parameter is characterized and is not 100% tested.R F Pin Capacitancef = 1 MHz, T = 25°C (1)Symbol Typ Max Units Conditions C IN 46pF V IN = 0V C OUT 812pFV OUT = 0V7AT28BV2560273H–PEEPR–10/04Note:1.NR = No Restriction.AC Write WaveformsWE ControlledCE ControlledAC Write CharacteristicsSymbol ParameterMin MaxUnits t AS , t OES Address, OE Set-up Time 0ns t AH Address Hold Time 50ns t CS Chip Select Set-up Time 0ns t CH Chip Select Hold Time 0ns t WP Write Pulse Width (WE or CE)200ns t DS Data Set-up Time 50ns t DH , t OEH Data, OE Hold Time 0nst DV Time to Data Valid NR(1)8AT28BV2560273H–PEEPR–10/04Programming Algorithm (1)(2)(3)Notes:1.Data Format: I/O7 - I/O0 (Hex); Address Format: A14 - A0 (Hex).2.Data protect state will be re-activated at the end of program cycle.3. 1 to 64 bytes of data are loaded.Software Protected Program Cycle Waveforms (1)(2)(3)Notes:1.A0 - A14 must conform to the addressing sequence for the first three bytes as shown above.2.A6 through A14 must specify the same page address during each high to low transition of WE (or CE) after the softwarecode has been entered.3.OE must be high only when WE and CE are both low.Page Mode CharacteristicsSymbol Parameter MinMax Units t WC Write Cycle Time 10ms t AS Address Set-up Time 0ns t AH Address Hold Time 50ns t DS Data Set-up Time 50ns t DH Data Hold Time 0ns t WP Write Pulse Width 200ns t BLC Byte Load Cycle Time 150µs t WPHWrite Pulse Width High100ns9AT28BV2560273H–PEEPR–10/04Notes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 5.Notes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 5.Toggle Bit WaveformsNotes:1.2.Beginning and ending state of I/O6 will vary.3.Any address location may be used but the address should not vary.(1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 0ns t OEH OE Hold Time 0ns t OE OE to Output Delay (2)ns t WR Write Recovery TimensToggle Bit Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 10ns t OEH OE Hold Time 10ns t OE OE to Output Delay (2)ns t OEHP OE High Pulse 150ns t WR Write Recovery Time0ns10AT28BV2560273H–PEEPR–10/0411AT28BV2560273H–PEEPR–10/04Note: 1.See Valid Part Numbers table below.Ordering Information (1)t ACC (ns)I CC (mA)Ordering Code Package Operation Range Active Standby 200150.02A T28BV256-20JC A T28BV256-20PC A T28BV256-20SC A T28BV256-20TC 32J 28P628S 28T Commercial (0° to 70°C)150.02A T28BV256-20JI A T28BV256-20PI A T28BV256-20SI A T28BV256-20TI 32J 28P628S 28T Industrial (-40° to 85°C)150.02A T28BV256-20TU A T28BV256-20JU 32J Green 28T Green Industrial (-40° to 85°C)250150.02A T28BV256-25JC A T28BV256-25PC A T28BV256-20SC A T28BV256-25TC 32J 28P628S 28T Commercial (0° to 70°C)150.02A T28BV256-25JI A T28BV256-25PI A T28BV256-20SI A T28BV256-25TI32J 28P628S 28TIndustrial (-40° to 85°C)Valid Part NumbersThe following table lists standard Atmel products that can be ordered.Device Numbers Speed Package and Temperature Combinations AT28BV25620JC, JI, PC, PI, SC, SI, TC, TI, TU, JU AT28BV25625JC, JI, PC, PI, SC, SI, TC, TIDie ProductsReference Section: Parallel EEPROM Die ProductsPackage Type32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)28P628-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)28T28-lead, Plastic Thin Small Outline Package (TSOP)12AT28BV2560273H–PEEPR–10/04Packaging Information32J – PLCC13AT28BV2560273H–PEEPR–10/0428P6 – PDIP14AT28BV2560273H–PEEPR–10/0428S – SOIC15AT28BV2560273H–PEEPR–10/0428T – TSOP0273H–PEEPR–10/04Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABIL ITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBIL ITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature© Atmel Corporation 2004. All rights reserved. Atmel ®, logo and combinations thereof, are registered trademarks, and Everywhere You Are SM are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

凯尔贝280i等离子中文界面说明

操作序列操作序列1 紧急情况释放开关S3(急停)左旋转2 旋转钥匙开关S1(电源总输入)选‘I’改变选‘PGC’显示消耗-电源电压控制变压器-选PGC显示数据参数,仅在连接气体自动控制时有效3绿色灯S2开(准备好操作)打开开关等离子电源、风扇、冷却控制打开测试:-显示电弧电压(20)和切割电流(19)在不久后-20电弧电压的实际值-19目前设定值预留-绿色开S2准备好操作-(16)黄色LED OFF‘累计错误’- (7)绿色LED ON‘冷却系统正常’- (8)绿色LED ON‘其他供应正常’- (9)绿色LED ON‘电源温度正常’此单元已经准备就绪4 旋转开关S5(切割技术范围)按照制定计划选择的切割参数5 操作PGC3,PGE360 orPGE3-360(见维修手册)预选等离子单元(解除不合格单元),激活等离子易损件、气体等切割参数电位计-电压显示(20)错误错误 原因原因//解决方案解决方案1当S1开关打开总电源,激活S2绿色开关后风扇和冷却液单元无法启动 -S3急停开关未复位-通信线路X102(C3-C4)(系统发出紧急停止)没有堵塞-电源后盖板以及PBA 开-等离子割炬控制电缆未连接上X121 -电机断路器F7冷却装置关闭2风扇和冷却单元ON,(16)黄色LED‘累计错误’ON 和(8)绿色LED‘气体供应’OFF选择气体压力过低 (见切割参数表) 3(16)黄色LED‘累计错误’ON,(7)绿色LED‘冷却回路’OFF,报警信号显示在电位器上(19) -冷却装置水泵旋转方向相反→调换俩相线 -冷却液流量过低 -缺少冷却液 -主开关S1冷却装置关-电机断路器F7冷却装置关闭4(16)黄色LED‘累计错误’ON,(9)绿色LED‘电源温度’OFF -整流器过热→风扇运行冷却、根据维护手册清洗本单元和箱体风扇后过滤垫 5(11)白色LED ‘主弧’OFF:主电源OFF,电流显示器(19)当等离子电源关闭10秒以后 -测试弧时间>10S -工件电流无回路-工件连接电缆无连接-穿孔高度不正确-测试弧与工件未接触该HiFocus 280i 等离子电源显示顺等离子电源显示顺序为错误代码序为错误代码序为错误代码,,如果在运行中或者操作过程中中或者操作过程中,,电流电流显示记显示记显示记显示数字从显示数字从和各自LED等亮等亮,,这些错误的描述见下表这些错误的描述见下表显示信息(19)表示信息 原因1 气体错误 手动气体控制台:(PGE) -气体压力过低-控制气体4 测试弧错误起弧时间>10S工件无电流通过-工件电缆未连接 -初始定位高度不正确 -主弧与工件无接触5 起弧错误 2秒内未起弧6 主弧丢失 主弧未与工件连接7 距离错误 割炬在切割过程中距离过小8 气体测试错误 测试时间大于三分钟9 引导弧丢失 在起弧过程中引导弧未建立,无主弧10 通讯错误 仅在自动气体控制有效11 数据库错误 仅在自动气体控制有效202122252627电源出错 联系服务人员303132 354041424344505152 55。

TMS28F200AXY资料

PIN NOMENCLATURE A0 – A16 A17 BYTE DQ0 – DQ14 DQ15/A –1 E G NC RP VCC VPP VSS W DU/WP Address Inputs Address Input (40-Pin Package Only) Byte-Enable Data In / Out Data In / Out (Word-Wide Mode), Low-Order Address (Byte-Wide Mode) Chip-Enable Output-Enable No Internal Connection Reset / Deep Power-Down Power Supply Power Supply for Program / Erase Ground Write-Enable Do Not Use for AMy or AZy/Write-Protect

44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

RP W A8 A9 A10 A11 A12 A13 A14 A15 A16 BYTE VSS DQ15/A –1 DQ7 DQ14 DQ6 DQ13 DQ5 DQ12 DQ4 VCC

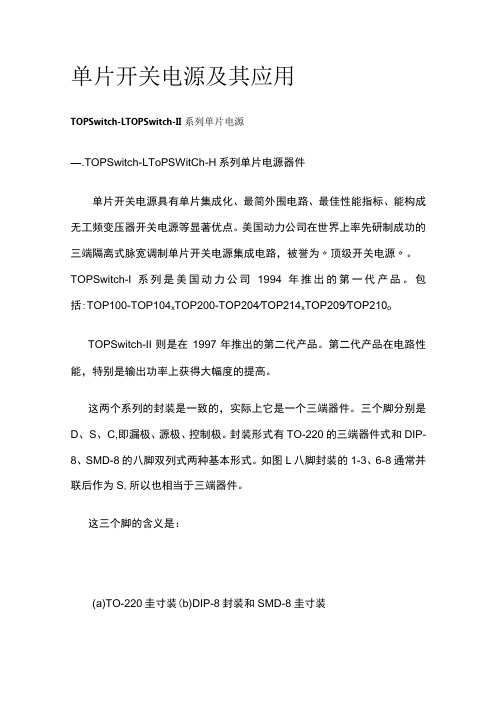

单片开关电源及其应用

单片开关电源及其应用TOPSwitch-LTOPSwitch-II系列单片电源—.TOPSwitch-LToPSWitCh-H系列单片电源器件单片开关电源具有单片集成化、最简外围电路、最佳性能指标、能构成无工频变压器开关电源等显著优点。

美国动力公司在世界上率先研制成功的三端隔离式脉宽调制单片开关电源集成电路,被誉为〃顶级开关电源〃。

TOPSwitch-I系列是美国动力公司1994年推出的第一代产品。

包括:TOP100-TOP104x TOP200-TOP204∕TOP214x TOP209∕TOP210o TOPSwitch-II则是在1997年推出的第二代产品。

第二代产品在电路性能,特别是输出功率上获得大幅度的提高。

这两个系列的封装是一致的,实际上它是一个三端器件。

三个脚分别是D、S、C,即漏极、源极、控制极。

封装形式有TO-220的三端器件式和DIP-8、SMD-8的八脚双列式两种基本形式。

如图L八脚封装的1-3、6-8通常并联后作为S,所以也相当于三端器件。

这三个脚的含义是:(a)TO-220圭寸装(b)DIP-8封装和SMD-8圭寸装图1:TOPSwitch的封装源极S:连接内部MOSFET的源极,同时也是TOP开关及开关电源初级电路的公共接地点及基准点。

漏极D:是内部MOSFET的漏极,也是内部电流的检测点。

该点内部有一电流源提供芯片偏置电流。

控制极C:误差放大电路和反馈电流输入端。

其作用是:1)提供自动重启电容连接点并决定重启频率。

2)通过调节其输入电流,可以调整占空比。

3)为芯片提供正常工作的偏置电流。

4)提供旁路和补偿功能的电容连接点。

下面的介绍中,我们以TOPSWitCh-11为主。

二.ToPSWitCh-11产品的分类及特点(一)、产品分类TOPSwitch-11与第一代产品相比,它不仅在性能上进一步改进,而且输出功率得到显著提高,现已成为国际上开发中、小功率开关电源及电源模块的优选集成电路,其产品分类见表I o表1TOPSwitch-II的产品分类及最大输出功率P0M(单位:W)To—220封装(Y)DIP-8封装(P)/SMD—8封装(G)产品固定输入宽范产品型固定输入宽范型号(110/115/230V,AC,±15%)围输入(85V265V,AC)号(110/115/230V,AC,±15%)围输入(85V265V,AC)T0P2 21Y 127TOP221P 9/221G6T0P2 22Y 2515TOP222P 15/222G10T0P2 23Y 5030TOP223P 25/223G15T0P2 24Y 7545TOP224P 30/224G20T0P225Y10060T0P226Y12575T0P227Y15090(二)、性能特点1 .将脉宽调制(PWM)控制系统的全部功能集成到三端芯片中。

安立台式频谱仪MS2830A资料

5 kHz

10 kHz

310000 (31 s)

10 kHz

25 kHz

610000 (30.5 s)

25 kHz

50 kHz

730000 (14.6 s)

50 kHz

100 kHz

730000 (7.3 s)

100 kHz

200 kHz

730000 (3.65 s)

250 kHz

500 kHz

730000 (1.46 s)

33+

幅度

混频器转换失真

设置幅度: 0 to 99.9 dB

最大输入电平, 平均噪声电平,频率响应: 取决于外部混频器

输入/输出

应用混频器: 两口混频

本振频率: 5 GHz to 10 手 册 l MS2830A-044/045

一般参数

尺寸和重量

电影功率 温度 EMC

MS2830A-006 分析带宽 10 MHz选件

此选件增加分析10MHz宽带信号功能.

MS2830A-005 分析带宽扩展到31.25 MHz

此选件增加分析31.25 MHz 宽带信号功能. (需要安装选件 Opt. 006) MS2830A-005 与 MS2830A-045 不可同时安装.

MS2830A-008 预放

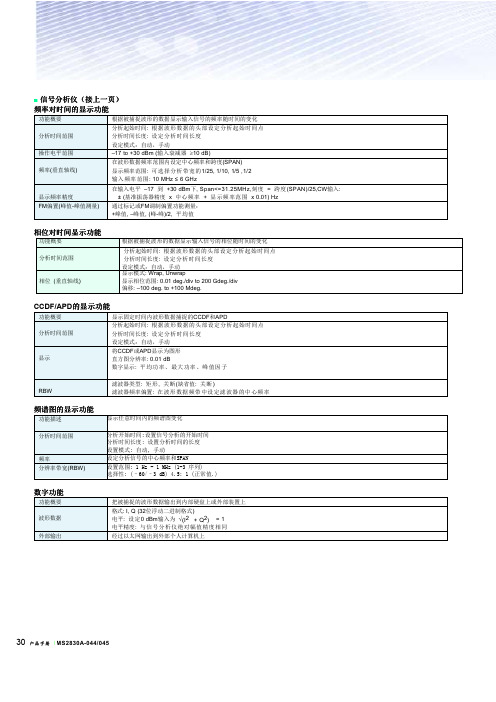

信号分析仪(接上一页)

频率对时间的显示功能

功能概要

根据被捕捉波形的数据显示输入信号的频率随时间的变化

分析时间范围

分析起始时间: 根据波形数据的头部设定分析起始时间点 分析时间长度: 设定分析时间长度 设定模式:自动,手动

操作电平范围

–17 to +30 dBm (输入衰减器 ≥10 dB)

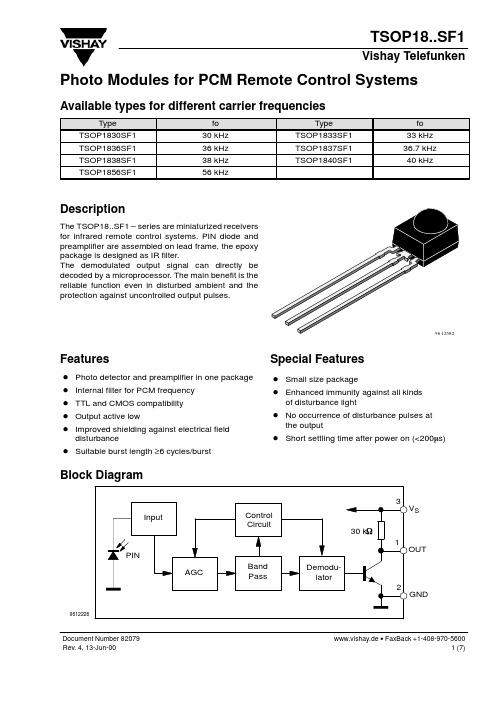

TSOP1838SF1中文资料

D Suitable burst length ≥6 cycles/burst

Block Diagram

3 Input Control Circuit 30 kW 1 PIN AGC Band Pass Demodulator 2

9612226

VS

OUT

GND

Document Number 82079 Rev. 4, 13-Jun-00

Special Features

D Small size package D Enhanced immunity against all kinds

of disturbance light

D No occurrence of disturbance pulses at D Short settling time after power on (<200ms)

Description

The TSOP18..SF1 – series are miniaturized receivers for infrared remote control systems. PIN diode and preamplifier are assembled on lead frame, the epoxy package is designed as IR filter. The demodulated output signal can directly be decoded by a microprocessor. The main benefit is the reliable function even in disturbed ambient and the protection against uncontrolled output pulses.

CM2830中文资料

元器件交易网

元器件交易网

CM2830/CM2830A

300mA CMOS LDO

GENERAL DESCRIPTION

The CM2830/CM2830A family is a positive voltage linear regulator developed utilizing CMOS technology featured low quiescent current (30µA typ.), low dropout voltage, and high output voltage accuracy. Built-in low on-resistance transistor provides low dropout voltage and large output current. A 2.2µF or greater can be used as an output capacitor. The SOT-23-3, SOT-23-5, and TO-92 miniaturized package and the SOT-89 package are recommended for configuring portable devices and large current application, respectively. These robust devices are designed to prevent device failure under the worst operation condition with both Thermal Shutdown and Current Fold-back. ! ! ! ! ! ! ! ! !

博思得q8用户手册

iii

Q8 系列用户手册

传动系统的清洁和机箱内的清洁 .............................................33 探测器的清洁 ...........................................................................33

Q8 系列用户手册

声明

此为 A 级产品,在生活环境中,该产品可能会造成无线电干扰。在 这种情况下,可能需要用户对其干扰采取切实可行的措施。

商标

ARM 是 Advanced RISC Machines Ltd.的注册商标。 Centronics 是 Centronics Data Computer Corporation 的注册商标。 Microsoft, Windows 是 Microsoft Corporation 的注册商标。 POSTEK 是深圳市博思得科技发展有限公司的注册商标。 PS/2 是 International Business Machines Corporation 的注册商标。

i

Q8 系列用户手册

重要安全事项

在没有该产品制造商授权人员指导下,严禁私自拆装这台打印机及 其电源适配器,否则可能会发生触电、打印机的传动机构伤人或损 坏机器零部件的事故。 严禁使用损坏的或破旧的电源线,否则可能会造成触电或引发火灾。 严禁过度弯曲、用力拉扯电源线。不要在电源线上放置重物。当拔 出电源插头时,要抓住插头部分,不能拉扯电源线部分,否则可能 会损伤电源线并引发火灾或触电。 请参考打印机后面和电源适配器上的规格标签, 以确定您所使用的 电源规格是正确的。请使用原配的或经过制造商认可的电源适配器, 否则可能会发生故障甚至损坏打印机的零部件。 这台打印机只适合在室内使用,请勿在室外或潮湿、高温、低温环 境下使用。 不要重压或撞击打印机,以免损坏打印机的零部件或使打印机运转 不正常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Signal Gap Time

0

10

20

30

40

50 time [ms]

60

70

80

90

100

Figure A: Data Signal (Output of IR Receiver) with a Signal Gap Time of 20ms

Siபைடு நூலகம்nal Gap Time

0

2

4

6

8

10 time [ms]

14 500

Features

D D D D D

Photo detector and preamplifier in one package Internal filter for PCM frequency TTL and CMOS compatibility Output active low Improved shielding against electrical field disturbance

the output

D Suitable burst length ≥6 cycles/burst

Block Diagram

2 Input Control Circuit 30 kW 1 PIN AGC Band Pass Demodulator 3 GND OUT VS

14318

Document Number 82078 Rev. 5, 13-Jun-00

Description

The TSOP28..ON1 – series are miniaturized receivers for infrared remote control systems. PIN diode and preamplifier are assembled on lead frame, the epoxy package is designed as IR filter. The demodulated output signal can directly be decoded by a microprocessor. The main benefit is the reliable function even in disturbed ambient and the protection against uncontrolled output pulses.

(Tamb 85 °C) t 10 s, 1 mm from case

x

x

Basic Characteristics

Tamb = 25_C Parameter Supply Current ( y (Pin 2) ) Supply Voltage (Pin 2) Transmission Distance Output Voltage Low (Pin 1) Irradiance (30 – 40 kHz) Test Conditions VS = 5 V, Ev = 0 VS = 5 V, Ev = 40 klx, sunlight Ev = 0, test signal see fig.6, IR diode TSAL6200, IF = 300 mA IOL = 0.5 mA, Ee = 0.7 mW/m2, f = fo Pulse width tolerance: tpi – 4/fo < tpo < tpi + 6/fo, test signal (see fig.6) Pulse width tolerance: tpi – 4/fo < tpo < tpi + 6/fo, test signal see fig.6 Angle of half transmission distance Symbol ISD ISH VS d VOL Ee min 0.3 Min 0.9 4.5 35 250 0.5 Typ 1.2 1.3 Max 1.5 5.5 Unit mA mA V m mV mW/m2

mC

3 GND

14319

*) recommended to suppress power supply disturbances

www.vishay.de • FaxBack +1-408-970-5600 2 (7)

Document Number 82078 Rev. 5, 13-Jun-00

元器件交易网

www.vishay.de • FaxBack +1-408-970-5600 1 (7)

元器件交易网

TSOP28..ON1

Vishay Telefunken Absolute Maximum Ratings

Tamb = 25_C Parameter Supply Voltage Supply Current Output Voltage Output Current Junction Temperature Storage Temperature Range Operating Temperature Range Power Consumption Soldering Temperature Test Conditions (Pin 2) (Pin 2) (Pin 1) (Pin 1) Symbol VS IS VO IO Tj Tstg Tamb Ptot Tsd Value –0.3...6.0 5 –0.3...6.0 5 100 –25...+85 –25...+85 50 260 Unit V mA V mA °C °C °C mW °C

Special Features

D Small size package D Enhanced immunity against all kinds of

disturbance light

D No occurrence of disturbance pulses at D Short settling time after power on (<200ms)

元器件交易网

TSOP28..ON1

Vishay Telefunken Typical Characteristics (Tamb = 25_C unless otherwise specified)

1.0 0.8 E e min – Threshold Irradiance (mW/m2 ) /eE – Rel. Responsitivity 100.0

TSOP28..ON1

Vishay Telefunken Suitable Data Format

The circuit of the TSOP28..ON1 is designed in that way that unexpected output pulses due to noise or disturbance signals are avoided. A bandpassfilter, an integrator stage and an automatic gain control are used to suppress such disturbances. The distinguishing mark between data signal ( not suppressed) and disturbance signal (supressed) are carrier frequency, burst length and Signal Gap Time (see diagram below). The data signal should fullfill the following condition: • Carrier frequency should be close to center frequency of the bandpass (e.g. 38kHz). • Burst length should be 6 cycles/burst or longer. • After each burst a gap time of at least 10 cycles is neccessary. • The data format should not make a continuous signal transmission. There must be a Signal Gap Time (longer than 15ms) at least each 90ms (see Figure A). Some examples for suitable data format are: NEC Code (repetitive pulse), NEC Code (repetitive data), Toshiba Micom Format, Sharp Code, RC5 Code, RECS–80 Code, R–2000 Code. When a disturbance signal is applied to the TSOP28..ON1 it can still receive the data signal. However the sensitivity is reduced to that level that no unexpected pulses will occure. Some examples for such disturbance signals which are suppressed by the TSOP28..ON1 are: • DC light (e.g. from tungsten bulb or sunlight), • Continuous signal at 38kHz or at any other frequency, • Signals from fluorescent lamps (see Figure B). • Continuous IR signal (e.g. 1ms burst, 2ms pause)