adc2xx-en-3

ADC选型经典指南

ADC选型经典指南选择ADC(模数转换器)是设计电子系统中的重要环节,它决定了信号从模拟域到数字域的转换质量。

因此,正确选择适合应用需求和性能要求的ADC至关重要。

对于初学者来说,ADC选型可能会变得复杂和困难,因为市场上有各种不同类型和规格的ADC可供选择。

本篇文章将为您提供一个经典的ADC选型指南,以帮助您了解选择ADC的关键因素,从而更好地满足您的应用需求和性能要求。

1. 分辨率(Resolution):ADC的分辨率是指它可以区分和表示的模拟输入电压范围的细微变化程度。

分辨率通常以位数(bits)表示,例如8位、10位、12位等等。

较高的分辨率可以提供更精确的模拟信号转换,但通常伴随着更高的成本和功耗。

因此,需要根据应用需求和所需精度来选择适当的分辨率。

2. 采样率(Sampling Rate):ADC的采样率是指它可以将模拟信号转换为离散数字样本的速率。

采样率通常以每秒样本数(Samples per Second, SPS)或赫兹(Hz)表示。

采样率的选择应基于所需的信号频率范围和应用频谱。

通常,采样率应至少是输入信号频率的两倍,以避免混叠(aliasing)问题。

3. 噪声(Noise):ADC的噪声是指在信号转换过程中引入的非期望信号成分。

噪声会降低系统的信噪比(Signal-to-Noise Ratio, SNR),从而影响转换的准确性和可靠性。

因此,选择具有较低噪声指标的ADC对于需要高转换精度的应用至关重要。

4. 功耗(Power Consumption):ADC的功耗是指在进行信号转换时消耗的电能。

功耗通常以瓦特(W)或毫瓦(mW)表示。

功耗与采样率和分辨率密切相关,较高的采样率和分辨率通常伴随着较高的功耗。

因此,在选择ADC时需要平衡性能要求和能源限制。

5. 输入电压范围(Input Voltage Range):ADC的输入电压范围是指它可以接受的模拟输入信号的电压范围。

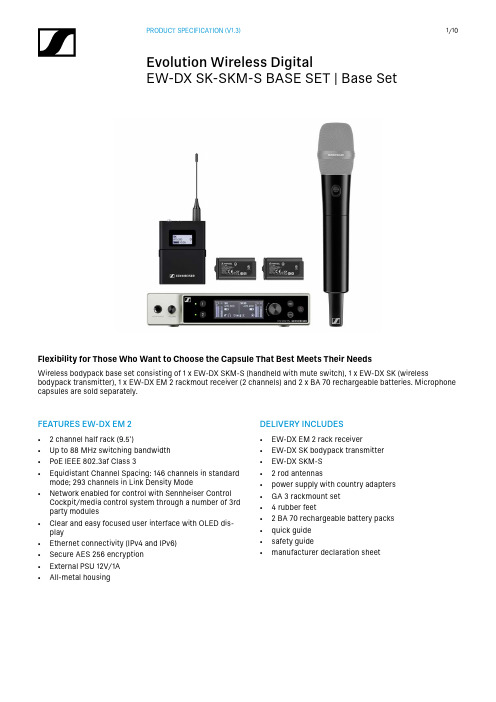

Sennheiser Evolution Wireless Digital EW-DX SK-SKM

DELIVERY INCLUDES• EW-DX EM 2 rack receiver • EW-DX SK bodypack transmitter • EW-DX SKM-S • 2 rod antennas• power supply with country adapters • GA 3 rackmount set • 4 rubber feet• 2 BA 70 rechargeable battery packs • quick guide • safety guide• manufacturer declaration sheetFEATURES EW-DX EM 2• 2 channel half rack (9.5’)• Up to 88 MHz switching bandwidth • PoE IEEE 802.3af Class 3• Equidistant Channel Spacing: 146 channels in standardmode; 293 channels in Link Density Mode • Network enabled for control with Sennheiser ControlCockpit/media control system through a number of 3rd party modules • Clear and easy focused user interface with OLED dis-play • Ethernet connectivity (IPv4 and IPv6)• Secure AES 256 encryption • External PSU 12V/1A •All-metal housingFlexibility for Those Who Want to Choose the Capsule That Best Meets Their NeedsWireless bodypack base set consisting of 1 x EW-DX SKM-S (handheld with mute switch), 1 x EW-DX SK (wirelessbodypack transmitter), 1 x EW-DX EM 2 rackmout receiver (2 channels) and 2 x BA 70 rechargeable batteries. Microphone capsules are sold separately.PRODUCT VARIANTSEW-DX SK-SKM-S BASE SET (Q1-9)470.2 - 550 MHz Art. no. 509462EW-DX SK-SKM-S BASE SET (R1-9)520 - 607.8 MHz Art. no. 509463EW-DX SK-SKM-S BASE SET (S1-10)606.2 - 693.8 MHz Art. no. 509464EW-DX SK-SKM-S BASE SET (S2-10)614.2 - 693.8 MHz Art. no. 509467EW-DX SK-SKM-S BASE SET (S4-10)630 - 693.8 MHzArt. no. 509468EW-DX SK-SKM-S BASE SET (U1/5)823.2 - 831.8 MHz & 863.2 - 864.8 MHz Art. no. 509469EW-DX SK-SKM-S BASE SET (V3-4)925.2 - 937.3 MHzArt. no. 509471EW-DX SK-SKM-S BASE SET (V5-7)941.7 - 951.8 MHz & 953.05 - 956.05 MHz & 956.65 - 959.65 MHz Art. no. 509472EW-DX SK-SKM-S BASE SET (Y1-3)1785.2 - 1799.8 MHzArt. no. 509475FEATURES EW-DX SKM-S• 10mW RF power with up to 100m/328ft working range • Charging contacts for in-device charging with CHG 70N • Persistent eInk display - parameters visible on screeneven when device is not powered on • Programmable mute switch on EW-DX SKM-S - custo-mize the device depending on your professional needs • Function buttons - control all the transmitter settingsdirectly from handheld microphone • Extended runtime with lithium-ion batteries - up to 12hours operation time • Standard capsule interface - compatible with a widerange of Sennheiser and Neumann capsules • Mic input trim control • Metal housingFEATURES EW-DX SK• 3,5 mm jack• 10mW RF power with up to 100m/328ft working range • Charging contacts for in-device charging with CHG 70N • Persistent eInk display - parameters visible on screeneven when device is not powered on • Programmable mute switch - customize the devicedepending on your professional needs • Extended runtime with lithium ion batteries - up to 12hours operation time • Mic input trim control • Metal housingACCESSORIESEW-D ASA (Q-R-S)Active Antenna Splitter470 - 694 MHz Art. no. 508879 EW-D ASA (T-U-V-W)Active Antenna Splitter694 - 1075 MHz Art. no. 508880 EW-D ASA (X-Y)Active Antenna Splitter1350 - 1805 MHz Art. no. 508881 EW-D ASA CN/ANZ (Q-R-S)Active Antenna Splitter470 - 694 MHz Art. no. 508998EW-D AB (Q)Antenna Booster470 - 550 MHz Art. no. 508873 EW-D AB (R)Antenna Booster520 - 608 MHz Art. no. 508874 EW-D AB (S)Antenna Booster606 - 694 MHz Art. no. 508875 EW-D AB (U)Antenna Booster823 - 865 MHz Art. no. 508876 EW-D AB (V)Antenna Booster902 - 960 MHz Art. no. 508877 EW-D AB (Y)Antenna Booster1785 - 1805 MHz Art. no. 508878ADP UHF (470 - 1075 MHz)Passive directional antenna470 - 1075 MHz Art. no. 508863BA 70Rechargeable battery pack for SK and SKM-S Art. no. 508860 L 70 USB Charger for BA 70 rechargeable battery pack Art. no. 508861 EW-D CHARGING SET Set of L 70 USB charger and 2 BA 70 rechargeable battery packs Art. no. 508862 CHG 70N Network-enabled charger for SK, SKM and BA 70Art. no. 509455 CHG 70N + PSU KIT CHG 70N charger with NT 12-35 CS power supply unit Art. no. 509456 EW-D COLOR CODING SET Colored labels for wireless link identification for EM, SKM-S, SK Art. no. 508989 EW-D SK COLOR CODING Colored labels for wireless link identification for SK Art. no. 508990 EW-D SKM COLOR CODING Colored labels for wireless link identification for SKM-S Art. no. 508991 EW-D EM COLOR CODING Colored labels for wireless link identification for EM Art. no. 508992MICROPHONE COMPATIBILITYLavalier and headset microphones compatible with the EW-DX SK bodypack transmitterME 2Omni-directional lavalier microphoneModels produced from 2021 onward, featuring a gold-plated connector*ME 4Cardioid lavalier microphoneModels produced from 2021 onward, featuring a gold-plated connector*MKE Essential Omni Omni-directional lavalier microphoneMKE 2 Gold Omni-directional lavalier microphoneModels produced from 2018 onward, featuring a blue serial number plateMKE 1Omni-directional lavalier microphoneME 3Cardioid headset microphoneModels produced from 2021 onward, featuring a gold-plated connector*HSP Essential Omni Omni-directional headset microphoneHSP 2Omni-directional headset microphoneModels produced from March 2020 onward (featuring code 1090 or later)HS 2Omni-directional headset microphoneModels produced from 2021 onward, featuring a gold-plated connector*SL Headmic 1Omni-directional headset microphone* Models produced prior to 2021 will feature a nickel connector. Earlier models may pick up noise when placed close to the transmitter and are not recommended for useMicrophone modules compatible with the EW-DX SKM-S handheld transmitterMMD 835-1Dynamic microphone module with cardioid polar patternMMD 845-1Dynamic microphone module with supercardioid polar patternMME 865-1Pre-polarized condenser microphone module with supercardioid polar patternMMD 935-1Dynamic microphone module with cardioid polar patternMMD 945-1Dynamic microphone module with supercardioid polar patternMMK 965-1Condenser microphone module with switchable cardioid and supercardioid polar pattern MMD 42-1Dynamic microphone module with omni-directional polar patternNeumann KK 204Condenser microphone module with cardioid polar patternNeumann KK 205Condenser microphone module with supercardioid polar patternMM 435Dynamic microphone module with cardioid polar patternMM 445Dynamic microphone module with supercardioid polar patternME 9002Pre-polarized condenser microphone module with omni-directional polar patternME 9004Pre-polarized condenser microphone module with cardioid polar patternME 9005Pre-polarized condenser microphone module with supercardioid polar patternSPECIFICATIONS SystemAudio link frequency ranges Q1-6R1-6R4-9S1-7S4-7S7-10U1/5V3-4Y1-3470.2 - 526 MHz520 - 576 MHz552 - 607.8 MHz606.2 - 662 MHz630 - 662 MHz662 - 693.8 MHz823.2 - 831.8 MHz &863.2 - 864.8 MHz925.2 - 937.3 MHz1785.2 - 1799.8 MHzBluetooth® Low Energy(BLE) frequency range2402 - 2480 MHzAudio frequency response20 Hz - 20 kHz (-3 dB)@ 3 dBfsAudio THD≤ -60 dB for 1 kHz@ -3 dBfs input level Dynamic range134 dBSystem latency 1.9 msOperating temperature-10 °C - +55 °C(14 °F - 131 °F)Relative humidity 5 - 95 % (non-condensing)EW-DX EM 2 (Rack Receiver)Input voltage11 - 13 V ⎓orPoE IEEE 802.3af Class 0(CAT5e or higher)Input current≤ 1 ATransmit power(radiated)BLE: max. 10 mW EIRP Audio output power18 dBu max.Headphone output2x 70 mW @ 32 ΩEthernet RJ-45 socket, IEEE802.3100Base-TX (half+full duplex)10Base-T (half+full duplex)(CAT5e or higher) Dimensions212 x 44 x 189 mm(8.35" x 1.73" x 7.44") Weight approx. 1000 g (2.2 l bs)(without antennas and powersupply)EW-DX SKM-S (Handheld Transmitter)Input voltage 2.0 - 4.35 VInput current< 300 mAPower supply 2 AA batteries 1.5 V(alkali manganese) orBA 70 rechargeablebattery packOccupied bandwidth200 kHzTransmit power (radiated)Audio link: 10 mW ERP(Range Y1-3: 12 mW ERP)LD mode: 10 mW ERPBLE: max. 10 mW EIRP Dimensions (ø x l)(incl. MMD 835 microphonemodule)(without microphonemodule)50 x 268 mm (1.97" x 10.55")40 x 200 mm (1.57" x 7.87")Weight (without batteries)(incl. MMD 835 microphonemodule)(without microphonemodule)approx. 304 g (0.67 l bs)approx. 195 g (7.14 lbs)EW-DX SK (Bodypack Transmitter)Input voltage 2.0 - 4.35 VInput current< 300 mAPower supply 2 AA batteries 1.5 V(alkali manganese) orBA 70 rechargeablebattery packOccupied bandwidth200 kHzTransmit power (radiated)Audio link: 10 mW ERP(Range Y1-3: 12 mW ERP)LD mode: 10 mW ERPBLE: max. 10 mW EIRP Dimensions (without anten-na)63.5 x 85 x 20 mm(2.5" x 3.35" x 0.79") Weight (without batteries)approx. 115-120 g(0.26-0,27 - l bs)EW-DX EM 2DIMENSIONSDIMENSIONS EW-DX SK5907611785-1800 MHZ 203.8 / 8.02"590758941-960 MHZ 157.8 / 6.21"590757925-938 MHZ157.8 / 6.21"590756823-832 MHZ & 863-865 MHZ166.2 / 6.54"590755630-694 MHZ 195.8 / 7.71"590754614-694 MHZ195.8 / 7.71"590753606-638 MHZ & 650-694 MHZ195.8 / 7.71"590752606-694 MHZ 195.8 / 7.71"590751520-608 MHZ 217.8 / 8.57"470-550 MHZ 231.8 / 9.13"Teile-Nr.Part no.Frequenzbereich Frequency rangeL590750DIMENSIONS 40.31.59Mikrofonmodul MMD835 - nur Beispiel microphon module MMD835 - example only341.34268.510.5750.51.99200.77.9156.56.16EW-DX SKM-SARCHITECT‘S SPECIFICATIONEW-DX EM 2 rack receiverThe stationary two-channel receiver with switching diver-sity technology shall be for use with up to two companion transmitters as part of a digital wireless RF transmission system.The receiver shall operate within the following UHF fre-quency ranges, with a switching bandwidth of up to 88 MHz: 470.2 – 550 MHz, 520 – 607.8 MHz, 606.2 – 693.8 MHz, 614.2 – 693.8 MHz, 630 – 693.8 MHz, 823.2 – 831.8 MHz, 863.2 – 846.8 MHz, 925.2 – 937.3 MHz, 941.7 – 951.8 MHz, 953.05 – 956.05 MHz, 956.65 – 959.65 MHz, 1785.2 – 1799.8 MHz. Different frequency variants shall be available depending on country-specific regulations.The receiver shall feature Bluetooth® Low Energy (BLE) at a frequency range between 2402 and 2480 MHz for remote controlling the devices via a control App for iOS and And-roid.The receiver shall feature an automatic frequency setup function with spectrum scan functionality in order to es-tablish an equidistant frequency grid with 146 channels in standard mode and 293 channels in Link Density Mode. The audio frequency response shall be between 20 Hz and 20 kHz (-3 dB). Audio total harmonic distortion (THD) shall be≤****************************************** shall be 134 dB. System latency shall be 1.9 ms.The receiver shall be menu-driven with an OLED display showing the current frequency, channel number, metering of RF level, metering of AF level, lock status, muting fun-ction, antenna switching diversity, app connection, gain, audio output level, menu and battery status for each of the two associated transmitters. An auto-lock feature shallbe provided to prevent settings from being accidentally altered.The following settings shall be configurable by function buttons and an encoder for each channel in the menu: frequency, channel name, gain, trim, AF output, low cut, AES 256 encryption, test tone, network settings, integrated antenna booster settings, display brightness, device name, auto setup settings for automatic frequency setup.For each of the two channels the receiver shall feature a balanced XLR-3M audio output with a maximum outputof +18 dBu along with an unbalanced 6.3 mm (¼“) audio output with a maximum output of +12 dBu.For secure transmission the receiver shall feature AES 256 encryption.The receiver shall provide a walktest mode for monitoring the RF and AF signal status in the location over time.Two BNC-type input sockets shall be provided for connec-ting the antennas. The receiver shall be usable with active and passive wide range UHF antennas for the entire sup-ported RF spectrum.A headphone output with headphone volume control shall be provided and shall utilize a 6.3 mm stereo jack socket. The receiver shall have an Ethernet port (RJ-45) for remote network-based monitoring and control using the Sennhei-ser Control Cockpit software or the Sennheiser Wireless Systems Manager software.The receiver shall operate on 12 V DC power supplied from the power supply unit or on Power over Ethernet (PoE IEEE 802.af Class 0). Power consumption shall be ≤ 1 A.The receiver shall have a rugged metal housing; dimensi-ons shall be approximately 212 x 44 x 206 mm (8.35“ x 1.73“ x 8.11“). Weight shall be approximately 1000 grams (2.2 lbs) without antennas and power supply. Operating tempera-ture shall range from −10 °C to +50 °C (+14 °F to +122 °F). The receiver shall be the Sennheiser EW-DX EM 2.EW-DX SK bodypack transmitterThe bodypack transmitter shall be for use with a compa-nion receiver as part of a digital wireless RF transmission system.The bodypack transmitter shall operate within the follo-wing UHF frequency ranges, with a switching bandwidth of up to 88 MHz: 470.2 – 550 MHz, 520 – 607.8 MHz, 606.2 – 693.8 MHz, 614.2 – 693.8 MHz, 630 – 693.8 MHz, 823.2 – 831.8 MHz, 863.2 – 846.8 MHz, 925.2 – 937.3 MHz, 941.7 – 951.8 MHz, 953.05 – 956.05 MHz, 956.65 – 959.65 MHz, 1785.2 – 1799.8 MHz. Different frequency variants shall be available depending on country-specific regulations.The audio frequency response shall be between 20 Hz and 20 kHz (-3 dB). Audio total harmonic distortion (THD) shall be≤****************************************** shall be 134 dB. System latency shall be 1.9 ms. Occupied bandwidth shall be 200 kHz. Transmit power (radiated) shall be 10 mW ERP (1785.2 – 1799.8 MHz Range:12 mW ERP).A programmable mute switch shall be provided for muting or unmuting either the audio signal or the radio signal. The mute switch can also be deactivated.The bodypack transmitter shall be menu-driven with a backlit eInk display showing the relevant status informati-on such as frequency, battery status or AES 256 encrypti-on status.All transmitter parameters shall be adjustable with functi-on buttons on the device itself or by Bluetooth Low Energy (BLE) synchronization via the associated receiver. The fun-ction buttons shall be lockable against accidental misuse. Power shall be supplied to the bodypack transmitter by two 1.5 V AA size batteries or by one Sennheiser BA 70 rechargeable battery pack. Operating time shall be typical-ly 12 hours with a battery pack and up to 8 hours with AA batteries.The bodypack transmitter shall feature charging contacts for direct charging of the transmitter with inserted BA 70 battery pack in a Sennheiser CHG 70N network-enabled charger.The bodypack transmitter’s microphone/line input shall utilize a lockable 3.5 mm Jack socket.The bodypack transmitter shall be compatible with micro-phones for every application: Sennheiser lavalier micro-phones ME 2, ME 4, MKE 1, MKE 2 Gold and MKE Essential Omni, Sennheiser headset microphones HS 2, HSP 2, HSP Essential Omni, ME 3 and SL Headmic 1.The bodypack transmitter shall have a rugged metal housing; dimensions shall be approximately 63.5 x 85 x 20 mm (2.5” x 3.35” x 0.79“). Weight without batteries shall be approximately 115 - 120 grams depending on antenna length. Operating temperature shall range from −10 °C to +50 °C (+14 °F to +122 °F).The handheld transmitter shall be the SennheiserEW-DX SK.EW-DX SKM-S handheld transmitterThe handheld transmitter shall be for use with a compa-nion receiver as part of a digital wireless RF transmission system.The handheld transmitter shall operate within the following UHF frequency ranges, with a switching bandwidth of up to 88 MHz: 470.2 – 550 MHz, 520 – 607.8 MHz, 606.2 – 693.8 MHz, 614.2 – 693.8 MHz, 630 – 693.8 MHz, 823.2– 831.8 MHz, 863.2 – 846.8 MHz, 925.2 – 937.3 MHz, 941.7 – 951.8 MHz, 953.05 – 956.05 MHz, 956.65 – 959.65 MHz, 1785.2 – 1799.8 MHz. Different frequency variants shall be available depending on country-specific regulations.The audio frequency response shall be between 20 Hz and 20 kHz (-3 dB). Audio total harmonic distortion (THD) shall be≤****************************************** shall be 134 dB. System latency shall be 1.9 ms. Occupied bandwidth shall be 200 kHz. Transmit power (radiated) shall be 10 mW ERP (1785.2 – 1799.8 MHz Range:12 mW ERP).A programmable mute switch shall be provided for muting or unmuting either the audio signal or the radio signal. The mute switch can also be deactivated.The handheld transmitter shall be menu-driven with a backlit eInk display showing the relevant status informati-on such as frequency, battery status or AES 256 encrypti-on status.All transmitter parameters shall be adjustable with functi-on buttons on the device itself or by Bluetooth Low Energy (BLE) synchronization via the associated receiver. The fun-ction buttons shall be lockable against accidental misuse. Power shall be supplied to the handheld transmitter by two 1.5 V AA size batteries or by one Sennheiser BA 70 rechar-geable battery pack. Operating time shall be typically12 hours with a battery pack and up to 8 hours with AA batteries.The handheld transmitter shall feature charging contacts for direct charging of the transmitter with inserted BA 70 battery pack in a Sennheiser CHG 70N network-enabled charger.The handheld transmitter shall utilize Sennheiser’s stan-dard capsule interface serving Sennheiser microphone modules of the evolution wireless and 2000 series and Digital 6000 and 9000 as well as the Neumann KK 204 / 205 microphone modules.The handheld transmitter shall have a rugged metal housing; dimensions shall be approximately 50 mm (1.97“) in diameter and 268 mm (10.55“) in length including a Sennheiser MMD 835 microphone module. Weight inclu-ding MMD 835 microphone module shall be approximately 304 grams (0.67 lbs). Operating temperature shall range from −10 °C to +50 °C (+14 °F to +122 °F).The handheld transmitter shall be the SennheiserEW-DX SKM-S.Sennheiser electronic GmbH & Co. KG · Am Labor 1 · 30900 Wedemark · Germany · 。

ICP DAS I-7017R 8-ch Voltage and Current Input DAQ

I-7017R - 8-ch Voltage and Current Input DAQ Module - QuickStart (May/2020)ICP DAS USA, Inc. | | 1-310-517-9888 | 24309 Narbonne Ave. Suite 200. Lomita, CA 90717I-7017R8 Channels Voltage & Current InputData Acquisition ModuleQuick Start GuideProduct Website:https:///i_7017_r.html/dcon_utility_pro.htmlIntroductionThe I-7017R is an 8-channel analog input module with an extremely high quality protection mechanism where the overvoltage protection is 240 Vrms. The input type includes both voltage and current. The sampling rate of the I-7017R is adjustable, meaning that either fast mode or normal mode can be selected. The I-7017R also has 4 kV ESD protection as well as 3000 VDC intra-module isolation. The I-7017R-A5 is an 8-channel analog input module that is especially designed for high voltage input, and has an input range of between -50 V ~ +50 V or -150 V ~ +150 V.Packing ListI-7017RPlastic RailCDQuick Start GuideI-7017R - 8-ch Voltage and Current Input DAQ Module - QuickStart (May/2020)ICP DAS USA, Inc. | | 1-310-517-9888 | 24309 Narbonne Ave. Suite 200. Lomita, CA 90717⏹Internal I/O Structure < I-7017R >⏹Pin Assignments < I-7017R, I-7017R >⏹Internal I/O Structure (I-7017R)⏹Modbus Table (M-7017R only)Address Description R/W 10129 ~Over/under range status of channel 0R 10136to 7 for 4 ~ 20mA or 0 ~ 20mA ranges 00129 ~0013630001 ~Analog input value of channel 0 to 7R 3000840001 ~4000840481Firmware version (low word)R 40482Firmware version (high word)R 40483Module name (low word)R 40484Module name (high word)R 40485Module address, valid range: 1 ~ 247R/W 40486Bits 5:0R/WBaud rate, 0x03 ~ 0x0ACode0x030x040x050x06Baud1200240048009600Code0x070x080x090x0ABaud192003840057600115200Bits 7:600: no parity, 1 stop bit01: no parity, 2 stop bit10: even parity, 1 stop bit11: odd parity, 1 stop bit40487Type code R/W Address Description R/W 40488Modbus response delay time in ms,R/W valid range: 0 ~ 3040489Host watchdog timeout value, 0 ~R/W 255, in 0.1s40490Channel enable/disable, 00h ~ FFh R/W 40492Host watchdog timeout count, write 0R/W to clear00257Protocol, 0: DCON, 1: Modbus RTU R/W 00259Filter setting, 0: 60Hz rejection, 1:R/W 50Hz rejection002611: enable, 0: disable host watchdog R/W 00269Modbus data format, 0: hex, 1:R/W engineering00270Host watch dog timeout status, write R/W1 to clear host watch dog timeoutstatus002711: enable, 0: disable fast mode R/W 00273Reset status, 1: first read after R powered on, 0: not the first read afterpowered on⏹DCON ProtocolFunctions Command Response NotesRead module name$AAM!AA(Data)AA: address number Read module firmware version$AAF!AA(Data)Read all analog input data#aa>(data)Read analog input data of each channel (<=16 channel)#aai>(data)i: channel number (Hex) Read analog input data of each channel (>16 channel)#aaii>(data)ii: channel number (Hex) If you want to know the detail DCON protocol, please check it from CD or webCD path: \\napdos\7000\manual\Web: ftp:///pub/cd/8000cd/napdos/7000/manual/I-7017R - 8-ch Voltage and Current Input DAQ Module - QuickStart (May/2020)ICP DAS USA, Inc. | | 1-310-517-9888 | 24309 Narbonne Ave. Suite 200. Lomita, CA 90717I-7017R - 8-ch Voltage and Current Input DAQ Module - QuickStart (May/2020)ICP DAS USA, Inc. | | 1-310-517-9888 | 24309 Narbonne Ave. Suite 200. Lomita, CA 90717⏹Module test and configurationStep 1: INIT switch Operation Step 2: Install & Run DCON Utility 1. Please Install DCON Utility firstYou can find the software in the CD.CD path:<Driver>:\napdos\driver\dcon_utility\Web link:/pub/cd/8000cd/napdos/driver/dcon_utility/ 2. Run DCON utility1. Find out the INIT switch( back of the module),and turn to INIT.2. Reboot the moduleStep 3: Set search configuration & search module Select COM Port Number1. Click “COM Port”2. Assign the communication information and click“OK”Module Default Setting COM Port Refer converter Port Number Baud Rate 9600ProtocolDCON for I-7000Modbus RTU for M-7000Parity Option N,8,13. Click “Search” and select “Start Searching”Software will search the modules from COM Port 4. Click “Search“ and select “stop searching”Manual stop when the modules searchedNote:When no module can be searched, please check the wire and communication informationStep 4: Select Module for testing and configurationDouble click “select module”Step 5: Configuration Settings & Channel SettingsChannel StatusModule SettingsProtocol DCON / ModbusAddress1~255 (0:INIT)Baud rate1200~115200Parity option N,8,1Input range Depends on signalsourcesStep 6: Change to normal mode and keep the settings1.Turn the INIT Switch to Normal.2.Reboot the moduleI-7017R - 8-ch Voltage and Current Input DAQ Module - QuickStart (May/2020)ICP DAS USA, Inc. | | 1-310-517-9888 | 24309 Narbonne Ave. Suite 200. Lomita, CA 90717Trouble ShootingQ1. How to do when forgot module address or baud rate?Please turn to INIT mode, and run DCON Utility to search.The module supports DCON protocol at the INIT mode.And the address is 0. The communication setting is “9600,N,8,1”.Q2. How to configure the I-7000 and M-7000 modules?ICP DAS provide DCON Utility to configure I-7000 and M-7000 modules.Please download the last version from: /pub/cd/8000cd/napdos/driver/dcon_utility/Q3. How to calibrate the analog input module?Usually it is not necessary to calibrate the analog input module.However, in case you need to perform this operation, we provide a function to calibrate the module.Please refer to user manual 1.10.Notice:1.Please update DCON Utility to version 5.2.3 or more.2.Keep the module running more than 30 minutes to warm-up.Q4. How to measure the current?I-7017R and I-7017R require optional external resistance (125Ω) for current measurement.Please refer wired connections diagram.And then select a suitable input range by DCON Utility.Or please use our I-7017RC or I-7017RC modules.Q5. How to programming with I-7000 or M-7000 by C#, VB, VC?ICP DAS I-7000 and M-7000 series both support DCON protocol. And Only M-7000 series supports Modbus protocol.For DCON protocol, please download SDK and Demo from:/pub/cd/8000cd/napdos/driver/dcon_dll_new/For Modbus protocol, please refer this web link:/products/PAC/i-8000/modbus.htmIfthereisanyotherquestion,pleasefeelfreetocontactus.Email:******************Website: /contact_us/contact_us.htmlI-7017R - 8-ch Voltage and Current Input DAQ Module - QuickStart (May/2020)ICP DAS USA, Inc. | | 1-310-517-9888 | 24309 Narbonne Ave. Suite 200. Lomita, CA 90717。

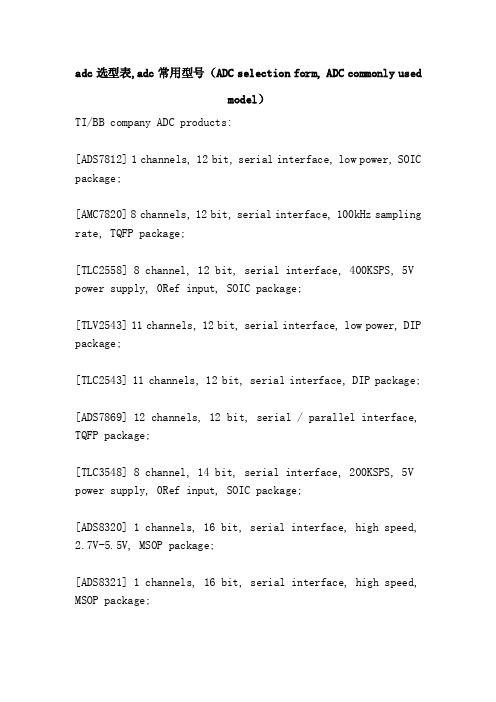

adc选型表,adc常用型号(A...

adc选型表,adc常用型号(ADC selection form, ADC commonly usedmodel)TI/BB company ADC products:[ADS7812] 1 channels, 12 bit, serial interface, low power, SOIC package;[AMC7820] 8 channels, 12 bit, serial interface, 100kHz sampling rate, TQFP package;[TLC2558] 8 channel, 12 bit, serial interface, 400KSPS, 5V power supply, 0Ref input, SOIC package;[TLV2543] 11 channels, 12 bit, serial interface, low power, DIP package;[TLC2543] 11 channels, 12 bit, serial interface, DIP package;[ADS7869] 12 channels, 12 bit, serial / parallel interface, TQFP package;[TLC3548] 8 channel, 14 bit, serial interface, 200KSPS, 5V power supply, 0Ref input, SOIC package;[ADS8320] 1 channels, 16 bit, serial interface, high speed, 2.7V-5.5V, MSOP package;[ADS8321] 1 channels, 16 bit, serial interface, high speed, MSOP package;[ADS8505] 1 channels, 16 bit, parallel interface, 250-KSPS, SSOP package;[ADS8509] 1 channels, 16 bit, serial interface, 250Ksps, SSOP package;[ADS7809] 1 channels, 16 bit, serial interface, 100Ksps, 5V power supply, SOIC package;[ADS8342] 4 channel, 16 bit parallel interface, 250Ksps, input range -2.52.5, TQFP package;[ADS8345] 8 channels, 16 bit, serial interface, serial, SSOP package;[ADS1241] 4 channels, 24 bit, serial interface, SSOP package;[ADS7835] 1 channels, 24 bit, serial interface, high speed, low power AD converter, MSOP package;AD company ADC products:[AD7864] 4 channels, 12 bit, parallel interface, high-speed simultaneous sampling, single supply, TQFP package;[AD7865] 4 channels, 14 bit, parallel interface, high-speed simultaneous sampling, single supply, TQFP package;[AD677] 1 channels, 16 bit, serial interface, 100KSPS, DIP package;[AD7612] 1 channels, 16 bit, parallel / serial, 750KSPS, single stage / dual stage input, DIP package;[AD7715] 1 channels, 16 bit, serial interface, 3V power supply, DIP package;[AD974] 4 channels, 16 bit, serial interface, single supply, 200KSPS, DIP package;[AD976] 4 channels, 16 bit, serial interface, single supply, 200KSPS, + 10V input, DIP package;[AD7710] 2 channels, 24 bit, serial interface, input programmable gain, SOIC package;MAXIM company ADC products:[MAX156] 4 channels, 8 bit, parallel interface, high speed, voltage reference, DIP package;[MAX158] 8 channels, 8 bit, parallel interface, high speed, voltage reference, DIP package;[MAX160] 1 channel, 8 bit parallel interface, + 5V, + 5, 10 input range, 4 S, DIP package;[MAX176] 1 channels, 12 bit, serial interface, 250ksps, voltage reference, DIP package;[MAX187] 1 channels, 12 bit, serial interface, +5V, low power, DIP package;[MAX163] 1 channels, 12 bit, parallel interface, 5V input, sampling rate 100k, voltage reference, DIP package;[MAX167] 1 channels, 12 bit, parallel interface, + 2.5V input, sampling rate, 100k, voltage reference, DIP package;[MAX144] 2 channels, 12 bit, serial interface, +3V/5V, low power, 108ksps, DIP package;[MAX1282] 4 channels, 12 bit, serial interface, 400ksps, +5V, built in voltage reference, SSOP package;[MAX1270] 8 channels, 12 bit, serial interface, 110ksps, multi range, +5V, built in voltage reference, DIP package;[MAX146] 8 channels, 12 bit, serial interface, +2.7V, low power, DIP package;[MAX186] 8 channels, 12 bit, serial interface, low power, DIP package, SOIC package;[MAX197] 8 channels, 12 bit, parallel interface, multi range, single +5V, DIP package, SOIC package;[MAX110] 2 channels, 14 bit, serial interface, + 3V input, low cost, DIP package;[MAX111] 2 channels, 14 bit, serial interface, + 1.5V input, low cost, DIP package;[MAX1134] 1 channels, 16 bit, serial interface, 150ksps, 3.3V, single power supply, SSOP package;[MAX1165] 1 channels, 16 bit, parallel interface (16 bit), low power, TSSOP package;[MAX1166] 1 channels, 16 bit, parallel interface (8 bit), low power, TSSOP package;[MAX1169] 1 channels, 16 bit, 2 wire serial interface, 58.6ksps, TSSOP package;[MAX7129] 4 1/2 bits, with multiplexed LCD drivers, low-noise, DIP packages.AD7865AS-1 function applications simple description: 14 bit, 4 channel simultaneous sampling, 175KSPS rate analog to digital converter, with 2SHA, and, 2ADCs (industrial level), the original manufacturer is packaged as: PQFPLQFP Function Description: 14 bit 65MSPS analog to digital converter (industrial level) AD6644ASTAD7856AN function applications simple description: 14 bit 8 channel 285KSPS sampling rate analog-to-digital converter (industrial level), the original manufacturer is packaged as: DIPAD537SH Function Description: 150KHZ integrated voltage to frequency converter (military level) TO-99AD537JH function applications simple description: 150KHZ integrated voltage converter (civil level), the original manufacturer is packaged as: TO-99AD75019JP Function Application Description: 16 * 16 audio frequency switch (civil level), the original manufacturer is packaged as: PLCCApplication of AD7701AN Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7705BN Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7706BN Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7715AN-5 Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: DIP 5V power packageApplication of AD7705BR Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: SOIC packageApplication of AD7707BR Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: SOIC packageApplication of AD7715AR-5 Function Description: 16 - Sigma Delta ADC (industrial grade) original manufacturer: SOIC 5V power packageAD1380JD function applications simple description: 16 bit 20us high performance analog to digital converter (civil level)AD1380KD function applications simple description: 16 bit 20us high performance analog to digital converter (civil level)AD569JN Function Description: 16 bit 3us current output digital to analog converter (Civil) DIPAD669AN function application brief description: 16 bit 8us parallel input digital to analog converter (industrial level), the original manufacturer is packaged as: DIPAD660AN function applications simple description: 16 bit 8us serial parallel input, digital to analog converter (industrial level), the original manufacturer is packaged as: DIPAD420AN-32 function applications simple description: 16 bit single power 4-20mA output digital to analog converter (industrial level), the original manufacturer is packaged as: DIPAD420AR-32 function applications simple description: 16 bit single power 4-20mA output digital to analog converter (industrial level), the original manufacturer is packaged as: SOICAD7846JN function description of the application: 16 bit voltage output digital to analog converter (civil level), the original manufacturer is packaged as: DIPAD768AR Function Application Description: 16 bit high-speed current output digital to analog converter (civil level), the original manufacturer is packaged as: SOICAD7660AST function applications simple description: 16 bit 100KSPS CMOS analog to digital converter (industrial level), the original manufacturer is packaged as: LQFPAD676JD function applications simple description: 16 bit 100KSPS sampling rate parallel output ADC (civil level), the original manufacturer is packaged as: DIPAD676JN function applications simple description: 16 bit 100KSPS sampling rate parallel output ADC (civil level), the original manufacturer is packaged as: DIPAD676KD function applications simple description: 16 bit 100KSPS sampling rate parallel output ADC (civil level), the original manufacturer is packaged as: DIPAD677JD function applications simple description: 16 bit 100KSPS sampling rate, serial output analog to digital converter (civil level), the original manufacturer is packaged as: DIPAD677JN function applications simple description: 16 bit 100KSPS sampling rate, serial output analog to digital converter (civil level), the original manufacturer is packaged as: DIP100KSPS sampling rate, serial output analog to digital converter (civil level), the original manufacturer is packaged as: SOICAD7664AST function applications simple description: 16 bit 570KSPS CMOS analog to digital converter (industrial level), the original manufacturer is packaged as: LQFPAD421BN function application brief description: 16 bit loop power supply, in line with the HART agreement, 4-20mA output digital to analog converter (industrial level), the original manufacturer is packaged as: DIPAD421BR function application brief description: 16 bit loop power supply, in line with the HART agreement, 4-20mA output digital to analog converter (industrial level), the original manufacturer is packaged as: SOICAD7506JN function applications simple description: 16 election 1 CMOS multiplexer (civil level), the original manufacturer is packaged as: DIPAD650JN function application brief description: 1MHz, voltage frequency converter (civil level), the original manufacturer is packaged as: DIPAD650KN function application brief description: 1MHz, voltage frequency converter (civil level), the original manufacturer is packaged as: DIPchannel sample and hold amplifier (civil level), the original manufacturer is packaged as: DIPAD780AN function description simple description: 2.5V or 3V optional output high-precision voltage reference source (industrial level), the original manufacturer is packaged as: DIPApplication of AD7703AN Function Description: 20 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7703BN Function Description: 20 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7710AN Function Description: 24 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7711AN Function Description: 24 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7713AN Function Description: 24 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7731BN Function Description: 24 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7712AN Function Description: 24 - Sigma Delta ADC (industrial grade) original manufacturer: DIP packageApplication of AD7714AN-3 Function Description: 24 - SigmaDelta ADC (industrial grade) original manufacturer: DIP 3V power packageApplication of AD7714AN-5 Function Description: 24 - Sigma Delta ADC (industrial grade) original manufacturer: DIP 5V power packageAD652AQ function application brief description: 2MHz, synchronous voltage frequency converter (industrial level), the original manufacturers are packaged as: DIPAD585AQ function application brief description: 3us sample and hold amplifier (industrial level), the original manufacturers are packaged as: DIPAD654JN function application brief description: 500KHz, low price, voltage, frequency converter (civil level), the original manufacturer is packaged as: DIPAD654JR function application brief description: 500KHz, low price, voltage, frequency converter (civil level), the original manufacturer is packaged as: SOIC。

ASML X系列产品手册

6.0

0.06

0.8

MF-MSMF020/60

60.0

40 0.20 0.40 0.40 6.00

1.5

0.15

0.8

MF-MSMF030

30.0

10 0.30 0.60 0.30 3.00

8.0

0.10

0.8

MF-MSMF050

15.0

100 0.50 1.00 0.15 1.00

8.0

0.15

0.8

x

xx

Linear AC/DC adapters

xxx xxxx

x

Electromagnetic loads, motor

x x x xxxxx x x

xxxx x

Solenoid protection

x

x

xxx

x

Displays

x xx x x

xxx

Security systems

x xxxxxxxxxx

3 What is the ambient temperature of your circuit?

"Bourns” and "Multifuse" are registered trademarks of Bourns, Inc. in the U.S. and other countries. COPYRIGHT© 2021, BOURNS, INC. • LITHO IN U.S.A. • MIMEO • 2/21 • e/MF2105

Bourns® Multifuse® Device Application Table

Industry

Telecom

Computer

ASM 142系列蜜芬泄漏检测器说明书

G B 00207 - E d i t i o n 05 - F e b r u a r y 121/1A 100Introduction to the ASM 142 seriesA new generation of adixen helium leakdetectorModel photographed: ASM 142The ASM 142/142 D/142 S/ASM Graph/ASM Graph D/ASM Graph D+ are universal helium leak detectors which set new performance standards for multi-purpose unit.These detectors are the end-result of an innovative engineering approach utilizing the latest electronics technologies and vacuum concepts, whichmake them a truly universal unit:142I high performances, such as, a roughing capacity of 7 CFM (60 l/mn) with a usable helium sensitivity in the 10-11 /sec range.x x xI high performances, such as, a dry roughing capacity of 0.9 CFM (1.5 m 3/h) with a usable helium sensitivity in the 10-11 /sec range.x x xI a usable helium sensitivity in the10-7 /sec range (with auto-zero function).xI comprehensive control panel with two distinct areas (one for the operation of the unit, the other for entering the test parameters).x x x x x xI evolved features to assist the operator in his daily operation (auto-calibration, auto-zero, helium signal direct readout, ...).x x x x x xI very rugged design, based on field-proven components, which makes it ideal for any industrial environment.x x x x x xI various accessories to reinforce the versatility of the product (remote control, sniffer probe).x x x x x xI totally dry leak detector.x xxI specific to sniffing test mode applications.xI graphic interface.xxxWe suggest that you read this manual before you start to use your detector to obtain optimum levels of performance and complete satisfaction.adixen Vacuum Products - ASM 142 S Operating instructions。

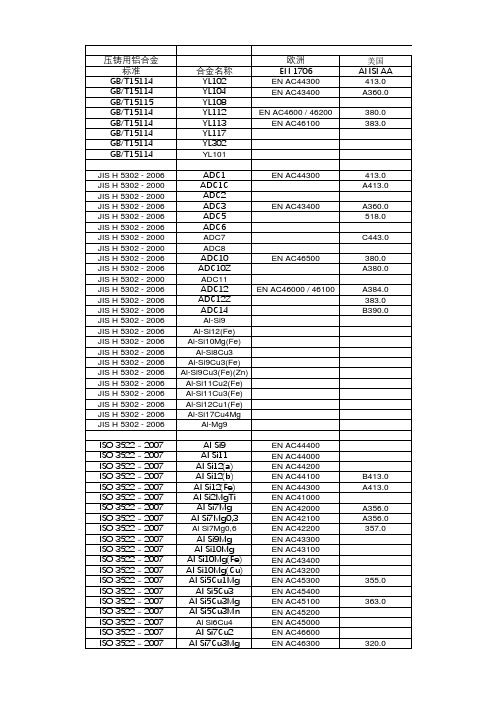

铝合金各国牌号对照及化学成分表

Al-Si8Cu3Fe

Al-Si9 Al-Si12(Fe) Al-Si10Mg(Fe) Al-Si8Cu3 Al-Si9Cu3(Fe) Al-Si9Cu3(Fe)(Zn) Al-Si11Cu2(Fe) Al-Si11Cu3(Fe) Al-Si12Cu1(Fe) Al-Si17Cu4Mg

JIS H 5302 - 2006

JIS H 5302 - 2006

JIS H 5302 - 2006

ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007 ISO 3522 - 2007

挤出用铝合金 标准

EN 573-3 EN 573-4 EN 573-3 EN 573-3 EN 573-3

Al Si8Cu3 Al Si9Cu1Mg Al Si9Cu3(Fe) Al Si9Cu3(Fe)(Zn) Al Si11Cu2(Fe) Al Si11Cu3(Fe) Al Si12(Cu) Al Si12Cu1(Fe) Al Si12CuMgNi Al Si17Cu4Mg

压铸用铝合金 标准

GB/T15114 GB/T15114 GB/T15115 GB/T15114 GB/T15114 GB/T15114 GB/T15114 GB/T15114

ADC性能分析设备

ADC性能分析设备概述ADC(Analog-to-Digital Converter,模数转换器)性能分析设备是一种专门用于测试和分析模数转换器性能的仪器。

模数转换器是将连续的模拟信号转换为离散的数字信号的设备,常见于各种电子设备中,如音频设备、通信设备、测量仪器等。

ADC性能分析设备通过对模数转换器进行各种性能指标的测试,能够评估模数转换器的性能表现,为系统设计和优化提供重要参考。

本文将介绍ADC性能分析设备的原理、常用指标以及使用方法等内容,帮助读者更好地了解和应用ADC性能分析设备。

原理ADC性能分析设备主要基于测试设备和信号源两个部分组成。

其中,测试设备负责采集和处理来自信号源的模拟信号和数字信号,信号源则用于向被测试的模数转换器提供模拟输入信号。

在测试过程中,信号源将模拟输入信号传递给被测试的模数转换器,经过转换后的数字信号被测试设备采集和处理。

测试设备可以通过内部的高精度时钟和采样电路,对转换后的数字信号进行采样和分析,从而得到各种性能指标。

常用指标分辨率分辨率是指ADC转换结果表示的离散等级数。

一般来说,分辨率越高,表示ADC能够精细地转换模拟信号,对细微变化更敏感。

常见的分辨率单位有bit、字节等。

信噪比(SNR)信噪比是指ADC在转换过程中输出信号与输入信号的噪声之比。

高信噪比表示ADC抗干扰能力强,输出信号纯净,不受噪声干扰。

有效位数(ENOB)有效位数是指ADC输出数据中真正包含有效信息的位数。

通常使用ENOB来衡量ADC的精度和性能。

采样率采样率是指ADC每秒钟进行模拟信号采样的次数,常用单位为Hz。

采样率决定了ADC能够捕捉到的模拟信号频率范围,对于高频信号的采样,需要有足够高的采样率才能准确还原信号。

以上只是ADC性能分析设备常见的指标之一,不同的设备可能还具有其他的性能指标。

在实际应用中,根据具体需求选择合适的性能指标进行测试和评估。

使用方法1. 连接测试设备和信号源首先,根据设备的连接规范,将测试设备和信号源进行正确的连接。

STM32的ADC和DAC问题集锦

1、STM32的DAC转换是什么开始的呢?问:STM32的DAC转换是什么开始的呢?如何利用DAC输出一个脉宽的控的单脉冲呢?答:DAC是通过写入DAC输出寄存器开始的。

另外,如果想要脉冲,使用TIM功能。

2、STM32的DAC输出电压问:DAC的输出电压是如何调节的呢,输入的数字量和输出的电压怎么不成比例呢,输出电压不符合数据手册上提供的公式(DAC输出= VREF X DOR / 4095),求高人指点,程序如下:#include "stm32f10x_lib.h"#define DAC_DHR8R1_Address 0x40007410DAC_InitTypeDef DAC_InitStructure;DMA_InitTypeDef DMA_InitStructure;ErrorStatus HSEStartUpStatus;uc8 Escalator8bit[50] = {0x0, 0x33, 0x66, 0x99, 0xcc, 0xff};void RCC_Configuration(void);void GPIO_Configuration(void);void NVIC_Configuration(void);void Delay(vu32 nCount);int main(void){#ifdef DEBUGdebug();#endifRCC_Configuration();GPIO_Configuration();NVIC_Configuration();TIM_PrescalerConfig(TIM6, 0xF, TIM_PSCReloadMode_Update);TIM_SetAutoreload(TIM6, 0xFF);TIM_SelectOutputTrigger(TIM6, TIM_TRGOSource_Update);DAC_InitStructure.DAC_Trigger = DAC_Trigger_T6_TRGO;DAC_InitStructure.DAC_WaveGeneration = DAC_WaveGeneration_None;DAC_InitStructure.DAC_OutputBuffer = DAC_OutputBuffer_Disable;DAC_Init(DAC_Channel_1, &DAC_InitStructure);DMA_DeInit(DMA2_Channel3);DMA_InitStructure.DMA_PeripheralBaseAddr = DAC_DHR8R1_Address; DMA_InitStructure.DMA_MemoryBaseAddr = (u32)&Escalator8bit;DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralDST;DMA_InitStructure.DMA_BufferSize = 6;DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Byte; DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte; DMA_InitStructure.DMA_Mode = DMA_Mode_Circular;DMA_InitStructure.DMA_Priority = DMA_Priority_High;DMA_InitStructure.DMA_M2M = DMA_M2M_Disable;DMA_Init(DMA2_Channel3, &DMA_InitStructure);DMA_Cmd(DMA2_Channel3, ENABLE);DAC_Cmd(DAC_Channel_1, ENABLE);DAC_DMACmd(DAC_Channel_1, ENABLE);TIM_Cmd(TIM6, ENABLE);while (1){}}void RCC_Configuration(void){RCC_DeInit();RCC_HSEConfig(RCC_HSE_ON);HSEStartUpStatus = RCC_WaitForHSEStartUp();if(HSEStartUpStatus == SUCCESS){FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);FLASH_SetLatency(FLASH_Latency_2);RCC_HCLKConfig(RCC_SYSCLK_Div1);RCC_PCLK2Config(RCC_HCLK_Div1);RCC_PCLK1Config(RCC_HCLK_Div2);RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);RCC_PLLCmd(ENABLE);while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);while(RCC_GetSYSCLKSource() != 0x08){}}RCC_AHBPeriphClockCmd(RCC_AHBPeriph_DMA2, ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO | RCC_APB2Periph_GPIOA, ENABLE); RCC_APB1PeriphClockCmd(RCC_APB1Periph_DAC, ENABLE);RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM6, ENABLE);}void GPIO_Configuration(void){GPIO_InitTypeDef GPIO_InitStructure;GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;GPIO_Init(GPIOA, &GPIO_InitStructure);}void NVIC_Configuration(void){#ifdef VECT_TAB_RAMNVIC_SetVectorTable(NVIC_V ectTab_RAM, 0x0);#else /* VECT_TAB_FLASH */NVIC_SetVectorTable(NVIC_V ectTab_FLASH, 0x0);#endif}void Delay(vu32 nCount){for(; nCount != 0; nCount--);}输出电压为什么不是0~3.3V呢?答1:(u32)&Escalator8bit;你把这个里面的数据强制转换为32位,也就是0x0, 0x33, 0x66, 0x99转换为一个32位的数据,你这样做是不对的。

ADC-EMC用户手册说明书

ADC-EMCUser ManualAD001174Version 1.3Copyright © 2007 Alpha Data Parallel Systems Ltd. All rights reserved.This publication is protected by Copyright Law, with all rights reserved. No part of this publication may be reproduced, in any shape or form, without prior written consent from Alpha Data Parallel Systems Limited.Alpha Data Parallel Systems Ltd.4 West Silvermills LaneEdinburgh EH3 5BDScotlandUKPhone: +44 (0) 131 558 2600Fax: +44 (0) 131 558 2700Email: **********************Reserved rightsThis manual is designed to provide outline information only. Alpha Data has acontinual policy of improving its products; hence it reserves the right to changeproduct specification without prior warning. Alpha Data cannot accept any liabilityfor loss or damages arising from the use of this manual or the use of productsdetailed within it.Trademark acknowledgementsPCI TM, PCI-X TM, PCI EXPRESS® and PCIe® are registered trademarks of PCI-SIG TM.Warranty and SupportAll Alpha Data products enjoy parts and labour warranty for 12 months afterpurchase. The warranty is based on the customer returning the defective goods toAlpha Data for repair or replacement, which will be at the discretion of thecompany. The warranty does not cover damages caused by negligence, misuse, andnormal wear and tear. No liability is accepted by the company for any damagecaused by the use of its hardware or software.All goods from Alpha Data carry a 6 months free support service. This service isavailable by letter, phone, fax, and email. Technical support contracts for longerperiods are available on request. Support contracts for software components alsonormally cover the cost of upgrades.Table of Contents1.Introduction...........................................................................................................................1-11.1About the Hardware......................................................................................................1-11.2Board Architecture Description.....................................................................................1-11.3Board Clocking.............................................................................................................1-21.4JTAG Debugging..........................................................................................................1-32.Installation.............................................................................................................................2-42.1Into a PC.......................................................................................................................2-42.2Adding PMC/XMC cards..............................................................................................2-42.3Software Support...........................................................................................................2-42.4Power Considerations....................................................................................................2-53.Hardware Information............................................................................................................3-63.1Switches........................................................................................................................3-63.2JP1................................................................................................................................3-63.3JP4................................................................................................................................3-63.4J1 JTAG Connector.......................................................................................................3-63.5J2 / J3 Samtec QSE-DP Connector................................................................................3-73.6J4 Disk Power Connector..............................................................................................3-73.7J16 / J17 JTAG Headers................................................................................................3-73.8J18 I2C Header.............................................................................................................3-73.9Board LEDs..................................................................................................................3-73.10J5 Header Configuration................................................................................................3-83.11P15 / P25 XMC Primary Connector.............................................................................3-103.12P11, P21, P12, P22 PMC Connectors..........................................................................3-103.13P13, P23, P14, P24 PMC Connectors..........................................................................3-11 Revision History............................................................................................................................3-121.Introduction1.1About the HardwareThe ADC-EMC is a full length PCI Express card designed to carry two PCI Mezzanine Cards (PMC) or Switched Mezzanine Cards (XMC). It can be used in x1, x2, x4 and x8 PCIesignalling environments installed in x8 or x16 PCIe slots. There are two PMC slots on the card which support 32 or 64-bit operation on independent PCI/PCI-X busses. The secondary busVIO is configured for 3.3V operation, and a key pin prevents 5V signalling devices from being installed.The board has many configurations for XMC support. The high speed serial lanes of twoXMC cards can be connected for inter-XMC communication, can route to the PCI expressbridge for host communication and can route to a Samtec QS-DP connector for intra-carriercard communication.The ADC-EMC carrier card also supports features of Alpha Data FPGA boards in a PCIenvironment with the provision of Pn4 routing between the two PMC sites and selectively to a 64-way header.The secondary bus interfaces are rated at up to 133MHz operation in PCI-X mode. Theprimary PCIe interfaces are rated for Gen1 at 2.5GHz.1.2Board Architecture DescriptionThe ADC-EMC is based on the PEX8525 PCIe switch and PEX8114 PCIe-PCIX bridges.Each PMC site is connected to an independent PCI/PCI-X bus as shown in Figure 1.Each of the two PMC sites supports Pn4 IO with quick-switch isolation to permit various IO combinations. A set of switches on the board enables each of the quick-switch blocks. The IO-Bus is 64 bits wide and connects to all 64 signals from the Pn4 connector of each PMC site.Further, all of the IO-Bus can be routed to the J5 header through a quick-switch block thatprovides a level of protection to the IO bus signals by limiting the external signal levels.Figure 1 ADC-EMC Board Block DiagramFigure 2 XMC SwitchingFigure 2 shows the interface between primary XMC connectors of the two PMC/XMC sites.There are two groups of x4 SERDES signals between the two sites using switched routing.Each SERDES lane (x1) consists of a TX and RX pair.The first group of x4 connects via a multiplexer to a x4 PCIe port of the 8525 switch to allow host communication to XMC resources. Alternatively, the XMCs may be connected via the multiplexer to each other for sideband communication.The second group of x4 connects via a multiplexer to a Samtec QSE-DP connector to allow linking of multiple ADC-EMC boards. Alternatively, the XMCs may be connected via the multiplexer to each other for sideband communication. The cable used to connect 2 carrier cards via the QSE-DP connectors is a Samtec EQDP-014-06.00-TTR-TBL-2.1.3Board ClockingFigure 3 Clock DistributionThe clock distribution network on the ADC-EMC uses a 1:6 buffer to replicate the 100MHz reference clock from the edge connector to all PCI Express devices. Each clock driven to an XMC connector is automatically disabled if the plug-in card is not present.1.4JTAG DebuggingThe ADC-EMC features a versatile JTAG debugging chain that has selectable routing to the carrier card devices, and either of the PMC JTAG headers. The main JTAG connector (J1)connects to a Xilinx Parallel IV or Xilinx Platform Cable USB using the IDC ribbon cableprovided with these devices.There are 2 JTAG headers (J16 and J17) which allow connections to the PMC/XMC cards’JTAG chains by using flying leads which are available from Xilinx. The I/O voltage of theJTAG header signals is controlled by the VCC signal from the PMC, and is supported from2.5V to 5.0V.There are 3 switches on the ADC-EMC that control the routing of the JTAG chain. When the corresponding switch is closed, the devices will automatically be inserted into the JTAG chain in the following order: SW2-1 will include the PEX8525, and both PEX8114 devices in the chain, SW2-2 will include the PMC1 header in the chain, and SW2-3 will include the PMC2 header in the chain. When the corresponding switch is open, the JTAG signals will be set in an idle state and the JTAG chain routed around them.The PMC JTAG headers have an auto-detect feature that will remove them from the JTAGchain if the header is not connected.Note: Routing is also included for JTAG connections to each PMC via the PMC connectors,and can be enabled with a firmware change from the factory.Figure 4 JTAG Routing2.InstallationIn order to ensure that the board operates correctly first time, please read these instructionscompletely before attempting installation. It will also help you to read the whole manual first so that you know how you want the board to be set up. The installation instructions for your PC should be followed at all times.2.1Into a PCThe ADC-EMC can be installed in any x8 or x16 PCIe host connector.2.2Adding PMC/XMC cardsFit any PMC modules that are required. If only one PMC module is to be fitted, either site can be used. PMC site #1 is positioned so that an I/O connector on the module aligns with theaperture in the ADC-EMC's edge panel. The PMC modules should be supplied with mounting kits, which normally include spacers, nuts, bolts and washers. Figure 1 shows the typicalassembly of a PMC to the ADC-EMC. It is recommended that washers be used on both sides of the ADC-EMC to avoid damage to the PCB.Figure 5 Assembly of a PMC to the ADC-EMC2.3Software SupportThe ADC-EMC uses transparent bridge devices that are compatible with most operatingsystems that adhere to the PCI Bios specification.No software is required to enable operation of the ADC-EMC.Configuration of the 8525 switch is by a dedicated pre-programmed SPI EEPROM on theADC-EMC. Configuration of each of the 8114 bridges is also by individual dedicated pre-programmed SPI EEPROMs. The 8525 switch can also be controlled via a dedicated I2Cconnection available via a header for debug purposes.2.4 Power ConsiderationsThe ADC-EMC is designed to support standard PMC or PMC/XMC format boards. These cards are usually specified to consume a maximum of 7.5W each and these, together with the background power consumed by the ADC-EMC amount to around 22W, within the budget of a typical PCI Express slot (x16/x8).The ADC-EMC can operate using the power provided by the PCI Express edge connector if the PMC/XMC cards will require less than 19W total. Where additional power is required, a disk drive type connector is provided to allow a controlled connection to the system power supply to source and additional 24W (12V at up to 2.0A).A protection mechanism will prevent the board from exceeding the current limit of the PCIe connector by more than 50%. A red LED will illuminate and the 12V power will be removed automatically if this condition is reached. This indicates the auxiliary disk power connector must also be used. This protection mechanism is set at a higher limit than the recommended maximum, so care should be taken to ensure the board has adequate power supplied. The ADC-EMC seamlessly controls the two sources of 12V power, and will not allow current to flow from one source back to the other (when jumper JP4 is removed).The PMC/XMC cards are supplied with +12V, -12V, +5V and +3.3V power rails. Figure 6 shows the maximum power limit on each supply rail to the combined load of both PMC/XMC cards. The system must not exceed any of these limits in the given configuration. The total power provided to the PMC/XMC cards must not exceed 19W, or 43W if the disk power connector is supplied.PMC Power Limits Using External PowerConnector PCIe Power Only Total available for both PMC Sites 43W 19W +12V Rail available power 43W 19W -12V Rail available power 18W 18W +5V Rail available power 28W 19W +3.3V Rail available power 25W19WFigure 6 Power Supply LimitsFigure 7 Power Supply Diagram3. Hardware Information3.1 SwitchesThere are 16 switches on the board that are used for configuration settings.* Note: Switch controls the corresponding lanes of both XMC sites** Note: Root signal is used in PCI-express mode to enable a processor XMC root features (bus enumeration). It also enablesthe carrier card to propagate the XMC (Reset) MRSTOn to both XMC sites MRSTIn.3.2 JP1JP1 is connected to the PortEN signal of the CPLD. It is used at the factory to configure the device and should and should only be installed in manufacturing as changes to this device could cause system failure.3.3 JP4JP4 should be left installed, unless the system uses separate power supplies for the PCIebackplane and J4 Power connector. It is connected to the power controller device and can be removed to enable the OR’ing feature between the disk power connector and PCIe edgeconnector. This feature will protect the ADC-EMC from feeding power from one power supply back to the other.3.4 J1 JTAG ConnectorNC 14NC 12TDI 10TDO 8TCK 6TMS 4VREF 213 GND 11 GND 9 GND 7 GND 5 GND 3 GND 1 GNDSWITCH FUNCTION CLOSED (ON) OPEN (OFF)SW1-1 XMC1 NVM WRITE PROHIBIT ALLOW NON-VOLITILE MEM WRITES PROHIBIT SW1-2 XMC2 NVM WRITE PROHIBIT ALLOW NON-VOLITILE MEM WRITES PROHIBIT SW1-3 XMC MUX SELECT LANES 0-1 * CONNECT LANES TO BRIDGE CONNECT LANES (J15-J25) SW1-4 XMC MUX SELECT LANES 2-3 * CONNECT LANES TO BRIDGE CONNECT LANES (J15-J25) SW1-5 XMC MUX SELECT LANES 4-5 * CONNECT LANES TO HEADER CONNECT LANES (J15-J25) SW1-6 XMC MUX SELECT LANES 6-7 * CONNECT LANES TO HEADER CONNECT LANES (J15-J25) SW1-7 XMC1 ROOT COMPLEX ** ENABLE DISABLE SW1-8XMC2 ROOT COMPLEX **ENABLEDISABLESW2-1 JTAG CARRIER DEBUG BYPASS CARRIER (8525 & 8114) INCLUDE IN JTAG CHAIN SW2-2 JTAG PMC1 DEBUG BYPASS PMC1 JTAG HEADER INCLUDE IN JTAG CHAIN SW2-3 JTAG PMC2 DEBUG BYPASS PMC2 JTAG HEADER INCLUDE IN JTAG CHAIN SW2-4 80 PIN HEADER J5 ENABLE CONNECT BUSSED Jn4 SIGNALS HEADER UNCONNECTED SW2-5 PMC1 J14 BUS CONNECT CONNECT LOWER 32 BITS UNCONNECTED SW2-6 PMC1 J14 BUS CONNECT CONNECT UPPER 32 BITS UNCONNECTED SW2-7 PMC2 J24 BUS CONNECT CONNECT LOWER 32 BITS UNCONNECTED SW2-8PMC2 J24 BUS CONNECTCONNECT UPPER 32 BITSUNCONNECTEDFor use with Xilinx Parallel IV or Platform Cable USB IDC ribbon cables. For more information see DS300 or DS097 available at .3.5 J2 / J3 Samtec QSE-DP Connector(Note: J2 Connects to XMC1 J15 signals, J3 connects to XMC2 J25 signals)LINK DESCRIPTION PIN PIN DESCRIPTIONLINK XMC_ DP4 + 1 2 XMC_ DP14 +TXA XMC_ DP4 - 3 4 XMC_ DP14 – RXAXMC_ DP5 + 5 6 XMC_ DP15 +TXB XMC_ DP5 - 7 8 XMC_ DP15 – RXBXMC_ DP6 + 9 10 XMC_ DP16 +TXC XMC_ DP6 - 11 12 XMC_ DP16 – RXCXMC_ DP7 + 13 14 XMC_ DP17 +TXD XMC_ DP7 - 15 16 XMC_ DP17 –RXDUnused 17 18 Unused Unused 19 20 Unused Unused 21 22 Unused Unused 23 24 Unused Unused 25 26 Unused Unused 27 28 Unused3.6 J4 Disk Power Connector+12VGNDGNDNC3.7 J16 / J17 JTAG HeadersPinFunction1 VCC (JTAG I/O Voltage input from PMC)2 GND3 Unused4 TCK5 NC6 TDO7 TDI8 *KEY* Not Installed 9TMS3.8 J18 I2C HeaderPin Function 1 SDA 2 GND3 GPO (General Purpose Output of PEX8525)4 VCC (3.3V Fused) 5SCLThe 1/10 inch header can be used to access the internal registers of the PEX8525, at I2C bus address 0x58. The I2C bus is also routed to the XMC connectors J15 and J16 with I2C channel select addresses of 0x00 and 0x01 respectively. The ADC-EMC board has the necessary pull-ups for I2C communication.3.9 Board LEDsReference Color FunctionD1 Green PCIe-PCI Bridge PMC2 Port Good D2 Green PCIe-PCI Bridge PMC1 Port Good D3GreenPCIe Host Port GoodD4 Green3V3 Power OK Indicator D5 Green XMC2 PCIe Port Good D6 Green XMC1 PCIe Port Good D7 Green 12V Power OK Indicator D8RedPCIe 12V Supply Limit Exceeded3.10 J5 Header ConfigurationThe IO header, J5, is suitable for mating with IDC connectors and is a RN P50E-080-P1-SR1-TG or equivalent. The signaling level is dependant on the PMC drivers and the header inputs, but is limited to 3.3V in either direction by level shifting circuitry on the ADC-EMC carrier card.179J5gnd 1 2 gnd gnd 3 4 gnd gnd 5 6 gnd gnd 7 8 gnd gnd 9 10 gnd Pn4-1 11 12 Pn4-3 Pn4-2 13 14 Pn4-4 Pn4-5 15 16 Pn4-7 Pn4-6 17 18 Pn4-8 Pn4-9 19 20 Pn4-11 Pn4-10 21 22 Pn4-12 Pn4-13 23 24 Pn4-15 Pn4-14 25 26 Pn4-16 Pn4-17 27 28 Pn4-19 Pn4-18 29 30 Pn4-20 Pn4-21 31 32 Pn4-23 Pn4-22 33 34 Pn4-24 Pn4-25 35 36 Pn4-27 Pn4-26 37 38 Pn4-28 Pn4-29 39 40 Pn4-31 Pn4-30 41 42 Pn4-32 Pn4-33 43 44 Pn4-35 Pn4-34 45 46 Pn4-36 Pn4-37 47 48 Pn4-39 Pn4-38 49 50 Pn4-40 Pn4-41 51 52 Pn4-43 Pn4-42 53 54 Pn4-44 Pn4-45 55 56 Pn4-47 Pn4-46 57 58 Pn4-48 Pn4-49 59 60 Pn4-51 Pn4-50 61 62 Pn4-52 Pn4-53 63 64 Pn4-55 Pn4-54 65 66 Pn4-56 Pn4-57 67 68 Pn4-59 Pn4-58 69 70 Pn4-60 Pn4-61 71 72 Pn4-63 Pn4-62 73 74 Pn4-64 gnd 75 76 gnd gnd 77 78 gnd gnd7980gndThe IO header is optimised for LVDS pairing to ADM-XRC-4FX and later mezzanine card connections. All odd number J5 header signals are “P” with even numbers being “N”. For example J5-11 and J5-12 are a P/N pair connected to Pn4-1 and Pn4-3. The pairing on this connector is consistent with the heritage ADC-PMC board, and the routing from Pn4 is updated for the new pairing system on the ADM-XRC-4FX and later PMC boards.3.11P15 / P25 XMC Primary ConnectorA B C D E F01 DP00+ DP00- 3.3V DP01+ DP01- VPWR02 GND GND NC GND GND MRSTI#03 DP02+ DP02- 3.3V DP03+ DP03- VPWR04 GND GND NC GND GND MRSTO#05 DP04+ DP04- 3.3V DP05+ DP05- VPWR06 GND GND NC GND GND +12V07 DP06+ DP06- 3.3V DP07+ DP07- VPWR08 GND GND NC GND GND -12V09 NC NC NC NC NC VPWR10 GND GND NC GND GND GA011 DP10+ DP10- NC DP11+ DP11- VPWR12 GND GND GA1 GND GND MPRESENT#13 DP12+ DP12- NC DP13+ DP13- VPWR14 GND GND GA2 GND GND MSDA15 DP14+ DP14- NC DP15+ DP15- VPWR16 GND GND MVMRO GND GND MSCL17 DP16+ DP16- NC DP17+ DP17- NC18 GND GND NC GND GND NC19 REFCLK + REFCLK- NC PCIE_WAKE PCIE_ROOT NCNotes:VPWR = 5.0VJTAG Connections pulled high to inactive state and TDI is connected to TDO.For signal definitions, see VITA42.0, VITA42.2 (Serial Rapid IO) or VITA42.3 (PCI-Express)3.12 P11, P21, P12, P22 PMC ConnectorsPn1/Jn1 32 Bit PCI Pn2/Jn2 32 Bit PCIPin Signal Signal Pin Pin Signal Signal Pin1 TCK -12V2 1 +12V TRST# 23 Ground INTA#4 3 TMS TDO 45 INTB# INTC#6 5 TDI Ground 67 BUSMODE1# +5V 8 7 Ground NC 89 INTD# NC 10 9 NC NC 1011 Ground NC 12 11 BUSMODE2# +3.3V 1213 CLK Ground 14 13 RST# BUSMODE3# 1415 Ground GNT# 16 15 3.3V BUSMODE4# 1617 REQ# +5V 18 17 PME# Ground 1819 V(I/O) AD[31] 20 19 AD[30] AD[29] 2021 AD[28] AD[27] 22 21 Ground AD[26] 2223 AD[25] Ground 24 23 AD[24] +3.3V 2425 Ground C/BE[3]# 26 25 IDSEL AD[23] 2627 AD[22] AD[21] 28 27 +3.3V AD[20] 2829 AD[19] +5V 30 29 AD[18] Ground 3031 V(I/O) AD[17] 32 31 AD[16] C/BE[2]# 3233 FRAME# Ground 34 33 Ground IDSELB 3435 Ground IRDY# 36 35 TRDY# +3.3V 3637 DEVSEL# +5V 38 37 Ground STOP# 3839 PCIXCAP LOCK# 40 39 PERR# Ground 4041 NC NC 42 41 +3.3V SERR# 4243 PAR Ground 44 43 C/BE[1]# Ground 4445 V(I/O) AD[15] 46 45 AD[14] AD[13] 4647 AD[12] AD[11] 48 47 M66EN AD[10] 4849 AD[09] +5V 50 49 AD[08] +3.3V 5051 Ground C/BE[0]# 52 51 AD[07] REQB# 5253 AD[06] AD[05] 54 53 +3.3V GNTB# 5455 AD[04] Ground 56 55 NC Ground 5657 (I/O) AD[03] 58 57 NC NC 5859 AD[02] AD[01] 60 59 Ground NC 6061 AD[00] +5V 62 61 ACK64# +3.3V 6263 Ground REQ64# 64 63 Ground MONARCH# 64Notes:V(I/O) = 3.3VFor signal definitions, see IEEE Std 1386-20013.13P13, P23, P14, P24 PMC ConnectorsPn3/Jn3 64 Bit PCI Pn4/Jn4 User Defined I/O Pin Signal Signal Pin Pin Signal Signal Pin1 NC Ground2 1 I/O I/O 23 Ground C/BE[7]#4 3 I/O I/O 45 C/BE[6]# C/BE[5]#6 5 I/O I/O 67 C/BE[4]# Ground 8 7 I/O I/O 89 V(I/O) PAR64 10 9 I/O I/O 1011 AD[63] AD[62] 12 11 I/O I/O 1213 AD[61] Ground 14 13 I/O I/O 1415 Ground AD[60] 16 15 I/O I/O 1617 AD[59] AD[58] 18 17 I/O I/O 1819 AD[57] Ground 20 19 I/O I/O 2021 V(I/O) AD[56] 22 21 I/O I/O 2223 AD[55] AD[54] 24 23 I/O I/O 2425 AD[53] Ground 26 25 I/O I/O 2627 Ground AD[52] 28 27 I/O I/O 2829 AD[51] AD[50] 30 29 I/O I/O 3031 AD[49] Ground 32 31 I/O I/O 3233 Ground AD[48] 34 33 I/O I/O 3435 AD[47] AD[46] 36 35 I/O I/O 3637 AD[45] Ground 38 37 I/O I/O 3839 V(I/O) AD[44] 40 39 I/O I/O 4041 AD[43] AD[42] 42 41 I/O I/O 4243 AD[41] Ground 44 43 I/O I/O 4445 Ground AD[40] 46 45 I/O I/O 4647 AD[39] AD[38] 48 47 I/O I/O 4849 AD[37] Ground 50 49 I/O I/O 5051 Ground AD[36] 52 51 I/O I/O 5253 AD[35] AD[34] 54 53 I/O I/O 5455 AD[33] Ground 56 55 I/O I/O 5657 V(I/O) AD[32] 58 58 I/O I/O 5859 NC NC 60 59 I/O I/O 6061 NC Ground 62 61 I/O I/O 6263 Ground NC 64 63 I/O I/O 64Notes:V(I/O) = 3.3VFor signal definitions, see IEEE Std 1386-2001Revision HistoryDate Rev CommentNov-2007 1.0 Initial releaseJun – 2008 1.1 Added JP4 InformationAug – 2008 1.2 Section 3.3Recommendation to install JP4 unless different powersupplies are used in the system.Section 3.10Updated J5 Header table to clarify connections to Pn4 andpairing of differential signals.Jun – 2009 1.3 Fixed LED Definitions。

发泡剂偶氮二甲酰胺(ADC)采购)规范

发泡剂ADC (偶氮二甲酰胺)采购(检验)规范编号:CGG095–20041.适用范围:本规范适用于发泡剂ADC (偶氮二甲酰胺)的采购(检验)。

2.采用标准:HG/T2097-913.技术要求3.1商品名称:发泡剂ADC,又名发泡剂AC。

化学名称:偶氮二甲酰胺相对分子量:116(1987年国际原子量)分子式:C2H4O2N43.2技术要求必须符合下表规定。

4.1发泡剂ADC必须从评审合格的供方采购。

4.2从未评审的供方采购必须经部门主管领导审批。

5.检验规则5.1每批发泡剂ADC必须附有合格证,供方应提供合格试验报告。

5.2产品检验按第3条进行。

5.3一次采购总量为一批,每批取样的数量为3包,用取样管在桶(袋)的上、中、下三部位各取等量试样,将取出的试样混合均匀,用四分法缩分至约300g,装入洁净、干燥、带磨口塞的广口瓶中,瓶上粘贴标签,供检验用。

5.4产品检验如不符合本规范要求时,则应由未经试验的发泡剂ADC中任取双倍数量的试样对不合格项目进行复检,如复检仍不合格,则该批发泡剂ADC为不合格品。

但必须在到货后两个月内提出异议。

如使用单位因保管、使用不当等原因造成产品质量下降不得提出异议。

供需双方如发生争议,则由质量仲裁单位按本规范进行检验。

5.5对于我公司目前不能检验的项目,由供方提供证明该项合格的试验报告,我公司进行认可。

每年结合供方评审,取样到供方进行监督检测。

6.试验方法:按照GB3778-94原文版规定的标准方法进行。

7.包装、标志、运输和贮存7.1发泡剂ADC用编织袋内衬两层塑料袋或纤维桶或木桶,内衬塑料袋包装,每件(桶)净重为20±0.20kg。

或依双方协商。

7.2包装容器应于明显部位注明:产品的名称、级别、净重、生产厂(公司)名称、生产日期或生产批号等标志。

7.3货袋(桶)应贮存在干燥的库房内,离墙壁的距离应不小于0.5m,不应放置于上下水道或暖气设备近旁,以防潮湿或变质,更不能靠近火源。

ADC工作原理PPT优秀课件

一:ADC介绍

12位ADC是一种逐次逼近型模拟数字转换器。它 有多达18个通道,可测量16个外部和2个内部信号源。 各通道的A/D转换可以单次、连续、扫描或间断模式 执行。ADC的结果可以左对齐或右对齐方式存储在16 位数据寄存器中。模拟看门狗特性允许应用程序检测 输入电压是否超出用户定义的高/低阀值。ADC 的输 入时钟不得超过14MHz,它是由PCLK2经分频产生。

通过设置ADC_CR2寄存器的CAL位启动校准。一旦校准结 束,CAL位被硬件复位,可以开始正常转换。建议在上电时执 行一次ADC校准。校准阶段结束后,校准码储存在ADC_DR 中。

注意: 1 建议在每次上电后执行一次校准。 2 启动校准前,ADC必须处于关电状态(ADON=’0’)超

过至少两个ADC时钟周期。

● 如果一个注入通道被转换: ─ 转换数据被储存在16位的ADC_DRJ1寄存器中 ─ JEOC(注入转换结束)标志被设置 ─ 如果设置了JEOCIE位,则产生中断。然后ADC停止。

普中STM32开发板带您进入ARM世界

五:连续转换模式

在连续转换模式中,当前面ADC转换一结束马上就启动另一次 转换。此模式可通过外部触发启动或通过设置ADC_CR2寄存器上的 ADON位启动,此时CONT位是1。

● 规则组由多达16个转换组成。规则通道和它们的转换顺序在 ADC_SQRx寄存器中选择。规则组中转换的总数应写入ADC_SQR1寄存器的 L[3:0]位中。

● 注入组由多达4个转换组成。注入通道和它们的转换顺序在 ADC_JSQR寄存器中选择。注入组里的转换总数目应写入ADC_JSQR寄存器的 L[1:0]位中。

普中STM32开发板带您进入ARM世界

ADC种类及参数选择

ADC的分类特性和参数选择尽管A/D转换器的种类很多,但目前广泛应用的主要有:逐次逼近式A/D转换器、双积分式A/D转换器、V/F变换式A/D转换器,新型的Σ—Δ型A/D转换器。

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。

SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。

这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法.所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。

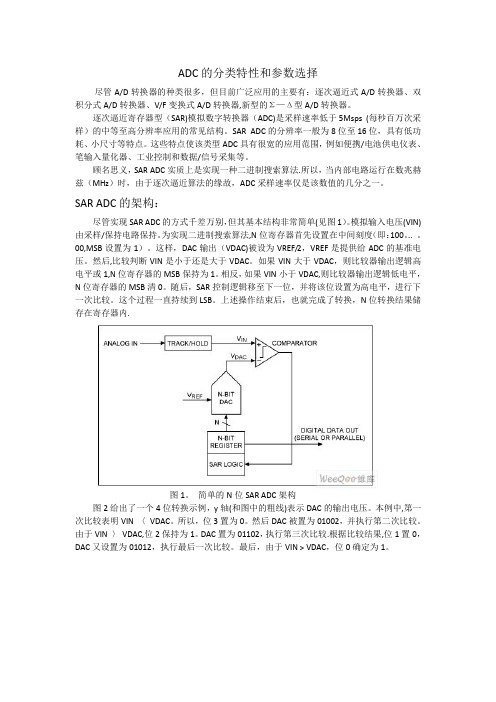

SAR ADC的架构:尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100。

.. 。

00,MSB设置为1)。

这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。

然后,比较判断VIN是小于还是大于VDAC。

如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。

上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内.图1。

简单的N位SAR ADC架构图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明VIN 〈VDAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于VIN 〉VDAC,位2保持为1。

DAC置为01102,执行第三次比较.根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

恩智浦半导体S32K1xx汽车微控制器ADC指南、规格和配置说明书

恩智浦半导体文档编号:AN12217 应用笔记第0版,2018年8月S32K1xx ADC 指南、规格和配置作者:恩智浦半导体1. 简介NXP S32K1xx 汽车微控制器具有 12 位逐次逼近模数转换器(SAR ADC),可用于模拟输入信号的采集和数字化。

本应用笔记提供了有关以下基本主题的信息,便于从ADC模块的使用中获得最大收益:-理解 ADC 常用术语、误差来源和规格。

-提高测量精度的最佳做法。

-S32K1xx 系列的常见触发配置示例。

目录作者:恩智浦半导体 (1)1. 简介 (1)2. ADC 概念、误差源和规格 (2)2.1. ADC 基本概念 (2)2.2. ADC测量中的误差来源 (3)2.3. S32K1xx ADC 规格 (5)3. 提高准确性的最佳措施 (8)4. ADC 触发模式示例 (10)4.1. 软件触发 (11)4.2. PDB 触发器 (11)4.3. 背靠背模式下的 PDB 触发器 (13)4.4. TRGMUX 触发器 (14)5. 参考资料 (16)附录A. 示例代码:ADC 软件触发 (17)附录B. 示例代码:带有 PDB 触发器的 ADC (19)附录 C. 示例代码:带有 PDB 和背靠背触发器的 ADC .. 21S32K1xx ADC 指南、规格和配置,第0版,2018年8月2恩智浦半导体2. ADC 概念、误差源和规格本节解释了用于表征 ADC 的概念和术语以及潜在的误差源,并提供了S32K1xx 系列数据表中的规范参数。

2.1. ADC 基本概念分辨率:ADC 数字输出中代表模拟输入信号的位数。

对于 S32K1xx 系列,分辨率可配置为 8、10 或 12 位。

参考电压:ADC 需要一个参考电压,用于与模拟输入进行逐次近似比较,以产生数字输出。

数字输出是模拟输入相对于该参考电压的比率。

VREF = VREFH – VREFL 其中:VREFH = 高参考电压 VREFL = 低参考电压ADC 输出公式:ADC 的转换公式用于计算特定模拟输入电压对应的数字输出。

DS-2DY7432IXG-XY 7寸4 MP 32X DarkFighter 爆破网络 ATEx

DS-2DY7432IXG-XY7-inch 4 MP 32X DarkFighter Explosion NetworkATEx:II 2 G Ex db IIC T6 GbII 2 D Ex tb IIIC T80°C Db IECEx:Ex db IIC T6 Gb Ex tb IIIC T80°C Db⏹1/1.8" progressive scan CMOS⏹Up to 2560 × 1440 @30 fps resolution⏹Min. illumination:Color: 0.005 Lux @(F1.5, AGC ON), B/W:0.001 Lux @(F1.5, AGC ON), 0 Lux with IR⏹32 × optical zoom, 16 × digital zoom⏹120 dB WDR, HLC, BLC, 3D DNR, Defog, EIS, Regional Exposure, Regional Focus⏹Up to 100 m IR distance⏹Support H.265+/H.265 video compressionSpecificationCameraImage Sensor 1/1.8" progressive scan CMOSMax. Resolution 2560 × 1440Min. Illumination color: 0.005 Lux @ (F1.5, AGC ON), B/W: 0.001 Lux @ (F1.5, AGC ON), 0 Lux with IR Shutter Speed 1/1 s to 1/30000 sDay &Night ICRZoom 32 × optical, 16 × digitalSlow Shutter yesLensFocal Length 5.9 to 188.8 mm, 32 × opticalFOV Horizontal field of view: 60.2° to 2.5° (wide-tele) Vertical field of view: 35.2° to 1.3° (wide-tele) Diagonal field of view: 67.4° to 2.7° (wide-tele)Focus Auto/Semi-automatic/Manual Aperture F1.5Zoom Speed approx. 7 sIlluminatorSupplement Light Type IRSupplement Light Range 100 mSmart Supplement Light yesIR Wavelength 850 nmPTZMovement Range (Pan) 360° endlessMovement Range (Tilt) From -90° to 90° (auto-flip)Pan Speed Configurable, from 0.1°/s to 25°/s, Preset speed: 25°/sTilt Speed Configurable, from 0.1°/s to 15°/s Preset Speed: 15°/sProportional Pan yesPresets 300Preset Freezing yesPatrol Scan 8 patrols, up to 32 presets for each patrolPattern Scan 4 pattern scans, record time over 10 minutes for each scanPark Action Preset/Pattern Scan/Patrol Scan/Auto Scan/Tilt Scan/Random Scan/Frame Scan/Panorama Scan3D Positioning yes PTZ Status Display yesScheduled Task Preset/Pattern Scan/Patrol Scan/Auto Scan/Tilt Scan/Random Scan/Frame Scan/Panorama Scan/Dome Reboot/Dome Adjust/Aux OutputPower-off Memory yes VideoMain Stream 50 Hz: 25 fps (2560 × 1440, 1920 × 1080, 1280 × 960, 1280 × 720) 60 Hz: 30 fps (2560 × 1440, 1920 × 1080, 1280 × 960, 1280 × 720)Sub-Stream 50 Hz: 25 fps (704 × 576, 640 × 480, 352 × 288) 60 Hz: 30 fps (704 × 480, 640 × 480, 352 × 240)Third Stream 50 Hz: 25 fps (1920 × 1080, 1280 × 960, 1280 × 720, 704 × 576, 640 × 480, 352 × 288) 60 Hz: 30 fps (1920 × 1080, 1280 × 960, 1280 × 720, 704 × 480, 640 × 480, 352 × 240)Video Compression Main Stream: H.265+/H.265/H.264+/H.264 Sub-stream: H.265/H.264/MJPEGThird Stream: H.265/H.264/MJPEGVideo Bit Rate 32 Kbps to 16384 KbpsH.264 Type Baseline Profile/Main Profile/High ProfileH.265 Type Main ProfileScalable Video Coding (SVC) SupportRegion of Interest (ROI) 8 fixed regions for each streamAudioAudio Compression G.711alaw, G.711ulaw, G.722.1, G.726, MP2L2, PCMAudio Bit Rate 64 Kbps (G.711)/16 Kbps (G.722.1)/16 Kbps (G.726)/32-192 Kbps (MP2L2) Audio Sampling Rate 8 kHz/16 kHz/32 kHz/48 kHzEnvironment Noise Filtering yesNetworkProtocols IPv4/IPv6, HTTP, HTTPS, 802.1x, QoS, FTP, SMTP, UPnP, SNMP, DNS, DDNS, NTP, RTSP, RTCP, RTP, TCP/IP, UDP, IGMP, ICMP, DHCP, PPPoE, BonjourSimultaneous Live View Up to 20 channelsAPI Open Network Video Interface (Version 19.12, Profile S, Profile G, Profile T), ISAPI, SDK, ISUPSmooth Streaming yesUser/Host Up to 32 users, 3 user levels: administrator, operator, and userSecurity Password protection, complicated password, HTTPS encryption, 802.1X authentication (EAP-TLS, EAP-LEAP, EAP-MD5), watermark, IP address filter, basic and digest authentication for HTTP/HTTPS, RTP/RTSP over HTTPS, control timeout settings, security audit log, TLS 1.2, TLS 1.3, host authentication (MAC address)Network Storage NAS (NFS, SMB/CIFS), auto network replenishment (ANR) Client iVMS-4200, HikCentral Pro, Hik-ConnectWeb Browser IE11, Chrome 57+, Firefox 52+, Safari 11+ImageImage Parameters Switch yesImage Settings Saturation, brightness, contrast, sharpness, gain, and white balance adjustable by client software or web browserDay/Night Switch autoWide Dynamic Range (WDR) 120 dB WDRSNR ≥52 dBDefog Optical defogImage Enhancement HLC/BLC/3D DNR/Defog/EIS/Regional Exposure/Regional FocusPrivacy Mask 24 programmable polygon privacy masks, mask color or mosaic configurable InterfaceEthernet Interface 1 RJ45 10 M/100 M EthernetOn-board Storage support microSD/microSDHC/microSDXC cards, up to 256 GBAudio 1-ch audio input and 1-ch audio outputAlarm 7-ch alarm input and 2-ch alarm outputEventBasic Event Motion detection, video tampering alarm, exception, alarm input and outputSmart Event Line crossing detection, intrusion detection, region entrance detection, region exiting detection, unattended baggage detection, object removal detection, audio exception detectionAlarm Linkage Manual tracking, Event trackingSmart Tracking Upload to FTP/NAS/memory card, notify surveillance center, send email, trigger alarm output, trigger recording, and PTZ actions (such as preset, patrol scan, pattern scan)Deep Learning FunctionFace Capture 1. Detects up to 10 faces simultaneously2. Uploads face with background and closed-up face pictures3. Support detecting, tracking, capturing, grading, selecting of face in motion, and output the best face picture of the faceGeneralPower 100 VAC to 240 VACMax.110 W (Max. 15 W for IR)Dimension 369.1 mm × 219.9 mm ×434.5 mm (14.5" × 8.7" × 17.1") Weight Approx. 24.5 kg (53.9 lb.)Material SUS316L with anti-corrosion surface spray treatment Operating Condition -40°C to 60°C (-40°F to 140°F),Working Humidity≤ 95%General Function Anti-flicker, heartbeat, mirror, flash log, password reset via e-mail, pixel counter, password protection, one-key reset, three streamsWiper yes ApprovalEMC FCC (47 CFR Part 15, Subpart B); CE-EMC (EN 55032: 2015, EN 61000-3-2: 2014, EN 61000-3-3: 2013, EN 50130-4: 2011 +A1: 2014); RCM (AS/NZS CISPR 32: 2015); IC (ICES-003: Issue 6, 2016); KC (KN 32: 2015, KN 35: 2015)Safety UL (UL 62368-1);CB (IEC 60950-1:2005 + Am 1:2009 + Am 2:2013); CE-LVD (EN 62368-1:2014+A11:2017);BIS (IS 13252 (Part 1):2010+A1:2013+A2:2015); LOA (IEC/EN 60950-1)Environment CE-RoHS (2011/65/EU); WEEE (2012/19/EU); Reach (Regulation (EC) No 1907/2006)Protection IP68, TVS 6000V Lightning Protection, Surge Protection and Voltage Transient ProtectionExplosion-Proof Protection Ex-mark: ATEX: Ex II 2GD Ex db IIC T6 Gb /Ex tb IIIC T80℃Db; IECEx: Ex db IIC T6 Gb /Ex tb IIIC T80℃DbDORIThe DORI (detect, observe, recognize, identify) distance gives the general idea of the camera ability to distinguish persons or objects within its field of view. It is calculated based on the camera sensor specification and the criteria given by EN 62676-4: 2015.DORI Detect Observe Recognize IdentifyDefinition25 px/m63 px/m125 px/m250 px/mDistance (Tele) 1855.2 m (6085.06 ft) 736.2 m (2414.74 ft) 371 m (1216.88 ft) 185.5 m (608.44 ft)⏹Dimension⏹Accessory⏹Included⏹Available Model DS-2DY7432IXG-XYDS-1677ZJ-XS-1.0(D)OthersOptionalDS-2780ZJ-X(OS)(O-STD)/316LJunction Box。

ADC分类及参数