示波器前级程控放大与数据采集存储电路

2007年全国大学生电子设计竞赛一等奖作品——数字示波器

2007年全国大学生电子设计竞赛一等奖作品——数字示波器发布时间: 2007-11-27 20:28:37作者:责任编辑:数字示波器作者:黄霖宇、陈鹍、侯碧波一等奖作品摘要本数字示波器以单片机和FPGA为核心,对采样方式的选择和等效采样技术的实现进行了重点设计,使作品不仅具有实时采样方式,而且采用随机等效采样技术实现了利用实时采样速率为1MHz的ADC进行最大200MHz的等效采样。

同时系统还具有可测2mV小信号、波形存储回放、测频、触发沿选择、校准信号输出等功能。

AbstractThis digital oscilloscope takes a MCU and FPGA as the core .We made emphases on the choice of the sampling methods and the implement of equivalent sampling, as a result, our design not only has the real-time sampling mode but also can reach the highest equivalent sample rate of 200 MHz using the real-time sample rate of 1 MHz, by way of random equivalent sampling. At the same time, this system has many other functions, such as 2mV small-signal measuring, storage andre-display of waveform, measuring frequency, selective trigger edge , output of thecorrection signal and so on.一、总体方案设计1.方案比较与选择仔细分析题目要求,以实时采样速率为1MHz的ADC实现最大200MHz的等效采样,是本题的最大难点,也是设计的重点之一。

列出数字示波器的主要组成部分及其功能

数字示波器是一种广泛应用于电子测量和测试领域的仪器,它可以将电信号转换成图形显示,直观地展现电信号的波形和特征。

数字示波器由许多不同的部分组成,每个部分都扮演着不同的角色,以确保仪器的功能正常运转。

下面我们将列出数字示波器的主要组成部分及其功能:1. 输入部分输入部分是数字示波器接收外部信号的地方,主要包括以下几个部分:- 输入通道:用于连接被测电路的输入端,通常有多个通道,可以同时测量多个信号。

- 输入阻抗:不同的数字示波器可能有不同的输入阻抗选项,通常为50欧姆或1兆欧姆,以适配不同的信号源。

- 输入耦合:选择直流(DC)或交流(AC)耦合,以适应不同的测量需求。

2. 信号采集部分信号采集部分是数字示波器对输入信号进行采样和处理的地方,主要包括以下几个部分:- 采样系统:负责对输入信号进行采样,并将采样到的数据转换成数字信号。

- ADC转换器:将模拟信号转换成数字信号的核心部件,通常有不同的采样速度和分辨率可选。

3. 存储和处理部分存储和处理部分是数字示波器对采集到的信号进行存储和处理的地方,主要包括以下几个部分:- 存储系统:用于存储采集到的波形数据,通常有不同的存储深度可选。

- 处理器:负责对采集到的数据进行处理和分析,通常有不同的处理速度和功能可选。

4. 显示部分显示部分是数字示波器将处理后的信号转换成图形显示的地方,主要包括以下几个部分:- 显示屏幕:用于显示波形图像和测量结果,通常有不同的尺寸和分辨率可选。

- 控制面板:用于操作数字示波器的各项功能和参数设定,通常包括旋钮、按钮和触摸屏等操作元件。

5. 校准和校验部分校准和校验部分是数字示波器保证测量准确性和稳定性的地方,主要包括以下几个部分:- 校准电路:用于校准示波器的各个部分,保证测量结果的准确性。

- 自校准功能:一些数字示波器内置了自动校准功能,可以定期对示波器进行自校准,保证测量结果的稳定性。

通过以上列出的数字示波器的主要组成部分及其功能,可以看出数字示波器是一个高度复杂的仪器,由多个部件共同协作完成对电信号的测量和分析。

示波器的采样率和存储深度

示波器的采样率和存储深度在选择示波器时,工程师首先需要确定测量所需的带宽。

然而当示波器的带宽确定后,影响实际测量的恰恰是相互作用、相互制约的采样率和存储深度。

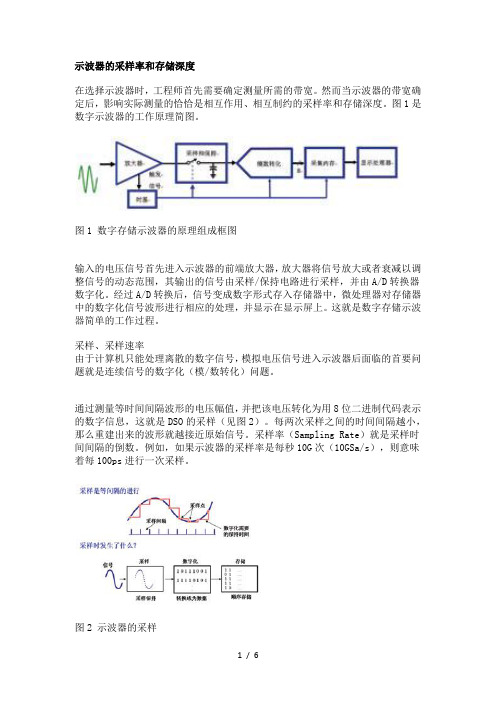

图1是数字示波器的工作原理简图。

图1 数字存储示波器的原理组成框图输入的电压信号首先进入示波器的前端放大器,放大器将信号放大或者衰减以调整信号的动态范围,其输出的信号由采样/保持电路进行采样,并由A/D转换器数字化。

经过A/D转换后,信号变成数字形式存入存储器中,微处理器对存储器中的数字化信号波形进行相应的处理,并显示在显示屏上。

这就是数字存储示波器简单的工作过程。

采样、采样速率由于计算机只能处理离散的数字信号,模拟电压信号进入示波器后面临的首要问题就是连续信号的数字化(模/数转化)问题。

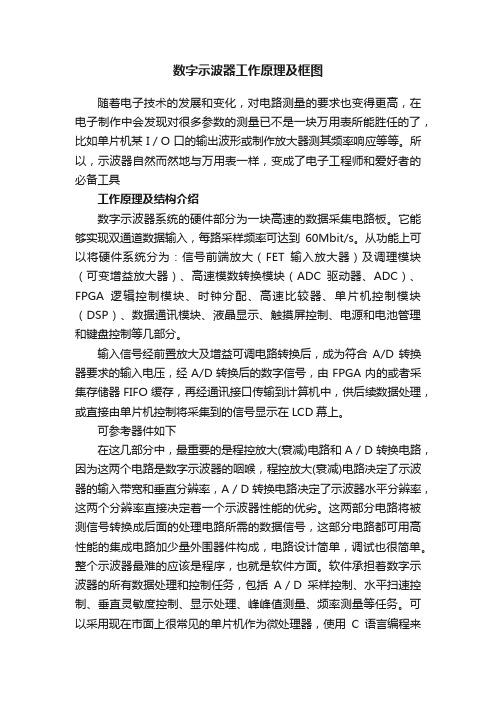

通过测量等时间间隔波形的电压幅值,并把该电压转化为用8位二进制代码表示的数字信息,这就是DSO的采样(见图2)。

每两次采样之间的时间间隔越小,那么重建出来的波形就越接近原始信号。

采样率(Sampling Rate)就是采样时间间隔的倒数。

例如,如果示波器的采样率是每秒10G次(10GSa/s),则意味着每100ps进行一次采样。

图2 示波器的采样根据Nyquist采样定理,对于正弦波,每个周期至少需要两次以上的采样才能保证数字化后的脉冲序列能较为准确的还原原始波形。

如果采样率低于Nyquist采样率则会导致混叠(Aliasing)现象。

由Nyquist定理知道对于最大采样率为10GSa/s的示波器,可以测量最高频率为5GHz的信号,即采样率的一半,这就是示波器的数字带宽,而这个带宽是DSO的上限频率,实际带宽是不可能达到这个值的,数字带宽是从理论上推导出来的,是DSO带宽的理论值。

与我们经常提到的示波器带宽(模拟带宽)是完全不同的两个概念。

那么在实际的测量中,对确定的示波器带宽,采样率到底选取多大?通常还与示波器所采用的采样模式有关。

采样模式采样技术大体上分为两类:实时模式和等效时间模式。

数字示波器工作原理及框图

数字示波器工作原理及框图随着电子技术的发展和变化,对电路测量的要求也变得更高,在电子制作中会发现对很多参数的测量已不是一块万用表所能胜任的了,比如单片机某I/O口的输出波形或制作放大器测其频率响应等等。

所以,示波器自然而然地与万用表一样,变成了电子工程师和爱好者的必备工具工作原理及结构介绍数字示波器系统的硬件部分为一块高速的数据采集电路板。

它能够实现双通道数据输入,每路采样频率可达到60Mbit/s。

从功能上可以将硬件系统分为:信号前端放大(FET输入放大器)及调理模块(可变增益放大器)、高速模数转换模块(ADC驱动器、ADC)、FPGA逻辑控制模块、时钟分配、高速比较器、单片机控制模块(DSP)、数据通讯模块、液晶显示、触摸屏控制、电源和电池管理和键盘控制等几部分。

输入信号经前置放大及增益可调电路转换后,成为符合A/D转换器要求的输入电压,经A/D转换后的数字信号,由FPGA内的或者采集存储器FIFO缓存,再经通讯接口传输到计算机中,供后续数据处理,或直接由单片机控制将采集到的信号显示在LCD幕上。

可参考器件如下在这几部分中,最重要的是程控放大(衰减)电路和A/D转换电路,因为这两个电路是数字示波器的咽喉,程控放大(衰减)电路决定了示波器的输入带宽和垂直分辨率,A/D转换电路决定了示波器水平分辨率,这两个分辨率直接决定着一个示波器性能的优劣。

这两部分电路将被测信号转换成后面的处理电路所需的数据信号,这部分电路都可用高性能的集成电路加少量外围器件构成,电路设计简单,调试也很简单。

整个示波器最难的应该是程序,也就是软件方面。

软件承担着数字示波器的所有数据处理和控制任务,包括A/D采样控制、水平扫速控制、垂直灵敏度控制、显示处理、峰峰值测量、频率测量等任务。

可以采用现在市面上很常见的单片机作为微处理器,使用C语言编程来实现。

程控放大(衰减)电路与电源电路信号由常见的X10X1示波器探头输入,进入放大(衰减)电路。

简易数字存储示波器

简易数字存储示波器摘要本简易数字存储示波器由信号输入电路、数据采集与存储电路、A/D与转D/A换电路以及AT89C51单片机系统组成。

本仪器利用软件的强大功能,配合普通示波器可以实现任意波形输入信号的单次触发存储显示、存储回放,并按要求进行了扫描速度和垂直灵敏度的档位设置,波形显示无明显失真。

关键词:简易采集存储单片机转换电路一、方案设计与比较论证数字存储示波器的一般设计原理是:先用A/D转换器将被测信号数字化,并写入数字存储器,在需要显示时,再从存储器中读出,经过D/A转换器还原为模拟信号,送到示波器的相应输入口。

1.模拟通道:系统需要对模拟信号的实时采集存储,模拟通道的性能直接影响系统的性能。

方案一:利用集成放大器AD524组成模拟通道。

考虑到本题目的要求,垂直灵敏度的档位不是很多。

可以利用AD公司生产的AD524,其组成的差分放大器,外电路简单,可以实现本题要求,但其价格非常高,用在此处性价比不是太高,所以不采用此电路。

方案二:利用模拟开关和运算放大器组成增益可控的放大器,这样可以较为方便的控制增益,可以利用较少的级数达到较好的要求,这样有利于减少误差便于逐级累加。

本电路采用常用集成电路,电路非常成熟,性价比高,所以本电路采用了该方案。

2、控制模块方案论证方案一:采用大规模可编程逻辑器件作为系统的控制核心。

目前,大规模可编程逻辑器件容量不断增大,速度不断提高,且多具有ISP 功能,也可以在不改变硬件电路的情况下改变功能。

但其对数据的采集速率要求较高,对数据的处理相对较弱,必须使用高速大规模可编程逻辑器件作为控制核心。

普通的可编程逻辑器件难以满足对采样速率的要求。

高速可编程逻辑器件时钟频率不过几十兆,其价格昂贵,普及程度不高。

考虑到以上因素,没有采用此方案方案二:利用现在较为流行的单片机控制高速A/D转换器和RAM实现高速数据采集。

单片机虽速度不是特别快,但使用较少的外围器件就可以实现复杂的逻辑和时序控制功能,是较为理想的方案,所以本电路采用该方案。

数据采集电路和简易存储示波器设计

数据采集电路和简易存储示波器设计一、实验目的掌握LPM RAM模块VHDL元件定制、调用和使用方法;熟悉A/D和D/A与FPGA 接口电路设计;了解HDL文本描述与原理图混合设计使用方法。

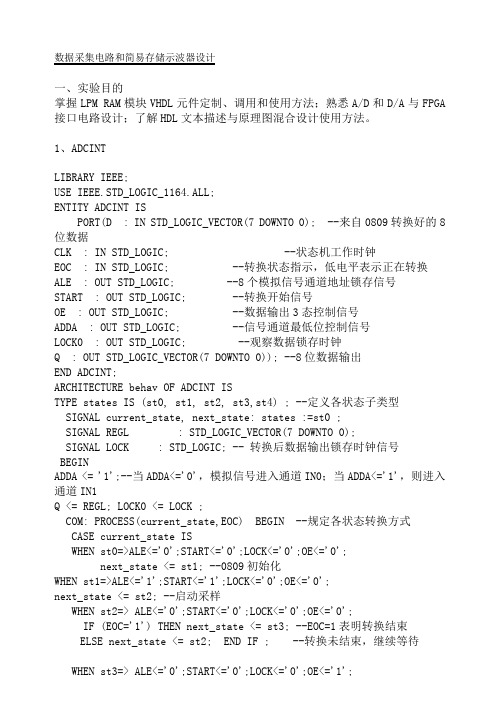

1、ADCINTLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADCINT ISPORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --来自0809转换好的8位数据CLK : IN STD_LOGIC; --状态机工作时钟EOC : IN STD_LOGIC; --转换状态指示,低电平表示正在转换ALE : OUT STD_LOGIC; --8个模拟信号通道地址锁存信号START : OUT STD_LOGIC; --转换开始信号OE : OUT STD_LOGIC; --数据输出3态控制信号ADDA : OUT STD_LOGIC; --信号通道最低位控制信号LOCK0 : OUT STD_LOGIC; --观察数据锁存时钟Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出END ADCINT;ARCHITECTURE behav OF ADCINT ISTYPE states IS (st0, st1, st2, st3,st4) ; --定义各状态子类型SIGNAL current_state, next_state: states :=st0 ;SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号BEGINADDA <= '1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1Q <= REGL; LOCK0 <= LOCK ;COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式CASE current_state ISWHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0';next_state <= st1; --0809初始化WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0';next_state <= st2; --启动采样WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0';IF (EOC='1') THEN next_state <= st3; --EOC=1表明转换结束 ELSE next_state <= st2; END IF ; --转换未结束,继续等待WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1';next_state <= st4;--开启OE,输出转换好的数据WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1'; next_state <= st0;WHEN OTHERS => next_state <= st0;END CASE ;END PROCESS COM ;REG: PROCESS (CLK)BEGINIF (CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF; END PROCESS REG ;-- 由信号current_state将当前状态值带出此进程:REG LATCH1: PROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL <= D ; END IF;END PROCESS LATCH1 ;END behav;编译无误后,生成元件:2、CNT10BLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10B ISPORT (LOCK0,CLR : IN STD_LOGIC;CLK : IN STD_LOGIC;WE : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(8 DOWNTO 0);CLKOUT : OUT STD_LOGIC );END CNT10B;ARCHITECTURE behav OF CNT10B ISSIGNAL CQI : STD_LOGIC_VECTOR(8 DOWNTO 0);SIGNAL CLK0 : STD_LOGIC;BEGINCLK0 <= LOCK0 WHEN WE='1' ELSECLK;PROCESS(CLK0,CLR,CQI)BEGINIF CLR = '1' THEN CQI <= "000000000";ELSIF CLK0'EVENT AND CLK0 = '1' THEN CQI <= CQI + 1; END IF; END PROCESS;DOUT <= CQI; CLKOUT <= CLK0;END behav;编译无误后,生成元件:3、定制LPM RAM4、调用以上三个元件,绘制电路图5、编译无误后,仿真6、配置引脚7、再次编译后,下载配置文件。

数字存储示波器工作原理

数字存储示波器工作原理

数字存储示波器是一种电子测量仪器,用于观测和分析电信号的波形。

它的工作原理可分为三个主要部分:输入信号采样、信号转换与存储、波形显示。

输入信号采样:数字存储示波器通过探头将待测信号引入仪器内部。

信号首先经过一个模拟开关,使得信号可以以高速模拟的方式进入示波器的内部电路。

然后信号经过一系列预处理电路,如放大、滤波等,以适应后续的数字处理需求。

信号转换与存储:经过预处理后,信号被转换成数字形式。

示波器内部包含一种称为模数转换器的芯片,它将连续的模拟信号转换为离散的数字信号。

模数转换器以一定的速率对输入信号进行采样,并将每个采样点的电压值转换为对应的数字值,通常采用二进制表示。

转换后的数字信号被存储在示波器的内存中。

示波器通常具有一定的存储容量,可以存储多个波形周期的信号数据。

存储器的速度和容量决定了示波器能持续采集和存储的信号时间长度。

波形显示:一旦信号采样和存储完成,示波器就可以根据需求将存储的数据进行处理和显示。

示波器内部有一个显示器,可以将数字信号转换为可见的波形。

示波器通过将数字信号转换为模拟信号,然后通过屏幕进行显示,以呈现出信号的波形特征。

数字存储示波器的工作原理基于模数转换技术和数字处理能力,

相比传统的模拟示波器,它具有更高的测量精度、灵活的信号处理功能和便捷的数据存储与读取能力。

这使得数字存储示波器成为现代电子测量领域中不可或缺的重要工具。

示波器信号前级处理

示波器信号前级处理0052018摘要由交直流耦合选择、电压衰减、高阻隔离放大、程控放大、电压偏移等组成的信号调理部分的功能是将各种幅值的被测信号按照确定比例,转换到A/D可处理的电压之内. 光耦继电器作为选择直流耦合或者交流耦合的开关.采用阻容分压将电压衰减1/50, .程控增益放大电路增益范围在0~40dB之间,偏移电路将交流信号抬升为AD可以测量的直流信号,关键字:交直流耦合;程控放大;光耦继电器一.方案论证与比较信号调理部分的功能是将各种幅值的被测信号按照确定比例,转换到A/D可处理的电压之内.主要有交直流耦合选择、电压衰减、高阻隔离放大、程控放大、电压偏移等组成。

1.开关的选择:方案一:74HC4051是一款高速CMOS器件,引脚兼容低功耗肖特基TTL(LSTTL)系列.74HC4051是8通道模拟多路选择器/多路分配器,带有3个数字选择端,1个低有效使能端,8个独立输入/输出端和1个公共输入/输出端.具有速度高、价格便宜、寿命长的优点.但是导通电阻大(约几十Ω),不宜作为输入信号通道的开关.在这里我们用它作为TL431输出的电压基准的分配开关,使用单片机可方便的控制通道的切换.方案二:光耦继电器是用光耦来控制开关状态的固态继电器,无机械触点,使用寿命长,安静环保防震抗摔,体积小,安全可靠,高速切换,低放电电压,低动作电流,输入输出间完全绝缘,可控制各种负载.NAIS公司的光耦继电器210EH导通电阻R=20Ω,可以作为选择直流耦合或者交流耦合的开关.DS方案三:普通继电器可以实现电气隔离,可靠导通.但是开关动作慢,体积大,寿命有限,不宜作为频繁开断的开关.SRS-05VDC-SL耐压250VAC、30VDC,耐流3A,导通时导通电阻接近为零,可以作为衰减倍数选择的开关.方案四:干簧继电器主要由干式舌簧片与励磁线圈组成。

干式舌簧片(触点)是密封的,由铁镍合金做成,舌片的接触部分通常镀有贵重金属(如金、铑、钯等),接触良好,具有优良的导电性能。

示波器的相关使用介绍

示波器的相关使用介绍示波器是一种用于观察和分析电信号的仪器,广泛应用于电子、通信、计算机、医疗等领域。

它具有显示电压信号波形、测量电信号参数、分析电路运行状态等功能,为电子工程师和技术人员提供了便捷的测试工具。

本文将详细介绍示波器的使用方法和功能。

一、示波器的基本原理:示波器基于示波管原理工作,将电压信号转换为可视的波形展示在屏幕上。

示波器通常包括前置放大器、触发电路、水平扫描电路、竖直扫描电路等部分。

当电压信号输入示波器后,前置放大器将信号放大,然后经过触发电路进行触发和同步,水平扫描电路控制水平方向的扫描速度和范围,竖直扫描电路控制垂直方向的扫描速度和灵敏度。

最终,在示波管上形成电压波形或其他信号的图形。

二、示波器的类型:1.模拟示波器:利用电子束在阴极射线管上的移动成像原理,显示连续的电压波形。

模拟示波器已经逐渐被数字示波器所替代。

2.数字示波器:以数字电子技术为基础,通过快速采样、数字处理和数字显示技术来显示和分析电压波形。

数字示波器能够显示更复杂的波形,具有更高的准确性和精度。

三、示波器的使用方法:1.连接电路:首先,将被测试的电路与示波器连接起来。

一般情况下,电压信号通过探头输入示波器,探头连接到被测电路上。

注意,选择合适的探头和电压范围以避免对被测电路造成损坏。

2.调整探头:示波器的探头一般需要调整以满足波形的观测要求。

比如,可以通过前置控制旋钮调整探头的灵敏度。

3.设置水平和竖直参数:调整示波器的水平和竖直参数,包括时间/频率、亮度、触发等参数,以获得所需的波形显示效果。

4.触发设置:示波器的触发功能可以帮助用户在波形上稳定地显示感兴趣的信号,减少噪声和干扰的影响。

通过选择合适的触发源、触发方式和触发电平,可以实现稳定和清晰的波形显示。

5.波形分析:示波器可以提供多种波形参数的测量和分析功能,包括峰值、峰峰值、平均值、周期、频率、相位等。

根据需要,可以使用示波器的自动测量功能或手动测量功能进行分析。

示波器的存储和回放功能详解

示波器的存储和回放功能详解示波器是一种常见的电子测量仪器,在电子工程、通信、嵌入式系统等领域具有广泛的应用。

它可以通过显示波形来分析和观察电信号的特征,而示波器的存储和回放功能是其中重要的特性之一。

本文将详细介绍示波器的存储和回放功能原理及其应用。

一、存储功能的原理及作用示波器的存储功能通过将采集到的电信号波形数据保存在内存中,实现对波形数据的暂存和处理。

它的原理是将输入信号经过采样和量化转换后,存储到示波器的内部或外部存储器中。

存储功能可以实现对波形数据的长期保存、重复分析和进一步处理,为后续的信号分析和故障排查提供了便利。

存储功能的作用主要有以下几个方面:1. 数据保存与共享:示波器的内存容量较大,可以存储大量的波形数据。

通过存储功能,用户可以将采集到的波形数据保存下来,方便后续的复查和共享。

同时,也可以将波形数据导出到外部存储设备或计算机中,进行更深入的分析和处理。

2. 波形观察与比较:存储功能允许用户将多个波形数据同时存储下来,并进行比较和观察。

这对于观察波形的稳定性、频谱特征等方面非常有帮助。

通过比较多组波形数据,可以更准确地判断信号的变化规律,进一步分析电路的性能。

3. 信号捕获与存储:示波器的存储功能可以将瞬态信号的瞬间变化捕获下来,并保存为波形数据。

这对于分析瞬态信号的幅值、频率等参数非常有用。

用户可以通过存储功能,捕捉到一些短暂的信号现象,以便进一步研究和分析。

二、回放功能的原理及应用示波器的回放功能是指将已存储的波形数据重新播放出来,实现对信号波形的再现。

它的原理是将存储的波形数据按照一定的速率重新读取出来,并通过显示装置呈现出来。

回放功能可以帮助用户在不再接入真实信号源的情况下,对已存储的波形数据进行再次观察和分析。

回放功能主要应用于以下几个方面:1. 故障分析与调试:当某个故障发生时,示波器的回放功能可以帮助用户将故障时的波形数据重新播放,并进行详细分析。

这对于了解故障发生的原因及其影响非常有帮助。

魏坤示波器原理

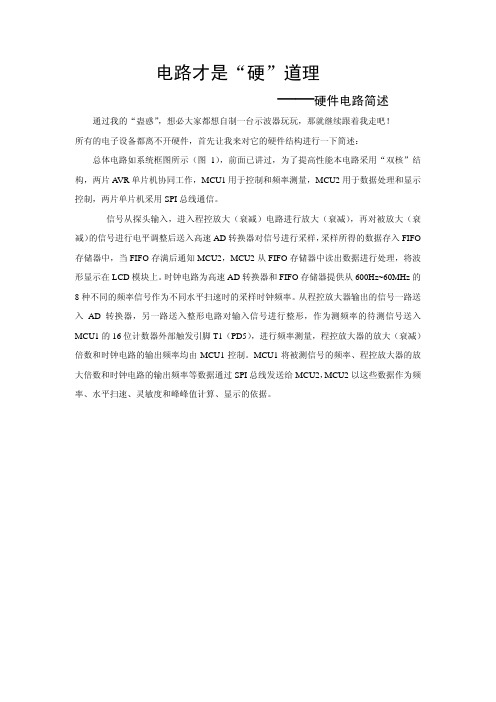

电路才是“硬”道理——硬件电路简述 通过我的“蛊惑”,想必大家都想自制一台示波器玩玩,那就继续跟着我走吧!所有的电子设备都离不开硬件,首先让我来对它的硬件结构进行一下简述: 总体电路如系统框图所示(图1),前面已讲过,为了提高性能本电路采用“双核”结构,两片A VR单片机协同工作,MCU1用于控制和频率测量,MCU2用于数据处理和显示控制,两片单片机采用SPI总线通信。

信号从探头输入,进入程控放大(衰减)电路进行放大(衰减),再对被放大(衰减)的信号进行电平调整后送入高速AD转换器对信号进行采样,采样所得的数据存入FIFO 存储器中,当FIFO存满后通知MCU2,MCU2从FIFO存储器中读出数据进行处理,将波形显示在LCD模块上。

时钟电路为高速AD转换器和FIFO存储器提供从600Hz~60MHz的8种不同的频率信号作为不同水平扫速时的采样时钟频率。

从程控放大器输出的信号一路送入AD转换器,另一路送入整形电路对输入信号进行整形,作为测频率的待测信号送入MCU1的16位计数器外部触发引脚T1(PD5),进行频率测量,程控放大器的放大(衰减)倍数和时钟电路的输出频率均由MCU1控制。

MCU1将被测信号的频率、程控放大器的放大倍数和时钟电路的输出频率等数据通过SPI总线发送给MCU2,MCU2以这些数据作为频率、水平扫速、灵敏度和峰峰值计算、显示的依据。

图1:系统框图下面就各个模块电路做以简单介绍。

1.程控放大电路和电源电路:将程控放大电路与电源电路放在一块讲,是因为他们不仅有着密切的联系,而且还是做在一块电路板上的。

程控放大器的作用是对输入信号进行衰减或放大调整,使输出信号电压在AD转换器输入电压要求范围内,达到最好的测量与观察效果,所以程控放大器电路在规定带宽内的增益一定要平坦,故对运算放大器的要求比较高,在本电路中我选用的是NSC公司生产的高速运算放大器LM6172双运放,带宽为100MHz,转换速率3000v/μs,每通道消耗电流2.3mA,输出电流可达50mA,完全满足本电路的要求,选择该芯片的另一个原因是价格,邮购价格为8元一片,相比ADI,MAX等公司几十元一片的高速运放芯片来说算是很廉价了,电源采用正负双电源供电,由于整个电路总的电源输入为单8v,所以专门用一片dc/dc电路MC34063为其构成了负压转换器再经稳压得到-5v电压,+5v通过对输入电压稳压得到。

存储示波器的工作原理

存储示波器的工作原理

示波器是一种用于观察电信号波形的仪器。

它可以将电信号转换成可见的波形,并通过光电转换器将其显示在屏幕上。

示波器的工作原理是基于信号采样和图像显示的技术。

具体来说,示波器的工作原理可以分为以下几个步骤:

1. 信号采集:示波器通过探头将待测信号与仪器连接。

探头会将电信号转换成电压信号,并传送到示波器的输入电路中。

2. 信号解调:示波器接收到输入信号后,会对信号进行放大、滤波和解调等处理。

这些处理旨在提高信号的可观测性和准确性。

3. 信号采样:示波器会对输入信号进行周期性采样。

采样过程中,示波器会在一定的时间间隔内对信号进行取样,以获取信号在不同时间点的电压数值。

4. 数字化处理:示波器会将采样到的模拟信号转换成数字信号。

这个过程一般是通过数模转换器来完成的。

数字化处理可以使示波器具备更高的分辨率和精确度。

5. 数据存储:示波器会将采样到的数字信号存储在内部存储器中,以备将来显示和分析。

6. 波形显示:示波器会将存储的数据通过光电转换器转换成可见的波形,并通过屏幕显示出来。

用户可以通过调节示波器的

触发、时间和电压尺度等参数,以获得所需的波形。

总的来说,示波器的工作原理是将输入信号转换成数字信号,并通过波形显示技术在屏幕上显示出来。

这使得用户可以直观地观察和分析电信号的波形特征,从而进行相应的研究和调试工作。

示波器使用原理

示波器使用原理介绍如下:

示波器是一种测量电压信号的仪器,它能够将电信号转换成可视化的波形,从而帮助工程师和技术人员分析和诊断电路中的问题。

示波器的使用原理主要包括信号采集、信号放大、信号显示和观测测量等方面。

信号采集是示波器使用的第一个原理。

当要测量一个电路中的电压信号时,示波器的探头会将电路中的信号引出,并将其送入示波器的输入端。

为了防止探头对电路的干扰,示波器的输入阻抗通常很高,一般在1MΩ左右。

信号放大是示波器使用的第二个原理。

一旦信号被输入到示波器中,它需要被放大,以便在示波器屏幕上显示出来。

示波器通常使用放大器来放大信号,放大器的增益通常在1到1000之间,这样可以根据需要调整放大倍数来适应不同的信号强度。

信号显示是示波器使用的第三个原理。

当信号被放大后,它就可以在示波器的屏幕上显示出来。

示波器的屏幕通常是一个液晶显示器或者CRT显示器,可以显示不同形式的波形,例如正弦波、方波、脉冲等等。

示波器还可以通过改变屏幕的水平和垂直缩放来调整波形的大小和形状。

观测测量是示波器使用的最后一个原理。

一旦信号被放大并显示在屏幕上,工程师和技术人员可以使用示波器来测量各种信号参数,例如频率、幅度、相位差等等。

示波器可以通过内置的测量功能来自动测量各种参数,也可以通过手动测量来获取更精确的结果。

总之,示波器的使用原理涉及到信号采集、信号放大、信号显示和观测测量等多个方面。

通过这些原理,示波器可以帮助工程师和技术人员分析和诊断电路中的问题,从而提高工作效率和准确性。

数据采集电路和简易存储示波器设计

梧州学院课程论文(2012 -2013学年第一学期)课程论文题目:数据采集电路和简易存储示波器设计学生姓名:石凯摘要:设计中采用了模块化设计方法,并使用了多种EDA工具,提高了设计效率。

整个设计实现了存储示波器的所有功能要求,达到较高的性能指标。

本设计分为四个模块分别是:数据采集模块,控制模块和数据存储模块和数据输出模块。

数据采集模块采用A/D(ADC0809)对不同频率的输入信号分别以相应的采样速度予以采样,并将采样数据存在FPGA内部的RAM中。

数据输出模块采用D/A(DAC0832)输出采样信号,在示波器上以X-Y的方式显示波形。

控块以采用EDA中的状态机控制A/D的采样和数字信号的输出。

关键词: 数字存储示波器,状态机, AD,DA, EDA,LPM RAM一、设计内容:数据采集电路和简易存储示波器设计二、设计目的与要求:用ADC0809采集外部一个信号(从IN1输入),转换为8位的二进制数据存储到存储器中,采样一个周期后,把存储器里面的数据重新读出来,通过DAC0832输出,用示波器观察比较被采集的信号和重新输出的信号。

三、设计原理本设计利用FPGA直接控制ADC0809对模拟信号进行采样,然后将转换好的8位二进制数迅速存储到FPGA内部RAM存储器中,在完成对模拟信号一个或数个周期的采样后,由外部按键电路系统将存储器中的采样数据读出处理。

包括如下模块:对ADC0809的采样控制电路、8位地址计数器、存储器、D触发器和按键电路模块。

为使电路设计更加简单快捷,且方便阅读与理解,本电路使采用模块化的设计思想,先由VHDL源程序对各个模块进行独立编写(对各个模块进行硬件描述)、测试,然后生成原理图封装,再用原理图方式进行连接、整合。

A/D采样控制电路可以分为三个部分来分别实现:ADC0809的控制部分、地址计数器部分、数据存储器部分。

系统框图:在设计整个系统的过程中,可以把设计分成信号采样、存储、信号输出等几部分。

高速数字存储示波器前端电路设计

信号直通 ;当 S接地时 , AD8009 组成同相比例放大电 路 , R3 = 9 ×R2 , 放大倍数 K = 1 + R3 /R2 = 10,从而实现 了 1倍或 10倍的信号放大 。

图 2 无源衰减网络电路 Fig. 2 Passive attenuation network circuit

本文选择低失真集成运放 AD8009来实现前置放大。 AD8009为电流反馈运算放大器 ,其转化速率可达 4 500 V /μs, - 3dB 小信号单位增益带宽为 1 GHz。如 图 4所示为放大电路 ,其中 , S为继电器 ,由控制信号 来控制是否接地 ; R1、R2 比较小 ,一般取几十欧姆 。当 S不接地时 , AD8009 构成电压跟随器 ,放大倍数为 1,

1 前端信号调理电路

前端调理电路的目的一般有两个 : 一是扩大可测 信号的幅度范围 ,设置衰减器和放大器 ,对大信号进行 衰减 ,对小信号进行放大 ,以保证足够的动态范围 ; 二 是为了不对被测信号带来影响 ,保证输入端有较高的

修改稿收到日期 : 2009 - 09 - 27。 第一作者张宇翔 ,男 , 1962年生 , 1991年毕业于西安交通大学信息与控 制系 ,获硕士学位 ,副教授 ;主要从事自动化与仪器仪表等方面的研究。

66

PROCESS AUTOM AT IO N INSTRUM ENTAT IO N Vol131 No14 Apr il 2010

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

高速数字存储示波器前端电路设计 张宇翔 ,等

较低 , 170 MHz时仅为 65 dB; 采用单端或者差分模拟 输入 、LVDS输出 ,模拟输入范围为 1V。AD9480 还含 有内置基准电压源和采样保持电路 [5 ] 。高速并行 A /D 的原理图如图 6所示 。

EDA_VHDL_数据采集电路和简易存储示波器设计

EDA数据采集电路和简易存储示波器设计(1) 实验目的:掌握LPM RAM模块VHDL元件定制、调用和使用方法;熟悉A/D和D/A与FPGA接口电路设计;了解HDL文本描述与原理图混合设计方法。

先用文本输入方式分别完成对元件ADCINT、元件CNT10B的VHDL的源程序设计,然后采用图形输入方式将元件ADCINT、元件CNT10B、元件RAM8B连接起来,绘制出符合要求的原理图,如图1所示。

(2) 实验原理:本设计项目是利用FPGA直接控制0809对模拟信号进行采样,然后将转换好的8位二进制数据迅速存储到存储器中,在完成对模拟信号一个或数个周期的采样后,由外部电路系统(如单片机)将存储器中的采样数据读出处理。

采样存储器可以有多种方式实现:1、外部随机存储器RAM。

其优点是存储量大,缺点是需要外接芯片,且常用的RAM 读写速度较低;与FPGA间的连接线过长;特别是在存储数据时需要对地址进行加1操作,进一步影响数据写入速度。

2、FPGA内部EAB/ESB等。

在Altera的大部分FPGA器件中都含有类似于EAB的模块。

3、由EAB等模块构成高速FIFO。

FIFO比较适合于用作A/D采样数据高速存储。

基于以上讨论,A/D采样电路系统可以绘成图1所示的电路原理图。

其中元件功能描述如下:1. 元件ADCINT。

见程序1,ADCINT是控制0809的采样状态机,其VHDL描述以及其输入输出信号的含义与试题26完全相同。

2. 元件CNT10B。

见程序2,CNT10B中有一个用于RAM的9位地址计数器,此计数器的工作时钟CLK0由WE控制:当WE=’1’时,CLK0=LOCK0;LOCK0来自0809采样控制器的LOCK0(每一采样周期产生一个锁存脉冲),这时处于采样允许阶段,RAM的地址锁存时钟inclock=CLKOUT=LOCK0;每一个LOCK0的脉冲通过0809采到一个数据,同时将此数据锁入RAM(RAM8B模块)中。

示波器的结构和工作过程

示波器的结构和工作过程示波器是一种用于测量和显示电信号波形的仪器。

它具有复杂的结构和工作原理,一般分为模拟示波器和数字示波器两种类型。

1.模拟示波器结构和工作过程:模拟示波器是由电子元件和电路组成的。

其基本结构包括垂直放大器、水平放大器、扫描发生器、时间基准、显示器和触发电路等部分。

垂直放大器:垂直放大器负责对输入信号进行放大。

它包括一个放大器和一个偏置电源。

放大器可以调节放大倍数,偏置电源用于调整起始位置。

水平放大器:水平放大器控制电子束的水平位置。

它包括一个水平电压控制器和一个扫描发生器。

水平电压控制器调节水平扫描速度和幅度,扫描发生器产生扫描信号。

时间基准:时间基准提供一个精确的时间标准,用于测量信号的时间间隔和频率。

触发电路:触发电路决定示波器何时开始记录和显示波形。

它根据用户设置的触发电平和斜率,在信号满足条件时进行触发操作。

显示器:显示器用于显示被测信号的波形。

一般使用阴极射线管(CRT)作为显示器。

工作过程:当被测信号输入示波器后,垂直放大器对其进行放大处理,然后通过水平放大器控制电子束的水平位置进行扫描。

扫描过程中,电子束按照扫描发生器提供的扫描信号进行水平移动。

当电子束移动到垂直放大器输出的信号位置时,电子束的亮度受到垂直放大器的控制,进而通过显示器显示出波形。

触发电路使示波器能够按照用户指定的触发条件对信号进行触发,并确保获得稳定的波形显示。

2.数字示波器结构和工作过程:数字示波器是基于数字信号处理技术的测量仪器。

它的基本结构包括输入部分、模拟-数字转换(A/D)部分、数字信号处理(DSP)部分和显示部分。

输入部分:输入部分接收被测信号,通常使用电压分压器将信号调整到示波器可输入的范围内。

A/D部分:A/D部分将模拟信号转换为数字信号。

它由一个采样器和一个A/D转换器组成。

采样器将连续的模拟信号分成离散的样本,并且按固定的时间间隔进行采样。

A/D转换器将每个样本的电压值转换为数字表示。

放大电路及数据采集

扩音机的输入级

多级放大电路

三极管功率放大作用

三极管工作在饱和区和截止区 在数字控制电路中,经 常采用三极管做功率驱 动,比如驱动蜂鸣器, LED,继电器,指示灯, 直流小电机等。

Vin Ik

集成运算放大器及信号处理电路

集成运算放大器的基本概念

集成运算放大器的线性应用

滤波的概念和基本滤波电路

电压比较电路

I BQ

VCC VBEQ Rb

ICQ βIBQ ICEO βIBQ

VCEQ=VCC-ICQRc

直流通路

直流通路

iC iC i B= 常数 (a) Q ICQ O

t

Байду номын сангаас

O

u CE

3. 简单工作原理 直流电源:内阻为零, 相当于短路 耦合电容:通交流, 相当于短路

Vi=Vsint(动态)

RF Auf ' R1 uI uI

uO

(4.2.9)

差分电路的输出电压与两个输入电压之差成正比, 实现了差分比例运算。其比值|Auf|同样决定于电阻 RF和R1之比,而与集成运放内部各项参数无关。由 以上分析还可以知道:差分比例运算电路中集成运 放的反相输入端和同相输入端可能加有较高的共模 输入电压,电路中不存在“虚地”现象。

uu+

ii+

+

Aod

uO

2)理想集成运放的输入电流等于零

由于理想集成运放的差模输入电阻rid=∞, 因此在其两个输入端均没有电流,即运放的 同相输入端和反相输入端的电流都等于零, 如同该两点被断开了一样,这种现象称为 “虚断”。

“虚短”和“虚断”是理想运放工作在 线性区时的两个重要结论。这两个重要结论 常常作为今后分析许多运放应用电路的出发 点,因此必须牢牢记住并掌握。