Ross7_Ch15

Ross7eCh14Long-Term Financing An Introduction(公司理财,罗斯,第七版)

CHAPTER

14

© 2005 The McGraw-Hill Companies, Inc. All Rights Reserved.

Long-Term Financing: An Introduction

McGraw-Hill/Irwin Corporate Finance, 7/e

14-1

The articles of incorporation must state the number of shares of common stock the corporation is authorized to issue. The board of directors, after a vote of the shareholders, may amend the articles of incorporation to increase the number of shares.

McGraw-Hill/Irwin Corporate Finance, 7/e © 2005 The McGraw-Hill Companies, Inc. All Rights Reserved.

14-11

Proxy Voting

A proxy is the legal grant of authority by a shareholder to someone else to vote his or her shares. For convenience, the actual voting in large public corporations is usually done by proxy.

The exact mechanism varies across companies.

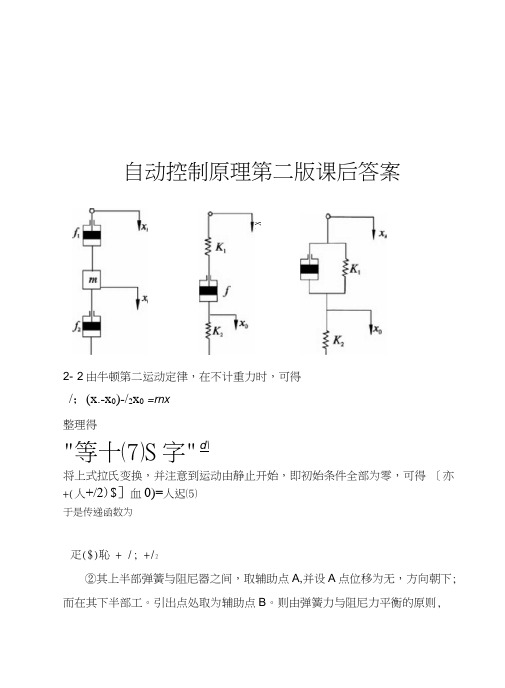

自动控制原理第二版课后答案

自动控制原理第二版课后答案X.2- 2由牛顿第二运动定律,在不计重力时,可得/;(x.-x0)-/2x0=rnx整理得"等十⑺S字" d\将上式拉氏变换,并注意到运动由静止开始,即初始条件全部为零,可得[亦+(人+/2)$]血0)=人迟⑸于是传递函数为疋($)恥 + /; +/2②其上半部弹簧与阻尼器之间,取辅助点A,并设A点位移为无,方向朝下; 而在其下半部工。

引出点处取为辅助点B。

则由弹簧力与阻尼力平衡的原则,从A和B两点可以分别列出如下原始方程:K](兀-x) = /(x-x c)消去中间变量X,可得系统微分方程佔+心)牛+ K心0 = 牛at at对上式取拉氏变换,并计及初始条件为零,得系统传递函数为K ⑸一/(&+£)$+&瓦③以引出点作为辅助点,根据力的平衡原则,可列出如下原始方程: 蜀(兀-X)+ /(乙-对)=丘%移项整理得系统微分方程/贽+ (陌+ 0)心=令+瓦兀对上式进行拉氏变换,并注意到运动由静止开始,即X r(。

) = X0(。

)= °则系统传递函数为X。

(£)_ fz K\ 兀G) 一冷+ (K]+0)2-3r 並'C 2s=1 (&C°s 十 1)一 1 {T.S + 1)・・・——(T.s + 1)所以.5(s)_ S _ C“ -_⑺s + l)®s + l)'5(s) Z 1 + Z 2 尽 |1(匚「J 尽C Q S + ^S + I)込s + 1)T 、s +1 C 2s 2(b) 以幻和fl 之间取辅助点A,并设A 点位移为方向朝下;根据力的平 衡原则,可列出如下原始方程:解:(a):利用运算阻抗法得:Z] =R 』R.——1 _ C\s泾尽+丄R 】 RiGs +1+1K2(X.-X0)+ f2(x. - x0) = /;(x0 -x) (1)A:1x = /;(x(> -x) (2)所以K2(x i-X0)4-/2(X,--X0)=K x x (3)対(3)式两边取微分得恳2(乙—攵。

USR-C215 说明书

USR-C215说明书文件版本:V1.6.4产品特点:●支持********GHz802.11b/g/n无线标准●支持WEP/WPA/WPA2安全模式●支持AP、STA、AP+STA工作模式●完全集成的串口转无线TCP/UDP传输功能,多个串口速率选择●局域网搜索和无线参数设置功能●支持TCP/UDP Client注册包机制●支持Simple Config/Airkiss/usrlink快速联网配置●支持类RFC2217自动波特率适配功能●支持简单AT+指令集配置●Httpd Client功能●3.3V单电源供电●可选择内置天线,外置天线(IPEX连接器)●超小尺寸:22.0mm x13.5mm x9.2mm,1x102mm间距插针封装目录USR-C215说明书 (1)1.快速入门 (3)1.1.模块测试硬件环境 (3)1.2.数据传输测试 (5)2.产品概述 (7)2.1.产品简介 (7)2.2.模块基本参数 (7)2.3.模块工作电源及功耗 (8)2.4.硬件描述 (9)3.产品功能 (11)3.1.Wi-Fi无线配网方式 (11)3.1.1.模块作为STA方式 (12)3.1.2.模块作为AP方式 (13)3.1.3.模块作为AP+STA模式 (13)3.1.4.加密方式 (14)3.2.工作模式 (14)3.2.1.透明传输模式 (15)3.2.2.命令模式 (16)3.2.3.HTTPD Client模式 (17)3.3.串口参数 (18)3.3.1.串口参数简介 (18)3.3.2.类RFC2217自动波特率功能 (20)3.4.特色功能 (21)3.4.1.局域网内搜索 (21)3.4.2.TCP/UDP Client注册包机制 (22)3.4.3.快速联网协议(usrlink) (23)3.4.4.Simple Config/Airkiss智能配网 (24)3.4.5.心跳包机制 (25)3.4.6.自定义网页功能 (26)3.4.7.Wi-Fi连接异常处理 (26)4.设置方法 (28)4.1.Web页面设置 (28)4.2.AT指令配置 (29)4.2.1.AT指令集 (30)5.联系方式 (33)6.免责声明 (34)7.更新历史 (35)1.快速入门USR-C215是有人WiFi模块USR-C21系列的一款低成本模块。

Atmel ATF15xx Complex Programmable Logic Device(CP

The Atmel ® ATF15xx Complex Programmable Logic Device (CPLD) LPT-based JTAG ISP Download Cable [Atmel PN: ATDH1150VPC] connects to a standard parallel port of a PC on one side and to a 10-pin JTAG header of a programming circuit board on the other side. It transfers the JTAG instructions and data generated by the ATMISP software running on a PC to the Atmel ATF15xx series CPLDs on the target circuit board. The ATMISP software can be downloaded from the Atmel website at/tools/ATMISP.aspx . With this In-System Programming (ISP) download cable, design changes can easily be downloaded directly to the ATF15xx JTAG devices, resulting in easyprototyping of designs.●Supports Industry Standard IEEE 1149.1 (JTAG) Compliant Devices ●Allows Users to Perform JTAG ISP of Atmel ATF15xx CPLDs ●Supports Target Systems Using 5.0V, 3.3V, 2.5V or 1.8V V CC and I/O Standards ●Fully Supported by the ATMISP Software (Version 6.x)●Interfaces with a Standard DB25 Parallel Port of PC ●Uses a Standard 10-pin JTAG ConnectorThe ATDH1150VPC ISP Download Cable (Rev 6.0) supports all of the ATF15xx CPLDs with JTAG support.ATDH1150VPCATF15xx CPLD JTAG ISP Download CableUSER GUIDE2Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Frequently Asked Questions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7ATDH1150VPC – ATF15xx CPLD JTAG ISP Download Cable [USER GUIDE]Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_0320143ATDH1150VPC – ATF15xx CPLD JTAG ISP Download Cable [USER GUIDE]Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_032014The ATDH1150VPC ISP Download Cable connects to a standard PC parallel port (LPT) on one sideand to a 10-pin JTAG header on the programming circuit board on the other side. A functional blockdiagram of the ATDH1150VPC ISP Download Cable is shown in the below figure, and Table 1provides the signal descriptions.Figure 1.ATF15xx JTAG ISP Download Cable Functional Block DiagramTable 1.10-pin JTAG Header Signal DescriptionThe ISP circuit board must supply V CC and GND to the ATDH1150VPC ISP Download Cablethrough the 10-pin JTAG male header. A regulated V CC voltage between 1.7V to 5.5V isrecommended, and it should be the same V CC supply used by the JTAG devices.L P T P o r t JT A GConnec tor23811159342, 1013, 18 to 25CC4The Power LED on the 10-pin male connector can be used to show the cable is connected properly.The user must make sure this LED is turned on before using the ATMISP software to program the JTAG devices. The color stripe on ATDH1150VPC ISP Download Cable indicates the orientation of Pin1 of the JTAG connector. The color stripe or the polarized connector can be used as a guide to assurethat the female connector is properly oriented when it is attached to the board. This cable has built-in circuitry to adjust its programming voltage level according to the V CC applied to the cable via Pin 4 of the 10-pin JTAG connector. The following figure illustrates the correct orientation of ATDH1150VPC ISP Download Cable on the programming circuit side.Figure 2.Connection Diagram of ATF15xx JTAG ISP CableThe below figure illustrates the pinout of the 10-pin female header on the ATDH1150VPC ISPDownload Cable. The pinout of the 10-pin male header on the PC board must match this pinout.Figure 3.ATDH1150VPC ISP Download Cable 10-pin Female Header PinoutATDH1150VPC – ATF15xx CPLD JTAG ISP Download Cable [USER GUIDE]Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_0320145ATDH1150VPC – ATF15xx CPLD JTAG ISP Download Cable [USER GUIDE]Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_032014Figure 4 illustrates the dimensions for the 10-pin male header which is mounted on ISP board. Figure 5illustrates the pinout for the 10-pin male header.Figure 4.10-pin Male Header DimensionsFigure 5.10-pin Male Header PinoutThe ATDH1150VPC ISP Download Cable (Rev 6.0) is included in the ATF15xx-DK3 Atmel ATF15xxCPLD Development/Programmer kit or it can be purchased separately.Table 2.Atmel CPLD Kits Ordering Information0.1000.025 Sq.Top View Side ViewAll dimensions are in inchesTCK GND TDO V CCTMS NCNC NCTDI GND6For a multiple device JTAG hardware chain, which device is considered the firstdevice (Device #1) when setting up the Atmel CPLD ISP (ATMISP) software?The device with its TDI pin connected to the TDI pin of the 10-pin JTAG header is the firstdevice (Device #1) of a JTAG chain. The device with its TDO pin connected to the TDO pinof the 10-pin JTAG header is the last device of the chain.For devices with different V CC INT and V CC IO supplies, which V CC (V CC IO or V CC INT)should be used to supply the ATDH1150VPC ISP Download Cable's V CC?V CC IO should be used to supply the V CC of the ATDH1150VPC ISP Download Cable.Can a JEDEC file with the JTAG port feature disabled be programmed into theATF15xx through JTAG ISP?Since all ATF15xx devices are shipped in a blank (erased) state, the JTAG port is enabled bydefault. Therefore, they can be programmed with a JEDEC file with the JTAG port featuredisabled ONLY ONCE via JTAG ISP. However, this is not recommended since the pins usedfor the JTAG port can become outputs immediately after programming is completed and theycan content with the output drivers in the ATDH1150VPC ISP Download Cable. Furthermore,please note that once the JTAG port is disabled, the device can no longer be accessedthrough the JTAG port. To re-enable the JTAG port, you must erase the device or re-program the device with a JEDEC file with the JTAG port feature enabled using a stand-alone 3rd-party device programmer from vendors such as BPM Microsystems, Data I/O, Hi-Lo Systems,. etc.In the Port Setting dialog box of the ATMISP v6.x software window, what LPT portaddresses are associated to the LPT1, LPT2 and LPT3 settings?LPT1 - 378 (hex), LPT2 - 278 (hex), LPT3 - 3BC (hex).The LPT port address of my PC is 1AFF (hex). How do I specify this address in theATMISP software?From the main ATMISP window, select Other in the Port Setting dialog box. In the PortSetting window, enter 1AFF and click OK. Any 3 or 4-digit hex values can be entered into thiswindow.ATDH1150VPC – ATF15xx CPLD JTAG ISP Download Cable [USER GUIDE]Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_0320147ATDH1150VPC – ATF15xx CPLD JTAG ISP Download Cable [USER GUIDE]Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_032014For Atmel PLD technical support, please contact the Atmel PLD Applications Group at:Phone:+1 (408) 436-4333Email: *************Online:/bin/customer.exeX X X X X XAtmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311F: (+1)(408) 436.4200| © 2014 Atmel Corporation. / Rev.: Atmel-8907A-CPLD-ATDH1150VPC-ATF15-JTAG-ISP-Download-Cable-UserGuide_032014.Atmel ®, Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

企业和个人合作利润分红协议书

企业和个人合作利润分红协议书(侧重分红收益权的约定)第 1页 /共 6页XX有限公司之合作利润分红协议甲方乙方身份证号身份证号联系电话联系电话以上双方合作人经友好协商一致,根据中华人民共和国法律、法规的相关规定,双方本着互惠互利这一基本原则,意见统一共同拟定以下合作事项和各条款。

一、协议期限本协议有效期为一年,自年月日起,至年月日止。

二、职责和要求1、甲方(1)制定和实施公司总体战略与年度经营计划,建立和健全公司的管理体系与组织结构。

第 2页 /共 6页(2)主持公司的日常经营管理工作,实现公司经营目标和发展目标,严格管理部门,确保旅行部各项工作安全、高效、运转正常。

(3)关于双方和客户在业务过程中发生的任何法律纠纷,由甲乙双方共同协商解决。

2、乙方(1)协助甲方制定并实施企业战略、经营计划等政策方略,实现公司的经营管理目标及发展目标。

(2)乙方按正常班制上下班,工作细致、严谨,认真履行工作职责,遵守国家法律法规。

(3)拓展公司业务,扩大公司知名度,促进公司经营目标的实现和长远发展。

(4)规划并推进市场营销战略与策略,实现公司各项年度经营指标。

(5)根据公司业务量及发展状况,建设和管理高素质团队,由甲方给乙方制定每月任务量,乙方保证完成该任务额。

三、投资额与投资方式1、乙方投资额为万元,以方式出资,该资金主要用于公司经营开支,其次作为公司营运后的流动资金,不得撤回。

2、乙方应于年底分红前将应支付的资金转入甲方公司账户。

3、合作期间,乙方投资人的出资为共有财产,不得随意请求分割。

合作终止后,乙方投资人的出资为个人所有,届时予以返还。

四、利润分享与分红方式第 3页 /共 6页1、甲方公司总营净利润60%作为乙方投资人的可分享利润,乙方投资人分享该利润的10%。

2、若乙方不能完成甲方制定的年度任务额,则乙方年底分红相应减少。

3、乙方投资人不能转让其在投资合作中的全部或部分分红。

4、在年底分红前,乙方若没有资金注入甲方公司,则不占有公司分红。

ch15-3

Upper threshold voltage Lower threshold voltage

R1 + R2

Hysteresis width VT = VT + VT = R1 (VOH VOL )

The BJT will work. saturation region Active region or saturation region?

VCES ≈ 0

vO = 0V

Sketch Voltage Transfer Characteristic

+12V + 5V A1 -12V +12V vO1 D1 +6V R2 5.1k R1 D2 -12V 51k β=50 vO

15.3.1 Schmitt Trigger Circuits

3. Comparator Application Street light control

Photodetector vI circuit vn

–+ – +

VCC

vO

R

VREF

Photodector D prevent reverse-bias B-E junction vI is proportional to amount of light, increases linearly with time vn is noise

Sol: :

(1) A1 , A2 open loop

Comparator

vI > +5V

vI < +5V

vO1 vO1

TRAC32 HC12 MCS12 仿真器在线帮助说明书

Simulator for HC12/MCS12 Release 09.2023Simulator for HC12/MCS12TRACE32 Online HelpTRACE32 DirectoryTRACE32 IndexTRACE32 Documents ......................................................................................................................TRACE32 Instruction Set Simulators ..........................................................................................Simulator for HC12/MCS12 (1)TRACE32 Simulator License (5)Quick Start of the Simulator (6)Peripheral Simulation (8)FAQ (8)CPU specific SYStem Settings and Restrictions (9)SYStem.CPU Select CPU type9 SYStem.LOCK Lock and tristate the debug port9 SYStem.MemAccess Real-time memory access (non-intrusive)10 SYStem.Mode Establish the communication with the simulator10 SYStem.Option.BASE Base address of internal registers11 SYStem.Option.DUALPORT Run-time memory access for all windows11TrOnchip Commands (12)TrOnchip.state Display on-chip trigger window12 TrOnchip.RESet Set on-chip trigger to default state12Memory Classes (13)Banked Applications (14)Background and Compatibility Information14 SYStem.Option.GLOBAL Memory accesses are done global14 SYStem.Option.PAGING Banked applications15 SYStem.Option.RAMHM Alternate RAM mapping15 SYStem.Option.ROMHM ROM in second half of map15 SYStem.Option.TRANS Transparent mode15 Using the MMU for HC12DA/DG/DT12818 SYStem.Option.MEMEXP Memory expansion18 SYStem.Option.ROMTST FLASH EEPROM test mode19 Using the MMU for HC12A4/F819 Basics19 Logical Address19 Physical Address20Expanded Physical Address21 Memory Mapping Unit24Simulator for HC12/MCS12Version 10-Oct-2023All general commands are described in the “PowerView Command Reference” (ide_ref.pdf) and“General Commands Reference”.TRACE32 Simulator License[build 68859 - DVD 02/2016] The extensive use of the TRACE32 Instruction Set Simulator requires a TRACE32 Simulator License.For more information, see /sim_license.html.Quick Start of the SimulatorTo start the simulator, proceed as follows:1.Select the device prompt for the Simulator and reset the system.The device prompt B:: is normally already selected in the TRACE32 command line . If this is not the case, enter B:: to set the correct device prompt. The RESet command is only necessary if you do not start directly after booting TRACE32.2.Specify the CPU specific settings.The default values of all other options are set in such a way that it should be possible to work without modification. Please consider that this is probably not the best configuration for your target.B::RESetSYStem.CPU <cpu_name>3.Enter debug mode.SYStem.UpThis command resets the CPU and enters debug mode. After this command is executed it is possible to access memory and registers.4.Load the program.Data.LOAD.<file_format> <file>; load program and symbols See the Data.LOAD command reference for a list of supported file formats. If uncertain about the required format, try Data.LOAD.auto.A detailed description of the Data.LOAD command and all available options is given in the referenceguide.5.Start-up exampleA typical start sequence is shown below. This sequence can be written to a PRACTICE script file(*.cmm, ASCII format) and executed with the command DO<file>.B::; Select the ICD device promptWinCLEAR; Clear all windowsSYStem.CPU <cpu_name>; Select CPU typeSYStem.Up; Reset the target and enter; debug modeData.LOAD.<file_format> <file>; Load the applicationRegister.Set pc main; Set the PC to function mainPER.view; Show clearly arranged; peripherals in window *) List.Mix; Open source code window *)Register.view /SpotLight; Open register window *)Frame.view /Locals /Caller; Open the stack frame with; local variables *) Var.Watch %Spotlight flags ast; Open watch window for; variables *) *) These commands open windows on the screen. The window position can be specified with the WinPOS command.Peripheral SimulationFor more information, see “API for TRACE32 Instruction Set Simulator” (simulator_api.pdf).FAQPlease refer to https:///kb.CPU specific SYStem Settings and RestrictionsSYStem.CPU Select CPU type Format:SYStem.CPU<type><type>:M68HC12A | M68HC12B | M68HC12BC | M68HC12D | M68HC12DA |M68HC12DG| M68HC12G | M68HC12FWith this command the processor type is selected.SYStem.LOCK Lock and tristate the debug port Format:SYStem.LOCK [ON | OFF]The command has no effect for the simulator.SYStem.MemAccessReal-time memory access (non-intrusive)SYStem.ModeEstablish the communication with the simulatorDefault: Down.Selects the target operating mode.Format:SYStem.MemAccess Enable | StopAndGo | Denied SYStem.ACCESS (deprecated)EnableCPU (deprecated)Real-time memory access during program execution to target is enabled.Denied Real-time memory access during program execution to target is disabled.StopAndGoTemporarily halts the core(s) to perform the memory access. Each stop takes some time depending on the speed of the JT AG port, the number of the assigned cores, and the operations that should be performed.Format:SYStem.Mode <mode>SYStem.Down (alias for SYStem.Mode Down)SYStem.Up (alias for SYStem.Mode Up)<mode>:Down UpDownThe CPU is in reset. Debug mode is not active. Default state and state after fatal errors.UpThe CPU is not in reset but halted. Debug mode is active. In this mode the CPU can be started and stopped. This is the most typical way to activate debugging.SYStem.Option.BASE Base address of internal registers Format:SYStem.Option.BASE <address>Defines the base address of the internal registers. On HC12 target systems the user should always keep this address on the same value as the internal CPU register INITRG. (<address> is a 16-bit value).The ICD needs to know, where the CPU’ s internal registers are assigned to. This information is used to show the CPU’ s internal registers in the peripheral window, which can be opened by the PERipheral command.SYStem.Option.DUALPORT Run-time memory access for all windows Format:SYStem.Option.DUALPORT [ON | OFF]Default: OFF.Dualport access of memory while simulation in running.TrOnchip CommandsTrOnchip.state Display on-chip trigger window Format:TrOnchip.stateOpens the TrOnchip.state window.TrOnchip.RESet Set on-chip trigger to default state Format:TrOnchip.RESetSets the on-chip trace and trigger module to reset state.Memory ClassesMemory Class DescriptionC:, P:, D:Specify the same address-area (CPU-access)A:Absolute memory access (requires MMU-table)EEPROM:EEPROM writeE:Emulation memory access (dual-ported)AP:Physical address (68HC12A4/F8/DA128/DG128 only)G:Global (S12X only)X:XGate (S12X only)C:, P: and D:This storage classes operate on the same physically memory. They are only used to be compatible with other emulation probes. CPU internal registers and memory may not be accessed dual-ported, by mapping memory to the same address range data written to the internal memory are also present in the emulation memory.EEPROM:This storage class is used to program the internal EEPROM. On read cycles there is no difference to the access mode with C: or D:. On write cycles the monitor program executes an EEPROM write protocol.Data.Set EEPROM:0E00 12 34D.s EE: 0E00 12 34; EE: can be used as short formBanked ApplicationsT o support applications which use more than the 64K direct accessible memory paging is required. T o activate banking switch the SYStem.Option.PAGING to ON and set the SYStem.Option.ROMHM and the SYStem.Option.TRANS according to the needs of your application.Background and Compatibility InformationThere are two memory schemes to support banked applications. One is based on the memory model used in the ICE12 with the artificial expanded physical addresses, the other one is based on the memory model used in FIRE12 where all commands are based on logical addresses. The last one is easier to use and available for all derivatives except for HC12A4. For applications with HC12A4 refer to the chapter Using the MMU for HC12A4/F8.T o activate banking with the FIRE12 similar memory model switch the SYStem.Option.PAGING to ON. This is available for all MCS12 (Star12) derivatives.For HC12DA/DG/DT128 both options are available. For new designs LAUTERBACH recommends to use FIRE12 based memory scheme. The ICE12 based memory model is still there to be compatible with old command files (*.cmm - files). See chapter Using the MMU for HC12DA/DG/GT128 for further information. SYStem.Option.GLOBAL Memory accesses are done globalFormat:SYStem.Option.GLOBAL [ON | OFF]On S12X targets two different views on the memory map are possible. One is similar to the view used for the MC9S12 with a 64k address room and memory expansion using page pointers in some ranges (Local Memory Map), the other view has one linear address map (Global Memory Map).If you use commands without memory class and the SYStem.Option.Global is off, the TRACE32 software will use the memory classes p: and d: which are intended to be used for logical addresses (Local Memory Map).If you use commands without memory class and the SYStem.Option.Global is on, the TRACE32 software will use the classes gp: and gd: which are intended to be used for global addresses (Global Memory Map).SYStem.Option.PAGING Banked applications Format:SYStem.Option.PAGING [ON | OFF]The SYStem.Option.PAGING enables the support for banked applications. It activates a memory scheme similar to the one used for FIRE12. No MMU is required, all address based commands (map.bonchip, flash programming) are based on logical addresses.SYStem.Option.RAMHM Alternate RAM mapping Format:SYStem.Option.RAMHM [ON | OFF]The SYStem.Option RAMHM must be set if the bit RAMHM is set in the CPU’s MISC register. SYStem.Option.ROMHM ROM in second half of map Format:SYStem.Option.ROMHM [ON | OFF]The SYStem.Option.ROMHM must be set if the bit ROMHM is set in the CPU’s MISC register. In this case page 6 of the FLASH EEPROM is visible from $4000--$7fff.SYStem.Option.TRANS T ransparent mode Format:SYStem.Option.TRANS [ON | OFF]The SYStem.Option.Trans has effect on logical addresses smaller then 64K. If it is on then accesses in this area show the 64K of memory as seen by the CPU in the current paging configuration. This is thetransparent mode. If it is off then in banked areas page zero of this area is shown and the contents of the according page register has no influence. It has no effect on the memory access of the CPU executing user code.Address Access to000000--00ffff current 64K address space (when TRANS is on)A logical address alone doesn't unique identify the physical address, as the address depends also on the setup of the INITRG, WINDEF , MXAR, MISC, CSCTL0 and CSCTL1 registers. As a result, logicaladdresses should only be used, if the MMU registers were already setup. Accessing internal resources (RAM or peripherals) is handled like an access outside of the MMU window. The following schematic shows these relations for some examples:000000--00ffff page 0 (when TRANS is off)010000--0ffffff pages 1..0ff100000--0ffffffffcurrent 64K address spacepreset: CSCTL0=30, CSCTL1=10, WINDEF=40 logical address:38567(Hex)16 bitA21..A14logical CPU address -->exp. physical address:0bfc567logical address:014567(Hex)16 bitPAGE logical CPU address -->exp. physical address:0ff4567logical address:8567(Hex)16 bitcurrent-mmu logical CPU address -->inside PROG , assume PPAGE=1-->exp. physical address:0bf4567logical address:00cd e f(Hex)16 bitcurrent-mmu logical CPU address -->outside pages-->exp. physical address:0ffcdefT o activate the correct address translation for breakpoints, the MMU command must be activated. The creation and activation of the MMU translation can be done automatically for some file formats during download. The following script will prepare the 68HC12A4 for using the MMU without additional address lines and with CSP0 line to select between RAM and ROM:sys.res y.res mmu.res map.ressys.o csp0e on sys.m ai map.m fastmap.ram 0x0200--0x0ffff map.ram 0x0bf0000++0x0ffff map.opf 0x8000--0x0ffff map.opf 0x0bf0000++0x0ffff map.id.s 0x013 0x0e d.s 0x16 0x0d.s 0x3c 0x30d.s 0x3d 0x10d.s 0x12 0x11d.s 0x3e 0x5d.s 0x0f0 0x0fc d.s 0x0f1 0x0d.s 0x37 0x40; disable rom; disable the watchdog ; CSCTL0; CSCTL1; set EEPROM to $1000; enable P-Pagingd.load.elf bankdemo.abs /spath /mmu enddoUsing the MMU for HC12DA/DG/DT128Banked applications on HC912DA128, HC912DG128 or HC12DT128 are supported similar toHC812A4/F8. Refer to that chapter to get BASIC information. Different to that derivatives is that HC12Dx128 have no chip selects or address lines higher than A15. The memory expansion is done with the PP AGE register which contains the page index (Bit2--Bit0 of the PP AGE register are called PIX2--PIX0). So there is a different table for the expanded physical address:The expanded physical address lines A13 to A0 contain the same level as the according pins of the CPU.The table shows that the expanded physical address depends on the address, the page index and on the bits ROMTST and ROMHM in the MISC register of the CPU. This information is given with the following SYStem.Options:SYStem.Option.MEMEXPMemory expansionThe SYStem.Option.MEMEXP enables the support for banked applications. If it is off, then the address information on the CPU’s pins is put on the emulator’s memory , break and trace system directly . If it is on the expanded physical address is put on instead.Address in 64K area SYStem.Options A23A22A21A20A19A18A17A16A15A14$0000--$3FFF MEMEXP off 0000000000MEMEXP on 1111111100$4000--$7FFFMEMEXP off 0000000001MEMEXP on ROMHM off 1111111101MEMEXP on ROMHM on1111111011$8000--$BFFFMEMEXP off 0000000010MEMEXP on ROMTST off 11111PIX2PIX1PIX011MEMEXP on ROMTST on11111PIX2PIX1011$C000--$FFFFMEMEXP off 0000000011MEMEXP on ROMTST off 1111111111MEMEXP on ROMTST on11111PIX2PIX1111Format:SYStem.Option .MEMEXP [ON | OFF ]SYStem.Option.ROMTST FLASH EEPROM test mode Format:SYStem.Option.ROMTST [ON | OFF]The SYStem.Option.ROMTST must be set if the bit ROMTST is set in the CPU’s MISC register. In this case the CPU is running in the Flash EEPROM TEST mode, where the FLASH EEPROM is in use as four 32K windows located from $8000--$ffff. This option is only available if SYStem.Option.MEMEXP is activated. Using the MMU for HC12A4/F8BasicsT o support memory expansion beyond 64K the ICD12 needs to know how the memory expansion and chip select unit of the CPU is used in the target application. T o make the system work, an exact relation must be given between the logical address (address in the 64K area combined with the selected program or data page) and the physical address combined with the chip select generated by the CPU. This relation is given by an expanded physical address and an MMU table (Memory Mapping Unit table).There were a few important expressions in this first paragraph. The following lines will describe theseexpressions.Logical AddressThe logical address is a combination of an address in the 64K address area and the selected program or data page. It contains 6 hexadecimal digits. The lower four digits contain the 64K address and the upper two digits contain the number of the program or data page. The following table shows a few examples: Address in 64K Address Range Contents of affected Page Register Logical Address $8000PPAGE = $F1$F18000$7124DPAGE = $10$107124$400EPAGE = $03$30400Physical AddressThe physical address is the address the CPU shows on its bus. It depends on the application which address lines are used and which not. T o make the ICD12 know if an Address or ChipSelect is used or not there is a switch for each of the Addresses ADDR[21..16].Format:SYStem.Option.A16E [ON | OFF]SYStem.Option.A17E [ON | OFF]SYStem.Option.A18E [ON | OFF]SYStem.Option.A19E [ON | OFF]SYStem.Option.A20E [ON | OFF]SYStem.Option.A21E [ON | OFF]If a line of PortG is used as address line the according SYStem.Option must be set to ON if it is used as general I/O it should be set to OFF.Format:SYStem.Option.CSP0E [ON | OFF]SYStem.Option.CSP1E [ON | OFF]SYStem.Option.CSDE [ON | OFF]SYStem.Option.CSD2E [ON | OFF]SYStem.Option.CS3E [ON | OFF]If a line of PortF is used as chip select line the according SYStem.Option must be set to ON. If it is used as general I/O is should be set to OFF.Expanded Physical AddressPhysical address combined with the information on the chip select lines select a location in memory. T o be compatible with the modular concept of TRACE32 the information on the chip select lines is translated to additional address lines. The following table shows the translation table for HC12A4/F8.Active Chip Select A23A22A21A20CS30010CSD0001CSD20000CSP101CPU A21CPU A20CSP010CPU A21CPU A20all other cases11CPU A21CPU A20 The expanded physical address range contains 23 address lines though the CPU has only 21 address lines.The chip select lines affect A[23..20] of the expanded physical address. IF CSD, CSD2 or CS3 are active the lines A21 and A20 contain levels which may be different to the levels on the CPU’s pins. A[19..0] contain the same levels as the CPU’s pins (These statements and the table are only valid if the address lines A21 to A16 on the CPU are in use as address).The following table gives an overview on the relation between logical address and expanded physical address on the HC12A4:Address in 64K Area ActiveChipSelectA23A22A21A20A19A18A17A16$0000--$03FF EWDIR = 1 EWEN = 1CS3001011PEA17PEA16$0400--$07FF EWDIR = 0 or EWEN = 1CS3001011PEA17PEA16$7000--$7FFF CSD0001PDA19PDA18PDA17PDA16$8000--$BFFF PWEN = 1CSP101PPA21PPA2PPA19PPA18PPA17PPA16$8000--$BFFF PWEN = 1CSP010PPA21PPA2PPA19PPA18PPA17PPA16all othercases11111111Address in 64K Area ActiveChipSelectA15A14A13A12A11A10A9--A0$0000--$03FF EWDIR = 1, EWEN = 1CS3PEA15PEA14PEA13PEA12PEA11PEA1A9--A0$0400--$07FF EWDIR = 0 or EWEN = 1CS3PEA15PEA14PEA13PEA12PEA11PEA1A9--A0$7000--$7FFF CSD PDA15PDA14PDA13PDA12A11A10A9--A0$8000--$BFFF PWEN = 1CSP1PPA15PPA14A13A12A11A10A9--A0$8000--$BFFF PWEN = 1CSP0PPA15PPA14A13A12A11A10A9--A0all othercasesA15A14A13A12A11A10A9--A0Memory Mapping UnitThe MMU (Memory Mapping Unit) translation table is used for translating logical addresses to expanded physical addresses and vice versa. This table is specified with the commands concerning MMU.On ICD12 there is a mechanism which calculates the correct expanded physical address from the logical address. This mechanism is started if the physical address is not specified when using the commandTRANSlation.Create. In this case the logical to expanded physical address translation is done by reading the MMU registers of the CPU and calculating the expanded physical address dependent on theSYStem.Options concerning chip selects and higher address lines. This calculation doesn't take care about memory areas, which are overlaid by internal memory or I/O. It is strongly recommended to define all logical and physical addresses in the MMU table.The breakpoints are based on the expanded physical address. So the MMU must be set correct to make them work proper.。

Edwards 7000-CHS-SP 通讯系统说明书

The 28 pushbuttons include a 12-button standard telephone keypad, one speaker phone button, one push-to-talk button, and one volume up/down switch. One menu button, eight programmable generalpurpose function keys and four programmable special function keys are also included.

© Copyright 2004 Edwards

18-4 D-04

TECHNICAL INFORMATION

INTERCOM SYSTEMS

SPECIFICATIONS

Speaker

2.5" (4.6cm) 8 ohms, 1.5 watts

Microphone

Built-in condenser type

INTERCOM SYSTEMS

Administrative Telephone

FEATURES > Handset, hands-free, or push-to-

talk operation > 16 character alphanumeric

display > Alphanumeric 3-, 4-, or 5-digit

Telephone Functions

Extension dialing, PBX/KSU or outside line dialing, direct dial, speed dial, redial, call hold, call transfer, call forward, music-on-hold, three-party conference calling, handset operation, half duplex with push-to-talk switching or hands free speaker phone microphone/speaker operation.Weight源自4 lbs (1.8kg)

机器人操作系统ROS的安装与配置教程

机器人操作系统ROS的安装与配置教程机器人操作系统(Robot Operating System,ROS)是一个通用的机器人软件开发平台,提供了一系列的库和工具,方便开发者创建和运行机器人应用程序。

ROS的安装与配置是使用该平台的第一步,下面将详细介绍ROS的安装和配置教程。

1. 确认操作系统和硬件要求在开始安装ROS之前,需要确保你的操作系统符合要求。

ROS支持多种操作系统,包括Ubuntu、Fedora等。

此外,还需要确认你的硬件配置满足ROS的最低要求,如处理器、内存等。

2. 选择ROS版本并下载安装包ROS有多个版本可供选择,其中ROS Kinetic是目前最新的稳定版本。

访问ROS官方网站,选择与你的操作系统匹配的ROS版本,并按照指引下载对应的安装包。

3. 安装ROS下载安装包后,执行以下命令进行安装:```$ sudo apt-get update$ sudo apt-get install ros-<version>-desktop-full```请将上述命令中的`<version>`替换为你下载的ROS版本号,例如`kinetic`。

安装过程可能需要较长时间,请耐心等待。

4. 初始化ROS工作空间安装完成后,需要初始化ROS工作空间以便于开发和构建ROS的应用程序。

执行以下命令创建一个工作空间:```$ mkdir -p ~/catkin_ws/src$ cd ~/catkin_ws/$ catkin_make```上述命令创建了一个名为`catkin_ws`的工作空间,并执行了编译操作。

在工作空间中,包含了`src`目录用于存放ROS的软件包。

5. 配置ROS环境为了能够正确地使用ROS,需要将ROS的环境变量配置到系统中。

执行以下命令将ROS的环境变量添加到`.bashrc`文件中:```$ echo "source /opt/ros/<version>/setup.bash" >> ~/.bashrc $ source ~/.bashrc```请将命令中的`<version>`替换为你安装的ROS版本号。

Electro-Voice ZLX-15BT 15 2-way powered speaker B

▪High-quality Bluetooth® audio streaming for background music or musical accompaniment. Bluetooth® connectivity is available in select countries.▪Quick Smart DSP features best-in-class processing. Easy setup via four presets, sub/top system-match, two-band EQ, five user-programmable presets, visual monitoring of limiter status, input level control and meters, and master volume control to optimize gain structure, all via LCD.▪High-efficiency 1000 W Class-D power amplifier delivers us to 127 dB peak SPL utilizing transducers designed and engineered by EV.▪EV-patented Signal Synchronized Transducers (SST) waveguide design provides precise and consistent coverage, minimal distortion, and maximized acoustical loading.▪Three optimally located handles combined with a rugged composite structure provides the most portable professional sound speaker on the market.NOW STREAMING: Cut through the competition with Bluetooth® enhanced ZLX portableloudspeakersZLX portable loudspeakers offer the best performance and reliability in their class - with components and engineering that work together to make it quicker and easier than ever to take control of your sound, whatever the gig. Now with Bluetooth® enabled wireless audio streaming, legendary ZLX performance becomes even more convenient with the ability to connect to any mobile device for streaming your music library.Featuring custom drivers housed in an innovative cabinet design, the two new wireless, compact, and versatile ZLX models make EV's renowned sound quality and rugged reliability more accessible than ever before.Bluetooth® is available in select countries.Technical specificationspreset.2.Maximum SPL is measured at 1 m using broadband pink noise at maximum output.3.Current rating is specified at 1/8 full output power.Frequency response:Dimensions:System overviewFull-Range loudspeaker control and monitoring interface1253 4876Full-Range loudspeaker amplifier panel1.LCD - DSP control and monitoring interface.2.MASTER VOL - Adjusts the sound level.DSP - Scroll through the menu and select theavailable choices. Push the MASTER VOL knob toenter the DSP menu.3.INPUT LEVEL - Level control for adjusting theindividual inputs’ level. The 12 o’clock position isunity gain (no gain or attenuation), the range to theleft of zero is for adjusting line level sources, and the range to the right of zero (0) is for adjustingmicrophone levels. LINE and MIC input level control is available for both INPUT 1 and INPUT 2.4.POWER - AC switch or switching the power ON orOFF. The LCD screen lights up when the power isturned ON, after approximately 3 seconds.5.MAINS IN - AC connection is established via an IEC-connector.6.INPUT - Balanced input for the connection of signalsources like mixing consoles, instruments, ormicrophones. Connections can be established using¼ inch TRS or XLR connectors.7.OUTPUT - XLR output sends the mix of all inputsignals to another loudspeaker or subwoofer. INPUTLEVEL controls the signal level to OUTPUT. TheMASTER VOL or DSP control settings do not affectOUTPUT. This is also the output for the BT signalwhich is configurable via the MIX OUT setting.8.AUX IN - 3.5 mm audio jack input for connectingexternal audio media devices, such as MP3 players. For more information, see the ZLX Powered Loudspeaker Series Installation manual (F.01U.349.854).Ordering informationZLX-15BT-EU 15" 2-way powered speaker BT EUcord Powered 15-inch 2-way loudspeaker with Bluetooth®and EU cord, blackOrder number ZLX-15BT-EUZLX-15BT-US 15" 2-way powered speaker BT UScord Powered 15-inch 2-way loudspeaker with Bluetooth®and US cord, blackOrder number ZLX-15BT-USAccessoriesZLX-BRKT ZLX Wall Mount BracketWall mount bracket for ZLX-12/12P/12BT andZLX-15/15P/15BT, blackOrder number ZLX-BRKTZLX-15-CVR ZLX Padded Cover for ZLX-15/P - EV Logo Padded cover for ZLX-15/15P/15BT, EV logo, black Order number ZLX-15-CVRRepresented by: Germany:Bosch Sicherheitssysteme GmbH Robert-Bosch-Ring 585630 GrasbrunnGermany Bosch Security Systems, Inc. 12000 Portland Avenue South Burnsville MN 55337USA© Bosch Security Systems 2018 | Data subject to change without notice Document Number | Vs1 | 11. Apr 2018。

西门子 S7-1500、ET 200MP、ET 200SP、ET 200AL、ET 200pro 通

SIMATICS7-1500、ET 200MP、ET 200SP、ET 200AL、ET 200pro 通信功能手册Siemens AG Division Digital Factory Postfach 48 48 90026 NÜRNBERG A5E03735819-AEⓅ 10/2016 本公司保留更改的权利Copyright © Siemens AG 2013 - 2016.保留所有权利法律资讯警告提示系统为了您的人身安全以及避免财产损失,必须注意本手册中的提示。

人身安全的提示用一个警告三角表示,仅与财产损失有关的提示不带警告三角。

警告提示根据危险等级由高到低如下表示。

危险表示如果不采取相应的小心措施,将会导致死亡或者严重的人身伤害。

警告表示如果不采取相应的小心措施,可能导致死亡或者严重的人身伤害。

小心表示如果不采取相应的小心措施,可能导致轻微的人身伤害。

注意表示如果不采取相应的小心措施,可能导致财产损失。

当出现多个危险等级的情况下,每次总是使用最高等级的警告提示。

如果在某个警告提示中带有警告可能导致人身伤害的警告三角,则可能在该警告提示中另外还附带有可能导致财产损失的警告。

合格的专业人员本文件所属的产品/系统只允许由符合各项工作要求的合格人员进行操作。

其操作必须遵照各自附带的文件说明,特别是其中的安全及警告提示。

由于具备相关培训及经验,合格人员可以察觉本产品/系统的风险,并避免可能的危险。

按规定使用Siemens 产品请注意下列说明:警告Siemens 产品只允许用于目录和相关技术文件中规定的使用情况。

如果要使用其他公司的产品和组件,必须得到 Siemens 推荐和允许。

正确的运输、储存、组装、装配、安装、调试、操作和维护是产品安全、正常运行的前提。

必须保证允许的环境条件。

必须注意相关文件中的提示。

商标所有带有标记符号 ® 的都是西门子股份有限公司的注册商标。

ROS软路由超详细的PCC设置步骤,实现一线多拨,五条宽带叠加

PCC实验一、基本配置,使网络能够正常连通1.pppoe拨号:拨通五个帐号PPPOE client的连接状态,已连接设备NAT:5个接口出去都做NAT创建一个bridge,把其他局域网口添加到bridge中。

添加其他局域网口到bridge中DHCP 服务器设置(局域网自动获取IP地址)局域网的网段为192.168.10.0/24把192.168.10.254作为内网的网关设置网关的地址,接口添加到bridge1上一般我们用DHCP setup来自动设置DHCP server这种设置比较简单快速路由配置:所有的基本配置都设置好了,局域网可以正常上网了,但是为了实现更好的网络环境,我们需要做更好的策略。

这就需要使用PCC了,下面就看看PCC怎么做的吧。

二、PCC的配置Mangle标记标记内网地址为192.168.10.0的五条线路的连接标记标记第一条连接:同理:配置剩余的4调链路:5/1,c2; 5/2.c3; 5/3,c4; 5/4,c5.从连接中提取路由标记:从连接里提取路由标记标记第一条连接c1,命令为R1同理:提出其他4调路由命名为R2,R3,R4,R5.标记连接,的命名配置方式为:[admin@MikroTik] /ip firewall mangle> printFlags: X - disabled, I - invalid, D - dynamic0 chain=prerouting action=mark-connection new-connection-mark=c1passthrough=yes src-address=192.168.10.0/24 dst-address-type=!localper-connection-classifier=both-addresses:5/01 chain=prerouting action=mark-connection new-connection-mark=c2passthrough=yes src-address=192.168.10.0/24 dst-address-type=!localper-connection-classifier=both-addresses:5/12 chain=prerouting action=mark-connection new-connection-mark=c3passthrough=yes src-address=192.168.10.0/24 dst-address-type=!localper-connection-classifier=both-addresses:5/23 chain=prerouting action=mark-connection new-connection-mark=c4passthrough=yes src-address=192.168.10.0/24 dst-address-type=!localper-connection-classifier=both-addresses:5/34 chain=prerouting action=mark-connection new-connection-mark=c5passthrough=yes src-address=192.168.10.0/24 dst-address-type=!localper-connection-classifier=both-addresses:5/4提取路由的命令5 chain=prerouting action=mark-routing new-routing-mark=R1 passthrough=yes src-address=192.168.10.0/24 connection-mark=c16 chain=prerouting action=mark-routing new-routing-mark=R2 passthrough=yes src-address=192.168.10.0/24 connection-mark=c27 chain=prerouting action=mark-routing new-routing-mark=R3 passthrough=yes src-address=192.168.10.0/24 connection-mark=c38 chain=prerouting action=mark-routing new-routing-mark=R4 passthrough=yes src-address=192.168.10.0/24 connection-mark=c49 chain=prerouting action=mark-routing new-routing-mark=R5 passthrough=yes src-address=192.168.10.0/24 connection-mark=c5回程路由设置需要将从那个口进入就从相应的口回去,即保证每个外网口的数据能得到正确的路由同理标记c2,c3,c4,c5的回程路由提取回程路由同理提取c2,c3,c4,c5命令方式:10 chain=input action=mark-connection new-connection-mark=c1 passthrough=yesin-interface=pppoe-out111 chain=input action=mark-connection new-connection-mark=c2 passthrough=yesin-interface=pppoe-out212 chain=input action=mark-connection new-connection-mark=c3 passthrough=yesin-interface=pppoe-out313 chain=input action=mark-connection new-connection-mark=c4 passthrough=yesin-interface=pppoe-out414 chain=input action=mark-connection new-connection-mark=c5 passthrough=yesin-interface=pppoe-out515 chain=output action=mark-routing new-routing-mark=R1 passthrough=yesconnection-mark=c116 chain=output action=mark-routing new-routing-mark=R2 passthrough=yesconnection-mark=c217 chain=output action=mark-routing new-routing-mark=R3 passthrough=yesconnection-mark=c318 chain=output action=mark-routing new-routing-mark=R4 passthrough=yesconnection-mark=c419 chain=output action=mark-routing new-routing-mark=R5 passthrough=yesconnection-mark=c5路由设置添加五条默认路由,指定标记的路由内网PC上开启迅雷下载资料,可以看到所有的拨号出口都有流量。

ros中第七轴控制算法的类型

在机器人操作系统(ROS)中,第七轴(或外部轴)控制算法通常用于控制机器人或机器臂的额外轴。

这些算法可以根据不同的需求和场景进行选择。

以下是一些常见的第七轴控制算法类型:

1. PID控制器:比例-积分-微分控制器是最常见的控制算法之一。

它通过调整比例、积分和微分系数来控制第七轴的位置、速度和加速度。

2. 模糊逻辑控制器:模糊逻辑控制器基于模糊集合和模糊逻辑规则,可以处理不确定性和非线性问题。

这种控制器对于复杂或非线性的系统非常有效。

3. 鲁棒控制器:对于具有不确定性和噪声的系统,鲁棒控制器可以提供稳定的性能。

这些控制器设计用于处理系统参数的变化和非线性行为。

4. 最优控制器:基于最优控制理论设计的控制器,如线性二次调节器(LQR)或动态规划(DP),可以找到使某个性能指标最优的控制输入。

5. 滑模控制器:滑模控制器是一种变结构控制器,它通过在状态空间中滑动一个超平面来控制系统的状态。

这种控制器对于处理不确定性和非线性问题非常有效。

6. 模型预测控制器:模型预测控制器使用系统的动态模型来预测未来的状态,并计算使某个性能指标最优的控制输入。

这种控制器通常用于处理多输入多输出系统。

在选择合适的第七轴控制算法时,需要考虑系统的动态特性、

不确定性和约束条件。

此外,这些算法通常需要参数调整和优化以获得最佳的控制性能。

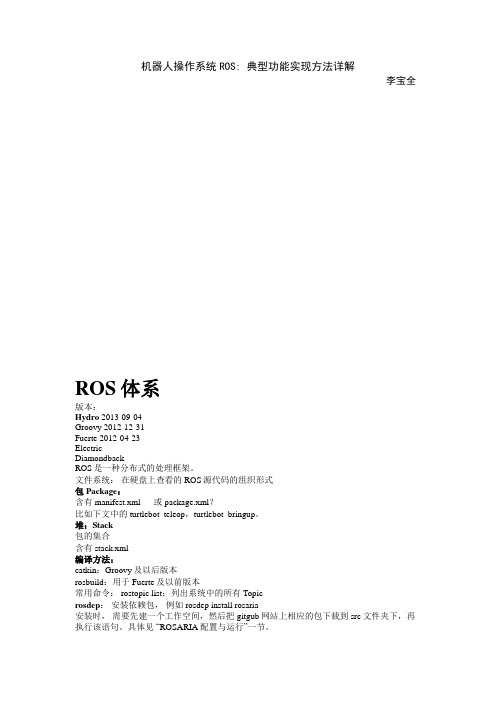

机器人操作系统典型功能实现方法详解

机器人操作系统ROS: 典型功能实现方法详解李宝全ROS体系版本:Hydro 2013-09-04Groovy 2012-12-31Fuerte 2012-04-23ElectricDiamondbackROS是一种分布式的处理框架。

文件系统:在硬盘上查看的ROS源代码的组织形式包 Package:含有manifest.xml 或package.xml?比如下文中的turtlebot_teleop,turtlebot_bringup。

堆:Stack包的集合含有stack.xml编译方法:catkin:Groovy及以后版本rosbuild:用于Fuerte及以前版本常用命令: rostopic list;列出系统中的所有Topicrosdep:安装依赖包,例如 rosdep install rosaria安装时,需要先建一个工作空间,然后把gitgub网站上相应的包下载到src文件夹下,再执行该语句。

具体见“ROSARIA配置与运行”一节。

环境变量设置:export例如:export ROS_HOSTNAME=marvinexport ROS_MASTER_URI=Bulks给的一些有用的命令rosnode info /rosaria_teleop_key_1rosrun rqt_robot_steering rqt_robot_steeringrosrun rqt_gui rqt_guirostopic helprosnode helprosnode info /RosAriarosnode info /rosaria_teleop_key_1rosnode listecho $ROS_HOSTNAMEROS安装安装教程:1.3 安装keys1.4 安装使Debian包为最新:sudo apt-get updateFull安装:sudo apt-get install ros-hydro-desktop-full会出现一个界面,利用Tab选择Yes即可成功则提示:ldconfig deferred processing now taking place找到可以使用的包:apt-cache search ros-hydro1.5初始化rosdepsudo rosdep initrosdep update1.6环境设置echo "source /opt/ros/hydro/setup.bash" >> ~/.bashrcsource ~/.bashrc1.7得到rosintallsudo apt-get install python-rosinstallTurtleBot 配置与运行介绍TurtleBot的主页面(安装&运行):TurtleBot包(Package)的安装过程安装(/// ):按照Debs Installation按照方法来安装:1.首先安装:> sudo apt-get install ros-hydro-turtlebot ros-hydro-turtlebot-apps ros-hydro-turtlebot-viz ros-hydro-turtlebot-simulator ros-hydro-kobuki-ftdi2.之后加入sourse的bash中:> . /opt/ros/hydro/setup.bash. 说明:a)在终端中输入这一行后很快就结束.b)效果是在.bashrc(Home中的隐藏文件)的最后一行加入了"source/opt/ros/hydro/setup.bash",c)效果等效于命令> echo "source /opt/ros/hydro/setup.bash" >> ~/.bashrc. 这样的话就不用每次启动都输入命令“source /opt/ros/hydro/setup.bash”了.d)这个好像在安装ROS时已经执行过了,不需要再执行一次吧?e)3.之后加入kobuki的udev规则:> rosrun kobuki_ftdi create_udev_rules安装完之后还需要加入网络时间控制(/// ), 否则与kokuki无法通讯.1.首先安装chrony:sudo apt-get install chrony问题:我重装系统后再安装turtlebot后,连接不上kokuki,但能正常连接Kinect。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Raising Capital

Prepared by Anne Inglis, Ryerson University

Modified by Eric Wang

McGraw-Hill Ryerson

Copyright © 2010 McGraw-Hill Ryerson Limited

15-9

LO3

Underwriters 15.4

• Services provided by underwriters

• • o issue securities Price the securities Sell the securities Price stabilization by lead underwriter

• Syndicate – group of underwriters that market the securities and share the risk associated with selling the issue • Spread – difference between what the syndicate pays the company and what the security sells for in the market

15-13

LO3

Over allotment Option

• Over allotment Option / Green Shoe provision

• Allows syndicate to purchase an additional 15% of the issue from the issuer • Allows the issue to be oversubscribed • Provides some protection for the lead underwriter as they perform their price stabilization function

Key Concepts and Skills

• Understand the venture capital market and its role in financing new businesses • Understand how securities are sold to the public and the role of investment bankers • Understand initial public offerings and the costs of going public • Know how rights are issued to existing shareholders and how to value those rights

15-4

LO2

The Public Issue 15.2

• Public issue – the creation and sale of securities that are intended to be traded on the public markets • All companies on the TSE come under the Ontario Securities Commission’s jurisdiction

15-14

LO3

Additional Details

• Lockup Agreements – Specify how long insiders must wait after an IPO before they can sell stock, usually 180 days • Quiet Period – For 40 days following an IPO, the OSC requires that all communications with the public are limited to ordinary announcements

15-6

LO2

Alternative Issue Methods

• For equity sales, there are two kinds of public issues:

• General Cash Offer – New securities offered for sale to the general public on a cash basis. • Rights Offer – New securities are first offered to existing shareholders. These are more common outside North America.

15-1

Chapter Outline

• The Financing Life Cycle of a Firm: Early-Stage Financing and Venture Capital • The Public Issue • The Basic Procedure for a New Issue • The Cash Offer • IPOs and Under pricing • Rights • Summary and Conclusions

15-12

LO3

Dutch Auction Underwriting

• Underwriter conducts an auction and investors bid for shares • Offer price is determined based on the submitted bids • More commonly used in bond markets • Also called uniform price auction

15-11

LO3

Best Efforts Underwriting

• Underwriter must make their “best effort” to sell the securities at an agreed-upon offering price • The company bears the risk of the issue not being sold • The offer may be pulled if there is not enough interest at the offer price. In this situation, the company does not get the capital and they have still incurred substantial flotation costs

15-3

LO1

Choosing a Venture Capitalist

• Look for financial strength • Choose a VC that has a management style that is compatible with your own • Obtain and check references • What contacts does the VC have? • What is the exit strategy?

15-7

LO2

Table 15.1 – Methods of Issuing New Securities

15-8

LO3

IPOs and SEOs

• IPO – Initial Public Offering (or unseasoned new issue). A company’s first equity issue made available to the public. • SEO – Seasoned Equity Offering. A new issue for a company that has previously issued securities to the public.

15-5

LO2

Selling Securities to the Public 15.3

• Management must obtain permission from the Board of Directors • Firm must prepare and distribute copies of a preliminary prospectus (red herring) to the OSC and to potential investors • OSC studies the preliminary prospectus and notifies the company of required changes (usually takes 2 weeks) • When the prospectus is approved, the price is determined and security dealers can begin selling the new issue

15-15

LO3

IPO Under pricing 15.5

• Initial Public Offering – IPO • May be difficult to price an IPO because there isn’t a current market price available • Additional asymmetric information associated with companies going public • Underwriters want to ensure that their clients earn a good return on IPOs on average • Underpricing causes the issuer to “leave money on the table”