4306-003LF;中文规格书,Datasheet资料

NCV8450STT3G;中文规格书,Datasheet资料

NCV8450, NCV8450ASelf-Protected High Side Driver with Temperatureand Current LimitThe NCV8450/A is a fully protected High−Side Smart Discrete device with a typical R DS(on) of 1.0 W and an internal current limit of 0.8 A typical. The device can switch a wide variety of resistive, inductive, and capacitive loads.Features•Short Circuit Protection•Thermal Shutdown with Automatic Restart •Overvoltage Protection•Integrated Clamp for Inductive Switching•Loss of Ground Protection•ESD Protection•Slew Rate Control for Low EMI•Very Low Standby Current•NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q100 Qualified and PPAP Capable•This is a Pb−Free DeviceTypical Applications•Automotive•IndustrialPRODUCT SUMMARYSymbolCharacteristics Value Unit V IN_CL Overvoltage Protection54V V D(on)Operation Voltage 4.5 − 45V R on On−State Resistance 1.0WMARKINGDIAGRAM1AYWXXXXX GGXXXXX= V8450 or 8450AA= Assembly LocationY= YearW= Work WeekG= Pb−Free Package(Note: Microdot may be in either location)SOT−223(TO−261)CASE 318ESee detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.ORDERING INFORMATIONFigure 1. Block Diagram V (Pins 2, 4)OUT(Pin 3)IN(Pin 1)PACKAGE PIN DESCRIPTIONPin #Symbol Description1IN Control Input, Active Low2V D Supply Voltage3OUT Output4V D Supply VoltageMAXIMUM RATINGSRatingSymbol ValueUnit Min Max DC Supply Voltage (Note 1)V D −1645V Load Dump Protection(RI = 2 W , t d = 400 ms, V IN = 0, 10 V, I L = 150 mA, V bb = 13.5 V)V Loaddump100V Input CurrentIin −1515mAOutput Current (Note 1)I out Internally Limited A Total Power Dissipation@ T A = 25°C (Note 2)@ T A = 25°C (Note 3)P D1.131.60WElectrostatic Discharge (Note 4)(Human Body Model (HBM) 100 pF/1500 W )Input All other15kVSingle Pulse Inductive Load Switching Energy (Note 4)(V DD = 13.5 V, I = 465 mApk, L = 200 mH, T JStart = 150°C)E AS 29mJ Operating Junction Temperature T J −40+150°C Storage TemperatureT storage−55+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Reverse Output current has to be limited by the load to stay within absolute maximum ratings and thermal performance.2.Minimum Pad.3. 1 in square pad size, FR −4, 1 oz Cu.4.Not subjected to production testing.THERMAL RESISTANCE RATINGSParameterSymbol Max Value Unit Thermal Resistance (Note 5)Junction −to −Ambient (Note 2)Junction −to −Ambient (Note 3)R q JA R q JA11078.3K/W5.Not subjected to production testing.Figure 2. Applications Test CircuitELECTRICAL CHARACTERISTICS (6 v V D v 45 V; −40°C <T J < 150°C unless otherwise specified)Rating Symbol ConditionsValueUnit Min Typ MaxOUTPUT CHARACTERISTICSOperating Supply Voltage V SUPPLY 4.5−45VOn Resistance(Pin 1 Connected to GND)R ON T J = 25°C , I OUT = 150 mA, V D = 7 V − 45 VT J = 150°C, I OUT = 150 mA, V D = 7 V − 45 V(Note 6)T J = 25°C , I OUT= 150 mA, V D = 6 V1.01.41.1232.1WStandby Current (Pin 1 Open)I D V D v 20 VV D> 20 V 0.610100m AINPUT CHARACTERISTICSInput Current – Off State I IN_OFF V OUT v 0.1 V, R L = 270 W, T J = 25°CV OUT v 0.1V, R L= 270 W, T J = 150°C (Note 6)−50−40m AInput Current – On State(Pin 1 Grounded)I IN_ON 1.53mA Input Resistance (Note 6)R IN1k W SWITCHING CHARACTERISTICSTurn−On Time (Note 7)(V IN = V D to 0 V) to 90% V OUT t ON R L = 270 W(Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C30125100m sTurn−Off Time (Note 7)(V IN= 0 V to V D) to 10% V OUT t OFF R L = 270 W (Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C60175150m sSlew Rate On (Note 7)(V IN = V D to 0V) 10% to 30% V OUT dV/dt ON R L = 270 W(Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C0.744V/m sSlew Rate Off (Note 7)(V IN= 0 V to V D) 70% to 40% V OUT dV/dt OFF R L = 270 W (Note 6)V D = 13.5 V, R L = 270 W, T J = 25°C0.944V/m sOUTPUT DIODE CHARACTERISTICS (Note 6)Drain−Source Diode Voltage V F I OUT = −0.2 A0.6V Continuous Reverse DrainCurrentI S T J = 25°C0.2A PROTECTION FUNCTIONS (Note 8)Temperature Shutdown (Note 6)T SD150175−°C Temperature ShutdownHysteresis (Note 6)T SD_HYST5°COutput Current Limit I LIM T J = −40°C, V D = 13.5 V, t m = 100 m s (Note 6)T J = 25 °C, V D = 13.5 V, t m = 100 m sT J = 150 °C , V D = 13.5 V, t m = 100 m s (Note 6)0.50.81.5AOutput Clamp Voltage(Inductive Load Switch Off)At V OUT = V D− V CLAMPV CLAMP I OUT = 4 mA4552VOvervoltage Protection V IN_CL I CLAMP = 4 mA5054V6.Not subjected to production testing7.Only valid with high input slew rates8.Protection functions are not designed for continuous repetitive operation and are considered outside normal operating rangeR D S (o n ) (W )TEMPERATURE (°C)Figure 3. R DS(on) vs. TemperatureR D S (o n ) (W )OUTPUT LOAD (A)Figure 4. R DS(on) vs. Output LoadV D (V)Figure 5. R DS(on) vs. V DR D S (o n ) (W )1020304050607080T U R N O N T I M E (m s )TEMPERATURE (°C)Figure 6. Turn On Time vs. TemperatureTEMPERATURE (°C)Figure 7. Turn Off Time vs. TemperatureT U R N O F F T I M E (m s )S L E W R A T E (O N ) (V /m s )TEMPERATURE (°C)Figure 8. Slew Rate (ON) vs. Temperature−40−20020406080100120140−40−20020406080100120140−TEMPERATURE (°C)Figure 9. Slew Rate (OFF) vs. Temperature S L E W R A T E (O F F ) (V /m s )TEMPERATURE (°C)Figure 10. Current Limit vs. TemperatureC U R R E N T L I M I T (A )P E A K S C C U R R E N T (A )V D , VOLTAGE (V)Figure 11. Peak Short Circuit Current vs. V DVoltageTEMPERATURE (°C)Figure 12. V D Leakage Current vs.Temperature Off −StateV D , L E A K A G E C U R R E N T (m A )V D , L E A K A G E C U R R E N T (m A )V D , VOLTAGE (V)Figure 13. V D Leakage Current vs. V D VoltageOff −State TEMPERATURE (°C)Figure 14. On −State Input Current vs.TemperatureI N P U T C U R R E N T (m A )V D , VOLTAGE (V)Figure 15. Output Voltage vs. V D VoltageO U T P U T V O L T A G E (V )V D , VOLTAGE (V)Figure 16. Input Current vs. V D VoltageOn −StateI N P U T C U R R E N T (m A )LOAD INDUCTANCE (mH)Figure 17. Single Pulse Maximum Switch −offCurrent vs. Load InductanceC U R R E N T (m A )V D , VOLTAGE (V)Figure 18. Input Current vs. V D VoltageOff −StateI N P U T C U R R E N T (m A )−S H U T D O W N T I M E (m s )TEMPERATURE (°C)Figure 19. Initial Short −Circuit Shutdown Timevs. TemperaturePULSE TIME (s)R (t ), E F F E C T I V E T R A N S I E N T T H E R M AL R E S P O N S ECOPPER HEAT SPREADER AREA (mm 2)R q J A (°C /W )06080100120140Figure 20. R q JA vs. Copper Area2040Figure 21. Transient Thermal ResponseISO PULSE TEST RESULTSTest PulseTest Level Test ResultsPulse Cycle Time and Generator Impedance1200 V C 500 ms, 10 W 2150 V C 500 ms, 10 W 3a 200 V C 100 ms, 50 W 3b 200 V C 100 ms, 50 W 5175 VE(100 V)400 ms, 2 WORDERING INFORMATIONDevicePackage Shipping †NCV8450STT3G SOT −223(Pb −Free)4000 / Tape & Reel NCV8450ASTT3GSOT −223(Pb −Free)4000 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSSOT −223 (TO −261)CASE 318E −04ISSUE MNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.DIM A MIN NOM MAX MIN MILLIMETERS1.50 1.63 1.750.060INCHESA10.020.060.100.001b 0.600.750.890.024b1 2.90 3.06 3.200.115c 0.240.290.350.009D 6.30 6.50 6.700.249E 3.30 3.50 3.700.130e 2.20 2.30 2.400.0870.850.94 1.050.0330.0640.0680.0020.0040.0300.0350.1210.1260.0120.0140.2560.2630.1380.1450.0910.0940.0370.041NOM MAX L1 1.50 1.75 2.000.0606.707.007.300.2640.0690.0780.2760.287H E−−e10°10°0°10°q*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息: ONSEMINCV8450STT3G。

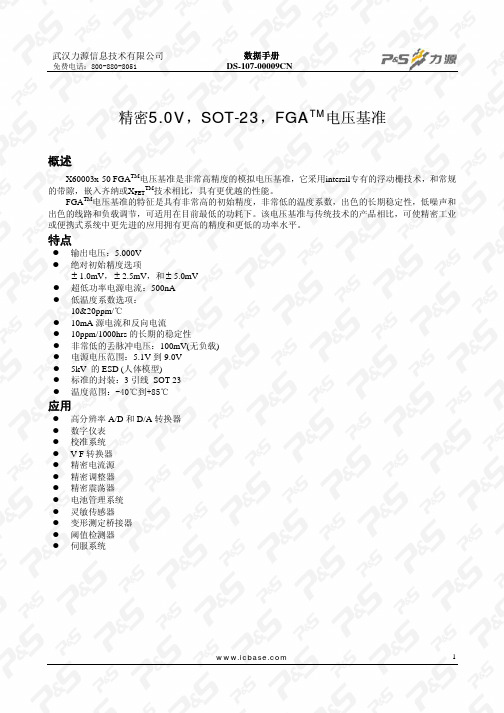

电压基准X60003中文资料

特点

输出电压:5.000V 绝对初始精度选项 ± 1.0mV, ± 2.5mV,和 ± 5.0mV 超低功率电源电流:500nA 低温度系数选项: 10&20ppm/℃ 10mA 源电流和反向电流 10ppm/1000hrs 的长期的稳定性 非常低的丢脉冲电压:100mV(无负载) 电源电压范围:5.1V 到 9.0V 5kV 的 ESD (人体模型) 标准的封装:3 引线 SOT-23 温度范围:-40℃到+85℃

3

武汉力源信息技术有限公司

免费电话:800-880-8051

数据手册 DS-107-00009CN

3. 丢脉冲电压 (VDO) 是输入到X60003x-50 的最小电压 (VIN) ,这一电压将产生输出电压降 (ΔVOUT) , 如电气指标表中所规定的值。 4.由器件的特征保证。

纳功率工作

当持续加电,且达到初始稳定工作后,基准器件达到最高精度。通过保持持续通电,可消除漂移。 X60003x-50 是第一个具有超低功耗的高精度电压基准,因此在电池供电电路中,可保持持续的供电。 由于它拥有 FGA 技术,X60003x-50 消耗极低的电源电流。室温下,电流的典型值是 500nA ,这比同类产 品低 1-2 个级别。使用电池供电的应用电路将大大得益于拥有一个精确,稳定的基准而根本不会增加电池 的负载。 特别地,在电池供电电路中,通常数据转换器在不使用时要求数据转换器(如图 1)被禁止。由于极 低的功耗,基准器件保持供电,没有功率损失,能够提供高精度和最低的长期漂移,这样数据转换器提供 12 到 24 比特的精度。 其他基准器件因为要消耗较高的电源电流,因此在转换结束后需要停用,来降低能耗。上电后器件需 要时间调整它的最终值,很可能因为上电时间太短而没有调整最终值,使绝对精度受损失。

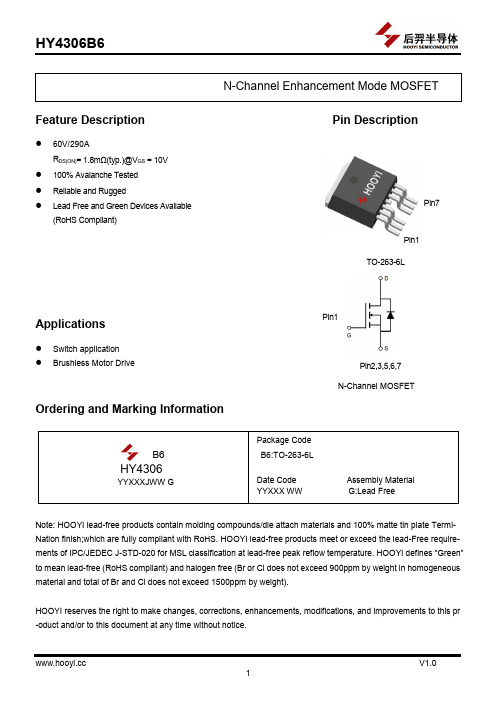

HY4306B6 datasheet_v1.0

Pin1Pin7Pin1Pin2,3,5,6,7 Pin4Feature Description Pin Description●60V/290AR DS(ON)= 1.8m Ω(typ.)@V GS = 10V● 100% Avalanche Tested ● Reliable and Rugged●Lead Free and Green Devices Available (RoHS Compliant)Applications● Switch application ● Brushless Motor DriveOrdering and Marking InformationHY4306 YYXXXJWW G Note: HOOYI lead-free products contain molding compounds/die attach materials and 100% matte tin plate Termi- Nation finish;which are fully compliant with RoHS. HOOYI lead-free products meet or exceed the lead-Free require- ments of IPC/JEDEC J-STD-020 for MSL classification at lead-free peak reflow temperature. HOOYI defines “Green ” to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).HOOYI reserves the right to make changes, corrections, enhancements, modifications, and improvements to this pr -oduct and/or to this document at any time without notice.TO-263-6LN-Channel MOSFETAbsolute Maximum RatingsNote: * Repetitive rating;pulse width limited by max.junction temperature.** Surface mounted on FR-4 board.*** Limited by T J max , starting T J=25°C, L =0.5mH, R G= 25Ω, V GS =10V. Electrical Characteristics(Tc =25°C Unless Otherwise Noted)Electrical Characteristics (Cont.) (Tc =25°C Unless Otherwise Noted)Note: *Pulse test,pulse width ≤ 300us,duty cycle ≤ 2%Typical Operating CharacteristicsFigure 1: Power Dissipation Figure 2: Drain CurrentTc-Case Temperature(℃) Tc-Case Temperature(℃)Figure 3: Safe Operation Area Figure 4: Thermal Transient ImpedanceV DS -Drain-Source Voltage(V)Maximum Effective Transient ThermalImpedance, Junction-to-CaseFigure 5: Output Characteristics Figure 6: Drain-Source On ResistanceV DS -Drain-Source Voltage (V) I D -Drain Current(A)I D -D r a i n C u r r e n t (A )I D -D r a i n C u r r e n t (A )R D S (O N )-O N -R e s i s t a n c e (Ω)Typical Operating Characteristics(Cont.)Figure 7: On-Resistance vs. Temperature Figure 8: Source-Drain Diode ForwardTj-Junction Temperature (℃)V SD -Source-Drain Voltage(V)Figure 9: Capacitance Characteristics Figure 10: Gate Charge CharacteristicsV DS -Drain-Source Voltage (V) Q G -Gate Charge (nC )C -C a p a c i t a n c e (p F )N o r m a l i z e d O n -R e s i s t a n c eI S -S o u r c e C u r r e n t (A )Avalanche Test Circuit and WaveformsSwitching Time Test Circuit and WaveformsGate Charge Test Circuit and WaveformsDevice Per UnitPackage Information TO-263-6LClassification ProfileClassification Reflow ProfilesCustomer ServiceWorldwide Sales and Service: sales@Technical Support: technical @Xi’an Hooyi Semiconductor Technology Co., Ltd.No.105,5th Fengcheng Road, Economic and Technological Development Zone, Xi'an,China TEL: (86-029) 86685706FAX: (86-029) 86685705E-mail: sales@Web net: 。

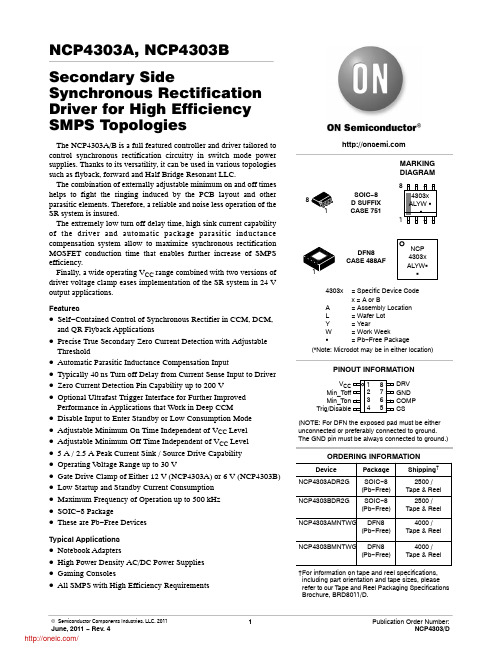

NCP4303ADR2G;NCP4303BDR2G;中文规格书,Datasheet资料

Secondary Side Synchronous Rectification Driver for High Efficiency SMPS Topologies

The NCP4303A/B is a full featured controller and driver tailored to control synchronous rectification circuitry in switch mode power supplies. Thanks to its versatility, it can be used in various topologies such as flyback, forward and Half Bridge Resonant LLC.

(NOTE: For DFN the exposed pad must be either unconnected or preferably connected to ground. The GND pin must be always connected to ground.)

ORDERING INFORMATION

Y

= Year

W

= Work Week

G

= Pb−Free Package

(*Note: Microdot may be in either location)

PINOUT INFORMATION

VCC Min_Toff Min_Ton

Trig/Disable

18 27

36 45

DRV GND COMP CS

This pin detects if the current flows through the SR MOSFET and/or its body diode. Basic turn off detection threshold is 0 mV. A resistor in series with this pin can modify the turn off threshold if needed.

PT4316资料

C3 C4

C2

3

RFIN

Frequency (MHz) 315 433.92

LNA Input Impedance (Pin 3) Normalized to 50Ω 4.18—j251.63 3.60—j180.20

The LNA output of PT4316 internally connects to the mixer stage so that its output impedance cannot be measured directly. The LNA output requires a DC supply through a choke inductor. For obtaining better LNA gain, a capacitor is recommended to be added in parallel with this inductor to implement a resonant tank at the desired frequency as shown in the following figure. Note that the LNA might self-oscillate and degrade the receiver sensitivity, particularly if a large inductor value is chosen. An alternate matching method is to replace the parallel capacitor with a 330 to 1KΩ resistor, which would reduce the resonant tank Q (quality factor) and avoid the self-oscillation.

IRGP4086PBF;中文规格书,Datasheet资料

tf

Fall time

td(on)

Turn-On delay time

tr

Rise time

— 65 —

— 30 —

IC = 25A, VCC = 196V

— 33 — ns RG = 10Ω, L=200μH, LS= 200nH

td(off) tf tst

EPULSE

Turn-Off delay time Fall time Shoot Through Blocking Time

2

/

240

VGE = 18V

200

VGE = 15V

VGE = 12V

160

VGE = 10V VGE = 8.0V

120

VGE = 6.0V

ICE (A)

80

40

0

0

4

8

12

16

VCE (V)

Fig 1. Typical Output Characteristics @ 25°C

––– 29 ––– ––– 65 ––– ––– 22 ––– — 36 — — 31 — — 112 —

S VCE = 25V, ICE = 25A nC VCE = 200V, IC = 25A, VGE = 15Ve

IC = 25A, VCC = 196V ns RG = 10Ω, L=200μH, LS= 200nH

Parameter Thermal Resistance Junction-to-Case-(each IGBT) d Case-to-Sink (flat, greased surface) Junction-to-Ambient (typical socket mount) d Weight

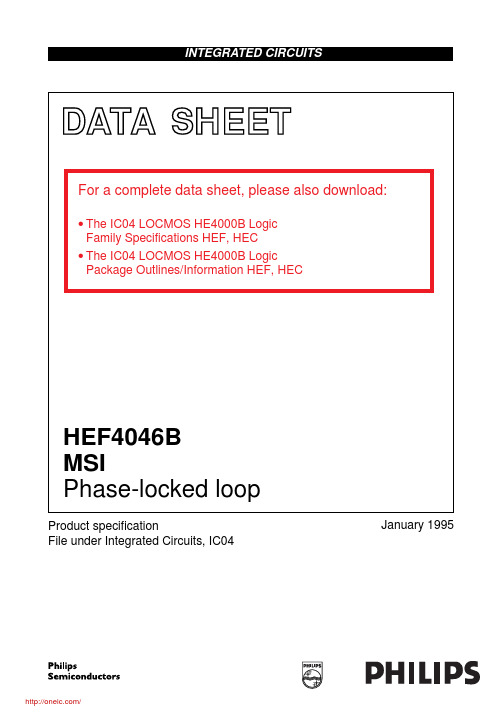

HEF4046BT,653;HEF4046BT,652;HEF4046BP,652;中文规格书,Datasheet资料

HEF4046B MSI

15. Zener diode input for regulated supply. Fig.2 Pinning diagram.

FUNCTIONAL DESCRIPTION VCO part The VCO requires one external capacitor (C1) and one or two external resistors (R1 or R1 and R2). Resistor R1 and capacitor C1 determine the frequency range of the VCO. Resistor R2 enables the VCO to have a frequency off-set if required. The high input impedance of the VCO simplifies the design of low-pass filters; it permits the designer a wide choice of resistor/capacitor ranges. In order not to load the low-pass filter, a source-follower output of the VCO input voltage is provided at pin 10. If this pin (SFOUT) is used, a load resistor (RSF) should be connected from this pin to VSS; if unused, this pin should be left open. The VCO output (pin 4) can either be connected directly to the comparator input (pin 3) or via a frequency divider. A LOW level at the inhibit input (pin 5) enables the VCO and the source follower, while a HIGH level turns off both to minimize stand-by power consumption. Phase comparators The phase-comparator signal input (pin 14) can be direct-coupled, provided the signal swing is between the standard HE4000B family input logic levels. The signal must be capacitively coupled to the self-biasing amplifier at the signal input in case of smaller swings. Phase comparator 1 is an EXCLUSIVE-OR network. The signal and comparator input frequencies must have a 50% duty January 1995 3

IRLML0040TRPBF;中文规格书,Datasheet资料

100 D = 0.50

0.20

10

0.10

0.05

0.02

1

0.01

0.1

0.01

0.001 1E-006

1E-005

Fig 4. Normalized On-Resistance Vs. Temperature 3

ID, Drain-to-Source Current (A)

/

IRLML0040TRPbF

C, Capacitance (pF)

10000 1000 100

VGS = 0V, f = 1 MHZ Ciss = C gs + Cgd, C ds SHORTED Crss = Cgd Coss = Cds + Cgd

IRLML0040TRPbF

ID, Drain Current (A)

4.2

3.6

3

2.4

1.8

1.2

0.6

0 25

50

75

100 125 150

TA , Ambient Temperature (°C)

Fig 9. Maximum Drain Current Vs. Ambient Temperature

4

1

1msec

0.1 TA = 25°C Tj = 150°C Single Pulse

10msec

0.01

0

1

10

100

VDS, Drain-to-Source Voltage (V)

Fig 8. Maximum Safe Operating Area

/

PD @TA = 25°C

Maximum Power Dissipation

LTC4306中文资料

V CC = 3.3VVCARD1 = 3.3VVCARD4 = 5VVBACK = 2.5V SCL42V/DIVSCL12V/DIVSCLIN 2V/DIV(Note 1)Supply Voltage (V CC )...................................–0.3V to 7V Input Voltages (ADR0, ADR1, ADR2,ENABLE, ALERT1, ALERT2, ALERT3,ALERT4)..................................................–0.3V to 7V Output Voltages (ALERT, READY)...............–0.3V to 7V Input/Output Voltages (SDAIN, SCLIN,SCL1, SDA1, SCL2, SDA2, SCL3,SDA3, SCL4, SDA4, GPIO1, GPIO2)........–0.3V to 7VOperating Temperature RangeLTC4306C ...............................................0°C to 70°C LTC4306I.............................................–40°C to 85°C Storage Temperature RangeSSOP.................................................–65°C to 150°C QFN ...................................................–65°C to 125°C Lead Temperature (Soldering, 10 sec)SSOP................................................................300°CConsult LTC Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container.ABSOLUTE AXI U RATI GSW W WU The ● denotes specifications which apply over the full specified temperaturerange, otherwise specifications are at T A = 25°C. V CC = 3.3V unless otherwise noted.ELECTRICAL CHARACTERISTICSThe ● denotes specifications which apply over the full specified temperature range, otherwise specifications are at T A = 25°C. V CC = 3.3V unless otherwise noted.Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.Note 2: Guaranteed by design and not subject to test.Note 3: The boosted pull-up currents are regulated to prevent excessively fast edges for light loads. See the Typical Performance Characteristics for rise time as a function of V CC and parasitic bus capacitance C BUS and for I BOOST as a function of V CC and temperature.Note 4: When a logic low voltage, V LOW, is forced on one side of the Upstream-Downstream Buffers, the voltage on the other side is regulated to a voltage V LOW2 = V LOW + V OS, where V OS is a positive offset voltage. V OS,UP-BUF is the offset voltage when the LTC4306 is driving the upstream pin (e.g., SDAIN) and V OS,DOWN-BUF is the offset voltage when theLTC4306 is driving the downstream pin (e.g., SDA1). See the Typical Performance Characteristics for V OS,UP-BUF and V OS,DOWN-BUF as a function of V CC and bus pull-up current.Note 5: When floating, the ADR0-ADR2 pins can tolerate pin leakage currents up to I ADR(FLOAT) and still convert the address correctly.ELECTRICAL CHARACTERISTICSUUUPI FU CTIO S (GN24 Package/UFD24 Package)ALERT (Pin 3/Pin 1): Fault Alert Output. An open-drain output that is pulled low when a fault occurs to alert the host controller. The LTC4306 pulls ALERT low when any of the ALERT1-ALERT4 pins is low, when the 2-wire bus is stuck low, or when the Connection Requirement bit of Register 2 is low and a master tries to connect to a downstream channel that is low. See Operation section for the details of how ALERT is set and cleared. The LTC4306 is compatible with the SMBus Alert Response Address protocol. Connect a 10k resistor to a power supply voltage to provide the pull-up. Tie to ground if unused. SDAIN (Pin 4/Pin 2): Serial Bus Data Input and Output. Connect this pin to the SDA line on the master side. An external pull-up resistor or current source is required. GND (Pin 5/Pin 3): Device Ground.SCLIN (Pin 6/Pin 4): Serial Bus Clock Input. Connect this pin to the SCL line on the master side. An external pull-up resistor or current source is required.ENABLE (Pin 7/Pin 5): Digital Interface Enable and Regis-ter Reset. Driving ENABLE high enables I2C communica-tion to the LTC4306. Driving this pin low disables I2C communication to the LTC4306 and resets the registers to their default state as shown in the Operation section. When ENABLE returns high, masters can read and write the LTC4306 again. If unused, tie ENABLE to V CC.V CC (Pin 8/Pin 6): Power Supply Voltage. Connect a bypass capacitor of at least 0.01µF directly between V CC and GND for best results.GPIO1-GPIO2 (Pins 10, 11/Pins 8, 9): General Purpose Input/Output. These two pins can be used as logic inputs, open-drain outputs or push-pull outputs. The N-channel MOSFET pull-down devices are capable of driving LEDs. When used in input or open-drain output mode, the GPIOs can be pulled up to a supply voltage ranging from 1.5V to 5.5V independent of the V CC voltage. GPIOs default to a high impedance open-drain output mode. There are GPIO configuration and status bits in Register 1 and Register 2. Float if unused.ADR0-ADR2 (Pins 12, 13, 14/Pins 10, 11, 12): Three-State Serial Bus Address Inputs. Each pin may be floated, tied to ground or tied to V CC. There are therefore 27 possible addresses. See Table 1 in applications informa-tion. When the pins are floated, they can tolerate ±5µA of leakage current and still convert the address correctly. READY (Pin 15/Pin 13): Connection Ready Digital Output. An N-channel MOSFET open-drain output transistor that pulls down when none of the downstream channels is connected to the upstream bus and turns off when one or more downstream channels is connected to the upstream bus. Connect a 10k resistor to a power supply voltage to provide the pull-up. Tie to ground if unused.SCL1-SCL4 (Pins 18, 23, 1, 17/Pins 16, 21, 23, 15): Serial Bus Clock Outputs Channels 1-4. Connect pins SCL1-SCL4 to the SCL lines on the downstream channels 1-4, respectively. It is acceptable to float any pin that will never be connected to the upstream bus. Other-wise, an external pull-up resistor or current source is required on each pin.SDA1-SDA4 (Pins 19, 22, 2, 16/Pins 17, 20, 24, 14): Serial Bus Data Output Channels 1-4. Connect pins SDA1-SDA4 to the SDA lines on downstream channels 1-4, respectively. It is acceptable to float any pin that will never be connected to the upstream bus. Otherwise, an external pull-up resistor or current source is required on each pin.ALERT1-ALERT4 (Pins 20, 24, 21, 9/Pins 18, 22, 19, 7): Fault Alert Inputs, Channels 1-4. Devices on each of the four output channels can pull their respective pin low to indicate that a fault has occurred. The LTC4306 then pulls the ALERT low to pass the fault indication on to the host. See Operation section below for the details of how ALE RT is set and cleared. Connect unused fault alert inputs to V CC.Exposed Pad (Pin 25, UFD Package Only): Power Ground. Exposed Pad may be left open or connected to device ground.Control Register Bit Definitions OPERATIORegister 0 (00h)BIT NAME TYPE*DESCRIPTIONd7Downstream R Indicates if upstream bus is connected Connected to any downstream buses0 = upstream bus disconnected fromall downstream buses1 = upstream bus connected to one ormore downstream busesd6ALERT1 Logic State R Logic state of ALERT1 pin, noninverting d5ALERT2 Logic State R Logic state of ALERT2 pin, noninverting d4ALERT3 Logic State R Logic state of ALERT3 pin, noninverting d3ALERT4 Logic State R Logic state of ALERT4 pin, noninverting d2Failed Connection R Indicates if an attempt to connect to a Attempt downstream bus failed because the“Connection Requirement” bit inRegister 2 was low and thedownstream bus was low0 = Failed connection attempt occurred1 = No failed attempts at connectionoccurredd1Latched Timeout R Latched bit indicating if a timeout hasoccurred and has not yet been cleared.0 = no latched timeout1 = latched timeoutd0Timeout Real Time R Indicates real-time status of Stuck LowTimeout Circuitry0 = no timeout is occurring1 = timeout is occurringNote: Masters write to Register 0 to reset the fault circuitry after a fault has occurred and been resolved. Because Register 0 is Read-Only, no other functionality is affected.* For Type, “R/W” = Read Write, “R” = Read Only Register 1 (01h)BIT NAME TYPE*DESCRIPTIONd7Upstream R/W Activates upstream rise time Accelerators accelerator currentsEnable0 = upstream rise time acceleratorcurrents inactive (default)1 = upstream rise time acceleratorcurrents actived6Downstream R/W Activates downstream rise time Accelerators accelerator currentsEnable0 = downstream rise time acceleratorcurrents inactive (default)1 = downstream rise time acceleratorcurrents actived5GPIO1 Output R/W GPIO1 output driver state,Driver State noninverting, default = 1d4GPIO2 Output R/W GPIO2 output driver state,Driver State noninverting, default = 1d3-d2Reserved R Not Usedd1GPIO1 Logic R Logic state of GPIO1 pin,State noninvertingd0GPIO2 Logic R Logic state of GPIO2 pin,State noninverting* For Type, “R/W” = Read Write, “R” = Read OnlyRegister 2 (02h)BIT NAME TYPE*DESCRIPTIONd7GPIO1 ModeR/W Configures Input/Output mode ofConfigureGPIO10 = output mode (default)1 = input mode d6GPIO2 ModeR/W Configures Input/Output Mode ofConfigureGPIO20 = output mode (default)1 = input mode d5ConnectionR/W Sets logic requirements forRequirementdownstream buses to be connected to upstream bus0 = Bus Logic State bits (see register 3) of buses to be connected must be high for connection to occur (default)1 = Connect regardless of downstream logic state d4GPIO1 OutputR/W Configures GPIO1 Output ModeMode Configure 0 = open-drain pull-down (default)1 = push-pull d3GPIO2 OutputR/W Configures GPIO2 Output ModeMode Configure 0 = open-drain pull-down (default)1 = push-pull d2Mass Write EnableR/W Enable Mass Write Address usingaddress (1011 101)b 0 = Disable Mass Write1 = Enable Mass Write (default)d1Timeout Mode Bit 1R/W Stuck Low Timeout Set Bit 1**d0Timeout Mode Bit 0R/W Stuck Low Timeout Set Bit 0*** For Type, “R/W” = Read Write, “R” = Read Only **Stuck bus program tableTIMSET1TIMSET0TIMEOUT MODE 00Timeout Disabled (Default)01Timeout After 30ms 10Timeout After 15ms 11Timeout After 7.5msOPERATIORegister 3 (03h)BIT NAME TYPE*DESCRIPTIONd7Bus 1 FET StateR/W Sets and indicates state of FETswitches connected to downstream bus 10 = switch open (default)1 = switch closed d6Bus 2 FET StateR/W Sets and indicates state of FETswitches connected to downstream bus 20 = switch open (default)1 = switch closed d5Bus 3 FET StateR/W Sets and indicates state of FETswitches connected to downstream bus 30 = switch open (default)1 = switch closed d4Bus 4 FET StateR/W Sets and indicates state of FETswitches connected to downstream bus 40 = switch open (default)1 = switch closed d3Bus 1 Logic StateRIndicates logic state of downstream bus 1; only valid when disconnected from upstream bus †0 = SDA1, SCL1 or both are below 1V 1 = SDA1 and SCL1 are both above 1Vd2Bus 2 Logic StateRIndicates logic state of downstream bus 2; only valid when disconnected from upstream bus †0 = SDA2, SCL2 or both are below 1V 1 = SDA2 and SCL2 are both above 1Vd1Bus 3 Logic State RIndicates logic state of downstream bus 3; only valid when disconnected from upstream bus †0 = SDA3, SCL3 or both are below 1V 1 = SDA3 and SCL3 are both above 1Vd0Bus 4 Logic State RIndicates logic state of downstream bus 4; only valid when disconnected from upstream bus †0 = SDA4, SCL4 or both are below 1V 1 = SDA4 and SCL4 are both above 1V* For Type, “R/W” = Read Write, “R” = Read Only† These bits give the logic state of disconnected downstream buses to the master, so that the master can choose not to connect to a low downstream bus. A given bit is a “don’t care” if its associated downstream bus is already connected to the upstream bus.The LTC4306 is a 4-channel, 2-wire bus multiplexer/ switch with bus buffers to provide capacitive isolation between the upstream bus and downstream buses. Mas-ters on the upstream 2-wire bus (SDAIN and SCLIN) can command the LTC4306 to any combination of the 4 downstream buses. Masters can also program the LTC4306 to disconnect the upstream bus from the downstream buses if the bus is stuck low.Undervoltage Lockout (UVLO) and ENABLE FunctionalityThe LTC4306 contains undervoltage lockout circuitry that maintains all of its SDA, SCL, GPIO and ALERT pins in high impedance states until the device has sufficient V CC supply voltage to function properly. It also ignores any attempts to communicate with it via the 2-wire buses in this condi-tion. When the ENABLE pin voltage is low (below 0.8V), all control bits are reset to their default high impedance states, and the LTC4306 ignores 2-wire bus commands. However, with ENABLE low, the LTC4306 still monitors the ALERT1-ALERT4 pin voltages and pulls the ALERT pin low if any of ALERT1-ALERT4 is low. When ENABLE is high, devices can read from and write to the LTC4306. Connection CircuitryMasters on the upstream SDAIN/SCLIN bus can write to the Bus 1 FET State through Bus 4 FET State bits of register 3 to connect to any combination of downstream channels 1 to 4. By default, the Connection Circuitry shown in the Block Diagram will only connect to downstream channels whose corresponding Bus Logic State bits in register3 are high at the moment that it receives the connection com-mand. If the LTC4306 is commanded to connect to mul-tiple channels at once, it will only connect to the channels that are high. Masters can override this feature by setting the Connection Requirement bit of register 2 high. With this bit high, the LTC4306 executes connection com-mands without regard to the logic states of the down-stream channels.Upon receiving the connection command, the Connec-tion Circuitry will activate the Upstream-Downstream Buffers under two conditions: first, the master must be commanding connection to one or more downstream channels, and second, there must be no stuck low condition (see Stuck Low Timeout Fault discussion). If the connection command is successful, the Upstream-Downstream Buffers pass signals between the upstream bus and the connected downstream buses. The LTC4306 also turns off its N-channel MOSFET open-drain pull-down on the READY pin, so that READY can be pulled high by its external pull-up resistor.Upstream-Downstream BuffersOnce the Upstream-Downstream Buffers are activated, the functionality of the SDAIN and any connected down-stream SDA pins is identical. A low forced on any con-nected SDA pin at any time results in all pins being low. External devices must pull the pin voltages below 0.4V worst-case with respect to the LTC4306’s ground pin to ensure proper operation. The SDA pins enter a logic high state only when all devices on all connected SDA pins force a high. The same is true for SCLIN and the connected downstream SCL pins. This important feature ensures that clock stretching, clock arbitration and the acknowl-edge protocol always work, regardless of how the devices in the system are connected to the LTC4306.The Upstream-Downstream Buffers provide capacitive isolation between SDAIN/SCLIN and the downstream con-nected buses. Note that there is no capacitive isolation between connected downstream buses; they are only separated by the series combination of their switches’ on resistances.While any combination of downstream buses may be connected at the same time, logic high levels are corrupted if multiple downstream buses are active and both the V CC voltage and one or more downstream bus pull-up voltages are larger than the pull-up supply voltage for another downsteam bus. An example of this issue is shown in Figure 1. During logic highs, DC current flows from V BUS1 through the series combination of R1, N1, N2 and R2 and into V BUS2, causing the SDA1 voltage to drop and current to be sourced into V BUS2. To avoid this problem, do not activate bus 1 or any other downstream bus whose pull-up voltage is above 2.5V when bus 2 is active.OPERATIO114306f12In all other cases, the LTC4306 communicates with the master to resolve the fault. After the master broadcasts theconnect to bus 2, so that it can communicate with the source of the fault. At this point, the master writes to OPERATIOOPERATIOTable 1. LTC4306 I2C Device AddressingHEX DEVICE LTC4306 DESCRIPTION ADDRESS BINARY DEVICE ADDRESS ADDRESS PINSh a6a5a4a3a2a1a0R/W ADR2ADR1ADR0Mass Write BA10111010X X X Alert Response1900011001X X X 0801000000X L NC L 1821000001X L H NC 2841000010X L NC NC 3861000011X L NC H 4881000100X L L L 58A1000101X L H H 68C1000110X L L NC 78E1000111X L L H 8901001000X NC NC L 9921001001X NC H NC 10941001010X NC NC NC 11961001011X NC NC H 12981001100X NC L L 139A1001101X NC H H 149C1001110X NC L NC 159E1001111X NC L H 16A01010000X H NC L 17A21010001X H H NC 18A41010010X H NC NC 19A61010011X H NC H 20A81010100X H L L 21AA1010101X H H H 22AC1010110X H L NC 23AE1010111X H L H 24B01011000X H H L 25B21011001X L H L 26B41011010X NC H Lusers follow the Write Byte protocol exactly, the new data contained in the Data Byte is written into the register selected by bits r1 and r0 on the Stop Bit.General Purpose Input/Outputs (GPIOs)The LTC4306 provides two general purpose input/output pins (GPIOs) that can be configured as logic inputs, open-drain outputs or push-pull outputs. The GPIO1 and GPIO2Mode Configure bits in register 2 determine whether the GPIOs are used as inputs or outputs. When the GPIOs are used as outputs, the GPIO1 and GPIO2 Output Mode Configure bits of register 2 configure the GPIO outputs either as open-drain N-channel MOSFET pull-downs or push-pull stages.In push-pull mode, at V CC = 3.3V, the typical pull-up impedance is 670Ω and the typical pull-down impedance134306f4306f14OPERATIOis 35Ω, making the GPIO pull-downs capable of driving LEDs. At V CC = 5V, the typical pull-up impedance is 320Ωand the typical pull-down impedance is 20Ω. In open-drain output mode, the user provides the logic high by connecting a pull-up resistor between the GPIO pin and an external supply voltage. The external supply voltage can range from 1.5V to 5.5V independent of the V CC voltage.In input mode, the GPIO input threshold voltage is 1V.The GPIO1 and GPIO2 Logic State bits in register 1indicate the logic state of the two GPIO pins. The logic-level threshold voltage for each pin is 1V. The GPIO1 and GPIO2 Output Driver State bits in register 1 indicate the logic state that the LTC4306 is attempting to write to the GPIO pins. This is useful when the GPIOs are being usedFigure 4. Protocols Accepted by LTC4306Figure 3. Data Transfer Over I 2C or SMBusSCLSDASTART CONDITIONSTOP CONDITIONADDRESS ACK DATA ACK DATA ACK1-7894306 F03a6-a0d7-d0d7-d01-7891-789PS4306 F04S 0M 1ALERT RESPONSE ADDRESS PROTOCOL1in open-drain output mode and one or more external devices are connected to the GPIOs. If the LTC4306 is trying to write a high to a GPIO pin, but the pin’s actual logic state is low, then the LTC4306 knows that the low is being forced by an external device.Glitch FiltersThe LTC4306 provides glitch filters on the SDAIN and SCLIN pins as required by the I 2C Fast Mode (400kHz)Specification. The filters prevent signals of up to 50ns (minimum) time duration and rail-to-rail voltage magnitude from passing into the two-wire bus digital interface circuitry.154306f16Assume in Figure 5 that the total parasitic bus capacitance on SDA1 due to trace and device capacitance is 100pF. To ensure that the boost currents are active during rising edges, the pull-up resistor must be strong enough to cause the SDA1 pin voltage to rise at a rate of 0.8V/µs as the pin voltage is rising above 0.8V. The equation is:R k V V ns V PULL UP MAX BUSMIN −Ω[]=⎡⎣⎢,(–.)•081250⎤⎦⎥⎧⎨⎩⎫⎬⎭[]C pF BUS (1)where V BUSMIN is the minimum operating pull-up supply voltage, and C BUS is the bus parasitic capacitance. In our example, V BUS1 = V CC = 3.3V, and assuming ±10% supply tolerance, V BUS1MIN = 2.97V. With C BUS = 100pF,R PULL-UP,MAX = 27.1k. Therefore, we must choose a pull-up resistor smaller (i.e., stronger pull-up) than 27.1k, so a 10k resistor works fine.ALERT, READY and GPIO Component Selection The pull-up resistors on the ALERT and READY pins must provide a maximum pull-up current of 3mA, so that the LTC4306 is capable of holding the pin at logic low voltages below 0.4V. When choosing LE Ds to be driven by the LTC4306’s GPIO pins, make sure that the required LED sinking current is less than 5mA, and add a current-limiting resistor in series with the LED.Level Shifting ConsiderationsIn the design example of Figure 5, the LTC4306 V CC voltage is less than or equal to both of the downstream bus pull-up voltages, so buses 1 and 4 can be active at the same time. Likewise, the rise time accelerators can be turned on for the downstream buses, but must never be activated on SCLIN and SDAIN, because doing so would result in significant current flow from V CC to V BACK during rising edges.Other Application CircuitsFigure 6 illustrates how the LTC4306 can be used to expand the number of devices in a system by using nested addressing. Each I/O card contains a temperature sensorhaving device address 1001 000. If the four I/O cards were plugged directly into the backplane, the four sensors would require four unique addresses. However, if masters use the LTC4306 in multiplexer mode, where only one downstream channel is connected at a time, then each I/O card can have a device with address 1001 000 and no problems will occur.Figures 7 and 8 show two different methods for hot-swapping I/O cards onto a live two-wire bus using the LTC4306. The circuitry of Figure 7 consists of an LTC4306residing on the edge of an I/O card having four separate downstream buses. Connect a 200k resistor to ground from the E NABLE pin and make the E NABLE pin the shortest pin on the connector, so that the ENABLE pin remains at a constant logic low while all other pins are connecting. This ensures that the LTC4306 remains in its default high impedance state and ignores connection transients on its SDAIN and SCLIN pins until they have established solid contact with the backplane 2-wire bus. In addition, make sure that the ALE RT connector pin is shorter than the V CC pin, so that V CC establishes solid contact with the I/O card pull-up supply pin and powers the pull-up resistors on ALERT1–ALERT4 before ALERT makes contact.Figure 8 illustrates an alternate SDA and SCL hot-swap-ping technique, where the LTC4306 is located on the backplane and an I/O card plugs into downstream channel 4. Before plugging and unplugging the I/O card, make sure that channel 4’s downstream switch is open, so that it does not disturb any 2-wire transaction that may be occurring at the moment of connection/disconnection. Note that pull-up resistor, R17, on ALERT4 should be located on the backplane and not the I/O card to ensure proper operation of the LTC4306 when the I/O card is not present. The pull-up resistors on SCL4 and SDA4, R15 and R16 respec-tively, may be located on the I/O card, provided that downstream bus 4 is never activated when the I/O card is not present. Otherwise, locate R15 and R16 on the backplane.APPLICATIO S I FOR ATIOW UUU174306f18Figure 7. Hot-Swapping ApplicationAPPLICATIO S I FOR ATIOW UUUBACKPLANE CONNECTOR CARD CONNECTORV CARD_SCL1CARD_SDA1CARD_ALERT1CARD_SCL2CARD_SDA2CARD_ALERT2CARD_SCL3CARD_SDA3CARD_ALERT3CARD_SCL4CARD_SDA4CARD_ALERT4ADDRESS = 1010 000Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.194306f20Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2005LT/LWI/TP 0805 500 • PRINTED IN USAAPPLICATIO S I FOR ATIOW UUU RELATED PARTSPART NUMBER DESCRIPTIONCOMMENTSLTC1380/LTC1393Single-Ended 8-Channel/Diffierential 4-Channel Analog Low R ON : 35Ω Single-Ended/70Ω Differential, Expandable to Mux with SMBus Interface32 Single or 16 Differential ChannelsLTC1427-50Micropower, 10-Bit Current Output DAC with SMBus Precision 50µA ±2.5% Tolerance Over Temperature, 4 Selectable InterfaceSMBus Addresses, DAC Powers Up at Zero or MidscaleLTC1694/LTC1694-1SMBus AcceleratorImproved SMBus/I 2C Rise Time, Ensures Data Integrity with Multiple SMBus/I 2C DevicesLT ®1786F SMBus Controlled CCFL Switching Regulator 1.25A, 200kHz, Floating or Grounded Lamp Configurations LTC1695SMBus/I 2C Fan Speed Controller in ThinSOT TM 0.75Ω PMOS 180mA Regulator, 6-Bit DACLTC1840Dual I 2C Fan Speed Controller Two 100µA 8-Bit DACs, Two Tach Inputs, Four GPIO LTC4300A-1/LTC4300A-2Hot Swappable 2-Wire Bus Buffer Isolates Backplane and Card Capacitances LTC4300A-3Hot Swappable 2-Wire Bus BufferProvides Level Shifting and Enable Functions LTC4301Supply Independent Hot Swappable 2-Wire Bus Buffer Supply IndependentLTC4301LHot Swappable 2-Wire Bus Buffer with Low Voltage Allows Bus Pull-Up Voltages as Low as 1V on SDAIN and SCLIN Level TranslationLTC4303/LTC4304How Swappable Bus Buffers with Stuck Bus Recovery Recover Stuck Buses with Automatic ClockingLTC43052-Channel 2-Wire Multiplexer with Capacitance2 Selectable Downstream Buses, Stuck Bus Disconnect, Rise Time BufferingAccelerators, Fault Reporting, ±10kV HBM ESD ToleranceThinSOT is a trademark of Linear Technology Corporation.Figure 8. Downstream Side Hot-Swapping Application。

LTC4306IUFD-DC906A-用户手册说明书

QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 906A4-CHANNEL, 2-WIRE BUS MULTIPLEXER WITH CAPACITANCE BUFFERINGLTC4306IUFDDESCRIPTIONDemonstration circuit 906A features the LTC ®4306IUFD, a 4-channel, 2-wire I2C bus and SMBus compatible multiplexer having bus buffers that provide capacitive isolation between the up-stream bus and downstream buses. Through soft-ware control, the LTC4306IUFD connects the up-stream 2-wire bus to any desired combination of downstream buses. Each bus can be pulled up to a supply voltage ranging from 2.2V to 5.5V, independ-ent of the LTC4306IUFD supply voltage. The down-stream buses are also provided with ALERT1B – ALERT4B inputs for fault reporting.Programmable timeout circuitry disconnects the downstream buses if the bus is stuck low. When acti-vated, rise time accelerators source currents into the 2-wire bus pins during rising edges to reduce rise time. Two general purpose input/output (GPIO) pins can be configured as inputs, open-drain outputs or push-pull outputs. Green LED’s D3 and D2 light up when GPIO1 and GPIO2, respectively, are low. Driv-ing the ENABLE pin low restores all device features totheir default states. Three address pins provide 27 distinct addresses.Design files for this circuit board are available. Call the LTC factory.LTC is a registered trademark of Linear Technology CorporationTable 1. Performance Summary (T A = 25°C)PARAMETERCONDITION VALUE V CC Voltage Operating Range2.7V – 5.5V Bus Pull-up Supply Voltage Range (V BUS1-V BUS4) 2.2V – 5.5V 2-Wire Bus Frequency Range0 - 400kHzBus Stuck Low Disconnect TimesV CC = 2.7V - 5.5V7.5ms, 15ms, 30ms optionsall times +/-16.7% feature can also be disabledBus Buffer V OL Offset Voltage R BUS = 10K 100mV (maximum) V CC = 3.3V 5.5mA (typical) Rise Time Accelerator Pull-up Current V CC = 5V9mA (typical) ALERTB and READY Output V OL VoltagesV CC = 2.7V - 5.5V; I ALERTB = I READY = 3mA0.4V (maximum)OPERATING PRINCIPLESFor operation with the DC906A, connect the host con-troller’s SDA and SCL pins to the LTC4306IUFD’s SDAIN and SCLIN pins (hereafter referred to as the upstream bus), and connect the upstream bus supply of 2.7V to 5.5V to Vcc (as shown in Figure 1). The host controller on the upstream side first addresses and configures the LTC4306IUFD to connect the up-stream bus to one or more of the four downstreambuses. Communications between the upstream and downstream components are then established and a host controller on any bus can then control the LTC4306IUFD.Use turrets VBUS1-VBUS4 and jumpers JP1-JP4 to pull up the downstream buses to supply voltages dif-ferent than VCC (i.e., to provide level-shifting). Forexample, in Figure1, JP1 is set to the right position and a supply voltage is connected between VBUS1 and ground. Voltages on VBUS1-VBUS4 must range between 2.2V and 5.5V. To connect a downstream bus’s pull-up supply to VCC, set its jumper to the left position.Additional configurations include enabling and dis-abling the rise time accelerators on the backplane side and/or the card side, setting the GPIO’s to open-drain output, push-pull output, or input mode, setting or resetting the GPIO’s outputs, disabling the Bus Stuck Low disconnect feature or setting the discon-nect time to 7.5ms, 15ms, 30ms. A host controller can also read the internal registers of the LTC4306IUFD to determine the settings of these fea-tures as well as fault statuses. All of these features are accessed by sending commands on the 2-wire bus.The ENABLE pin, when pulled low, resets the LTC4306IUFD to its registers default state and dis-ables communication to it. Communication can be reestablished when ENABLE is released high. There-fore, set jumper JP5 to the left position for normal operation, and set it to the right position to disable the LTC4306IUFD.Slave devices that are capable of fault reporting and that are located on downstream buses 1-4 should connect their fault pins to ALERT1B-ALERT4B, re-spectively. The LTC4306IUFD passes downstream faults to the upstream host by pulling down on the ALERTB pin, so this host’s fault input should be con-nected to the LTC4306IUFD ALERTB pin.When the upstream bus is connected to one or more downstream buses, the READY pin voltage is pulled up to VCC. When the upstream bus is disconnected from all downstream buses, the READY voltage is low (~0.2V).On the DC906A, the board’s default setting for jump-ers JP6, JP7 and JP8 is the center position, which sets the address of the LTC4306IUFD to (1001 010)2. To set a different address, configure the jumpers ac-cording to Table 1 of the data sheet (note: left posi-tion = H, middle position = NC, right position = L; de-fault = NC for all three jumpers).QUICK START PROCEDUREDemonstration circuit 906A is easy to set up to evalu-ate the performance of the LTC4306IUFD. Refer toFigure 1 for proper measurement equipment setup and follow the procedure below:KEY NOTES: a. Do not activate rise time acceleratorson buses whose pull-up supply voltages are lower than VCC. b. Make sure logic low voltages forced onall clock and data pins are < 0.4V. c. When activatingmultiple downstream buses that are powered from separate supply voltages, make sure that theLTC4306IUFD’s VCC voltage is less than or equal tothe lowest downstream bus pull-up supply voltage. 1.Jumpers JP1-JP4 choose the pull-up supply volt-ages VBUS1 – VBUS4 for downstream buses 1-4.For unused buses and buses pulled up to VCC, set the jumpers in the left position. To pull up a down-stream bus to a different voltage than VCC, set itsjumper to the right position, and connect the sup-ply voltage to the appropriate turret on the left side of the board.2.Set jumper J5 in the left position to enable communication to the LTC4306IUFD.3.Configure jumpers JP6 – JP8 to set the desired 2-wire bus address for the LTC4306IUFD according to Table 1 on page 13 of the datasheet (note: left position = H, middle position = NC, right position = L; default = NC for all three jumpers).4.Connect a cable from 6-pin header J2 to a board containing the master device(s).5.Connect a 20-pin ribbon cable from J1 to a board that contains downstream slave devices. Note: the downstream buses can contain masters, but the original command to connect must come from amaster connected to the upstream SDAIN/SCLIN bus.6. Connect power supplies to VCC and, if required,one or more of VBUS1 – VBUS4.7. Turn on the power supplies.NOTE: Make sure that the power supply voltages donot exceed 5.5V.8. Use the SMBus Read Byte and Write Byte proto-cols in conjunction with the register definitions on pages 8 and 9 of the datasheet to experiment with the LTC4306IUFD’s features and to establish up-stream-downstream communications between the master and slave devices.Figure 1.Proper Measurement Equipment Setup。

DSEI60-06A;中文规格书,Datasheet资料

166 W

0.8...1.2 Nm

6

g

Symbol

IR

VF

VT0 rT RthJC RthCH trr IRM

Conditions

Characteristic Values typ. max.

VR = VRRM VR = 0.8·VRRM VR = 0.8·VRRM

TVJ = 25°C TVJ = 25°C TVJ = 125°C

IXYS reserves the right to change limits, test conditions and dimensions

© 2007 IXYS All rights reserved

/

0549

2-2

Dimensions TO-247 AD

C

D

t = 8.3 ms (60 Hz), sine

TC = 25°C mounting torque typical

Maximum Ratings

100 A 60 A

550 A 600

480 A 520Biblioteka 1510 A2s 1490

1150 A2s 1120

-55...+150 °C 150 °C

-55...+150 °C

Fast Recovery Epitaxial Diode (FRED)

DSEI60-06A DSEI60-06AT

IFAV = 60 A VRRM = 600 V trr = 35 ms

VRSM V

600 600

VRRM V

600 600

Type

DSEI 60-06A DSEI 60-06AT

A

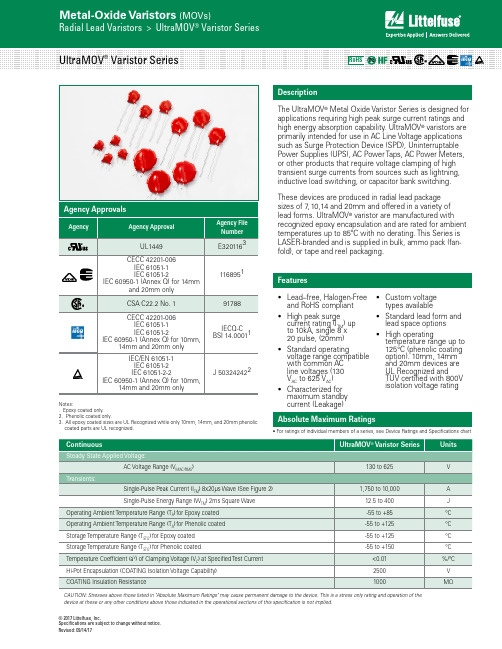

Littelfuse ULTRAMOV Datasheet力特压敏电阻规格书

Features

• Lead–free, Halogen-Free • Custom voltage

and RoHS compliant

types available

• High peak surge

• Standard lead form and

ctour1r0eknAt ,rastiinnggle(IT8M)xup 20 pulse, (20mm)

91788 BSIIE1C4Q.0-0C011

J 503242422

Notes: . Epoxy coated only. 2. Phenolic coated only. 3. All epoxy coated sizes are UL Recognized while only 10mm, 14mm, and 20mm phenolic

UltraMOV® Series Ratings & Specifications

Epoxy Coated Models

Phenolic Coated Models

Part Number

Branding

Part Number

Branding

V07E130P P7V130 V07P130P P7P130 V10E130P P10V130 V10P130P P10P130 V14E130P P14V130 V14P130P P14P130 V20E130P P20V130 V20P130P P20P130 V07E140P P7V140 V07P140P P7P140 V10E140P P10V140 V10P140P P10P140 V14E140P P14V140 V14P140P P14P140 V20E140P P20V140 V20P140P P20P140 V07E150P P7V150 V07P150P P7P150 V10E150P P10V150 V10P150P P10P150 V14E150P P14V150 V14P150P P14P150 V20E150P P20V150 V20P150P P20P150 V07E175P P7V175 V07P175P P7P175 V10E175P P10V175 V10P175P P10P175 V14E175P P14V175 V14P175P P14P175 V20E175P P20V175 V20P175P P20P175 V07E230P P7V230 V07P230P P7P230 V10E230P P10V230 V10P230P P10P230 V14E230P P14V230 V14P230P P14P230 V20E230P P20V230 V20P230P P20P230 V07E250P P7V250 V07P250P P7P250 V10E250P P10V250 V10P250P P10P250 V14E250P P14V250 V14P250P P14P250 V20E250P P20V250 V20P250P P20P250 V07E275P P7V275 V07P275P P7P275 V10E275P P10V275 V10P275P P10P275 V14E275P P14V275 V14P275P P14P275 V20E275P P20V275 V20P275P P20P275 V07E300P P7V300 V07P300P P7P300 V10E300P P10V300 V10P300P P10P300 V14E300P P14V300 V14P300P P14P300 V20E300P P20V300 V20P300P P20P300 V07E320P P7V320 V07P320P P7P320 V10E320P P10V320 V10P320P P10P320 V14E320P P14V320 V14P320P P14P320 V20E320P P20V320 V20P320P P20P320 V07E385P P7V385 V07P385P P7P385 V10E385P P10V385 V10P385P P10P385 V14E385P P14V385 V14P385P P14P385 V20E385P P20V385 V20P385P P20P385 V07E420P P7V420 V07P420P P7P420 V10E420P P10V420 V10P420P P10P420 V14E420P P14V420 V14P420P P14P420 V20E420P P20V420 V20P420P P20P420 V07E440P P7V440 V07P440P P7P440 V10E440P P10V440 V10P440P P10P440 V14E440P P14V440 V14P440P P14P440 V20E440P P20V440 V20P440P P20P440 V07E460P P7V460 V07P460P P7P460 V10E460P P10V460 V10P460P P10P460

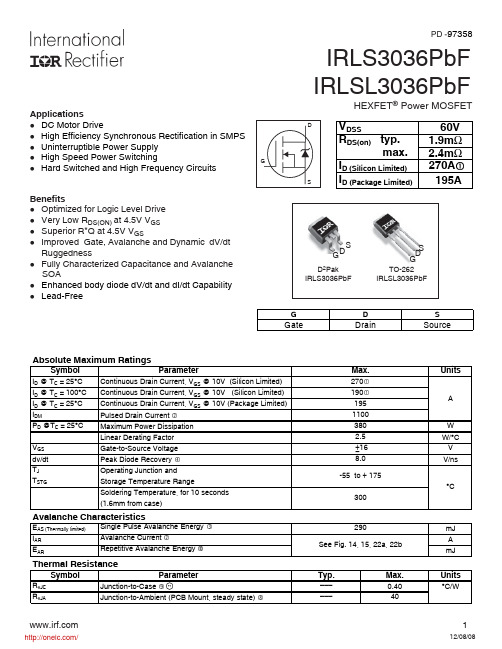

IRLS3036TRLPBF;IRLSL3036PBF;IRLS3036TRRPBF;IRLS3036PBF;中文规格书,Datasheet资料

HEXFET ®Power MOSFETPD -97358IRLS3036PbF IRLSL3036PbFApplicationsl DC Motor Drivel High Efficiency Synchronous Rectification in SMPS l Uninterruptible Power Supply l High Speed Power Switchingl Hard Switched and High Frequency Circuits Benefitsl Optimized for Logic Level Drive l Very Low R DS(ON) at 4.5V V GS l Superior R*Q at 4.5V V GSl Improved Gate, Avalanche and Dynamic dV/dt Ruggednessl Fully Characterized Capacitance and Avalanche SOAl Enhanced body diode dV/dt and dI/dt Capability l Lead-FreeD 2Pak IRLS3036PbFTO-262IRLSL3036PbFGD S GDSIRLS/SL3036PbFC oss eff. (TR) is a fixed capacitance that gives the same charging time as C oss while V DS is rising from 0 to 80% V DSS .C oss eff. (ER) is a fixed capacitance that gives the same energy as C oss while V DS is rising from 0 to 80% V DSS .When mounted on 1" square PCB (FR-4 or G-10 Material). Forrecommended footprint and soldering techniquea refer to applocation note # AN- 994 echniques refer to application note #AN-994. R θ is measured at T J approximately 90°C.Limited by TJmax, see Fig. 14, 15, 22a, 22b for typical repetitive avalanche performance.R θJC value shown is at time zero.Notes:Calcuted continuous current based on maximum allowable junctiontemperature Bond wire current limit is 195A. Note that current limitation arising from heating of the device leds may occur with some lead mounting arrangements.Repetitive rating; pulse width limited by max. junctiontemperature.Limited by T Jmax , starting T J = 25°C, L = 0.021mHR G = 25Ω, I AS = 165A, V GS =10V. Part not recommended for use above this value .I SD ≤ 165A, di/dt ≤ 430A/µs, V DD ≤ V (BR)DSS , T J ≤ 175°C. Pulse width ≤ 400µs; duty cycle ≤ 2%.Static @ T = 25°C (unless otherwise specified)Dynamic @ T = 25°C (unless otherwise specified)IRLS/SL3036PbFFig 1. Typical Output CharacteristicsFig 3. Typical Transfer CharacteristicsFig 4. Normalized On-Resistance vs. TemperatureFig 6. Typical Gate Charge vs. Gate-to-Source VoltageFig 5. Typical Capacitance vs. Drain-to-Source Voltage V GS , Gate-to-Source Voltage (V)0.11101001000I D , D r a i n -t o -S o u r c e C u r r e n t (A )T J , Junction Temperature (°C)110100V DS , Drain-to-Source Voltage (V)100100010000100000C , C a p a c i t a n c e (p F )0.11101001000V DS , Drain-to-Source Voltage (V)20406080100120Q G , Total Gate Charge (nC)0.01.02.03.04.05.0V G S , G a t e -t o -S o u r c e V o l t a g e (V )IRLS/SL3036PbFFig 10. Drain-to-Source Breakdown VoltageFig 11. Typical C OSS Stored EnergyFig 9. Maximum Drain Current vs.Case TemperatureFig 12. Maximum Avalanche Energy vs. DrainCurrent0.11101001000I S D , R e v e r s e D r a i n C u r r e n t (A )T J , Temperature ( °C )-1010203040506070V DS, Drain-to-Source Voltage (V)0.00.51.01.52.02.53.0E n e r g y (µJ )255075100125150175Starting T J , Junction Temperature (°C)20040060080010001200E A S , S i n g l e P u l s e A v a l a n c h e E n e r g y (m J )255075100125150175T C , Case Temperature (°C)050100150200250300I D , D r a i n C u r r e n t (A )IRLS/SL3036PbFFig 13. Maximum Effective Transient Thermal Impedance, Junction-to-CaseFig 14. Typical Avalanche Current vs.PulsewidthFig 15. Maximum Avalanche Energy vs. TemperatureNotes on Repetitive Avalanche Curves , Figures 14, 15:(For further info, see AN-1005 at )1.Avalanche failures assumption:Purely a thermal phenomenon and failure occurs at a temperature far in excess of T jmax . This is validated for every part type.2. Safe operation in Avalanche is allowed as long asT jmax is not exceeded.3. Equation below based on circuit and waveforms shown in Figures 16a, 16b.4. P D (ave) = Average power dissipation per single avalanche pulse.5. BV = Rated breakdown voltage (1.3 factor accounts for voltage increase during avalanche).6. I av = Allowable avalanche current.7. ∆T = Allowable rise in junction temperature, not to exceed T jmax (assumed as 25°C in Figure 14, 15).t av = Average time in avalanche.D = Duty cycle in avalanche = t av ·fZ thJC (D, t av ) = Transient thermal resistance, see Figures 13)P D (ave) = 1/2 ( 1.3·BV·I av ) = D T/ Z thJCI av = 2D T/ [1.3·BV·Z th ]E AS (AR) = P D (ave)·t avt 1 , Rectangular Pulse Duration (sec)255075100125150175Starting T J , Junction Temperature (°C)050100150200250300E A R , A v a l a n c h e E n e r g y (m J )tav (sec)IRLS/SL3036PbFFig. 17 - Typical Recovery Current vs. di f /dtFig 16. Threshold Voltage vs. TemperatureFig. 19 - Typical Stored Charge vs. di f /dtFig. 18 - Typical Recovery Current vs. di f /dtT J , Temperature ( °C )V G S (t h ), G a t e t h r e s h o l d V o l t a g e (V )100200300400500di F/dt (A/µs)100200300400500600700800900Q R R (A )100200300400500di F /dt (A/µs)200300400500600Q R R (A )0100200300400500di F /dt (A/µs)2468101214I R R M (A )100200300400500di F /dt (A/µs)24681012I R R M (A )IRLS/SL3036PbFFig 23a. Switching Time Test CircuitFig 23b. Switching Time WaveformsFig 22b. Unclamped Inductive WaveformsFig 22a. Unclamped Inductive Test CircuitI ASV DDIdQgs1Qgs2Qgd QgodrFig 21. Peak Diode Recovery dv/dt Test Circuit for N-Channel® Power MOSFETs* V GS = 5V for Logic Level DevicesDSCurrent Sampling ResistorsV DS 90%10%V GSd(on)rd(off)fV DDTO-262 Package Outline Dimensions are shown in millimeters (inches)IRLS/SL3036PbFNote: For the most current drawing please refer to IR website at /package/Data and specifications subject to change without notice.This product has been designed and qualified for the Industrial market.Qualification Standards can be found on IR’s Web site.IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903Visit us at for sales contact information . 12/2008D 2Pak (TO-263AB) Tape & Reel InformationDimensions are shown in millimeters (inches)344TRRFEED DIRECTION1.85 (.073)1.65 (.065)1.60 (.063)1.50 (.059)4.10 (.161)3.90 (.153)TRLFEED DIRECTION 10.90 (.429)10.70 (.421)16.10 (.634)15.90 (.626)1.75 (.069)1.25 (.049)11.60 (.457)11.40 (.449)15.42 (.609)15.22 (.601)4.72 (.136)4.52 (.178)24.30 (.957)23.90 (.941)0.368 (.0145)0.342 (.0135)1.60 (.063)1.50 (.059)13.50 (.532)12.80 (.504)330.00(14.173) MAX.27.40 (1.079)23.90 (.941)60.00 (2.362) MIN.30.40 (1.197) MAX.26.40 (1.039)24.40 (.961)NOTES :1. COMFORMS TO EIA-418.2. CONTROLLING DIMENSION: MILLIMETER.3. DIMENSION MEASURED @ HUB.4. INCLUDES FLANGE DISTORTION @ OUTER EDGE.分销商库存信息:IRIRLS3036TRLPBF IRLSL3036PBF IRLS3036TRRPBF IRLS3036PBF。

iw3616、3617、3630datasheet中文翻译(绝对真实)

产品特色大幅简化离线式LED驱动器设计●单级功率因数校正(PFC)与精确恒流(CC)输出相结合●输入/输出电容和变压器体积小●一次侧反馈控制,无需光耦电路,简化了电路设计●简化初级侧PWM调光接口●符合IEC61000-3-2标准高效节能和高兼容性●大幅提升效率,可达到85%以上●减少元件数量●总谐波失真<15%且PF>0.95●前沿、后沿和数字调光器●传感器和定时器精确稳定的性能●LED负载恒流精度不低于±5%●支持LED负载热插拔●1%-100%宽范围调光,调光无闪烁先进的保护及安全特性●通过自动重启动提供短路保护●开路故障检测模式●自动热关断重启动无论在PCB板上还是在封装上,都保证高压漏极引脚与其他所有信号引脚之间满足高压爬电要求应用●LED离线固态照明说明G7617 是一款的适用于LED调光控制的离线式两级交流/直流电源控制器,是适用于25W 输出功率的可调光LED 灯具的最优之选。

G7617符合电磁兼容性(EMC) IEC61000-3-2 标准,在120V AC或230V AC输入电压下其功率因数(PF) 可达到0.95 以上。

采用先进的数控技术来检测调光器的类型和相位,为调光器提供动态阻抗的同时可调节LED发光亮度,自动检测调光器类型和相位,从而实现了业内与模拟及数字调光器最广泛的兼容性。

G7617工作于准谐振工作模式,工作效率高,可工作于前沿后沿调光模式,也可工作于R 型、R-C型或R-L型调光控制模式。

G7617 符合热插拔LED 模块的固态照明行业标准Zhaga,同时还集成了调光功能的映射选项(位于白炽灯替代灯的NEMA SSL6 调光曲线内)。

G7617 系列有两个版本:针对120V AC输入应用进行优化的G7617-00 和针对230V AC 应用进行优化的G7617-01。

订购信息应用框图图1典型应用内部框图Vcc VinVcbVT CFGASU BisenseBdrvFdrvFisensePGNDAGND C O R E图2 内部框图引脚功能描述BV SENSE V IN BI SENSE B DRV CFG ASU V CCV CBV TFV SENSEFI SENSEF DRVAGNDPGND 图3. 引脚布局BV SENSE引脚:PFC电感电压反馈点,用于感知Boost电感的磁通状态。

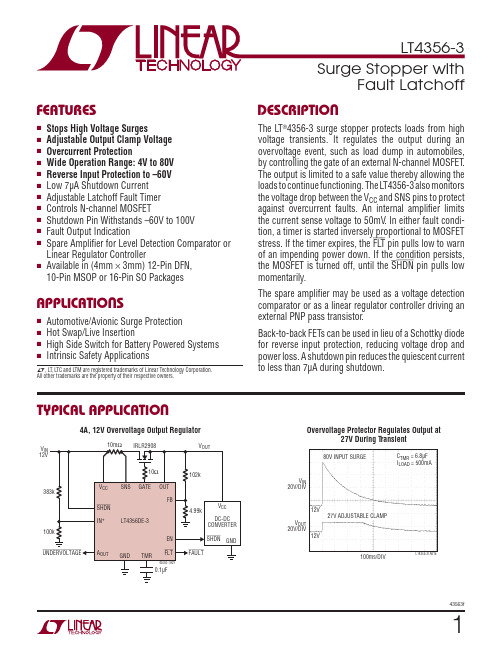

LT4356-3中文资料

LT4356IS-3#TRPBF

LT4356S-3

16-Lead Plastic SO

–40°C to 85°C

LEAD BASED FINISH

TAPE AND REEL

PART MARKING*

PACKAGE DESCRIPTION

TEMPERATURE RANGE

LT4356CDE-3

LT4356CDE-3#TR

FLT

43563 TA01

0.1μF

102k

4.99k

VCC

DC-DC CONVERTER

SHDN GND FAULT

Overvoltage Protector Regulates Output at 27V During Transient

80V INPUT SURGE

CTMR = 6.8μF ILOAD = 500mA

元器件交易网

FEATURES

n Stops High Voltage Surges n Adjustable Output Clamp Voltage n Overcurrent Protection n Wide Operation Range: 4V to 80V n Reverse Input Protection to –60V n Low 7μA Shutdown Current n Adjustable Latchoff Fault Timer n Controls N-channel MOSFET n Shutdown Pin Withstands –60V to 100V n Fault Output Indication n Spare Amplifier for Level Detection Comparator or

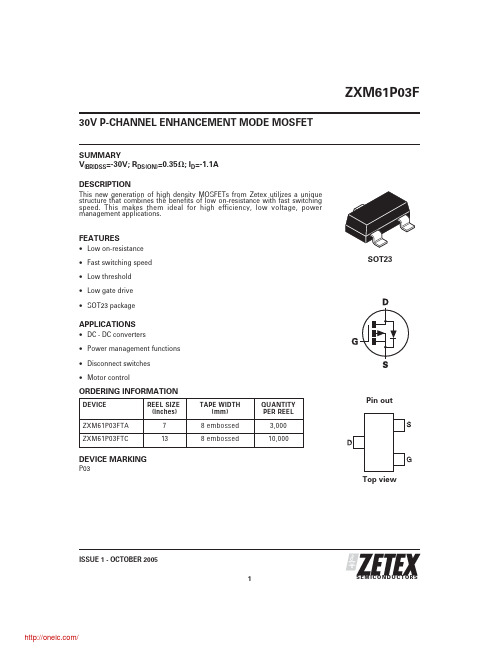

ZXM61P03FTA;ZXM61P03FTC;中文规格书,Datasheet资料

1S E M I C O N D U C T O R SZXM61P03FISSUE 1 - OCTOBER 200530V P-CHANNEL ENHANCEMENT MODE MOSFETSUMMARYV (BR)DSS =-30V; R DS(ON)=0.35⍀; I D =-1.1A DESCRIPTIONThis new generation of high density MOSFETs from Zetex utilizes a unique structure that combines the benefits of low on-resistance with fast switching speed.This makes them ideal for high efficiency,low voltage,power management applications.FEATURES•Low on-resistance •Fast switching speed •Low threshold •Low gate drive •SOT23 packageAPPLICATIONS•DC - DC converters•Power management functions •Disconnect switches •Motor controlORDERING INFORMATIONDEVICE REEL SIZE (inches)TAPE WIDTH(mm)QUANTITY PER REEL ZXM61P03FTA 78embossed 3,000ZXM61P03FTC138embossed10,000DEVICE MARKINGP03SOT23Pin outTop viewZXM61P03FS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20052THERMAL RESISTANCEPARAMETERSYMBOL VALUE UNIT Junction to Ambient (a)R θJA 200°C/W Junction to Ambient (b)R θJA155°C/WNOTES:(a) For a device surface mounted on 25mm x 25mm FR4 PCB with high coverage of single sided 1oz copper, in still air conditions (b) For a device surface mounted on FR4 PCB measured at t р5 secs.(c) Repetitive rating - pulse width limited by maximum junction temperature. Refer to Transient Thermal Impedance graph.ABSOLUTE MAXIMUM RATINGSPARAMETERSYMBOL LIMIT UNIT Drain-Source Voltage V DSS -30V Gate-Source Voltage V GSϮ20VContinuous Drain Current(V GS =-10V;T A =25°C)(b)(V GS =-10V;T A =70°C)(b)I D -1.1-0.9A Pulsed Drain Current (c)I DM -4.3A Continuous Source Current (Body Diode)(b)I S -0.88A Pulsed Source Current (Body Diode)(c)I SM -4.3A Power Dissipation at T A =25°C (a)Linear Derating FactorP D 6255mW mW/°C Power Dissipation at T A =25°C (b)Linear Derating FactorP D 8066.4mW mW/°C Operating and Storage Temperature RangeT j :T stg-55 to +150°CZXM61P03FS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20053CHARACTERISTICSZXM61P03FS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20054ELECTRICAL CHARACTERISTICS (at T amb =25°C unless otherwise stated).PARAMETER SYMBOLMIN.TYP.MAX.UNIT CONDITIONS.STATICDrain-Source Breakdown Voltage V (BR)DSS -30V I D =-250µA,V GS =0V Zero Gate Voltage Drain Current I DSS -1µA V DS =-30V,V GS =0V Gate-Body LeakageI GSS Ϯ100nA V GS =Ϯ20V,V DS =0V Gate-Source Threshold VoltageV GS(th)-1.0V I D=-250µA,V DS =V GS Static Drain-Source On-State Resistance (1)R DS(on)0.350.55ΩΩV GS =-10V,I D =-0.6A V GS =-4.5V,I D =-0.3A Forward Transconductance (3)g fs0.44SV DS =-10V,I D =-0.3ADYNAMIC (3)Input Capacitance C iss 140pF V DS =-25V,V GS =0V,f=1MHzOutput CapacitanceC oss 45pF Reverse Transfer Capacitance C rss20pFSWITCHING (2)(3)Turn-On Delay Time t d(on) 1.9ns V DD =-15V,I D =-0.6A R G =6.2Ω,R D =25Ω(Refer to test circuit)Rise Timet r 2.9ns Turn-Off Delay Time t d(off)8.9ns Fall Timet f 5.0nsTotal Gate Charge Q g 4.8nC V DS =-24V,V GS =-10V,I D =-0.6A(Refer to test circuit)Gate-Source Charge Q gs 0.62nC Gate Drain Charge Q gd1.3nCSOURCE-DRAIN DIODE Diode Forward Voltage (1)V SD -0.95V T j =25°C,I S =-0.6A,V GS =0VReverse Recovery Time (3)t rr 14.8ns T j =25°C,I F =-0.6A,di/dt=100A/µsReverse Recovery Charge(3)Q rr7.7nCNOTES:(1) Measured under pulsed conditions. Width=300µs. Duty cycle Յ2%.(2) Switching characteristics are independent of operating junction temperature.(3) For design aid only, not subject to production testing.ZXM61P03FS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20055TYPICAL CHARACTERISTICSZXM61P03FS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20056TYPICAL CHARACTERISTICSZXM61P03FS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20057EuropeZetex GmbHStreitfeldstraße 19D-81673 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49europe.sales@AmericasZetex Inc700 Veterans Memorial Hwy Hauppauge, NY 11788USATelephone: (1) 631 360 2222Fax: (1) 631 360 8222usa.sales@Asia PacificZetex (Asia) Ltd3701-04Metroplaza Tower 1Hing Fong Road, Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494asia.sales@Corporate Headquarters Zetex Semiconductors plc Zetex Technology ParkChadderton, Oldham, OL9 9LL United KingdomTelephone (44) 161 622 4444Fax: (44) 161 622 4446hq@These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.For the latest product information,log on to ©ZetexSemiconductors plc 2005PACKAGE DETAILSPAD LAYOUT DETAILSDIM MillimetersInches DIM Millimeters Inches Min Max Min Max Min Max Max Max A 2.67 3.050.1050.120H 0.330.510.0130.020B 1.20 1.400.0470.055K 0.010.100.00040.004C ᎏ 1.10ᎏ0.043L 2.10 2.500.0830.0985D 0.370.530.0150.021M 0.450.640.0180.025F 0.0850.150.00340.0059N 0.95 NOM 0.0375 NOMG1.90 NOM 0.075 NOMᎏᎏᎏPACKAGE DIMENSIONS分销商库存信息:DIODESZXM61P03FTA ZXM61P03FTC。

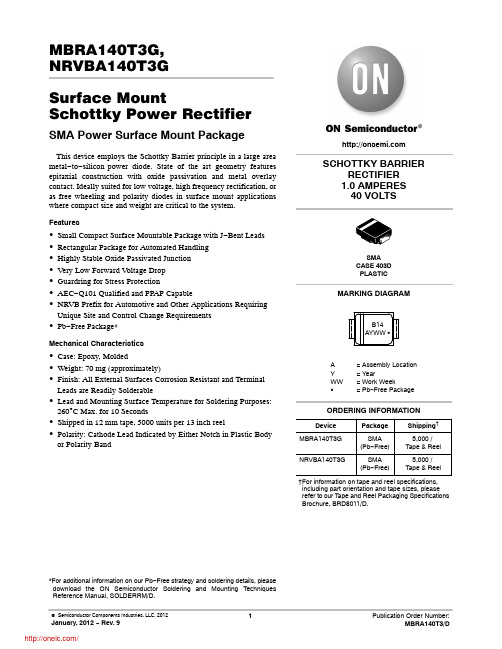

MBRA140T3G;MBRA140T3;中文规格书,Datasheet资料

Figure 5. Current Derating

R (T) , TRANSIENT THERMAL RESISTANCE (NORMALIZED) T, TIME (s) 1.0E+0

Figure 6. Forward Power Dissipation

中文规格书datasheet资料datasheetdatasheet网站l298ndatasheeticdatasheetpl2303datasheetds18b20datasheetdatasheetcomlm324datasheetrt5350datasheet

MBRA140T3G, NRVBA140T3G Surface Mount Schottky Power Rectifier

vF, INSTANTANEOUS FORWARD VOLTAGE (VOLTS)

Figure 1. Typical Forward Voltage

Figure 2. Maximum Forward Voltage

100E-3 I R , REVERSE CURRENT (AMPS)

100E-3 I R , MAXIMUM REVERSE CURRENT (AMPS)

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

10E-3

TJ = 125C TJ = 85C

10E-3 TJ = 85C 1.0E-3 TJ = 25C

SC35VB160-G;中文规格书,Datasheet资料

FIG.2- DERATING CURVE OUTPUT RECTIFIED CURRENT 50 40 30 WITH HEATSINK

20

10

0

50

100

150

CASE TEMPERATURE,°C

FIG.3-TYPICAL FORWARD CHARACTERISTICS 100

10

1.0

0.1 0.01

FIG.1-MAXMUN FORWARD SURGE CURRENT

500

450 400

350

PULSE WIDTH 8.3ms

SINGLE HALF-SINE -WAVE

300

(JEDEC METHOD)

250

200

150

100

50

0

1

10

100

NUMBER OF CYCLES AT 60Hz

AVERAGE FORWARD OUTPUT CURRENT , AMPERES

0.1

0.01 0 20 40 60 80 100 120 140 PERCENT OF RATED PEAK REVERSE VOLTAGE

INSTANTANEOUS FORWARD CURRENT ,(A)

MDS0905016A

/

2

分销商库存信息:

COMCHIP SC35VB160-G

IFSM

I2t Vdis TOR VF

IR RθJC

TJ

Storage Temperature Range

TSTG

NOTES: 1.Thermal Resistance Junction to case.

SC35VB160 1600 1120 35