A Bandwidth-Efficient Architecture for Media Processing

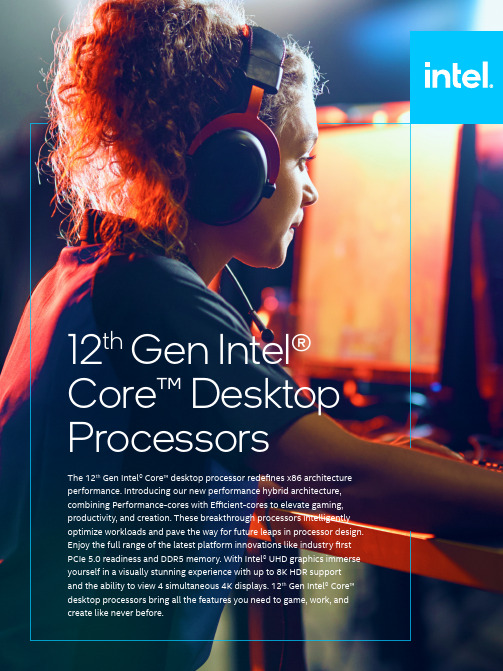

12代英特尔核心桌面处理器产品介绍说明书

The 12th Gen Intel® Core™ desktop processor redefines x86 architecture performance. Introducing our new performance hybrid architecture, combining Performance-cores with Efficient-cores to elevate gaming, productivity, and creation. These breakthrough processors intelligently optimize workloads and pave the way for future leaps in processor design. Enjoy the full range of the latest platform innovations like industry first PCIe 5.0 readiness and DDR5 memory. With Intel® UHD graphics immerse yourself in a visually stunning experience with up to 8K HDR support and the ability to view 4 simultaneous 4K displays. 12th Gen Intel® Core™ desktop processors bring all the features you need to game, work, and create like never before.12thGen Intel® Core™ Desktop ProcessorsWhether you’re delving into the latest gaming titles or focusing on advanced professional applications, 12th Gen Intel® Core™ Desktop processors enable you to immerse without interruptions. Intel® UHD Graphics driven by X e Architecture invite you to take a deep-dive into vivid new experiences with enhanced visual support for up to 8K HDR video in billions of colors and up to 4 simultaneous 4K displays. 12th Gen Intel® Core™ desktop processors are capable of canceling out interruptions with enhanced Gaussian & Neural Accelerator 3.0 (GNA) for more efficient noise suppression and back-ground blurring on video. For elite gaming, world-class productivity, free flowing creation, and more, 12th Gen Intel® Core™ desktop processors enable deep immersion and focus.Immersive ExperiencesAccelerating Platform InnovationTap into the latest platform technologies that drive incredible gaming, workflow, and creation. Our 12th Gen Intel® Core™ desktop processors offer up to 20 lanes (16 PCIe 5.0 and 4 PCIe 4.0) to drive optimal discrete graphics and storage performance by enabling higher bandwidth connection points. DDR5 brings fast speeds up to 4800 MT/s, this allows for increased memory bandwidth speeds compared to previous genera-tions that use DDR4 3200 MT/s memory.2 Fine tune both compute power and performance with unlocked 12th Gen Intel® Core™ desktop processors that have overclocking capabili-ties and Advanced Tuning support via Intel® Extreme Tuning Utility (XTU).3 With these and other platform enhancements you’ll be able to work, game, and create with impressive control and confidence.FEATURE BENEFITPerformance Hybrid Architecture Performance hybrid architecture, combining Performance-cores (P-cores)and Efficient-cores (E-Cores) to deliver balanced single-thread and multi-threadedreal-world performance.Intel® Thread Director1Optimizes workloads by helping the OS scheduler intelligently distribute workloadsto the optimal cores.PCIe 5.0 up to 16 Lanes Offers readiness for up to 32 GT/s for fast access to peripheral devices and networkingwith up to 16 PCI Express 5.0 lanes.PCIe 4.0 up to 4 Lanes Offers up to 16 GT/s for fast access to peripheral devices and networking withup to 4 PCI Express 4.0 lanes.Up to DDR5 4800 MT/s2This industry first memory technology supports fast frequencies and high bandwidthand throughput leading to enhanced workflow and productivity.Up to DDR4 3200 MT/s2Supports faster frequencies and higher bandwidth and throughput leadingto enhanced workflow and productivity.L3 and L2 Cache Increased shared Intel® Smart Cache (L3) and L2 cache sizes deliver large memorycapacity and reduced latency for fast game loading and smooth frame rates.Intel® Deep Learning Boost Accelerates AI inference to improve performance for deep learning workloads.Gaussian & Neural Accelerator 3.0 (GNA 3.0)IProcesses AI speech and audio applications such as neural noise cancellation while simultaneously freeing up CPU resources for overall system performance and responsiveness.Intel® Turbo Boost Max Technology 3.0Identifies the processor’s fastest cores and directs critical workloads to them.Intel® UHD Graphics driven by X e Architecture Rich media and intelligent graphics capabilities enable amplified visual complexity, enhanced 3D performance, and faster image processing.Overclocking Features and Capabilities When paired with the Intel® Z690 chipset, processor P-cores, E-cores, graphics, and memory can be set to run at frequencies above the processor specification resulting in higher performance.Intel® Core™i9-12900K & i9-12900KF4Intel® Core™i7-12700K &i7-12700KF4Intel® Core™i5-12600K &i5-12600KF4Max Turbo Frequency [GHz]Up to 5.2Up to 5.0Up to 4.9 Intel® Turbo Boost Max Technology3.0 Frequency [GHz]Up to 5.2Up to 5.0n/a Single P-core Turbo Frequency [GHz]Up to 5.1Up to 4.9Up to 4.9 Single E-core Turbo Frequency [GHz]Up to 3.9Up to 3.8Up to 3.6P-core Base Frequency [GHz] 3.2 3.6 3.7E-core Base Frequency [GHz] 2.4 2.7 2.8 Processor Cores (P-cores + E-cores)16 (8P + 8E)12 (8P + 4E)10 (6P + 4E) Intel® Hyper-Threading Technology5Yes Yes YesTotal Processor Threads242016Intel® Thread Director1Yes Yes YesIntel® Smart Cache (L3) Size [MB]302520Total L2 Cache Size [MB]14129.5Max Memory Speed [MT/s] Up to DDR5 4800Up to DDR4 3200Up to DDR5 4800Up to DDR4 3200Up to DDR5 4800Up to DDR4 3200Number of Memory Channels222CPU PCIe 5.0 Lanes161616CPU PCIe 4.0 Lanes444Enhanced Intel® UHD Graphics drivenby X e ArchitectureIntel® UHD Graphics 770Intel® UHD Graphics 770Intel® UHD Graphics 770 Graphics Dynamic Frequency [MHz]Up to 1550Up to 1500Up to 1450Processor P-core/E-core/Graphics/Memory Overclocking3Yes Yes YesIntel® Quick Sync Video Yes Yes YesIntel® Deep Learning Boost (Intel® DL Boost)Yes Yes YesIntel® Advanced Vector Extensions 2 (Intel® AVX2)Yes Yes YesIntel® Gaussian and Neural Accelerator (GNA) 3.0Yes Yes YesIntel® Virtualization Technology (Intel® VT-x / VT-d)Yes Yes YesMode-based Execution Control (MBEC)Yes Yes YesIntel® Threat Detection Technology (Intel® TDT)Yes Yes YesIntel® Control-Flow Enforcement Technology(Intel® CET)Yes Yes YesIntel® Advanced Encryption Standard NewInstructions (Intel® AES-NI)Yes Yes YesIntel® BIOS Guard Yes Yes YesIntel® Boot Guard Yes Yes YesIntel® OS Guard Yes Yes YesIntel® Advanced Programmable Interrupt ControllerVirtualization (Intel® APIC-v)Yes Yes YesIntel® Secure Key Yes Yes YesIntel® Platform Trust Technology (Intel® PTT)Yes Yes YesProduct Brief ©Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.Notices & Disclaimers1Intel® Thread Director is designed into 12th Gen Intel® Core™ processors and helps supportingoperating systems to more intelligently channel workloads to the right core. No user action required. See for details.2Based on memory bandwidth results using Intel® Memory Latency Checker Tool v3.9a System A: Core i9-12900K on Asus Z690 TUF DDR4 Motherboard. 2x16GB G.Skill TridentZ 3200Mhz CL14 RAM System B: Core i9-12900K on Asus Z690 Prime-P DDR5 Motherboard. 2x16GB SK.Hynix 4400Mhz CL40 RAM.3Altering clock frequency or voltage may damage or reduce the useful life of the processor and other system components, and may reduce system stability and performance. Product warranties may not apply if the processor is operated beyond its specifications. Check with the manufacturers of system and components for additional details.4Processor names with an ‘F’ suffix do not have processor graphics and require a discrete graphics solution. Without processor graphics the processor display output ports will not function. 5Intel® Hyper-Threading Technology is only available on P-cores.Performance varies by use, configuration and other factors. Learn more at /PerformanceIndex .Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available u pdates. See backup for configuration details. No product or component can be abso-lutely secure.Your costs and results may vary.Intel technologies may require enabled hardware, software or service activation.Altering clock frequency or voltage may void any product warranties and reduce stability, security, performance, and life of the processor and other components. Check with system and component manufacturers for details.For use only by product developers, software developers, and system integrators. For evaluation only; not FCC approved for resaleThis device has not been authorized as required by the rules of the Federal Communications Commission. This device is not, and may not be, offered for sale or lease, or sold or leased, until authorization is obtained.Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at .12th Gen Intel® Core™ Desktop Processors。

华为云引擎系列交换机技术介绍说明书

CloudEngine Is the Foundation of the Intent-driven NetworkHuawei CloudEngine Series Switches Technical PresentationContentsClick to add Title 1Click to add Title 2Click to add Title 3CloudEngine Switch OverviewCloudEngine Switch HighlightsCloudEngine Switch Market ProgressSwitches Are the Cornerstone for Transforming Data Centers from Service Centers to Value CentersCloud computingBig DataDistributed storageMetcalfe's Law: The effect of a telecommunications network is proportional to the square of the number of connected users of the system.-Robert Metcalfe who invented Ethernet, founder of 3Com In the future, even if all hardware network devices will disappear, data center switches used as the buses connecting to servers, will always exist. The Ethernet helps release the value of data.AISDN NFVIntent-driven networkUltra-broadbandInfrastructureSimplifiedOpenController and management tool layerControllerAnalyzerSecurityCharacteristics of the Future of DC Switches: Ultra-broadband, Simplified, Intelligent, Secure, and OpenIntelligentSecureManagementControlAnalysisOpenConvergenceEcosystemSpine LeafGatewayBandwidth -> LatencyLayer 2 and Layer 3 -> SecurityManual driving -> Automated drivingWeb page -> Service integrationCloudEngine Series Data Center Switches Portfolio(1)Core SwitchesAccess SwitchesCloudEngine 6881-48S6CQ (New)CloudEngine 6863-48S6CQ (New)CloudEngine 16800 (New)CloudEngine 16816CloudEngine 16808CloudEngine 1680410GE ToR switch25GE ToR switchCloudEngine Series Data Center Switches Portfolio(2)Core SwitchesAccess Switches10GE ToR switchCE6851-48S6Q-HICE6810-48S4Q-LICE6810-32T16S4Q-LIGE ToR switchCE5855-48T4S2Q-EICE5855-24T4S2Q-EIVirtual SwitchesCE1800VCE6855/CE6856-48S6Q-HICE6855/CE6856-48T6Q-HI10GE large-buffer ToR switchCE6870-48S6CQ-EIToR switch with flexible cardsCE8861-4C-EI40GE switchCE7855-32Q-EICE6865-48S8CQ-EI25GE ToR switch100GE switchCE8850-64CQ-EICE12816CE12812CE12808CE12808S CE12804SCE12804CE12800CE12800SCE6870-48T6CQ-EICE6875-48S4CQ-EICE8850-32CQ-EICE6860-48S8CQ-EICE6857-48S6CQ-EICE8860-4C-EICE5880-48T6Q-EICE6880-24S4Q2CQ-EIOrthogonal architectureStrict front-to-back airflow designNon-blocking switchingCounter-rotating fansLine cardNo cabling of the backplaneIncreased bandwidth of the entire systemCE12800Patent No.: CN201110339954.1Independent front-to-back airflowEven heat dissipation, suitable for data centersCell switching and VoQTraffic balancing, improving bandwidth utilizationCounter-rotating and turbo fansHighly efficient heat dissipationLeading energy-conserving designHigh-Quality CloudEngine: High-Quality Architecture Creates a Green and Stable Network•Industry-leading architecture design and high quality:orthogonal SFU design,Clos architecture,cell switching,and Virtual Output Queue (VOQ)mechanism 1/31/31/31/31/31/31/31/31/31/31/31/31/31/31/31/31/31/3ContentsClick to add Title 1Click to add TitleCloudEngine Switch Overview3CloudEngine Switch Market Progress▪Ultra-broadband Cloud Engine ▪Simplified Cloud Engine ▪Intelligent Cloud Engine▪Secure Cloud Engine ▪Open Cloud Engine2CloudEngine Switch HighlightsClos Theory: Cluster Scale Is the Driving Force for Data Center Network Architecture EvolutionSpineLeafCore EdgeSpineLeafCoreEdgeSpineLeafEdgeL2L310GE10GE40GE 40GE 40GEL2BGPL3L3First generation: 3K GE serversSecond generation: 10K GE serversThird generation: 20K 10GE servers⚫The port capacity of cards increases continuously, and CE switches canprovide 36*100GE ports.⚫To avoid HASH polarization, CE switches provide 128 ECMP paths.⚫Network congestion control: CE switches provide large buffer, and split a single flow into multiple ones to load balance them.Difficulties in the non-blocking Clos architecture: The convergence ratio and packet loss ratio cannot be compromised.⚫Data center network architecture: A fat-tree topology is used and the capacity of the root node determines the server cluster scale.⚫Evolution direction: Add network layers, and increase the quantity and capacity of spine or code nodes.⚫Network congestion control: Increase the buffer and optimize load balancing.CE switches' buffer is 80 times higher than the industry average, implementing zero packet loss for microburst traffic. The switches' performance is 1032 Tbit/s. CE switches can connect to over 50,000 servers with no blocking.Larger Interface Rate: The Rise of 25GE Interfaces Balance the Cost and Efficiency10M1980100M: IEEE802.3u199519981000M: IEEE802.3ab/z20021G: IEEE802.3ae/ak201040G/100G: IEEE802.3ba2008DCB/PB (IETF TRILL)2013400G2009FCoE201625G: 802.byDevelopment of Ethernet:DPDKIn the past two years, why are 25GE interfaces used?➢The 25GE interface can better match the SerDes rate: 1.25 Gbit/s -> 3.125 Gbit/s -> 6.25 Gbit/s -> 10.3125 Gbit/s -> 25 Gbit/s -> 56 Gbit/s➢Compared with the 40GE NIC, the 25GE NIC has higher use efficiency of the PCIe channel. (40G+40G)/8G*16= 62.5%; 25G*2/(8G*8) = 78%➢Lower cabling costs for 25GE interfaces: The SFP28 module is used. Because only single-channel connections are used, the SFP28 module is compatible with LC optical fibers in the 10GE era, without cabling.➢The bandwidth between NICs has exceeded 10 Gbit/s: As technologies such as RDMA, SR-IOV, and DPDK develop, the bandwidth between NICs has exceeded 10 Gbit/s.APP RDMA NICCoprocess or/FPGAAPPRDMA NICFast CNPCNPPPVIQ: eliminates packet lossinside chipsVIQ12Dynamic ECN3Dynamic ECNFast CNPPacket lossTraditionalVIQVIQ enables the outbound interface to send backpressure signals to the inbound interface, achieving zero packet loss.PFCSRECNNormal CNPPhysical queueThreshold (Port-Buffer)SwitchServer Q0Q1ECN waterline ECN waterlineRR ServerServerServer.. .Dynamic ECN uses dynamic collection and dynamic threshold adjustment to realize low latency and high throughput.Fast CNP provides fast congestion feedback to improve networkconvergence performance by 30%.AI Fabric: Intelligent Lossless Data Center Network Solution Provides Low latency and Zero Packet LossFast CNPUltra-broadband Cloud Engine Simplified Cloud Engine Intelligent Cloud Engine Secure CloudEngine Open Cloud Engine➢Independent forwarding, control, anddetection, and 3-channel cluster design ➢Four dedicated GE interfaces are used ascluster control channels.➢ A maximum of 3.2 Tbit/s cluster bandwidthis supported.Unique three-channel separated cluster, control plane coupling…Control signalingchannelData forwardingchannel Dual-active detection (DAD) channel➢The control plane runs independently and synchronizes asmall amount of information about interface status entries.➢Devices in the DFS group can be upgraded independently,without interrupting services.➢When the peer-link is faulty or the M-LAG master devicefails twice, the M-LAG backup device can still work properly.Independent control plane, protocol-level coupling…Peer-linkDAD channelDevice Virtualization: Easy-to-Manage, High-Performing, Highly Reliable Virtual SystemsC luster S witch S ystem (CSS)M ulti-Chassis LAG (M-LAG)➢The control plane runs independently anddoes not have synchronization information.➢Two switches are configured with the samegateway IP address and MAC address.➢Two links of the server NIC are configured tosend broadcast packets simultaneously.Independent control planewithout couplingM-LAG Lite➢Provide a maximum of 1:16virtualization capabilities in port and port group mode.On-demand VS allocation, improving resource utilization➢Exclusive CPU, memory, and MAC/VLAN/FIB entriesExclusive resources in VSs and highest specificationsFault isolation between VSs, improving securityVS (V irtual S ystem )Ultra-broadband Cloud Engine Simplified Cloud Engine Intelligent Cloud Engine Secure CloudEngine Open Cloud EngineLayer 2 Boundary Extension: Build a Large-Scale Network Resource Pool Based on BGP EVPNBGP EVPN acts as the VXLAN control plane to provide the following functions:➢Triggers automatic VXLAN tunnel setup between VTEPs to avoid the need to manually configure full-mesh tunnels.➢Advertises host routes and MAC address table, prevents unknown traffic flooding, and optimizes packet forwarding.➢Implements Layer 2 interconnection between data centers in different networking.Layer 2 large-scale horizontal expansion in the data centerand extension to the remote DCVXLAN BGP EVPNVTEP VTEP VTEP VTEP RRRRBGP EVPNVTEP VTEPProtocol vitality: open interconnection and interworkingbetween devices from different vendorsNetwork Automation: Interconnection with Third-Party Management Tools, Controllers, Virtualization Management Platforms, and Cloud PlatformsScenario 1: traditional network management➢Interconnection with a third-party management tool : CE switches can interconnect with a third-party management tool such as Ansible to implement automatic network configuration.Scenario 2: network and computing association➢Interconnection with a virtualization management platform : CE switches are connected to the Agile Controller-DCN, and the Agile Controller-DCN is associated with the third-party computing management platform.Scenario 3: third-party management on the overlay➢Interconnection with a third-party controller : The CE switch functions as the VXLAN Layer 2 VTEP and is managed by the NSX.Scenario 4: cloud-network integration➢Interconnection with a cloud platform through the Agile Controller-DCN : CE switches are connected to the AgileController-DCN, and the Agile Controller-DCN connects to the third-party cloud platform.SpineLeafGateway10GE40GEDCScenario 1Interconnection with a managementtoolISP2Scenario 2Interconnection with avirtualization managementplatformScenario 3Interconnectionwith a third-party controller Scenario 4Interconnection with a cloud platformSimplified Deployment: IPv4 and IPv6, Unicast and Overlay Multicast, and Rollout of Full-stack Services Within MinutesServer leaf IPv6IPv4VTEP Server leaf SpineVTEPServer leaf VM VM VMOVSBorder-LeafBMVTEP VM VM VMOVSServer leaf VTEPBMIPv4 extranetIPv4Service-centered IPv6 evolution mode➢2018 Q3: virtualization ➢2019 Q1: cloud-network cooperationServer leafIPv6IPv4VTEP Server leaf SpineVTEPServer leaf VM VM VMOVSBorder-LeafBMVTEP VM VM VMOVSServer leaf VTEPIPv6 extranetIPv4 extranetIPv4IPv6 extranetReplicate IPv4 O&MexperiencesServer leafVTEP Server leaf SpineVTEPServer leaf VM VM VMOVSBM VTEP VM VM VMOVSServer leaf VTEPIPv4 extranetIPv4 extranetOverlay multicastSave bandwidthServer leafVTEP Server leaf SpineVTEPServer leaf VM VM VMOVSBM VTEP VM VM VMOVSServer leaf VTEPIPv4 extranetIPv4 extranetDual-stackMulticastIngress replicationIGMP/PIM-SM➢2018 Q3: commercial chip ready ➢2019 Q1: controller mappingCollectorAnalyzerCPU Forwarding Chip CollectorAnalyzerCPUForwarding ChipCollectorAnalyzerCPUForwarding ChipNP•SNMP or NETCONF uses the query/response mechanism, minute-level reporting, and XML or text encoding, which is inefficient.•NetStream uses the flow sampling mechanism and requires CPU participation, which has low performance and is inaccurate.•gRPC uses the subscription/reporting mechanism, subsecond-level reporting , protobuffer coding, and HTTP transmission, which has a high efficiency .•ERSPAN+ adds ingress and egress ports or timestamps of original flows to calculate the flow path and delay .•INT supports in-line path or quality detection.SNMP NetconfNetstreamERSPANSNMP NetconfNetstreamERSPAN+INTgRPCSNMP NetconfFlow tableProtobuf over UDPgRPCERSPAN+Netstream1:1•Protobuf over UDP is used to encode andtransmit forwarding plane information, which is efficient and does not affect CPU performance .•Small NP intelligent analysis algorithm is used to perform in-depth analysis of abnormal flows to learn in-depth information such as the latency, jitter, packet loss ratio, and packet loss location .Historical CapabilitiesCurrent CapabilitiesFuture EvolutionTelemetry Capability: Transformation of the Data Collection Mode Is the Basis of Big Data O&MUltra-broadband Cloud Engine Simplified Cloud Engine Intelligent Cloud Engine Secure CloudEngine Open Cloud EngineMicroburst Detection Capability: Millisecond-level Buffer Monitoring and Subscription Collection, Which Are Visible and ClearData CenterService exceptionNormal networkTraditional NMSArtifactFreezeSubsecond-levelcollectiongRPC subscription . . .Content feedbackOne request formultiple tasks•Visible: subsecond-level subscription data collection510us50%100%The buffer is full and packet loss may occur.2-ms buffer monitoring•Clear: high-precision data monitoring5-minute pollingperiodSNMP request and response. . .Multiple requests for a single task510s50%100%Normal buffer detectionMicrosecond-level buffer monitoring•The collection period is too long, which may ignore network details.•The detection interval is too long, so device details may be incomplete.Forwarding chipCPUFPGACE8860Monitoring queueNote: The CE8860 supports this function.VM 1VM 2VM 3 1.1.1.1 1.1.1.2 1.1.1.3VM 4VM 5VM 6 2.2.2.1 2.2.2.2 2.2.2.3As Is: subnet-based isolation To Be:VM-level isolationFine-grained DefenseDefining applications based on VM names and discrete IP addresses, with finer granularity and wider dimensionsFlexible DeploymentDefining services based on application groups and decoupling from subnets to achieve flexible deployment Distributed SecurityTraffic of access switches is filtered nearby and east-west isolation is implemented without using firewalls.Use Microsegmentation to Achieve Fine-grained Isolation and Service SecurityWebAppAFW IDS LB NATVASResource poolSimplified deploymentThe SDN controller definesservice chains through drag-and-drop operations.Efficient forwardingProvide traffic diversion for one time, simple configuration, service traffic forwarding, and secure monitoring.Flexible orchestrationDecouple the VAS function from Fabric, providing flexible orchestration.Switch SwitchSwitchAgile CloudEngine: Supporting NSH Service Chains, Providing Easier VAS OrchestrationACOpticalfiber/transmissiondevice/Layer 2 transparenttransmissionMacSec at the Link Layer: IP Layer 3 Features such as Encryption Are Introduced to the MAC Link LayerSwitch ASwitch BScenario➢In scenarios that require high data confidentiality, such asgovernment, military, and finance scenarios, interconnection is required between data centers or between different modules of data centers across buildings.➢The CE6875 uplink port (100GE), and CEL16CQFD (16*100GE) and CEL08CFFG1 (8*200GE) cards of the CE12800 can be used.Definition➢Media Access Control Security (MACsec) ensures securecommunication within LANs in compliance with IEEE 802.1AE and 802.1X. It provides identity authentication, data encryption, integrity check, and replay protection to protect Ethernet frames and prevent devices from processing attack packets.NetworkingNetworkingOriginal packetData encryption protectionMACsec packetData integrity protectionStandardsChinaIntegration InnovationEcological cooperationGermany MoscowMulti-vendor pre-integration verificationMulti-layer open ecosystemOpen Ecosystem: Huawei Joins Hands with 20+ Industry Chain Partners to Perform System IntegrationOpen ecosystem: fast integration andsimplified managementSystem integration: 10+ OpenLabs in the globeManufacturerNSXAnsible. . .Rapid response to service requirementsHardware BFDMicrosegmentationNSH modeIPv6 over VXLANCPUForwarding chipIntra-card CPU chip Quad-core CPU:▪Protocol packet processing▪FIB entry delivery ▪. . .Co-processor▪Hardware BFD ▪High-performance sFlow ▪. . .Forwarding chipAdjustable processes New service processes Adjustable entry resourcesEnhanced serviceprocessesVRPnetconfCLILinux ContainergRPCopenflowSSHpuppetFuncEditnetconfSNMPLinux and driverFragmentation and reassemblyOpen architecture, Flexible Business Innovation•Higher interface rate: 25GE interfaces and larger buffer cope with traffic surge in N:1 scenarios.•Flowlet&DLB: One flow is load balanced among multiple links.•AI Fabric intelligent lossless data center network solution: low latency and zero packet lossUltra-broadband: higher interface rate, more even load balancing, larger buffer, and lower latency•Telemetry capability•Microburst detection •Edge analysis capability•Microsegmentation used to isolate east-west traffic on switches (east-west traffic is isolated on firewalls originally)•SFC used to divert traffic from the control plane to the data plane•MACsec hardware encryption, providing high security and reliability•Open API•Interconnection with third-party management tools: Ansible•Interconnection with third-party management tools or controllers: VMaare NSX•Multiple virtualization technologies: CSS, M-LAG, M-LAG Lite, and VS •VXLAN + BGP EVPN: intra-DC and inter-DC virtualization•SDN controller: deployment in drag-and-drop mode, IPv4 and IPv6, rollout of unicast and multicast full-stack services in minutesIntelligent: enabling service agilitySimplified: automatic deployment of full-stack services and service rollout within minutesOpen: easy integration and timelyresponse to servicesSecure: best quality in the industry and pioneering energy-saving technology CloudEngine High-Performance Cloud SwitchesContents1Click to add Title 2CloudEngine Switch OverviewCloudEngine Switch Highlights Click to add Title 3CloudEngine Switch Market ProgressChina's No.1 and One of World's Top 3 DCN Vendors2014Source: IHS “2015 Infonetics Data Center and Enterprise SDN Vendor Leadership Analysis ”20132012•Data center network vendor with the fastest growth•First release of InterOP impressing the world •Industry-leading ultra-high performance2015•Huawei was the only Chinese vendor in the global SDN leadership list.•Largest market share in China in Q2•Huawei was the global data center network vendor with the fastest growth.•Annual growth rate up to 137%Global SDN AuthoritativeReport of Leading Vendors2016•The market share ranks No. 1 in Chi na and the third largest in the world .•SDN capability won the Best of ShowNet Award at Tokyo Interop.2017•Huawei was positioned as challenger in Gartner's Magic Quadrant for Data Center Networking.2018•Huawei has been positioned as a leader in data center hardware platforms for SDN.•The AI Fabric won the Best of Show Gold Award.In 2013, the CloudEngine 12800 won the Best of Show Award at Interop, which is the highest exhibition in the IT industry. Huawei is the first Chinese provider that wins the position.Highly Recognized PerformanceAward of Excellent Product Trusted byCIOAward of the Most Competitive Product Awards and CertificationsPreferred Brand of Cloud Computing and Network SolutionAward of Annual Excellent TechnologyChina SDN SDN Best Practice AwardAward of Excellent Product in Big DataIn 2016, the CE8860 and CE6851 won the Best of Show Award at Interop.InterOP AwardsHuawei's AI FabricIntelligent Lossless Data Center Network Solution Takes Home Interop Tokyo Best of Show AwardCloudEngineSeries Switches Serve 7800+ Global Customers⚫The market share is No.1in China and No.3in theworld.⚫The global market share growth rate is No. 1 for fourconsecutive years .⚫Over 32,000 CE12800 switches have been soldaround the world, serving 7800+customers in 120+countries.DC SDN SDN hardware platform leader⚫2018 Approaching the Leaders Quadrant ⚫2017 ChallengerGartner Peer InsightsCustomers’ Choice for Data Center NetworkingCopyright©2018 Huawei Technologies Co., Ltd.All Rights Reserved.The information in this document may contain predictivestatements including, without limitation, statements regarding the future financial and operating results, future productportfolio, new technology, etc. There are a number of factors that could cause actual results and developments to differ materially from those expressed or implied in the predictive statements. Therefore, such information is provided for reference purpose only and constitutes neither an offer nor an acceptance. Huawei may change the information at any time without notice.把数字世界带入每个人、每个家庭、每个组织,构建万物互联的智能世界。

数字无线通信系统中的调制(英文)

AgilentDigital Modulation in Communications Systems—An IntroductionApplication Note 1298This application note introduces the concepts of digital modulation used in many communications systems today. Emphasis is placed on explaining the tradeoffs that are made to optimize efficiencies in system design.Most communications systems fall into one of three categories: bandwidth efficient, power efficient, or cost efficient. Bandwidth efficiency describes the ability of a modulation scheme to accommodate data within a limited bandwidth. Power efficiency describes the ability of the system to reliably send information at the lowest practical power level.In most systems, there is a high priority on band-width efficiency. The parameter to be optimized depends on the demands of the particular system, as can be seen in the following two examples.For designers of digital terrestrial microwave radios, their highest priority is good bandwidth efficiency with low bit-error-rate. They have plenty of power available and are not concerned with power efficiency. They are not especially con-cerned with receiver cost or complexity because they do not have to build large numbers of them. On the other hand, designers of hand-held cellular phones put a high priority on power efficiency because these phones need to run on a battery. Cost is also a high priority because cellular phones must be low-cost to encourage more users. Accord-ingly, these systems sacrifice some bandwidth efficiency to get power and cost efficiency. Every time one of these efficiency parameters (bandwidth, power, or cost) is increased, another one decreases, becomes more complex, or does not perform well in a poor environment. Cost is a dom-inant system priority. Low-cost radios will always be in demand. In the past, it was possible to make a radio low-cost by sacrificing power and band-width efficiency. This is no longer possible. The radio spectrum is very valuable and operators who do not use the spectrum efficiently could lose their existing licenses or lose out in the competition for new ones. These are the tradeoffs that must be considered in digital RF communications design. This application note covers•the reasons for the move to digital modulation;•how information is modulated onto in-phase (I) and quadrature (Q) signals;•different types of digital modulation;•filtering techniques to conserve bandwidth; •ways of looking at digitally modulated signals;•multiplexing techniques used to share the transmission channel;•how a digital transmitter and receiver work;•measurements on digital RF communications systems;•an overview table with key specifications for the major digital communications systems; and •a glossary of terms used in digital RF communi-cations.These concepts form the building blocks of any communications system. If you understand the building blocks, then you will be able to under-stand how any communications system, present or future, works.Introduction25 5 677 7 8 8 9 10 10 1112 12 12 13 14 14 15 15 16 17 18 19 20 21 22 22 23 23 24 25 26 27 28 29 29 30 311. Why Digital Modulation?1.1 Trading off simplicity and bandwidth1.2 Industry trends2. Using I/Q Modulation (Amplitude and Phase Control) to Convey Information2.1 Transmitting information2.2 Signal characteristics that can be modified2.3 Polar display—magnitude and phase representedtogether2.4 Signal changes or modifications in polar form2.5 I/Q formats2.6 I and Q in a radio transmitter2.7 I and Q in a radio receiver2.8 Why use I and Q?3. Digital Modulation Types and Relative Efficiencies3.1 Applications3.1.1 Bit rate and symbol rate3.1.2 Spectrum (bandwidth) requirements3.1.3 Symbol clock3.2 Phase Shift Keying (PSK)3.3 Frequency Shift Keying3.4 Minimum Shift Keying (MSK)3.5 Quadrature Amplitude Modulation (QAM)3.6 Theoretical bandwidth efficiency limits3.7 Spectral efficiency examples in practical radios3.8 I/Q offset modulation3.9 Differential modulation3.10 Constant amplitude modulation4. Filtering4.1 Nyquist or raised cosine filter4.2 Transmitter-receiver matched filters4.3 Gaussian filter4.4 Filter bandwidth parameter alpha4.5 Filter bandwidth effects4.6 Chebyshev equiripple FIR (finite impulse response) filter4.7 Spectral efficiency versus power consumption5. Different Ways of Looking at a Digitally Modulated Signal Time and Frequency Domain View5.1 Power and frequency view5.2 Constellation diagrams5.3 Eye diagrams5.4 Trellis diagramsTable of Contents332 32 32 33 33 34 3435 35 3637 37 37 38 38 39 39 39 40 41 41 42 434344466. Sharing the Channel6.1 Multiplexing—frequency6.2 Multiplexing—time6.3 Multiplexing—code6.4 Multiplexing—geography6.5 Combining multiplexing modes6.6 Penetration versus efficiency7. How Digital Transmitters and Receivers Work7.1 A digital communications transmitter7.2 A digital communications receiver8. Measurements on Digital RF Communications Systems 8.1 Power measurements8.1.1 Adjacent Channel Power8.2 Frequency measurements8.2.1 Occupied bandwidth8.3 Timing measurements8.4 Modulation accuracy8.5 Understanding Error Vector Magnitude (EVM)8.6 Troubleshooting with error vector measurements8.7 Magnitude versus phase error8.8 I/Q phase error versus time8.9 Error Vector Magnitude versus time8.10 Error spectrum (EVM versus frequency)9. Summary10. Overview of Communications Systems11. Glossary of TermsTable of Contents (continued)4The move to digital modulation provides more information capacity, compatibility with digital data services, higher data security, better quality communications, and quicker system availability. Developers of communications systems face these constraints:•available bandwidth•permissible power•inherent noise level of the systemThe RF spectrum must be shared, yet every day there are more users for that spectrum as demand for communications services increases. Digital modulation schemes have greater capacity to con-vey large amounts of information than analog mod-ulation schemes. 1.1 Trading off simplicity and bandwidthThere is a fundamental tradeoff in communication systems. Simple hardware can be used in transmit-ters and receivers to communicate information. However, this uses a lot of spectrum which limits the number of users. Alternatively, more complex transmitters and receivers can be used to transmit the same information over less bandwidth. The transition to more and more spectrally efficient transmission techniques requires more and more complex hardware. Complex hardware is difficult to design, test, and build. This tradeoff exists whether communication is over air or wire, analog or digital.Figure 1. The Fundamental Tradeoff1. Why Digital Modulation?51.2 Industry trendsOver the past few years a major transition has occurred from simple analog Amplitude Mod-ulation (AM) and Frequency/Phase Modulation (FM/PM) to new digital modulation techniques. Examples of digital modulation include•QPSK (Quadrature Phase Shift Keying)•FSK (Frequency Shift Keying)•MSK (Minimum Shift Keying)•QAM (Quadrature Amplitude Modulation) Another layer of complexity in many new systems is multiplexing. Two principal types of multiplex-ing (or “multiple access”) are TDMA (Time Division Multiple Access) and CDMA (Code Division Multiple Access). These are two different ways to add diversity to signals allowing different signals to be separated from one another.Figure 2. Trends in the Industry62.1 Transmitting informationTo transmit a signal over the air, there are three main steps:1.A pure carrier is generated at the transmitter.2.The carrier is modulated with the informationto be transmitted. Any reliably detectablechange in signal characteristics can carryinformation.3.At the receiver the signal modifications orchanges are detected and demodulated.2.2 Signal characteristics that can be modified There are only three characteristics of a signal that can be changed over time: amplitude, phase, or fre-quency. However, phase and frequency are just dif-ferent ways to view or measure the same signal change. In AM, the amplitude of a high-frequency carrier signal is varied in proportion to the instantaneous amplitude of the modulating message signal.Frequency Modulation (FM) is the most popular analog modulation technique used in mobile com-munications systems. In FM, the amplitude of the modulating carrier is kept constant while its fre-quency is varied by the modulating message signal.Amplitude and phase can be modulated simultane-ously and separately, but this is difficult to gener-ate, and especially difficult to detect. Instead, in practical systems the signal is separated into another set of independent components: I(In-phase) and Q(Quadrature). These components are orthogonal and do not interfere with each other.Figure 3. Transmitting Information (Analog or Digital)Figure 4. Signal Characteristics to Modify2. Using I/Q Modulation to Convey Information72.3 Polar display—magnitude and phase repre-sented togetherA simple way to view amplitude and phase is with the polar diagram. The carrier becomes a frequency and phase reference and the signal is interpreted relative to the carrier. The signal can be expressed in polar form as a magnitude and a phase. The phase is relative to a reference signal, the carrier in most communication systems. The magnitude is either an absolute or relative value. Both are used in digital communication systems. Polar diagrams are the basis of many displays used in digital com-munications, although it is common to describe the signal vector by its rectangular coordinates of I (In-phase) and Q(Quadrature).2.4 Signal changes or modifications inpolar formFigure 6 shows different forms of modulation in polar form. Magnitude is represented as the dis-tance from the center and phase is represented as the angle.Amplitude modulation (AM) changes only the magnitude of the signal. Phase modulation (PM) changes only the phase of the signal. Amplitude and phase modulation can be used together. Frequency modulation (FM) looks similar to phase modulation, though frequency is the controlled parameter, rather than relative phase.Figure 6. Signal Changes or Modifications8One example of the difficulties in RF design can be illustrated with simple amplitude modulation. Generating AM with no associated angular modula-tion should result in a straight line on a polar display. This line should run from the origin to some peak radius or amplitude value. In practice, however, the line is not straight. The amplitude modulation itself often can cause a small amount of unwanted phase modulation. The result is a curved line. It could also be a loop if there is any hysteresis in the system transfer function. Some amount of this distortion is inevitable in any sys-tem where modulation causes amplitude changes. Therefore, the degree of effective amplitude modu-lation in a system will affect some distortion parameters.2.5 I/Q formatsIn digital communications, modulation is often expressed in terms of I and Q. This is a rectangular representation of the polar diagram. On a polar diagram, the I axis lies on the zero degree phase reference, and the Q axis is rotated by 90 degrees. The signal vector’s projection onto the I axis is its “I” component and the projection onto the Q axisis its “Q” component.Figure 7. “I-Q” Format92.6 I and Q in a radio transmitterI/Q diagrams are particularly useful because they mirror the way most digital communications sig-nals are created using an I/Q modulator. In the transmitter, I and Q signals are mixed with the same local oscillator (LO). A 90 degree phase shifter is placed in one of the LO paths. Signals that are separated by 90 degrees are also known as being orthogonal to each other or in quadrature. Signals that are in quadrature do not interfere with each other. They are two independent compo-nents of the signal. When recombined, they are summed to a composite output signal. There are two independent signals in I and Q that can be sent and received with simple circuits. This simpli-fies the design of digital radios. The main advan-tage of I/Q modulation is the symmetric ease of combining independent signal components into a single composite signal and later splitting such a composite signal into its independent component parts. 2.7 I and Q in a radio receiverThe composite signal with magnitude and phase (or I and Q) information arrives at the receiver input. The input signal is mixed with the local oscillator signal at the carrier frequency in two forms. One is at an arbitrary zero phase. The other has a 90 degree phase shift. The composite input signal (in terms of magnitude and phase) is thus broken into an in-phase, I, and a quadrature, Q, component. These two components of the signal are independent and orthogonal. One can be changed without affecting the other. Normally, information cannot be plotted in a polar format and reinterpreted as rectangular values without doing a polar-to-rectangular conversion. This con-version is exactly what is done by the in-phase and quadrature mixing processes in a digital radio. A local oscillator, phase shifter, and two mixers can perform the conversion accurately and efficiently.Figure 8. I and Q in a Practical Radio Transmitter Figure 9. I and Q in a Radio Receiver102.8 Why use I and Q?Digital modulation is easy to accomplish with I/Q modulators. Most digital modulation maps the data to a number of discrete points on the I/Q plane. These are known as constellation points. As the sig-nal moves from one point to another, simultaneous amplitude and phase modulation usually results. To accomplish this with an amplitude modulator and a phase modulator is difficult and complex. It is also impossible with a conventional phase modu-lator. The signal may, in principle, circle the origin in one direction forever, necessitating infinite phase shifting capability. Alternatively, simultaneous AM and Phase Modulation is easy with an I/Q modulator. The I and Q control signals are bounded, but infi-nite phase wrap is possible by properly phasing the I and Q signals.This section covers the main digital modulation formats, their main applications, relative spectral efficiencies, and some variations of the main modulation types as used in practical systems. Fortunately, there are a limited number of modula-tion types which form the building blocks of any system.3.1 ApplicationsThe table below covers the applications for differ-ent modulation formats in both wireless communi-cations and video. Although this note focuses on wireless communica-tions, video applications have also been included in the table for completeness and because of their similarity to other wireless communications.3.1.1 Bit rate and symbol rateTo understand and compare different modulation format efficiencies, it is important to first under-stand the difference between bit rate and symbol rate. The signal bandwidth for the communications channel needed depends on the symbol rate, not on the bit rate.Symbol rate =bit ratethe number of bits transmitted with each symbol 3. Digital Modulation Types and Relative EfficienciesBit rate is the frequency of a system bit stream. Take, for example, a radio with an 8 bit sampler, sampling at 10 kHz for voice. The bit rate, the basic bit stream rate in the radio, would be eight bits multiplied by 10K samples per second, or 80 Kbits per second. (For the moment we will ignore the extra bits required for synchronization, error correction, etc.)Figure 10 is an example of a state diagram of a Quadrature Phase Shift Keying (QPSK) signal. The states can be mapped to zeros and ones. This is a common mapping, but it is not the only one. Any mapping can be used.The symbol rate is the bit rate divided by the num-ber of bits that can be transmitted with each sym-bol. If one bit is transmitted per symbol, as with BPSK, then the symbol rate would be the same as the bit rate of 80 Kbits per second. If two bits are transmitted per symbol, as in QPSK, then the sym-bol rate would be half of the bit rate or 40 Kbits per second. Symbol rate is sometimes called baud rate. Note that baud rate is not the same as bit rate. These terms are often confused. If more bits can be sent with each symbol, then the same amount of data can be sent in a narrower spec-trum. This is why modulation formats that are more complex and use a higher number of states can send the same information over a narrower piece of the RF spectrum.3.1.2 Spectrum (bandwidth) requirementsAn example of how symbol rate influences spec-trum requirements can be seen in eight-state Phase Shift Keying (8PSK). It is a variation of PSK. There are eight possible states that the signal can transi-tion to at any time. The phase of the signal can take any of eight values at any symbol time. Since 23= 8, there are three bits per symbol. This means the symbol rate is one third of the bit rate. This is relatively easy to decode.Figure 10. Bit Rate and Symbol Rate Figure 11. Spectrum Requirements3.1.3 Symbol ClockThe symbol clock represents the frequency and exact timing of the transmission of the individual symbols. At the symbol clock transitions, the trans-mitted carrier is at the correct I/Q(or magnitude/ phase) value to represent a specific symbol (a specific point in the constellation).3.2 Phase Shift KeyingOne of the simplest forms of digital modulation is binary or Bi-Phase Shift Keying (BPSK). One appli-cation where this is used is for deep space teleme-try. The phase of a constant amplitude carrier sig-nal moves between zero and 180 degrees. On an I and Q diagram, the I state has two different values. There are two possible locations in the state dia-gram, so a binary one or zero can be sent. The symbol rate is one bit per symbol.A more common type of phase modulation is Quadrature Phase Shift Keying (QPSK). It is used extensively in applications including CDMA (Code Division Multiple Access) cellular service, wireless local loop, Iridium (a voice/data satellite system) and DVB-S (Digital Video Broadcasting — Satellite). Quadrature means that the signal shifts between phase states which are separated by 90 degrees. The signal shifts in increments of 90 degrees from 45 to 135, –45, or –135 degrees. These points are chosen as they can be easily implemented using an I/Q modulator. Only two I values and two Q values are needed and this gives two bits per symbol. There are four states because 22= 4. It is therefore a more bandwidth-efficient type of modulation than BPSK, potentially twice as efficient.Figure 12. Phase Shift Keying3.3 Frequency Shift KeyingFrequency modulation and phase modulation are closely related. A static frequency shift of +1 Hz means that the phase is constantly advancing at the rate of 360 degrees per second (2 πrad/sec), relative to the phase of the unshifted signal.FSK (Frequency Shift Keying) is used in many applications including cordless and paging sys-tems. Some of the cordless systems include DECT (Digital Enhanced Cordless Telephone) and CT2 (Cordless Telephone 2).In FSK, the frequency of the carrier is changed as a function of the modulating signal (data) being transmitted. Amplitude remains unchanged. In binary FSK (BFSK or 2FSK), a “1” is represented by one frequency and a “0” is represented by another frequency.3.4 Minimum Shift KeyingSince a frequency shift produces an advancing or retarding phase, frequency shifts can be detected by sampling phase at each symbol period. Phase shifts of (2N + 1) π/2radians are easily detected with an I/Q demodulator. At even numbered sym-bols, the polarity of the I channel conveys the transmitted data, while at odd numbered symbols the polarity of the Q channel conveys the data. This orthogonality between I and Q simplifies detection algorithms and hence reduces power con-sumption in a mobile receiver. The minimum fre-quency shift which yields orthogonality of I and Q is that which results in a phase shift of ±π/2radi-ans per symbol (90 degrees per symbol). FSK with this deviation is called MSK (Minimum Shift Keying). The deviation must be accurate in order to generate repeatable 90 degree phase shifts. MSK is used in the GSM (Global System for Mobile Communications) cellular standard. A phase shift of +90 degrees represents a data bit equal to “1,”while –90 degrees represents a “0.” The peak-to-peak frequency shift of an MSK signal is equal to one-half of the bit rate.FSK and MSK produce constant envelope carrier signals, which have no amplitude variations. This is a desirable characteristic for improving the power efficiency of transmitters. Amplitude varia-tions can exercise nonlinearities in an amplifier’s amplitude-transfer function, generating spectral regrowth, a component of adjacent channel power. Therefore, more efficient amplifiers (which tend to be less linear) can be used with constant-envelope signals, reducing power consumption.Figure 13. Frequency Shift KeyingMSK has a narrower spectrum than wider devia-tion forms of FSK. The width of the spectrum is also influenced by the waveforms causing the fre-quency shift. If those waveforms have fast transi-tions or a high slew rate, then the spectrumof the transmitter will be broad. In practice, the waveforms are filtered with a Gaussian filter, resulting in a narrow spectrum. In addition, the Gaussian filter has no time-domain overshoot, which would broaden the spectrum by increasing the peak deviation. MSK with a Gaussian filter is termed GMSK (Gaussian MSK).3.5 Quadrature Amplitude ModulationAnother member of the digital modulation family is Quadrature Amplitude Modulation (QAM). QAM is used in applications including microwave digital radio, DVB-C (Digital Video Broadcasting—Cable), and modems.In 16-state Quadrature Amplitude Modulation (16QAM), there are four I values and four Q values. This results in a total of 16 possible states for the signal. It can transition from any state to any other state at every symbol time. Since 16 = 24, four bits per symbol can be sent. This consists of two bits for I and two bits for Q. The symbol rate is one fourth of the bit rate. So this modulation format produces a more spectrally efficient transmission. It is more efficient than BPSK, QPSK, or 8PSK. Note that QPSK is the same as 4QAM.Another variation is 32QAM. In this case there are six I values and six Q values resulting in a total of 36 possible states (6x6=36). This is too many states for a power of two (the closest power of two is 32). So the four corner symbol states, which take the most power to transmit, are omitted. This reduces the amount of peak power the transmitter has to generate. Since 25= 32, there are five bits per sym-bol and the symbol rate is one fifth of the bit rate. The current practical limits are approximately256QAM, though work is underway to extend the limits to 512 or 1024 QAM. A 256QAM system uses 16 I-values and 16 Q-values, giving 256 possible states. Since 28= 256, each symbol can represent eight bits. A 256QAM signal that can send eight bits per symbol is very spectrally efficient. However, the symbols are very close together and are thus more subject to errors due to noise and distortion. Such a signal may have to be transmit-ted with extra power (to effectively spread the symbols out more) and this reduces power efficiency as compared to simpler schemes.Figure 14. Quadrature Amplitude ModulationCompare the bandwidth efficiency when using256QAM versus BPSK modulation in the radio example in section 3.1.1 (which uses an eight-bit sampler sampling at 10 kHz for voice). BPSK uses80 Ksymbols-per-second sending 1 bit per symbol.A system using 256QAM sends eight bits per sym-bol so the symbol rate would be 10 Ksymbols per second. A 256QAM system enables the same amount of information to be sent as BPSK using only one eighth of the bandwidth. It is eight times more bandwidth efficient. However, there is a tradeoff. The radio becomes more complex and is more susceptible to errors caused by noise and dis-tortion. Error rates of higher-order QAM systems such as this degrade more rapidly than QPSK as noise or interference is introduced. A measureof this degradation would be a higher Bit Error Rate (BER).In any digital modulation system, if the input sig-nal is distorted or severely attenuated the receiver will eventually lose symbol lock completely. If the receiver can no longer recover the symbol clock, it cannot demodulate the signal or recover any infor-mation. With less degradation, the symbol clock can be recovered, but it is noisy, and the symbol locations themselves are noisy. In some cases, a symbol will fall far enough away from its intended position that it will cross over to an adjacent posi-tion. The I and Q level detectors used in the demodulator would misinterpret such a symbol as being in the wrong location, causing bit errors. QPSK is not as efficient, but the states are much farther apart and the system can tolerate a lot more noise before suffering symbol errors. QPSK has no intermediate states between the four corner-symbol locations, so there is less opportunity for the demodulator to misinterpret symbols. QPSK requires less transmitter power than QAM to achieve the same bit error rate.3.6 Theoretical bandwidth efficiency limits Bandwidth efficiency describes how efficiently the allocated bandwidth is utilized or the ability of a modulation scheme to accommodate data, within a limited bandwidth. The table below shows the theoretical bandwidth efficiency limits for the main modulation types. Note that these figures cannot actually be achieved in practical radios since they require perfect modulators, demodula-tors, filter, and transmission paths.If the radio had a perfect (rectangular in the fre-quency domain) filter, then the occupied band-width could be made equal to the symbol rate.Techniques for maximizing spectral efficiency include the following:•Relate the data rate to the frequency shift (as in GSM).•Use premodulation filtering to reduce the occupied bandwidth. Raised cosine filters,as used in NADC, PDC, and PHS, give thebest spectral efficiency.•Restrict the types of transitions.Modulation Theoretical bandwidthformat efficiencylimitsMSK 1bit/second/HzBPSK 1bit/second/HzQPSK 2bits/second/Hz8PSK 3bits/second/Hz16 QAM 4 bits/second/Hz32 QAM 5 bits/second/Hz64 QAM 6 bits/second/Hz256 QAM 8 bits/second/HzEffects of going through the originTake, for example, a QPSK signal where the normalized value changes from 1, 1 to –1, –1. When changing simulta-neously from I and Q values of +1 to I and Q values of –1, the signal trajectory goes through the origin (the I/Q value of 0,0). The origin represents 0 carrier magnitude. A value of 0 magnitude indicates that the carrier amplitude is 0 for a moment.Not all transitions in QPSK result in a trajectory that goes through the origin. If I changes value but Q does not (or vice-versa) the carrier amplitude changes a little, but it does not go through zero. Therefore some symbol transi-tions will result in a small amplitude variation, while others will result in a very large amplitude variation. The clock-recovery circuit in the receiver must deal with this ampli-tude variation uncertainty if it uses amplitude variations to align the receiver clock with the transmitter clock. Spectral regrowth does not automatically result from these trajectories that pass through or near the origin. If the amplifier and associated circuits are perfectly linear, the spectrum (spectral occupancy or occupied bandwidth) will be unchanged. The problem lies in nonlinearities in the circuits.A signal which changes amplitude over a very large range will exercise these nonlinearities to the fullest extent. These nonlinearities will cause distortion products. In con-tinuously modulated systems they will cause “spectral regrowth” or wider modulation sidebands (a phenomenon related to intermodulation distortion). Another term which is sometimes used in this context is “spectral splatter.”However this is a term that is more correctly used in asso-ciation with the increase in the bandwidth of a signal caused by pulsing on and off.3.7 Spectral efficiency examples inpractical radiosThe following examples indicate spectral efficien-cies that are achieved in some practical radio systems.The TDMA version of the North American Digital Cellular (NADC) system, achieves a 48 Kbits-per-second data rate over a 30 kHz bandwidth or 1.6 bits per second per Hz. It is a π/4 DQPSK based system and transmits two bits per symbol. The theoretical efficiency would be two bits per second per Hz and in practice it is 1.6 bits per second per Hz.Another example is a microwave digital radio using 16QAM. This kind of signal is more susceptible to noise and distortion than something simpler such as QPSK. This type of signal is usually sent over a direct line-of-sight microwave link or over a wire where there is very little noise and interference. In this microwave-digital-radio example the bit rate is 140 Mbits per second over a very wide bandwidth of 52.5 MHz. The spectral efficiency is 2.7 bits per second per Hz. To implement this, it takes a very clear line-of-sight transmission path and a precise and optimized high-power transceiver.。

描述机房的英语作文

描述机房的英语作文英文回答:The data center, the heart of modern digital infrastructure, is a highly specialized facility designed to house and support the critical IT systems and data that power today's businesses and organizations. Thesefacilities are typically purpose-built to provide a secure, reliable, and energy-efficient environment for the operation and maintenance of servers, storage devices, networking equipment, and other essential components.One of the most notable characteristics of a data center is its high level of physical security. To protect against unauthorized access and potential threats, data centers employ multiple layers of security measures, including access control systems, video surveillance, intrusion detection, and perimeter fencing. Controlled access points, biometric identification, and specialized security personnel ensure that only authorized individualscan enter the facility.Another crucial aspect of data center design is the provision of a stable and reliable power supply. Redundant power systems, including backup generators anduninterruptible power supplies (UPS), are implemented to ensure that critical IT equipment remains operational evenin the event of a power outage. Precision cooling systems, such as air conditioning units and liquid cooling technologies, are also employed to maintain optimal operating temperatures and prevent equipment overheating.To meet the ever-increasing demand for data storage and processing, data centers utilize high-density server racks and blade servers that maximize space utilization andenergy efficiency. These racks typically accommodatemultiple servers within a single enclosure, allowing for efficient cable management and reduced cooling requirements.Furthermore, data centers implement advanced network connectivity and high-speed data transfer capabilities to facilitate seamless communication between servers andstorage devices. Fiber optic cables, high-bandwidth switches, and load balancers ensure rapid and reliable data transmission, enabling the efficient handling of large volumes of information.In addition to security, power, and network infrastructure, modern data centers also prioritize environmental sustainability. Energy-efficient designs, such as virtualization technologies and power-saving cooling systems, help reduce energy consumption and minimize the facility's carbon footprint. Sustainable practices, including recycling programs and responsible waste management, are also implemented to promote environmental responsibility.中文回答:机房。

j3160

j3160J3160: A Comprehensive OverviewIntroduction:The J3160 is an advanced processor that is part of the Intel® Celeron® family. It offers a range of powerful features and capabilities, making it a popular choice for various computing applications. In this document, we will delve into the architecture, specifications, performance, and use cases of the J3160 processor.1. Architecture:The J3160 processor is built on Intel's advanced 14nm manufacturing process, ensuring superior power efficiency and performance. Its architecture consists of four cores and four threads, allowing for efficient multitasking. The base clock speed of the processor is 1.60 GHz, with a maximum turbo frequency of 2.24 GHz. This ensures fast and responsive computing across various applications.2. Specifications:The J3160 processor offers a range of impressive specifications that contribute to its overall performance. It has a TDP (thermal design power) of 6 watts, which enables it to deliver excellent performance while maintaining low power consumption. The processor supports DDR3L and LPDDR3 memory with a maximum capacity of 8GB, providing ample memory bandwidth for smooth operation.3. Performance:The J3160 processor delivers reliable performance, making it suitable for a wide range of computing tasks. Its multi-core architecture enables efficient multitasking, ensuring smooth performance even during resource-intensive activities. The processor's integrated Intel® HD Graphics unit enhances visual experiences and enables the handling of graphics-intensive tasks with ease.When it comes to everyday computing tasks such as web browsing, word processing, and media consumption, theJ3160 processor performs admirably. It offers excellent responsiveness and seamless multitasking, allowing for smooth user experience.4. Use Cases:The J3160 processor finds applications in various computing domains, ranging from entry-level desktops and all-in-one PCs to compact industrial systems. Its low power consumption and robust performance make it an ideal choice for environments where both energy efficiency and reliability are crucial.The processor's graphics capabilities make it suitable for media streaming, casual gaming, and light video editing tasks. Its efficient architecture also supports smooth handling of multimedia playback, ensuring high-quality visual experiences.In industrial settings, the J3160 processor proves its worth by powering compact systems used in automation, surveillance, and embedded computing applications. Its low power consumption and compact size make it an excellent choice for space-constrained environments.5. Connectivity and Features:The J3160 processor supports a range of connectivity options, including USB 3.0, SATA 6 Gbps, and PCIe Gen2. These features enable quick data transfer and facilitate the integration of modern peripherals and storage devices.Moreover, the processor supports Intel® Virtualization Technology (Intel® VT-x), which enhances system security and allows for the efficient utilization of computing resources.Conclusion:In summary, the J3160 processor from Intel® Celeron® family offers a combination of powerful performance, low power consumption, and reliable multitasking. Its architecture, specifications, and features make it an excellent choice for various computing applications, including entry-level desktops, all-in-one PCs, compact industrial systems, and media streaming devices.With its advanced technology and efficient architecture, theJ3160 processor is a reliable solution that delivers exceptional performance and enhances user experiences. Whether it's for everyday computing tasks or demanding industrial applications, the J3160 processor is sure to meet the requirements of diverse computing needs.。

节点方案英文

节点方案英文Node SchemeIntroductionIn today's rapidly evolving technological landscape, the need for efficient and reliable networks is paramount. One crucial aspect of designing a network is determining the appropriate node scheme. A node scheme refers to the arrangement and configuration of network nodes, which are the essential building blocks of any network infrastructure. This article aims to explore the fundamental principles and considerations involved in devising a node scheme, focusing on key aspects such as scalability, redundancy, and network optimization.ScalabilityScalability is a vital factor when it comes to designing a node scheme. It refers to the network's ability to handle an increasing workload and expand in response to growing demands. To achieve scalability, a node scheme should incorporate modular architectures that allow for easy addition or removal of nodes without disrupting the entire network. Additionally, the use of virtualization technologies, such as cloud computing, can enhance scalability by enabling seamless resource allocation and management.RedundancyEnsuring network reliability is another crucial aspect of a well-designed node scheme. Redundancy, which involves duplicating network components, plays a significant role in achieving this goal. By incorporating redundantnodes, failures or disruptions in one part of the network can be mitigated as traffic is rerouted through alternative paths. Redundancy can be achieved at various levels, including hardware redundancy, where multiple physical devices are deployed, and software redundancy, which involves implementing failover mechanisms and backup systems.Network OptimizationOptimizing network performance is a key objective of any node scheme. This involves fine-tuning various parameters to ensure efficient data transmission and minimize latency. An effective node scheme should consider factors such as bandwidth allocation, routing protocols, and network traffic management. By applying load balancing techniques, network administrators can evenly distribute the workload across nodes, preventing bottlenecks and optimizing overall performance.Security ConsiderationsWhen designing a node scheme, security should be paramount. In an interconnected world, networks are vulnerable to various threats, such as unauthorized access, data breaches, and malware attacks. Implementing robust security measures, including authentication mechanisms, encryption protocols, and intrusion detection systems, is essential to safeguard network integrity. The node scheme should take into account these security considerations and provide a framework for secure data transmission and protection against potential threats.Case Study: Enterprise NetworkTo better understand the practical implementation of a node scheme, let's consider a case study of an enterprise network. In this scenario, the node scheme should cater to the organization's specific requirements, such as seamless communication, data exchange, and resource sharing.The node scheme for an enterprise network might consist of a centralized hub, where critical services and central data repositories are located. From this central hub, various branches or remote locations can be connected through distributed nodes, ensuring efficient communication and data synchronization. The deployment of redundant nodes at critical points within the network provides resilience and fault tolerance, minimizing downtime and ensuring business continuity.ConclusionIn conclusion, a well-designed node scheme is fundamental to building a robust and efficient network infrastructure. By considering scalability, redundancy, network optimization, and security, network architects can develop a node scheme that meets the specific requirements of any organization or application. Understanding the intricacies of node schemes is crucial in today's interconnected world, where networks are the backbone of modern communication and information exchange.。

英语作文-探索集成电路设计中的新技术与应用前景

英语作文-探索集成电路设计中的新技术与应用前景As integrated circuit (IC) design continues to evolve, new technologies are constantly emerging, offering exciting possibilities for innovation and advancement. In this essay, we will explore some of the latest trends and applications in IC design, highlighting their potential impact on various industries and the future landscape of technology.One of the most significant advancements in IC design is the development of 3D integration technology. Unlike traditional 2D designs, which place all components on a single plane, 3D integration allows for stacking multiple layers of integrated circuits, thereby increasing functionality and performance while reducing footprint. This technology enables the creation of smaller, more power-efficient devices, making it ideal for applications in mobile devices, wearables, and IoT devices.Another area of innovation in IC design is the use of advanced materials such as graphene and carbon nanotubes. These materials offer unique electrical and mechanical properties that can greatly enhance the performance of integrated circuits. For example, graphene-based transistors have demonstrated higher electron mobility and faster switching speeds compared to traditional silicon transistors, paving the way for next-generation computing devices with unprecedented speed and efficiency.In addition to new materials, machine learning and artificial intelligence (AI) are playing an increasingly important role in IC design. By leveraging AI algorithms, designers can automate the process of optimizing chip architectures, reducing time-to-market and improving overall performance. AI-driven design tools can analyze vast amounts of data to identify the most efficient circuit layouts and power management strategies, leading to more reliable and cost-effective ICs.Moreover, the integration of photonics into IC design is opening up new possibilities for high-speed data communication and processing. Photonic integrated circuits (PICs)use light instead of electricity to transmit and manipulate data, offering significant advantages in terms of bandwidth and latency. PICs are already being used in data centers and telecommunications networks to improve the performance and scalability of optical communication systems.Furthermore, the emergence of quantum computing represents a paradigm shift in IC design, with the potential to solve complex problems that are currently intractable for classical computers. Quantum ICs, which exploit the principles of quantum mechanics to perform calculations, have the potential to revolutionize fields such as cryptography, materials science, and drug discovery. While quantum computing is still in its infancy, ongoing research and development efforts are rapidly advancing the state-of-the-art, bringing us closer to realizing the full potential of this transformative technology.In conclusion, the field of IC design is experiencing rapid innovation driven by advancements in materials science, machine learning, photonics, and quantum computing. These technologies hold the promise of delivering faster, more efficient, and more powerful integrated circuits, with profound implications for a wide range of industries and applications. As we continue to push the boundaries of what is possible, the future of IC design looks brighter than ever before.。

5g的优点和缺点英文作文

5g的优点和缺点英文作文The Pros and Cons of 5G TechnologyThe rapid advancements in technology have revolutionized the way we live our lives. One of the latest and most significant developments in the world of telecommunications is the emergence of 5G technology. 5G, or the fifth generation of wireless communication systems, promises to deliver unprecedented speeds, lower latency, and a more efficient network infrastructure. While the potential benefits of 5G are undeniable, it is crucial to also consider the potential drawbacks and challenges associated with its implementation.One of the primary advantages of 5G is its significantly faster data transmission speeds. Compared to its predecessors, 5G offers download and upload speeds that are up to 100 times faster. This enhanced speed can greatly improve the user experience in various applications, such as streaming high-definition videos, playing online games, and seamless file transfers. The increased bandwidth provided by 5G also allows for more devices to be connected simultaneously without compromising performance.Another key benefit of 5G is its reduced latency. Latency refers to the time it takes for data to be transmitted and received. With 5G, latency can be reduced to as little as a few milliseconds, which is a vast improvement over the higher latency experienced in previous generations of wireless technology. This low latency is particularly important for applications that require real-time responsiveness, such as autonomous vehicles, remote surgery, and industrial automation.Furthermore 5G's improved network efficiency can lead to significant energy savings. The advanced architecture of 5G networks allows for more efficient use of spectrum and resources, reducing the overall energy consumption of the network infrastructure. This improved energy efficiency can have positive environmental implications, as it contributes to a more sustainable and eco-friendly telecommunications landscape.However, the implementation of 5G technology is not without its challenges and potential drawbacks. One of the primary concerns is the potential impact on human health and the environment. There are ongoing debates and studies regarding the potential health risks associated with the higher frequency electromagnetic radiation used in 5G networks. While the scientific consensus on the long-term effects is still inconclusive, the perceived risks have led to public apprehension and resistance in some regions.Additionally the deployment of 5G infrastructure can be a complex and costly undertaking. The installation of new cell towers and the upgrading of existing infrastructure require significant financial investment from telecommunication companies and governments. This can lead to higher costs for consumers and potentially widen the digital divide in regions where the investment in 5G infrastructure may be limited.Another potential drawback of 5G is the increased cybersecurity risks. The greater connectivity and data transmission capabilities of 5G networks can also make them more vulnerable to cyber threats such as hacking, data breaches, and network disruptions. Ensuring the security and privacy of 5G networks is crucial to mitigate these risks and maintain the trust of users.Moreover the transition to 5G may also have unintended consequences on certain industries and workforce. The increased automation and efficiency brought by 5G could lead to job displacements in sectors such as transportation and logistics. Policymakers and stakeholders will need to address these potential societal impacts and develop strategies to support affected communities and workers.In conclusion the potential benefits of 5G technology are indeedsignificant offering faster speeds lower latency and improved energy efficiency However the implementation of 5G also presents challenges and potential drawbacks that need to be carefully considered and addressed These include concerns about health and environmental impacts the high costs of deployment cybersecurity risks and the potential disruption to certain industries and workforce As we embrace the 5G revolution it is crucial that we develop a balanced and well-rounded understanding of its pros and cons to ensure its sustainable and responsible deployment for the betterment of society。

华为固定转换解决方案——PSTN更新简易解决方案说明书