AS13985中文资料

美国ASTM A580 - 98不锈钢丝标准(中文翻译稿,仅供学习参考)

ASTM A580/580M-98Standard Specification for Stainless Steel Wire不锈钢丝的标准规范1. Scope 范围1.1 This specification covers stainless steel wire, except the free-machining types. It includes round, square, octagon, hexagon, and shape wire in coils only for the more commonly used types of stainless steels for general corrosion resistance and high-temperature service. For bars in straightened and cut lengths, see Specifications A276 or A479/A479M.本规范包括除了自由加工类型以外的不锈钢丝。

包括只为较常用的一般耐腐蚀和用于高温类型的(截面为)圆形、方形、八角形、六角形等钢丝型材,仅限线圈。

对于在拉直和定尺长度的棒材,见规范A276或A479/A479M。

NOTE 1 ---- For free-machining stainless wire, designed especially for optimum machinability, see Specification A581/A581M.注1:对于自由加工的不锈钢丝,尤其为优化可加工性设计的不锈钢丝,见规范A581/A581M。

1.2 The value stated in either inch-pound units or SI(metric) units are to be regarded separately as standards; within the text and tables, the SI units are shown in [brackets]. The values stated in each system are not exact equivalents; therefore, each system must be used independently of the other. Combining values from the two systems may result in nonconformance with the specification.无论是英制单位还是公制单位的值均被视作标准;在正文和表格内,公制单位显示在括号[ ]内。

MAX13085EASA+中文资料

General DescriptionThe MAX13080E–MAX13089E +5.0V, ±15kV ESD-protect-ed, RS-485/RS-422 transceivers feature one driver and one receiver. These devices include fail-safe circuitry,guaranteeing a logic-high receiver output when receiver inputs are open or shorted. The receiver outputs a logic-high if all transmitters on a terminated bus are disabled (high impedance). The MAX13080E–MAX13089E include a hot-swap capability to eliminate false transitions on the bus during power-up or hot insertion.The MAX13080E/MAX13081E/MAX13082E feature reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 250kbps. The MAX13083E/MAX13084E/MAX13085E also feature slew-rate-limited drivers but allow transmit speeds up to 500kbps. The MAX13086E/MAX13087E/MAX13088E driver slew rates are not limited, making transmit speeds up to 16Mbps possible. The MAX13089E slew rate is pin selectable for 250kbps,500kbps, and 16Mbps.The MAX13082E/MAX13085E/MAX13088E are intended for half-duplex communications, and the MAX13080E/MAX13081E/MAX13083E/MAX13084E/MAX13086E/MAX13087E are intended for full-duplex communica-tions. The MAX13089E is selectable for half-duplex or full-duplex operation. It also features independently programmable receiver and transmitter output phase through separate pins.The MAX13080E–MAX13089E transceivers draw 1.2mA of supply current when unloaded or when fully loaded with the drivers disabled. All devices have a 1/8-unit load receiver input impedance, allowing up to 256transceivers on the bus.The MAX13080E/MAX13083E/MAX13086E/MAX13089E are available in 14-pin PDIP and 14-pin SO packages.The MAX13081E/MAX13082E/MAX13084E/MAX13085E/MAX13087E/MAX13088E are available in 8-pin PDIP and 8-pin SO packages. The devices operate over the com-mercial, extended, and automotive temperature ranges.ApplicationsUtility Meters Lighting Systems Industrial Control Telecom Security Systems Instrumentation ProfibusFeatures♦+5.0V Operation♦Extended ESD Protection for RS-485/RS-422 I/O Pins±15kV Human Body Model ♦True Fail-Safe Receiver While Maintaining EIA/TIA-485 Compatibility ♦Hot-Swap Input Structures on DE and RE ♦Enhanced Slew-Rate Limiting Facilitates Error-Free Data Transmission(MAX13080E–MAX13085E/MAX13089E)♦Low-Current Shutdown Mode (Except MAX13081E/MAX13084E/MAX13087E)♦Pin-Selectable Full-/Half-Duplex Operation (MAX13089E)♦Phase Controls to Correct for Twisted-Pair Reversal (MAX13089E)♦Allow Up to 256 Transceivers on the Bus ♦Available in Industry-Standard 8-Pin SO PackageMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers________________________________________________________________Maxim Integrated Products 1Ordering Information19-3590; Rev 1; 4/05For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Selector Guide, Pin Configurations, and Typical Operating Circuits appear at end of data sheet.Ordering Information continued at end of data sheet.M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSDC ELECTRICAL CHARACTERISTICS(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.) (Note 1)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All Voltages Referenced to GND)Supply Voltage (V CC ).............................................................+6V Control Input Voltage (RE , DE, SLR,H/F , TXP, RXP)......................................................-0.3V to +6V Driver Input Voltage (DI)...........................................-0.3V to +6V Driver Output Voltage (Z, Y, A, B).............................-8V to +13V Receiver Input Voltage (A, B)....................................-8V to +13V Receiver Input VoltageFull Duplex (A, B)..................................................-8V to +13V Receiver Output Voltage (RO)....................-0.3V to (V CC + 0.3V)Driver Output Current.....................................................±250mAContinuous Power Dissipation (T A = +70°C)8-Pin SO (derate 5.88mW/°C above +70°C).................471mW 8-Pin Plastic DIP (derate 9.09mW/°C above +70°C).....727mW 14-Pin SO (derate 8.33mW/°C above +70°C)...............667mW 14-Pin Plastic DIP (derate 10.0mW/°C above +70°C)...800mW Operating Temperature RangesMAX1308_EC_ _.................................................0°C to +75°C MAX1308_EE_ _..............................................-40°C to +85°C MAX1308_EA_ _............................................-40°C to +125°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°CMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________3DC ELECTRICAL CHARACTERISTICS (continued)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.) (Note 1)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 4_______________________________________________________________________________________DRIVER SWITCHING CHARACTERISTICSMAX13080E/MAX13081E/MAX13082E/MAX13089E WITH SRL = UNCONNECTED (250kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)RECEIVER SWITCHING CHARACTERISTICSMAX13080E/MAX13081E/MAX13082E/MAX13089E WITH SRL = UNCONNECTED (250kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________5DRIVER SWITCHING CHARACTERISTICSMAX13083E/MAX13084E/MAX13085E/MAX13089E WITH SRL = V CC (500kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)RECEIVER SWITCHING CHARACTERISTICSMAX13083E/MAX13084E/MAX13085E/MAX13089E WITH SRL = V CC (500kbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 6_______________________________________________________________________________________DRIVER SWITCHING CHARACTERISTICSMAX13086E/MAX13087E/MAX13088E/MAX13089E WITH SRL = GND (16Mbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)RECEIVER SWITCHING CHARACTERISTICSMAX13086E/MAX13087E/MAX13088E/MAX13089E WITH SRL = GND (16Mbps)(V CC = +5.0V ±10%, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +5.0V and T A = +25°C.)Note 2:∆V OD and ∆V OC are the changes in V OD and V OC , respectively, when the DI input changes state.Note 3:The short-circuit output current applies to peak current just prior to foldback current limiting. The short-circuit foldback outputcurrent applies during current limiting to allow a recovery from bus contention.MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________70.800.901.501.101.001.201.301.401.60-40-10520-253550958011065125SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (m A )0201040305060021345OUTPUT CURRENTvs. RECEIVER OUTPUT-HIGH VOLTAGEM A X 13080E -89E t o c 02OUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )20104030605070021345OUTPUT CURRENTvs. RECEIVER OUTPUT-LOW VOLTAGEM A X 13080E -89E t o c 03OUTPUT LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )4.04.44.24.84.65.25.05.4RECEIVER OUTPUT-HIGH VOLTAGEvs. TEMPERATURETEMPERATURE (°C)O U T P U T H I G H V O L T A G E (V )-40-10520-2535509580110651250.10.70.30.20.40.50.60.8RECEIVER OUTPUT-LOW VOLTAGEvs. TEMPERATURETEMPERATURE (°C)O U T P U T L O W V O L T A G E (V )-40-10520-25355095801106512502040608010012014016012345DRIVER DIFFERENTIAL OUTPUT CURRENT vs. DIFFERENTIAL OUTPUT VOLTAGEDIFFERENTIAL OUTPUT VOLTAGE (V)D I F FE R E N T I A L O U T P U T C U R R E N T (m A )2.02.82.43.63.24.44.04.8DRIVER DIFFERENTIAL OUTPUT VOLTAGE vs. TEMPERATURED I F FE R E N T I A L O U T P U T V O L T A G E (V )-40-10520-253550958011065125TEMPERATURE (°C)40201008060120140180160200-7-5-4-6-3-2-1012354OUTPUT CURRENT vs. TRANSMITTEROUTPUT-HIGH VOLTAGEOUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )60402080100120140160180200042681012OUTPUT CURRENT vs. TRANSMITTEROUTPUT-LOW VOLTAGEOUTPUT-LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )Typical Operating Characteristics(V CC = +5.0V, T A = +25°C, unless otherwise noted.)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 8_______________________________________________________________________________________21543679810SHUTDOWN CURRENT vs. TEMPERATUREM A X 13080E -89E t o c 10S H U T D O W N C U R R E N T (µA )-40-10520-253550958011065125TEMPERATURE (°C)600800700100090011001200DRIVER PROPAGATION DELAY vs. TEMPERATURE (250kbps)D R I VE R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)300400350500450550600DRIVER PROPAGATION DELAY vs. TEMPERATURE (500kbps)D R I VE R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)1070302040506080DRIVER PROPAGATION DELAY vs. TEMPERATURE (16Mbps)D R I VE R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)40201008060120140160180RECEIVER PROPAGATION DELAYvs. TEMPERATURE (250kpbs AND 500kbps)R E C E I V E R P R O P A G A T I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)40201008060120140160180RECEIVER PROPAGATION DELAYvs. TEMPERATURE (16Mbps)R EC E I V E R P R O P A G AT I O N D E L A Y (n s )-40-10520-253550958011065125TEMPERATURE (°C)2µs/div DRIVER PROPAGATION DELAY (250kbps)DI 2V/divV Y - V Z 5V/divR L = 100Ω200ns/divRECEIVER PROPAGATION DELAY(250kbps AND 500kbps)V A - V B 5V/divRO 2V/divTypical Operating Characteristics (continued)(V CC = +5.0V, T A = +25°C, unless otherwise noted.)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers_______________________________________________________________________________________9Test Circuits and Waveforms400ns/divDRIVER PROPAGATION DELAY (500kbps)DI 2V/divR L = 100ΩV Y - V Z 5V/div10ns/div DRIVER PROPAGATION DELAY (16Mbps)DI 2V/divR L = 100ΩV Y 2V/divV Z 2V/div40ns/divRECEIVER PROPAGATION DELAY (16Mbps)V B 2V/divR L = 100ΩRO 2V/divV A 2V/divTypical Operating Characteristics (continued)(V CC = +5.0V, T A = +25°C, unless otherwise noted.)Figure 2. Driver Timing Test CircuitM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 10______________________________________________________________________________________Test Circuits and Waveforms (continued)Figure 4. Driver Enable and Disable Times (t DHZ , t DZH , t DZH(SHDN))DZL DLZ DLZ(SHDN)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversTest Circuits and Waveforms (continued)Figure 6. Receiver Propagation Delay Test CircuitM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversMAX13080E/MAX13083E/MAX13086EMAX13081E/MAX13084E/MAX13086E/MAX13087EFunction TablesM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers MAX13082E/MAX13085E/MAX13088EFunction Tables (continued)MAX13089EDetailed Description The MAX13080E–MAX13089E high-speed transceivers for RS-485/RS-422 communication contain one driver and one receiver. These devices feature fail-safe circuit-ry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted, or when they are connected to a terminated transmission line with all dri-vers disabled (see the Fail-Safe section). The MAX13080E/MAX13082E/MAX13083E/MAX13085E/ MAX13086E/MAX13088E/MAX13089E also feature a hot-swap capability allowing line insertion without erroneous data transfer (see the Hot Swap Capability section). The MAX13080E/MAX13081E/MAX13082E feature reduced slew-rate drivers that minimize EMI and reduce reflec-tions caused by improperly terminated cables, allowing error-free data transmission up to 250kbps. The MAX13083E/MAX13084E/MAX13085E also offer slew-rate limits allowing transmit speeds up to 500kbps. The MAX13086E/MAX13087E/MAX13088Es’ driver slew rates are not limited, making transmit speeds up to 16Mbps possible. The MAX13089E’s slew rate is selectable between 250kbps, 500kbps, and 16Mbps by driving a selector pin with a three-state driver.The MAX13082E/MAX13085E/MAX13088E are half-duplex transceivers, while the MAX13080E/MAX13081E/ MAX13083E/MAX13084E/MAX13086E/MAX13087E are full-duplex transceivers. The MAX13089E is selectable between half- and full-duplex communication by driving a selector pin (H/F) high or low, respectively.All devices operate from a single +5.0V supply. Drivers are output short-circuit current limited. Thermal-shutdown circuitry protects drivers against excessive power dissi-pation. When activated, the thermal-shutdown circuitry places the driver outputs into a high-impedance state.Receiver Input Filtering The receivers of the MAX13080E–MAX13085E, and the MAX13089E when operating in 250kbps or 500kbps mode, incorporate input filtering in addition to input hysteresis. This filtering enhances noise immunity with differential signals that have very slow rise and fall times. Receiver propagation delay increases by 25% due to this filtering.Fail-Safe The MAX13080E family guarantees a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver input threshold between -50mV and -200mV. If the differential receiver input voltage (A - B) is greater than or equal to -50mV, RO is logic-high. If (A - B) is less than or equal to -200mV, RO is logic-low. In the case of a terminated bus with all transmitters disabled, the receiv-er’s differential input voltage is pulled to 0V by the termi-nation. With the receiver thresholds of the MAX13080E family, this results in a logic-high with a 50mV minimumnoise margin. Unlike previous fail-safe devices, the-50mV to -200mV threshold complies with the ±200mVEIA/TIA-485 standard.Hot-Swap Capability (Except MAX13081E/MAX13084E/MAX13087E)Hot-Swap InputsWhen circuit boards are inserted into a hot or powered backplane, differential disturbances to the data buscan lead to data errors. Upon initial circuit board inser-tion, the data communication processor undergoes itsown power-up sequence. During this period, the processor’s logic-output drivers are high impedanceand are unable to drive the DE and RE inputs of these devices to a defined logic level. Leakage currents up to±10µA from the high-impedance state of the proces-sor’s logic drivers could cause standard CMOS enableinputs of a transceiver to drift to an incorrect logic level. Additionally, parasitic circuit board capacitance couldcause coupling of V CC or GND to the enable inputs. Without the hot-swap capability, these factors could improperly enable the transceiver’s driver or receiver.When V CC rises, an internal pulldown circuit holds DElow and RE high. After the initial power-up sequence,the pulldown circuit becomes transparent, resetting thehot-swap tolerable input.Hot-Swap Input CircuitryThe enable inputs feature hot-swap capability. At theinput there are two NMOS devices, M1 and M2 (Figure 9). When V CC ramps from zero, an internal 7µstimer turns on M2 and sets the SR latch, which alsoturns on M1. Transistors M2, a 1.5mA current sink, andM1, a 500µA current sink, pull DE to GND through a5kΩresistor. M2 is designed to pull DE to the disabledstate against an external parasitic capacitance up to100pF that can drive DE high. After 7µs, the timer deactivates M2 while M1 remains on, holding DE low against three-state leakages that can drive DE high. M1 remains on until an external source overcomes the required input current. At this time, the SR latch resetsand M1 turns off. When M1 turns off, DE reverts to a standard, high-impedance CMOS input. Whenever V CCdrops below 1V, the hot-swap input is reset.For RE there is a complementary circuit employing two PMOS devices pulling RE to V CC. MAX13080E–MAX13089E+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversM A X 13080E –M A X 13089EMAX13089E ProgrammingThe MAX13089E has several programmable operating modes. Transmitter rise and fall times are programma-ble, resulting in maximum data rates of 250kbps,500kbps, and 16Mbps. To select the desired data rate,drive SRL to one of three possible states by using a three-state driver: V CC , GND, or unconnected. F or 250kbps operation, set the three-state device in high-impedance mode or leave SRL unconnected. F or 500kbps operation, drive SRL high or connect it to V CC .F or 16Mbps operation, drive SRL low or connect it to GND. SRL can be changed during operation without interrupting data communications.Occasionally, twisted-pair lines are connected backward from normal orientation. The MAX13089E has two pins that invert the phase of the driver and the receiver to cor-rect this problem. F or normal operation, drive TXP and RXP low, connect them to ground, or leave them uncon-nected (internal pulldown). To invert the driver phase,drive TXP high or connect it to V CC . To invert the receiver phase, drive RXP high or connect it to V CC . Note that the receiver threshold is positive when RXP is high.The MAX13089E can operate in full- or half-duplex mode. Drive H/F low, leave it unconnected (internal pulldown), or connect it to GND for full-duplex opera-tion. Drive H/F high for half-duplex operation. In full-duplex mode, the pin configuration of the driver and receiver is the same as that of a MAX13080E. In half-duplex mode, the receiver inputs are internally connect-ed to the driver outputs through a resistor-divider. This effectively changes the function of the device’s outputs.Y becomes the noninverting driver output and receiver input, Z becomes the inverting driver output and receiver input. In half-duplex mode, A and B are still connected to ground through an internal resistor-divider but they are not internally connected to the receiver.±15kV ESD ProtectionAs with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electro-static discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX13080E family of devices have extra protection against static electricity. Maxim’s engineers have devel-oped state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD struc-tures withstand high ESD in all states: normal operation,shutdown, and powered down. After an ESD event, the MAX13080E–MAX13089E keep working without latchup or damage.ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX13080E–MAX13089E are characterized for protec-tion to the following limits:•±15kV using the Human Body Model•±6kV using the Contact Discharge method specified in IEC 61000-4-2ESD Test ConditionsESD performance depends on a variety of conditions.Contact Maxim for a reliability report that documents test setup, test methodology, and test results.Human Body ModelFigure 10a shows the Human Body Model, and Figure 10b shows the current waveform it generates when dis-charged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest,which is then discharged into the test device through a 1.5k Ωresistor.IEC 61000-4-2The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX13080E family of devices helps you design equip-ment to meet IEC 61000-4-2, without the need for addi-tional ESD-protection components.+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversThe major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD with-stand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 10c shows the IEC 61000-4-2 model, and Figure 10d shows the current waveform for IEC 61000-4-2 ESD Contact Discharge test.Machine Model The machine model for ESD tests all pins using a 200pF storage capacitor and zero discharge resis-tance. The objective is to emulate the stress caused when I/O pins are contacted by handling equipment during test and assembly. Of course, all pins require this protection, not just RS-485 inputs and outputs.Applications Information256 Transceivers on the BusThe standard RS-485 receiver input impedance is 12kΩ(1-unit load), and the standard driver can drive up to 32-unit loads. The MAX13080E family of transceivers has a1/8-unit load receiver input impedance (96kΩ), allowingup to 256 transceivers to be connected in parallel on one communication line. Any combination of these devices,as well as other RS-485 transceivers with a total of 32-unit loads or fewer, can be connected to the line.Reduced EMI and ReflectionsThe MAX13080E/MAX13081E/MAX13082E feature reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to250kbps. The MAX13083E/MAX13084E/MAX13085Eoffer higher driver output slew-rate limits, allowing transmit speeds up to 500kbps. The MAX13089E withSRL = V CC or unconnected are slew-rate limited. WithSRL unconnected, the MAX13089E error-free data transmission is up to 250kbps. With SRL connected toV CC,the data transmit speeds up to 500kbps. MAX13080E–MAX13089E+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversM A X 13080E –M A X 13089ELow-Power Shutdown Mode (Except MAX13081E/MAX13084E/MAX13087E)Low-power shutdown mode is initiated by bringing both RE high and DE low. In shutdown, the devices typically draw only 2.8µA of supply current.RE and DE can be driven simultaneously; the devices are guaranteed not to enter shutdown if RE is high and DE is low for less than 50ns. If the inputs are in this state for at least 700ns, the devices are guaranteed to enter shutdown.Enable times t ZH and t ZL (see the Switching Characteristics section) assume the devices were not in a low-power shutdown state. Enable times t ZH(SHDN)and t ZL(SHDN)assume the devices were in shutdown state. It takes drivers and receivers longer to become enabled from low-power shutdown mode (t ZH(SHDN), t ZL(SHDN))than from driver/receiver-disable mode (t ZH , t ZL ).Driver Output ProtectionTwo mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention.The first, a foldback current limit on the output stage,provides immediate protection against short circuits over the whole common-mode voltage range (see the Typical Operating Characteristics ). The second, a thermal-shut-down circuit, forces the driver outputs into a high-imped-ance state if the die temperature exceeds +175°C (typ).Line LengthThe RS-485/RS-422 standard covers line lengths up to 4000ft. F or line lengths greater than 4000ft, use the repeater application shown in Figure 11.Typical ApplicationsThe MAX13082E/MAX13085E/MAX13088E/MAX13089E transceivers are designed for bidirectional data commu-nications on multipoint bus transmission lines. F igures 12 and 13 show typical network applications circuits. To minimize reflections, terminate the line at both ends in its characteristic impedance, and keep stub lengths off the main line as short as possible. The slew-rate-lim-ited MAX13082E/MAX13085E and the two modes of the MAX13089E are more tolerant of imperfect termination.Chip InformationTRANSISTOR COUNT: 1228PROCESS: BiCMOS+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversFigure 11. Line Repeater for MAX13080E/MAX13081E/MAX13083E/MAX13084E/MAX13086E/MAX13087E/MAX13089E in Full-Duplex Mode+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversMAX13080E–MAX13089EM A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 TransceiversPin Configurations and Typical Operating CircuitsMAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers______________________________________________________________________________________21Pin Configurations and Typical Operating Circuits (continued)M A X 13080E –M A X 13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers 22______________________________________________________________________________________Ordering Information (continued)MAX13080E–MAX13089E+5.0V , ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers______________________________________________________________________________________23Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

STY139N65M5;中文规格书,Datasheet资料

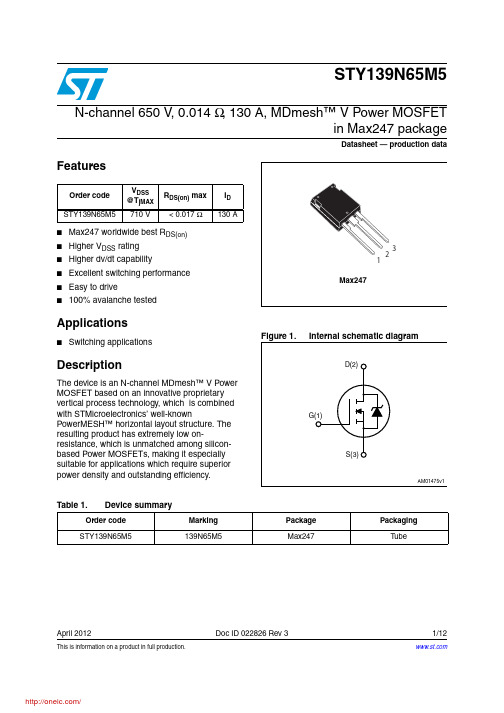

This is information on a product in full production.April 2012Doc ID 022826 Rev 31/12STY139N65M5N-channel 650 V , 0.014 Ω, 130 A, MDmesh™ V Power MOSFETin Max247 packageDatasheet — production dataFeatures■Max247 worldwide best R DS(on)■Higher V DSS rating ■Higher dv/dt capability■Excellent switching performance ■Easy to drive■100% avalanche testedApplications■Switching applicationsDescriptionThe device is an N-channel MDmesh™ V Power MOSFET based on an innovative proprietary vertical process technology, which is combined with STMicroelectronics’ well-knownPowerMESH™ horizontal layout structure. The resulting product has extremely low on-resistance, which is unmatched among silicon-based Power MOSFETs, making it especially suitable for applications which require superior power density and outstanding efficiency.Order code V DSS @T jMAX R DS(on) max I D STY139N65M5710 V< 0.017 Ω130 ATable 1.Device summaryOrder code Marking Package Packaging STY139N65M5139N65M5Max247TubeContents STY139N65M5Contents1Electrical ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42.1Electrical characteristics (curves) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 3Test circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 4Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 5Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122/12Doc ID 022826 Rev 3STY139N65M5Electrical ratingsDoc ID 022826 Rev 33/121 Electrical ratingsTable 2.Absolute maximum ratingsSymbol ParameterValue Unit V GS Gate- source voltage± 25V I D Drain current (continuous) at T C = 25 °C 130A I D Drain current (continuous) at T C = 100 °C 78A I DM (1)1.Pulse width limited by safe operating area.Drain current (pulsed)520A P TOT Total dissipation at T C = 25 °C625W I AR Max current during repetitive or single pulse avalanche(pulse width limited by T JMAX )15A E AS Single pulse avalanche energy(starting T j = 25°C, I D = I AR , V DD = 50V)2000mJ dv/dt (2)2.I SD ≤ 130 A, di/dt = 400 A/µs, V DD = 400 V, peak V DS < V (BR)DSS.Peak diode recovery voltage slope 15V/ns T stg Storage temperature- 55 to 150°C T jMax. operating junction temperature150°CTable 3.Thermal dataSymbolParameterValue Unit R thj-case Thermal resistance junction-case max 0.2°C/W R thj-amb Thermal resistance junction-ambient max 30°C/W T lMaximum lead temperature for soldering purpose300°CElectrical characteristics STY139N65M54/12Doc ID 022826 Rev 32 Electrical characteristics(T C = 25 °C unless otherwise specified)Table 4.On /off statesSymbol Parameter Test conditionsMin.Typ.Max.Unit V (BR)DSS Drain-sourcebreakdown voltageI D = 1 mA, V GS = 0650V I DSS Zero gate voltage drain current (V GS = 0)V DS = 650 VV DS = 650 V , T C =125 °C 10100µA µA I GSS Gate-body leakage current (V DS = 0)V GS = ± 25 V±100nA V GS(th)Gate threshold voltage V DS = V GS , I D = 250 µA 345V R DS(on)Static drain-source onresistanceV GS = 10 V , I D = 65 A0.0140.017ΩTable 5.DynamicSymbol Parameter Test conditionsMin.Typ.Max.Unit C iss C oss C rss Input capacitance Output capacitance Reverse transfer capacitance V DS = 100 V , f = 1 MHz, V GS = 0-156003659-pF pF pFC o(tr)(1)1.C o(tr) is a constant capacitance value that gives the same charging time as C oss while V DS is rising from 0to 80% V DSS .Equivalentcapacitance time relatedV GS = 0, V DS = 0 to 520 V-1559-pFC o(er)(2)2.C o(er) is a constant capacitance value that gives the same stored energy as C oss while V DS is rising from 0to 80% V DSS .Equivalentcapacitance energy related V GS = 0, V DS = 0 to 520 V -360-pFR GIntrinsic gate resistancef = 1 MHz open drain - 1.2-ΩQg Q gs Q gdT otal gate charge Gate-source charge Gate-drain chargeV DD = 520 V , I D = 65 A,V GS = 10 V (see Figure 15)-36388164-nC nC nCSTY139N65M5Electrical characteristicsDoc ID 022826 Rev 35/12Table 6.Switching timesSymbol ParameterTest conditions Min.Typ.Max.Unitt d(v)t r(v)t f(i)t c(off)Voltage delay time Voltage rise time Current fall time Crossing timeV DD = 400 V , I D = 80 A, R G = 4.7 Ω, V GS = 10 V (see Figure 16)(see Figure 19)-295563784-ns ns ns nsTable 7.Source drain diodeSymbol ParameterTest conditionsMin.Typ.Max.Unit I SD I SDM (1)1.Pulse width limited by safe operating area.Source-drain currentSource-drain current (pulsed)-130520A A V SD (2)2.Pulsed: pulse duration = 300 µs, duty cycle 1.5%Forward on voltage I SD = 130 A, V GS = 0- 1.5V t rr Q rr I RRM Reverse recovery time Reverse recovery charge Reverse recovery current I SD = 130 A, di/dt = 100 A/µs V DD = 100 V (see Figure 16)-5701553ns µC A t rr Q rr I RRMReverse recovery time Reverse recovery charge Reverse recovery currentI SD = 130 A, di/dt = 100 A/µs V DD = 100 V , T j = 150 °C (see Figure 16)-7202468ns µC AElectrical characteristics STY139N65M5 2.1 Electrical characteristics (curves)6/12Doc ID 022826 Rev 3STY139N65M5Electrical characteristicsDoc ID 022826 Rev 37/12Figure 10.Normalized gate threshold voltageFigure 11.Normalized on resistance vsFigure 12.Output capacitance stored energyFigure 13.Switching losses vs gate resistance(1)1.Eon including reverse recovery of a SiC diode.Test circuits STY139N65M58/12Doc ID 022826 Rev 33 Test circuitsFigure 14.Switching times test circuit forFigure 15.Gate charge test circuitFigure 16.Test circuit for inductive loadFigure 17.Unclamped inductive load testFigure 18.Unclamped inductive waveformFigure 19.Switching time waveformSTY139N65M5Package mechanical data 4 Package mechanical dataIn order to meet environmental requirements, ST offers these devices in different grades ofECOP ACK® packages, depending on their level of environmental compliance. ECOPACK®specifications, grade definitions and product status are available at: .ECOP ACK® is an ST trademark.Table 8.Max247 mechanical datammDim.Min.Typ.Max.A 4.70 5.30A1 2.20 2.60b 1.00 1.40b1 2.00 2.40b2 3.00 3.40c0.400.80D19.7020.30e 5.35 5.55E15.3015.90L14.2015.20L1 3.70 4.30Doc ID 022826 Rev 39/12Package mechanical data STY139N65M510/12Doc ID 022826 Rev 3分销商库存信息: STMSTY139N65M5。

L9953XP;L9953XPTR;L9953TR;L9953;中文规格书,Datasheet资料

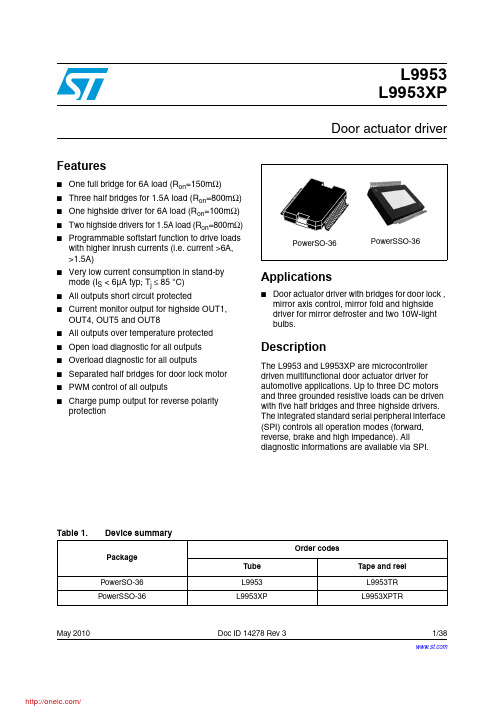

May 2010Doc ID 14278 Rev 31/38L9953L9953XPDoor actuator driverFeatures■One full bridge for 6A load (R on =150m Ω)■Three half bridges for 1.5A load (R on =800m Ω)■One highside driver for 6A load (R on =100m Ω)■Two highside drivers for 1.5A load (R on =800m Ω)■Programmable softstart function to drive loads with higher inrush currents (i.e. current >6A, >1.5A)■Very low current consumption in stand-by mode (I S < 6µA typ; T j ≤ 85 °C)■All outputs short circuit protected■Current monitor output for highside OUT1, OUT4, OUT5 and OUT8■All outputs over temperature protected ■Open load diagnostic for all outputs ■Overload diagnostic for all outputs ■Separated half bridges for door lock motor ■PWM control of all outputs■Charge pump output for reverse polarity protectionApplications■Door actuator driver with bridges for door lock , mirror axis control, mirror fold and highside driver for mirror defroster and two 10W-light bulbs.DescriptionThe L9953 and L9953XP are microcontroller driven multifunctional door actuator driver for automotive applications. Up to three DC motors and three grounded resistive loads can be driven with five half bridges and three highside drivers. The integrated standard serial peripheral interface (SPI) controls all operation modes (forward, reverse, brake and high impedance). All diagnostic informations are available via SPI.PowerSSO-36Table 1.Device summaryPackageOrder codesTubeTape and reel PowerSO-36L9953L9953TR PowerSSO-36L9953XPL9953XPTRContents L9953 / L9953XPContents1Block diagram and pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.1Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.2ESD protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.3Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.4Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102.5SPI - electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.1Dual power supply: VS and VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.2Standby mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.3Inductive loads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.4Diagnostic functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.5Overvoltage and under voltage detection . . . . . . . . . . . . . . . . . . . . . . . . . 203.6Charge pump . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203.7Temperature warning and thermal shutdown . . . . . . . . . . . . . . . . . . . . . . 203.8Open load detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203.9Over load detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203.10Current monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.11PWM inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.12Cross-current protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.13Programmable softstart function to drive loads with higher inrush current 214Functional description of the SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234.1Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234.2Chip Select Not (CSN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234.3Serial Data In (DI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234.4Serial Data Out (DO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.5Serial clock (CLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.6Input data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.7Status register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 2/38 Doc ID 14278 Rev 3L9953 / L9953XP Contents4.8Scan mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.9Test mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254.10SPI - input data and Status registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265Packages thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306Package and packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.1ECOP ACK® packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.2PowerSO-36™ package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.3PowerSSO-36™ package information . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.4PowerSO-36™ packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.5PowerSSO-36™ packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 7Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37Doc ID 14278 Rev 33/38List of tables L9953 / L9953XP List of tablesTable 1.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2.Pin definitions and functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 3.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 4.ESD protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 5.Operating junction temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 6.Temperature warning and thermal shutdown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 7.Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 8.Overvoltage and under voltage detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 9.Current monitor output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 10.Charge pump output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 11.OUT1 - OUT8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Table 12.Delay time from standby to active mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 13.Inputs: CSN, CLK, PWM1/2 and DI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 14.DI timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 15.DO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Table 16.DO timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Table 17.CSN timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Table 18.Test mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table 19.SPI - input data and Status registers 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 20.SPI - input data and status registers 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 21.PowerSO-36™ mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Table 22.PowerSSO-36™ mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 23.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 4/38 Doc ID 14278 Rev 3L9953 / L9953XP List of figures List of figuresFigure 1.Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 2.Configuration diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 3.SPI - transfer timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 4.SPI - input timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 5.SPI - DO valid data delay time and valid time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 6.SPI - DO enable and disable time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 7.SPI - driver turn-on/off timing, minimum CSN hi time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 8.SPI - timing of status bit 0 (fault condition). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 9.Example of programmable softstart function for inductive loads . . . . . . . . . . . . . . . . . . . . 22 Figure 10.Packages thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Figure 11.PowerSO-36™ package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 12.PowerSSO-36™ package dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Figure 13.PowerSO-36™tube shipment (no suffix). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Figure 14.PowerSO-36™tape and reel shipment (suffix “TR”) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Figure 15.PowerSSO-36™tube shipment (no suffix). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Figure 16.PowerSSO-36™tape and reel shipment (suffix “TR”) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36Doc ID 14278 Rev 35/38Block diagram and pin description L9953 / L9953XP6/38 Doc ID 14278 Rev 31 Block diagram and pin descriptionTable 2.Pin definitions and functionsPinSymbolFunction1, 18, 19, 36GNDGround:Reference potentialImportant: for the capability of driving the full current at the outputs all pins of GND must be externally connected.2, 35OUT8Highside driver output 8The output is built by a highside switch and is intended for resistive loads, hence the internal reverse diode from GND to the output is missing. For ESD reason a diode to GND is present but the energy which can be dissipated is limited. The highside driver is a power DMOS transistor with an internal parasitic reverse diode from the output to VS (bulk-drain-diode). The output is over-current and open load protected.Important: for the capability of driving the full current at the outputs both pins of OUT8 must be externally connected.345OUT1 OUT2OUT3Half-bridge-output 1,2,3The output is built by a highside and a lowside switch, which are internally connected. The output stage of both switches is a power DMOS transistor. Each driver has an internal parasitic reverse diode (bulk-drain-diode: highside driver from output to VS, lowside driver from GND to output). This output is over-current and open load protected.L9953 / L9953XPBlock diagram and pin descriptionDoc ID 14278 Rev 37/386, 7, 14, 15, 23, 25, 28, 32VSPower supply voltage (external reverse protection required)For this input a ceramic capacitor as close as possible to GND is recommended.Important: for the capability of driving the full current at the outputs all pins of VS must be externally connected.8DISerial data inputThe input requires CMOS logic levels and receives serial data from the microcontroller. The data is an 24bit control word and the least significant bit (LSB, bit 0) is transferred first.9CM/PWM2Current monitor output/PWM2 inputDepending on the selected multiplexer bits of Input Data Register thisoutput sources an image of the instant current through thecorresponding highside driver with a ratio of 1/10.000. This pin is bidirectional. The microcontroller can overdrive the current monitor signal to provide a second PWM input for the output OUT7.10CSNChip select not input / test modeThis input is low active and requires CMOS logic levels. The serial data transfer between L9953 and micro controller is enabled by pulling the input CSN to low level. If an input voltage of more than 7.5V is applied to CSN pin the L9953 will be switched into a test mode.11DOSerial data outputThe diagnosis data is available via the SPI and this tristate-output. The output will remain in tristate, if the chip is not selected by the input CSN (CSN = high)12VCCLogic supply voltageFor this input a ceramic capacitor as close as possible to GND is recommended.13CLKSerial clock inputThis input controls the internal shift register of the SPI and requires CMOS logic levels.16,17, 20,21,OUT4 OUT5Half-bridge-output 4,5: see OUT1 (pin 3).Important: for the capability of driving the full current at the outputs both pins of OUT4 (OUT5, respectively) must be externally connected.26CPCharge pump outputThis output is provided to drive the gate of an external n-channel power MOS used for reverse polarity protection27PWM1PWM1 input:This input signal can be used to control the drivers OUT1-OUT6 and OUT8 by an external PWM signal.Table 2.Pin definitions and functions (continued)PinSymbolFunctionBlock diagram and pin descriptionL9953 / L9953XP8/38 Doc ID 14278 Rev 33133OUT6, OUT7Highside driver output 6,7:Each output is built by a highside switch and is intended for resistive loads, hence the internal reverse diode from GND to the output is missing. For ESD reason a diode to GND is present but the energy which can be dissipated is limited. Each highside driver is a power DMOS transistor with an internal parasitic reverse diode from each output to VS (bulk-drain-diode). Each output is over-current and open load protected.22, 24, 29,30, 34NCNot connected pins.Table 2.Pin definitions and functions (continued)PinSymbolFunctionL9953 / L9953XP Electrical specificationsDoc ID 14278 Rev 39/382 Electrical specifications2.1Absolute maximum ratingsStressing the device above the rating listed in the “Absolute maximum ratings” table maycause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions forextended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality document2.2 ESD protection2.3 Thermal dataTable 3.Absolute maximum ratingsSymbol ParameterValue Unit V S DC supply voltage -0.3 to28V Single pulse t max < 400ms40V V CCStabilized supply voltage, logic supply -0.3 to 5.5V V DI , V DO, V CLK , V CSN, V pwm1Digital input / output voltage -0.3 to V CC + 0.3V V CM Current monitor output -0.3 to V CC + 0.3V V CP Charge pump output -25 to V S + 11V I OUT1,2,3,6,7Output current ±5A I OUT4,5,8Output current±10ATable 4.ESD protectionParameterValue Unit All pins± 2(1)1.HBM according to MIL 883C, Method 3015.7 or EIA/JESD22-A114-A.kV Output pins: OUT1 - OUT8± 8(2)2.HBM with all unzapped pins grounded.kVTable 5.Operating junction temperatureSymbol ParameterValue Unit T jOperating junction temperature-40 to 150°CElectrical specificationsL9953 / L9953XP10/38 Doc ID 14278 Rev 32.4 Electrical characteristicsV S = 8 to 16V , V CC = 4.5 to 5.3V , T j = - 40 to 150°C, unless otherwise specified.The voltages are referred to GND and currents are assumed positive, when the currentflows into the pin.Table 6.Temperature warning and thermal shutdownSymbol ParameterMin.Typ.Max.Unit T jTW ON Temperature warning threshold junction temperatureT j 130150°C T jSD ON Thermal shutdown threshold junction temperatureT j increasing 170°C T jSD OFFThermal shutdown threshold junction temperatureT jdecreasing150°C T jSD HYS Thermal shutdown hysteresis5°KTable 7.SupplySymbol ParameterTest conditionMin.Typ.Max.Unit V SOperating supply voltage range728VI SV S DC supply currentV S = 16V , V CC = 5.3V active modeOUT1 - OUT8 floating 720mAV S quiescent supply currentV S = 16V , V CC = 0V standby modeOUT1 - OUT8 floating T test = -40°C, 25°C 412µAT test = 85°C (1)1.Guaranteed by design.625µA I CCV CC DC supply currentV S = 16V , V CC = 5.3V CSN = V CC , active mode 13mAV CC quiescent supply currentV S = 16V , V CC = 5.3V CSN = V CC standby mode OUT1 - OUT8 floating 2550µAI S + I CCSum quiescent supply currentV S = 16V , V CC = 5.3V CSN = V CC standby modeOUT1 - OUT8 floating T test = 130°C50100µA分销商库存信息:STML9953XP L9953XPTR L9953TR L9953。

PA85中文资料

.建立时间1%CC = 10pf, 2V step1μs

电阻,空载RCL = 050Ω

电源

电压6全温度范围±15±150±225V

电流,静态2125mA

热

电阻,交流,

结到外壳5全温度范围F > 60Hz2.5°C/W

电阻,直流

结到外壳5全温度范围F < 60Hz4.2

4。+ VS和-比表示正,负电源轨分别。

5。评级适用于如果两者之间的输出电流输出晶体管候补的增长率高于60赫兹。

6。减额最大电源评级.625第V /低于25°C案℃。无降容需要25℃以上的情况。

注意

从构造的PA85 MOSFET晶体管。防静电处理程序必须得到遵守。内部基板包含氧化铍(BeO)。不要拆封。如不慎损坏,请不要挤压,机,或须在850℃,以避免产生有毒气体以上的温度。

共模抑制,直流VCM =±90V90110dB

噪声100kHz BW, RS = 1KΩ,

CC = 10pf1μVrms

增益

开环,@15HzRL = 2KΩ,CC = OPEN96111dB

增益带宽积在1MHzRL = 2KΩCC = 3.3pf100MHz

功率带宽CC = 10pf300kHz

CC = 3.3pf500kHz

输入保护

虽然PA85可承受的差分电压高达±25V的,额外的外部保护建议。由于在PA85是一种高速放大器,低漏电,低电容

作为二极管连接JFETs建议(例如2N4416,第一至第四季度在图2)。差分输入电压钳位到±1.4V时。这足以产生超速最大功率带宽。

电源保护

齐纳二极管的瞬态抑制器单向建议由于在电源引脚保护。该齐纳二极管钳位瞬变内的电源电压和额定还钳电源逆转到地面。无论是齐纳二极管使用与否,系统电源应评估包括瞬态性能上电过冲和关闭电源极性反转以及电压调节。条件,可能会导致开路或极性反转在任一电源轨应避免或保护反对。转回或打开上负电源轨众所周知,导致输入级失败。单向transzorbs防止这种情况,这是可取的,他们既电并尽量靠近身体尽可能放大器。

SNJ54AS138J中文资料

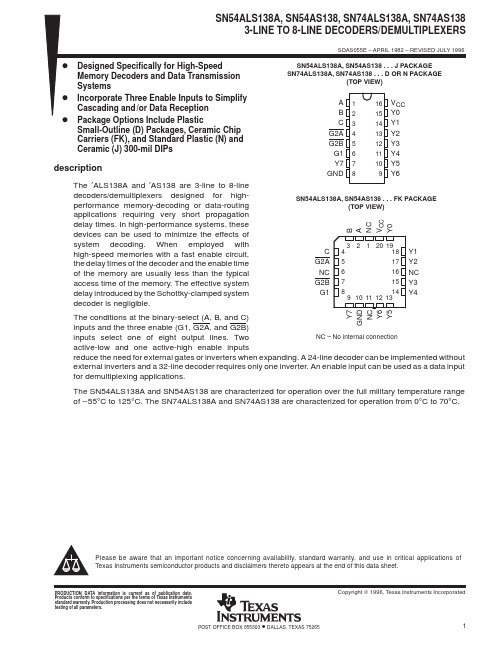

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-86866012A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-8686601FA ACTIVE CFP W161TBD Call TI Level-NC-NC-NC JM38510/37701B2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC JM38510/37701BEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN54ALS138AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN54AS138J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SN74ALS138AD ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS138ADG4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS138ADR ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS138ADRG4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS138AN ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74ALS138ANE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74ALS138ANSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74ALS138ANSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS138D ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS138DE4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS138DR ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS138DRE4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS138N ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74AS138N3OBSOLETE PDIP N16TBD Call TI Call TISN74AS138NE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AS138NSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AS138NSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54ALS138AFK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54ALS138AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54ALS138AW ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54AS138FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54AS138J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

镍合金油套管产品手册

油管/Tubing

Grade 110

Burst

Collapse

Joint

resistance strength

MPa

MPa

Байду номын сангаасKN

100.2 100.3

882

127.4 142.2

131.6 145.1

1097.6 1251.2

81.9

67.1 1087.8

96.3

93.3 1264.2

109.6

114.9

Min

20.5 33.0 4.0

BG2235

Max 0.03 0.75 1.0 23.5 38.0 5.0 0.7

Min

24.0 29.0 2.5

BG2532

Max 0.03 0.5 1.0 27.0 36.5 4.0 1.5

力学性能

Mechanical properties

grade

110 125 140

80 109.2

Joint strength

KN

1009.4 1254.4 1381.8 1234.8 1440.6 1617 2048.2 1489.6 1705.2 2116.8 1852.2 1999.2 2126.6 2450

Burst

MPa

76 89 109 132 144 75.4 83 99 114 131 68.3 78 88 98 107 116 64.9 74.2 85.1 98.9

宝山钢铁股份有限公司

BAOSHAN IRON & STEEL CO., LTD.

镍基合金油套管产品

Ni-based Alloy Tubing & Casing

ADS8555SPM;ADS8555SPMR;中文规格书,Datasheet资料