mipi 调试经验

mipi倍频原理 -回复

mipi倍频原理-回复MIPI是移动产业处理器接口(Mobile Industry Processor Interface)的缩写,它是一种旨在提供移动系统内部通信基础架构的接口标准。

MIPI 倍频技术是指将MIPI总线的基础时钟频率倍增,以提高总线的带宽和传输效率。

本文将从MIPI倍频的原理、应用场景、优缺点、实现方式等方面详细介绍。

一、MIPI倍频原理MIPI标准中使用的基础时钟频率为100MHz,在实际应用中,单个MIPI 总线很难满足高速数据传输的需求,为了提高总线的带宽,需要增加传输速率。

MIPI倍频技术就是通过倍增时钟频率,来提高传输速率。

MIPI倍频技术主要实现方式有两种:PLL(锁相环)倍频和逻辑倍频。

PLL 倍频是通过基础时钟频率经过PLL锁相环倍频器的倍增来实现。

逻辑倍频是通过复用低速总线的信号线进行数据交错来实现。

PLL倍频可将基础时钟频率提高到200、400、800MHz甚至更高,而逻辑倍频最高只能将基础时钟频率提高到200MHz。

二、MIPI倍频的应用场景MIPI倍频技术在各种多媒体设备和移动设备中得到广泛应用,特别是像4K高清视频、高速摄像头拍摄和数据传输等大流量场景。

MIPI倍频可以提高总线的带宽,增强图像和视频信号的传输速度,同时也能改善设备对于时序稳定性、功耗和EMI等方面的表现。

在高速数据传输的场景中,一些传感器的数据量很大,比如高速摄像头,单个画面的数据就可以达到几百万像素,或是大规模数据访问场景下,也需要传递海量的数据流,MIPI倍频技术就可以发挥很大的作用。

三、MIPI倍频的优缺点1. 优点MIPI倍频技术可以有效提高数据传输速率,提升总线的带宽,所以在高速数据传输场景下,倍频技术可以大大提高数据传输效率。

同时也能降低带宽利用率,减少设备能耗。

2. 缺点MIPI倍频技术也存在一些不足之处,比如倍频器的价格相对较高,同时线上噪声也有所增加。

此外,倍频技术所耗费的能量也比较大,会引起热量问题,这在移动设备中需要付出更多的代价。

MIPILCD调试总结(转载)

MIPILCD调试总结(转载)近来在⽤SSD2828驱动⼩⽶屏,没有代码,没有技术⽀持,⾃⼰写代码反复调试,整死我了,⽬前已经能正常显⽰图⽚,现在总结⼀下与⼤家分享⼀下,要点:1. ⼩⽶3屏的分辨率是19201080, 24bit, ⾏列像素点为10801920, 默认显⽰⽅式为从左->右,上->下,这个可以通过DCS指令修改.2. SSD2828⼿册上说SSD2828⼀⾏最⼤可显⽰1920个像素点(60Hz),⽽官⽹上说SSD2828的最⼤分辨率为1920x1200,所以我⼀直认为SSD2828⾏像素最⼤可设置为1920,列最⼤像素可设置为1200,实际上驱动⼩⽶3屏时,⾏列分别设置为1080*1920.3. 要⽤SSD2828最新的⼿册,⽬前能找到的是V1.3,旧版本有些地⽅是错的,误导⼈.4. SSD2828 RGB接⼝和MIPI接⼝的位数是⼀起设置的(通过B6寄存器设置),即没有RGB为24bit,MIPI为16bit的这种情况.5. SSD2828可⽀持的16,18,24bit的屏,⽽有的屏不⽀持16bit的,如⼩⽶3的屏就不⽀持,这个要看清楚.6. 屏的data lane和SSD2828设置的要⼀致7. SSD2828的VBP, VFP, HBP, HFP,和CPU这端设置不能⼀致,显⽰不正常,我也不知道为什么.驱动初始化包括SSD2828,LCD屏的初始化1. SSD2828初始化主要有设置PLL, 设置LCD参数(分辨率,VBP, VFP, HBP, HFP).CPU这端的Pclk设置为90~120MHz, SSD2828 PLL output为800MHz左右,900以上有些危险,⼲扰⼤(跟PCB有关系咯)2. SSD2828提供给CPU接⼝,通过DCS设置LCD的⼀些参数,这个要看LCD⼿册有哪些参数要设置,最主要的是0x29,0x11指令, 让LCD exit sleep mode和display on.屏不显⽰可能有⼏种情况1. 0x29,0x11指令发送不对,LCD没收到,⼀直在sleep状态.2. 屏要显⽰,data lane上肯定有波型,如果data lane波型都没有,那就是ssd2828都没有配置好,跟CPU这端没有关系.3. data lane有波型,可能跟C9, CA, CB,这⼏个寄存器有关,随便设置⼏个值试⼀下(最⼤,最⼩,中间值),我调试了⼀周,就是C9没有设置对,所以⼀直没显⽰屏幕抖动可能跟VBP, VFP, HBP, HFP,这⼏个参数有关,修改SSD2828和CPU LCD controler的这⼏个参数试⼀下颜⾊过度失真,右能跟B6寄存器中的PCLK_P和0xDB中的CLK_DELAY_SEL有关,我设置PCLK_P为1, CLK_DELAY_SEL为0,显⽰图⽚就好了.不⾏可修改CLK_DELAY_SEL试⼀下,再不⾏我也没办法了.除了必须设置的参数外,对显⽰有影响的寄存器主要有:C9, CA, CB, DB, DD, ED, 调试中主要修改了这些寄存器************************在展讯平台上点亮MIPI接⼝屏正常显⽰需要满⾜以下⼏条就可以:1:确认Lcd的驱动⽂件被正常编译编译进去,并且lcd 和board name⾥⾯注册⼀质,我有⼀次就是因为编译出现问题了,导致在kernel中⽆法正确读取LCD的ic的id,导致系统加载屏的驱动失败,造成系统进⼊kernel显⽰花屏,这部分是⾮常重要的,假如未能正确的编译进系统,你再怎么调试,屏照样⽆法正常的显⽰,这⾮常的关键!2. 必须保证数据能够正确的传输到屏上,我有⼀次调试屏驱动时,发现屏上的显⽰始终是⼀些横竖条纹,或者直接灰屏,通过在⽰波器上检测屏引脚的波形,发现屏上的数据不正常,根本没有切换到hp下刷数据,导致屏⽆法正常的显⽰,⼀般在读取ic 的id和初始化设置指令时,都是在mipi的低速(lp)模式下,在初始化完成后,需要切换到⾼速(hp)状态下,才能正常的显⽰!3. 必须保证ic设置的proch和timing,通道,速率正确,屏才可以正常的显⽰,⼀般显⽰出现花屏,显⽰偏移等问题,通常情况下,就是因为你设置的某些参数不正确,导致显⽰异常!4:仔细检查上电同时测量,同时将28根rgb interface对应gpio设为lcdc func。

mipi之dsi协议 低速模式的时钟频率

mipi之dsi协议低速模式的时钟频率

摘要:

1.介绍MIPI DSI 协议

2.讲解低速模式的时钟频率

3.分析低速模式的优势和应用场景

4.总结MIPI DSI 协议在低速模式下的性能表现

正文:

MIPI DSI(Display Serial Interface)协议是一种显示器串行接口,用于连接移动设备(如智能手机、平板电脑等)的处理器和显示器。

它通过减少显示器接口的引脚数量和提高数据传输速度,实现了更高的显示分辨率和更好的显示效果。

MIPI DSI 协议支持多种数据传输模式,包括高速模式、中速模式和低速模式。

在MIPI DSI 协议中,低速模式的时钟频率较低。

具体而言,低速模式的时钟频率为100MHz,相较于高速模式(高达1.2GHz)和中速模式

(500MHz-600MHz),其时钟频率较低。

低速模式的优势在于降低功耗和减少电磁干扰(EMI),这使得它非常适合用于低功耗设备和环境对EMI 要求较高的场景。

低速模式的主要应用场景包括:

a.低功耗设备:如智能手表、健康追踪器等,这些设备对功耗要求较高,低速模式有助于降低整体功耗。

b.医疗设备:如心电图仪、超声波扫描仪等,这些设备需要在较小范围内

进行精确的图像显示,低速模式能够满足这一要求。

c.工业控制和自动化:如生产线上的检测设备、机器人控制等,这些应用场景对EMI 有较高要求,低速模式有助于降低电磁干扰。

总之,MIPI DSI 协议在低速模式下具有较低的时钟频率,这使得它在功耗和电磁干扰方面具有优势,非常适合应用于对功耗和EMI 要求较高的场景。

MIPI技术的发展、常见问题及测量方法

MIPI技术的发展、常见问题及测量方法MIPI 技术的发展、常见问题及测量方法安捷伦科技(中国)有限公司马卓凡2012.7最近一段时间有不少手机芯片、智能手机、摄像头和显示模块客户等对MIPI的测试方案很感兴趣,对传统的无线应用的客户来说,这个领域还是比较新的,作者写作本文的目的是对MIPI技术的发展状况及D-PHY测试中常见的问题、测试内容、方法进行梳理,以及对MIPI标准的进展进行总结,希望能帮助读者更加深入理解这个总线的测试原理和方案。

MIPI的概况随着3G、LTE以及4G标准的发展,智能手机也呈现爆炸式增长,手机也不再仅仅是简单的语音通话和收发短信的工具,而越来越成为一个智能终端,除了手机的基本功能之外,它还能实现高分辨率显示,高像素拍照,高速的数据下载传输,以及高性能的图形处理及软件处理能力。

从内在来看,这推动着芯片间及模组间的数据传输速率呈指数性增长,另一个方面,为了能够简化设计和提高芯片间及模组间的兼容性,统一的接口标准也是一大发展趋势。

MIPI联盟正是在这样的技术发展背景下应运而生,它的全称是Mobile Industry Processor Interface (移动产业处理器接口) 。

这个联盟是一个开放的会员制组织,旨在推进标准化的应用处理器接口,鼓励所有移动设备行业的公司参加,其中包括半导体厂商,软件厂商,IP 供应商,外围设备制造商,测试实验室和终端产品的制造商。

根据MIPI联盟官方网站上引用的IPNes提供的研究报告预计,到2013年MIPI规范在智能手机中的普及率将达到100%,到2015年在其它类型手机中也将达到90%。

MIPI联盟的目的是在移动设备比如智能手机和平板电脑等硬件和软件建立接口标准,通过一套标准的硬件接口,将各种外设产品及不同的供应商产品能够与众多的处理器或SOC能够兼容对接。

另外软件的标准化也会提高设计可重用性,降低参与者的进入市场的时间。

下图来源于MIPI官方网站,这张图给出了MIPI涵盖的所有的接口总线。

力科发布MIPI测试解决方案

仓 无 线 烟 感 ”项 目 ; ( ) 方 便 群 众 3 出 行 的 ~ “ 业 园 区 智 能 公 交 ” 项 工 目 ; ( )提 升 管 理 水 平 、实 现 精 细 4

化 管 理 的 一 “ 州 公 交 车 辆 巡 更 系 苏 统 ” ( )从 节 能 降耗 出发 ,实 现 供 ; 5

指定 数 据 中的 比特 或群 组 。

It ae ne c)标 准 提 供 最 全 面 的 测 试 解 f

决方 案 。MI I 准 正 在 驱 动 下 一 代 移 P标

动 设 备一 许 更 快 的 数 据 传 输 率 ,更 允 低 的 功 耗 .以及 更 高分 辨率 的显 示 器 和 照相 机 。相 关 的设 计 人 员 要 求 能测

联 盟 规 范 D— HY 版 本 v rin 10 .0 P eso .H0 D 执 行 发 送 端 物 理层 测 试 的能 力 。

测 试报 告 。除 此之 外 ,所 有 Q HY P —

MI I D H 测 试 过 的 波 形 都 能 被 保 P— P Y 存 .方 便 共 享 信 息 或 在 日后 的某 个 时 间重 新 运 行 测试 。

力科 的 P R0T b sMAG 串 行 调 O u

应 了这 种 需 求 。 Q aiH P — P Y ( P Y— u l Y MI I D H P Q H MI I D HY 测试 方 案 提供 自动 化 控 P— P 1 制力 科 示 波 器 的能 力 ,支 持 按 照MI I P

MII iR G 标 到 B I FC B C接 口 。 D g F 3 标 准 对 于 移 动 设 备 的 好 处 i G R

易 用 的用 户 配 置 接 口 ,允 许 定 制 化 测 试 和 限 制器 选 择 .显 示 连 接 示 意 图 让 用 户确 保 连 接 正 确 ,并 且 生 成 完 整 的

全面的MIPI测试解决方案范文

全面的MIPI测试解决方案范文MIPI标准正在驱动下一代移动设备——允许更快的数据传输速率、更低的功耗以及更高分辨率的显示器和照相机,正在与该标准打交道的芯片设计人员要求能测试这些技术的工具。

力科公司推出了DPHY标准物理层的自动化一致性测试软件包,可满足MIPI标准的全面测试需求。

.W01ei下的发光强度为40mC至安装变动更加快捷方便,只需简单的旋10,可耐受高温循环。

RCL623流50dcd。

转即锁紧。

和RC113过了AE-20Re.L28e通CQ0v认证,其宽大的端头实现了高功率耗Q—某C0连接器不仅适合光连接C器,还可以安装以太网口RJ5接器。

4连HUBER+SUHNER散。

在密集堆叠的PCB上,器件的小尺寸可节约空间,实现更多的温度循环,从而提高汽车电子系统和其他通用电子系统的可靠性。

Re系列的容差为CL315%和%,阻值范围为1~22(。

电Q.M】ED采用无杂质、无色的塑料军用级捆扎线缆标识阻具有一层保护釉面,在镍阻挡层上的歪,视角为±2.。

,具有很镜25可打印CM—NM某军用级线缆标志纯锡焊接面兼容无铅和含铅焊接工艺。

l指令20/5EC,并符029/渝出和可视性能。

其热阻低至适用于大型线束、线缆、管道及管路的器件符合RoSE1421,,功率耗散高达9mW。

器件的标志识别。

该标志采用高耐用性的防火合IC6292的无卤素定义。

5meaaad 见角为±2.。

,根据发光情况芳香族聚醯胺纤维(t—rmi),25VihyIttchoOyanerenIg廷,使每个包装内器件的发光强可承受各种严苛环境要求,是工业、能都保持一致。

LD可承受2V的源、航空及国防等行业的最佳选择。

ERE,符合JS2一规范,ED2A14B1}o指令20/5E。

RHS029/C;aynetcnOghItrehOIyCM—MN某标志具有优秀的耐溶性并符合MI—TD一0、25LS221K标准的液体防护要求。

MIPI_debugging_tips(MIPI调试小结)

LP01CLK_dly-----TLPX LP00CLK_dly-----TCLK-PREPARE HS00CLK_dly-----TCLK-ZERO HSXXCLK_dly-----No meaning CLK2DATA_dly----TCLK-PRE

LP01DATA_dly-----TLPX LP00DATA_dly-----THS-PREPARE HS00DATA_dly-----THS-ZERO HSXXDATA_dly-----THS-TRAIL

MIPI调试小结

1. 输入输出的各种不同接法。 2. CSI/DSI输入部分的调试。 3. CSI/DSI输出部分的调试。

用示波器测量输入/输出的MIPI信号的波形,以确认信号的连接,电阻的匹配,电路板的焊接 等等是否正确。特别要注意的是高速或者低速的P和N端不能接反。下面几个图是介绍非MIPI专 用管脚(XO2/XO3/ECP3/ECP5)的IO的连接,主要是针对输入部分。输出部分所有的时钟管脚和数 据管脚都是接分压电阻。 (1)DSI在LP的时候有可能会有双向传输,这种情况就要采用下面这种连接方法:

(3)DSI输出点屏的注意点

DSI输出点屏第一步就是要初始化屏,一般会有reset信号的产生以及各种命令的发 送。初始化的命令大多数都是在low power时产生。每个命令发完都会进low power,间 隔时间一般都有最短时间的要求。一开始可以用color bar或者纯色去点屏。

快速掌握MIPI开发攻略,对接百度人工智能计算卡EdgeBoard

快速掌握MIPI开发攻略,对接百度人工智能计算卡EdgeBoardMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写,是MIPI联盟发起的为移动应⽤处理器制定的开放标准。

MIPI采⽤高速串行接口传输数据,满⽤高分辨率摄像头的传输需求,采用串行接口方便PCB布局布线,提高信号完整性,也有利于减小PCB面积。

MIPI接口的摄像头一般体积较小,适合于小型的嵌入式设备,比如手机和行车记录仪等,同时也广泛应用到AI端上推理设备。

本文以百度的端上推理设备EdgeBoard作为原型来介绍MIPI相关技术的开发。

如果用户购买EdgeBoard,出厂的镜像中带有MIPI的功能,只需再购买推荐的MIPI摄像头,即可实现即插即用。

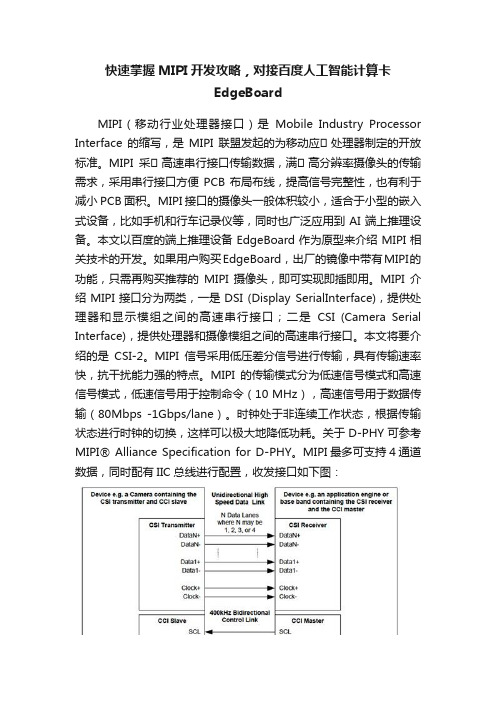

MIPI介绍MIPI接口分为两类,一是DSI (Display SerialInterface),提供处理器和显示模组之间的高速串行接口;二是CSI (Camera Serial Interface),提供处理器和摄像模组之间的高速串行接口。

本文将要介绍的是CSI-2。

MIPI信号采用低压差分信号进行传输,具有传输速率快,抗干扰能力强的特点。

MIPI的传输模式分为低速信号模式和高速信号模式,低速信号用于控制命令(10 MHz),高速信号用于数据传输(80Mbps -1Gbps/lane)。

时钟处于非连续工作状态,根据传输状态进行时钟的切换,这样可以极大地降低功耗。

关于D-PHY可参考MIPI® Alliance Specification for D-PHY。

MIPI最多可支持4通道数据,同时配有IIC总线进行配置,收发接口如下图:MIPI协议也是采用类似于以太网协议结构,采用分层设计的思想,分为PHY Layer,Protocal Layer和Application Layer。

MIPI传输的报文中定义了图像数据的类型/格式(Data type),这些类型/格式方便在调试的时候确定链路是否工作正常,常用的Data Type如下图,比如YUV的数据格式的标示符是0x18到0x1F,期间的数值定义了具体的格式,比如YUV422,YUV444等,具体可参考MIPI Alliance Specification for CameraSerial Interface 2。

移动网页加速器MIP问题解决方案大全

网页加速,百度搜索推出了“MIP”,Google推出了“AMP”,其实,很多人不做MIP改造还是因为移动端打开后,是百度的域名。

网页加速技术介绍MIP(Mobile Instant Page - 移动网页加速器),是一套应用于移动网页的开放性技术标准。

通过提供MIP-HTML规范、MIP-JS运行环境以及MIP-Cache页面缓存系统,实现移动网页加速。

AMP(Accelerated Mobile Pages)是谷歌的一项开放源代码计划,可在移动设备上快速加载的轻便型网页,旨在使网页在移动设备上快速加载并且看起来非常美观。

百度目前可支持AMP提交。

一、MIP 认知类问题1.1 MIP 化的收益是什么?具体数据是怎样的?从目前收集到的数据来看,网站 MIP 化上线后,页面速度提升 30%~80%,页面到达率提升 5%~40%。

1.2 有没有已上线MIP页可以参考呢?现在已经有上千家站点完成了MIP改造,点击《MIP页面效果精选》查看示例。

1.3 开发 MIP 后,搜索流量是导流到 MIP,还是导流到原页面?应该导流到 MIP 页面,需要在 MIP 页面中做好和原页面的对应关系。

1.4 MIP 移动网页加速器做了之后是只针对移动百度的展示,还是说也对我们其他的正常用户一样显示?MIP 页面是可以独立运行的,可以在浏览器中通过url 直接访问,不依赖百度结果页。

由于 MIP 页速度较快,体验更优,会在百度移动结果页有更高的权重。

1.5 搜索结果打开是百度的域名,用户分享的是否也是是百度链接?使用百度域名是否不利于网站的品牌传播同时也会影响流量统计,该如何解决?答:如果用户通过分享组件分享,则分享的标题,图片和内容都是原页面内容,具体分享内容可以在使用组件时定义。

这种做法不会影响品牌传播,也不会影响流量统计。

如果用户直接从浏览器复制链接分享,那么被分享的是当前页面 URL (MIP Shell 链接),URL 中是能够反解出原页面 URL 的。

(完整word版)MIPIDSI协议介绍

一、MIPIMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。

MIPI (移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

已经完成和正在计划中的规范如下:二、MIPI联盟的MIPI DSI规范1、名词解释• DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

• DSI, CSI (DisplaySerialInterface, CameraSerialInterface• DSI 定义了一个位于处理器和显示模组之间的高速串行接口。

• CSI 定义了一个位于处理器和摄像模组之间的高速串行接口。

• D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:• PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

• Lane Management层:发送和收集数据流到每条lane。

• Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

• Application层:描述高层编码和解析数据流。

3、Command和Video模式• DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定• Command模式是指采用发送命令和数据到具有显示缓存的控制器。

主机通过命令间接的控制外设。

Command模式采用双向接口• Video模式是指从主机传输到外设采用时实象素流。

这种模式只能以高速传输。

为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径三、D-PHY介绍1、 D-PHY 描述了一同步、高速、低功耗、低代价的PHY。

• 一个 PHY配置包括• 一个时钟lane• 一个或多个数据lane• 两个Lane的 PHY配置如下图• 三个主要的lane的类型• 单向时钟Lane• 单向数据Lane• 双向数据Lane• D-PHY的传输模式•低功耗(Low-Power)信号模式(用于控制):10MHz (max)• 高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane • D-PHY低层协议规定最小数据单位是一个字节• 发送数据时必须低位在前,高位在后.• D-PHY适用于移动应用• DSI:显示串行接口• 一个时钟lane,一个或多个数据lane• CSI:摄像串行接口2、Lane模块• PHY由D-PHY(Lane模块)组成• D-PHY可能包含:• 低功耗发送器(LP-TX)• 低功耗接收器(LP-RX)• 高速发送器(HS-TX)• 高速接收器(HS-RX)• 低功耗竞争检测器(LP-CD)• 三个主要lane类型• 单向时钟Lane• Master:HS-TX, LP-TX• Slave:HS-RX, LP-RX• 单向数据Lane• Master:HS-TX, LP-TX• Slave:HS-RX, LP-RX• 双向数据Lane• Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD3、Lane状态和电压• Lane状态• LP-00, LP-01, LP-10, LP-11 (单端)• HS-0, HS-1 (差分)• Lane电压(典型)• LP:0-1.2V• HS:100-300mV (200mV)4、操作模式• 数据Lane的三种操作模式• Escape mode, High-Speed(Burst) mode, Control mode•从控制模式的停止状态开始的可能事件有:• Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)• High-Speed mode request (LP-11→LP-01→LP-00)• Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)• Escape mode是数据Lane在LP状态下的一种特殊操作•在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger•数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00•一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作• Escape mode 使用Spaced-One-Hot Encoding•超低功耗状态(Ultra-Low Power State)•这个状态下,lines处于空状态 (LP-00)•时钟Lane的超低功耗状态•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态•通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms•高速数据传输•发送高速串行数据的行为称为高速数据传输或触发(burst)•全部Lanes门同步开始,结束的时间可能不同。

MIPIDPHY调试记录

MIPIDPHY调试记录1. 系统框架MIPI接⼝在系统的实现如上图所⽰,MIPI DPHY提供了4 Lane的Rx接⼝,由Sensor提供Clock,并通过四条数据Lane输⼊图像数据。

DPHY与CSI-2 Host Contrller之间通过PPI(PHY-Protocol Interface)相连,该接⼝包括了控制,数据,时钟等多条信号。

CSI-2 Host Contrller通过PPI接⼝收到数据后进⾏解析,完成后通过IDI(Image Data Interface)或者IPI(Image Pixel Interface)输出到SoC的其他模块(ISP);同时SoC通过APB Slave总线控制CSI-2 Host Contrller的相关寄存器。

2. 功能IP下⾯两表描述了系统使⽤的CSI-2 Controller与DPHY,以及与CSI对接的ISP相关的部分性能参数:(1)Synopsys CSI-2 ControllerIDI(Image Data Interface )接⼝:- 输出CSI-2 规格书中推荐的32位或者64位的图像格式;- 提供⽔平或竖直⽅向的精确视频同步信号;- 提供CSI-2 Data Type (DT) 和 Virtual Channel (VC)的相关信息;IPI(Image Pixel Interface)接⼝:- 48 位并⾏输出,提供像素时钟同步信号;- 提供⽔平或竖直⽅向的精确视频同步信号;(2)Synopsys DPHYPPI(Phy Protocal Interface)接⼝:- 根据DPHY规格书定义的PPI接⼝;(3)Om ISP3. DPHY输⼊MIPI DPHY采⽤1对源同步的差分时钟和1~4对差分数据链路来进⾏数据传输,数据传输采⽤DDR⽅式,即在时钟的上下边沿都有数据传输;根据Sensor不同的输出链路数量,接收端可以配置1到4条输⼊链路;数据链路越多,图像数据传输速度也就越快,多通道发送实现如上图所⽰,接收端与其类似,从不同通道接收的数据加以合并最后形成完整的数据流。

mipicrc校验计算

mipicrc校验计算

MIPICRC(MIPI Camera Serial Interface 2, Clock Recovery Checksum)校验是一种用于MIPI CSI-2接口的数据完整性校验。

它是通过计算数据包中每个字节的校验和来实现的。

校验和是将每个字节的二进制值相加,并取结果的低8位。

以下是一个计算MIPICRC校验的示例算法:

1. 定义一个变量,用于存储校验和的结果。

2. 遍历数据包中的每个字节:

- 将当前字节的二进制值与校验和进行相加。

- 如果相加的结果大于255,则将结果减去256。

3. 最终的校验和即为结果。

例如,假设待校验的数据包为 [0x12, 0x34, 0x56],对应的二进制值为 [00010010, 00110100, 01010110]。

计算过程如下:

1. 初始化校验和为0。

2. 将0x12与0进行相加,结果为0x12。

3. 将0x34与0x12进行相加,结果为0x46。

4. 将0x56与0x46进行相加,结果为0x9C。

由于结果大于255,需要减去256。

5. 最终的校验和为0x9C。

因此,对于给定的数据包 [0x12, 0x34, 0x56],其MIPICRC校验值为0x9C。

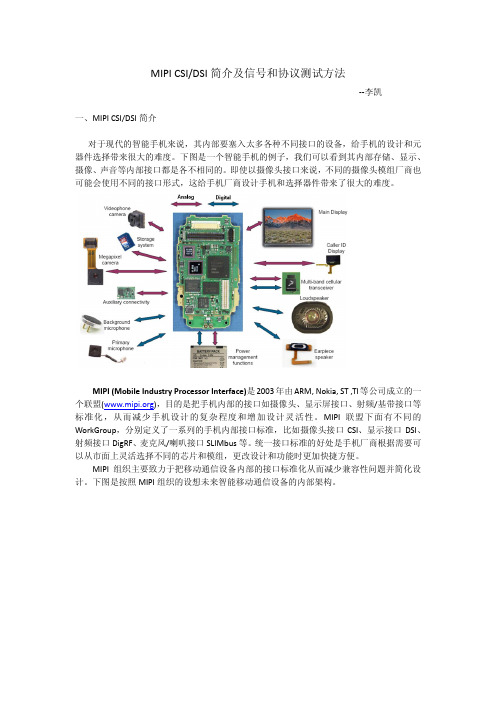

MIPI CSIDSI 简介及信号和协议测试方法

MIPI CSI/DSI简介及信号和协议测试方法--李凯一、MIPI CSI/DSI简介对于现代的智能手机来说,其内部要塞入太多各种不同接口的设备,给手机的设计和元器件选择带来很大的难度。

下图是一个智能手机的例子,我们可以看到其内部存储、显示、摄像、声音等内部接口都是各不相同的。

即使以摄像头接口来说,不同的摄像头模组厂商也可能会使用不同的接口形式,这给手机厂商设计手机和选择器件带来了很大的难度。

MIPI (Mobile Industry Processor Interface)是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟(),目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风/喇叭接口SLIMbus等。

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

MIPI组织主要致力于把移动通信设备内部的接口标准化从而减少兼容性问题并简化设计。

下图是按照MIPI组织的设想未来智能移动通信设备的内部架构。

目前已经比较成熟的MIPI应用有摄像头的CSI接口、显示屏的DSI接口以及基带和射频间的DigRF接口。

UFS、LLI等规范正在逐步制定和完善过程中。

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前采用的物理层标准是D-PHY。

D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。

数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。

D-PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。

HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps);LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。

mipi之dsi协议 低速模式的时钟频率

mipi之dsi协议低速模式的时钟频率

摘要:

1.介绍MIPI DSI 协议

2.讲解低速模式的时钟频率

3.分析低速模式的优势和应用场景

4.总结MIPI DSI 协议在低速模式下的性能和特点

正文:

MIPI DSI(Display Serial Interface)协议是一种显示器串行接口,用于连接移动设备中的处理器和显示器。

它支持多种显示器接口标准,如RGB、LVDS 和HDMI 等。

MIPI DSI 协议通过低速模式和高速模式两种不同的数据传输模式,以满足不同性能需求的设备。

在MIPI DSI 协议中,低速模式的时钟频率是一个重要的参数。

低速模式的时钟频率通常为100MHz 至300MHz,相较于高速模式(高达

800MHz),其时钟频率较低。

低速模式适用于对带宽要求不高的应用场景,如低分辨率显示器、简单的图形界面等。

低速模式的优势在于其较低的功耗和成本。

由于时钟频率较低,低速模式可以降低系统功耗,延长设备的电池续航时间。

同时,低速模式所需的硬件成本也相对较低,可以降低整体系统的成本。

因此,低速模式在智能手机、平板电脑等移动设备中得到了广泛应用。

在MIPI DSI 协议中采用低速模式,虽然数据传输带宽有所降低,但其性能仍然可以满足大部分低分辨率显示器的需求。

同时,低速模式下的MIPI DSI

协议依然具有较低的功耗和成本优势,使其成为移动设备显示器接口的理想选择。

综上所述,MIPI DSI 协议在低速模式下具有较低的时钟频率、较低的功耗和成本,以及满足低分辨率显示器需求的性能。

mipi之dsi协议 低速模式的时钟频率

mipi之dsi协议低速模式的时钟频率

摘要:

1.介绍MIPI DSI 协议

2.详述低速模式的时钟频率

3.总结低速模式时钟频率的作用和意义

正文:

MIPI DSI(Display Serial Interface)协议是一种用于连接显示器和嵌入式系统的串行接口标准。

它被广泛应用于智能手机、平板电脑等消费电子产品中,以实现高效、低功耗的显示器驱动。

MIPI DSI 协议支持多种数据传输模式,包括高速模式、中速模式和低速模式。

其中,低速模式的时钟频率是一个重要的参数。

低速模式的时钟频率是指在MIPI DSI 协议的低速模式下,数据传输所采用的时钟频率。

根据MIPI DSI 协议规定,低速模式的时钟频率范围为100 MHz 至300 MHz。

在这个范围内,可以根据实际需求选择合适的时钟频率。

低速模式的时钟频率直接影响到数据传输速率和显示器的刷新率,从而影响到显示效果和系统性能。

低速模式的时钟频率对于显示器驱动具有重要意义。

较低的时钟频率可以降低功耗,提高电池续航时间,但可能导致显示效果不佳;较高的时钟频率则可以带来更好的显示效果,但会增加功耗,缩短电池续航时间。

因此,在实际应用中需要根据具体需求和条件,权衡低速模式的时钟频率。

总之,MIPI DSI 协议中的低速模式的时钟频率是一个关键参数,影响着数

据传输速率和显示效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、D-PHY1、传输模式LP(Low-Power)模式:用于传输控制信号,最高速率10 MHzHS(High-Speed)模式:用于高速传输数据,速率范围[80 Mbps,1Gbps] per Lane传输的最小单元为1 个字节,采用小端的方式及LSB first,MSB last。

2、Lane States* LP mode 有4 种状态:LP00、LP01(0)、LP10(1)、LP11 (Dp、Dn)* HS mode 有2 种状态:HS-0、HS-1HS 发送器发送的数据LP 接收器看到的都是LP00,3、Lane Levels* LP:0 ~ 1.2V* HS:100 ~ 300mV,HS common level = 200mV,swing = 200 mv4、操作模式在数据线上有3 种可能的操作模式:Escape mode, High-Speed (Burst) mode and Control mode,下面是从停止状态进入相应模式需要的时序:* Escape mode 进入时序:LP11→LP10→LP00→LP01→LP00,退出时序:LP10→LP11当进入Escape mode 需要发送8-bit entry command 表明请求的动作,比如要进行低速数据传输则需要发送cmd:0x87,进入超低功耗模式则发送cmd:0x78。

在DSI 中LP 通讯只用Data Lane 0。

* High-Speed mode 进入时序:LP11→LP01→LP00→SoT(0001_1101),退出时序:EoT→LP11,时序图如下:* Turnaround 进入时序:LP11→LP10→LP00→LP10→LP00,退出时序:LP00→LP10→LP11这是开启BTA 的时序,一般用于从slave 返回数据如ACK:0x84。

5、时序要求在调试DSI 或者CSI 的时候,HS mode 下的几个时序非常重要:T_LPX,T_HS-SETTLE ≈ T_HS-PREPARE + T_HS-ZERO,T_HS-TRAIL,一般遵循的原则为:Host 端的T_HS-SETTLE > Slave 端的T_HS-SETTLE。

二、DSI1、线路构成在DSI 中需要1 根时钟线以及1 ~ 4 根数据线。

2、两种接口的LCD* Comman mode(对应MPU 接口)* Video mode(对应RGB 接口)该模式下视频数据只能通过HS mode 传输。

3、数据包类型短包:4 bytes,由3 部分组成:* Data Identifier (DI) * 1byte:Contains the Virtual Channel[7:6] and Data Type[5:0].* Packet Data * 2byte:Length is fixed at two bytes* Error Correction Code (ECC) * 1byte:allows single-bit errors to be corrected and 2-bit errors to be detected.长包:6 ~ 65541 bytes,同样由3 部分组成:* Packet Header(4 bytes) - 包头Data Identifier (DI) * 1byte:Contains the Virtual Channel[7:6] and Data Type[5:0]. Word Count (WC) * 2byte:defines the number of bytes in the Data Payload.Error Correction Code (ECC) * 1byte:allows single-bit errors to be corrected and 2-bit errors to be detected.* Data Payload(0~65535 bytes) - 有效数据Length = WC × bytes* Packet Footer(2 bytes):Checksum - 包尾If the payload has length 0, then the Checksum calculation results in FFFFhIf the Checksum isn’t calculated, the Checksum value is 0000h4、从控制器到外设发送的包类型如果希望从外设读取数据或者状态,则在处理器发送完读取命令后还需要发送BTA 命令,非读取命令在外设接收成功后会返回trigger message 0x84。

5、从外设到处理器数据包类型返回的数据一般分为4 个类型:* Tearing Effect (TE):trigger message (BAh)* Acknowledge:trigger message (84h)* Acknowledge and Error Report:short packet (Data Type is 02h)* Response to Read Request:short packet or long packetGeneric Read Response、DCS Read Response(1byte, 2byte, multi byte)读取数据返回值解析示例如下:[cpp]view plaincopy1.- Acknowledge and Error report (if error occurs)2.Byte 0 is 0x87 (escape mode low power data transmission header)3.Byte 1 is 0x02 (Data type, 8.10 of “MIPI Alliance Specification for DSI”)4.Byte 3,2 are error report bits[15:0] (8.9.5 of “MIPI Alliance Specificationfor DSI”)5.Byte 4 is the ECC, calculated from byte 1,2,36.7.- Generic Short READ response8.Byte 0 is 0x87 (escape mode low power data transmission header)9.Byte 1 is 0x11 or 0x12 (8.10 of “MIPI Alliance Specification for DSI”)10.Byte 2,3 are the read data. If only 1 byte is returned, byte 3 will be 0x0011.Byte 4 is the ECC, calculated from byte 1,2,312.13.- Long READ packet response14.Byte 0 is 0x87 (escape mode low power data transmission header)15.Byte 1 is 0x1A (8.10 of “MIPI Alliance Specification for DSI”)16.Byte 3,2 are the word count N (N=0 to 65535)17.Byte 4 is the ECC, calculated from byte 1,2,318.Byte 5 to byte 5+N-1 are the N-byte read data19.Byte 5+N+1, byte 5+N are the checksum, calculated on byte 5 to byte 5+N-1. If20.checksum is not calculated by peripheral, this field is 0x0000.[cpp]view plaincopy1.- Acknowledge and Error report (if error occurs)2.Byte 0 is 0x87 (escape mode low power data transmission header)3.Byte 1 is 0x02 (Data type, 8.10 of “MIPI Alliance Specification for DSI”)4.Byte 3,2 are error report bits[15:0] (8.9.5 of “MIPI Alliance Specificationfor DSI”)5.Byte 4 is the ECC, calculated from byte 1,2,36.7.- Generic Short READ response8.Byte 0 is 0x87 (escape mode low power data transmission header)9.Byte 1 is 0x11 or 0x12 (8.10 of “MIPI Alliance Specification for DSI”)10.Byte 2,3 are the read data. If only 1 byte is returned, byte 3 will be 0x0011.Byte 4 is the ECC, calculated from byte 1,2,312.13.- Long READ packet response14.Byte 0 is 0x87 (escape mode low power data transmission header)15.Byte 1 is 0x1A (8.10 of “MIPI Alliance Specification for DSI”)16.Byte 3,2 are the word count N (N=0 to 65535)17.Byte 4 is the ECC, calculated from byte 1,2,318.Byte 5 to byte 5+N-1 are the N-byte read data19.Byte 5+N+1, byte 5+N are the checksum, calculated on byte 5 to byte 5+N-1. If20.checksum is not calculated by peripheral, this field is 0x0000.6、Video 模式的3 种数据格式* Non-Burst Mode with Sync Pulses* Non-Burst Mode with Sync Events* Burst Mode* 调试记录LCD半边闪屏问题,原厂给的信息:分析了系統板送出的video mode timing,資訊摘要如下HSCLK: 160MHzPer lane bit-rate: 320Mbps (UI=3.125ns)HS SoT HS-prepare + HS-zero 約155ns由上述的timing 懷疑與現象是因為IC HS data settle timing 搭配不當所導致看来是我们输出的mipi信号HS-prepare + HS-zero 比LCD 默认设置短引起的。