K4T51043QB-VCE6中文资料

科泰公司产品说明基本配置介绍

上海科泰电源股份有限公司

SHANGHAI COOLTECH POWER CO., LTD

Logo

KV系列机组 KV系列机组

KV系列80-700KVA

上海科泰电源股份有限公司

SHANGHAI COOLTECH POWER CO., LTD

Logo

KV系列机组 KV系列机组

VOLVO PENTA 发动机型号含义

无E表示输出功率为长行功率 有E表示输出功率为备用功率 C表示防音型 B表示方舱电站 A表示集装箱电站 T表示拖车 V表示车载 上海科泰电源股份有限公司

SHANGHAI COOLTECH POWER CO., LTD

Logo

K系列机组说明

测试条件和标准 ——40℃,海拔1000米,相对湿度60% ——发动机:ISO3046,DIM6271,BS5514 ——发电机:VDE0530,BS4999,NEMA MG21,IEC34.1 ——发电机组:ISO8528 GB2820 包装 基本型机组标准包装方式为塑料薄膜包装。 运行 长行功率:用于取代市电向变化负载持续供电,平均每12小时允许1小 时超负载10%运行 备用功率:当正常市电供应中断时向变化负载持续供电,无超载能力, 平均每12小时允许1小时满负载运行。 保修 自出厂之日起计12个月或者1500工作小时,以先到为准。 使用条件 机组在海拔1000米及以下,环境温度40度,相对湿度60%时,能够实现 满负荷输出,其他条件下,均可按照相关标准修正输出功率。

Logo

公司产品及基本配置介绍 公司产品及基本配置介绍 产品

上海科泰电源股份有限公司 —销售服务中心

版本编号:VO.0904-03

Logo

公司产品及基本配置介绍

1、K系列机组型号说明; 2、K系列柴油发电机组及基本配置; 3、K系列小功率柴油发电机组及基本配置; 4、特殊用途柴油发电机组; 5、8000系列控制屏及配套件; 6、自动负载切换屏(ATS); 7、机组随机配置

VNQ5E050AK-E中文资料

March 2008 Rev 21/37VNQ5E050AK-EQuad channel high side driver with analog current sensefor automotive applicationsFeatures■General–Inrush current active management by power limitation–Very low stand-by current– 3.0V CMOS compatible inputs–Optimized electromagnetic emissions –Very low electromagnetic susceptibility –In compliance with the 2002/95/EC european directive–Very low current sense leakage ■Diagnostic functions–Proportional load current sense–High current sense precision for wide currents range–Current sense disable–Off state open load detection –Output short to V CC detection–Overload and short to ground (power limitation) indication–Thermal shutdown indication■Protections–Undervoltage shutdown –Overvoltage clamp –Load current limitation–Self limiting of fast thermal transients–Protection against loss of ground and loss of V CC–Over-temperature shutdown with autorestart (thermal shutdown)–Reverse battery protected (see Figure 32)–Electrostatic discharge protectionApplication■All types of resistive, inductive and capacitive loads■Suitable as LED driverDescriptionThe VNQ5E050AK-E is a quad channel high-side driver manufactured in the ST proprietaryVIPower M0-5 technology and housed in the tiny PowerSSO-24 package. The VNQ5E050AK-E is designed to drive 12V automotive grounded loads delivering protection, diagnostics and easy 3V and 5V CMOS compatible interface with any microcontroller.The device integrates advanced protectivefunctions such as load current limitation, inrush and overload active management by power limitation, over-temperature shut-off with auto-restart and over-voltage active clamp.A dedicated analog current sense pin isassociated with every output channel in order to provide Ehnanced diagnostic functions including fast detection of overload and short-circuit to ground through power limitation indication, over-temperature indication, short-circuit to Vcc diagnosis and ON & OFF state open load detection.The current sensing and diagnostic feedback of the whole device can be disabled by pulling the CS_DIS pin high to allow sharing of the external sense resistor with other similar devices.Max supply voltage V CC41VOperating voltage range V CC 4.5 to 28V Max on-state resistance (per ch.)R ON 50 m ΩCurrent limitation (typ)I LIMH 27 A Off state supply currentI S2 µA (1)1.Typical value with all loads connected.PowerSSO-24Contents VNQ5E050AK-EContents1Block diagram and pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 52Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.1Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.2Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82.3Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.4Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182.5Electrical characteristics curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243.1GND protection network against reverse battery . . . . . . . . . . . . . . . . . . . 243.1.1Solution 1: resistor in the ground line (RGND only) . . . . . . . . . . . . . . . . 243.1.2Solution 2: diode (DGND) in the ground line . . . . . . . . . . . . . . . . . . . . . 253.2Load dump protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253.3MCU I/Os protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253.4Current sense and diagnostic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263.4.1Short to VCC and OFF state open load detection . . . . . . . . . . . . . . . . . 273.5Maximum demagnetization energy (VCC=13.5V) . . . . . . . . . . . . . . . . . . 284Package and PC board thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . 294.1PowerSSO-24 thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295Package and packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325.1ECOP ACK® packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325.2PowerSSO-24 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325.3Packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 6Order codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 7Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362/37VNQ5E050AK-E List of tables List of tablesTable 1.Pin functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Table 2.Suggested connections for unused and not connected pins . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 3.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table 4.Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Table 5.Power section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 6.Switching (V CC=13V; T j= 25°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 7.Logic inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 8.Protections and diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 9.Current sense (8V<VCC<18V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 10.Open load detection (8V<VCC<18V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Table 11.Truth table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Table 12.Electrical transient requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 13.Thermal parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 14.PowerSSO-24 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 15.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table 16.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 363/37List of figures VNQ5E050AK-E List of figuresFigure 1.Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 2.Configuration diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 3.Current and voltage conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4.Current sense delay characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 5.Open load Off-state delay timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 6.Switching characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 7.Delay response time between rising edge of ouput current and rising edge of current sense (CS enabled) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 8.Output voltage drop limitation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 9.I OUT/I SENSE vs. I OUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 10.Maximum current sense ratio drift vs. load current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 11.Normal operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 12.Overload or Short to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 13.Intermittent Overload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 14.OFF-State Open Load with external circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 15.Short to V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 16.T J evolution in Overload or Short to GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 17.Off state output current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 18.High level input current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 19.Input clamp voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 20.Input low level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 21.Input high level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 22.Input hysteresis voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 23.On state resistance vs. T case . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 24.On state resistance vs. V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 25.Undervoltage shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 26.Turn-On voltage slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 27.I LIMH vs. T case. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 28.Turn-Off voltage slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 29.CS_DIS high level voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 30.CS_DIS clamp voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 31.CS_DIS low level voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 32.Application schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 33.Current sense and diagnostic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 34.Maximum turn-Off current versus inductance (for each channel). . . . . . . . . . . . . . . . . . . . 28 Figure 35.PowerSSO-24 PC board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Figure 36.Rthj-amb vs. PCB copper area in open box free air condition (one channel ON). . . . . . . . 29 Figure 37.PowerSSO-24 thermal impedance junction ambient single pulse (one channel ON). . . . . 30 Figure 38.Thermal fitting model of a double channel HSD in PowerSSO-24 . . . . . . . . . . . . . . . . . . . 30 Figure 39.PowerSSO-24 package dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Figure 40.PowerSSO-24 tube shipment (no suffix) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Figure 41.PowerSSO-24 tape and reel shipment (suffix “TR”). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 4/37VNQ5E050AK-E Block diagram and pin configuration5/371 Block diagram and pin configurationTable 1.Pin functionsName FunctionV CCBattery connection.OUTPUT n Power output.GND Ground connection. Must be reverse battery protected by an external diode/resistor network.INPUT n Voltage controlled input pin with hysteresis, CMOS compatible. Controls output switch state.CURRENT SENSE n Analog current sense pin, delivers a current proportional to the load current.CS_DISActive high CMOS compatible pin, to disable the current sense pin.Block diagram and pin configuration VNQ5E050AK-E6/37Table 2.Suggested connections for unused and not connected pins Connection / pin Current sense N.C.Output Input CS_DIS Floating Not allowed X X X XT o groundThrough 1 kΩresistorXThrough 22 kΩresistorThrough 10 kΩresistorThrough 10 kΩresistorVNQ5E050AK-E Electrical specifications7/372 Electrical specificationsFigure 3.Current and voltage conventionsNote:V Fn = V OUTn - V CC during reverse battery condition.2.1 Absolute maximum ratingsStressing the device above the ratings listed in the “Absolute maximum ratings” tables may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to the conditions reported in this section for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.V FnI SI GNDV CCV CCOUTPUTnINPUTnV INnV SENSEnGNDCS_DISI CSDV CSDI INnCURRENTS ENSEnV OUTnI OUTnI SENSEnTable 3.Absolute maximum ratingsSymbol ParameterValue Unit V CC DC supply voltage 41V -V CC Reverse DC supply voltage 0.3V - I GND DC reverse ground pin current 200mA I OUT DC output currentInternally limitedA - I OUT Reverse DC output current 20A I IN DC input current-1 to 10mA I CSD DC current sense disable input current -1 to 10mA -I CSENSE DC reverse CS pin current 200mA V CSENSE Current sense maximum voltageV CC - 41 to +V CCV E MAXMaximum switching energy (single pulse)(L= 3mH; R L =0Ω; V bat =13.5V; T jstart =150ºC; I OUT = I limL (T yp.))104mJElectrical specificationsVNQ5E050AK-E8/372.2 Thermal dataSymbolParameterValueUnitV ESDElectrostatic discharge(Human Body Model: R=1.5K Ω; C=100pF)- INPUT- CURRENT SENSE - CS_DIS - OUTPUT - V CC40002000400050005000V V V V V V ESD Charge device model (CDM-AEC-Q100-011)750V T j Junction operating temperature -40 to 150°C T stgStorage temperature-55 to 150°CTable 3.Absolute maximum ratings (continued)Table 4.Thermal dataSymbol ParameterMax. valueUnit R thj-case Thermal resistance junction-case (with one channel ON) 2.8°C/W R thj-ambThermal resistance junction-ambientSee Figure 36.°C/WVNQ5E050AK-E Electrical specifications9/372.3 Electrical characteristicsValues specified in this section are for 8V<V CC <28V , -40°C< T j <150°C, unless otherwisestated.Table 5.Power sectionSymbol ParameterTest conditions Min.Typ.Max.Unit V CC Operating supply voltage 4.51328V V USD Undervoltage shutdown 3.5 4.5V V USDhystUndervoltage shutdown hysteresis0.5VR ON On state resistance (1)1.For each channelI OUT = 2A; T j = 25°C I OUT = 2A; T j = 150°CI OUT = 2A; V CC = 5V; T j = 25°C 5010065m Ωm Ωm ΩV clampClamp voltageI S = 20 mA414652VI SSupply currentOff State; V CC =13V; T j =25°C; V IN =V OUT =V SENSE =V CSD =0V On State; V CC =13V; V IN =5V; I OUT =0A2(2)82.PowerMOS leakage included.5(2)14µA mAI L(off)Off state output current (1)V IN =V OUT =0V; V CC =13V; T j =25°CV IN =V OUT =0V; V CC =13V;T j =125°C 000.0135µAV FOutput - V CC diode voltage (1)-I OUT =2A; T j =150°C0.7VTable 6.Switching (V CC =13V; T j = 25°C)Symbol Parameter Test conditions Min.Typ.Max.Unit t d(on)Turn-On delay time R L = 6.5Ω (see Figure 6.)20µs t d(off)Turn-Off delay timeR L = 6.5Ω (see Figure 6.)35µs (dV OUT /dt)on Turn-On voltage slope R L = 6.5ΩSee Figure 26.V /µs (dV OUT /dt)off Turn-Off voltage slope R L = 6.5ΩSee Figure 28.V /µs W ON Switching energy losses during t won R L = 6.5Ω (see Figure 6.)0.15mJ W OFFSwitching energy losses during t woffR L = 6.5Ω (see Figure 6.)0.25mJElectrical specifications VNQ5E050AK-E10/37Table 7.Logic inputsSymbol Parameter Test conditions Min.Typ.Max.Unit V IL Input low level voltage0.9VI IL Low level input current V IN= 0.9V1µAV IH Input high level voltage 2.1VI IH High level input current V IN= 2.1V10µAV I(hyst)Input hysteresis voltage0.25V V ICL Input clamp voltageI IN= 1mAI IN= -1mA5.5-0.77VV V CSDL CS_DIS low level voltage0.9VI CSDL Low level CS_DIS current V CSD= 0.9V1µAV CSDH CS_DIS high level voltage 2.1VI CSDH High level CS_DIS current V CSD= 2.1V10µA V CSD(hyst)CS_DIS hysteresis voltage0.25V V CSCL CS_DIS clamp voltageI CSD= 1mAI CSD= -1mA5.5-0.77VV Table 8.Protections and diagnostics (1)1.To ensure long term reliability under heavy overload or short circuit conditions, protection and relateddiagnostic signals must be used together with a proper software strategy. If the device is subjected toabnormal conditions, this software must limit the duration and number of activation cycles.Symbol Parameter Test conditions Min.Typ.Max.UnitI limHDC short circuitcurrentV CC=13V5V<V CC<28V19273838AAI limLShort circuit currentduring thermal cyclingV CC= 13V; T R<T j<T TSD7A T TSDShutdowntemperature150175200°C T R Reset temperature T RS + 1T RS + 5°C T RSThermal reset ofSTA TUS135°C T HYSTThermal hysteresis(T TSD-T R)7°C V DEMAGTurn-Off outputvoltage clampI OUT= 2A; V IN= 0; L= 6mH V CC-41V CC-46V CC-52VV ONOutput voltage droplimitationI OUT= 0.1A;T j= -40°C...150°C(see Figure 8.)25mVTable 9.Current sense (8V<VCC<18V)Symbol Parameter Test conditions Min.Typ.Max.UnitK0I OUT/I SENSE I OUT = 0.05A;V SENSE=0.5V; V CSD=0V;T j= -40°C...150°C105021103170K1I OUT/I SENSE I OUT=1A;V SENSE= 4V; V CSD=0V;T j= -40°C...150°CT j= 25°C...150°C151015101890189026502270dK1/K1(1)Current sense ratiodriftI OUT=1A; V SENSE= 4V;V CSD=0V;T J=-40 °C to 150 °C-1313%K2I OUT/I SENSE I OUT=2A;V SENSE= 4V; V CSD=0V;T j= -40°C...150°CT j= 25°C...150°C160016001800180022302000dK2/K2(1)Current sense ratiodriftI OUT=2A; V SENSE= 4V;V CSD= 0V;T J=-40 °C to 150 °C-88%K3I OUT/I SENSE I OUT=4A;V SENSE= 4V; V CSD= 0V;T j= -40°C...150°CT j= 25°C...150°C162016201770177019901920dK3/K3(1)Current sense ratiodriftI OUT= 4A; V SENSE= 4V;V CSD= 0V;T J=-40 °C to 150 °C-66%I SENSE0Analog senseleakage currentI OUT = 0A; V SENSE=0V;V CSD = 5V; V IN=0V; T j= -40°C...150°CV CSD = 0V; V IN=5V; T j= -40°C...150°CI OUT = 2A; V SENSE=0V;V CSD= 5V; V IN=5V; T j= -40°C...150°C121µAµAµAI OL Open load ON statecurrent detectionthresholdV IN = 5V, 8V<V CC<18VI SENSE= 5 µA420mAV SENSE Max analog senseoutput voltageI OUT= 4A; V CSD= 0V 5VV SENSEH Analog sense outputvoltage in faultcondition(2)V CC= 13V; R SENSE= 10KΩ8VI SENSEH Analog sense outputcurrent in faultcondition(2)V CC= 13V; V SENSE= 5V9mA11/37t DSENSE1H Delay response timefrom falling edge ofCS_DIS pinV SENSE<4V, 0.5A<Iout<4AI SENSE= 90% of I SENSE max(see Figure 4.)40100µst DSENSE1L Delay response timefrom rising edge ofCS_DIS pinV SENSE<4V, 0.5A<Iout<4AI SENSE= 10% of I SENSE max(see Figure 4.)520µst DSENSE2H Delay response timefrom rising edge ofINPUT pinV SENSE<4V, 0.5A<Iout<4AI SENSE= 90% of I SENSE max(see Figure 4.)80250µs∆t DSENSE2H Delay response timebetween rising edgeof output current andrising edge of currentsenseV SENSE<4V,I SENSE =90% of I SENSEMAX,I OUT=90% of I OUTMAXI OUTMAX=2A (see Figure7)60µst DSENSE2L Delay response timefrom falling edge ofINPUT pinV SENSE<4V, 0.5A<Iout<4AI SENSE= 10% of I SENSE max(see Figure 4.)80250µs1.Parameter guaranteed by design; it is not tested.2.Fault condition includes: power limitation, overtemperature and open load OFF state detection.Table 10.Open load detection (8V<VCC<18V)Symbol Parameter Test conditions Min.Typ.Max.UnitV OL Open load Off state voltagedetection thresholdV IN = 0V2SeeFigure 5.4Vt DSTKON Output short circuit to V ccdetection delay at turn OffSee Figure 5.1801200µsI L(off2)r Off state output current atV OUT = 4VV IN=0V; V SENSE=0VV OUT rising from 0V to 4V-1200µAI L(off2)f Off state output current atV OUT = 2VV IN=0V; V SENSE=V SENSEHV OUT falling from V CC to 2V-5090µAtd_vol Delay response from outputrising edge to V SENSE risingedge in open loadV OUT= 4 V; V IN= 0VV SENSE= 90% of V SENSEH20µsTable 9.Current sense (8V<VCC<18V) (continued)Symbol Parameter Test conditions Min.Typ.Max.Unit12/3713/37Figure 4.Current sense delay characteristicsFigure 6.Switching characteristics SENSE CURRENTINPUT LOAD CURRENT CS_DISt DSENSE2Ht DSENSE2Lt DSENSE1Lt DSENSE1H V OUTdV OUT /dt (on)t r80%10%t fdV OUT /dt (off)t d(off)t d(on)INPUTtt90%t Won t Woff14/37Figure 7.Delay response time between rising edge of ouput current and rising edge of current sense (CS enabled)Figure 8.Output voltage drop limitationV INI OUTI SENSEI OUTMAXI SENSEMAX 90% I SENSEMAX90% I OUTMAX∆t DSENSE2HtttVonIoutVcc-VoutTj=150o CTj=25o C Tj=-40o CVon/Ron(T)Note:Parameter guaranteed by design; it is not tested.15/3716/37Table 11.Truth tableConditionsInput Output Sense (V CSD =0V)(1)1.If the V CSD is high, the SENSE output is at a high impedance, its potential depends on leakage currentsand external circuit.Normal operation L H L H 0NominalOvertemperature L H L L 0V SENSEHUndervoltageL H L L00OverloadHH X(no power limitation)Cycling(power limitation)Nominal V SENSEHShort circuit to GND (Power limitation)L H L L 0V SENSEH Open load OFF State (with external pull-up)L H V SENSEH Short circuit to V CC (external pull-up disconnected)L H H H V SENSEH < NominalNegative output voltage clampLL17/37Table 12.Electrical transient requirementsISO 7637-2: 2004(E)Test pulseTest levels (1)1.The above test levels must be considered referred to V CC =13.5V except for pulse 5b.Number of pulses or test times Burst cycle/pulse repetition time Delays and impedanceIII IV Min.Max.1-75V -100V 5000 pulses 0.5s 5s 2 ms, 10Ω2a +37V +50V 5000 pulses0.2s 5s 50µs, 2Ω3a -100V -150V 1h 90ms 100ms 0.1µs, 50Ω3b +75V +100V 1h 90ms100ms0.1µs, 50Ω4-6V -7V 1 pulse 100ms, 0.01Ω5b (2)2.Valid in case of external load dump clamp: 40V maximum referred to ground.+65V+87V1 pulse400ms, 2ΩISO 7637-2:2004E Test pulseTest level resultsIII VI 1C C 2a C C 3a C C 3b C C 4C C 5b (2)CCClass ContentsC All functions of the device performed as designed after exposure to disturbance.EOne or more functions of the device did not perform as designed after exposure to disturbance and cannot be returned to proper operation without replacing the device.2.4 Waveforms18/3719/3720/37VNQ5E050AK-E Electrical specifications 2.5 Electrical characteristics curvesFigure 17.Off state output current Figure 18.High level input currentFigure 19.Input clamp voltage Figure 20.Input low levelFigure 21.Input high level Figure 22.Input hysteresis voltage21/37Electrical specifications VNQ5E050AK-E22/37Figure 23.On state resistance vs. TFigure 24.On state resistance vs. V Figure 25.Undervoltage shutdown Figure 26.Turn-On voltage slope Figure 27.Ivs. T Figure 28.Turn-Off voltage slopeVNQ5E050AK-E Electrical specifications Figure 29.CS_DIS high level voltage Figure 30.CS_DIS clamp voltageFigure 31.CS_DIS low level voltage23/37Application information VNQ5E050AK-E24/373 Application informationFigure 32.Application schematicNote:Channel 2, 3, 4 have the same internal circuit as channel 1.3.1 GND protection network against reverse batteryThis section provides two solutions for implementing a ground protection network againstreverse battery.3.1.1 Solution 1: resistor in the ground line (R GND only)This can be used with any type of load.The following is an indication on how to dimension the R GND resistor.1.R GND ≤ 600mV / (I S(on)max ). 2. R GND ≥ (−V CC ) / (-I GND )where -I GND is the DC reverse ground pin current and can be found in the absolutemaximum rating section of the device datasheet.Power Dissipation in R GND (when V CC <0: during reverse battery situations) is:P D = (-V CC )2/R GNDThis resistor can be shared amongst several different HSDs. Please note that the value of this resistor should be calculated with formula (1) where I S(on)max becomes the sum of the maximum on-state currents of the different devices.Please note that if the microprocessor ground is not shared by the device ground then the R GND will produce a shift (I S(on)max * R GND ) in the input thresholds and the status output values. This shift will vary depending on how many devices are ON in the case of several high side drivers sharing the same R GND .V CCGNDOUTPUTD GNDR GNDD ldΜCU+5VV GNDCS_DISIINPUTR protR protCURRENT SENSER protR SENSEC ext。

Kutai TCS4P125 Automatic Transfer Switch Control U

KUTAI ELECTRONICS INDUSTRY CO., LTD.TCS4P125Automatic Transfer SwitchControl Unit for 3 Phase 4 Wire SystemOperation ManualThree Phase Four Wire 4P 125 Amp Rated Voltage 250 VacPatent Number : U.S. Pat. No. 7,557,683TABLE OF CONTENTSSection PageSECTION 1 : INTRODUCTION1.1 Safety Precautions (3)1.2 Products Overview (3)SECTION 2 : HARDWARE DESCRIPTION2.1 Front Panel (4)2.2 TCS4P125 Dimensions (5)2.3 Panel Cut-Out For The TC-V2 (5)SECTION 3 : FUNCTION DESCRIPTION3.1 General (6)3.2 TDNE Setting (6)3.3 TDEN Setting (6)3.4 TDEC Setting (6)3.5 TDES Setting (6)3.6 TD-OFF Setting (6)3.7 Plant Exerciser (6)3.8 Over / Under Voltage Sensing (6)3.9 Transfer Failure (6)SECTION 4 : OPERATION4.1 General (7)4.2 AUTO Mode (7)4.3 TEST Mode (7)4.4 Programming Mode (7)4.5 AC Voltage Display Adjustment (7)4.6 Specification Summary (7)4.7 System Setting Reference Table (8)SECTION 5 : INSTALLATION INSTRUCTIONS5.1 General (9)5.2 Installation On The Plate (9)5.3 TC-V2 Installation On The Door Panel (10)SECTION 6 : TYPICAL WIRING6.1 TCS4P125 Standard Wiring Diagram (11)SECTION 1 : INTRODUCTION1.1 Safety Precautions (WARNINGS)This manual covers the installation, operation and maintenance of the TCS4P125 Automatic Transfer Switch. It is intended for qualified personal only.1.2 Products OverviewThe TCS4P125 automatic transfer switch consist of two parts the TS4P125 switch and the TC-V2 electronic control unit :1.2.1 TS125 FeaturesThe contacts on the Kutai TS4P125 transfer switch are class PC, this means that it is capable of making and withstanding short circuits but is not intended for breaking short circuit current.●Rated operating Voltage:250 Vac●Rated operating Current:125 Amps●Number of poles:4P●Coil operating voltage:110 / 220 Vac +/- 20%●Compact size, light weight and low powerconsumption.●Electrically operated and mechanically held.●Manufactured using UL 94V-0 plastics.●Adjustable time delay in OFF position whentransferring.●Designed for cell-phone repeaters, and manyindustrial and home ATS applications.1.2.2 TC-V2 Digital ControllerThe TC-V2 digital control unit offers programming flexibility to customize the ATS to different customer requirements.The Controller:●Monitor normal source for full phase over and undervoltages.●Monitor emergency source for single phase overand under voltages.●Normal & emergency source voltage and frequencyparameter display.●TDEN, TDNE, TDEC and TD-OFF real timecountdown display.●Permit testing the transfer switch from the controlpanel.●Permit system testing the transfer switch with orwithout load from the front panel.●Built-in 1 to 4 weeks exerciser timer.●Permit customer plant exerciser test with / withoutload on a preset period.●Safely store customer / factory settings inpermanent memory.●Shows status and failure alarm LED’s on the frontpanel.●No need for PC connection and programmingsoftware. All settings can be made on site.●Controller can be installed next to switch orseparately on an enclosure panel.SECTION 2 : HARDWARE DESCRIPTION 2.1 Front Panel2.2 TCS4P125 Dimensions (Unit : mm)2.3 Panel Cut-Out for the TC-V2 (Unit : mm)SECTION 3 : FUNCTION DESCRIPTION3.1 GeneralOperation of the TCS4P125 electronic control.3.2 TDNE SettingsTDNE provides a time delay when transferring from N ormal to E mergency. Timing begins when the Emergency Source (generator) becomes available. TDNE:Adjustable from 0 to 99 seconds.3.3 TDEN SettingsTDEN provides a time delay when transferring from Emergency to Normal. This permits stabilization of the Normal Power before transferring back to normal. Timing begins when the Normal Power returns and becomes available and steady.TDEN:Adjustable from 0 to 99 seconds.3.4 TDEC SettingsTDEC timer keeps the generator running without load (E ngine C ool-down) after the ATS transfer back to Normal Power. Timing begins when the transfer back to normal is completed.TDEC:Engine Cool-down - from 0 to 99 sec.3.5 TDES SettingTDES is the time delay for Engine Start when the Normal Source voltage is in over or under-voltage (OV or UV). If power return to normal while timing, the TDES timer resets and starts again.TDES:Adjustable from 0 to 30 seconds.3.6 TD-OFF SettingTime Delay on OFF this timer keeps the switch in the center neutral OFF position (completely disengaged) before transferring to the other side. You can preset the switch in Neutral or OFF from 0 to 18 seconds (Normally 2 to 3 sec).TD-OFF:Adjustable from 1 to 20 seconds.3.7 Plant ExerciserThis feature provides for automatic test operation of the generator. The interval is fixed at once per 1 to 4 weeks with a specific test day and time. The exerciser can be set for either testing with load or without load. When the exerciser is activated the exerciser LED (EX) on the right side of display flashes and turns on during the exercise period.3.8 Over / Under Voltage SensingThe TC-V2 constantly monitors normal & emergency power. When power falls outside the programmed voltages this LED turns RED from GREEN and flashing to show OV / UV problems.Adjustable over voltage range:110 - 280 VacOver voltage reset:When voltage falls below 10 Vac of the OV setting.Adjustable under voltage range:80 - 230 VacUnder voltage reset:When voltage exceeds 10 Vac of the UV setting.3.9 Transfer FailureWhen a transfer is made the TS125 communicates it’s position to the TC-V2 controller by using two small internal micro-switches, if this signal is not received, it will try switching 3 more times every 2 seconds or until the connection is made. A flashing light indicator and a “FAIL” signa l displayed an incomplete transfer and that the ATS mechanism or wiring is defective.If the ATS fails, the TC-V2 controller stops all ATS functions and starts’ flashing until the failure is corrected and the control is reset.To reset the transfer fail alarm:1. Manually move the ATS to the correct position.2. Press any button (Auto, Program or Test) on thefront panel to reset the alarm.SECTION 4 : OPERATION4.1 GeneralThis section specifically describes the operation and functional use of the TC-V2 controller.4.2 AUTO ModeIn AUTO the TC-V2 controller automatically transfer and retransfers from source to source as directed by the pre-programmed instructions.In AUTO the controller monitors the condition of both normal and standby power sources providing the logic for the transfer operation.4.3 TEST ModeThe TC-V2 is equipped with a test pushbutton that simulates the loss of normal source. Pushing the Test key the TC-V2 will execute a test on the ATS. The TDES and TDNE programmed time delays will be performed as part of the test. There are two test modes:●Testing with load .●Testing without load4.4 Programming ModeThe TC-V2 controller is fully programmable from the front panel when in the Program Mode. The build-in program buttons have multiple functions:●Real time clock displaying●Programming mode operatingTo enter programming mode, push and hold Program button for 10 seconds. In the first 10 seconds the screen showing internal real time clock and then the word “ Vr 1.0” will appears on the front display window for 2 seconds indicating the version of the software.At this time start a line by line programming sequence. To advance to the next line, push the Program button on the front panel. To change each line’s programming parameters, press the increase (∧) and decrease (∨) buttons. When pressing and releasing the (∧) or (∨) key the displayed parameter can be increased or decreased by one. The parameter will continue to scroll if the (∧) or (∨) button is pressed and not released. Always push the “ Program” button to advance to the next line or until the word “ End” appears on the screen. To immediately end the programming mode, you simply push the “ Program” button for 4 seconds. Then the word “ End” shows on the screen indicating the end of the programming mode.If you like to return to factory settings, stay in programming mode and simultaneously press all 3 buttons (∧), (∨) and Program buttons for 4 seconds. The TC-V2 will now automatically program itself to factory settings and the word “ Au.Po” will appear on the display window.4.5 AC Voltage Display AdjustmentThe TC-V2 controller continually monitors normal & emergency power displaying volts and frequency on the front panel. (The voltage value is calibrated and adjusted at the factory). But when the ATS works on high capacitive or inductive loads the waveform distortion may cause the displayed to have slight differences from the users measuring instrument.You can adjust the display value to equal to the users own instruments, by entering the setting mode to perform adjustment the parameter. Once the adjustment is completed, the voltage sensing value will increase or decrease according to the adjusted value and display it on the screen. The TC-V2 over and under voltage protection follow the adjusted value as the actual system voltage and perform the monitoring according to the new parameter.See Table lines 2, 3, 4, 5 for voltage display setting. 4.6 Specification Summary4.7 System Setting Reference TableSECTION 5 : INSTALLATION INSTRUCTIONS5.1 GeneralThe TC-V2 controller is modular and is designed for installation next to switch or on the front door panel. A longer harness is required for door installation.5.2 Installation On The Plate5.3 Installation On The Door PanelSECTION 6 : TYPICAL WIRING6.1 TCS4P125 Standard Wiring Diagram (110 or 220V)___________________________________________________________________________________________ TCS4P125(TC-V2)11。

2012培训教材-轻中卡操纵部分解析

3

2012年培训教材

2012年培训教材

轻卡变速器操纵部分大致相同(见图1),不同的地 方在于使用不同变速器时所用的软轴固定支架、软轴及挡 位标牌不同,见表1。

4

2012年培训教材

2012年培训教材

图1

5

2012年培训教材

变速器型号 HW20505TCL HW24505TCL 布置型式 变速器左操纵 变速器左操纵 变速器左操纵 HW25505TCL 变速器右操纵 软轴 选LG9704240010(2400) 手柄 LG9704240026 LG9704240003 LG9704240003 LG9704240002 软轴支架 LG9704240032 LG9704240032 LG9704240011 LG9704240019

2012年培训教材

2012年培训教材

轻型卡车变速器操纵部分结构简介

技术中心 2012年2月

2012年培训教材

2012年培训教材

2012年培训教材

2012年培训教材

目前我公司轻卡系列车型变速器操纵采用双软轴操纵, 该结构布置方便,结构简单,便于模块化装配。 通过优化设计,合理布置软轴走向,支架结构简单,重 量轻。 挡位清晰,换选挡力度适中。

2012年培训教材

26

2012年培训教材

2012年培训教材

图7

27

2012年培训教材

(6)软轴及气管走向与固定

2012年培训教材

轻卡系列车型使用的软轴最小转弯半径为200mm,因此

在固定软轴时要避免软轴直径小于200mm。软轴使用扎带固 定,避免和其他运动部件磨碰、干涉,尽可能远离排气管。 装HW50508C变速器时气管顺着软轴进入驾驶室,和软轴捆绑 在一起。

[精品]人体断层解剖学

![[精品]人体断层解剖学](https://img.taocdn.com/s3/m/73d930a9bed5b9f3f80f1c69.png)

• (五)第六脑室(verga腔、穹隆室) • 位于透明隔间腔后方的间隙,在第五脑室

后方

• 前界:第五脑室 • 后界:胼胝体压 • 上界:胼胝体干 • 下界:穹窿体

• 脑池

• 蛛网膜下隙在脑的沟裂处扩大而形成的蛛 网膜下池,临床称为脑池。

• 成对:大脑纵裂池、大脑外侧窝池、环池

•

脑桥小脑角池、池(中间帆腔) 、大脑大静脉池

•

小脑上池、小脑延髓池、小脑溪、

•

四叠体池、胼胝体周池

• 腹侧:延髓池、桥池、脚间池、交叉池、终板池

•

•

•

• 成对

• 1、大脑纵裂池:位于大脑纵裂内,大脑镰 两侧,向前下连于终板池,向后下续于大 脑大静脉池。

• 2、大脑外侧窝池:位于额叶眶回与颞极之 间的外侧沟的前端,内容大脑中A。

• 中央部:伸入顶叶,顶为胼胝体,内侧为 透明隔,底为穹窿、背侧丘脑

• 后角:伸入枕叶,顶和外侧壁为胼胝体, 内侧壁上部为胼胝体枕钳形成的后角球, 下部为距状沟内陷形成的禽距

• 下角:伸入颞叶,顶为胼胝体、尾状核尾 和杏仁体,底为海马、海马伞和侧副隆起

• (二)、第三脑室 • 位于两侧间脑之间,呈矢状位的狭窄腔隙 • 顶为:脉络丛 • 底为:下丘脑 • 前壁: 前连合和终板 • 后壁:缰连合和松果体 • 侧壁:背侧丘脑

• 5、终板池:位于终板前方,胼胝体嘴的下 方。

• *鞍 上池:蝶鞍上方的交叉池、脚间池、桥 池合称为鞍上池。池内有基底A环、鞍背、 垂体柄与漏斗、视交叉、视束。

YXUMx7EXXD)1N&P0T)ECXtj oH1Dc YBcT kL#$MdsiSYyJj pZR)zl oF+Cb#Gl)D1pys4ux9uiKBZIT k7gGc&XY&3cj

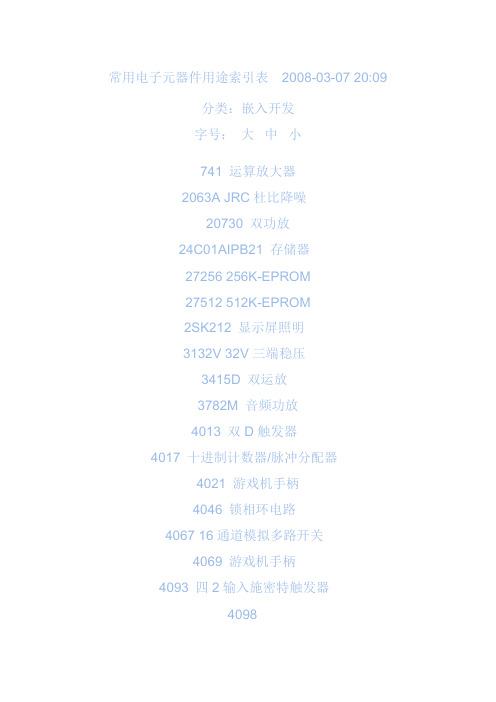

常用电子元器件用途索引表2008

常用电子元器件用途索引表2008-03-07 20:09分类:嵌入开发字号:大中小741 运算放大器2063A JRC杜比降噪20730 双功放24C01AIPB21 存储器27256 256K-EPROM27512 512K-EPROM2SK212 显示屏照明3132V 32V三端稳压3415D 双运放3782M 音频功放4013 双D触发器4017 十进制计数器/脉冲分配器4021 游戏机手柄4046 锁相环电路4067 16通道模拟多路开关4069 游戏机手柄4093 四2输入施密特触发器409841256 动态存储器52432-01 可编程延时电路56A245 开关电源5G0401 声控IC5G673 八位触摸互锁开关5G673 触摸调光5G673 电子开关6116 静态RAM6164 静态RAM65840 单片数码卡拉OK变调处理器7107 数字万用表A/D转换器74123 单稳多谐振荡器74164 移位寄存器7474 双D触发器7493 16分频计数器74HC04 六反相器74HC157 微机接口74HC405374HCU04 六反相器74LS00 与门74LS00 4*2与非门74LS00 四2与非门74LS00 与门74LS04 6*1非门74LS08 4*2与门74LS11 三与门74LS123 双单稳多谐振荡器74LS123 双单稳多谐振荡器74LS138 三~二译码器74LS142 十进制计数器/脉冲分配器74LS154 4-16线译码器74LS157 四与或门74LS161 四2计数器74LS161 十六进制同步计数器74LS161 四~二计数器74LS164 数码管驱动74LS18 射频调制器74LS193 加/减计数器74LS193 四2进制计数器74LS194 双向移位寄存器74LS27 4*2或非门74LS32 四或门74LS32 4*2或门74LS374 八位D触发器74LS374 三态同相八D触发器74LS37774LS48 7位LED驱动74LS73 双J-K触发器74LS74 双D触发器74LS85 四位比较器74LS90 计数器75140 线路接收器75141 线路接收器75142A 线路接收器75143A 线路接收器7555 时钟发生器79MG 四端负稳压器8051 空调单片机8338 六反相器A1011 降噪ACVP2205-26 梳状滤波视频处理AD536 专用运放AD558 双极型8位D-A(含基准电压)变换器AD558 双极型8位D-A(含基准电压)变换器AD574A 12比特A/D变换器AD650AD670 8比特A/D变换器(单电源)1995s-2、15 AD7523 D-A变换器1994x-125AD7524 D-A变换器1994x-126AD7533 模数转换器1994x-141AD7533 模数转换器1995s-184ADC0804 8比特A/D变换器1995s-2、20ADC0809 8CH8比特A/D 1995s-2、23ADC0833 A/D变换4路转换器1995s-2ADC80 12比特A/D变换器1995s-2、8 ADC84/85 高速12比特A/D变换器1995s-2 AG101 手掌游戏机1993x-155AM6081 双极型8位D-A变换器1994x-127 AMP1200 音频功放皇后1993s-104AN115 立体声解码1991-135AN2510S 摄象机寻象器1994x-109AN2661NK 影碟机视频1995s-45AN2662K 时基校正(模拟)1995s-45AN2664FBP 影碟机视频1995s-45AN2664NK 影碟机视频1995s-45AN2870 影碟机伺服1995s-45AN3100N 射频调制器1991-55AN362 立体声解码1991-135AN363N 立体声解码1991-135AN3890FBS 影碟机主轴电机驱动1995s-45 AN3891FBP 影碟机主轴电机驱动1995s-45 AN5026K 红外接收1993x-106AN51354 中放/音频/视频解调1994s-255 AN5138K 图象通道1994-308AN5265 音频功放1994s-298AN5342K 亮度锐度加强电路1994s-243 AN5344FBP CFU地1995s-274AN5352 模拟开关1994-245AN5515 彩电场输出1995s-34AN5515 场输出1994-73AN5521 场输出电路1991-203AN5521 场输出1994-73AN5521 场输出1994-240AN5521 场扫描1994-308AN5600K 图象处理1994-308AN5612 色差解调1994s-245AN5652 伴音中放1994-308AN5862K PIP切换输出1994s-245AN6551 双运放1991-54AN6612 电机稳速1992-63AN6612S 杜比降噪1995s-43 AN6650 电机稳速1991-183AN6650 电机稳速1992-7AN6650 电机稳速1992-83 AN6650 电机稳速1992-127 AN6650 电机稳速1993s-165AN6913L 双运放1995s-85 AN7106K 单片放音机1992-63 AN7108 单片放音机1992-7 AN7108 单片放音机1992-127 AN7108 单片放音机1992-136 AN7108 单片放音机1993s-165 AN7110 音频功放1994x-107 AN7112E 音频功放1994s-39AN7158N 音频功放1991-3 AN7158N 音频功放1991-203 AN7168 双音频功放1991-195 AN7178 音频功放1994x-107 AN7188NK 双音频功放1992-14 AN7311 双前置放大1991-195 AN7315 双前置放大1992-99 AN7410 立体声解码1991-135AN74LS293 1994x-93AN7812 三端稳压器1994s-299AN78N05 三端稳压器1994s-298AP500/A DC功放驱动1995s-60AP500/A 双声道DC功放驱动1995s-156 AT24C01 存储器1994x-46ATC105 充电控制1993x-191 AX5212D 微机鼠标编码1994s-183 BA1035B 高速运放1994x-94BA1106F 放音前置放大及功放1995s-43 BA1310 立体声解码1991-135BA1320 立体声解码1991-135BA1330 立体声解码1991-135BA1335 立体声解码1991-135BA1404 调频发射1994x-183BA3015 电风扇电脑1994s-162BA3105 电风扇电脑1994x-58BA3212N 录放前置1994-180BA328 双前置放大1991-43BA328 低噪前置1992-58BA328 双声道前置放大1995s-189 BA3506 音频功放1991-139BA3822LS 5段均衡1994-180BA508 遥控电路1995s-171BA5102 音频前置1993x-108BA5102 遥控电风扇编码1995s-119 BA5104 电风扇遥控1995s-183BA527 音频功放1991-168BA5302 红外接收头1995s-183 BA5406 双功放1992-47BA6124 电平指示1991-31BA6209 录象机加载1991-11BA6209 主导电机驱动1994-192 BA6219B 加载电机驱动1994-120 BA6227 电机稳速1991-139BA6303 磁鼓控速1992-139BA6439P 主导电机驱动1994-120 BA728 双运放1992-91BA7751LS 录象机音频处理1993s-84 BA8105 遥控电风扇电路1995s-119 BA8206A4 电风扇控制1995s-183 BAS3108T FM发射1992-94 BGJ3302 四运放电压比较器1994-25 BH-SK-I 声控IC 1994s-175BH-SK-V 声控IC 1994x-74BISS0001 红外传感信号处理1995s-182 BL3102 时钟频率脉冲1994s-255BL3207 BBD延时1994s-255BL50462AP 遥控编码与发射1995s-299 BM5060 彩电CPU 1994-308BM5067 彩电CPU 1995s-212BM5069 彩电CPU 1995s-212BTS114 感温高速开关管1992-34BTS115 感温高速开关管1992-34BTS130 感温高速开关管1992-34BTS131 感温高速开关管1992-34BTS240 感温高速开关管1992-34BTS412 电源开关模块1992-112C036 4*2与非门1993s-93C043 双D触发器1993s-101C066C 4*2与非门1993x-147C1225H 音响驱动1992-198C1470 电机稳速1992-99C1490HA 红外接收1991-110C1676 超高频放大1995s-199C1891A 环绕声处理器1992-24C7642 单片收音机1991-95CA3069 运放1994x-184CA3160 1994x-188CA3193 音频运放1994x-36CA3524 脉冲调制1992-14CC14433 三位半A/D转换1991-46CC14433 三位半A/D转换1991-174CC4093 含施密特触发器的四2输入与非门1994s-44 CC4511 七段译码器1991-46CCU3000-17 从属微处理器1995s-299CCU3002-FDTV-11 彩电CPU 1995s-299CD1403 单运放1991-2CD4001 4*2或非门1993s-69CD4001 4*2或非门1994x-2CD4011 4*2与非门1993s-53CD4011 4*2与非门1993x-150CD4011 四2输入与非门1994s-80CD4013 双D触发器1991-2CD4013 双D触发器1993s-101CD4013 双D触发器1993x-6CD4013 双D触发器1994s-82CD4013 双D触发器1994x-22、54CD4017 十进制计数/分配1991-110CD4017 十进制计数/分配1993s-142CD4017 十进制计数译码器1994s-82 CD4017 十进制计数器/脉冲分配器1994s-34 CD4017 十进制计数器/脉冲分配器1994x-2 CD40174 六D触发器1992-130 CD4017B 十进制计数/分配1993x-173CD4017B 十进制计数器1995s-184CD40193B 双向可预置可逆计数器1994x-84 CD4020 14级二进制计数器1994s-80 CD4024 七位二进制串行计数器1994s-80 CD4028 二~十进制译码器1992-98CD4035 移位寄存器1994s-72CD4040 十二进制二进制计数器1992-22 CD4040 十二进制二进制计数器1993s-207 CD4040 12级二进制计数器1993x-125CD4040 12级二进制计数器1994s-80 CD4046 锁相环电路1994x-188CD4046 锁相环电路1995s-181CD4051 模拟开关1992-130 CD4051 模拟多路转换器1995s-2、35CD4052 四选一模拟开关1992-82CD4053 3*2模拟开关1992-62、207CD4053 3*2模拟开关1994x-54CD4053 3*2模拟开关1994x-126CD4053B TV/AV切换1994-219CD4053B 双向模拟开关1994-247CD4060 分频计数1993s-12CD4060 十四位计数器/分配器/振荡器1994s-30、40 CD4066 4*2模拟开关1992-112CD4066 4*2模拟开关1993s-91CD4066BE 四路模拟开关1994-269CD4067 模拟多路转换器1992-162CD4067 模拟多路转换器1995s-2CD4069 6*1非门1991-166CD4069 6*1非门1993s-45CD4069 6*1非门1993x-150CD4069 六非门1994s-4、82CD4071 4*2或门1994s-30CD4072 2-4输入或门1992-130CD4075 三或门1991-170CD4078 多输入或门1991-170CD4093 四与非门施密特触发器1994x-42 CD4099 8路可寻址锁存器1991-170CD4510 二~十加减计数器1992-98 CD4511 LED显示驱动1991-2CD4511 译码驱动1993x-159CD4511 译码显示1994s-30CD4514 4-10线译码器1993x-158CD4518 双二~十进制计数器1993x-125 CD4518 计数器1994s-30CD4541B 双D触发器1995s-79CD4553 三位BCD码计数器1993s-47 CD74206 音频功放1994x-107 CD9020-002 字符产生器1994s-255 CD9135 六路互复位触摸开关1994x-188 CE550 电风扇控制1994s-170CH1058 音乐片1991-192CH208 译码输出1991-174CH220 电子密码锁1994x-26CIC7642 调幅收音1994s-55CIC9140 电话按键码1993s-107 CNX82A2 稳压反馈光电耦合器1995s-299 CP4027 双J-K触发器1993s-109CS839 霍尔开关1994s-34CS8704 电话振铃1994-46CSC5089 单片电话机1994-77CTC9140 电话脉冲拨号1994-46CU001 多功能遥控1991-56CU47C433AN-002 彩电CPU 1994s-255 CW-18 呼救语音1993x-133CW8403 音乐IC 1993s-125CW9300 音乐IC 1993s-101CW9300 音乐IC 1993x-198CX20029 单片收音机1992-111CX20106 红外接收1993s-126CX20106 红外接收1994-230CX20106A 红外预放器1991-30CX20106A 红外接收1994x-22CX20111 调频调幅中放1992-127CX20112 电视立体声/多语种解码1994x-4 CX20188 杜比B/C降噪1992-174CX522-054 彩电CPU 1994s-302CX7959 存储器1994s-307CXA1019 单片收音机1991-114CXA1019 单片调频收音1991-152CXA1019 调频静噪1995s-52CXA1019M 单片收音机1994-74CXA1019P 单片调频收音1993x-85CXA1034P 单片放音机1992-83CXA1100 杜比降噪1991-106CXA1101 杜比降噪1991-106CXA1101 杜比降噪1992-108CXA1102 杜比降噪1991-106CXA1145P 游戏机色处理1991-131CXA1145P PAL编码1993x-78CXA1191M 调幅调频电视单片收音1993x-158 CXA1191M 单片收音机1994s-198 CXA1191M 单片调频调幅收音1994x-63 CXA1191P 收音专用1994-11CXA1238 单片收音机1991-140CXA1238M 调频收音1994s-130CXA1238M 调频收音1994s-156CXA1250 场频驱动1993x-103CXA1262N 单片放音机1993x-99CXA1315M 彩电副总线1995s-272CXA1642 消歌声1993s-64CXA1642 消声(卡拉OK)1995s-36CXA1642 消歌声1995s-204CXA1644P 卡拉数字延时1993x-72CXA1735S 音频处理器1995s-272CXA8008P 单片放音机1991-75CXA8008P 单片收音机1992-163CXD1254AQ 摄象机同步1993x-103CXD1310BLA 视频处理器1993x-103CXK1001P 存储器1994-307CXP80420-139S 彩电CPU 1994-334D1130 AM/FM收音1992-43D2024 音频功放1991-48D2283 音频低放1994s-135D2283 音频功放1994x-47D2822 助听器专用1991-167D414 单片收音机1991-167D7176AP 中放及伴音鉴频1994-19D7240AP 音频功放1991-3D75028CW 空调器CPU 1995s-194D7796 音频均衡1991-32DAC08 双极型8位D-A变换器1994x-129DAC08 双极型8位D-A变换器1994x-135DAC90 双极型8位D-A(含基准电压)变换器1994x-126 DBL2004 彩电场输出1995s-34DCM0016 系列高速带掉电保护RAM 1995s-174DCM0064 系列高速带掉电保护RAM 1995s-174 DCM0256 系列高速带掉电保护RAM 1995s-174 DCM8128 系列高速带掉电保护RAM 1995s-174 DJ2001 洗衣机电脑1991-159DN888 数字延迟1993x-110DPU-2553-25 偏转处理器1995s-299DRAM4164 数据存储1993s-80DS8629N 100分频器1992-22 DTI-2260 数字瞬态改善处理器1995s-299EA1062 语音电路1994-138EK001 混频厚膜1994s-255ELM742A 低压低功耗电压比较器1995s-118 ET91210 电话程控1991-58F1212 程序快门1992-71GL7488P 录象机伺服系统1994-210GP605 开关电源PWM脉宽调制1995s-126 GS8200 录象机系统控制1994-210GSE-3568 多音声效片1994s-128 GY65839 单片卡拉OK专用1994s-172 GY9308 DDC数码延迟1993x-120GY9403 数码卡拉OK延迟1994x-52H9081 四声5闪光片1994x-167HA11227 立体声解码1991-135HA112A 音乐门铃1991-156HA11414 行场扫描1993s-28HA11489 亮度/彩色矩阵1991-203HA11489 视频处理1994x-19HA11509N 亮/色/行场扫描1991-43HA1166Z 黑白机行场扫描1994-82HA12017 放音均衡1991-8HA12058 杜比降噪1993x-160HA12102 双前置放大1991-43HA13001 音频功放1993s-75HA13119 音频功放1994x-99HA1392 音频功放1992-188HA1397 音频功放1991-176HA3302 四运放电压比较器1994-25HA51338SP 亮/色/行场扫描1991-43HA51338SP 彩电行场扫描/色度/亮度1995s-163 HCF40015 红外接收前置放大1994s-118HD14053B 电视遥控发射1993x-164HD401304 彩电CPU 1995s-174HD401314 彩电CPU 1995s-174HD44007A 彩色同步1991-14HEF4017 2-10进制计数器/脉冲分配器1994x-22 HEF4053BP 3*2模拟开关1994s-7HEF4066B 四路模拟开关1994-269HEF4503 3*2模拟开关1992-207HF-268/288 保密语音模块1995s-94HFC3030 彩灯闪光片1994x-71HFC3040 多发光二极管控制1991-64HFC3040 彩灯六路闪光芯片1994s-50HFC5203A 语音1994x-90HFC5219 “有电危险、请勿靠近”语音块1995s-95 HIC101 放象机电源厚膜块1995s-85HM50256 动态存储器1995s-159HM50464 动态存储器1995s-159HM511000 动态存储器1995s-159HM6117 游戏存储1993s-11HM6232 电源厚膜1993x-35HM6401 电源/场输出厚膜1991-115HM7101 电源厚膜1993x-35HM7942 电源厚膜1993x-35HM8951 电源厚膜1993s-35HM8951A 电源厚膜1995s-99HM8951B 电源厚膜1993x-195HM8951B 电源厚膜1994-65HM9007 电子镇流器1991-82HM9007 电子镇流器1993s-146HM9102 电源厚膜1992-103HM9102 电源厚膜1993x-35HM9102 开关电源取样1994-141HM9102D 电话按键码1993s-107 HM911L 热释电红外线探测1994x-194 HM9201 电源厚膜1993x-35HM9205 稳压电源取样1994-332 HM9207 电源厚膜1993s-3HM9207 电源厚膜1994-65HM9207B 电子镇流器1994s-6HM-JL1 音频模块1993s-160HN6401 电源厚膜1993x-35 HPC177C 四运放电压比较器1994-25 HPC339C 四运放电压比较器1994-25 HT12C 遥控发射1994x-110HT2880 八音音乐片1994s-32HT6337A 风扇遥控接收1994x-110 HT7713 声控闪光片1994x-10HT7713 触摸调光1994x-63HT82D 双音音乐门铃1994s-32 HY12503 可程式化语音模块1995s-94HY-20A 语音录放1994s-78HY42503 可程式化语音模块1995s-94HY-88A 动物叫声效片1993x-182HY8-S 三端音乐片1991-172IC1818P 单片游戏机1993s-95IC7107 三位半A/D转换器1993x-181ICL7107 三位半A/D驱动1993s-62ICL7107 三位半模/数转换器1994s-80ICL7107 DVM三位半A/D 1995s-2、21 ICL7109 积分型12比特A/D变换器1995s-2 ICL7139 自动量程万用表1992-42ICL7660 双直流变换1993s-62ICL7660 DC-DC变换器1995s-39、68 ICL8038 函数发生器1994x-112 ICL8211 欠压检测用IC 1995s-40、89ICM7555 时基电路1995s-46ICM7556 时基电路1995s-40ICWJ9301 电脑密码锁1994s-190ICX045BLA 1/3寸CCD图象传感器1993x-103 IR2155 日光灯电子镇流模块1995s-38IR3M02 微机开关电源1994s-109IR3M03A DC-DC变换1992-86IR3M03A DC-DC变换1993s-119 ISD1000A 系列单片语音录放IC 1995s-174 ISD1100 系列单片语音录放IC 1995s-174 ISD1400 系列单片语音录放IC 1995s-174 ISD2500 系列单片语音录放IC 1995s-174 IVR1601 一次性编程语音1993s-159 IX0238CE 场输出1994-73IX0250CE 音频功放1994-73IX0256CE 开关电源1994-73IX0308 电源厚膜1992-127IX0308CZ 电源厚膜1994-67IX0323CD 电源厚膜1994s-3IX0323CE 电源厚膜1994-33IX0324CFNI 行场扫描/色解码1994-34 IX0355CE 场输出1994-73IX0465CE 开关电源1994-73IX0517CE 开关电源1994-73IX0640CE 场输出1994-73IX0689CE 电源厚膜1994-48IX0711CE 彩电中放1994-73IX0711CEN 图象中放1994x-83IX0712CE 亮/色/行场扫描1994-73IX0712CEN1 扫描/解码1994-96IX0933CE 彩电CPU 1994-96JU0114 电源厚膜1991-155JU0114 彩电电源厚膜块1995s-43、51 JU0116 电源厚膜1994-66K2356 语音保密1992-178KA2184A 红外预放器1991-30KA2184A 红外线接收预放1991-56KA2184A 红外接收1993s-126KA2184A 红外接收放大1993x-170 KA2209 音频功放1993x-43KA22134 音频功放1994x-83KA2221 双前置放大1991-43KA22429 调频收音1994s-55KA2402 电机稳速1993x-99KA2402 电机稳速1995s-131KA2407 电机稳速1993x-43KA2410 电话振铃1994x-11KA2410 电话振铃1994-138KA2915 单片黑白电视机1993s-167KAC4558 双运放1991-71KD-07 闪光灯、音乐集成块1995s-71 KD-100 音乐IC 1993x-5KD-152B 音乐IC 1993x-189KD-155 口哨声控片1995s-183KD-253 “叮咚”门铃1994x-194KD-253B “叮咚”门铃1994s-62KD-254 音乐片1994s-143KD482FB 石英钟报时1991-4KD-482FC 钟控打点1993s-142 KD483 程控双音打点石英钟1994s-175 KD5068 狗叫声音乐片1993x-126 KD5105 电子爆竹1993s-38KD-5601 爆竹声1993x-189KD56010 “恭喜发财”语音片1994x-138 KD56012 鸟叫声1993s-157KD56012 鸟叫IC 1994x-143KD-5602 军号声音乐片1995s-191 KD5603 “欢迎光临”语音片1991-62 KD5603 欢迎光临1993s-142KD-5603 “欢迎光临”语音片1994s-63KD56032 六秒自然声1995s-143KD56033 娃娃哭笑语音块1995s-103 KD5604 谢谢光临1993s-142KD-5608 “狗叫”音乐片1992-168KD9300 音乐门铃1991-156KD9300 音乐门铃1994s-138KD9300 音乐门铃1994x-2、34KD9561 警车声音乐片1992-68KD9561 音乐IC 1994x-42KD9562B 警报声音乐1993x-52KD9562C 八声声效片1992-10KH1668 风扇控制1994x-154KIA6227H 音频功放1994-346KIA6299H 音频功放1994x-107KIA6401 电话振铃1994x-11KIA7299P 音频功放1994s-51KIA75558P 录象机伺服系统1994-210 KIA8125S 音频前置放大1994s-51KIA8127F AM/FM中放1994-180 KM41C64P-10 画中画DRAM 1995s-299 KS5194/5 液晶显示驱动1994x-66KS5803 红外遥控发射1991-56KS5803 红外发射1992-95KS5917 语音电路1993s-183L200 五端集成稳压器1994s-110 L4960 开关电源脉宽调制1995s-102 L4962 开关电源脉宽调制1995s-102 L4962 脉宽调制器1995s-152L4964 开关电源脉宽调制1995s-102 L4970 开关电源脉宽调制1995s-102 L4974 开关电源脉宽调制1995s-102 L78MR05 1994-240LA1231N FM解调1991-35LA1260 调频、调幅收音1994-104 LA3160 双前置放大1991-43LA3160 前置放大1994-340LA3350 立体声解码1991-135LA3361 立体声解码1991-66LA3361 立体声解码1991-135LA3365 立体声解码1991-135LA4127 双前置放大1993x-83LA4140 音频功放1993x-91LA4140 音频功放1994-137LA4275 音频功放1994s-255LA4422 音频功放1994-73LA4445 音频功放1991-67LA4445 音频功放1991-203LA4445 音频功放1993x-27LA4597 音频功放1993x-27LA5110 彩电稳压电源1995s-187LA5112 彩电稳压电源1995s-187LA5511 电机稳速1991-3LA5515 电机稳速1991-3LA5521D 电机稳速1995s-131LA7016 制式切换1995s-299LA7299 音频功放1991-67LA7555 中频信号处理1995s-342 LA7575 PLL同步检波中频解码1995s-299LA7680 图象/伴音中频/视放/解码1994-273、302 LA7830 场输出电路1991-203LA7830 场输出电路1992-39LA7830 场输出1994-73LA7832 彩电场输出1995s-27LA7832/33 场输出1994s-255LA7837 场输出1994s-299 1995-62LA7838 场输出1994-268LA7905 50Hz/60Hz识别1994s-255LA7910 波段开关1994-248LA7920 波段开关1994s-307LAG665 单片放音机1991-132LAG665 单片放音机1991-199LAG665 单片放音机1992-47LAG665 随身听IC 1994s-20LAG665 单片放音机1994x-83LAG665F 单片放音机1993x-109LAG665F 单片立体声放音1995s-12LB1405 电平指示1993x-154LB1407 电平指示1995s-55LC219 风扇红外遥控发射1993x-170LC219 红外发射编码1994-230LC220A 六路译码器1993x-170LC220A 红外译码1994-230LC4036 双向模拟开关1994s-255LC4066B 四路模拟开关1994-269LC7441 PIP系统控制1994s-245LC7444 双时钟发生器1994s-245LC7480 多路转换开关和模/数转换器1994s-245 LC7881 D/A转换1992-124LCL102 计程显示器1994s-34LD398C 卫视接收厚膜块1993x-157LD505 音频放大1992-141LD866A 雷达探测模块1994s-63LD866B 雷达探测模块1994s-63LF398 取样与保持1995s-2、29LH-169B “抓贼呀”语音片1994s-7LIC1149-5 降压控制器1994s-104LM010 1994x-192LM1035 音量、平衡、音调直流控制1993s-32 LM1036 音量、平衡、音调直流控制1993s-32 LM1040 音量、平衡、音调直流控制1993s-32LM12 运放1995s-30LM134 1994x-192LM1851N 漏电检测1994x-42LM1875 运算放大器1991-36LM1875 音频功放1994s-68LM1894 杜比降噪1991-106LM1894 动态降噪1991-200LM1894 降噪1993s-90LM1894 动态降噪1993s-170LM2575 开关电源脉宽调制1995s-102LM258 双前置放大1993x-43LM2904CT 三端稳压器1994s-168LM2907/2917 频率/电压转换器1994s-199 LM293X 低压差三端稳压器1995s-41LM311 专用运放比较器1994x-18LM317 三端可调稳压电源1991-103LM317 三端可调稳压电源1993s-124LM317 三端可调稳压电源1994s-4LM317 正压可调三端稳压1995s-39LM317T 可调三端稳压1991-186LM318N 高速运放1994x-128LM3272C 石英钟芯1992-35LM331 V/F变换器1995s-2、37LM337 负压可调三端稳压1995s-39、46LM339N 四运放电压比较器1994-25 LM3524A 开关电源脉宽调制1995s-102LM358 双运放1992-8LM358P 运放1995s-299LM358PS 录象机主导放大整形1994-120 LM35DZ 温度传感1992-198LM385 小功率基准电压1995s-39、60、76 LM386 音频功放1991-168LM386 音频功放1993s-6、77LM386N 音频功放1994x-90 LM3875T 单片功放1993s-146 LM3875T 音频功放1993x-144 LM3876T 单片功放1993s-146 LM389 调频发射1992-70LM3900 电流型四运放1994s-199 LM3909 单片振荡器1995s-63LM3909N 闪烁灯1995s-88LM3914 电平显示1993x-22LM3915 显示驱动1994x-16LM4280 音频功放1995s-299 LM567 频率解调1991-2LM567 音频解调1991-62LM567 红外音频解调1991-134 LM567 红外音频解调1994x-2 LM567 红外音频解调1994x-119 LM567 调频发射、接收1995s-143 LM6181 视频放大1994x-7LM723 通用型稳压块1994s-79 LM833 双运放1993s-170LM8361 数字钟1994x-162LM837 四运放1993s-170LMC1982 数控音响1993s-178LP167 环形脉冲分配/驱动1994s-122LP2950CZ 低压差5V稳压器(三端)1995s-88 LQ46 四合一语音片1992-76LQ46 语音片1994x-162LR3714AM 遥控发射1993x-156LR40993 电话机发号1995s-111LR6 低压线性稳压器1995s-94LS190 对数放大器1994x-77LS7232 触摸调光1991-100LS7232 触摸调光1993s-94LS7232 触摸调光1994x-142LS85 1994x-77LT1005 逻辑控制稳压器1995s-39LT1057 音频运放1991-120LT1073 充电检测控制1994s-56LT1173CS8 DC-DC变换器1994x-8。

MMSZ4xxxT1G系列和SZMMSZ4xxxT1G系列零点电阻电源器件的商品说明书

MMSZ4686T1G MMSZ4686T1G.MMSZ4xxxT1G Series, SZMMSZ4xxxT1G Series Zener Voltage Regulators 500 mW, Low I ZT SOD−123 Surface MountThree complete series of Zener diodes are offered in the convenient, surface mount plastic SOD−123 package. These devices provide a convenient alternative to the leadless 34−package style.Features•500 mW Rating on FR−4 or FR−5 Board•Wide Zener Reverse V oltage Range − 1.8 V to 43 V•Low Reverse Current (I ZT) − 50 m A•Package Designed for Optimal Automated Board Assembly •Small Package Size for High Density Applications•ESD Rating of Class 3 (>16 kV) per Human Body Model•SZ Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q101 Qualified and PPAP Capable•These Devices are Pb−Free and are RoHS Compliant*Mechanical Characteristics:CASE:V oid-free, transfer-molded, thermosetting plastic case FINISH:Corrosion resistant finish, easily solderableMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES: 260°C for 10 SecondsPOLARITY:Cathode indicated by polarity band FLAMMABILITY RATING:UL 94 V−0MAXIMUM RATINGSRating Symbol Max Units Total Power Dissipation on FR−5 Board,(Note 1) @ T L = 75°CDerated above 75°C P D5006.7mWmW/°CThermal Resistance, (Note 2) Junction−to−Ambient R q JA340°C/WThermal Resistance, (Note 2) Junction−to−Lead R q JL150°C/WJunction and Storage Temperature Range T J, T stg−55 to+150°CStresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.FR−5 = 3.5 X 1.5 inches, using the minimum recommended footprint.2.Thermal Resistance measurement obtained via infrared Scan Method.*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.Cathode AnodeSee specific marking information in the device marking column of the Electrical Characteristics table on page 3 of this data sheet.DEVICE MARKING INFORMATIONSOD−123CASE 425STYLE 1Device Package Shipping†ORDERING INFORMATIONMARKING DIAGRAM†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.MMSZ4xxxT1G SOD−123(Pb−Free)3,000 /Tape & ReelMMSZ4xxxT3G SOD−123(Pb−Free)10,000 /Tape & Reel xx= Device Code (Refer to page 3)M= Date CodeG= Pb−Free Package(Note: Microdot may be in either location)1SZMMSZ4xxxT1G SOD−123(Pb−Free)3,000 /Tape & ReelSZMMSZ4xxxT3G SOD−123(Pb−Free)10,000 /Tape & ReelELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 0.9 V Max. @ I F = 10 mA)Symbol ParameterV Z Reverse Zener Voltage @ I ZTI ZT Reverse CurrentI R Reverse Leakage Current @ V RVR Reverse VoltageI F Forward CurrentV F Forward Voltage @ I FProduct parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 0.9 V Max. @ I F = 10 mA)Device*DeviceMarkingZener Voltage (Note 3)Leakage CurrentV Z (Volts)@ I ZT I R @ V RMin Nom Max m A m A VoltsMMSZ4678T1G CC 1.71 1.8 1.89507.51 MMSZ4679T1G CD 1.90 2.0 2.105051 MMSZ4680T1G CE 2.09 2.2 2.315041 MMSZ4681T1G CF 2.28 2.4 2.525021 MMSZ4682T1G CH 2.565 2.7 2.8355011 MMSZ4683T1G CJ 2.85 3.0 3.15500.81 MMSZ4684T1G CK 3.13 3.3 3.47507.5 1.5 MMSZ4685T1G CM 3.42 3.6 3.78507.52 MMSZ4686T1G CN 3.70 3.9 4.105052 MMSZ4687T1G CP 4.09 4.3 4.525042 SZMMSZ4687T1G CG6 4.09 4.3 4.525042 MMSZ4688T1G CT 4.47 4.7 4.9450103 MMSZ4689T1G CU 4.85 5.1 5.3650103 MMSZ4690T1G/T3G CV 5.32 5.6 5.8850104 MMSZ4691T1G CA 5.89 6.2 6.5150105 MMSZ4692T1G CX 6.46 6.87.145010 5.1 MMSZ4693T1G CY7.137.57.885010 5.7 MMSZ4694T1G CZ7.798.28.61501 6.2 MMSZ4695T1G DC8.278.79.14501 6.6 MMSZ4696T1G DD8.659.19.56501 6.9 MMSZ4697T1G DE9.501010.505017.6 MMSZ4698T1G DF10.451111.55500.058.4 MMSZ4699T1G DH11.401212.60500.059.1 MMSZ4700T1G DJ12.351313.65500.059.8 MMSZ4701T1G DK13.301414.70500.0510.6 MMSZ4702T1G DM14.251515.75500.0511.4 MMSZ4703T1G†DN15.201616.80500.0512.1 MMSZ4704T1G DP16.151717.85500.0512.9 MMSZ4705T1G DT17.101818.90500.0513.6 MMSZ4706T1G DU18.051919.95500.0514.4 MMSZ4707T1G DV19.002021.00500.0115.2 MMSZ4708T1G DA20.902223.10500.0116.7 MMSZ4709T1G DX22.802425.20500.0118.2 MMSZ4710T1G DY23.752526.25500.0119.0 MMSZ4711T1G†EA25.652728.35500.0120.4 MMSZ4712T1G EC26.602829.40500.0121.2 MMSZ4713T1G ED28.503031.50500.0122.8 MMSZ4714T1G EE31.353334.65500.0125.0 MMSZ4715T1G EF34.203637.80500.0127.3 MMSZ4716T1G EH37.053940.95500.0129.6 MMSZ4717T1G EJ40.854345.15500.0132.6 3.Nominal Zener voltage is measured with the device junction in thermal equilibrium at T L = 30°C ±1°C.*Include SZ-prefix devices where applicable.†MMSZ4703 and MMSZ4711 Not Available in 10,000/Tape & ReelTYPICAL CHARACTERISTICSV Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θV Z , NOMINAL ZENER VOLTAGE (V)Figure 1. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ100101V Z , NOMINAL ZENER VOLTAGE (V)Figure 2. Temperature Coefficients (Temperature Range −55°C to +150°C)1.21.00.80.60.40.20T, TEMPERATURE (5C)Figure 3. Steady State Power Derating P p k, P E A K S U R G E P O W E R (W A T T S )PW, PULSE WIDTH (ms)Figure 4. Maximum Nonrepetitive Surge PowerP D , P O W E R D I S S I P A T I O N (W A T T S )V Z , NOMINAL ZENER VOLTAGEFigure 5. Effect of Zener Voltage onZener ImpedanceZ Z T , D Y N A M I C I M P E D A N C E ()ΩTYPICAL CHARACTERISTICSC , C A P A C I T A N C E (p F )V Z , NOMINAL ZENER VOLTAGE (V)Figure 6. Typical Capacitance 1000100101V Z , ZENER VOLTAGE (V)1001010.10.01I Z , Z EN E R C U R R E N T (m A )V Z , ZENER VOLTAGE (V)1001010.10.01I R , L E A K A G E C U R R E N T (A )μV Z , NOMINAL ZENER VOLTAGE (V)Figure 7. Typical Leakage Current10001001010.10.010.0010.00010.00001I Z , Z E N E R C U R R E N T (m A )Figure 8. Zener Voltage versus Zener Current(V Z Up to 12 V)Figure 9. Zener Voltage versus Zener Current(12 V to 91 V)SOD−123CASE 425−04ISSUE GDATE 07 OCT 2009SCALE 5:1NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: INCH.DIM MIN NOM MAXMILLIMETERSINCHESA0.94 1.17 1.350.037A10.000.050.100.000b0.510.610.710.020c1.600.150.055D 1.40 1.80E 2.54 2.69 2.840.100---3.680.140L0.253.860.0100.0460.0020.0240.0630.1060.1450.0530.0040.0280.0710.1120.152MIN NOM MAX3.56H E---------0.006------------GENERICMARKING DIAGRAM**For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT**This information is generic. Please refer to device datasheet for actual part marking. Pb−Free indicator, “G” ormicrodot “ G”, may or may not be present.XXX= Specific Device CodeM= Date CodeG= Pb−Free Package1STYLE 1:PIN 1. CATHODE2. ANODE0.910.036ǒmminchesǓSCALE 10:1------q001010°°°°(Note: Microdot may be in either location) MECHANICAL CASE OUTLINEPACKAGE DIMENSIONSON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor theON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.PUBLICATION ORDERING INFORMATIONTECHNICAL SUPPORTNorth American Technical Support:Voice Mail: 1 800−282−9855 Toll Free USA/Canada Phone: 011 421 33 790 2910LITERATURE FULFILLMENT :Email Requests to:*******************ON Semiconductor Website: Europe, Middle East and Africa Technical Support:Phone: 00421 33 790 2910For additional information, please contact your local Sales RepresentativeMMSZ4686T1G MMSZ4686T1G.。

半导体气敏元件

MQ-K4型半导体气敏元件

规格书

深圳市鸿瑞泰电子有限公司

2013年4月20日

一、性能规格

1、型号名称:MQ-K4型半导体气敏元件

2、适用范围:产品主要用于天然气检漏、监控、报警装置及智能化集中燃

气泄漏报警系统中作传感元件。

3、外形尺寸:

4、主要技术指标:

1.清洁空气中电压:V0 ≤1.5V

2.标定气体中电压:V1 ≥2.5V (0.5%甲烷中)

3.响应时间:≤30秒

4.恢复时间:≤60秒

5.回路电压:Vc=5V

6.灯丝电压:Vh=5V±0.1

7.灯丝电阻:34Ω±5Ω 8.负载电阻:RL=1K-10K可调

5、测试电路

二、试验条件:

A、稳定性:连续使用范围24小时为一个周期,每周期内气敏元件

在洁净空气中负载电阻RL上电压降漂移<±15%。

B、元件使用寿命连续通电工作可达五年以上。

C、环境条件:

1.环境温度:-10℃--+45℃

2.相对湿度:90%

3.大气压力:650—800mmHg。

三、使用注意事项:气敏元件开始工作时,在没有遇到可燃气体时其电导率也将增加,经过3-5分钟左右,电导率下降到一个基本稳定值,这时方可工作。

四、不良品的处置方式:不合格品全部退换。

五、品质保证承诺:严格按需方标准供货。

六.供应商自检项目:

1.清洁空气中电压:V0 ≤1.2(清洁空气)

2.标定气体中电压:V1≥2.6V(0.1%丁烷中)

3.响应时间:≤30秒

4.恢复时间:≤60秒。

KM416V4104CS-45资料

Refresh Timer Refresh Control Refresh Counter

Row Decoder

DQ0 to DQ7

Memory Array 4,194,304 x 16 Cells

OE DQ8 to DQ15

tRAC

45ns 50ns 60ns

tCAC

12ns 15ns 17ns

tRC

(400mil TSOP(II)) *(N.C) : N.C for 4K Refresh Product

Pin Name A0 - A12 A0 - A11 DQ0 - 15 VSS RAS UCAS LCAS W OE VCC N.C

Pin function Address Inputs(8K Product) Address Inputs(4K Product) Data In/Out Ground Row Address Strobe Upper Column Address Strobe Lower Column Address Strobe Read/Write Input Data Output Enable Power(+3.3V) No Connection

74ns 84ns 104ns

tHPC

17ns 20ns 25ns

A0~A12 (A0~A11)*1 A0~A8 (A0~A9)*1

Row Address Buffer Col. Address Buffer Column Decoder

Note) *1 : 4K Refresh

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

LM.NT774.A Specification

LCD Monitor Control Board Specification 平板显示器驱动板规格书Customer (客户):Product Type (产品型号): LM.NT774.ADate Issued (发布日期): 2013-6-20UNE.20.2013Content(目录)1. General Description(概述) (1)2. Function Layout(产品外观图) (2)3.Configuration & General Precautions(使用注意事项) (2)4. Product Features(产品特性) (3)5. PCB Dimension(产品结构图) (4)6. Interface Definition (接口定义) (5)7. Environmental Characteristics(环境特性要求) (9)7.1Temperature(环境温度) (9)7.2 Humidity(环境湿度) (9)7.3 Altitude(海拔高度) (9)7.4 High Temperature & Storage(高温负荷与存储) (9)7.5 Low Temperature & Storage(低温负荷与存储) (9)7.6 Humidity &Temperature Test(潮热试验) (9)7.7 Vibration Test(振动试验) (10)7.8 Drop Test(跌落试验) (10)1.General Description(概述)LM.NT774.A* is a Monitor control board for LCD/LED which resolution is up to 1920*1200. It supports VGA、DVI and HDMI/MHL inputs, and supports VGA signal of horizontal synchronization signal range from 30 to 80 KHz, vertical synchronization signal range from 56 to 75 Hz.LM.NT774.A*是一款液晶显示器驱动板,支持1920*1200及以下分辨率的液晶面板,支持VGA、DVI和HDMI/MHL输入,可支持行频在30-80KHz,场频在56-75Hz范围内的信号。

VF-Ti60F225-T产品手册说明书

《VF-Ti60F225-T产品手册》易灵思钛金16nm 60K FPGA开发板芯片介绍参数描述功能介绍尺寸介绍Demo介绍资料介绍套餐介绍实物演示u联系我们手册目录FPGA主芯片 系列介绍Trion系列FPGA40nm钛金系列FPGA16nm易灵思FPGAT20T35T55T85T120无DDR IP无MIPI CSI无DDR IP有MIPI CSI有DDR IP有MIPI CSI有DDR IP有MIPI CSI/DSI Ti35Ti60硬核DDR IP硬核MIPI IP Ti180Ti60F225I3 FPGA介绍供应商奥唯思 科技核心板型号VF-Ti60F225-CFPGA厂家易灵思(国产FPGA)钛金(Titanium) 系列FPGA型号Ti60F225I3FPGA资源60K 逻辑单元,集成DDR3/MIPI软核,160个DSP DDR3存储4G 16bit DDR3:K4B4G1646E PCBA尺寸40mm *40mmPCB工艺6层 1.6mm 沉金 绿色/亚黑板载FLASH 64Mbit SPI FLASH :W25Q64JWSSIQ 核心板外设1个USB供电口,8个测试LED2个用户按键,1个硬复位按键其他接口板载ZH1.25-6 JTAG下载口B2B接口2个0.5mm双排80P山谷道B2B接插件(母座*2)供电集成USB Mini供电口 | B2B接插件输入5V DC发烧设计,极致尺寸;工匠品质,为FPGA而生。

40m m40m mTi60F255I3易灵思FPGADCDC 电源模块8bit LED0.5mm双排80P 山谷道B2B接插件DDR3 16bit 4GbZH1.25-6JTAG下载口USB-Mini口仅供电24MHz晶振25MHz晶振2位用户按键64Mbit SPI-FLASH W25Q64JWSSIQ 1bit硬件复位按键【4*4cm极小尺寸】开供应商奥唯思 科技开发板型号VF-Ti60F225-TFPGA厂家易灵思(国产FPGA)钛金(Titanium) 系列FPGA型号Ti60F225I3FPGA资源60K 逻辑单元,集成DDR3/MIPI软核,160个DSP PCBA尺寸长 110mm * 宽 80mmPCB工艺4层 1.6mm 黑色 沉金 工艺核心板外设1)8个LED灯2)2个独立按键 + 1个硬复位按键3)1个ZH1.25-6 JTAG下载口底板外设1)1个USB串口(CH340N)2)DC3-40 40P 用户接口3)1路HDMI 1.4显示接口(FPGA驱动)4)1路LVDS LCD接口(1024*600显示屏)5)1路DVP相机接口(兼容奥唯思 科技所有DVP模组)6)1路MIPI RX接口(CSI/DSI 1.5Gbps)7)1路MIPI TX接口(CSI/DSI 1.5Gbps)备注MIPI RX+TX需要转接板16nm工艺,高速低功耗小尺寸FPGA u 集成DDR3/MIPI软核IPu 主打 MIPI CSI 1.5G 相机采集解决方案;u 主打 MIPI DSI 1.5G LCD显示解决方案;110mm80m mDVP摄像头接口(兼容奥唯思科技所有DVP相机)DCDC 电源模块1024x600LVDS LCD接口HDMI1.4接口4位用户独立按键USB串口(CH340N)IDC3-10JTAG下载口5V DC500供电接口电源开关DC3-40P用户接口(3.3V)8bit用户LED灯74HC595串转并驱动VF-Ti60F225-C 易灵思FPGA核心板MIPI TX/RX接口CSI/DSI 1.5GbpsFPGA开发板 尺寸/3D视图介绍FPGA开发板 基础Demo介绍分类工程名称FPGA工程介绍基础工程01_LED_8bit_Test LED流水灯测试实验(核心板)02_KEY_2bit_Test独立按键测试实验(核心板)03_FPGA_UART_Test_Bottom UART串口测试实验(底板)04_RGBLCD_Test_800480UART串口测试实验(底板)05_LVDS_LCD_Test_1024600800*480 RGB LCD屏幕显示实验05_MIPI_LCD_Test_10246001024*600 MIPI DSI屏幕显示实验07_Ti60_HDMI_1080P_Lvds_Test1920*1080@60 HDMI屏幕显示实验FPGA开发板 图像Demo介绍分类工程名称FPGA工程介绍图像工程01_Ti60_AR0135_HDMI_1280720基于AR0135 DVP相机的HDMI屏720P实时成像案例02_Ti60_AR0135_LCD-RGB_800480基于AR0135 DVP相机的RGB屏(800*480)实时成像案例03_Ti60_AR0135_LCD-LVDS_1024600基于AR0135 DVP相机的LVDS屏(1024*600)实时成像案例04_Ti60_AR0135_LCD-DSI_1024600基于AR0135 DVP相机的MIPI DSI屏(1024*600)实时成像案例05_Ti60_SC130GS_MIPIx4_HDMI_1280720基于SC130S MIPI 4lane相机的HDMI屏720P实时成像案例06_Ti60_SC130GS_MIPIx4_LCD-RGB_800480基于SC130S MIPI 4lane相机的RGB屏(800*480)实时成像案例07_Ti60_SC130GS_MIPIx4_LCD-LVDS_1024600基于SC130S MIPI 4lane相机的LVDS屏(1024*600)实时成像案例08_Ti60_SC130GS_MIPIx4_LCD-DSI_1024600基于SC130S MIPI 4lane相机的MIPI DSI屏(1024*600)实时成像案例完整的 MIPI CSI/DSI 解决方案,成熟的案例及量产经验!VF-Ti60F225易灵思FPGA主板FPGA下载器可选多种DVP模组SC130GS 彩色/黑白130万1/3寸1024*600 MIPI DSI液晶屏1024*600 LVDS液晶屏SC200AI 彩色200万1/3寸可选多种MIPI模组FPGA开发板 DVP/MIPI采集显示解决方案奥唯思FPGA官微奥唯思 技术支持官方网站: 资料下载: 官方淘宝: “奥唯思FPGA ” 店铺FPGA论坛: 851598171奥唯思FPGA交流群1。

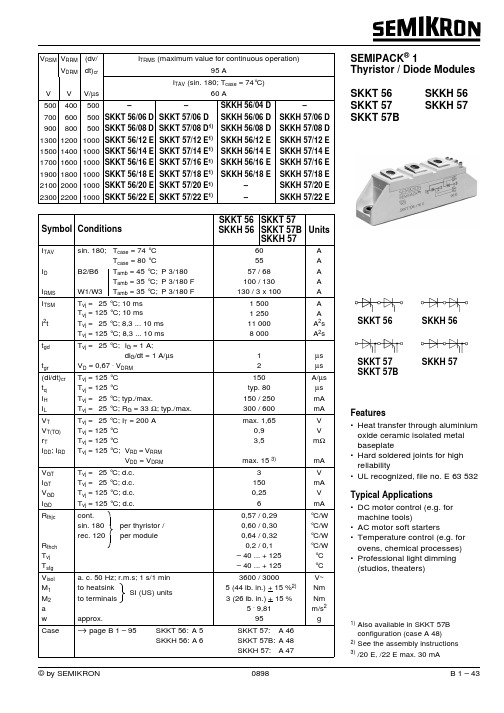

KT56中文资料

© by SEMIKRON 0898 B 1 – 43V RSM V RRM (dv/I TRMS (maximum value for continuous operation)V DRM dt)cr 95 AI TAV (sin. 180; T case = 74°C)V V V/µs60 A500700900130015001700190021002300400600800120014001600180020002200500500500100010001000100010001000–SKKT 56/06 D SKKT 56/08 D SKKT 56/12 E SKKT 56/14 E SKKT 56/16 E SKKT 56/18 E SKKT 56/20 E SKKT 56/22 E –SKKT 57/06 DSKKT 57/08 D 1)SKKT 57/12 E 1)SKKT 57/14 E 1)SKKT 57/16 E 1)SKKT 57/18 E 1)SKKT 57/20 E 1)SKKT 57/22 E 1)SKKH 56/04 D SKKH 56/06 DSKKH 56/08 D SKKH 56/12 E SKKH 56/14 E SKKH 56/16 E SKKH 56/18 E–––SKKH 57/06 D SKKH 57/08 D SKKH 57/12 E SKKH 57/14 E SKKH 57/16 E SKKH 57/18 E SKKH 57/20 E SKKH 57/22 ESymbol ConditionsSKKT 56SKKH 56SKKT 57SKKT 57B SKKH 57UnitsI TAV I D I RMS sin. 180;T case = 74 °CT case = 80 °CB2/B6T amb = 45 °C;P 3/180T amb = 35 °C;P 3/180 FW1/W3T amb = 35 °C;P 3/180 F 605557 / 68100 / 130130 / 3 x 100A A A A A I TSM i 2t T vj = 25 °C; 10 ms T vj = 125 °C; 10 msT vj = 25 °C; 8,3 ... 10 ms T vj = 125 °C; 8,3 ... 10 ms 1 5001 25011 0008 000A A A 2s A 2s t gd t gr T vj = 25 °C;I G = 1 A;di G /dt = 1 A/µsV D = 0,67 . V DRM12µs µs (di/dt)cr t q I H I L T vj = 125 °C T vj = 125 °CT vj = 25 °C; typ./max.T vj = 25 °C; R G = 33 Ω; typ./max.150typ. 80150 / 250300 / 600A/µs µs mA mA V TV T(TO)r TI DD ; I RD T vj = 25 °C; I T = 200 A T vj = 125 °C T vj = 125 °CT vj = 125 °C;V RD = V RRMV DD = V DRM max. 1,650,93,5max. 15 3)V V m ΩmA V GT I GT V GD I GD T vj = 25 °C; d.c.T vj = 25 °C; d.c.T vj = 125 °C; d.c.T vj = 125 °C; d.c.31500,256V mA V mA R thjcR thch T vj T stg cont.sin. 180per thyristor / rec. 120per module0,57 / 0,290,60 / 0,300,64 / 0,320,2 / 0,1– 40 ... + 125– 40 ... + 125°C/W °C/W °C/W °C/W °C °C V isol M 1M 2a w a. c. 50 Hz; r.m.s; 1 s/1 min to heatsinkto terminals approx.3600 / 30005 (44 lb. in.) + 15 %2)3 (26 lb. in.) + 15 %5 . 9,8195V~Nm Nm m/s 2gCase→ page B 1 – 95SKKT 56:A 5SKKT 57: A 46SKKH 56:A 6SKKT 57B:A 48SKKH 57: A 47SEMIPACK ® 1Thyristor / Diode Modules SKKT 56SKKH 56SKKT 57SKKH 57SKKT 57BFeatures•Heat transfer through aluminium oxide ceramic isolated metal baseplate•Hard soldered joints for high reliability•UL recognized, file no. E 63 532Typical Applications•DC motor control (e.g. for machine tools)•AC motor soft starters•Temperature control (e.g. for ovens, chemical processes)•Professional light dimming (studios, theaters)1)Also available in SKKT 57B configuration (case A 48)2)See the assembly instructions 3)/20 E, /22 E max. 30 mASKKT 56SKKT 57SKKT 57BSKKH 56SKKH 57SI (US) units© by SEMIKRON© by SEMIKRON B 1 – 45© by SEMIKRON© by SEMIKRON SKKT 19 . . . 105Case A 5SEMIPACK ® 1IEC 192-2: A 77 A JEDEC: TO-240 AAUL recognized, file no. E 63 532SKKT 20/ . . . 106/Case A 46SEMIPACK ® 1IEC 192-2: A 77 A JEDEC: TO-240 AADimensions in mmDimensions in mmSKKD 26 . . . 100Case A 10SKNH 56 . . . 91Case A 7SKKH 26 . . . 105Case A 6SKKL 56 . . . 105Case A 9SKND 46 . . . 81Case A 19SKMT 92Case A 72SKKE 81Case A 12SKKH 27 . . . 106Case A 47SKKT 20 B . . . 106 B Case A 48SKKL 42 . . . 106Case A 59。

454FTB系列100525中文版

应用场合

■ 工业气体的流量测量 ■ 美国EPA(环保局)颁布的大气污染法规中烟道气的流量测量 ■ 通风空气流量和化解过程中废气流量测量 ■ 溶剂回收系统流量测量 ■ 水泥厂生产过程中气体流量测量 ■ 压缩空气流量测量 ■ 半导体工艺气体测量 ■ 美国能源部空气取 样

■ 助燃气体流量测量 ■ 火炬气流量测量 ■ 焚烧炉烟气流量测量 ■ VOC烟道气流量测量 ■ 燃煤锅炉中助燃空气流量测量 ■ 天然气和大多数的工业气体流量测量 ■ 核电站 ■ O.E.M.应用

传感器材质:

标准配置: 哈氏合金C-276; 可选配: (1) 哈氏合金C-276材质传感器上涂氮化铬,更加耐磨损 (2) 在哈氏合金C-276传感器和传感器支撑杆上涂PTFE,耐腐蚀 但涂PTFE的HHT传感器:最高温度260℃

传感器支撑杆材质

316L 不锈钢, 可选配哈氏合金C-276;

重复性: 0.25% 流速响应时间:

气体标定

用户可选择实验室标定或相关气体标定。Kurz(S) 400D 型 NIST 可追踪风洞测量仪可用于空气标定。

传感器的保护

6

454FTB 的电路包括防止因传感器,电线或器件损坏而造成温度过高现象的保护电路。在零流量时,我们的传感器不会过热, 这与大部分竞争对手的设备不同,这是因为我们有与众不同的恒温传感器的控制方法和功率限制设计。

对于每种质量流量计型号pn编号和每种气体类型的基准流速v是指在标准状态下的最大流速方程式气体类型drp方程式drp10空气氮气氧气氩气1059drp12drp1353drp18drp30drp1000基本代码表使用定义说明方程式drppppsxtstp方程式在表2中所列的基准流速sfpm英制单位nmps公制单位vpht高温工作型号40hht超高温工作型号40fd2快速双铠装全焊接结构速度和温度传感器直径0105传感器探头ni无火花型atexcsa认证xpfp防爆隔爆型csa和atex认证ta一体型传感器和变送器于一体ts分体型传感器和变送器分别独立安装间距可调气体组号和气体类型气体组号气体类型氢气11vmax对于某种工艺条件下特定气体的最大流速流量因子ts标准绝对温度537r77f460英制单位

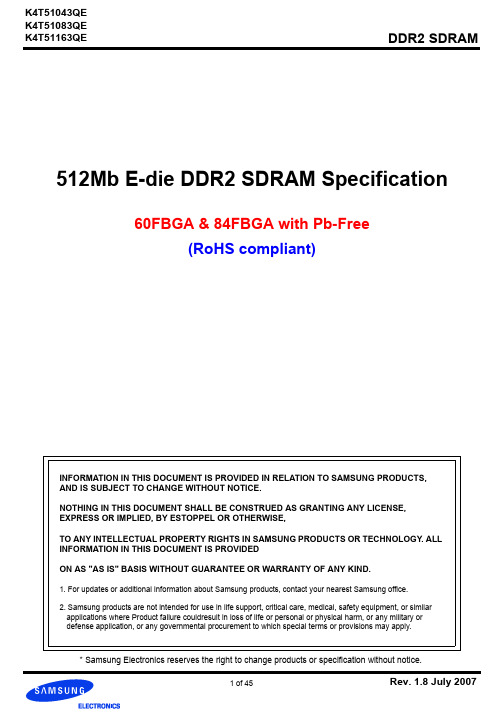

K4T51043QE资料