DAC5688中文资料

TLV5638中文数据手册

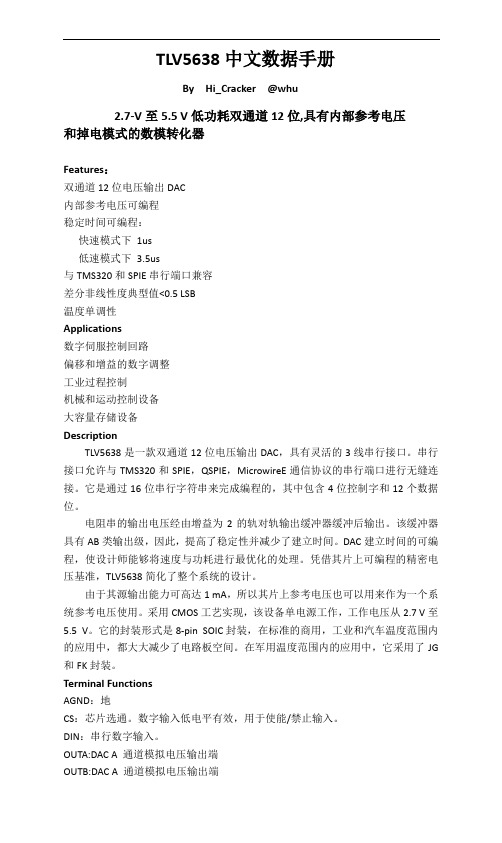

TLV5638中文数据手册By Hi_Cracker @whu2.7-V至5.5 V低功耗双通道12位,具有内部参考电压和掉电模式的数模转化器Features:双通道12位电压输出DAC内部参考电压可编程稳定时间可编程:快速模式下1us低速模式下3.5us与TMS320和SPIE串行端口兼容差分非线性度典型值<0.5 LSB温度单调性Applications数字伺服控制回路偏移和增益的数字调整工业过程控制机械和运动控制设备大容量存储设备DescriptionTLV5638是一款双通道12位电压输出DAC,具有灵活的3线串行接口。

串行接口允许与TMS320和SPIE,QSPIE,MicrowireE通信协议的串行端口进行无缝连接。

它是通过16位串行字符串来完成编程的,其中包含4位控制字和12个数据位。

电阻串的输出电压经由增益为2的轨对轨输出缓冲器缓冲后输出。

该缓冲器具有AB类输出级,因此,提高了稳定性并减少了建立时间。

DAC建立时间的可编程,使设计师能够将速度与功耗进行最优化的处理。

凭借其片上可编程的精密电压基准,TLV5638简化了整个系统的设计。

由于其源输出能力可高达1 mA,所以其片上参考电压也可以用来作为一个系统参考电压使用。

采用CMOS工艺实现,该设备单电源工作,工作电压从2.7 V至5.5 V。

它的封装形式是8-pin SOIC封装,在标准的商用,工业和汽车温度范围内的应用中,都大大减少了电路板空间。

在军用温度范围内的应用中,它采用了JG 和FK封装。

Terminal FunctionsAGND:地CS:芯片选通。

数字输入低电平有效,用于使能/禁止输入。

DIN:串行数字输入。

OUTA:DAC A 通道模拟电压输出端OUTB:DAC A 通道模拟电压输出端REF:模拟参考电压输入输出端SCLK:数字串行时钟输入端VDD:供电电压输入端APPLICATION INFORMATIONgeneral functionTLV5638是一个双12位通道,基于串式电阻结构的单电源供电DAC。

电气自动化技术《DAC0832的内部结构及引脚功能》

• 输出电流线性度可在满量程下调节; • 逻辑电平输入与TTL电平兼容; • 单一电源供电〔+5V~+15V〕; • 低功耗,20mW。

D1 6 D0 7 VREF 8 Rfb 9 DGND 10

DAC0832

20 Vcc 19 ILE 18 WR2 17 XFER 16 D4 15 D5 14 D6 13 D7 12 IOUT2 11 IOUT1

D7~ D0 8位数字量输入信号

其中: DI0为最低位,DI7为最高位

IOUT1 模拟电流输出端1 当输入数字为全〞1〞时, 输出电 流最大; 全〞0〞时, 输出电流为0。

IOUT2 模拟电流输出端2

IOUT1 I OUT2 = 常数

第四页,共七页。

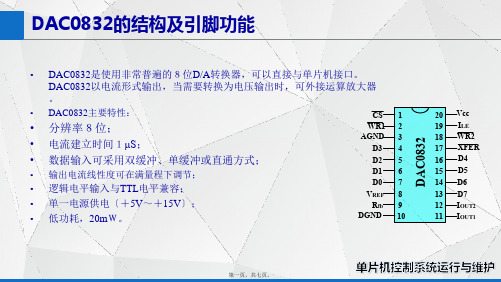

DAC0832的结构及引脚功能

CS

1

WR1 2

AGND 3

WR2 写信号2,低电平有效

第五页,共七页。

谢谢观看

第六页,共七页。

内容总结

DAC0832是使用非常普遍的8位D/A转换器,可以直接与单片机接口。DAC0832以电流形 式输出,当需要转换为电压输出时,可外接运算放大器。V cc 芯片电源电压, 5V~15V。当输 入数字为全〞1〞时, 输出电。全〞0〞时, 输出电流为0。D7~ D0 8位数字量输入信号。其中: DI0为最低位,DI7为最高位。ILE 输入锁存允许信号, 高电平有效。CS 片选信号, 低电平有效。 谢谢观看

第一页,共七页。

DAC0832的结构及引脚功能

DI7~DI0

ILE

CS WR1 XFER WR2

8位 输入 寄存器

LE

&

&

8位 DAC 寄存器

中频处理部分

中频处理子系统引言11.1 引入●软件无线电的关键技术:第一,需要研究一个开放式、可扩展、标准化的软件、硬件平台结构。

第二,需要研究实现适合于软件无线电系统的高性能射频、数字信号处理器件。

第三,需要研究适合于软件无线电的多波段、多速率、多模式信号接收理论和实现方法。

●一方面由于软件无线电在高中频甚至是在射频进行数字化,这样可以减少摹拟环节,使得前端引入的噪声更少,信号失真更小,电路更简洁、软件无线电和普通的窄带接收机相比,瞬时处理的带宽更宽,动态范围更大、可扩展性更好。

●另一方面目前市场上的A/D转换器的采样频率不能达到射频所发射的频率,因此涉及到变频至中频。

1.2 作用●完成高速ADC、高速DAC、数字下变频(DDC)、数字上变频(DUC)功能;●芯片通过监控子系统进行配置才干正常工作,实现摹拟信号和数字基带信号的互相转换●数字上变频(DUC)和数字下变频(DDC)功能逐渐由FPGA来实现;使用FPGA既可以实现载波选频产品,也可以实现宽带选频产品;2组成2.1 ADC前端驱动电路-常用器件2.1.1 Transformer包含两类:普通的transformer或者baluna)无源器件,不会给ADC前端带来额外的噪声,影响ADC SNR性能的测量;b)可以有效地隔离信号源地直流分量;c)使用不同匝数比的transformer,可以方便地实现升压或者降压d)应用电路简单,调试方便;2.1.2 有源器件(运放等)a)可以提供增益输入,但是由于是有源器件,产生的噪声会影响到ADC的SNR性能;b)外围电路较复杂,设计时需要考虑运放的输出阻抗、setting time 等指标与ADC 芯片的接口;c)由于增益带宽积的存在,在宽带应用中受到限制。

基于以上特点的考虑,我们的设计中普通使用transformer 来驱动ADC 。

2.2 ADC 前端驱动电路-Trans 的主要指标insertion loss(插入损耗)实际的transformer 都会有插损,中频应用中普通在1dB 以下input return loss (输入端回波损耗):允许用户设计匹配电路在某些频段满足transformer 的响应特性magnitude imbalance 和 phase imbalance (幅度不平衡和相位不平衡):理想的transformer 的差分端信号应该是幅度相同相位相反的,实际的巴伦总存在幅度和相位的不平衡。

常用的ADC和DAC

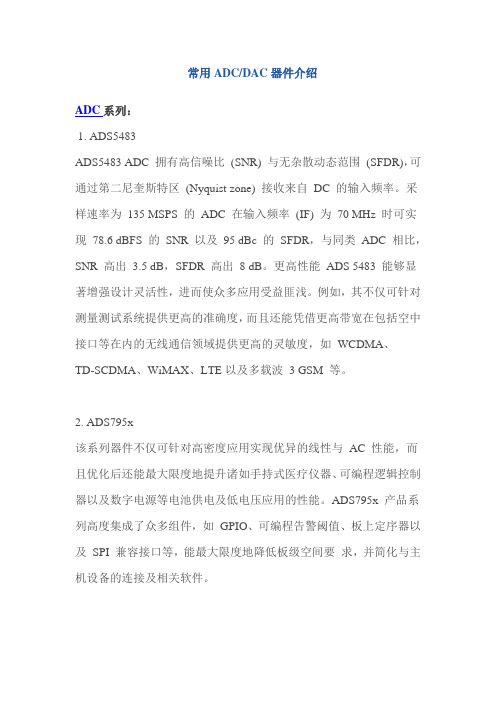

常用ADC/DAC器件介绍ADC系列:1. ADS5483ADS5483 ADC 拥有高信噪比(SNR) 与无杂散动态范围(SFDR),可通过第二尼奎斯特区(Nyquist zone) 接收来自DC 的输入频率。

采样速率为135 MSPS 的ADC 在输入频率(IF) 为70 MHz 时可实现78.6 dBFS 的SNR 以及95 dBc 的SFDR,与同类ADC 相比,SNR 高出3.5 dB,SFDR 高出8 dB。

更高性能ADS 5483 能够显著增强设计灵活性,进而使众多应用受益匪浅。

例如,其不仅可针对测量测试系统提供更高的准确度,而且还能凭借更高带宽在包括空中接口等在内的无线通信领域提供更高的灵敏度,如WCDMA、TD-SCDMA、WiMAX、LTE以及多载波3 GSM 等。

2. ADS795x该系列器件不仅可针对高密度应用实现优异的线性与AC 性能,而且优化后还能最大限度地提升诸如手持式医疗仪器、可编程逻辑控制器以及数字电源等电池供电及低电压应用的性能。

ADS795x 产品系列高度集成了众多组件,如GPIO、可编程告警阈值、板上定序器以及SPI 兼容接口等,能最大限度地降低板级空间要求,并简化与主机设备的连接及相关软件。

3. AS1538AS1538带有8个12Bit的分辨率的输入通道。

其在50ksps的转换速度下低于850μA(包括内部基准)消耗电流。

在关断模式下,AS1538的供电电流可降至1.5μA以下。

无论是2.5V的内部基准还是1V至5.25V范围内的外部基准,都能对满刻度模拟输入范围进行设定。

AS1538的I2C兼容接口支持速度高达3.4MHz的接口,包括100kHz 和400kHz的行业标准速度。

用户可编程I2C地址可以在一条I2C总线上挂多达4种设备。

4. LTC2262LTC2262 用1.8V 的低压模拟电源工作,极大地节省了功率,而且不牺牲AC 性能。

这个ADC 在基带提供了72.8dB 的信噪比(SNR) 性能和88dB 的无寄生动态范围(SFDR)。

SA568A中文资料

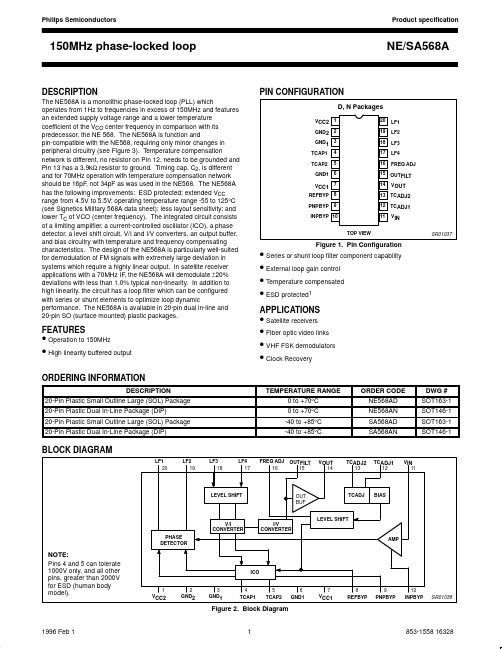

• Satellite receivers • Fiber optic video links • VHF FSK demodulators • Clock Recovery

TEMPERATURE RANGE 0 to +70°C 0 to +70°C -40 to +85°C -40 to +85°C ORDER CODE NE568AD NE568AN SA568AD SA568AN DWG # SOT163-1 SOT146-1 SOT163-1 SOT146-1

DC ELECTRICAL CHARACTERISTICS

VCC = 5V; TA = 25°C; fO = 70MHz, Test Circuit Figure 3, fIN = -20dBm, R4 = 3.9kΩ, unless otherwise specified. LIMITS SYMBOL VCC ICC PARAMETER Supply voltage Supply current TEST CONDITIONS MIN 4.5 NE/SA568A TYP 5 54 MAX 5.5 70 V mA UNITS

Capture TC of fO RIN

Input resistance4 Output impedance Demodulated VOUT AM rejection Distribution6 Drift with supply

fO fO

0 2

+15

% %/V

NOTE: 1. Signal level to assure all published parameters. Device will continue to function at lower levels with varying performance. 2. Limits are set symmetrical to fO. Actual characteristics may have asymmetry beyond the specified limits. 3. Not 100% tested, but guaranteed by design. 4. Input impedance depends on package and layout capacitances. See Figures 6 and 5. 5. Linearity is tested with incremental changes in inupt frequency and measurement of the DC output voltage at Pin 14 (VOUT). Non-linearity is then calculated from a straight line over the deviation range specified. 6. Free-running frequency is measured as feedthrough to Pin 14 (VOUT) with no input signal applied.

DAC8248中文资料

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

DAC8248–SPECIFICATIONS

ELECTRICAL CHARACTERlSTICS (@ V

IDD PSRR

2

Digital Inputs = VINL or VINH Digital Inputs = 0 V or VDD ∆VDD = ± 5%

10

AC PERFORMANCE CHARACTERISTICS Propagation Delay5, 6 tPD Output Current Setting Time6, 7 tS Output Capacitance CO

350 1 90 120 –70 –70

–2–

REV. B

DAC8248

Parameter Switching Characteristics (Notes 2, 8) LSB/MSB Select to Write Set-Up Time LSB/MSB Select to Write Hold Time DAC Select to Write Set-Up Time DAC Select to Write Hold Time LDAC to Write Set-Up Time LDAC to Write Hold Time Data Valid to Write Set-Up Time Data Valid to Write Hold Time Write Pulse Width LDAC Pulse Width Reset Pulse Width tCBS tCBH tAS tAH tLS tLH tDS tDH tWR tLWD tRWD Symbol Conditions VDD = +5 V +25؇C –40؇C to +85؇C (Note 9) 130 0 180 0 120 0 160 0 130 100 80 170 0 210 0 150 0 210 0 150 110 90 DAC8248 VDD = +15 V –55؇C to +125؇C All Temps (Note 10) 180 0 220 0 160 0 220 0 170 130 90 80 0 80 0 80 0 70 10 90 60 60 ns min ns min ns min ns min ns min ns min ns min ns min ns min ns min ns min Units

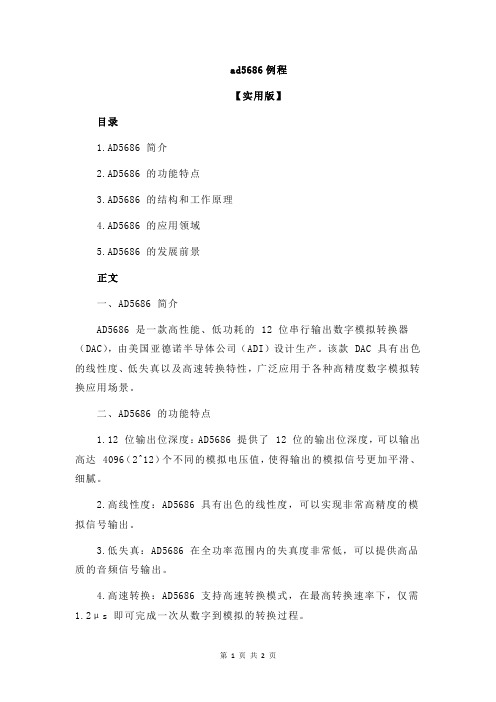

ad5686例程

ad5686例程【实用版】目录1.AD5686 简介2.AD5686 的功能特点3.AD5686 的结构和工作原理4.AD5686 的应用领域5.AD5686 的发展前景正文一、AD5686 简介AD5686 是一款高性能、低功耗的 12 位串行输出数字模拟转换器(DAC),由美国亚德诺半导体公司(ADI)设计生产。

该款 DAC 具有出色的线性度、低失真以及高速转换特性,广泛应用于各种高精度数字模拟转换应用场景。

二、AD5686 的功能特点1.12 位输出位深度:AD5686 提供了 12 位的输出位深度,可以输出高达 4096(2^12)个不同的模拟电压值,使得输出的模拟信号更加平滑、细腻。

2.高线性度:AD5686 具有出色的线性度,可以实现非常高精度的模拟信号输出。

3.低失真:AD5686 在全功率范围内的失真度非常低,可以提供高品质的音频信号输出。

4.高速转换:AD5686 支持高速转换模式,在最高转换速率下,仅需1.2μs 即可完成一次从数字到模拟的转换过程。

5.低功耗:AD5686 在正常工作模式下,功耗仅为 500μA,非常适合低功耗系统应用。

三、AD5686 的结构和工作原理AD5686 的内部结构包括输入寄存器、数字转换核心、输出缓冲器等部分。

其工作原理是:输入的数字信号经过输入寄存器进入数字转换核心,数字转换核心将数字信号转换为模拟电压信号,然后通过输出缓冲器将模拟电压信号输出到外部负载。

四、AD5686 的应用领域AD5686 广泛应用于各种高精度数字模拟转换应用场景,如音频处理、仪器仪表、通信系统、医疗设备等领域。

五、AD5686 的发展前景随着科技的不断发展,对于高性能、低功耗的数字模拟转换器的需求越来越大。

ZL38065GD中文资料(Zarlink Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

图 2 - 100引脚 LQFP

2

芯片中文手册,看全文,戳

ZL38065

数据表

目录

1.0设备概述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 1.1自适应滤波器. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 1.2双方通话检测. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 1.3路径变化检测. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 1.4非线性处理器(NLP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 1.5禁用音频检测器. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 1.6不稳定性检测. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 1.7窄带信号检测器(NBSD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 1.8偏移空筛选器. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 1.9级可调焊盘. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 1.10 ITU-T G.168合规性. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

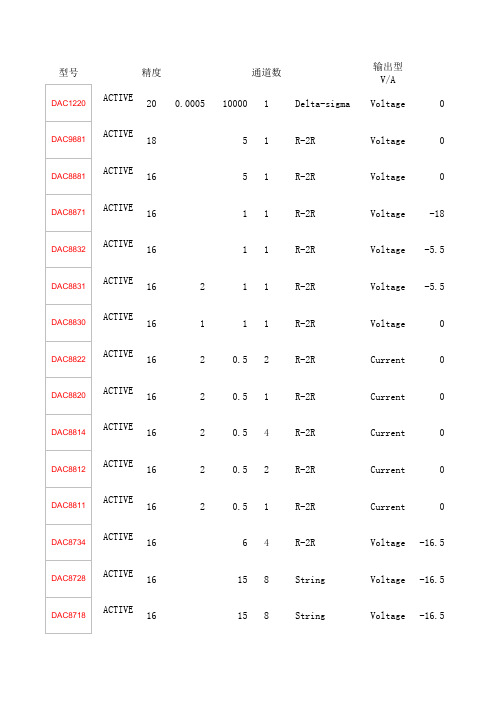

DAC选型手册

精度通道数输出型V/A200.0005100001 Delta-sigma Voltage 018 51 R-2R Voltage 016 51 R-2R Voltage 016 11 R-2R Voltage -1816 11 R-2R Voltage -5.516211 R-2R Voltage -5.516111 R-2R Voltage 01620.52 R-2R Current 01620.51 R-2R Current 01620.54 R-2R Current 01620.52 R-2R Current 01620.51 R-2R Current 016 64 R-2R Voltage -16.516 158 String Voltage -16.516 158 String Voltage -16.51630.651 String Voltage -5.516160.651 String Voltage -6160.043104 String Voltage -6160.043101 String Voltage 016 58 String Voltage 0160.284 String Voltage 0160.284 String Voltage 0 DAC856216 72 String Voltage 0160.281 String Voltage 0160.2104 String Voltage 0160.2104 String Voltage 0160.2102 String Voltage 0160.2101 String Voltage 0160.2101 String Voltage 016 84 String Voltage 0160.1101 String Voltage 0160.093104 String Voltage 0160.093102 String Voltage 0160.093101 String Voltage 0160.093101 String Voltage 016 61 String Voltage 0160.1104 R-2R Voltage -10160.251 R-2R Voltage -10160.251 R-2R Voltage -10160.089104 R-2R Voltage -10160.17251 R-2R Voltage -10160.1124 R-2R Voltage -2.5160.1124 R-2R Voltage -2.5160.1104 R-2R Voltage -2.5160.1102 R-2R Voltage -2.5160.1101 R-2R Voltage -2.5160.089104 R-2R Voltage -2.5160.089102 R-2R Voltage -2.5160.093101 R-2R Voltage -2.5160.086101 R-2R Voltage 0160.1101 R-2R Voltage 0160.086101 R-2R Voltage -10160.1101 R-2R Voltage -10168000.0112 Current sink Current 2168000.0112 Current sink Current 2165000.0122 Current sink Current 2165000.0122 Current sink Current 21610000.01042 Current sink Current 21610000.01041 Current sink Current 21610000.01041 Current sink Current 2168000.01042 Current sink Current 2166250.01042 Current sink Current 2160.000520001 Delta-sigma Voltage 0141250.0351 Current source Current 2142000.031 Current source Current 21420.51 R-2R Current 01420.52 R-2R Current 01420.54 R-2R Current 01420.52 R-2R Current 01420.51 R-2R Current 014 61 String Voltage 014 64 R-2R Voltage -16.514 158 String Voltage -16.514 158 String Voltage -16.514 58 String Voltage 014 84 String Voltage 014 84 String Voltage 0DAC816214 72 String Voltage 0144000.021 Current source Current 2142750.022 Current source Current 2142750.022 Current source Current 2142400 Current sink Current120.28611 String Voltage 0120.23312 String Voltage 0120.23311 String Voltage 0120.28611 String Voltage 0120.28318 String Voltage 012111 String Voltage 0120.10231 String Voltage 0120.10234 String Voltage 0120.102 4 String Voltage 0120.10234 String Voltage 0120.28611 String Voltage 0120.28318 String Voltage 0120.28318 String Voltage 0120.28318 String Voltage 0120.075 2.52 String Voltage 0121250.0351 Current source Current 2126661 R Ladder Voltage 0.78122000.031 Current source Current 2120.16741 R-2R Voltage -10120.2541 R-2R Voltage -10120.28411 R-2R Current 012100.22 R-2R Current 012100.21 R-2R Current 01250.21 R-2R Current 012 1.250.82 R-2R Current 012 1.250.82 R-2R Current 012 1.250.82 R-2R Current 012 158 String Voltage -16.5120.1104 R-2R Voltage -10120.1104 R-2R Voltage -1012 158 String Voltage -16.512 64 R-2R Voltage -16120.089104 R-2R Voltage -10120.089104 R-2R Voltage -10 ACTIVE 12 78 String Voltage 0 120.1104 R-2R Voltage -10120.1104 R-2R Voltage -2.5120.143101 R-2R Voltage -2.5120.089104 R-2R Voltage 0120.089104 R-2R Voltage 0120.089104 R-2R Voltage 0120.089104 R-2R Voltage -2.5120.1101 R-2R Voltage -2.5120.13102 R-2R Voltage -2.5120.132101 R-2R Voltage 0ACTIVE 12 78 String Voltage 0 120.043104 String Voltage 0120.043104 String Voltage 0120.05101 String Voltage 012 58 String Voltage 012 84 String Voltage 012 84 String Voltage 0 DAC756212 72 String Voltage 0120.558 String Voltage 012 54 String Voltage 012152 String Voltage 012152 String Voltage 0120.551 String Voltage 0120.095101 String Voltage 0120.095101 String Voltage 012 152 String Voltage -512 152 String Voltage -512 61 String Voltage 0122750.022 Current source Current 0122750.022 Current source Current 212400.0252 Current source Current 0.5100.2780.82 String Voltage 0100.28318 String Voltage 0100.093 2.52 String Voltage 0100.28318 String Voltage 0100.10231 String Voltage 0100.10234 String Voltage 0100.07512.51 String Voltage 0101250.0351 Current source Current 2102000.031 Current source Current 2102000.031 Current source Current 2 ACTIVE 10 78 String Voltage 0 100.18894 String Voltage 0100.18894 String Voltage 010 91 String Voltage 010 152 String Voltage -510 152 String Voltage -510 61 String Voltage 0102750.022 Current source Current 2102750.022 Current source Current 280.28318 String Voltage 080.28318 String Voltage 080.045108 String Voltage 080.107 2.54 String Voltage 080.2780.82 String Voltage 080.09332 String Voltage 080.23311 String Voltage 080.10231 String Voltage 080.008104 R-2R Voltage 080.048104 R-2R Voltage 08100.12 R-2R Current -108100.12 R-2R Current -108100.11 R-2R Current -1080.14354 R-2R Voltage -580.14354 R-2R Voltage -580.045108 String Voltage 080.048104 String Voltage 08300.031 I-steering Voltage 081000.0351 Current source Current 282000.031 Current source Current 2 ACTIVE 8 78 String Voltage 080.18884 String Voltage 080.18884 String Voltage 08 81 String Voltage 08 152 String Voltage -58 61 String Voltage 08 61 String Voltage 0ACTIVE 0.2561001 I-steering Current输入方式基准源E/I5.5 Serial SPI 1120 2.5 Ext 4.75 5.5 Serial SPI 1218 6 Ext 1.7 5.5 Serial SPI 1116 6 Ext 2.7 18 Serial SPI 1116 0.015 Ext 2.7 5.5 Serial SPI 1116 0.015 Ext 2.7 5.5 Serial SPI 1116 0.015 Ext 2.7 5.5 Serial SPI 1116 0.015 Ext 2.72 Parallel 1116 0.025 Ext 2.72 Parallel 1116 0.025 Ext 2.72 Serial SPI 1116 0.0275 Ext 2.72 Serial SPI 1116 0.025 Ext 2.72 Serial SPI 1116 0.025 Ext 2.7 16.5 Serial SPI 1116 280 Ext 2.7 33 Parallel 1416 107 Ext 2.7 33 Serial SPI 1416 115 Ext 2.75.5 Serial SPI 0.56416115100175 Ext 1.86 Serial SPI 16416115100175 Ext 1.86 Serial I2C 16416 2.7 Ext 2.7 5.5 Serial I2C 16516 0.42 Ext 2.7 5.5 Serial SPI 112168363 2.2 Int/Ext 2.7 5.5 Serial SPI 18168879 3.1 Int/Ext 1.8 5.5 Serial SPI 18168879 3.1 Int/Ext 1.85 Serial SPI 11216 0.5 Int/Ext5.5 Serial SPI 18168879 2.6 Int/Ext 2.7 5.5 Serial SPI 1121695873 Ext 1.8 5.5 Serial SPI 1121695873 Ext 1.8 5.5 Serial SPI 181695873 Ext 2.7 5.5 Serial SPI 1816 1 Ext 2.7 5.5 Serial SPI 181695871 Ext 2.7 5.5 Parallel 16516 4.75 Ext 1.8 5.5 Parallel 16516 0.72 Ext 1.8 5.5 Serial SPI 164169469 2.7 Ext 2.7 5.5 Serial SPI 165169469 1.35 Ext 2.7 5.5 Serial SPI 16416 0.72 Ext 2.7 5.5 Serial SPI 16416 0.72 Ext 2.7 5.5 Serial SPI 281588660.14 Ext 1.8 10 Parallel 1216 50 Ext 4.75 10 Parallel 1316 100 Int/Ext 4.75 10 Parallel 1316 100 Int/Ext 4.75 10 Serial SPI 2216 50 Ext 4.75 10 Serial SPI 3316 100 Int/Ext 4.75 2.5 Parallel 3316 18 Int/Ext 5.25 2.5 Serial SPI 1316 18 Int/Ext 4.75 2.5 Parallel 2315 7.5 Ext 4.75 2.5 Parallel 2315 2.5 Ext 4.752.5 Parallel 2315 2.5 Ext 4.752.5 Parallel 2315 1.8 Ext 4.752.5 Serial SPI 2315 7.5 Ext 4.752.5 Serial SPI 2315 2.5 Ext 4.752.5 Serial SPI 2315 1.8 Ext 4.7510 Serial SPI 2215 525 Int 4.510 Parallel 1216 525 Int 4.510 Serial SPI 1116 525 Int 4.510 Parallel 1215 525 Int 4.520 Parallel 24 79801750 Int 1.7120 Parallel 24 79801750 Int 1.7120 Parallel 36 75801410 Int 1.7120 Parallel 912 7272445 Int 1.6520 Parallel LVDS 24 79811300 Int 1.7120 Parallel LVDS 24 7981800 Int 1.7120 Parallel LVDS 24 7981650 Int 1.7120 8 Byte Wide LVDS 24 77831150 Int 1.7120 8 Byte Wide LVDS 24 7783950 Int 1.712.8 Serial SPI 1216 1.2 Ext 2.720 Parallel 3.57 75175 Ext 320 Parallel 2.53 76170 Int/Ext 2.72 Parallel 1114 0.025 Ext 2.72 Parallel 1114 0.025 Ext 2.72 Serial SPI 1114 0.0275 Ext 2.72 Serial SPI 1114 0.025 Ext 2.72 Serial SPI 0.5114 0.025 Ext 2.75.5 Serial SPI 141488660.14 Ext 1.8 16.5 Serial SPI 1114 260 2.733 Parallel 1214 107 2.733 Serial SPI 1214 115 Ext 2.755.5 Serial SPI 0.54148363 2.2 Int/Ext 2.75.5 Serial SPI 12148779 2.9 Int/Ext 1.85.5 Serial SPI 12148779 2.9 Int/Ext 1.85 Serial SPI 0.5314 0.5 Int/Ext5.5 Parallel LVDS 24 74660 Int 3.1520 Parallel 2 3.5 7176435 Int 1.6520 Parallel 34 7784330 Int 320 Parallel 34147784330 Int 3 Parallel LVDS 1.757.5 2000 Int5.1 Parallel 0.53127874 2.7 Int/Ext 2.75.1 Serial SPI 14127472 4.5 Int/Ext 2.75.1 Serial SPI 14127579 4.5 Int/Ext 2.75.1 Parallel 0.53127874 2.7 Int/Ext 2.75.1 Serial SPI 1612 18 Int/Ext 2.75.1 Parallel 14127872 4.3 Ext 2.75.1 Serial SPI 14127672 1.8 Ext 2.7 5.1 Serial SPI 141274700.9 Ext 2.7 5.1 Serial SPI 14127470 3.6 Ext 2.7 5.1 Serial SPI 14127470 3.6 Ext 2.75.1 Serial SPI 14127470 3.6 Ext 2.7 5.1 Parallel 14127872 1.2 Ext 2.7 5.1 Serial SPI 1612 18 Ext 2.7 5.1 Serial SPI 1612 18 Ext 2.75.1 Serial SPI 1612 18 Ext 2.7 5.1 Serial SPI 1412 3 Ext 4.5 20 Parallel 24 75175 Int/Ext 33.8 I2C SPI 1.3812 0.15 2.220 Parallel 1.75 2.5 75170 Int/Ext 2.7 10 Parallel 0.50.2512 270 Int/Ext 4.5 10 Parallel 0.50.2512 625 Int 4.5 1 Serial SPI 1112 2.5 Ext 4.75 1 Parallel 1112 0.0275 Ext 2.7 1 Parallel 1112 0.0275 Ext 2.7 1 Serial SPI 1112 0.025 Ext 2.7 1 Parallel 10.512 1 Ext 4.5 1 Parallel 10.512 1 Ext 4.5 1 Serial SPI 10.512 1 Ext 4.5 33 Parallel 1112 107 Ext 2.7 10 Parallel 1112 45 Ext 4.75 10 Parallel 1112 45 Ext 4.75 33 Serial SPI 1112 115 Ext 2.7 16 Serial SPI 1112 260 Ext 2.7 10 Serial SPI 1112 45 Ext 4.75 10 Serial SPI 1112 45 Ext 4.75 5.5 Serial I2C 0.25112 3.4 Int/Ext10 Parallel 1112 15 Ext 4.75 2.5 Parallel 1112 15 Ext 4.75 2.5 Parallel 1112 2.5 Int/Ext 4.75 4.1 Serial SPI 1112 2.4 Ext 3 1.3 Serial SPI 1112 2.4 Ext 31.3 Serial SPI 111212 15 Ext 4.752.5 Serial SPI 111212 15 Ext 4.75 2.5 Serial SPI 1112 1.8 Ext 4.75 2.5 Serial SPI 11123.5 Int4.75 4.1 Serial SPI 1112 5 Int 4.755.5 Serial I2C 0.25112 3.4 Ext4.1 Serial I2C 812 0.85 Ext 2.75.5 Serial I2C 1812 1.8 Ext 2.7 5.5 Serial I2C 412 0.85 Ext 2.7 5.5 Serial SPI 0.251128363 2.2 Int/Ext 2.7 5.5 Serial SPI 0.51128179 2.9 Int/Ext 2.7 5.5 Serial SPI 0.51128179 2.9 Int/Ext 1.8 5 Serial SPI 0.250.7512 0.5 Int/Ext5.5 Serial SPI 0.5112 4.5 Ext 2.7 5.5 Serial SPI 0.5112 3.5 Ext 2.7 5.5 Serial SPI 0.5112 0.675 Ext 2.7 5.5 Serial SPI 0.5112 0.675 Ext 2.7 5.5 Serial SPI 0.5112 0.27 Ext 2.7 5 Serial SPI 1812 0.3 Ext 2.7 5.5 Serial SPI 1812 0.345 Ext 2.7 5 Serial SPI 0.25112 0.5 Int/Ext5 Serial SPI 0.25112 0.5 Ext5.5 Serial SPI 111281650.14 Ext 1.8 5.5 Parallel 22 7381330 Ext 3 20 Parallel 22127381330 Ext 3 2 Parallel 3.5812617529 Int/Ext 2.7 5.1 Serial SPI 0.51105662 4.2 Int/Ext 2.7 5.1 Serial SPI 121010 18 Int/Ext 2.7 5.1 Serial SPI 0.51106864 1.8 Ext 2.7 5.1 Serial SPI 1210 18 Ext 2.7 5.1 Serial SPI 1 1.51062680.9 Ext 2.7 5.1 Serial SPI 111068703 Ext 2.7 5.1 Serial SPI 0.5110 0.75 Ext 4.5 20 Parallel 0.51 77175 Int/Ext 3 20 Parallel 0.51 170 Ext , Int20 Parallel 0.51 68170 Int/Ext 2.7 5.5 Serial I2C 0.20.510 3.4 Ext5.5 Serial I2C 0.5210 1.5 Ext5.5 Serial I2C 0.5210 500 Ext 2.75 5.5 Serial I2C 0.5210 160 Ext 2.75 5 Serial SPI 0.20.510 0.5 Int/Ext5 Serial SPI 0.20.510 0.5 Ext5.5 Serial SPI 0.50.51069650.14 Ext 1.8 20 Parallel 10.5 6380290 Int/Ext 3 20 Parallel 10.5106380290 Int/Ext 3 5.1 Serial SPI 110.48 18 Int/Ext 2.7 5.1 Serial SPI 118 18 Ext 2.7 5.1 Serial SPI 0.918 12 Ext 2.7 5.1 Serial SPI 0.50.5857603 Ext 2.75.1 Serial SPI 0.5185762 4.2 Int/Ext 2.75.1 Serial SPI 0.20.585450 2.4 Ext 2.75.1 Serial SPI 0.20.5857620.9 Int/Ext 2.75.1 Serial SPI 0.20.585760 2.1 Ext 2.75.1 Serial SPI 0.918 3.6 Ext 2.75.1 Serial SPI 0.918 6 Ext 2.710 Parallel 0.50.58 20 Ext 10.810 Parallel 0.50.58 7.5 Ext 4.7510 Parallel 0.50.58 5 Ext 4.7510 Parallel 118 90 Ext 4.510 Parallel 118 75 Ext 4.55 Serial SPI 0.918 15 Ext 4.755 Serial SPI 0.918 8 Ext 4.7550 Parallel 0.50.5 80 Ext 4.7520 Parallel 0.51 5067100 Ext 320 Parallel 0.50.5 67170 Int/Ext 2.75.5 Serial I2C 0.10.258 3.4 Ext5.5 Serial I2C 0.250.58 1.5 Ext5.5 Serial I2C 0.250.58 1.5 Ext 2.755.5 Serial I2C 0.2518 0.4 Ext 2.75 Serial SPI 0.080.258 0.5 Ext5.5 Serial SPI 0.250.2588165 Ext 1.85.5 Serial SPI 0.250.25855630.14 Ext 1.8 Bitstream 120 18 1.65封装5.25 4.75 4.75 Catalog 16SSOP/QSOP5.5 2.7 5.5 Catalog 24VQFN5.5 2.7 5.5 Catalog 24VQFN5.5-1818 Catalog 16TSSOP5.5 2.7 5.5 Catalog 14VQFN5.5 2.7 5.5 Catalog 14SOIC, 14VQFN5.5 2.7 5.5 Catalog 8SOIC5.5 2.7 5.5 Catalog 38TSSOP5.5 2.7 5.5 Catalog 28SSOP5.5 2.7 5.5 Catalog 28SSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 8MSOP, 8SON5.5 4.7524 Catalog 40VQFN, 48TQFP5.5 4.536 Catalog 56QFN, 64TQFP5.5 4.536 Catalog 48VQFN, 64TQFP546 Catalog 16TSSOP546 Catalog 16TSSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 8MSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 16TSSOPCatalog 10MSOP, 10SON5.5 2.7 5.5 Catalog 8MSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 8MSOP5.5 2.7 5.5 Catalog 8MSOP5.5 2.7 5.5 Catalog 8MSOP5.5 2.7 5.5 Catalog 48TQFP5.5 2.7 5.5 Catalog 32TQFP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 8MSOP5.5 2.7 5.5 Catalog 8MSOP, 8SON5.5 2.7 5.5 Catalog 8MSOP5.5 1.8 5.5 Catalog 6SC705.2514.2515.75 Catalog 48SSOP5.2514.2515.75 Catalog 48LQFP5.2514.2515.75 Catalog 48LQFP5.2514.2515.75 Catalog 48SSOP5.2514.2515.75 Catalog 24SSOP5.25 4.75 4.75 Catalog 64LQFP5.25 4.75 5.25 Catalog 64LQFP5.25 4.75 5.25 Catalog 48SSOP5.25 4.75 5.25 Catalog 32LQFP5.25 4.75 5.25 Catalog 32LQFP5.25 4.75 5.25 Catalog 32TQFP5.25 4.75 5.25 Catalog 48SSOP5.25 4.75 5.25 Catalog 32LQFP5.25 4.75 5.25 Catalog 20SSOP5.511.416.5 Catalog 16SOIC5.511.416.5 Catalog 28SOIC5.511.416.5 Catalog 16SOIC5.511.416.5 Catalog 28SOIC2.1533.6 Catalog 64VQFN2.1533.6 Catalog 64VQFN2.1533.6 Catalog 100HTQFP1.953 3.6 Catalog 100HTQFP2.1533.6 Catalog 64VQFN2.1533.6 Catalog 64VQFN2.1533.6 Catalog 64VQFN2.1533.6 Catalog 48VQFN2.1533.6 Catalog 48VQFN3.3 2.7 3.3 Catalog 16SSOP/QSOP5.53 5.5 Catalog 28SOIC, 28TSSOP5.5 2.7 5.5 Catalog 28SOIC, 28TSSOP5.5 2.7 5.5 Catalog 28SSOP5.5 2.7 5.5 Catalog 38TSSOP5.5 2.7 5.5 Catalog 28SSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 8MSOP, 8SON5.5 1.8 5.5 Catalog 6SC705 4.7518 Catalog 40VQFN, 48TQFP5 4.7518 Catalog 56QFN, 64TQFP5 4.7518 Catalog 48VQFN, 64TQFP5.5 2.7 5.5 Catalog 14TSSOP, 16TSSOP5.5 2.7 5.5 Catalog 16TSSOP1.82.7 5.5 Catalog 16TSSOPCatalog 10MSOP, 10SON3.6 3.15 3.6 Catalog 48HTQFP1.953 3.6 Catalog 48HTQFP3.63 3.6 Catalog 48TQFP3.63 3.6 Catalog 48TQFP3 3.6 Catalog 252BGA5.25 2.7 5.25 Catalog 20SOIC, 20TSSOP5.25 2.7 5.25 Catalog 8SOIC5.25 2.7 5.25 Catalog 8MSOP, 8SOIC5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 8PDIP, 8SOIC5.5 2.7 5.5 Catalog 8MSOP, 8PDIP, 8SOIC5.5 2.7 5.5 Catalog 16DIESALE5.5 2.7 5.5 Catalog 16DIESALE5.5 2.7 5.5 Catalog 16SOIC, 16TSSOP5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 20DIESALE5.5 2.7 5.5 Catalog 20DIESALE5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 4.5 5.5 Catalog 8SOIC5.53 5.5 Catalog 28SOIC, 28TSSOP3.6 2.2 3.6 Catalog5.5 2.7 5.5 Catalog 28SOIC, 28TSSOP5.511.416.5 Catalog 28SOIC5.511.416.5 Catalog 28SOIC5.25 4.75 5.25 Catalog 8SOIC5.5 2.5 5.5 Catalog 40WQFN5.5 2.7 5.5 Catalog 20TSSOP5.5 2.7 5.5 Catalog 10MSOP5.5 4.5 5.5 Catalog 24SOIC5.5 4.5 5.5 Catalog 24SOIC5.5 4.5 5.5 Catalog 16SOIC5 4.7518 Catalog 56QFN, 64TQFP5.2514.2515.75 Catalog 28PLCC, 28SOIC5.2514.2515.75 Catalog 28PLCC, 28SOIC5.5 4.533 Catalog 48VQFN, 64TQFP5 4.7518 Catalog 40VQFN, 48TQFP5.2514.2515.75 Catalog 16SOIC5.2514.2515.75 Catalog 16SOIC2.7 5.5 Catalog 16TSSOP, 24VQFN5.25 4.75 5.25 Catalog 28SOIC5.25 4.75 5.25 Catalog 28SOIC5.25 4.75 5.25 Catalog 20SSOP3.63 3.6 Catalog 16SOIC, 20SSOP3.63 3.6 Catalog 16SOIC, 20SSOP5.25 4.75 5.25 Catalog 16SOIC, 20SSOP5.25 4.75 5.75 Catalog 16SOIC, 20SSOP5.25 4.75 5.25 Catalog 24SSOP5.25 4.75 5.25 Catalog 8SOIC5.25 4.75 5.25 Catalog 8SOIC2.7 5.5 Catalog 16TSSOP, 24VQFN5.5 2.7 5.5 Catalog 10MSOP5.25 2.75 5.25 Catalog 16TSSOP5.5 2.7 5.5 Catalog 6SOT-235.5 2.7 5.5 Catalog 14TSSOP, 16TSSOP5.5 2.7 5.5 Catalog 16TSSOP5.5 2.7 5.5 Catalog 16TSSOPCatalog 10MSOP, 10SON5.5 2.7 5.5 Catalog 32QFN5.5 2.7 5.5 Catalog 10MSOP5.5 2.7 5.5 Catalog 16QFN5.5 2.7 5.5 Catalog 16QFN5.5 2.7 5.5 Catalog 12USON5.5 2.7 5.5 Catalog 8MSOP, 8SOT-235.5 2.7 5.5 Catalog 6SOT-23, 8MSOP Catalog 12WQFNCatalog 12WQFN5.5 1.8 5.5 Catalog 6SC703.63 3.6 Catalog 48TQFP3.63 3.6 Catalog 48TQFP3.3 2.7 3.3 Catalog 48TQFP5.25 2.7 5.25 Catalog 8SOIC5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 8SOIC5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 8MSOP, 8SOIC5.5 2.7 5.5 Catalog 16SOIC, 16TSSOP5.5 4.5 5.5 Catalog 8MSOP, 8PDIP, 8SOIC5.53 5.5 Catalog 28SOIC, 28TSSOP Automotive 28TSSOP5.5 2.7 5.5 Catalog 28SOIC, 28TSSOP 2.7 5.5 Catalog 16TSSOP, 24VQFN 2.7 5.5 Catalog 10MSOP5.25 2.75 5.25 Catalog 16TSSOP5.25 2.75 5.25 Catalog 6SOT-23Catalog 12WQFNCatalog 12WQFN5.5 1.8 5.5 Catalog 6SC703.63 3.6 Catalog 48TQFP3.63 3.6 Catalog 48TQFP5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.5 2.7 5.5 Catalog 20SOIC, 20TSSOP5.25 2.7 5.25 Catalog 16PDIP, 16SOIC5.5 2.7 5.5 Catalog 16SOIC, 16TSSOP5.5 2.7 5.5 Catalog 8SOIC5.5 2.7 5.5 Catalog 8SOIC5.5 2.7 5.5 Catalog 8MSOP, 8SOIC5.5 2.7 5.5 Catalog 8MSOP, 8SOIC5.5 2.7 5.5 Catalog 14SOIC5.25 2.7 5.5 Catalog 14PDIP, 14SOIC15.7510.815.75 Catalog 20PDIP, 20SOIC5.25 4.7515.75 Catalog 20PDIP, 20PLCC, 20SO, 20SOIC, 20TSSOP5.25 4.75 5.25 Catalog 16PDIP, 16SO, 16SOIC, 16TSSOP, 20PLCC5.511.416.5 Catalog 20PDIP, 20SOIC5.511.416.5 Catalog 24SOIC5.25 4.75 5.25 Catalog 16PDIP, 16SOIC5.25 4.75 5.25 Catalog 14PDIP, 14SOIC5.25 4.75 5.25 Catalog 20SOIC5.53 5.5 Catalog 28SOIC, 28TSSOP5.5 2.7 5.5 Catalog 28SOIC, 28TSSOP2.7 5.5 Catalog 16TSSOP, 24VQFN2.7 5.5 Catalog 10MSOP5.25 2.75 5.25 Catalog 16TSSOP5.25 2.75 5.25 Catalog 6SOT-23Catalog 12WQFN5.5 1.8 5.5 Automotive 6SC705.5 1.8 5.5 Catalog 6SC703.64.755.25 Catalog 16TSSOP描述7.15 | 1ku 20 位 Δ-Σ 低功耗数模转换器16.90 | 1ku 单通道 18 位低噪声电压输出数模转换器8.00 | 1ku 单通道 16 位低噪声电压输出数模转换器8.00 | 1ku 16-Bit, Ultra-Low Power, 10V Output (Unbuffered) Digital-to-Analog Converte 7.95 | 1ku 16 位、超低功耗、电压输出数模转换器7.95 | 1ku 16 位、超低功耗、电压输出数模转换器7.95 | 1ku 16 位超低功耗电压输出数模转换器8.65 | 1ku Dual, Parallel Input, 16-Bit, Multiplying Digital-to-Analog Converter8.50 | 1ku 16 位并行输入乘法 DAC16.95 | 1ku 16 位、四路、串行输入乘法数模转换器8.40 | 1ku 16 位、双串行输入乘法数模转换器7.15 | 1ku 16 位串行输入乘法数模转换器26.95 | 1ku 16 位四路高精度 +/-15V 输出数模转换器21.95 | 1ku 八路、低功耗、16 位 +/-15V 输出并行输入数模转换器21.95 | 1ku 八路、低功耗、16 位 +/-15V 输出串行输入数模转换器1.85 | 1ku 16 位高速低噪声电压输出数模转换器1.85 | 1ku 16 位高速低噪声电压输出数模转换器12.85 | 1ku 低功耗四路轨至轨输出 16 位 I2C 输入 DAC3.20 | 1ku 低功耗轨至轨输出 16 位 I2C 输入 DAC10.95 | 1ku 具有 2.5V、2ppm/℃ 内部参考的 16 位、八通道、超低短时脉冲波形干扰、电压输出 7.65 | 1ku 16-Bit, Quad Chanel, Ultra-Low Glitch, Vltg Output DAC w/2.5V, 5ppmC Intrnl 7.65 | 1ku 16-Bit, Ultra-Low Glitch, Voltage Output D/A Conv with 2.5V, 5ppm/C Interna 具有 2.5V、2ppm/C 内部参考的 16 位、双通道、 超低短时脉冲波形干扰、电压输出 2.90 | 1ku 具有 2.5V、2ppm/℃ 内部参考的 16 位、超低短时脉冲波形干扰、电压输出 DAC6.75 | 1ku 16 位、四通道、超低短时脉冲波形干扰、电压输出数模转换器6.75 | 1ku 16 位、四通道、超低短时脉冲波形干扰、电压输出数模转换器3.20 | 1ku DAC8552:16 位双路电压输出数模转换器2.35 | 1ku 16 位、超低短时脉冲波形干扰、电压输出数模转换器2.60 | 1ku 16 位、超低短时脉冲波形干扰、电压输出 DAC12.20 | 1ku 四路 16 位四路轨至轨电压输出并行接口数模转换器3.25 | 1ku 具有 1.8V 兼容并行接口和轨至轨电压输出的低功耗 16 位数模转换器8.75 | 1ku 2.7V 至 5.5V 四通道 16 位串行输入 DAC5.35 | 1ku 具有串行接口和轨至轨电压输出的 16 位双通道低功耗模数转换器3.00 | 1ku 低功耗轨至轨输出 16 位串行输入数模转换器3.00 | 1ku 乘法、低功耗、轨至轨输出、16 位串行输入数模转换器2.90 | 1ku 采用 SC70 封装的 16 位、单通道、80uA、1.8V-5.5V DAC31.45 | 1ku 16 位四路电压输出数模转换器12.40 | 1ku 具有内部参考的 16 位单通道并行接口8.30 | 1ku 具有内部 +10V 参考和并行 I/F 的 16 位单通道数模转换器31.45 | 1ku 16 位四路电压输出串行输入数模转换器8.20 | 1ku 具有内部 +10V 参考和串行 I/F 的 16 位单通道数模转换器25.95 | 1ku 数模转换器;四路、16 位、12uS 稳定时间、+/- 1 LSB DNL28.75 | 1ku 16 位四路电压输出数模转换器19.95 | 1ku 16 位四路电压输出数模转换器14.70 | 1ku 具有并行接口和复位到最小等级功能的 16 位双路电压输出 DAC14.70 | 1ku 具有并行接口和复位到中间等级功能的 16 位双路电压输出 DAC9.10 | 1ku 16 位电压输出数模转换器19.95 | 1ku 16 位四路电压输出数模转换器10.45 | 1ku 具有串行接口的 16 位双路电压输出 DAC5.95 | 1ku 串行输入 16 位电压输出数模转换器19.85 | 1ku 具有串行数据接口的 16 位数模转换器19.85 | 1ku 具有 16 位总线接口的 16 位数模转换器14.50 | 1ku 具有串行数据接口的 16 位数模转换器14.50 | 1ku 具有 16 位总线接口的 16 位数模转换器28.95 | 1ku 16 位 800 MSPS 2x-8x 内插双通道数模转换器 (DAC)37.45 | 100u 具有集成 PLL 的 16 位 800MSPS 2x-8x 内插双通道数模转换器28.15 | 100u 16 位 500 MSPS 2x-8x 内插双通道数模转换器 (DAC)26.70 | 1ku 具有 16x 内插的高性能 16 位 500MSPS 双 DAC39.95 | 100u 16 位 1.0 GSPS 2x-4x 内插双通道数模转换器 (DAC)38.70 | 100u 16 位 1.0GSPS 2x-4x 内插数模转换器 (DAC)34.40 | 100u 16 位 1.0GSPS 数模转换器 (DAC)33.70 | 100u 双路 16 位 800MSPS 通信 DAC31.20 | 100u 双路 16 位 625MSPS 通信 DAC6.60 | 1ku 16 位 Δ-Σ 低功耗数模转换器9.20 | 1ku 14 位 125 MSPS CommsDAC,差动 介于 2mA 至 20mA 的可伸缩电流输出8.35 | 1ku 可伸缩电流输出在 2mA 与 20mA 之间的 14 位 165MSPS SpeedPlus(TM) DAC5.50 | 1ku 14 位单通道并行接口乘法数模转换器6.15 | 1ku Dual, Parallel Input, 14-Bit, Multiplying Digital-to-Analog Converter12.65 | 1ku 14 位四通道串行接口乘法数模转换器6.10 | 1ku 14 位双通道串行接口乘法数模转换器4.60 | 1ku 14 位单通道串行接口乘法数模转换器2.65 | 1ku 采用 SC70 封装的 14 位、单通道、80uA、1.8V-5.5V DAC19.95 | 1ku 四路 14 位高准确度 +/-15V 输出串行输入数模转换器17.95 | 1ku 八路、低功耗、14 位 +/-15V 输出并行输入数模转换器17.95 | 1ku 八路、低功耗、14 位 +/-15V 输出串行输入数模转换器10.20 | 1ku 具有 2.5V、2ppm/℃ 内部参考的 14 位、八通道、超低短时脉冲波形干扰、电压输出 6.85 | 1ku 16-Bit, Quad Channel, Ultra-Low Glitch, Vltg Output DAC w/2.5V, 5ppmC Intrn 6.85 | 1ku 16-Bit, Quad Chanel, Ultra-Low Glitch, Vltg Output DAC w/2.5V, 5ppmC Intrnl 具有 2.5V、2ppm/C 内部参考的 14 位、双通道、 超低短时脉冲波形干扰、电压输出 31.25 | 1ku 14 位 400MSPS 数模转换器18.75 | 1ku 具有 2x/4x 插值滤波器的14 位 400 CommsDAC14.20 | 1ku Dual 14-Bit 275 MSPS Digital-to-Analog Converter14.20 | 1ku 数模转换器45.00 | 1ku 14 位 2.4GSPS 数模转换器4.35 | 1ku 12 位,DAC,并行,电压输出,可编程内部 参考,建立时间、功耗、1 通道4.65 | 1ku 12 位、1 或 3.5us DAC,具有串行输入、双路 DAC、可编程内部参考和稳定时间、功4.55 | 1ku 12 位 1us DAC,具有串行输入、可编程内部参考和稳定时间5.90 | 1ku 12 位 DAC,具有并行电压输出可编程内部参考设置时间、功耗、8 位微控制器兼容接 11.10 | 1ku 具有内部参考的 2.7V 至 5.5V 12 位 8 通道串行 DAC4.10 | 1ku 12 位单通道并行 DAC,具有电压输出、低功耗和异步更新5.10 | 1ku 12 位 2.5us 双路 DAC,具有串行输入、可编程稳定时间、在 Q temp 温度范围内运行 3.30 | 1ku 12 位 3us DAC 串行输入可编程设置时间/功耗,电压 O/P 范围 = 2x 基准电压11.00 | 1ku 采用晶圆芯片级封装的 2.7V 至 5.5V 12 位 DAC9.00 | 1ku 2.7V to 5.5V, 12-Bit Quad DAC in Wafer Chip Scale Package9.30 | 1ku 12 位 3us 四路 DAC,具有串行输入、可编程稳定时间、低功耗和 H/W 或 S/W 断电功 3.30 | 1ku 12 位,DAC,并行电压输出,可编程设定时间/功耗,自动断电10.65 | 1ku 采用晶圆芯片级封装的 2.7V 至 5.5V、12 位和 10 位八路 DAC12.15 | 1ku 采用晶圆芯片级封装的 2.7V 至 5.5V、12 位和 10 位八路 DAC10.65 | 1ku 2.7V 至 5.5V 12 位 8 通道串行 DAC4.40 | 1ku 12 位、2.5us 二路 DAC、串行输入、可编程稳定时间、同步更新、低功耗6.60 | 1ku 12 位、125MSPS、CommsDAC、差动 介于 2mA 至 20mA 的可变电流输出集成模拟外设。

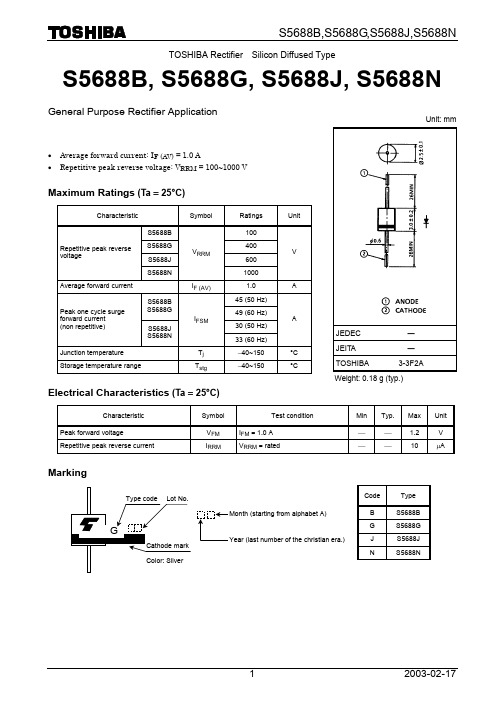

S5688B中文资料

TOSHIBA Rectifier Silicon Diffused TypeS5688B, S5688G, S5688J, S5688NGeneral Purpose Rectifier Application· Average forward current: I F (AV) = 1.0 A· Repetitive peak reverse voltage: V RRM = 100~1000 VMaximum Ratings (Ta = 25°C)Characteristic Symbol RatingsUnitS5688B 100S5688G 400S5688J 600 Repetitive peak reversevoltageS5688NV RRM1000V Average forward currentI F (AV) 1.0 A45 (50 Hz) S5688B S5688G49 (60 Hz) 30 (50 Hz) Peak one cycle surge forward current (non repetitive)S5688J S5688NI FSM33 (60 Hz)AJunction temperature T j -40~150 °C Storage temperature rangeT stg-40~150 °CElectrical Characteristics (Ta = 25°C)Characteristic Symbol Test condition Min Typ. Max UnitPeak forward voltageV FM I FM = 1.0 A ¾ ¾ 1.2 V Repetitive peak reverse currentI RRMV RRM = rated¾¾ 10 m AMarkingCode Type B S5688B G S5688GJ S5688J N S5688NUnit: mmJEDEC ― JEITA―TOSHIBA 3-3F2A Weight: 0.18 g (typ.)i F - v FTa (max) - I F (AV)Surge forward current (non-repetitive)Instantaneous forward voltage v F(V)Number of cycles at 50 Hz and 60 HzTime t (s)M a x i m u m a l l o w a b l e a m b i e n t t e m p e r a t u r e T a (m a x ) (°C )I n s t a n t a n e o u s o n -s t a t e c u r r e n t i F (A )T r a n s i e n t t h e r m a l i m p e d a n c e r t h (j -a ) (°C /W )S u r g e f o r w a r d c u r r e n t I F S M (A )0.0010.010.1110 100010013 5 1010030 50 0.40.8 1.2 1.6 2.0 2.4 3.22.8· TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.. · The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer’s own risk. · The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others. · The information contained herein is subject to change without notice.000707EAARESTRICTIONS ON PRODUCT USE。

AD5687 AD5687R AD5697 AD5697R 16位数字模拟转换器 (DAC) 数据手

Rev. 0Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved. Technical Support 功能框图图1.表1. 相关器件接口基准电压源12位10位SPI 内部AD5687R N/A外部AD5687 AD53131I2C 内部AD5697R AD5338R1外部N/A AD533811AD5313R和AD5313引脚或软件不兼容;同样地,AD5338R和AD5338引脚或软件不兼容。

SCLKV LOGICSYNCSDINSDOINPUTREGISTERDACREGISTERSTRINGDAC ABUFFERV OUT AINPUTREGISTERDACREGISTERSTRINGDAC BBUFFERV OUT BV REFGNDV DDPOWER-DOWNLOGICPOWER-ONRESETGAIN =×1/×2INTERFACELOGICRSTSEL GAINLDAC RESETAD5313R2.5VREFERENCE11254-1双通道、10位nano DAC集成2 ppm/°C基准电压源、SPI接口AD5313R 产品特性低漂移2.5 V基准电压源:2 ppm/°C(典型值)小型封装:3 mm × 3 mm、16引脚LFCSP总不可调整误差(TUE):±0.1% of FSR(最大值)失调误差:±1.5 mV(最大值)增益误差:±0.1% of FSR(最大值)高驱动能力:20 mA,0.5 V(供电轨)用户可选增益:1或2(GAIN引脚)复位到零电平或中间电平(RSTSEL引脚)1.8 V逻辑兼容带回读或菊花链的50 MHz SPI低毛刺:0.5 nV-sec鲁棒的HBM(额定值为4 kV)和FICDM ESD(额定值为1.5 kV)性能低功耗:3.3 mW (3 V)2.7 V至5.5 V电源温度范围:−40°C至+105°C应用光收发器基站功率放大器过程控制(PLC I/O卡)工业自动化数据采集系统概述AD5313R属于nano DAC®系列,是一款低功耗、双通道、10位缓冲电压输出数模转换器(DAC)。

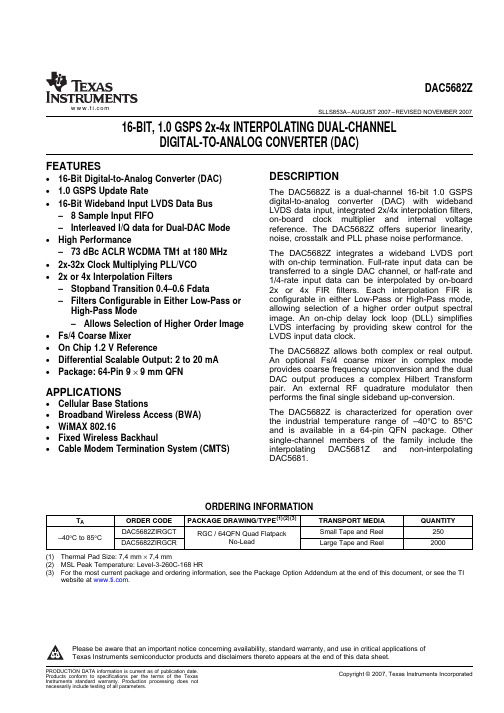

DAC5682Z中文资料

FEATURES

1

• 16-Bit Digital-to-Analog Converter (DAC) • 1.0 GSPS Update Rate • 16-Bit Wideband Input LVDS Data Bus

– 8 Sample Input FIFO – Interleaved I/Q data for Dual-DAC Mode • High Performance – 73 dBc ACLR WCDMA TM1 at 180 MHz • 2x-32x Clock Multiplying PLL/VCO • 2x or 4x Interpolation Filters – Stopband Transition 0.4–0.6 Fdata – Filters Configurable in Either Low-Pass or

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

DAC5682Z RGC PACKAGE

(TOP VIEW)

DAC5682Z

SLLS853A – AUGUST 2007 – REVISED NOVEMBER 2007

DAC5682Z

48 SDENB 47 SCLK 46 SDIO 45 SDO 44 VFUSE 43 D0N 42 D0P 41 D1N 40 D1P 39 DVDD 38 D2N 37 D2P 36 D3N 35 D3P 34 D4N 33 D4P

EM78568中文资料

ELAN MICROELECTRONICS CORP.No. 12, Innovation 1st RD., Science-Based Industrial Park Hsin Chu City, Taiwan, R.O.C. TEL: (03) 5639977FAX: (03)5782037(SL) 5780617 (SA2)EM785688-BIT MICRO-CONTROLLER for FRSVersion 3.5Version HistorySpecification Revision HistoryVersion ContentEM78568version1.0 Initial1.1 Updateerrorsdescriptiondescription1.2 Update1.3 Revise operating voltage for DAC and CTCSS1.4 Change package and pin configuration1.5 1. Remove CTCSS VOX function2. Add Microphone Amp mute function3. Change RE PAGE1 default value from 0x00 to 0xFF4. Change CTCSS tone generation channel 19 setting1.6 1. Update description “program ROM” form 32kx13 16kx132. Update “register configuration” table1.7 Add LCD waveform option bit in the code option. The new option : selectLCD waveform as Type0 or Type1.1.8 1. Change P73 interrupt setting from INT2 to INT32.Update pin configuration and pin description3. Update relative RF, IOCF register bit description4. Change feature description for interrupt numbers2.0 1.Add item 1,2 in the user application note (see user application note)2.Clarify “undefined bits” descriptions. Not allowed to used undefined bits.3. Add LCD Type0 and Type1 waveform2.1 1.Reduce data RAM from 1k to 0.5k. Remove R7 PAGE1 bit1.2.Relayout chip to fit 100-pin compatible with EM78P568bine A/B version distinction2.2 1.Fix bug in the application note.2.Add extra notice in the applicationconsumptionof DC electrical characteristiccurrent2.3 Revise2.4 Revise test condition of electrical characteristic2.5 1.Update operating voltage of Comparator, DAC and CTCSS block in thefeature description2.Add DC voltage characteristic for 2.5VREF.3.Revise sleep current max value from 8uA to 5uA.4.Add description in user application note2.6 1.Add DC characteristic under VDD=3V for 2.5VREF2.Update description in user application noteDCcharacteristic2.7 1.Update2.Fix code option3.Remove /POVD function4.Update user application note2.8 Revised waveform of LCD 1/4 duty for Type 12.9 1.Remove waveform of LCD for Type02.Update DC characteristic for driver/sink current3.0 1 Revise description in operating current for analog circuit2.Revise dB to dBm on level for CTCSS tone to MTX3.5 1. Update VII.10, VII.11 sections2. Add VII.12, VII.13, VII.14 sections3. Update Fig.4, 5 ,7, 10, 124. Add Fig.18, 19. 20, 21, 22, 235. Make some figures with color6. Add OSC and reset timing characteristic in page 507. Update register bit name of IOC6 PAGE1 bit 2 ~ 68. Revised pin number of Fig.26User Application Note(Before using this chip, take a look at the following description note, it includes important messages.)1. There are some undefined bits in the registers. The values in these bits are unpredicted. These bitsare not allowed to use. We use the symbol “-” in the spec to recognize them.2. You will see some names for the register bits definitions. Some name will be appear veryfrequently in the whole spec. The following describes the meaning for the register’s definitions such as bit type, bit name, bit number and so on.3. While in the ICE programming, the user need to follow the rule as :Let “IOCE PAGE0 Bit 4 ~ Bit 7” remain these values to “0”othwise it will generate unpredicted interrupts. Let “IOCC PAGE1 Bit 0” remain its value to “0” unchanged otherwise Comparator and CTCSS function will fail.4.The function difference between EM78568 and EM78P568.FunctionItem EM78568 EM78P568Data RAM 0.5k x 8 1k x 8I/O PC0 PC0 ~ PC7PB0 ~ PB7LCD driver SEG0 ~ SEG19 SEG0 ~ SEG31Package 100-pin QFP,63-pin die 100-Pin QPF, 78-pin dieDC characteristicMaxUnitCondition Min Typ Parameter SymbolInternal 2.5V ref.. 2.5VREF VDD=5V, 25 deg for EM78568 2.32 2.46 2.58 VVoltage VDD=5V, 25 deg for EM78P568 2.14 2.26 2.38 VVDD=3V, 25 deg for EM78568 2.22 2.36 2.48 VVDD=3V, 25 deg for EM78P568 2.04 2.18 2.3 V5. In the feature description CPU operating voltage 2.2 ~ 5.5V, the minimum operating voltage 2.2Vis under maximum main clock = 3.5826MHz.I. General DescriptionThe EM78568 is an 8-bit RISC type microprocessor with low power, high speed CMOS technology. This integrated single chip has an on_chip watchdog timer (WDT), program ROM, data RAM, LCD driver, programmable real time clock/counter, internal interrupt, power down mode, built-in 8-bit D/A converter, 5-bit Comparator, DAC tone generator, CTCSS analog circuit, programming dual tone generator and tri-state I/O.II. FeatureCPUE Operating voltage : 2.2V¡ 5.5VE16k x 13 program ROME0.5k x 8 on chip data RAME Up to 36 bi-directional tri-state I/O portsE16 level stack for subroutine nestingE8-bit real time clock/counter (TCC)E two 8-bit counters : COUNTER1 and COUNTER2E On-chip watchdog timer (WDT)E99.9¢H single instruction cycle commandsE Four modes (Main clock can be programmed from 447.829k to 17.913MHz generated by internal PLL)Mode CPU status Main clock 32.768kHz clock statusSleep mode Turn off Turn off Turn offIdle mode Turn off Turn off Turn onGreen mode Turn on Turn off Turn onNormal mode Turn on Turn on Turn onE Input port interrupt functionE8 interrupt source , 4 external , 4 internalE Dual clocks operation (Internal PLL main clock , External 32.768KHz)PROGRAMMING TONE GENERATORSE Operating voltage : 2.2V¡ 5.5VE Programming Tone1 and Tone2 dual tone generatorsE11-bit programming Tone1 generatorsE8-bit programming Tone2 generatorCOMPARATORE Operating voltage : 2.7V ~ 5.5VE3-channel inputE5-bit comparison reference level settingE Internal (2.5V or VDD) or external reference levelDACE Operating : 2.7V¡ 5.5VE8-bit R-2R D/A converterE8-bit programmable tone outputE Easy to direct access as programmable CTCSS tone output by DAC tone generatorE Internal (2.5V or VDD) or external reference levelCTCSS blockE Operating voltage : 2.7V¡ 5.5VE Microphone amplifier (can be used as general OP Amp)E Microphone mute functionE RX input OPE Audio BPF (300Hz ~ 3400Hz)E Sub-audio LPF (60Hz ~ 253Hz) for CTCSS tone detectionE Zero-crossing for detected CTCSS tone frequency outputE CTCSS Tx modulation summing AmpPOVDE Power-on voltage detector resetE Without external reset circuit while enablingLCDE Common driver pins : 4E Segment driver pins : 20E1/3 biasE1/4 duty, 1/2 dutyE16 Level LCD contrast control by softwarePACKAGEE100-pin QFP (EM78568Q)63-pin die (EM78568H)III. ApplicationFRS (Family Radio Systems) and other wireless portable productsIV. Pin ConfigurationNC NC NC NC NC NC 12345678910111213141516171821222425272829305049484746454443424140393837363575747370696867666564636261605958575655545352512026333419233132C M P 1/P 62P 61P 60P 877271S E G 13/P 97S E G 12/P 57S E G 11/P 56S E G 10/P 5582838485868788899091929394959697989910081S E G 14/P 96S E G 15/P 95NC NC NC NC PC0S E G 1S E G 9S E G 8S E G 7S E G 6S E G 5S E G 4S E G 3S E G 2D A O /P 67M T X /P 66A U R X /P 65C M P 3/P 64C M P 2/P 63P 86P 85X I NX O U TV S SP 84P 83P 82NC NC NC NC NC NC 807978NC 7776NC NC NC NC P77P76P75P74INT3/P73INT2/P72INT1/P71INT0/P70VDDP 81P 80AVDD RXO RXI NC NC PLLC MICI MICO TONE NC NC NC /R E S E TAVSSS E G 16/P 94S E G 18/P 92S E G 19/P 91P 90S E G 17/P 93SEG0COM3COM2COM1COM0NC NC NC NC NC NC NC NC NC NC NC100-pin QFP or 63-pin dieFig.1b Pin assignmentV. Functional Block DiagramFig.2a Block diagramP90~P97PC0Fig.2b Block diagramVI. Pin DescriptionsPIN I/O DESCRIPTION POWERVDD AVDD POWER DigitalpowerAnalog powerVSS AVSS POWER DigitalgroundAnalog groundCLOCKXIN I Input pin for 32.768 kHz oscillatorXOUT O Output pin for 32.768 kHz oscillatorPLLC I Phase loop lock capacitor, connect a capacitor 0.01u to 0.047u to the ground. LCDCOM0 ~ COM3 O Common driver pins of LCD driversSEG0 ~ SEG9 SEG10 ~ SEG12 SEG13 ~ SEG19 OO (I/O : PORT5)O (I/O : PORT9)Segment driver pins of LCD driversSEG10 to SEG19 are shared with IO PORT.Programmingtone generatorsTONE O Programming single tone or dual tone output ComparatorCMP1 CMP2 CMP3 I (P62)I (P63)I (P64)Comparator input pins. Shared with PORT62, PORT63 and PORT64.8-bit D/ADAO O (P67) D/A converter output pin.Shared with PORT67CTCSSMICO O Microphone amplifier output. Put a feedback resistor to adjust the gain MICI I Microphone amplifier inputRXO O Receiver amplifier output. Put a feedback resistor to adjust the gain RXI I Receiver amplifier inputAURX O(P65) Receiving audio outputShare with PORT65MTX O (P66) Modulation transmission output for CTCSS toneShared with PORT66IOP55~P57 I/O PORT5 can be INPUT or OUTPUT port each bit.PORT5(7:5) are shared with LCD Segment signal.P60 ~P67 I/O PORT6 can be INPUT or OUTPUT port each bit.P70 ~ P77 I/O PORT7 can be INPUT or OUTPUT port each bit.Internal Pull high function.PORT7(0~3) has interrupt function.P80 ~ P87 I/O PORT8 can be INPUT or OUTPUT port each bit.Internal pull high.PORT8(0~3) have wake-up functions(set by RE PAGE0)VII. Functional DescriptionsVII.1 Operational RegistersRegister configurationR PAGE registers IOC PAGE registers Addr R PAGE0 R PAGE1 IOC PAGE0 IOC PAGE100 Indirect addressing01 TCC02 PC03 Page, Status04 RAM bank, RSR05 Port5 I/O data,Program ROM page LCD RAM address Port5 I/O control,LCD bias controlComparator control06 Port6 I/O data LCD RAM data buffer Port6 I/O control Port6 switches07 Port7 I/O data CTCSS detection output,Data RAM bankPort7 I/O control Port7 pull high08 Port8 I/O data Data RAM address Port8 I/O control Port8 pull high09 Port9 I/O data Data RAM data buffer Port9 I/O control Port9 switches0A PLL, Main clock,Comparator flag,WDTE DAC input data buffer TONE2 control DAC control,2.5V ref control0B0C PortC I/O data Counter1 data PortC I/O control Port5 switch0D LCD control Counter2 data TONE1 control Clock source(CN1,CN2)Prescaler(CN1,CN2)0E Wake-up control, DAC tone selection TONE1 extra control, CTCSS control switches0F Interrupt flag Interrupt mask10 16 bytes: Common registers1F20 Bank0~Bank3: Common registers3F (32x8 for each bank)VII.2 Operational Register Detail DescriptionR0 (Indirect Addressing Register)R0 is not a physically implemented register. It is used as indirect addressing pointer. Any instruction using R0 as register actually accesses data pointed by the RAM Select Register (R4).Example:Mov A, @0x20 ;store a address at R4 for indirect addressingMov 0x04, AMov A, @0xAA ;write data 0xAA to R20 at bank0 through R0Mov 0x00, AR1 (TCC)TCC data buffer. Increased by 16.384KHz or by the instruction cycle clock (controlled by CONT register). Written and read by the program as any other register.R2 (Program Counter)The structure is depicted in Fig. 5.Generates 16k × 13 on-chip PROGRAM ROM addresses to the relative programming instruction codes. "JMP" instruction allows the direct loading of the low 10 program counter bits."CALL" instruction loads the low 10 bits of the PC, PC+1, and then push into the stack."RET'' ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack."MOV R2, A" allows the loading of an address from the A register to the PC, and the ninth and tenth bits are cleared to "0''."ADD R2,A" allows a relative address be added to the current PC, and contents of the ninth and tenth bits are cleared to "0''."TBL" allows a relative address added to the current PC, and contents of the ninth and tenth bits don't change. The most significant bit (A10~A13) will be loaded with the contents of bit PS0~PS3 in the status register (R5 PAGE0) upon the execution of a "JMP'', "CALL'', "ADD R2, A'', or "MOV R2, A'' instruction.If an interrupt is triggered, PROGRAM ROM will jump to address 0x08 at page0. The CPU will store ACC, R3 status and R5 PAGE automatically, and they will be restored after instruction RETI.Fig.3 Program counter organizationR3 (Status, Page selection)PAGE0 (Status flag, Page selection bits)7 6 5 4 3 2 1 0 RPAGE2 RPAGE IOCPAGE T P Z DC C R/W-0 R/W-0 R/W-0 R R R/W R/WR/W Bit 0(C) : Carry flagBit 1(DC) : Auxiliary carry flagPCR5(PAGE)Bit 2(Z) : Zero flagBit 3(P) : Power down bitSet to 1 during power on or by a "WDTC" command and reset to 0 by a "SLEP" command.Bit 4(T) : Time-out bitSet to 1 by the "SLEP" and "WDTC" command, or during power up and reset to 0 by WDT timeout.REMARKEVENT TPWDT wake up from sleep mode 0 0WDT time out (not sleep mode) 0 1/RESET wake up from sleep 1 0Power up 1 1Low pulse on /RESET x x x : don't careBit 5(IOCPAGE) : change IOC5 ~ IOCE to another pagePlease refer to Fig.4 control register configuration for details.0/1 page0 / page1Bit 6(RPAGE) : change R5 ~ RE to another pagePlease refer to Fig.4 control register configuration for details.0/1 page0 / page1Bit 7(RPAGE2) : change R5 ~ RE to R page2 (remain this bit to “0” unchanged)0 The page for R5 ~ RE depends on Bit 6(RPAGE)1 change R5 ~ RE to page2R4 (RAM selection for common registers R20 ~ R3F))(RAM selection register)7 6 5 4 3 2 1 0RB1 RB0 RSR5 RSR4 RSR3 RSR2 RSR1 RSR0R/W-0 R/W-0 R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 5 (RSR0 ~ RSR5) : Indirect addressing for common registers R20 ~ R3FRSR bits are used to select up to 32 registers (R20 to R3F) in the indirect addressing mode.Bit 6 ~ Bit 7 (RB0 ~ RB1) : Bank selection bits for common registers R20 ~ R3FThese selection bits are used to determine which bank is activated among the 4 banks for 32 register (R20 to R3F)..Please refer to VII.1 Operational Registers for details.R5 (PORT5 I/O data, Program page selection, LCD address)PAGE0 (PORT5 I/O data register, Program page register)7 6 5 4 3 2 1 0P57 P56 P55 - PS3 PS2 PS1 PS0R/W R/W R/W R/W-0 R/W-0 R/W-0 R/W-0Bit 0 ~ Bit 3 (PS0 ~ PS3) : Program page selection bitsPS3 PS2 PS1PS0 Program memory page (Address)0 0 0 0 Page10 0 0 1 Page20 0 1 0 Page30 0 1 1 Page: : : : :141 1 1 0 Page151 1 1 1 PageUser can use PAGE instruction to change page to maintain program page by user. Otherwise, user can use far jump (FJMP) or far call (FCALL) instructions to program user's code. And the program page is maintained by EMC's complier. It will change user's program by inserting instructions within program.Bit 4 : (undefined) not allowed to useBit 5 ~ Bit 7 (P55 ~ P57) : 8-bit PORT5(5~7) I/O data registerUser can use IOC register to define input or output each bit.PAGE1 (LCD address)7 6 5 4 3 2 1 0LCDA3LCDA2LCDA1LCDA0 - - - -R/W-0R/W-0R/W-0R/W-0Bit 0 ~ Bit 3 (LCDA0 ~ LCDA3) : LCD address for LCD RAM read or writeThe address of the LCD RAM correspond to the COMMON and SEGMENT signals as the table.COM3 ~ COM0 LCD address(LCDA3 ~ LCDA0)SEG1, SEG0 00HSEG3, SEG2 01HSEG5, SEG4 02HSEG7, SEG6 03HSEG9, SEG8 04HSEG11, SEG10 05HSEG13, SEG12 06HSEG15, SEG14 07HSEG17, SEG16 08HSEG19, SEG18 09HBit 4 ~ Bit 7 : (undefined) not allowed to useR6 (PORT6 I/O data, LCD data)PAGE0 (PORT6 I/O data register)7 6 5 4 3 2 1 0P67 P66 P65 P64 P63 P62 P61 P60R/W R/W R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 8 (P60 ~ P67) : 8-bit PORT6(0~7) I/O data registerUser can use IOC register to define input or output each bit.PAGE1 (LCD data)7 6 5 4 3 2 1 0LCDD7 LCDD6 LCDD5 LCDD4LCDD3LCDD2LCDD1LCDD0R/W R/W R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 7 (LCDD0 ~ LCDD7 ) : LCD data buffer for LCD RAM read or writeLCD data vs. COM-SEG LCD addressLCDD7 ~ LCDD4LCDD3 ~ LCDD0(LCDA3 ~ LCDA0)COM3 ~ COM0COM3 ~ COM0SEG1 SEG0 00HSEG3 SEG2 01HSEG5 SEG4 02HSEG7 SEG6 03HSEG9 SEG8 04HSEG11 SEG10 05HSEG13 SEG12 06HR7 (PORT7 I/O data, Data RAM bank)PAGE0 (PORT7 I/O data register)7 6 5 4 3 2 1 0P77 P76 P75 P74 P73 P72 P71 P70R/W R/W R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 7 (P70 ~ P77) : 8-bit PORT7(0~7) I/O data registerUser can use IOC register to define input or output each bit.PAGE1 (VOX detection output, CTCSS detection output, Data RAM bank selection bit)7 6 5 4 3 2 1 0- - - - - RAM_B0 -DETOR R/W-0 Bit 0 (RAM_B0) : Data RAM bank selection bitEach bank has address 0 ~ address 255 which is total 256 (0.25k) bytes RAM size.Data RAM bank selection : (Total RAM = 1.0K)RAM_B1 RAM_B0 RAMbank0 0 Bank00 1 Bank11 0 Bank21 1 Bank3Bit 1 ~ Bit 5 : (undefined) not allowed to useBit 6(DETO) : CTCSS tone detectionThe signal passing CTCSS sub audio LPF will be extracted CTCSS tone. Then this tone will go into the ZC(Zero-crossing detector) and output to DETO bit. This bit reflects the CTCSS tone frequency pulse waveform. The user can count the timing to get the CTCSS frequency. Also see IOCE PAGE1 for CTCSS block and switch control.Bit 7 : (undefined) not allowed to useR8 (PORT8 I/O data, Data RAM address)PAGE0 (PORT8 I/O data register)7 6 5 4 3 2 1 0P87 P86 P85 P84 P83 P82 P81 P80R/W R/W R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 7 (P80 ~ P87) : 8-bit PORT8(0~7) I/O data registerUser can use IOC register to define input or output each bit.PAGE1 (Data RAM address register)7 6 5 4 3 2 1 0RAM_A7 RAM_A6 RAM_A5 RAM_A4RAM_A3RAM_A2RAM_A1RAM_A0R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0R/W-0 R/W-0Bit 0 ~ Bit 7 (RAM_A0 ~ RAM_A7) : data RAM addressThe data RAM bank’s selection is from R7 PAGE1 bit0 ~ bit 1 (RAM_B0 ~ RAM_B1).R9 (PORT9 I/O data, Data RAM data buffer)PAGE0 (PORT9 I/O data register)7 6 5 4 3 2 1 0P97 P96 P95 P94 P93 P92 P91 P90R/W R/W R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 7 (P90 ~ P97) : 8-bit PORT9(0~7) I/O data registerUser can use IOC register to define input or output each bit.PAGE1 (Data RAM data register)7 6 5 4 3 2 1 0RAM_D7 RAM_D6 RAM_D5 RAM_D4RAM_D3RAM_D2RAM_D1RAM_D0R/W R/W R/W R/W R/W R/W R/W R/WBit 0 ~ Bit 7 (RAM_D0 ~ RAM_D7) : Data RAM’s dataThe address for data RAM is accessed from R8 PAGE1. The data RAM bank is selected by R7 PAGE1 Bit0 ~ Bit 1 (RAM_B0 ~ RAM_B1).RA (PLL, Main clock selection, Comparator flag, Watchdog timer, DAC input data buffer) PAGE0 (PLL enable bit, Main clock selection bits, Comparator control bits, Watchdog timer enable bit)7 6 5 4 3 2 1 0IDLE PLLEN CLK2 CLK1 CLK0 CMPFLAG CMPREF WDTENR/W-0 R/W-0 R/W-0 R/W-1R/W-1 R R/W-0 R/W-0Bit 0(WDTEN) : Watch dog control bitUser can use WDTC instruction to clear watch dog counter. The counter 's clock source is 32768/2 Hz. If the prescaler assigns to TCC. Watch dog will time out by (1/32768 )*2 * 256 = 15.616mS. If the prescaler assigns to WDT, the time of time out will be more times depending on the ratio of prescaler.0/1 disable/enableBit 1(CMPREF) : Comparator’s reference voltage source selection bit0 Comparator’s reference voltage is driven from internal bias resistor string. This reference voltage levelcan be set by RD PAGE0 bit 0 ~ bit 5 (CMP_B0 ~ CMP_B5).1 Comparator’s reference voltage is driven from external bias. This reference voltage input is CMP3/P65pin. Also IOC6 PAGE1 bit 2(CMP63/P63) should be set to “1”.Bit 2(CMPFLAG) : Output of the comparator0 Input voltage < reference voltage1 input voltage > reference voltageBit 3 ~ Bit 5 (CLK0 ~ CLK2) : MAIN clock selection bitsUser can choose different frequency of main clock by CLK1 and CLK2. All the clock selection is list below.PLLEN CLK2 CLK1 CLK0 Sub clock MAIN clock CPU clockmode)(Normal1 0 0 0447.829kHz32.768kHz447.829kHzmode)(Normal32.768kHz895.658kHz895.658kHz1 0 0 1mode)(Normal1.791MHz1 0 1 032.768kHz 1.791MHzmode)(Normal3.582MHz1 0 1 132.768kHz 3.582MHzmode)(Normal1 1 0 07.165MHz32.768kHz7.165MHzmode)(Normal32.768kHz10.747MHz10.747MHz1 1 0 1mode)(Normal32.768kHz14.331MHz14.331MHz1 1 1 0mode)(Normal32.768kHz17.913MHz17.913MHz1 1 1 10 don’t care don’t care32.768kHz don’t care 32.768kHz (Green mode)Bit 6(PLLEN) : PLL's power control bit which is CPU mode control register 0/1 disable PLL/enable PLLIf enable PLL, CPU will operate at normal mode (high frequency). Otherwise, it will run at green mode (low frequency, 32768 Hz).System clockFig.4 The relation between 32.768kHz and PLLBit 7(IDLE) : Sleep mode or IDLE mode control after using "SLEP" instruction. 0/1 SLEEP mode/IDLE mode.This bit will decide SLEP instruction which mode to go.The status after wake-up and the wake-up sources list as the table below. Wakeup signalSLEEP modeIDLE modeRA(7,6)=(0,0) + SLEP RA(7,6)=(1,0)+ SLEPTCC time out IOCF bit0=1No function (1) Wake-up (2) Jump to SLEP next instruction COUNTER1 time out IOCF bit1=1 No function (1) Wake-up (2) Jump to SLEP next instruction COUNTER2 time out IOCF bit2=2 No function (1) Wake-up (2) Jump to SLEP next instruction WDT time out Reset and jump to address 0 (1) Wake-up(2) Next instructionPORT8(0~3) RE PAGE0 bit3 or bit4 or bit5 or bit6 = 1 Reset and Jump to address 0 (1) Wake-up (2) Jump to SLEP next instruction PORT7(0~3) IOCF bit3 or bit4 or bit5 or bit7=1Reset and Jump to address 0 (1) Wake-up (2) Jump to SLEP next instruction <Note> PORT70 's wakeup function is controlled by IOCF bit 3. It's falling edge or rising edge trigger(controlled by CONT register bit7).PORT7(1~3) 's wakeup functions are controlled by IOCF bit (4,5,7). They are falling edge trigger. PORT80~PORT83’s wakeup function are controlled by RE PAGE0 bit 0 ~ bit 3. They are falling edge trigger.PAGE1 (DAC input data register)7 6 5 4 3 2 1 0DA7 DA6 DA5 DA4 DA3 DA2 DA1 DA0R/W-1 R/W-1 R/W-1 R/W-1R/W-1 R/W-1 R/W-1 R/W-1 Bit 0 ~ Bit 7 (DA0 to DA7) : DA converter data bufferRC (PORTC0 I/O data, Counter1 data)PAGE0 (PORT9 I/O data register)7 6 5 4 3 2 1 0- - - - - - - PC0R/WBit 0 (PC0) : PORTC0 I/O data registerUser can use IOC register to define input or output this bit.Bit 1 ~ Bit 7 : (undefined) not allowed to usePAGE1 (Counter1 data register)Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0CN17 CN16 CN15 CN14 CN13 CN12 CN11 CN10R/W-0 R/W-0 R/W-0 R/W-0R/W-0 R/W-0 R/W-0 R/W-0Bit 0 ~ Bit 7 (CN10 ~ CN17) : Counter1's buffer that user can read and write.Counter1 is a 8-bit up-counter with 8-bit prescaler that user can use RC PAGE1 to preset and read the counter.(write preset) After a interruption , it will reload the preset value.Example for writing :MOV 0x0C, A ; write the data at accumulator to counter1 (preset)Example for reading :MOV A, 0x0C ; read the data at counter1 to accumulatorRD (LCD control, Counter2 data)PAGE0 (LCD driver control bits)7 6 5 4 3 2 1 0LCD_C1LCD_C0LCD_MDETOED- - - -R/W-0R/W-0R/W-0 R/W-0Bit 0 (LCD_M) : LCD operation method including duty and frame frequencyBit 1 ~ Bit 2 (LCD_C0 ~ LCD_C1) : LCD display controlLCD_C1 LCD_C0LCD_M LCD Display Control Duty Bias0 0 0 change duty 1/4 1/3LCD)1/2 1/3off1Disable(turnBlanking : :0 1 :enable : :displayLCD1 1 :Ps. To change the display duty must set the "LCD_C1 ,LCD_C0" to "00".The controller can drive LCD directly. The LCD block is made up of common driver, segment driver, display LCD RAM, common output pins, segment output pins and LCD operating power supply. The basic structure contains a timing control. This timing control uses the basic frequency 32.768KHz to generate the proper timing for different duty and display access.RD PAGE0 Bit 0 ~ Bit 2 are LCD control bits for LCD driver. These LCD control bits determine the duty, the number of common and the frame frequency. The LCD display (disable, enable, blanking) is controlled by Bit 1 and Bit 2. The driving duty is decided by Bit 0. The display data is stored in LCD RAM which address and data access controlled by registers R5 PAGE1 and R6 PAGE1.User can regulate the contrast of LCD display by IOC5 PAGE0 Bit 0 ~ Bit 3 (BIAS0 ~ BIAS3). Up to 16 levels contrast is convenient for better display. Bit 3 ~ Bit 6 : (undefined) not allowed to use.Bit 7 (DETOED) : the interrupt triggering edge control for CTCSS tone detection output 0/1 falling edge/falling and rising PAGE1 (Counter2 data register)Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 CN27 CN26 CN25 CN24 CN23 CN22 CN21 CN20 R/W-0 R/W-0 R/W-0 R/W-0R/W-0 R/W-0 R/W-0 R/W-0 Bit 0 ~ Bit 7 (CN20 ~ CN27) : Counter2's buffer that user can read and write.Counter2 is a 8-bit up-counter with 8-bit prescaler that user can use RD PAGE1 to preset and read the counter.(write preset) After a interruption, it will reload the preset value. Example for writing :MOV 0x0D, A ; write the data at accumulator to counter2 (preset) Example for reading :MOV A, 0x0D ; read the data at counter2 to accumulatorRE (Wake-up control, DAC tone output frequency selection)PAGE0 (Interrupt flag, Wake-up control bits)7 6 5 4 3 2 1 0 - - - - /WUP83/WUP82/WUP81/WUP80 R/W-0 R/W-0 R/W-0 R/W-0 Bit 0 (/WUP80) : PORT80 wake-up control, 0/1 disable/enable P80 pin wake-up function Bit 1 (/WUP81) : PORT81 wake-up control, 0/1 disable/enable P81 pin wake-up function Bit 2 (/WUP82) : PORT82 wake-up control, 0/1 disable/enable P82 pin wake-up function Bit 3 (/WUP83) : PORT83 wake-up control, 0/1 disable/enable P83 pin wake-up function Bit 4 ~ Bit 7 : (undefined) not allowed to use PAGE1 (Programmable D/A tone selection register)7 6 5 4 3 2 1 0 DAT7 DAT6 DAT5 DAT4 DAT3DAT2DAT1DAT0R/W-1 R/W-1 R/W-1 R/W-1 R/W-1R/W-1R/W-1R/W-1Bit 0 ~ Bit 7 (DAT0 ~ DAT7) : D/A tone output frequency selectionThe programmable D/A tone output frequency = 447829Hz / Mi / 32, where Mi = DAT7 ~ DAT0 = 1 ~ 255 When Mi = DAT7 ~ DAT0 = 0 or DAT/DAD(IOCA PAGE1 Bit 7) = 0, the D/A tone output generation circuit will be disabled. It is specially used for CTCSS tone generation. Also refer to DAC for detailsfm =DAT/DADFig.5 Programmable DAC tone generationFor example : CTCSS tone generation :Channel DAT7~DAT0 D/A tonegeneration CTCSStoneMi Act.Freq.- 00000000Disable- - - 1 11010001Enable 67.0 209 66.9602 11001010 69.3 202 69.2803 11000011 71.9 195 71.7674 10111100 74.4 188 74.4405 10110110 77.0 182 76.8946 10110000 79.7 176 79.5157 10101010 82.5 170 82.3228 10100100 85.4 164 85.3339 10011110 88.5 158 88.57410 10011001 91.5 153 91.46811 10010100 94.8 148 94.55812 10010000 97.4 144 97.18513 10001100 100.0 140 99.96214 10000111 103.5 135 103.66415 10000011 107.2 131 106.82916 01111110 110.9 126 111.06917 01111010 114.8 122114.71018 01110110 118.8 118118.59919 01110010 123.0 114122.76020 01101110 127.3 110127.22421 01101010 131.8 106132.02522 01100111 136.5 103135.87023 01100011 141.3 99 141.36024 01100000 146.2 96 145.77825 01011100 151.4 92 152.11626 01011001 156.7 89 157.24327 01011000 159.8 88 159.03028 01010110 162.2 86 162.72929 01010011 167.9 83 168.61030 01010001 173.8 81 172.77331 01001110 179.9 78 179.41932 01001100 183.5 76 184.14033 01001011 186.2 75 186.59534 01001010 189.9 74 189.11735 01001001 192.8 73 191.70836 01000111 196.6 71 197.10837 01000110 199.5 70 199.92438 01000101 203.5 69 202.82139 01000100 206.5 68 205.80440 01000010 210.7 66 212.04041 01000000 218.1 64 218.66742 00111110 225.7 62 225.72043 00111101 229.1 61 229.42144 00111100 233.6 60 233.24445 00111010 241.8 58 241.28746 00111000 250.3 56 249.90547 00110111 254.1 55 254.448。

16位dac5686

PZP (S-PQFP-G100)THERMAL PAD MECHANICAL DATAPowerPAD ™PLASTIC QUAD FLATPACKSLWS147 - APRIL 2003IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Mailing Address:Texas InstrumentsPost Office Box 655303Dallas, Texas 75265Copyright 2003, Texas Instruments Incorporated。

高速数模转换芯片DAC5682在3G数字中频发射机中的应用

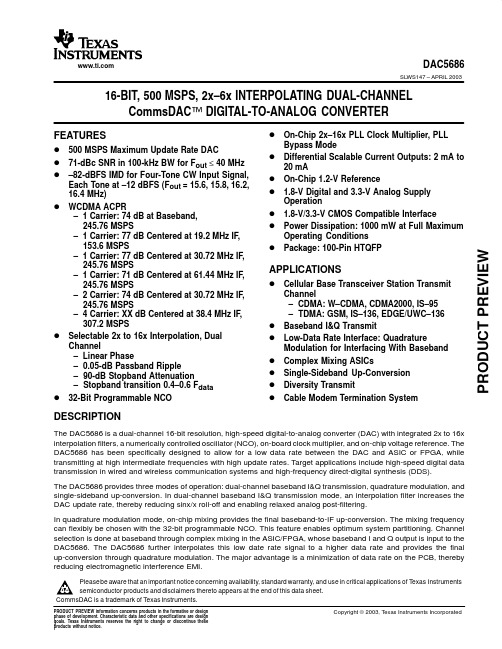

T e c h n o l o g i e s赵东亮,张捷(西北工业大学电子信息学院,陕西 西安 710072)【摘 要】文章给出了一种基于DAC5682的3G数字中频发射机的实现方案,通过与传统模拟发射机实现方案的对比,指出了基于软件无线电数字中频化思想的数字中频发射机实现方案的优势所在。

同时也研究了DAC5682的工作原理,介绍了DAC5682的主要技术特点,给出了其在3G系统应用中的典型配置,并给出了典型应用电路,最后指出了DAC5682在实际应用中应该注意的问题。

【关键词】数字中频;数字上变频;DAC5682【中图分类号】TN91 【文献标识码】A 【文章编号】1009-8054(2009) 07-0070-03Application of High-speed DAC DAC5682 in 3G Digital Intermediate-Frequency TransmitterZHAO Dong-liang, ZHANG Jie(College of Electronic Information, Northwestern Polytechnical University, Xi’an Shaanxi 710072, China)【Abstract 】In this paper, a solution of 3G digital intermediate-frequency transmitter based on DAC5682 is proposed,and its comparison with traditional, analog transmitter, indicates the advantage of the solution based on Software Defined Radio. The principle of DAC5682 is atudied, the main features of DAC5682 is described, the typical configuration and typical peripheral circuit also is given in this paper. Finally, the problems to which users should pay attention are men-tioned in DAC5682 application.【Keywords 】digital intermediate-frequency; digital up-conversion; DAC5682高速数模转换芯片DAC5682在3G 数字中频发射机中的应用0 引言随着3G标准的迅猛发展,其宽带信号、高信号采样速率的特点已使传统的数模转换器件已不能胜任新3G产品的应用。

DAC5688使用..

DAC5688使用指南一.正确的上电初始化顺序:1.Supply all 1.8V (CLKVDD, DVDD, VFUSE) and 3.3V (AVDD and IOVDD) voltages.2.Set TXENABLE low to disable any undesired transmit3.Toggle RESETB pin for a minimum 25 nSec active low pulse width.4.Provide a stable CLK2/C input clock.(In dual clk mode, must provide a stable CLK1 also.)5.Program all desired SIF registers.6.Provide a sync signal to all digital blocks. The sync input source may be either TXENABLE pin,SYNC pin or a software sync via CONFIG5 sif_sync_sig bit; however, only the TXENABLE orSYNC pins are recommended for multi-DAC synchronization. Refer to CONFIG5, CONFIG22and CONFIG23 registers for sync source selection. Note: Registers CONFIG6 throughCONFIG13 all require a sync input to transfer the contents of the control register inputs tothe active digital blocks.7.Provide data flow.8.Set TXENABLE high to enable the DAC outputs注意事项:在步骤5发同步信号之前一定要保证CLK2和CLK1(在dual clk mode下) 已经稳定得送给DAC5688, 否则该同步信号无效。

迪比特5688

迪比特5688迪比特5688是一款功能强大的微控制器,广泛应用于电子产品中。

它以其高性能、低功耗和可靠性而备受青睐。

本文将介绍迪比特5688的特点、应用领域以及其在电子产品中的优势。

首先,迪比特5688具有出色的性能。

它采用先进的32位ARM Cortex-M4内核,主频高达150MHz,具有强大的计算能力和高速数据处理能力。

同时,其具备丰富的存储器资源,包括128KB的Flash存储器和16KB的RAM,能够满足复杂应用程序的需求。

其次,迪比特5688具有低功耗特性。

它采用先进的功耗管理技术,能够自动调整功耗以延长电池寿命。

此外,它还支持多种低功耗模式,如待机模式和休眠模式,以进一步降低功耗。

这使得迪比特5688成为移动设备和便携式电子产品的理想选择。

迪比特5688还具备极高的可靠性。

它采用了先进的电路设计和工艺制造技术,具备抗干扰能力强、抗电磁干扰性好的特点。

此外,它还支持多种安全特性,如存储器保护和数据加密等,保障了系统的安全性和稳定性。

迪比特5688适用于多个领域的应用。

它可以广泛应用于工业自动化控制、智能家居系统、嵌入式系统和物联网等领域。

在工业自动化控制领域,迪比特5688可以实现对设备的精确控制,提高生产效率和降低能耗。

在智能家居系统中,它可以实现对家电设备的智能控制,提供便利和舒适的居家生活。

在嵌入式系统和物联网领域,迪比特5688可以实现设备之间的互联互通,构建智能化、高效率的系统。

与其他微控制器相比,迪比特5688更具竞争优势。

首先,迪比特5688拥有丰富的外设资源,包括多个通用输入输出口、模拟数字转换器、UART、SPI和I2C等接口,能够满足不同应用的需求。

其次,迪比特5688具有较低的功耗和较高的性能,使其成为低功耗、高性能电子产品的理想选择。

此外,它还提供了强大的开发工具和开发支持,如IDE和软件库等,方便开发者进行软硬件开发。

不仅如此,迪比特5688还拥有良好的生态系统。

8位以上DAC

11/42

16位串行输入 位串行输入D/A转换器 转换器PCM56 位串行输入 转换器 PCM56应用技术 应用技术

为了保证准确调节,应在加电5到10分钟后再工作,这是 分钟后再工作, 为了保证准确调节,应在加电 到 分钟后再工作 因为在刚加电后,芯片有一段加热时间,芯片温度会变化, 因为在刚加电后,芯片有一段加热时间,芯片温度会变化,会 使转换不准确, 到 分钟后才会稳定 分钟后才会稳定。 使转换不准确,5到10分钟后才会稳定。 调节时首先输入 进制的 调节时首先输入16进制的 输入 进制的7FFF,再用 位半的数字电压表 ,再用6位半的数字电压表 测量芯片的音频输出电压,并记录下来。 测量芯片的音频输出电压,并记录下来。 进制的8000,调节图中的 电位器, 再输入16进制的 输入 进制的 ,调节图中的100K 电位器,使得芯 片音频输出为92µV,大于前面的测试值(1LSB对应于 对应于92µV)。 片音频输出为 ,大于前面的测试值( 对应于 )。

14 MSB Adjust(1) 13 12 11 10 9 Sj Rf 模拟输出 Vout ±3.0V Iout 模拟地

Data 7 -5V 1μF -VL 8

PCM56内部结构与引脚图

由CLK、LE、 、 、 Data三个引脚输入 三个引脚输入 时钟脉冲、控制信 时钟脉冲、 串行数据; 号和串行数据; 这些数据进入控制 这些数据进入控制 逻辑和移位电路, 逻辑和移位电路, 然后进入16位串行 然后进入 位串行 转并行数据转换器 转换为16位并行数 转换为 位并行数 据; 再进入16位 再进入 位DAC数 数 据锁存器锁存, 据锁存器锁存,再 进入16位电流输出 进入 位电流输出 转换器。 型DA转换器。 转换器

16位串转并转换器控制逻辑与电平判别电路16位电流输出1011121314151616位dacvldataleclknc5vvl5vvs5vvstrim1msbadjust1ioutsj模拟地rfvout30v模拟输出pcm56内部结构与引脚图94216位串行输入da转换器pcm5616位串转并转换器控制逻辑与电平判别电路16位电流输出1011121314151616位dacvldataleclknc5vvl5vvs5vvstrim1msbadjust1ioutsj模拟地rfvout30v模拟输出图4612pcm56内部结构与引脚图pin记忆符pin记忆符p1模拟负电源p9电压输outp2逻辑地dgndp10反馈电rfp3逻辑正电源vlp11加法器连接sjp4ncp12模拟地agndp5时钟输clkp13电流输outp6号输入lep14msbmsbdajp7串行数据输入datap15msbtrimp8逻辑负电源vlp16模拟正电源104216位串行输入da转换器pcm5616位串转并转换器控制逻辑与电平判别电路16位电流输出1011121314151616位dacvldataleclknc5vvl5vvs5vvstrim1msbadjust1ioutsj模拟地rfvout30v模拟输出图4612pcm56内部结构与引脚图pcm56与微机的接口电路主要是通过微处理器进行连接由微机通过各种总线isapcican等将数据和控制命令发送给微处理器再由微处理器以串行方式将数据传送给pcm56控制pcm56进行转换输微处理器可以是dsp器件也可以是单片114216位串行输入da转换器pcm56pcm56的主要技术指标如下

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。