MII

各种MII详解(MII,GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI)

简介MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:T XD(Transmit Data)[3:0]:数据发送信号,共4根信号线;RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

MII接口介绍

视频硬件培训方案-MII接口介绍蒋汉初1.MII接口名词解释MII (Media Independent Interface 介质无关接口) MII即媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

MII接口一定会包含两部分,一个数据接口,以及一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号线接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII 管理接口(Management interface)只有两条信号线,就是我们熟悉的MDC/MDIO接口。

2.MII接口种类MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

我们在这里只讨论MII、RMII、SMII、GMII接口。

MII 支持10 兆和100 兆的操作,它要求是25 兆的总线时钟,一个接口由14 根线组成(没考虑收发时钟),它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8 端口的交换机要用到112 根线,16 端口就要用到224 根线,到32 端口的话就要用到448 根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII 简化出来的标准,比如RMII、SMII、GMII 等。

RMII 是简化的MII 接口,在数据的收发上它比MII 接口少了一倍的信号线,所以它一般要求是50 兆的总线时钟。

RMII 一般用在多端口的交换机,它不是每个端口安排收、发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目。

RMII 的一个端口要求7 根数据线,比MII 少了一倍,所以交换机能够接入多一倍数据的端口。

MII RMII

以太网接口MII,RMII以太网媒体接口有:MII、RMII、SMII、GMII。

所有的这些接口都从MII而来,MII是(Medium Independent Interface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII 等。

1. MII (Media Independent Interface 介质无关接口)MII,即媒体独立接口,是IEEE-802.3定义的以太网行业标准,用于 Fast Ethernet MAC-block 与各种类型的PHY 连接。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY 。

在其他速率下工作的与 MII等效的接口有:AUI(10M以太网)、GMII(Gigabit以太网)和XAUI(10-Gigabit以太网)。

MII Management interface只有两条信号线。

The configuration and status data is written/read to/from the PHY via the MDIO signal.ETHERNET的接口实质是MAC通过MII总线控制PHY的过程。

MAC是Media Access Control 的缩写,即媒体访问控制子层协议。

各种MII接口详解

简介MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

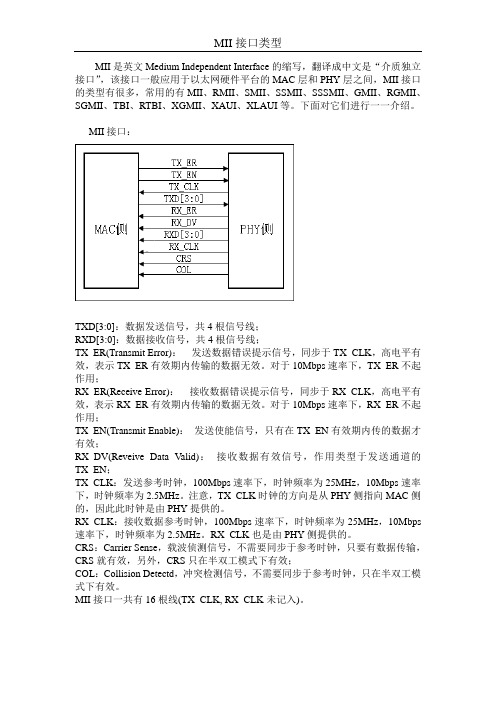

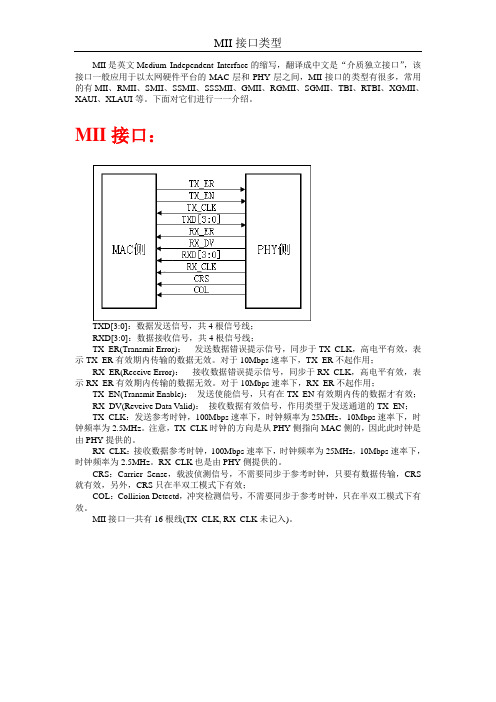

MII接口:T XD(Transmit Data)[3:0]:数据发送信号,共4根信号线;RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

以太网MII接口类型大全

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

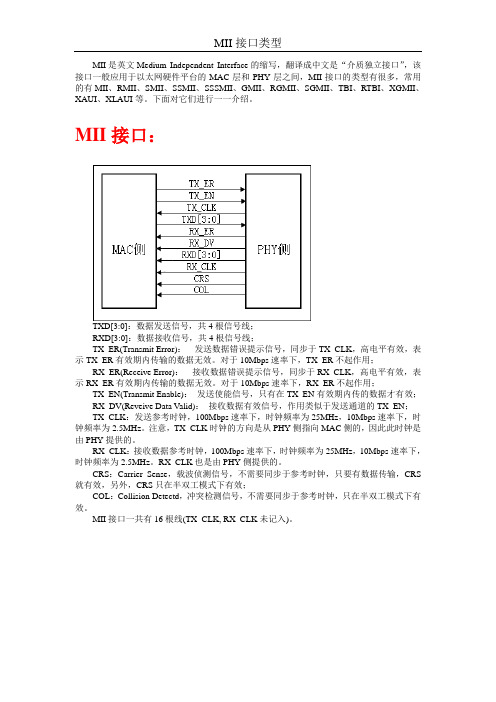

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps 速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

MII接口一共有16根线(TX_CLK, RX_CLK未记入)。

以太网MII接口类型大全_MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XL

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类似于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS 就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

MII接口一共有16根线(TX_CLK, RX_CLK未记入)。

MII

MII (Media Independent Interface(介质无关接口);或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII (Management interface)只有两条信号线。

目录展开编辑本段概述MII标准接口用于连快Fast Ethernet MAC-block与PHY。

"介质无关"表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

在其他速率下工作的与 MII等效的接口有:AUI(10M 以太网)、GMII(Gigabit 以太网)和XAUI(10-Gigabit 以太网)。

编辑本段MIICPU1997年,Cyrix被称作MII的新一代微处理器已正式推出.MII是在Cyrix在大规模投放市场的6X86的基础上将其第一级高速缓冲内存由原有的16K扩大到64K,大大地增加了运算速度,同时在流行的X86指令集中加入了MMX的功能。

MII传承了6X86出色的运行32位软件的功能并具有MMX功能。

所谓MMX是指一套加在流行的X86指令集的附加指令,它包括57条为加速多媒体单元设计的新指令,包括音频处理、视频解压和图形处理等。

Cyrix新的MII处理器依然是为用户提供一种简单的升级方法,以使他们的计算机拥有MMX技术。

相比INTEL和AMD的同时期CPU,MII的优势仍然在整数运算,其浮点运算仍然为人们所诟病.时至今日,Cyrix被威盛所收购,早已不复存在,这款处理器成为人们心中的回忆.作为Cyrix公司独自研发的最后一款微处理器,Cyrix MII于1998年3月开始量产。

各种MII详解(MII,GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI)

简介MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:TXD(Transmit Data)[3:0]:数据发送信号,共4根信号线;RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

各种MII详解(MII,GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI)

简介MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:T XD(Transmit Data)[3:0]:数据发送信号,共4根信号线;RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER 有效期传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER 有效期传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY 提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

(完整版)以太网MII接口类型大全_MII、RMII、SMII、SSMII、SSSMII、GMII、

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类似于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS 就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

MII接口一共有16根线(TX_CLK, RX_CLK未记入)。

MII、RMII、GMII、RGMII接口介绍

MII、RMII、GMII、RGMII接口介绍2010-04-28 18:44:46| 分类:电子技术| 标签:|字号大中小订阅1 MII (Media Independent Interface )是介质无关接口。

40针。

MII类似于10Mbps以太网的连接单元接口(AUI)。

MII层定义了在100BASE-T MAC和各种物理层之间的标准电气和机械接口,这种标准接口类似于经典以太网中的AUI,它允许制造厂家制造与介质和布线无关的产品,利用外接MAU去连接实际的物理电缆。

MII和AUI的电气信号是不同的,AUI信号具有较强的、能驱动50米电缆的能力,而MII的信号是数字型的,只能驱动0.5米电缆。

MII采用一个类似于SCSI连接器的40芯小型连接器。

2 任天堂Wii主机名为“Mii”的新功能,重点是让用户可以DIY个性化定制游戏角色的形象。

观察其操作界面,可以发现这个功能让用户可以对软件提供的各种五官元素进行自由组装拼合,产生接近本人长相特征的虚拟Avatar形象。

这个系统表面上就是现在各种网络社区的Avatar系统的一个翻版,但它本质上最关键的一点是这个Avatar可以通过统一的API被应用到各种Wii的游戏软件中,强化用户体验的代入感。

词条简介MII (Media Independent Interface(介质无关接口);或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII (Management interface)只有两条信号线。

MII标准接口用于连快Fast Ethernet MAC-block与PHY。

mii数据波形

MII(Media Independent Interface)是一个介质无关的交互接口,用于以太网MAC(媒体访问控制)层和PHY(物理层)之间的通信。

当以太网的速率为100Mb/s时,MII被用作MAC和PHY之间的交互接口。

在MII中,数据和控制信号在时钟下降沿发生变化,并在时钟上升沿被PHY芯片有效读取。

发送数据时,MII主要由TX_CLK、TXD[3:0]、TX_EN这几个信号线组成。

数据信号TXD[3:0]和TX_EN在时钟下降沿变化,并在时钟的上升沿被PHY芯片有效读取。

对于接收数据,MII的信号构成与发送方向相反。

接收数据的MII主要由RX_CLK、RXD[3:0]、RX_DV、RX_ER这几个信号构成。

以上内容仅供参考,如需更多信息,建议查阅相关文献或咨询专业人士。

eth的mdio和mdc管脚

eth的mdio和mdc管脚

MDIO(MII数据输入/输出)和MDC(MII管理数据时钟)是以

太网物理层接口中常见的两个信号。

它们通常用于连接以太网控制

器和以太网物理层芯片之间的管理接口。

MDIO是MII接口中的一个双向信号线,用于在以太网控制器和

物理层芯片之间传输管理数据。

通过MDIO,控制器可以向物理层芯

片发送管理命令,并从物理层芯片接收管理数据。

这些管理命令和

数据可以用于配置和监控物理层芯片的各种参数,例如速度、双工

模式、自动协商等。

MDC是MII接口中的时钟信号线,用于同步MDIO接口的数据传输。

MDC信号确定了管理数据的传输时序,确保了在MDIO上正确地

发送和接收管理数据。

在实际的硬件设计中,MDIO和MDC通常是通过物理层芯片和以

太网控制器的引脚来连接的。

MDIO通常是一个双向的数字信号引脚,而MDC则是一个时钟信号引脚。

这两个信号的具体管脚编号和连接

方式会根据具体的以太网芯片和控制器而有所不同,因此在设计和

连接硬件时需要参考相关的数据手册和规格说明。

总的来说,MDIO和MDC信号在以太网物理层接口中扮演着重要的角色,通过它们可以实现以太网控制器和物理层芯片之间的管理通信和数据传输。

这些信号的正确连接和使用对于确保以太网设备的正常运行和性能表现至关重要。

MII接口

JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 相关JTAG引脚的定义为:TCK为测试时钟输入;TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;TDO为测试数据输出,数据通过TDO引脚从JTAG接口输出;TMS为测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;TRST为测试复位,输入引脚,低电平有效。GND

JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(Test Access Port测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable;在线编程),对FLASH等器件进行编程。

PCI 外设组件互连标准(Peripheral Component Interconnection)

一种由英特尔(Intel)公司1991年推出的用于定义局部总线的标准。此标准允许在计算机内安装多达10个遵从PCI标准的扩展卡。最早提出的PCI总线工作在33MHz频率之下,传输带宽达到133MB/s(33MHz * 32bit/s),基本上满足了当时处理器的发展需要。随着对更高性能的要求,1993年又提出了64bit的PCI总线,后来又提出把PCI 总线的频率提升到66MHz。目前广泛采用的是32-bit、33MHz的PCI 总线,64bit的PCI插槽更多是应用于服务器产品。从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。管理器提供信号缓冲,能在高时钟频率下保持高性能,社和为显卡,声卡,网卡,MODEM等设备提供连接接口,工作频率为33MHz/66MHz。

以太网接口MII,RMII,SMII,GMII总线接口简介

以太网接口MII,RMII,SMII,GMII总线接口简介所有的这些接口都从MII而来,MII是(Medium Independent Interface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟。

RMII一般用在多端口的交换机,它不是每个端口安排收、发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目。

RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口。

和MII一样,RMII支持10兆和100兆的总线接口速度。

SMII是由思科提出的一种媒体接口,它有比RMII更少的信号线数目,S表示串行的意思。

因为它只用一根信号线传送发送数据,一根信号线传输接受数据,所以在时钟上为了满足100的需求,它的时钟频率很高,达到了125兆,为什么用125兆,是因为数据线里面会传送一些控制信息。

SMII一个端口仅用4根信号线完成100信号的传输,比起RMII差不多又少了一倍的信号线。

SMII在工业界的支持力度是很高的。

同理,所有端口的数据收发都公用同一个外部的125M时钟。

GMII是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口。

MII工作原理“媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

MII接口

MII接口详解词条简介MII (Media Independent Interface(介质无关接口);或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII (Management interface)只有两条信号线。

MII标准接口用于连快Fast Ethernet MAC-block与PHY。

"介质无关"表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

在其他速率下工作的与MII等效的接口有:AUI(10M 以太网)、GMII(Gigabit 以太网)和XAUI(10-Gigabit 以太网)。

MII总线在IEEE802.3中规定的MII总线是一种用于将不同类型的PHY与相同网络控制器(MAC)相连接的通用总线。

网络控制器可以用同样的硬件接口与任何PHY进行连接。

MII相关接口介绍以太网媒体接口有:MII RMII SMII GMII所有的这些接口都从MII而来,MII是(Medium Independent Interface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

以太网MII接口类型大全 MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XL

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS 就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

MII接口一共有16根线(TX_CLK, RX_CLK未记入)。

以太网接口总线接口简介

以太网接口MII,RMII,SMII,GMII总线接口简介所有的这些接口都从MII而来,MII是(Medium Independent Interface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC 的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟。

RMII一般用在多端口的交换机,它不是每个端口安排收、发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目。

RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口。

和MII一样,RMII支持10兆和100兆的总线接口速度。

SMII是由思科提出的一种媒体接口,它有比RMII更少的信号线数目,S表示串行的意思。

因为它只用一根信号线传送发送数据,一根信号线传输接受数据,所以在时钟上为了满足100的需求,它的时钟频率很高,达到了125兆,为什么用125兆,是因为数据线里面会传送一些控制信息。

SMII一个端口仅用4根信号线完成100信号的传输,比起RMII差不多又少了一倍的信号线。

SMII在工业界的支持力度是很高的。

同理,所有端口的数据收发都公用同一个外部的125M时钟。

GMII是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口。

MII工作原理“媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

各种MII详解(MII,GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI)

简介MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:T XD(Transmit Data)[3:0]:数据发送信号,共4根信号线;RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER 有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER 有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以太网媒体接口MII RMII SMII GMII 的定义

以太网媒体接口有:MII RMII SMII GMII

所有的这些接口都从MII而来,MII是(Medium Independent Interface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC 的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟。

RMII一般用在多端口的交换机,它不是每个端口安排收、发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目。

RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口。

和MII一样,RMII支持10兆和100兆的总线接口速度。

SMII是由思科提出的一种媒体接口,它有比RMII更少的信号线数目,S表示串行的意思。

因为它只用一根信号线传送发送数据,一根信号线传输接受数据,所以在时钟上为了满足100的需求,它的时钟频率很高,达到了125兆,为什么用125兆,是因为数据线里面会传送一些控制信息。

SMII一个端口仅用4根信号线完成100信号的传输,比起RMII差不多又少了一倍的信号线。

SMII在工业界的支持力度是很高的。

同理,所有端口的数据收发都公用同一个外部的125M时钟。

GMII是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口

MII (Media Independent Interface介质无关接口)

MII即媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口(图1)。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII Management interface只有两条信号线。

The configuration and status data is written/read to/from the PHY via the MDIO signal.

MII标准接口用于连快Fast Ethernet MAC-block与PHY。

“介质无关”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

在其他速率下工作的与MII等效的接口有:AUI(10M以太网)、GMII(Gigabit以太网)和XAUI(10-Gigabit 以太网)。

MII总线

在IEEE802.3中规定的MII总线是一种用于将不同类型的PHY与相同网络控制器(MAC)相连接的通用总线。

网络控制器可以用同样的硬件接口与任何PHY

GMII (Gigabit MII)

GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。

同时兼容MII 所规定的10/100 Mbps工作方式。

GMII接口数据结构符合IEEE以太网标准。

该接口定义见IEEE 802.3-2000。

发送器:

◇GTXCLK——吉比特TX..信号的时钟信号(125MHz)

◇TXCLK——10/100M信号时钟

◇TXD[7..0]——被发送数据

◇TXEN——发送器使能信号

◇TXER——发送器错误(用于破坏一个数据包)

注:在千兆速率下,向PHY提供GTXCLK信号,TXD、TXEN、TXER信号与此时钟信号同步。

否则,在10/100M速率下,PHY提供TXCLK时钟信号,其它信号与此信号同步。

其工作频率为25MHz(100M网络)或2.5MHz(10M网络)。

接收器:

◇RXCLK——接收时钟信号(从收到的数据中提取,因此与GTXCLK无关联)

◇RXD[7..0]——接收数据

◇RXDV——接收数据有效指示

◇RXER——接收数据出错指示

◇COL——冲突检测(仅用于半双工状态)

管理配置

◇MDC——配置接口时钟

◇MDIO——配置接口I/O

管理配置接口控制PHY的特性,即控制PHY是10兆、百兆还是千兆模式。

该接口有32个寄存器地址,每个地址16位。

其中前16个已经在“IEEE 802.3,2000-22.2.4 Management Functions”中规定了用途,其余的则由各器件自己指定。

RMII: Reduced Media Independant Interface

简化媒体独立接口

是标准的以太网接口之一,比MII有更少的I/O传输。

关于RMII口和MII口的问题

RMII口是用两根线来传输数据的,

MII口是用4根线来传输数据的,

GMII是用8根线来传输数据的。

MII/RMII只是一种接口,对于10M线速,MII的速率是2.5M,RMII则是5M;对于100M线速,MII的速率是25M,RMII则是50M。

MII/RMII用于传输以太网包,在MII/RMII接口是4/2bit的,在以太网的PHY里需要做串并转换、编解码等才能在双绞线和光纤上进行传输,其帧格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。

以太网帧的格式为:前导符+开始位+目的mac地址+源mac地址+类型/长度+数据+padding(optional)+32bitCRC

如果有vlan,则要在类型/长度后面加上2个字节的vlan tag,其中12bit来表示vlan id,另外4bit表示数据的优先级!。