VLSI设计基础8

VLSI设计基础课程教学大纲

《VLSI设计基础》课程教学大纲课程名称:VLSI设计基础课程代码:MICR2008英文名称:VLSI Design Foundation课程性质:专业必修课学分/学时:3.5/54开课学期:5适用专业:微电子科学与工程、电子科学与技术先修课程:数字系统与逻辑设计、半导体物理后续课程:集成电路工艺、半导体器件开课单位:电子信息学院课程负责人:黄秋萍大纲执笔人:黄秋萍大纲审核人:X一、课程性质和教学目标课程性质:VLSI设计基础课程是微电子、电子科学与技术等专业的一门专业基础课,是上述专业的必修课程,是集成电路工艺、集成电路测试、半导体器件等课程的前导课程。

教学目标:Purpose of education: First know what is integrated circuit.Understand the principle of transistor and layout design,know how to design CMOS logic gate, sequential machines .Understand switch logic and alternative gate, combinational logic network ,subsystem and floorplanning. After finished the course, can design basic circuits and layout. Because it is education of two kinds of language,know how to design IC,by the way catched special word,the ability of reading profession data has been improved.教学目的:通过本课程的学习,使学生对集成电路设计有初步系统了解,重点掌握晶体管原理和版图设计、CMOS逻辑门设计、时序机设计;了解开关逻辑和交替门电路、组合逻辑网络、子系统设计和布局布线。

VLSI课程设计

《VLSI设计基础》课程设计报告班级:电子10-02班学号:1006040208姓名:指导教师:8位移位寄存器设计一、设计要求1.查阅书籍资料,根据题目要求确定电路结构;2.明确电路实现的功能;3.明确电路中端口的数目、所联接的信号类型以及工作时序;4.采用Modelsim、Quartus II、Altium designer 中的任一种软件,基于Verilog 或VHDL语言设计综合设计题目中电路,实现功能仿真。

二、设计目的1.培养学生综合运用所学知识独立完成课题的工作能力,为毕业设计打好基础;2.培养学生从文献和调查研究中获取知识的能力,提高学生从别人经验,从其他学科找到解决问题的新途径的悟性;3.培养学生综合运用本专业基本理论、基本知识和基本技能的能力,使学生获得从事本专业工程技术工作的基本训练;4.培养学生勇于探索,严谨推理,实事求是,用实践来检验理论、全方位地考虑问题等科学技术人员应具有的素质;5.提高学生对工作认真负责、一丝不苟,对同学友爱团结、协作攻关,对新事物能潜心考察,勇于开拓,勇于实践的基本素质。

三、设计的具体实现1.电路概述此电路由8个4选1数据选择器、8个带异步清零的D触发器组成。

所有的S S分别对应地接在一起,同时选择D触发器的信号数据来数据选择器编码端10源。

D触发器时钟端CP接一起,清零端CR也同样接在一起,这样可以保证级联D触发器的同步,和并行输出数据的清零。

另,每个D触发器的输出对应一位并行输入。

Dsr是右移串行数据输入端,Dsl是左移串行数据输入端,分别接最低有效位对应的数据选择器和最高有效位对应的数据选择器。

图3 8位双向移位寄存器表2 8位双向移位寄存器真值表2. 设计综合电路1)设计流程a)编写源代码。

打开QuartusII软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件;b)按照实验箱上FPGA的芯片名更改编程芯片的设置。

VLSI设计基础复习资料..

VLSI设计基础复习资料1.为什么CMOS(含BiCMOS)工艺成为VLSI主流工艺?其最大特点是什么?在微电子技术领域,集成电路的制造有两个主要的实现技术:双极技术与MOS 技术。

CMOS以其结构简单,集成度高,耗散功率小等优点,成为当今VLSI制造的主流技术。

其最大特点是耗散功率小。

2.说明MOS器件的基本工作原理。

它与BJT基本工作原理的区别是什么?MOS器件基于表面感应的原理,是利用垂直的栅压VGS 实现对水平IDS的控制。

它是多子(多数载流子)器件。

用跨导描述其放大能力。

双极型晶体管(BJT)是利用发射结、集电结成的体内器件,由基极电流控制集电极电流的两种载流子均起作用的器件。

用电流放大系数描述其放大能力。

3.为什么说硅栅工艺优于铝栅工艺?硅栅工艺是利用重掺杂的多晶硅来代替铝做为MOS管的栅电极,使MOS电路特性得到很大改善,它使|VTP |下降1.1V,也容易获得合适的VTN值并能提高开关速度和集成度。

硅栅工艺具有自对准作用,这是由于硅具有耐高温的性质。

栅电极,更确切的说是在栅电极下面的介质层,是限定源、漏扩散区边界的扩散掩膜,使栅区与源、漏交迭的密勒电容大大减小,也使其它寄生电容减小,使器件的频率特性得到提高。

另外,在源、漏扩散之前进行栅氧化,也意味着可得到浅结。

铝栅工艺为了保证栅金属与漏极铝引线之间看一定的间隔,要求漏扩散区面积要大些。

而在硅栅工艺中覆盖源漏极的铝引线可重迭到栅区,这是因为有一绝缘层将栅区与源漏极引线隔开,从而可使结面积减少30%-40%。

硅栅工艺还可提高集成度,这不仅是因为扩散自对准作用可使单元面积大为缩小,而且因为硅栅工艺可以使用“二层半布线”即一层铝布线,一层重掺杂多晶硅布线,一层重掺杂的扩散层布线。

由于在制作扩散层时,多晶硅要起掩膜作用,所以扩散层不能与多晶硅层交叉,故称为两层半布线.铝栅工艺只有两层布线:一层铝布线,一层扩散层布线。

硅栅工艺由于有两层半布线,既可使芯片面积比铝栅缩小50%又可增加布线灵活性。

VLSI设计流程简介

VLSI设计流程简介VLSI設計流程簡介開宗須明義﹐什么是VLSI(Very Large Scale Integrated Circuit)呢?一般而言﹐VLSI是指電晶体(Transistor)數目超過1万個以上的IC。

但時至今日﹐市面上可見的IC數目多遠不止于此數﹐例如Intelr的Pentium系列CPU﹐所包含的電晶体數即高達200万以上。

可想而知﹐隨著IC功能的日益复雜与龐大﹐IC設計工作也愈形艱巨﹐非有适當的電腦輔助工具以及系統化的設計流程与方法是不能竟其功。

以上將針對系統化的設計方法做一個介紹。

描述IC的几個層次設計出來的IC是什么樣子﹐必須有适當的語言將其描述出來﹐才能做后續步驟的處理(圖一)﹐然而VLSI所做的運算多數是一些數學問題﹐所以設計IC首先必須將數學實体化﹐也就是“將數學轉成硬体可以執行的演算法”;在另一方面﹐IC所用的電路元件又牽涉到許多物理特性的問題﹐這意味著IC設計是一件橫跨抽象的數學到實際的元件物理的事情﹐面對的問題千頭万緒﹐實在無法一次解決﹐所以必須分層處理﹐各領域解決各領域的問題﹐以下是IC 設計時描述IC的几個層次。

Behavior Level在這個層次﹐IC動作的方式將以數學演算法(Algorithm)或流程圖等方式描述。

所以在這個層次﹐設計人員所關注的問題主要是在于如何將IC功能初步硬体化﹐至于詳細的電路如何設計﹑以及元件特性等問題則不在考慮之列.當數學運算化為演算法后﹐通常IC的大致架构(Architecture)便已浮現﹐所以這個層次也可稱為Architecture Level。

Register Transfel LeveL(RTL)在這個層次﹐設計人員首先必須定出電路中所有的暫存器﹐進而描述隨著時脈(Clock)前進﹑暫存器值之轉換關系﹐所以在這個層次,設計的重點在于循序(Sequential)電路﹑控制電路如何實現﹐以及時脈控制的策略(Clocking Strategy)為何。

vlsi数字集成电路一般设计流程

vlsi数字集成电路一般设计流程VLSI数字集成电路一般设计流程数字集成电路(VLSI)是现代电子技术领域的重要组成部分,广泛应用于计算机、通信、消费电子等领域。

VLSI数字集成电路的设计流程是一个系统性的过程,涉及到从需求分析到电路设计、验证、布局布线等多个环节。

本文将介绍VLSI数字集成电路的一般设计流程。

一、需求分析需求分析是VLSI数字集成电路设计的第一步,主要目的是明确设计要求和功能需求。

在需求分析阶段,设计团队与客户或项目经理进行沟通,了解项目的背景、功能要求、性能指标等。

同时,还需要考虑电路的功耗、面积、可靠性等因素,以确定设计的整体目标。

二、框架设计在框架设计阶段,设计团队根据需求分析的结果,确定整个电路的结构和功能模块。

框架设计需要考虑各个模块之间的连接方式、数据传输方式、时序要求等。

同时,还需要确定使用的逻辑门、存储器、寄存器等基本元件,并进行初步的电路图设计。

三、逻辑设计逻辑设计是VLSI数字集成电路设计的核心环节,主要目的是将框架设计的功能模块转化为逻辑电路。

在逻辑设计阶段,设计团队使用硬件描述语言(如Verilog、VHDL)进行电路的建模和描述,利用逻辑门、时序电路等元件进行电路的逻辑实现。

四、验证验证是确保电路设计正确性的重要环节。

在验证阶段,设计团队需要使用仿真工具对电路进行功能仿真,并设计测试用例进行验证。

通过仿真和测试,可以发现电路设计中的错误或潜在问题,并对其进行修复和优化。

五、布局布线布局布线是将逻辑电路转化为物理电路的过程。

在布局布线阶段,设计团队将逻辑电路转化为实际的布局图,确定各个元件的位置和相互之间的连线关系。

同时,还需要考虑电路的面积、功耗、信号延迟等因素,并进行布线优化。

六、物理验证物理验证是检验布局布线结果的环节。

在物理验证阶段,设计团队对布局布线后的电路进行电气规则检查(DRC)和电磁规则检查(ERC),以确保电路的物理完整性和可靠性。

根据验证结果,可以对布局布线进行调整和优化。

《VLSI设计基础》课件

欢迎来到《VLSI设计基础》PPT课件!本课程将介绍VLSI设计的基本概念、电 路设计流程、数字电路设计、模拟电路设计、特殊电路设计等内容。同时还 将通过案例研究,展示古早手机电路设计和现代处理器电路设计。

课程介绍

• 课程目标 • 授课内容 • 教学方法

课程大纲

单元1: 基本概念 单元4: 模拟电路设计

单元2: 电路设计流程

单元3: 数例研究

古早手机电路设计

现代处理器电路设计

结论及讨论

1 VLSI设计的重要性

2 学习本课程的好处

3 提问和回答

参考资料

书籍

网站

文献

VLSI设计基础(二选一多路选择器)

《VLSI设计基础》课程设计报告班级:电子科学与技术09级2班学号: 0906040216姓名:穆加林指导教师:李蕾1.摘要在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。

有2选1数据选择器、4选1数据选择器、8选1数据选择器、16选1数据选择器等之分二路选择器具有一个选择控制变量,当用来实现二变量函数功能时,应该首先输入选择控制变量来确定选择器的数据输入。

根据题目设计要求,完成二选一多路选择器设计。

我设计的是一个基于VHDL语言设计一个二选一多路选择器。

2.综述二选一多路选择器功能描述:输入端口a,b输入信号,在通道选择控制输入端口s输入低电频时,输出端口y输出a输入端口信号;在通道选择控制输入端口s输入高电频时,输出端口y输出b输入端口信号。

二选一多路选择器的电路图,如下图其中a,b是输入信号,s是通道选择信号,y是输出信号。

当s=0时,y=a;当s=1时,y=b。

三.方案设计与分析1.设计目的1)熟悉MAXPLUS2/Quartus II软件,掌握软件的VHDL程序输入、程序编译和程序仿真操作;2)学习利用VHDL语言设计二选一多路选择器电路程序;3)了解可多路选择器的工作方式。

2.设计要求采用Modelsim、Quartus II、Altium designer 中的任一种软件,基于Verilog或VHDL语言实现设计题目的功能仿真,完成设计;课程设计完成后,提交课程设计报告,要求提供编写的代码以及输出波形图3.设计的源程序及仿真1)、二选一多路选择器程序录入:LIBRARY IEEE; --IEEE 库使用说明USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux21 IS --器件mux21 的外部接口信号说明--PORT相当于器件的引脚,这一部分称为实体PORT ( a b : IN STD_LOGIC;s : IN STD_LOGIC;y : OUT STD_LOGIC );END ENTITY mux21; --器件mux21 的内部工作逻辑描述即--为实体描述的器件功能结构称为结构体ARCHITECTURE one OF mux21 ISBEGINy <= a WHEN s = '0' ELSEb WHEN s = '1' ;END ARCHITECTURE one;--器件mux21 的内部工作逻辑描述即--为实体描述的器件功能结构称为结构体ARCHITECTURE one OF mux21 ISBEGINy <= a WHEN s = '0' ELSEb WHEN s = '1' ;END ARCHITECTURE one;2)、系统设计仿真及分析a.系统功能仿真结果:图为二选一多路选择器功能仿真图b.仿真分析由上图可以看出1)当sel=0时,y=a,即当s=0时输出波形就是a输入端的输入波形。

VLSI设计与制造技术概述

VLSI设计与制造技术概述随着科技的不断发展,半导体行业在过去几十年中取得了巨大的进步。

VLSI(Very Large Scale Integration,超大规模集成电路)设计与制造技术作为半导体行业的核心,起到了决定性的作用。

本文将对VLSI 设计与制造技术进行概述,介绍其基本概念、发展历程和关键技术。

一、VLSI设计的基本概念VLSI设计是指在单个芯片上集成大量的电子元件,将复杂的电路系统等设计信息转化为实际可制造的芯片。

VLSI设计的关键目标是提高集成度和功能密度,从而实现更高性能和更小尺寸的芯片。

二、VLSI设计的发展历程VLSI设计技术起源于20世纪60年代末,当时人们开始研究如何在一块硅片上集成多个晶体管。

随着摩尔定律的提出,VLSI设计技术逐渐成为半导体行业的核心竞争力之一。

在过去的几十年中,VLSI设计技术经历了几个主要的发展阶段,从SSI(Small Scale Integration,小规模集成)到MSI(Medium Scale Integration,中规模集成)再到LSI (Large Scale Integration,大规模集成)和VLSI。

如今,VLSI设计已经进入到SOC(System-on-a-Chip,片上系统)和多核心时代。

三、VLSI设计的关键技术1. 逻辑设计:逻辑设计是VLSI设计的基础,它通过使用HDL (Hardware Description Language,硬件描述语言)描述电路功能,并系统地进行功能验证和仿真。

2. 物理设计:物理设计主要包括芯片布局和电路布线两个方面。

芯片布局决定电路元件的相对位置,而电路布线则是将逻辑电路转化为物理电路的过程。

3. 高级封装技术:高级封装技术是将VLSI芯片封装成可直接使用的模块或器件的过程。

常用的封装技术包括BGA(Ball Grid Array,球栅阵列)、CSP(Chip Scale Package,芯片尺寸封装)等。

第一章VLS知识点

第一章VLS知识点VLS(Very Large Scale integration)是指非常大规模集成电路技术,是现代集成电路技术的重要分支。

VLS技术的发展使得集成电路的规模大大增加,功能更加强大,性能更加优越。

本章将介绍VLS知识点的基础知识、设计原理、工艺和应用等方面的内容。

一、基础知识1.集成电路:将多个电子元件(如电晶体、电阻、电容等)集成到单个半导体晶片上的电路。

其主要特点是占用空间小、功耗低、可重复使用。

2.VLSI:非常大规模集成电路,是将成百上千个晶体管集成到一个微小的硅晶片上,使电路规模大大增加。

二、设计原理1.逻辑门电路:是通过逻辑门(与门、或门、非门等)来实现不同逻辑功能的电路。

逻辑门的输出结果仅与输入信号的逻辑关系有关。

2. 布尔代数:在逻辑门电路中,常用布尔代数来描述逻辑关系。

布尔代数是由数学家乔治·布尔(George Boole)创立的一种数学运算方法,用于描述逻辑关系和逻辑运算。

3.时序逻辑:逻辑电路的输出是由输入信号和时钟信号共同决定的。

时钟信号用于控制逻辑电路的工作时序。

三、工艺1.MOSFET:金属-氧化物-半导体场效应晶体管,是VLSI集成电路中常用的基本元件。

其主要特点是体积小、功耗低、噪声低、可靠性高。

2.CMOS:互补金属-氧化物-半导体技术,是一种集成电路制造工艺。

CMOS技术结合了NMOS(n型金属-氧化物-半导体场效应晶体管)和PMOS (p型金属-氧化物-半导体场效应晶体管)技术,具有功耗低、可靠性高的特点。

3.焊接技术:用于将船到的芯片和印刷电路板进行连接的一种技术。

常用的焊接技术有手工焊接、自动焊接、贴片焊接等。

4.接触孔技术:用于在不同层次的芯片之间进行电连接的一种技术。

接触孔技术将不同层次的芯片通过金属导线进行连接,实现不同层次之间的信号传输。

四、应用1.通信领域:VLSI技术的快速发展使得通信设备的功能大大增强。

在通信领域中,VLSI技术被广泛应用于芯片设计、信号处理、调制解调器等方面。

东南大学《VLSI设计基础》复习总结

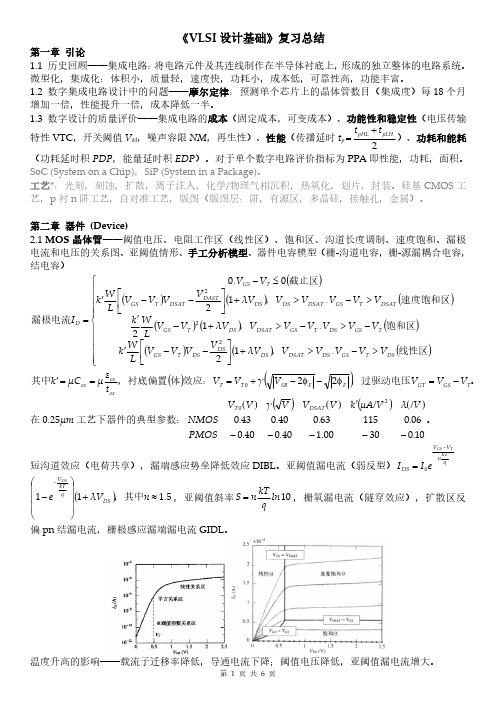

4.2*动态 CMOS 设计——预充电求值(晶体管数目少,无比逻辑,开关速度快,但稳定性弱,开关 活动性大,动态功耗大)

第五章 时序逻辑门设计 (Sequential Logic) 5.1 引言——时序电路的时序参数、时序约束——建立时间约束 T tcq tplogic tsetup ,维持时间约束

主从边沿触发寄存器的时序参数:建立时间 tsetup 3tpd_inv tpd_tx ,寄存器延时 tcq tpd_inv tpd_tx ,维 持时间 thold 0 。 为降低时钟负载,减小时钟功耗,可使用 NMOS 传输管电路,但阈值损失会导致静态功耗;或使用 弱反馈有比电路,但增加了设计的复杂性。

于外部负载电容,延时不再随尺寸增大而减小)、电源电压越大,则延时越小。

3.4

功耗、能量和能量延时——动态功耗:充放电电容引起

Pdyn

C

V2

L DD

f01

C

V2

L DD

P01

f

,直流通

路引起 Pdp tscVDDIpeak f ,负载电容越小、电源电压越小、反转频率(开关活动性)越小,信号斜率

越大,则动态功耗越小;静态功耗: Pstat IstatVDD ,漏电流(亚阈值电流,漏极漏电流),阈值电压

提升性能,负偏差 δ 0 可减弱竞争,但反馈回路的存在会使时钟偏差反向)、时钟抖动(Clock Jitter): T 2t jiter tcq tplogic tsetup (绝对抖动 t jiter 0 )、时钟偏差和抖动共同影响: T δ 2t jiter tcq

VLSI_Ch8_高速CMOS逻辑电路设计_2016_update

第8章高速CMOS逻辑电路设计本章概要⏹ 门延时的估计⏹ 驱动大电容负载⏹ 逻辑努力8.1 门延时的估计任意逻辑门的延时设计者的任务:选择合适的逻辑链,确定每个晶体管的宽长比,以满足规定的延时及芯片面积要求。

C FET 是输出节点对地的本级电容2(||)2nDp DD M Tp I V V V β=--8.1 门延时的估计反相器单位反相器放大m 倍00min2r pu f nu r L f Lin u t C t C t C C C t αα=+=+==min min min min,p n p n if L L W W ==20200032321212r r pu L f f nu L rN r nu LfNf nu Lt t C t t C N t t C N t Nt N C αααα=+=++=++=+00min3232r r pu L f f nu in t t C t t C C C αα=+=+=单位NAND2(最坏情况)单位尺寸m 00323233pu r L nuf t C t C αα=+=+8.1 门延时的估计单位NOR2min002323C C C t t C t t in Lnu f f L pu r r =+=+=αα0023 3323pur L nu f L t C t C αα=+=+2输入,放大8.1 门延时的估计逻辑链延迟3α延迟与扇入N的关系=+()t A Bnτ被驱动反相器的宽长比是驱动反相器的宽长比的S为使延迟时间不变,应使驱动反8.2 驱动大电容负载反相器链延时问题问题:要驱动具有大输入电容的后级门,必须增大本级驱动门的面积,而本级驱动门面积的增大又会增加前级门的负载电容,如何解决这个问题?问题:如何使反相器链的总延时最小?参考反相器8.2 驱动大电容负载优化目标⏹在负载电容C L给定的条件下,如何找出N、S的最优值,使信号从输最短?入到达负载所需要的时间τd☐Step1:求出τd与N、S的函数关系☐Step2:求N、S为何值时τd最小?ln lnLC C N S=1ln() d S S SS τ∂⎡⎤∂=⇔=⎢⎥∂∂⎣⎦00驱动大电容负载⎩其中:令⇒8.3 逻辑努力⏹组合逻辑电路设计中常遇到下列问题:☐一组合逻辑用电路实现,最优的拓扑结构是什么样的?☐使用几级逻辑给出的延时最小?☐晶体管的尺寸大小多少合适?☐仿真和时序分析工具可行吗?⏹使用逻辑努力的概念可以解答这些问题☐如何选择最优的拓扑结构、最优的逻辑级数和最佳的尺寸,使延时最小。

VLSI设计基础 复习题与思考题

“VLS I设计基础”复与思考题选用教材:VLSI设计基础”李伟华编著电子工业出版社2002 年10 月第一版参考教材半导体集成电路”,张开华编著,东南大学出版社,1995 年7 月第一版。

第1 章“VLS 工设计基础概述” 复与思考题(p.1~3)第2 章“MOS 器件与工艺基础”复习思考题(p.4~9)第3 章“工艺与设计接口”复习思考题(p.10)第4 章“晶体管规则阵列设计技术”复习思考题(p.10~13)第5 章“单元库设计技术”复习思考题(p.13~17)第6 章“微处理器”复习思考题(p.17~22)第7 章“集成电路的测试”复习思考题(p.22~23)第1 章“VLS 工设计基础概述” 复与思考题1. 为什么CMOS(含BiCMOS)工艺成为VLSI主流工艺?其最大特点是什么?在微电子技术领域,集成电路的制造有两个主要的实现技术:双极技术与MOS 技术。

CMOS 以其结构简单,集成度高,耗散功率小等优点,成为当今VLSI制造的主流技术。

其最大特点是耗散功率小。

2. 双极工艺还有用武之地吗?双极技术是以NPN 与PNP 晶体管为基本元件,融合其他的集成元件构造集成电路的技术方法。

双极器件以其速度高和驱动能力大,高频、低噪声等优良特性,在集成电路的设计制造领域,尤其是模拟集成电路的设计制造领域,占有一席之地。

但双极器件的耗散功率比较大,限制了它在VLSI系统中的应用。

3. 以你的体会,你认为集成电路设计师应具备哪些基本技术基础?设计者必须具备下列的技术基础:电路与逻辑没计技术基础,器件与工艺技术基础,版图设计技术基础和集成电路计算机辅助设计技术基础。

除此之外,设计者还应具备对电路、逻辑、器件、工艺和版图的分析能力。

4. 简要说明描述集成电路技术水平5 大指标的含义。

大指标的含义。

当前国内和国际上集成电路产业在特征尺寸及晶园尺寸方面各达到什么水平?寸及晶园尺寸方面各达到什么水平? 1 集成度是以一个IC 芯片所包含的元件(晶体管或门/数)来衡量,集成度特征尺寸特征尺寸定义为器件中最小线条宽度(对MOS 器件而言,通常指器件栅电极所决定的沟道长度的几何长度),芯片芯片面积大小,晶片直径晶片直径大小,封装引脚数封装引脚数多少。

VLSI设计基础ppt课件

掩膜编程的 输入输出单元

P+ P+ PN-

VLSI设计基础-5.2 (43)

东南大学电子科学与工程学院

5.2 标准单元设计技术

输入、输出单元(I/O PAD)

VLSI设计基础-5.2 (44)

东南大学电子科学与工程学院

5.2 标准单元设计技术

输入、输出单元(I/O PAD)

VLSI设计基础-5.2 (18)

东南大学电子科学与工程学院

5.2 标准单元设计技术

输入、输出单元(I/O PAD)

1. 输入单元 输入单元主要承担对内部电路的保护,一般认

为外部信号的驱动能力足够大,输入单元不必具备再 驱动功能。因此,输入单元的结构主要是输入保护电 路。输入保护分为单二极管、电阻结构和双二极管、 电阻结构,还可利用PN结的击穿特性。

有源区

VLSI设计基础-5 (22)

东南大学电子科学与工程学院

多晶硅

VLSI设计基础-5 (23)

东南大学电子科学与工程学院

P+区

VLSI设计基础-5 (24)

东南大学电子科学与工程学院

N+区

VLSI设计基础-5 (25)

东南大学电子科学与工程学院

引线孔

VLSI设计基础-5 (26)

东南大学电子科学与工程学院

主要目的是ESD(Electrostatic Discharge)保 护。

VLSI设计基础-5.2 (19)

东南大学电子科学与工程学院

5.2 标准单元设计技术

输入、输出单元(I/O PAD)

VLSI设计基础-5.2 (20)

东南大学电子科学与工程学院

P阱

第8章VLSI设计实例—AES加密芯片设计与实现

如果一个密码系统的加密密钥和解密密钥不同,并且 由加密密钥推导出解密密钥(或者由解密密钥推导出 加密密钥)是计算上不可行的,则称该密码系统采用 的是非对称密码体制。采用非对称密码体制的每个用 户都有一对选定的密钥,其中一个是可以公开的,一 个由用户自己秘密保存。 非对称密码体制的出现是现代密码学研究的一项重大 突破,它的主要优点是可以适应开放性的使用环境, 密钥管理问题相对简单,可以方便、安全地实现数字 签名和验证。但它的加/解密速度较慢(例如目前最快 的RSA芯片的加/解密速度为2Mb/s),而且其保密强度 目前还远远达不到对称密码体制的水平。

(3)有限域的加法运算 在有限域的多项式表示中,GF(28)上两个元素的和仍 然是一个次数不超过7的多项式,其系数等于两个元 素对应系数的模2加(比特异或)。 由于AES算法中的字节被看作有限域上的元素,因此 有限域中的加法运算相当于对两个字节进行异或操作。 例如:在GF(28)域中,16进制数57和83所表示的多项 式的为: (x6+x4+x2+x+1)+(x7+x+1)=x7+x6+x4+x2 用二进制表示为 {01010111}⊕{10000011} = {11010100} 用十六进制表示为 {57}⊕{83} = {d4}

Li-1 Ri-1

扩展置换

ki

S-盒代替

P-盒置换

Li

Ri

பைடு நூலகம்16

DES的子密钥产生流程图

k 64位 密钥置换1 56位 28位 C0 循环左移 C1 28位 D0 循环左移 D1 密钥置换2 循环左移 C2 循环左移 D2 密钥置换2 循环左移 C16 循环左移 D16 密钥置换2 k16 (48位) k2 (48位) k1 (48位)

清华大学VLSI8

2020/8/20

19

BBL模式下的布线区域比较复杂,未被模 块占用的芯片空间为布线区。通常要先 把它们划分成矩形的通道区,然后再按 一定次序逐个进行布线,传统的布线工 艺用两层金属,此时模块上面不能走线。 随着多层布线工艺的出现,模块上允许 有三层以上的走线,出现了“跨单元布 线”(Over the Cell Routing)技术。 它使得布线区域大大减小。

3

这种划分,可以是由人工来完成,也可以由 划分工具进行自动划分.关键是如何评价这一 划分结果是最优的。在进行电路划分的同时, 对芯片面积也进行相应的划分,其目的是为 每个模块确定一个布图面积的大小。这一步 叫布图规划(floor-planing)。

System

M1

M2

M3

Mn

T1 T2

Ts

4

二、模块性

2020/8/20

17

三、积木块自动布图

压焊块 第一层金属

第二层金属

通

数据通路

孔

PLA

I/O

ROM/

RAM

随

机

逻

A/D 转换

辑

2020/8/20

18

积木块自动布图(Building Block Layout) 又称为任意形状单元布图,简称作BBL。 限于实现的困难,大部分的BBL模式版 图都为矩形,也可有少量“T”型和“L”

2020/8/20

Байду номын сангаас

11

大部分CAD公司都提供实用的交互图形 编 辑 器 , 如 Cadence、Mentor等 都有功 能完善、性能良好的编辑工具。我国自 行开发的PANDA系统也包括有一个交互 图形编辑工具。除了工作站版本外,有

超大规模集成电路设计基础:第八讲 VLSI计算机辅助设计

超大规模集成电路设计基础:第八讲 VLSI计算机辅助设计刘以皓;冯世琴

【期刊名称】《电子技术应用》

【年(卷),期】1991(000)008

【摘要】8.1 VLSI/CAD 的涵义如前所述,计算机辅助设计(CAD)是进行VLSI芯片设计的主要手段。

若在面积为数十平方毫米的芯片上设计包含数十万器件的复杂电路的多层几何图形,则完全超越了单纯手工设计的可能性,因此VLSI技来的发展是和CAD 技术紧密结合在一起的。

【总页数】3页(P36-38)

【作者】刘以皓;冯世琴

【作者单位】不详;不详

【正文语种】中文

【中图分类】TN402

【相关文献】

1.超大规模集成电路设计基础:第一讲微电子技术概况 [J], 冯世琴

2.超大规模集成电路设计基础:第二讲 HMOS集成电路基础 [J], 冯世琴

3.超大规模集成电路设计基础:第三讲 NMOS VLSI的结构特性 [J], 刘以皓;冯世琴

4.超大规模集成电路设计基础:第四讲 NMOS VLSI基本单元电路 [J], 刘以皓;冯世琴

5.超大规模集成电路设计基础第七讲 NMOS超大规模集成电路芯片设计技术 [J], 刘以暠;冯世琴

因版权原因,仅展示原文概要,查看原文内容请购买。

VLSI

File →New → Cell View

新建、開啟Schematic和 Layout (cont.)

Cell View主要有兩種可自此建立:一是 schematic,一則是layout

Cell name應取6個字母以內的name,否 則執行 lvs 或 lpe 時會有錯

VLSI設計導論.上機實作

元智資工所 VLSI實驗室 徐偉倫製

設計驗證流程

開啟icfb 建新Library

開啟Library Manager

LPE LVS

開啟、繪製 Schematic和 Layout Export File

進入icfb

在Terminal下,由個人根目錄進入 Cadence後,鍵入icfb &。

makecom035 xxx 產生

LVS和LPE的事前準備 (cont.)

在export file的目錄下執行

LOGLVS

htv cir con xxx x

產生LVSLOGIC.DAT檔案

LVS

在export file的目錄下執行

PDRACULA

/g n /f

產生 檔案 用文字編輯器修改

將“ #!/bin/csh –f “修改成” #!/bin/tcsh –f “

LVS (cont.)

執行 ,產生 xxx.lvs檔案 檢查 xxx.lvs 是否有 un-matched,若有則回 到 layout和 schematic 檢查

建立transistors之間的連線

Add → Wire (narrow) 開出現後填入pin name,若為input pin則 選input;反之選output。 選擇 Hide隱藏視窗回schematic建pin。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

通常将P型衬底接电路中最低电位,N型衬底接最 高电位,这样,最坏工作情况是电阻只有一端处于零 偏置,其余点都处于反偏置。

正是因为这个PN结的存在,又导致了掺杂半导体电 阻的另一个寄生效应:寄生电容。

电阻的衬底通常都是处于交流零电位,使得电阻对 交流地存在旁路电容。如果将电阻的一端接地,并假 设寄生电容沿电阻均匀分布,则电阻幅模的-3db带宽 近似的为:

1

1

f

3RC 3R□C0 L2

其中,R□是电阻区的掺杂层方块电阻,C0是单位 面积电容,L是电阻的长度。

第八章 模拟单元与变换电路

8.1 模拟集成电路中的基本元件

电阻、电容和晶体管是模拟集成电路的主要积木 单元,MOS晶体管在第二章中已作了介绍,这里将主 要讨论电阻和电容的设计。我们还将考虑一些分布参 数对元件性能的影响。

8.1.1 电阻

电阻是基本的无源元件,在集成工艺技术中有多 种设计与制造电阻的方法,根据阻值和精度的需要可 以选择不同的电阻结构和形状。

通常的修正包括端头修正和拐角修正。

端头和拐角修正

因为电子总是从电阻最小的地方流动,因此, 从引线孔流入的电流,绝大部分是从引线孔正对着 电阻条的一边流入的,从引线孔侧面和背面流入的 电流极少,因此,在计算端头处的电阻值时需要引 入一些修正,称之为端头修正。端头修正常采用经 验数据,以端头修正因子k1表示整个端头对总电阻 方块数的贡献。

合金薄膜电阻通过修正可以使其绝对值公差达到 1%~0.01%的精度。主要的修正方法有氧化、退火和激 光修正。

3. 有源电阻

所谓有源电阻是指采用晶体管进行适当的连接并 使其工作在一定的状态,利用它的直流和交流导通电 阻作为电路中的电阻元件使用。

NMOS的直流电阻所对应的工作电流是I,源漏电压 是V,直流电阻。

Ron VGS V

2tox L

n ox W

V V VTN

2

交流电阻是曲线在工作点O处的切线。因为VDS=VGS, 所以,

rds

VDS I DS

VGS V

VGS I DS

VGS V

1 gm

tox L 1 n ox W (V VTN )

显然,这个电阻是一个非线性电阻,但因为一般交 流信号的幅度较小,因此,这个有源电阻在模拟集成电 路中的误差并不大。

掺杂半导体电阻的几何图形设计 电阻的几何图形设计包括两个主要方面: 几何形状的设计和尺寸的设计。

形状设计与考虑

一个基本的依据是:一般电阻采用窄条结构, 精度要求高的采用宽条结构;小电阻采用直条形, 大电阻采用折弯形。

电阻图形尺寸的计算

R

R□

L W

这样的计算实际上是很粗糙的,因为在计算中 并没有考虑电阻的形状对实际电阻值的影响,在实 际的设计中将根据具体的图形形状对计算加以修正,

1. 掺杂半导体电阻 扩散电阻

所谓扩散电阻是指采用热扩散掺杂的方式构造而 成的电阻。这是最常用的电阻之一,工艺简单且兼容 性好,缺点是精度稍差。

离子注入电阻

同样是掺杂工艺,由于离子注入工艺可以精确 地控制掺杂浓度和注入的深度,并且横向扩散小, 因此,采用离子注入方式形成的电阻的阻值容易控 制,精度较高。

对于折弯形状的电阻,通常每一直条的宽度都是相同

的,在拐角处是一个正方形,但这个正方形不能作为一 个电阻方来计算,这是因为在拐角处的电流密度是不均 匀的,靠近内角处的电流密度大,靠近外角处的电流密 度小。经验数据表明,拐角对电阻的贡献只有0.5方,即 拐角修正因子k2=0.5。

衬底电位与分布电容

2. 薄膜电阻 可以利用多种薄膜材料制作电阻。主要的薄膜电阻

有多晶硅薄膜电阻和合金薄膜电阻。

多晶硅薄膜电阻

合金薄膜电阻

常用的合金材料有:Ta,方块电阻:10~10000Ω/□; Ni-Cr , 方 块 电 阻 : 40~400Ω/□ ; SnO2, 方 块 电 阻 : 80~4000Ω/□;CrSiO,方块电阻:30~2500Ω/□。

饱和接法的MOS器件的直流电阻在一定的范围内比 交流电阻大。在许多的电路设计中正是利用了这样结 构的有源电阻所具有的交、直流电阻不一样的特性, 来实现电路的需要。

利用MOS的工作区域和特点,我们也能够得到具有 直流电阻小于交流电阻的特性。

8.1.2 电容

1. 以N+硅作为下极板的MOS电容器

MOS电容器结构是:以金属或重掺杂的多晶硅作 为电容的上极板,二氧化硅为介质,重掺杂扩散区为 下极板。

以多晶硅作为下极板的MOS电容器

以多晶硅作为电容器下极板所构造的MOS电容器是无极 性电容器。这种电容器通常位于场区,多晶硅下极板与衬底 之间的寄生电容比较小。

MOS电容器的电容量的大小和电容器的面积有关,还 与单位面积的电容即两个极板之间的氧化层的厚度有关。 可以用下式计算

0 SiO2

t ox

真空电容率 0=8.85×10-14F·cm-1, SiO2 是二氧化硅的

相对介电常数,约等于3.9,两者乘积为3.45×10-13F·㎝-1,

如果极板间氧化层的厚度为80nm(0.08 m),可以算出单

位面积电容量为4.3×10-4 pF m2,也就是说,一个1万平方 微米面积的电容器的电容只有4.3pF。

3. 电容的放大——密勒效应

对于跨接在一个放大器输入和输出端之间的电 容,因为密勒效应将使等效的输入电容放大。

Байду номын сангаас

i

vi v0 1 jwC 0

vi

( Av vi ) 1 jwC 0

vi

jwC 0 (1

Av)

vi

1

i jw(1 Av)C0

8.2 基本偏置电路

在 通 常 情 况 下 , 大 部 分 的 MOS 模 拟 集 成 电 路 中 的 MOS晶体管,不论是工作管,还是负载管都工作在饱和 区。