s3c2440的IIS应用

s3c2410s3c2440处理器介绍

鲁东大学 LUDONG UNIVERSITY

S3C2410A结构框图

S3c2440处理 器结构框图

❖ S3C2410A在片上,S3通C过24A1M0ABA简总介线集成了以下资源:

AHB总线-各类控制器

✓支持STN和TFT的LCD控制器 ✓ NAND Flash 控制器 ✓存储管理器(片选逻辑和SDRAM控制器) ✓时钟及电源管理器

APB总线-设备与接口 ✓ 3通道UART、 ✓ 4通道DMA、 ✓ 4通道PWM定时器、 ✓ I/O口、 ✓ RTC、

: 1M bps

CTS/RTS

Key

Debug

GPS

BT

Matrix

SRAM/ROM /NOR Flash /OneNAND/OneDRAM

1Gbit X 6banks (x8/x16/x32)

UART0 SMC

UART1

NAND

NAND Flash IF

SDRAM/mDDR

1Gbit X 2banks (x16/x32)

PMIC

Main Charger

Li-Ion

USB Charger

Control

Data

5V DC

5V USB

TV-out

TV

TFT/CSTN LCDC + SPI(GPIO) + TSADC RGB I/F

Main TFT LCD & TSP

1/2/4/8/16 bpp Up to QVGA

SD/SDIO IIS I/F

✓ I2C总线接口、 ✓ I2S总线接口、 ✓ USB主设备、USB从设备 ✓ SD主卡和MMC(Multi Media Card,多媒体卡)卡接口 ✓2通道的SPI接口)

mini2440放音录音实验

地址模式用来选择一个设备为了之后的数 据传输 数据传输模式: 即,在地址模式的时候选择了地址,然后 再传输数据。如程序: WriteL3(0x14 + 2,1); //地址模式:10状态模式 (00010100+10) WriteL3(0x10,0); //数据传输:0,0,01, 000,0 : 状态0, 384fs,IIS,no DC-filtering

//Gain of DAC 6 dB,Gain of ADC 0dB, ADC non-inverting, //DAC non-inverting,Single speed playback,ADC-Off DAC-On

配置s3c2440的IIS寄存器

//配置s3c2440的IIS寄存器 //预分频器为3,所以CDCLK=PCLK/(2+1)=16.6mHz rIISPSR = 2<<5|2; //rGPECON &= 0x3ff; //无效DMA,输入空闲,预分频器有效 rIISCON = (0<<5)|(0<<4)|(0<<3)|(1<<2)|(1<<1); //PCLK为时钟源,输出模式,IIS模式,每个声道16位, CODECLK=384fs,SCLK=32fs rIISMOD = (0<<9)|(0<<8)|(2<<6)|(0<<5)|(0<<4)|(1<<3)|(1<<2)|(1<<0); //输出FIFO正常模式,输出FIFO使能 rIISFCON = (0<<15)|(1<<13);

配置UDA1341

WriteL3(0x14 + 2,1); WriteL3(0x60,0); //状态模式(000101xx+10) //0,1,10, 000,0 : 状态0,复位

使用JLink间接烧写S3C2410、S3C2440开发板Nor、Nand Flash的方法

nand write.jffs2 30000000 0 30000 // 把前面下载到 0x30000000 的程序烧写到 Nand 去

注意,上面用的 2ffff、30000 等数字是 192K,如果你的程序比较小,请自行设置。

本贴被 juedi 编辑过,最后修改时间:2009-03-04,14:30:34.

3. 下载特制的 uboot: h loadbin e:\u-boot.bin 0x33f80000 setpc 0x33f80000 g 上述操作命令可以参考图 5。

(原文件名:使用 jlink 下载运行 uboot.JPG) 现在,u-boot 已经启动了,在串口工具上可以看到如图 6 所示界面,以后就可以通过网络、串口下载文件,然后使用 u-boot 里 的命令进行烧写。

1. speed 12000

//设置 TCK 为 12M,下载程序时会很快

2. 下载并运行 init.bin,这是用来初始化 SDRAM 的 2.1 如果是 NAND 启动: loadbin e:\init.bin 0 setpc 0 g 2.2 如果是 Nor 启动: loadbin e:\init.bin 0x40000000 setpc 0x40000000 g

编辑 删除 编辑 删除

积分:287 派别: 等级:-----来自:广东佛山

__________________________ suffering from C library

2009-03-04,14:38: 19

资料 邮件

编辑 删除

【3 楼】 yangsen 积分:1199 派别: 等级:-----来自:

顶一个,好东东

2009-03-04,14:49: 02

芯片选型

芯片选型微控制器是移动机器人运动控制系统的核心,它的选择直接决定了整个机器人运动系统的性能和开发方式。

目前,国内外移动机器人平台采用的微控制器有多种,主要有8/16位单片机和数字信号处理器DSP两大类型。

采用8/16位单片机,控制系统设计制作简单,硬件开发周期短,但数据处理能力不强,需要借助外加器件如计数器、PID调节器和PWM产生器等,系统的稳定性不是很强,系统控制板的结构尺寸也比较大。

DSP具有数据处理能力强、速度快等特点,且体积比较小,有利于电路板布局,但DSP在中断处理、位处理或逻辑操作方面不如单片机,资料相对较少,芯片价格和相应的开发套件比较昂贵,专用性比较强,通用性比较弱。

与DSP具有同等性能的ARM微处理器资源丰富,具有很强的通用性,以其高速度、高性能低价格、低功耗等优点而广泛应用于各个领域。

ARM本身是32位处理器,但是集成了16位的Thumb指令集,这使得ARM可以代替16位的处理器使用,同时具有32位处理器的速度,用单片机和DSP实现的系统,ARM都可以实现。

ARM还集成了丰富的片内外设资源,利用自身资源不必增加外围器件就可以实现控制所要求的功能,同时使得机器人控制板的结构尺寸可以做的很小。

另外,利用ARM处理器设计的嵌入式系统还具有非常好的移植性,这是其他处理器所不具备的特点。

考虑到这些因素,本课题决定选择以ARM为核心的微处理器作为机器人底层运动控制芯片。

然而,ARM微处理器有几十种架构,几十个芯片生产厂家以及各种各样的内部功能配置,因此开发时需要对芯片做一些对比分析,芯片选型时主要考虑以下几个因素:1.ARM微处理器内核的选择不同的内核,适用于不同的应用领域。

如ARM7内核没有MMU,而ARM9内核有MMU。

由于uCLinux等不需要MMU单位,因而可以在ARM7上运行,相反,嵌入式Linux具有MMU,因而可以在ARM9上运行。

2.系统的工作频率系统的工作频率很大程度上决定了系统处理任务的能力。

基于S3C2440与0V9650的嵌入式监控设计

保证 图像 质量 , 适合银行 、 小区门禁、 仓库等无人值 守场合 。图 4表 2参 1 0

关 键 词 : 频 监 控 ; 入 式 监 控 ; P G4编 码 :3 2 4 : V 6 0 Lnx 视 嵌 ME - S C 4 0 O 9 5 :iu

中 图分 类 号 :P 7 T 24

文 献标 志 码 : A

t e OV9 5 m a e s n o s wela he e h 6 0 i g e s ra l s t mbe d d L n x s fwae p af r . h tS mo e, t i y tm s e o e t d e i u ot r l to m W a r h s s se i nc d d wi h o t ie pi z d XVI e e d r Al t e e c n e s r ih c mp e so ai n ma e q a i m D n o e . l h s a n u e h g o r s in r to a d i g u lt ma i g i s ia l o a ks y k n t u tb e f rb n ,

只能 工 作 在从 模 式 下 , 以 由 ¥ C 4 0对 O 9 5 所 3 24 V 6 0配

置参数 , 含输 出数 据 的格 式 与 分 辨 率标 准 等 。摄像 包

头产 生数 据输 出时 钟 , 自动 控 制 曝 光 。帧 同步 通 过 检 测H E( R F 水平 参 考 信 号 ) V Y C( 直 同 步信 号 ) 与 SN 垂 来进行 , H E 当 R F为低 电平 且 V Y C处 于上升 沿 时进 SN

基 于 S 2 4 3 4 0与 0V 6 0的 C 95 嵌 入 式 监 控 设 计

GEC2440开发板用户手册-v1.0

ARM9GEC2440开发板用户手册粤嵌中心广州广嵌电子科技有限公司/中心简介粤嵌中心是最早期从事嵌入式产品研发及技术培训的机构,中心拥有自己的产品研发、产品测试、课程技术培训平台,面向社会企业、高校提供技术创新、课程技术培训等一体化服务。

粤嵌中心是广东省政府为了普及嵌入式软件技术知识,提高省内外嵌入式人才的素质,满足社会对嵌入式技术应用人才的需求,面向全社会开展嵌入式相关技术系列培训课程的服务机构。

目前,粤嵌中心已形成嵌入式技术与产品解决方案、嵌入式系统评测认证、技术培训服务和电子商务平台四大业务体系,以“专业诚信、开拓创新、行业引领、齐商共赢”的中心精神为指导,努力为客户的技术创新和产品升级提供支持。

在开发板系列产品方面,GEC目前已经形成了完善的产品体系结构,包括以下四个方面:1、多样化的开发板产品:目前GEC开发板系列产品包括2410开发板、2440开发板、开发板等一系列产品,目标是向有志于从事嵌入式学习及开发的高校、学生、工程师以及企业客户提供完善的嵌入式开发平台的整体解决方案。

2、严谨的产品评测过程:本中心设立了专门的嵌入式产品评测团队,拥有完善的评测设备,保证每个出厂产品都经过严谨的评测过程,从而保证了产品的质量。

3、完善的售后服务:开发板产品出现质量问题10天包换,12个月免费保修。

保修时间之长堪称国内之最。

4、强大的技术支持:本中心拥有雄厚的技术研发团队,拥有强大的技术研发力量,技术领域涉及到嵌入式开发的各个方面,为开发板客户提供全面的技术支持。

目录中心简介 (2)目录 (3)第一章GEC2440V1.0开发板介绍 (4)1.1GEC2440开发板布局 (4)1.2GEC2440开发板实物图 (4)1.3、选配模块 (5)1.4GEC2440开发板硬件构成 (6)1.5硬件资源分配 (7)1.5.1地址空间分配以及片选信号定义 (7)1.5.2接口资源及按键说明 (8)1.6开发板开发套件包含的内容 (10)1.7操作系统支持的驱动 (10)第二章粤嵌GEC2440开发板使用 (13)2.1GEC2440开发板快速使用入门 (13)2.1.1串口连接 (13)2.1.2PC端USB驱动安装 (14)2.2启动LINUX和WINCE (14)2.2.1启动LINUX (14)2.2.2启动WINCE (15)2.3GEC2440的BIOS功能说明 (16)2.4非操作系统下的外围资源测试 (17)2.4.1运行测试程序 (17)2.4.2相关外围资源测试 (19)2.6用SJF2440工具将BIOS烧写到FLASH (26)第三章烧写和启动linux (29)3.1烧写LINUX内核 (29)3.2烧写根文件系统 (30)3.3启动LINUX (31)3.3.1通过BIOS的3号功能启动LINUX (31)3.3.2LINUX的自启动 (32)第四章烧写WINCE和启动WINCE (34)4.1下载运行WINCE (34)4.2烧写WINCE (35)4.3自启动WINCE (35)第一章GEC2440V1.0开发板介绍1.1GEC2440开发板布局1.2GEC2440开发板实物图1.3、选配模块1蓝牙模块选配,实现数据图象等文件的传输,1Mbps 传输速率,USB 1.1总线,支持蓝牙1.1(兼容1.2)版本协议,2.4GHz-2.4835GHz 频谱带宽。

MEMORY存储芯片S3C2440AL-40中文规格书

IIC-BUS INTERFACE SPECIAL REGISTERSMULTI-MASTER IIC-BUS CONTROL (IICCON) REGISTERRegister Address R/W DescriptionReset ValueIICCON0x54000000R/WIIC-Bus control register0x0XIICCON Bit DescriptionInitial StateAcknowledge generation (note 1)[7]IIC-bus acknowledge enable bit.0 = Disable, 1 = EnableIn Tx mode, the IICSDA is free in the ack time.In Rx mode, the IICSDA is L in the ack time.Tx clock source selection [6]Source clock of IIC-bus transmit clock prescaler selection bit.0 = IICCLK = f PCLK /161 = IICCLK = f PCLK /512Tx/Rx Interrupt(note 5)[5]IIC-Bus Tx/Rx interrupt enable/disable bit.0 = Disable, 1 = Enable0Interrupt pending flag (note 2), (note 3)[4]IIC-bus Tx/Rx interrupt pending flag. This bit cannot be written to 1. When this bit is read as 1, the IICSCL is tied to L and the IIC is stopped. To resume the operation, clear this bit as 0.0 = 1) No interrupt pending (when read).2)Clear pending condition &Resume the operation (when write).1 = 1) Interrupt is pending (when read)2)N/A (when write)0Transmit clock value (note 4)[3:0]IIC-Bus transmit clock prescaler.IIC-Bus transmit clock frequency is determined by this 4-bit prescaler value, according to the following formula:Tx clock = IICCLK/(IICCON[3:0]+1).UndefinedNOTES:1.Interfacing with EEPROM, the ack generation may be disabled before reading the last data in order to generate theSTOP condition in Rx mode.2.An IIC-bus interrupt occurs 1) when a 1-byte transmit or receive operation is completed, 2) when a general call or a slaveaddress match occurs, or 3) if bus arbitration fails.3.To adjust the setup time of IICSDA before IISSCL rising edge, IICDS has to be written before clearing the IIC interruptpending bit.4.IICCLK is determined by IICCON[6].Tx clock can vary by SCL transition time.When IICCON[6]=0, IICCON[3:0]=0x0 or 0x1 is not available.5.If the IICON[5]=0, IICON[4] does not operate correctly.So, It is recommended that you should set IICCON[5]=1, although you does not use the IIC interrupt.IIC-BUS INTERFACES3C2410XMULTI-MASTER IIC-BUS CONTROL/STATUS (IICSTAT) REGISTERRegister Address R/W DescriptionReset ValueIICSTAT0x54000004R/WIIC-Bus control/status register0x0IICSTAT Bit DescriptionInitial StateMode selection[7:6]IIC-bus master/slave Tx/Rx mode select bits.00: Slave receive mode 01: Slave transmit mode 10: Master receive mode 11: Master transmit mode00Busy signal status /START STOP condition[5]IIC-Bus busy signal status bit.0 = read) Not busy (when read) write) STOP signal generation 1 = read) Busy (when read)write) START signal generation.The data in IICDS will be transferred automatically just after the start signal.0Serial output [4]IIC-bus data output enable/disable bit.0 = Disable Rx/Tx, 1 = Enable Rx/Tx 0Arbitration status flag[3]IIC-bus arbitration procedure status flag bit.0 = Bus arbitration successful1 = Bus arbitration failed during serial I/O 0Address-as-slave status flag[2]IIC-bus address-as-slave status flag bit.0 = Cleared when START/STOP condition was detected1 = Received slave address matches the address value in the IICADDAddress zero status flag[1]IIC-bus address zero status flag bit.0 = Cleared when START/STOP condition was detected.1 = Received slave address is 00000000b.0Last-received bit status flag[0]IIC-bus last-received bit status flag bit.0 = Last-received bit is 0 (ACK was received).1 = Last-received bit is 1 (ACK was not received).S3C2410X IIC-BUS INTERFACEIIC-BUS INTERFACE S3C2410XS3C2410X SPI INTERFACESPI SPECIAL REGISTERSSPI CONTROL REGISTERRegister Address R/W Description Reset Value SPCON00x59000000R/W SPI channel 0 control register0x00 SPCON10x59000020R/W SPI channel 1 control register0x00SPCONn Bit Description Initial StateSPI Mode Select (SMOD)[6:5]Determine how and by what SPTDAT is read/written.00 = polling mode, 01 = interrupt mode10 = DMA mode, 11 = reserved00SCK Enable (ENSCK)[4]Determine whether you want SCK enable or not (for onlymaster).0 = disable, 1 = enableMaster/Slave Select (MSTR)[3]Determine the desired mode (master or slave).0 = slave, 1 = masterNOTE: In slave mode, there should be set up time formaster to initiate Tx/Rx.Clock Polarity Select (CPOL)[2]Determine an active high or active low clock.0 = active high, 1 = active lowClock Phase Select (CPHA)[1]Select one of two fundamentally different transfer formats.0 = format A, 1 = format BTx Auto Garbage Data mode enable (TAGD)[0]Decide whether the receiving data only needs or not.0 = normal mode, 1 = Tx auto garbage data modeNOTE: In normal mode, if you only want to receive data,you should transmit dummy 0xFF data.。

S3C2440处理器资料

1

S3C2440处理器介绍

1.1三星ARM处理器介绍 1.2 S3C2440功能特点 1.3 S3C2440系统管理/体系结构 1.4 S3C2440存储器 1.5 S3C2440时钟和电源管理

2

1.1三星ARM处理器介绍

S3C44B0:ARM7TDMI、66MHz、集成LCD控制器 (支持STN,但不支持TFT)、无网络接口;适用产品: POS、PDA、E-BOOK、GPS、智能电话、电子书包、 机顶盒,手持游戏机等等。160LQFP,160FBGA。支 持LINUX、PSOS、uC/OSII等。 S3C2410:ARM920T、200MHz、支持TFT、USB HOST、USB DEVICE、 SD Card 以及MMC接口、 触摸屏接口, NAND FLASH直接引导。无网络接口。 适用产品: POS、PDA、E-BOOK、GPS、智能电话、 电子书包、机顶盒,手持游戏机、电子相册、多媒体产 品、视频监控、智能控制仪表等等。272BGA。支持 WINCE、LINUX、VxWorks等。

用于控制各模块是否有频率输入,一般保持默认即可

32

3、时钟控制寄存器(CLKCON续1)

33

3、时钟控制寄存器(CLKCON续2)

Bit3: 1:进入睡眠模式 Bit2:1 进入特别模式(保留模式,没有使用)

34

4、慢时钟控制寄存器(CLKSLOW)

慢时钟模式,用于设置与慢时钟模式相关的配置信息

大纲

s3c2440 时钟频率管理 S3c2440 电源管理模块 相关寄存器使用说明

15

时钟 频率 管理

16

晶振电路和外部时钟

17

时钟源选择

arm920t中S3C2440、S3C2450和S3C6410的区别

arm920t 中S3C2440、S3C2450 和S3C6410 的区别

三星目前推出了S3C6400 和S3C6410,都是基于ARM 架构的,而且硬件管脚兼容,应该说大致的功能基本相同,比较明显的区别就是S3C6410 带有2D/3D 硬件加速

S3C2440 其实是一个很不错的CPU,价格便宜、内部资源多、最主

要的是国内很多人使用,相关的资料比较多。

ARM920T 内核,400M 主频,支持NAND FLASH、NORFLASH、SDRAM、支持STN/TFT LCD、4 通道DMA、3 通道UART、2 通道SPI、IIC 总线、IIS/AC97 音频控制器、

SD/MMC 控制器、2 通道USB HOST 1 通道USB DEVICE、4 通道PWM、8 通道A/D 转换、触摸屏控制器、RTC、CMOS 摄像头、多功能IO 及多种电

源管理。

S3C2440、S3C2450 和S3C6410 之间区别

作为GPS、PDA、数字电视等手持设备的主要方案处理器提供方韩

国Sumsung 公司,最近又新推出ARM 处理器S3C2450、S3C6410 芯片。

这些平台又与S3C2440 处理器有哪些区别优势。

S3C2440外部中断操作

1

20100831

编写:小龍

吧把 INTPND 中相应位置 1,所以同一时间只有一位是 1。也就是说前面的寄存 器置 1 是表示发生了,只有 INTPND 置 1,CPU 才会处理。 INTOFFSET :用来表示 INTPND 中哪一位置 1 了,好让你查询,普 通中断跳转时查询用。清除 INTPND、SRCPND 时自动清除。 4.各寄存器关系:

5

20100831 case 0x2000: if(rGPBDAT & 0x80) LED3_ON(); else LED3_OFF(); break; case 0x4000: if(rGPBDAT & 0x100) LED4_ON(); else LED4_OFF(); break; case 0x8000: LED_ON(); break; case 0x80000: LED_OFF(); break;

下面看图说明: 5.中断过程。 a 如果是不带子中断的内部中断:发生后 SRCPND 相应位置 1,如果没有被 INTMSK 屏蔽,那么等待进一步处理。 b 如果是带子中断的内部中断:发生后 SUBSRCPND 相应位置 1,如果没有被 INTSUBMSK 屏蔽,那么 SRCPND 相应位置 1,等待进一步处理,几个 SUBSRCPND 可能对应同一个 SRCPND,对应表如下: SRCPND SUBSRCPND INT_UART0 INT_RXD0,INT_TXD0,INT_ERR0 INT_UART1 INT_RXD1,INT_TXD1,INT_ERR1 INT_UART2 INT_RXD2,INT_TXD2,INT_ERR2 INT_ADC INT_ADC_S, INT_TC INT_CAM INT_CAM_C, INT_CAM_P INT_WDT_AC97 INT_WDT, INT_AC97

音乐播放器的设计与实现

第一章绪论1.1背景随着电子技术的飞速发展,嵌入式设备在各领域的应用越来越广泛,复杂度也越来越高,对其他开发方法也提出了更多的要求和更大的挑战。

在嵌入式设备系统开发过程中需要将软件应用与操作系统编译连接成一个整体,然后下载到目标机上运行,所以,嵌入式设备的开发过程是一个复杂的过程。

MP3作为高质量音乐压缩标准,给音频产业带来了具大的冲击。

MP3技术使音乐数据压缩比率大,回放质量高。

如CD格式的音乐数据压缩成MP3格式,音效相差无己,但大小至少可压缩12倍。

由于MP3音乐的较小数据量和近乎完美的播放效果使其在网络上传输得以实现。

1995年,MP3格式的音乐文件刚在网络上传播时,主要用Winamp等播放软件进行播放,使MP3音乐无法脱离计算机进行播放,给音乐欣赏带来了不便。

近几年以来,随着MP3播放器的出现及其技术的发展,人们对MP3播放器的要求越来越高,制造商在MP3播放器的选型、设计、开发、附加功能和适用领域等方面做了很多努力,设计了多种方案。

本设计主要是利用ARM技术设计一款新型的MP3播放器。

ARM9是ARM公司的16/32位RSIC处理器,是适用于普通设备的一种高性价比的微控制器。

本设计采用的MCU是三星公司推出的ARM9芯片S3C2440,具有低价格、低功耗、高性能、超小体积等特点主要适用于中高端场合,目前在嵌入式系统中正得到日益广泛的应用。

S3C2440主频高达400M,片上集成了丰富的资源:如IIS(Inter-IC sound)总线与DMA控制器,为与数模转换器(DAC)的连接提供了一种理想的解决方案。

MP3播放器的设计比较复杂且对处理器的要求较高,因而MP3播放器必须仔细设计以降低成本。

本设计是在ARM9平台上设计、实现一个MP3播放器。

第二章系统总体方案2.1 系统功能本设计提出了一种基于嵌入式ARM处理器硬件平台的MP3播放器设计方法。

此播放器采用ARM体系结构中的ARM9作为系统控制器,利用外围设备USB通用串行接口下载MP3歌曲,用flashcard存贮MP3文件。

嵌入式系统试题库

嵌入式系统试题库一、选择题(20分)1、下列描述不属于RISC 计算机的特点的是()。

A. 流水线每周期前进一步。

B. 更多通用寄存器。

C. 指令长度不固定,执行需要多个周期。

D. 独立的Lo a d和St or e指令完成数据在寄存器和外部存储器之间的传输。

2、存储一个32位数Ox2168465到2000H,....__,2003H四个字节单元中,若以小端模式存储,则2000H 存储单元的内容为()。

A 、Ox21A 、OvB、Ox68B 、3.3vC 、Ox65C 、+sv ,..___,+15vD 、Ox023、RS232-C 串口通信中,表示逻辑1的电平是()。

D 、-5v ,.___,-15v4、ARM 汇编语句"A DD R O, R 2, R 3, LSL#l"的作用是()。

A. R O= R 2 + (R3 << 1)C. R 3= R O+ (R 2 << 1) B. R O=(R 2<< 1) + R 3D. (R 3 << 1)= R O+ R2 5、I RQ中断的入口地址是()。

A 、OxOOOOOOOOB 、Ox00000008C 、Ox00000018D 、Ox000000146、S3C 2440X 1/0口常用的控制器是()。

A. 端口控制寄存器(GP A C ON -G PJ C O N )。

B. 端口数据寄存器(GPA DAT-G PJ D AT )。

C. 外部中断控制寄存器(EXT I N T n )。

D. 以上都是。

7、GET伪指令的含义是()A. 包含一个外部文件B. 定义程序的入口C. 定义一个宏D. 声明一个变量8、A DD R O, R l, #3 ; #3属于()寻址方式。

A. 立即寻址B. 多寄存器寻址C. 寄存器直接寻址D. 相对寻址9、ARM 指令集和Th um b 指令集分别是()位的。

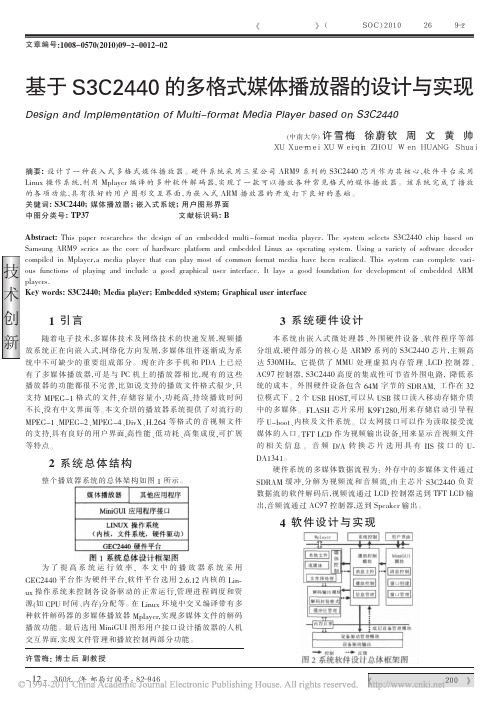

基于S3C2440的多格式媒体播放器的设计与实现

技术创新《微计算机信息》(嵌入式与SOC)2010年第26卷第9-2期博士论坛基于S3C2440的多格式媒体播放器的设计与实现Design and Implementation of Multi-format Media Player based on S3C2440(中南大学)许雪梅徐蔚钦周文黄帅XUXue-meiXUWei-qinZHOUWenHUANGShuai摘要:设计了一种嵌入式多格式媒体播放器。

硬件系统采用三星公司ARM9系列的S3C2440芯片作为其核心,软件平台采用Linux操作系统,利用Mplayer编译的多种软件解码器,实现了一款可以播放各种常见格式的媒体播放器。

该系统完成了播放的各项功能,具有很好的用户图形交互界面,为嵌入式ARM播放器的开发打下良好的基础。

关键词:S3C2440;媒体播放器;嵌入式系统;用户图形界面中图分类号:TP37文献标识码:BAbstract:This paper researches the design of an embedded multi-format media player.The system selects S3C2440chip based on Samsung ARM9series as the core of hardware platform and embedded Linux as operating ing a variety of software decoder compiled in Mplayer,a media player that can play most of common format media have been realized.This system can complete vari-ous functions of playing and include a good graphical user interface.It lays a good foundation for development of embedded ARM players.Key words:S3C2440;Media player;Embedded system;Graphical user interface文章编号:1008-0570(2010)09-2-0012-021引言随着电子技术,多媒体技术及网络技术的快速发展,视频播放系统正在向嵌入式,网络化方向发展,多媒体组件逐渐成为系统中不可缺少的重要组成部分。

S3C2440重要资料

S3C2440与SDRAM的地址连线分析S3C2440有27根地址线ADDR[26:0],8根片选信号ngcs0-ngcs7,对应bank0-ba nk7,当访问bankx的地址空间,ngcsx引脚为低电平,选中外设。

2^27=2^7 * 2^10 * 2^10 = 128Mbyte8*128Mbyte = 1Gbyte所以S3C2440总的寻址空间是1Gbyte。

市面上很少有32位宽度的单片SDRAM,一般选择2片16位SDRAM扩展得到32位SDRAM.选择的SDARM是HY57V561620F,4Mbit * 4bank *16,共32Mbyte。

首先了解下SDRAM的寻址原理。

SDRAM内部是一个存储阵列。

可以把它想象成一个表格。

和表格的检索原理一样,先指定行,再指定列,就可以准确找到所需要的存储单元。

这个表格称为逻辑B ANK。

目前的SDRAM基本都是4个BANK。

寻址的流程就是先指定BANK地址,再指定行地址,最后指定列地址。

这就是SDRAM的寻址原理。

存储阵列示意图如下:查看HY57V561620F的资料,这个SDRAM有13根行地址线 RA0-RA129根列地址线CA0-CA82根BANK选择线 BA0-BA1SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写的地址分两次输入到芯片中,每一次都由同一组地址线输入。

两次送到芯片上去的地址分别称为行地址和列地址。

它们被锁存到芯片内部的行地址锁存器和列地址锁存器。

/RAS是行地址锁存信号,该信号将行地址锁存在芯片内部的行地址锁存器中;/CAS是列地址锁存信号,该信号将列地址锁存在芯片内部的列地址锁存器中。

地址连线如下图:SDRAM的A0接S3C2440的ADDR2,很多初学者都对这里又疑问。

A0为什么不接ADDR0?要理解这种接法,首先要清楚在CPU的寻址空间中,字节(8位)是表示存储容量的唯一单位。

用2片HY57V561620F扩展成32位SDRAM,可以认为每个存储单元是4个字节。

嵌入式复习题

一、简答题1.什么是嵌入式系统?嵌入式系统的特点是什么?答:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能,可靠性,成本,体积,功耗严格要求的专用计算机系统特点:与应用密切相关,实时性,复杂的算法,制造成本,功耗,开发和调试,可靠性,体积2.简要说明嵌入式系统的硬件组成和软件组成。

答:硬件组成:微处理器,存储器,输入设备和输出设备。

软件组成:操作系统,文件系统,图形用户接口,网络系统,通用组建模块。

3.S3C2410A的AHB总线上连接了那些控制器?APB总线上连接了那些部件?AHB:LCD控制器,LCD DMA,总线控制器,USB主控制器,中断控制器,ExtMaster,电源管理,Nandflash控制器,储存器控制器。

APB:通用异步收发器,部集成电路总线(IIC),USB设备控制器,集成电路部声音总线(IIS),MMC/SD/SDIO主控制器,通用I/O端口(GPIO),看门狗定时器(WDT),定时时钟(RTC),总线控制器,A/D转换器,串行外设接口,定时器/脉宽调制。

4.ARM体系结构支持几种类型的异常,并说明其异常处理模式和优先级状态?答,支持7种类型的异常异常处理过程:(进入异常)PC→LR,CPRS→SPSR,设置CPSR的运行模式位,跳转到相应的异常处理程序,(异常返回)LR→PC,SPSR→CPSR,若在进入异常处理时设置中断禁止位,要在此清楚,复位异常处理程序不需要返回。

Reset>数据中指>快速中断请求(FIQ)>中断请求(IRQ)>指令预取中止>未定义指令和软件中止。

5.存储器生长堆栈可分为哪几种?各有什么特点?4种,满递增堆栈,满递减堆栈,空递增堆栈,空递减堆栈。

6.简述存储器系统层次结构与特点。

答:层次结构主要表达在“Cache-主存”层次和“主存-辅存”(Cache,主存储器,辅助存储器),前者主要解决CPU 和主存速度不匹配的问题,后者主要解决存储器系统的问题。

S3c2440处理器与s3c2410相比

附-s3c2410/s3c2440处理器介绍

College of Computer Science & Technology

S3C2410A简介

鲁东大学 LUDONG UNIVERSITY

S3C2410是Samsung公司推出的32位RISC处理器,主要面 向高性价比、低功耗的手持设备应用。

DRAMC

SD/SDIO CAM I/F IIC I/F Control PMIC Main Charger USB Charger 5V DC 5V USB Main TFT LCD & TSP TV

1/2/4/8/16 bpp Up to QVGA

System Power

TFT/CSTN LCDC + SPI(GPIO) + TSADC

内核电压1.8V/2.0V,存储器电压3.3V,外部I/O电压3.3V

S3C2410有S3C2410X和S3C2410A两个型号,A型是X型的改 进型,具有更好的性能和更低的功耗。

32位ARM920T 内核,同时还采用了AMBA(Advanced Microcontroller Bus Architecture)。

S3C2410A结构框图

鲁东大学 LUDONG UNIVERSITY

S3c2410处理 器结构框图

S3C2410A结构框图

鲁东大学 LUDONG UNIVERSITY

S3c2440处理 器结构框图

UART1

UART2

GPIO

USB Host 1.1 USB Device 1.1

SMC ARM920T 300/400Mhz 16K/16K ID Cache SPI TDMB/WLAN

S3C2440输入-输出端口

S3C2440输入/输出端口

端口控制描述(详细见S3C2440 的数据手册)

端口配置寄存器(GPACON 至GPJCON)

端口数据寄存器(GPADAT 至GPJDAT)

端口上拉寄存器(GPBUP 至GPJUP)

杂项控制寄存器

外部中断控制寄存器

用一个实例(LED 流水灯)来学习下输入/输出端口

(在TQ2440 开发板中是用GPB5~8 控制LED1~4)

#include”2440addr.h”#defineLED1_ON(rGPBDAT&=~(1其中启动代码那块你需要自己加上去,

说明下2440addr.h:定义2440 寄存器的地址,包括存储器寄存器地址、中断向量地址、DMA 地址、时钟电源管理寄

存器地址、LCD 控制寄存器地址、Nand Flash 地址、UART、PWM 定时器、USB Device、WatchDog、IIC、IIS、I/O

端口、ADC、SPI、SD 卡、ISR 寄存器地址等。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

第1讲三星s3c2440微处理器

掉电模式:所有外设和内核的电源都切断了;

1. 可以通过EINT[15:0]或RTC报警中断来从掉电模式中唤醒处

理器

12

S3C2440A特性

中断控制器

60个中断源(1个看门狗定时器,5个定时器, 9个UARTs,24个外部中断,4个DMA,2个 RTC,2 个ADC,1 个IIC,2 个SPI,1个SDI, 2个USB,1 个LCD和1个电池故障,1个NAND 和2个Camera),1个AC97音频

电平/边沿触发模式的外部中断源 可编程的边沿/ 电平触发极性 1. 支持为紧急中断请求提供快速中断服务

13

S3C2440A特性

具有脉冲带宽调制功能的定时器(PWM) 4 通道16位具有PWM功能的定时器,1通道16

位内部定时器,可基于DMA或中断工作 可编程的占空比周期,频率和极性 能产生死区 1. 支持外部时钟源

Main TFT LCD & TSP

1/2/4/8/16 bpp Up to QVGA

SD/SDIO IIS I/F

Audio Codec

TDMB/WLAN

SD/MMC Stereo Speaker Head Set Mic

引言

三星公司推出的16/32位RISC微处理器 S3C2440A,为手持设备和一般类型应用 提供了低价格、低功耗、高性能小型微 控制器的解决方案。

–LCD 实际尺寸的典型值是:640 ×480,320 ×240, 160×160 及其他

–最大虚拟屏幕大小是4M字节

–256 色模式下支持的最大虚拟屏是:4096 ×1024,

2048 ×2048,1024×4096等

17

S3C2440A特性

TFT彩色显示屏 支持彩色TFT的1,2,4或8bbp(像素每位)调色显示 支持16,24bbp无调色真彩显示TFT 在24bbp 模式下支持最大16M色TFT lpc3600定时控制器,为嵌入式lts350Q1-PD1/2(SAMSUNG

IIS接口模仿简易音频播放器

IIS接口模仿简易音频播放器IIS接口组合UDA1341编解码芯片实现音频播录放功能。

产品介绍模仿简易音频播放器实验主要是在ARM开发板上实现的,它主要是通过S3C2440A 芯片中的IIS总线来实现音频数据的传输,UDA1341芯片进行音频信号的编码解码,也就是ADC和DAC的转换,最后实现录音及放音的功能。

产品功能介绍总功能介绍使用说明:按键1:开始放音、暂停、关闭(长按(不小于3s))按键2:模式(1调音、2调歌、3录音)按键3:1、音量调小;2、上一首;3、录音开始按键4:1、音量调大;2、下一首;3、录音结束灯状态说明:灯1闪烁:放歌状态灯一亮:暂停灯全灭:关闭灯2亮:状态1(调音模式)灯3亮:状态2(调歌模式)灯4亮:状态3(录音模式)灯4闪烁:开始录音(录音结束灯4亮)分功能放音按键1 开始,暂停,关闭按键2 下一首按键3 上一首录音按键1 开始,暂停,关闭灯状态说明:灯1闪烁:放歌状态灯2亮/灭:录音/结束需求分析详细设计s3c2440有关IIS的寄存器除了IISPSR外,还包括IIS控制寄存器IISCON,主要用于控制数据传输的方式、预分频器和IIS接口是否开启;IIS模式寄存器IISMOD,主要用于设置IIS的时钟源、主从方式、接收发送方式、串行接口方式、每个声道串行数据位数和各种频率值;IIS的FIFO接口寄存器IISFCON用于设置和判断数据传输的FIFO 状态;而寄存器IISFIFO则用于音频数据的传输。

s3c2440与UDA1341之间除了我们前面介绍过的IIS接口相连接外,还有一个称之为L3总线的连接,用于s3c2440配置UDA1341内部的寄存器。

由于s3c2440不具备L3总线接口,因此我们是用三个通用IO口来模拟L3,从而实现L3总线的传输。

UDA1341有两种模式:地址模式和数据传输模式。

地址模式表示传输的是地址信息,它的高6位永远是000101,低两位表示的是传输的模式,是状态模式、数据0模式还是数据1模式,其中状态模式主要用于配置UDA1341的各类初始状态,数据模式主要用于改善音频输入、输出的效果。

IIS-I2S音频总线知识

IIS音频总线学习(一)数字音频技术一、声音的基本概念声音是通过一定介质传播的连续的波。

图1 声波重要指标:1. 振幅:音量的大小2. 周期:重复出现的时间间隔3. 频率:指信号每秒钟变化的次数声音按频率分类:图2 声音的频率(语音信号频率范围:300Hz-3kHz)声音的传播携带了信息,它是人类传播信息的一种主要媒体。

声音的三种类型:1. 波形声音:包含了所有声音形式2. 语音:不仅是波形声音,而且还有丰富的语言内涵(抽象→提取特征→意义理解)3. 音乐:与语音相比,形式更规范。

音乐是符号化的声音。

二、声音的数字化1.声音信号的类型∙模拟信号(自然界、物理)∙数字信号(计算机)2.声音数字化过程图3 声音数字化过程3.声音数字化过程示意图音频数据量=采样频率×量化位数×声道数/8(字节/秒)WAV是Microsoft/IBM共同开发的PC波形文件。

因未经压缩,文件数据量很大。

特点:声音层次丰富,还原音质好2.MP3文件MP3(MPEG Audio layer3)是一种按MPEG标准的音频压缩技术制作的音频文件。

特点:高压缩比(11:1),优美音质3.WMA文件WMA(Windows Media Audio)是Windows Media格式中的一个子集(音频格式)。

特点:压缩到MP3一半4.MIDI文件MIDI(乐器数字接口)是由一组声音或乐器符号的集合。

特点:数据量很小,缺乏重现自然音四、数字音频压缩标准1.音频压缩方法概述图5压缩编码技术是指用某种方法使数字化信息的编码率降低的技术音频信号能压缩的基本依据:①声音信号中存在大量的冗余度;②人的听觉具有强音能抑制同时存在的弱音现象。

音频信号压缩编码的分类:①无损压缩(熵编码)霍夫曼编码、算术编码、行程编码②有损压缩波形编码--PCM、DPCM、ADPCM 、子带编码、矢量量化参数编码--LPC混合编码--MPLPC、CELP声卡是负责录音、播音和声音合成的一种多媒体板卡。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

s3c2440的IIS应用——放音与录音No Comments知识点, by lyping. | Tags: I2CIIS(Inter-IC Sound)由飞利浦公司开发,是一种常用的音频设备接口,主要用于CD、MD、MP3等设备。

s3c2440一共有5个引脚用于IIS:IISDO、IISDI、IISSCLK、IISLRCK和CDCLK。

前两个引脚用于数字音频信号的输出和输入,另外三个引脚都与音频信号的频率有关,可见要用好IIS,就要把信号频率设置正确。

IISSCLK为串行时钟,每一个时钟信号传送一位音频信号,因此IISSCLK 的频率=声道数×采样频率×采样位数,如采样频率fs为44.1kHz,采样的位数为16位,声道数2个(左、右两个声道),则IISSCLK的频率=32fs=1411.2kHz。

IISLRCK为帧时钟,用于切换左、右声道,如IISLRCK为高电平表示正在传输的是左声道数据,为低电平表示正在传输的是右声道数据,因此IISLRCK的频率应该正好等于采样频率。

由于IIS只负责数字音频信号的传输,而要真正实现音频信号的放、录,还需要额外的处理芯片(在这里,我们使用的是UDA1341),CDCLK为该芯片提供系统同步时钟,即编解码时钟,主要用于音频的A/D、D/A采样时的采样时钟,一般CDCLK为256fs或384fs。

通过以上分析可以发现,采样频率fs对频率的设置至关重要。

而fs不是任意设置的,一般基于不同的应用场合和听觉效果,而设置不同的几个固定的值,如8kHz、16kHz、22.05kHz、44.1kHz、48kHz、96kHz等。

为了使系统得到以fs为基数的各类时钟信号,就要重新调整系统时钟。

s3c2440用于IIS的时钟源有PCLK和MPLLin,我们这里选择PCLK作为IIS的时钟源。

PCLK经过两个预分频器处理后分别得到IISSCLK、IISLRCK和CDCLK(预分频器A得到IISSCLK、IISLRCK,预分频器B得到CDCLK)。

寄存器IISPSR是IIS预分频器寄存器,5~9位是预分频器A,0~4位是预分频器B,一般来说,这两个预分频器的值N相等,即只要知道一个,另一个也就知道,而这里我们是通过CDCLK来计算预分频器B的值N的,即CDCLK=PCLK / (N+1)。

PCLK与FCLK有一定的比例关系,而FCLK又是由输入频率Fin得到。

在这里,我们为了简化计算,不改变PCLK与FCLK的比例关系(即维持在启动代码中定义的1:8的关系),那么由Fin 而得到CDCLK一共涉及到四个参数:MDIV、PDIV、SDIV和前面公式中的N,涉及到的寄存器有MPLLCON和IISPSR。

因此要得到这四个参数值,就需要一点耐心地计算,原则是误差最小,其中需要注意的是,计算的结果(包括中间过程的结果)不要溢出,即不要超过32位。

例如Fin为12MHz,我们设置采样频率fs=44.1kHz,而CDCLK=384fs=16.9344MHz,那么经过计算,最终得到N=3,MDIV=150,PDIV=5,SDIV=0,即IISPSR = (3< <5) | 3;,MPLLCON = (150<<12) | (5<<4) | 0;。

s3c2440有关IIS的寄存器除了IISPSR外,还包括IIS控制寄存器IISCON,主要用于控制数据传输的方式、预分频器和IIS接口是否开启;IIS模式寄存器IISMOD,主要用于设置IIS的时钟源、主从方式、接收发送方式、串行接口方式、每个声道串行数据位数和各种频率值;IIS的FIFO 接口寄存器IISFCON用于设置和判断数据传输的FIFO状态;而寄存器IISFIFO则用于音频数据的传输。

由于s3c2440要实现IIS的录、放音,还需要UDA1341芯片,因此我们再简要介绍一下这个芯片的使用。

s3c2440与UDA1341之间除了我们前面介绍过的IIS接口相连接外,还有一个称之为L3总线的连接,用于s3c2440配置UDA1341内部的寄存器。

由于s3c2440不具备L3总线接口,因此我们是用三个通用IO口来模拟L3,从而实现L3总线的传输。

UDA1341有两种模式:地址模式和数据传输模式。

地址模式表示传输的是地址信息,它的高6位永远是000101,低两位表示的是传输的模式,是状态模式、数据0模式还是数据1模式,其中状态模式主要用于配置UDA1341的各类初始状态,数据模式主要用于改善音频输入、输出的效果。

下面我们就给出具体的程序,在这里我们使用的是正常模式来实现数据的输入和输出的,即不使用DMA模式。

首先是实现s3c2440对某一音频信号数据的输出,即放音。

我们事先已知道该音频信号的各类特性,如采样频率、声道数、采样信号的位数等。

…………//L3接口#define L3C (1<<4) //GPB4 = L3CLOCK#define L3D (1<<3) //GPB3 = L3DATA#define L3M (1<<2) //GPB2 = L3MODE//纯音频信号数据数组unsigned char music[ ] = {0xB8, 0xFF, 0xBA, 0xFF, 0xBF, 0xFF, 0xC0, 0xFF, 0xD4, 0xFF, 0xD3, 0xFF, 0xF2, 0xFF, 0xED, 0xFF,0x0E, 0×00, 0×05, 0×00, 0x1C, 0×00, 0x0F, 0×00, 0×15, 0×00, 0×06, 0×00, 0xFC, 0xFF, 0xEC, 0xFF,…………}//L3总线接口的写函数//输入参数data为要写入的数据//输入参数address,为1表示地址模式,为0表示数据传输模式static void WriteL3(U8 data,U8 address){int i,j;if(address == 1)//地址模式;rGPBDAT = rGPBDAT & ~(L3D | L3M | L3C) | L3C; //L3D=L, L3M=L(地址模式), L3C=HElse//数据模式;rGPBDAT = rGPBDAT & ~(L3D | L3M | L3C) | (L3C | L3M); //L3M=H(数据传输模式) for(i=0;i<10;i++); //等待一段时间//并行数据转串行数据输出,以低位在前、高位在后的顺序for(i=0;i<8;i++){if(data & 0×1) // H{rGPBDAT &= ~L3C; //L3C=LrGPBDAT |= L3D; //L3D=Hfor(j=0;j<5;j++); //等待一段时间rGPBDAT |= L3C; //L3C=HrGPBDAT |= L3D; //L3D=Hfor(j=0;j<5;j++); //等待一段时间}else // L{rGPBDAT &= ~L3C; //L3C=LrGPBDAT &= ~L3D; //L3D=Lfor(j=0;j<5;j++); //等待一段时间rGPBDAT |= L3C; //L3C=H使CLOCK 为1;rGPBDAT &= ~L3D; //L3D=Lfor(j=0;j<5;j++); //等待一段时间}data >>= 1;}rGPBDAT = rGPBDAT & ~(L3D | L3M | L3C) | (L3C | L3M); //L3M=H,L3C=H}//放音void playsound(unsigned char *buffer, int length){int count,i;char flag;rGPBDAT = rGPBDAT & ~(L3M|L3C|L3D) |(L3M|L3C); //L3开始传输:L3M=H, L3C=H //配置UDA1341WriteL3(0×14 + 2,1); //状态模式(000101xx+10)WriteL3(0×60,0); //0,1,10, 000,0 : 状态0,复位WriteL3(0×14 + 2,1); //状态模式(000101xx+10)WriteL3(0×10,0); //0,0,01, 000,0 : 状态0, 384fs,IIS,no DC-filteringWriteL3(0×14 + 2,1); //状态模式(000101xx+10)WriteL3(0xc1,0); //1,0,0,0, 0,0,01:状态1,//Gain of DAC 6 dB,Gain of ADC 0dB,ADC non-inverting,//DAC non-inverting,Single speed playback,ADC-Off DAC-On//配置s3c2440的IIS寄存器//预分频器为3,所以CDCLK=PCLK/(3+1)=16.928kHzrIISPSR = 3< <5|3;//无效DMA,输入空闲,预分频器有效rIISCON = (0<<5)|(0<<4)|(0<<3)|(1<<2)|(1<<1);//PCLK为时钟源,输出模式,IIS模式,每个声道16位,CODECLK=384fs,SCLK=32fs rIISMOD = (0<<9)|(0<<8)|(2<<6)|(0<<5)|(0<<4)|(1<<3)|(1<<2)|(1<<0); rIISFCON = (0<<15)|(1<<13); //输出FIFO正常模式,输出FIFO使能flag=1;count=0;//开启IISrIISCON |= 0×1;while(flag){if((rIISCON & (1<<7))==0) //检查输出FIFO是否为空{//FIFO中的数据为16位,深度为32//当输出FIFO为空时,一次性向FIFO写入32个16位数据for(i=0;i<32;i++){rIISFIFO=(buffer[2*i+count])+(buffer[2*i+1+count]<<8);//每一次写两个字节,64字节,须写32次;}count+=64;if(count>length)flag=0; //音频数据传输完,则退出}}rIISCON = 0×0; //关闭IIS}void Main(void){//配置MPLL//fs=44.1kHz,CODECLK=384fs=16.9344MHz//不改变CLKDIVN,所以PCLK=FCLK/8//MPLLCON:MDIV=150,PDIV=5,SDIV=0,所以FCLK=541.7143MHz,PCLK=67.714MHz rMPLLCON = (150< <12) | (5<<4) | 0;//配置L3接口总线,GPB2:L3MODE, GPB3:L3DATA, GPB4:L3CLOCKrGPBCON = 0×015550; //输出rGPBUP = 0x7ff; //上拉无效//配置IIS接口rGPEUP = rGPEUP & ~(0x1f) | 0x1f; //上拉无效,GPE[4:0] 1 1111rGPECON = rGPECON & ~(0x3ff) | 0x2aa;playsound(music,sizeof(music));while(1){;}}上面的程序可以实现简单的播放内存中固有音频数据的功能,下面的程序实现了录制一段音频数据,然后再播出的功能。