74VCX16373MTD中文资料

sn74lvth16373—锁存器

FEATURESSN54LVTH16373...WD PACKAGESN74LVTH16373... DGG OR DL PACKAGE(TOP VIEW)CCCC DESCRIPTION/ORDERING INFORMATIONSN54LVTH16373,SN74LVTH163733.3-V ABT16-BIT TRANSPARENT D-TYPE LATCHESWITH3-STATE OUTPUTSSCBS144P–MAY1992–REVISED NOVEMBER2006•Members of the Texas Instruments Widebus™Family•State-of-the-Art Advanced BiCMOSTechnology(ABT)Design for3.3-V Operationand Low Static-Power Dissipation•Support Mixed-Mode Signal Operation(5-VInput and Output Voltages With3.3-V V CC)•Support Unregulated Battery Operation Downto2.7V•Typical V OLP(Output Ground Bounce)<0.8Vat V CC=3.3V,T A=25°C•I off and Power-Up3-State Support HotInsertion•Bus Hold on Data Inputs Eliminates the Needfor External Pullup/Pulldown Resistors•Distributed V CC and GND Pins MinimizeHigh-Speed Switching Noise•Flow-Through Architecture Optimizes PCBLayout•Latch-Up Performance Exceeds500mA PerJESD17•ESD Protection Exceeds JESD22–2000-V Human-Body Model(A114-A)–200-V Machine Model(A115-A)The'LVTH16373devices are16-bit transparent D-type latches with3-state outputs designed for low-voltage (3.3-V)V CC operation,but with the capability to provide a TTL interface to a5-V system environment.These devices are particularly suitable for implementing buffer registers,I/O ports,bidirectional bus drivers,and working registers.ORDERING INFORMATIONT A PACKAGE(1)ORDERABLE PART NUMBER TOP-SIDE MARKINGFBGA–GRD SN74LVTH16373GRDRReel of1000LL373FBGA–ZRD(Pb-free)SN74LVTH16373ZRDRTube of25SN74LVTH16373DLSN74LVTH16373DLG4SSOP–DL LVTH16373–40°C to85°C Reel of1000SN74LVTH16373DLRSN74LVTH16373DLRG4TSSOP–DGG Reel of2000SN74LVTH16373DGGR LVTH16373VFBGA–GQL SN74LVTH16373GQLRReel of1000LL373VFBGA–ZQL(Pb-free)SN74LVTH16373ZQLR(1)Package drawings,standard packing quantities,thermal data,symbolization,and PCB design guidelines are available at/sc/package.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.Widebus is a trademark of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©1992–2006,Texas Instruments Incorporated Products conform to specifications per the terms of the Texas On products compliant to MIL-PRF-38535,all parameters are Instruments standard warranty.Production processing does not tested unless otherwise noted.On all other products,production necessarily include testing of all parameters.processing does not necessarily include testing of all parameters.DESCRIPTION/ORDERING INFORMATION (CONTINUED)GQL OR ZQL PACKAGE(TOP VIEW)J H G F E D C B A 213465KSN54LVTH16373,SN74LVTH163733.3-V ABT 16-BIT TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTSSCBS144P–MAY 1992–REVISED NOVEMBER 2006ORDERING INFORMATION (continued)T APACKAGE (1)ORDERABLE PART NUMBER TOP-SIDE MARKING TubeSNJ54LVTH16373WD –55°C to 125°CCFP –WDSNJ54LVTH16373WD5962-9681001QXAThese devices can be used as two 8-bit latches or one 16-bit latch.When the latch-enable (LE)input is high,the Q outputs follow the data (D)inputs.When LE is taken low,the Q outputs are latched at the levels set up at the D inputs.A buffered output-enable (OE)input can be used to place the eight outputs in either a normal logic state (high or low logic levels)or a high-impedance state.In the high-impedance state,the outputs neither load nor drive the bus lines significantly.The high-impedance state and the increased drive provide the capability to drive bus lines without interface or pullup components.OE does not affect internal operations of the latch.Old data can be retained or new data can be entered while the outputs are in the high-impedance state.Active bus-hold circuitry holds unused or undriven inputs at a valid logic e of pullup or pulldown resistors with the bus-hold circuitry is not recommended.When V CC is between 0and 1.5V,the devices are in the high-impedance state during power up or power down.However,to ensure the high-impedance state above 1.5V,OE should be tied to V CC through a pullup resistor;the minimum value of the resistor is determined by the current-sinking capability of the driver.These devices are fully specified for hot-insertion applications using I off and power-up 3-state.The I off circuitry disables the outputs,preventing damaging current backflow through the devices when they are powered down.The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down,which prevents driver conflict.TERMINAL ASSIGNMENTS (1)(56-Ball GQL/ZQL Package)123456A 1OE NC NC NC NC 1CLK B 1Q21Q1GND GND 1D11D2C 1Q41Q3V CC V CC 1D31D4D 1Q61Q5GNDGND1D51D6E 1Q81Q71D71D8F 2Q12Q22D22D1G 2Q32Q4GND GND 2D42D3H 2Q52Q6V CC V CC 2D62D5J 2Q72Q8GND GND 2D82D7K 2OENCNCNCNC2CLK(1)NC –No internal connection2Submit Documentation FeedbackGRD OR ZRD PACKAGE(TOP VIEW)JH G F E D C B A 2134651OE 1LE1D1To Seven Other Channels1Q12OE 2LE2D12Q1To Seven Other ChannelsPin numbers shown are for the DGG, DL, and WD packages.SN54LVTH16373,SN74LVTH163733.3-V ABT 16-BIT TRANSPARENT D-TYPE LATCHESWITH 3-STATE OUTPUTSSCBS144P–MAY 1992–REVISED NOVEMBER 2006TERMINAL ASSIGNMENTS (1)(54-Ball GRD/ZRD Package)123456A 1Q1NC 1OE 1LE NC 1D1B 1Q31Q2NC NC 1D21D3C 1Q51Q4V CC V CC 1D41D5D 1Q71Q6GND GND 1D61D7E 2Q11Q8GND GND 1D82D1F 2Q32Q2GND GND 2D22D3G 2Q52Q4V CC V CC 2D42D5H 2Q72Q6NC NC 2D62D7J2Q8NC2OE2LENC2D8(1)NC –No internal connectionFUNCTION TABLE (8-BIT SECTION)INPUTSOUTPUTQOE CLK D L H H H L H L L L L X Q 0HXXZLOGIC DIAGRAM (POSITIVE LOGIC)3Submit Documentation FeedbackAbsolute Maximum Ratings (1)Recommended Operating Conditions (1)SN54LVTH16373,SN74LVTH163733.3-V ABT 16-BIT TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTSSCBS144P–MAY 1992–REVISED NOVEMBER 2006over operating free-air temperature range (unless otherwise noted)MINMAX UNIT V CC Supply voltage range –0.5 4.6V V I Input voltage range (2)–0.57V V O Voltage range applied to any output in the high-impedance or power-off state (2)–0.57V V O Voltage range applied to any output in the high state (2)–0.5V CC +0.5V SN54LVTH1637396I O Current into any output in the low state mA SN74LVTH16373128SN54LVTH1637348I O Current into any output in the high state (3)mA SN74LVTH1637364I IK Input clamp current V I <0–50mA I OKOutput clamp currentV O <0–50mADGG package70DL package 63θJAPackage thermal impedance (4)°C GQL/ZQL package 42GRD/ZRD package36T stg Storage temperature range–65150°C (1)Stresses beyond those listed under "absolute maximum ratings"may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.(3)This current flows only when the output is in the high state and V O >V CC .(4)The package thermal impedance is calculated in accordance with JESD 51-7.SN54LVTH16373SN74LVTH16373UNIT MINMAX MIN MAX V CC Supply voltage 2.7 3.62.73.6V V IH High-level input voltage 22V V IL Low-level input voltage 0.80.8V V I Input voltage5.5 5.5V I OH High-level output current –24–32mA I OL Low-level output current 4864mA ∆t/∆v Input transition rise or fall rate Outpts enabled1010ns/V ∆t/∆V CC Power-up ramp rate200200µs/V T A Operating free-air temperature–55125–4085°C(1)All unused control inputs of the device must be held at V CC or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs ,literature number SCBA004.4Submit Documentation FeedbackElectrical CharacteristicsSN54LVTH16373,SN74LVTH16373 3.3-V ABT16-BIT TRANSPARENT D-TYPE LATCHESWITH3-STATE OUTPUTSSCBS144P–MAY1992–REVISED NOVEMBER2006over recommended operating free-air temperature range(unless otherwise noted)SN54LVTH16373SN74LVTH16373 PARAMETER TEST CONDITIONS UNITMIN TYP(1)MAX MIN TYP(1)MAXV IK V CC=2.7V,I I=–18mA–1.2–1.2V V CC=2.7V to3.6V,I OH=–100µA V CC–0.2V CC–0.2V CC=2.7V,I OH=–8mA 2.4 2.4V OH VI OH=–24mA2V CC=3VI OH=–32mA2I OL=100µA0.20.2V CC=2.7VI OL=24mA0.50.5I OL=16mA0.40.4V OL VI OL=32mA0.50.5V CC=3VI OL=48mA0.55I OL=64mA0.55V CC=0or3.6V,V I=5.5V1010ControlV CC=3.6V,V I=V CC or GND±1±1 inputsI IµAV I=V CC11 DataV CC=3.6Vinputs VI=0–5–5I off V CC=0,V I or V O=0to4.5V±100µAV I=0.8V7575V CC=3VDataI I(hold)V I=2V–75–75µAinputsV CC=3.6V,(2)V I=0to3.6V±500I OZH V CC=3.6V,V O=3V55µAI OZL V CC=3.6V,V O=0.5V–5–5µAV CC=0to1.5V,V O=0.5V to3V,I OZPU±100(3)±100µAOE=don't careV CC=1.5V to0,V O=0.5V to3V,I OZPD±100(3)±100µAOE=don't careOutputs high0.190.19 V CC=3.6V,I CC I O=0,Outputs low55mAV I=V CC or GND Outputs disabled0.190.19V CC=3V to3.6V,One input at V CC–0.6V,∆I CC(4)0.20.2mA Other inputs at V CC or GNDC i V I=3V or033pFC o V O=3V or099pF(1)All typical values are at V CC=3.3V,T A=25°C.(2)This is the bus-hold maximum dynamic current.It is the minimum overdrive current required to switch the input from one state toanother.(3)On products compliant to MIL-PRF-38535,this parameter is not production tested.(4)This is the increase in supply current for each input that is at the specified TTL voltage level,rather than V CC or GND.5Submit Documentation FeedbackTiming RequirementsSwitching CharacteristicsSN54LVTH16373,SN74LVTH163733.3-V ABT 16-BIT TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTSSCBS144P–MAY 1992–REVISED NOVEMBER 2006over recommended operating free-air temperature range (unless otherwise noted)(see Figure 1SN54LVTH16373SN74LVTH16373V CC =3.3V V CC =3.3V V CC =2.7V V CC =2.7V UNIT±0.3V ±0.3V MIN MAXMIN MAXMIN MAXMIN MAXt w Pulse duration,LE high 3333ns t su Setup time,data before LE ↓2210.6ns t hHold time,data after LE ↓33.311.1ns over recommended operating free-air temperature range,C L =50pF (unless otherwise noted)(see Figure 1)SN54LVTH16373SN74LVTH16373FROM TO V CC =3.3V V CC =3.3V PARAMETERV CC =2.7V V CC =2.7V UNIT(INPUT)(OUTPUT)±0.3V ±0.3V MIN MAXMINMAX MIN TYP (1)MAX MINMAX t PLH 1.4 4.5 5.2 1.5 2.7 3.8 4.2D Q ns t PHL 1.4 4.4 4.8 1.5 2.5 3.64t PLH 1.8 5.5 5.8 2.13 4.3 4.8LE Q ns t PHL 1.8 5.2 5.6 2.1 2.944t PZH 1.4 5.7 6.7 1.5 2.8 4.3 5.1OE Q ns t PZL 1.4 5.56 1.5 2.8 4.3 4.7t PHZ 26 6.2 2.4 3.55 5.4OEQns t PLZ 1.45.25.623.24.7 4.8t sk(LH)0.5ns t sk(HL)0.5(1)All typical values are at V CC =3.3V,T A =25°C.6Submit Documentation FeedbackPARAMETER MEASUREMENT INFORMATIONFrom Output Under TestC LLOAD CIRCUITOpen Data Input Timing Input2.7 V0 V2.7 V0 V2.7 V0 VInputVOLTAGE WAVEFORMS SETUP AND HOLD TIMESVOLTAGE WAVEFORMS PROPAGATION DELAY TIMESINVERTING AND NONINVERTING OUTPUTSVOLTAGE WAVEFORMSPULSE DURATIONV OHV OHV OLV OL2.7 V0 V InputOutput Control Output Waveform 1S1 at 6 V (see Note B)Output Waveform 2S1 at GND (see Note B)V OLV OH 3 V0 V≈0 V2.7 VVOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES LOW- AND HIGH-LEVEL ENABLINGOutputOutputt PLH /t PHL t PLZ /t PZL t PHZ /t PZHOpen 6 V GNDTEST S1NOTES: A.C L includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z O = 50 Ω, t r ≤ 2.5 ns, t f ≤ 2.5 ns.D.The outputs are measured one at a time, with one transition per measurement.SN54LVTH16373,SN74LVTH163733.3-V ABT 16-BIT TRANSPARENT D-TYPE LATCHESWITH 3-STATE OUTPUTSSCBS144P–MAY 1992–REVISED NOVEMBER 2006Figure 1.Load Circuit and Voltage Waveforms7Submit Documentation FeedbackPACKAGING INFORMATIONOrderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)5962-9681001QXA ACTIVE CFP WD481TBD Call TI Call TI74LVTH16373DGGRG4ACTIVE TSSOP DGG482000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM74LVTH16373DLRG4ACTIVE SSOP DL481000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LVTH16373DGGR ACTIVE TSSOP DGG482000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LVTH16373DL ACTIVE SSOP DL4825Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LVTH16373DLG4ACTIVE SSOP DL4825Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LVTH16373DLR ACTIVE SSOP DL481000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LVTH16373GQLR NRND BGAMICROSTARJUNIORGQL561000TBD SNPB Level-1-240C-UNLIMSN74LVTH16373GRDR ACTIVE BGAMICROSTARJUNIORGRD541000TBD SNPB Level-1-240C-UNLIMSN74LVTH16373ZQLR ACTIVE BGAMICROSTARJUNIOR ZQL561000Green (RoHS& no Sb/Br)SNAGCU Level-1-260C-UNLIMSN74LVTH16373ZRDR ACTIVE BGAMICROSTARJUNIOR ZRD541000Green (RoHS& no Sb/Br)SNAGCU Level-1-260C-UNLIMSNJ54LVTH16373WD ACTIVE CFP WD481TBD A42N / A for Pkg Type(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.Addendum-Page 1(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN54LVTH16373, SN74LVTH16373 :•Catalog: SN74LVTH16373•Enhanced Product: SN74LVTH16373-EP, SN74LVTH16373-EP•Military: SN54LVTH16373NOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product•Enhanced Product - Supports Defense, Aerospace and Medical Applications•Military - QML certified for Military and Defense ApplicationsAddendum-Page 2TAPE AND REELINFORMATION*All dimensionsare nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74LVTH16373DGGR TSSOP DGG 482000330.024.48.615.8 1.812.024.0Q1SN74LVTH16373DLR SSOP DL 481000330.032.411.3516.2 3.116.032.0Q1SN74LVTH16373GQLRBGA MI CROSTA R JUNI OR GQL561000330.016.44.87.31.458.016.0Q1SN74LVTH16373GRDR BGA MI CROSTA R JUNI OR GRD 541000330.016.4 5.88.3 1.558.016.0Q1SN74LVTH16373ZQLR BGA MI CROSTA R JUNI OR ZQL 561000330.016.4 4.87.3 1.458.016.0Q1SN74LVTH16373ZRDR BGA MI CROSTA R JUNI ORZRD 541000330.016.4 5.88.3 1.558.016.0Q1PACKAGE MATERIALS INFORMATION23-Jul-2011Pack Materials-Page 1*Alldimensions are nominal DevicePackage Type Package Drawing Pins SPQ Length (mm)Width (mm)Height (mm)SN74LVTH16373DGGRTSSOP DGG 482000346.0346.041.0SN74LVTH16373DLRSSOP DL 481000346.0346.049.0SN74LVTH16373GQLRBGA MICROSTAR JUNIOR GQL 561000333.2345.928.6SN74LVTH16373GRDRBGA MICROSTAR JUNIOR GRD 541000333.2345.928.6SN74LVTH16373ZQLRBGA MICROSTAR JUNIOR ZQL 561000333.2345.928.6SN74LVTH16373ZRDR BGA MICROSTARJUNIOR ZRD 541000333.2345.928.6PACKAGE MATERIALS INFORMATION 23-Jul-2011Pack Materials-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

74LVT16373MTD资料

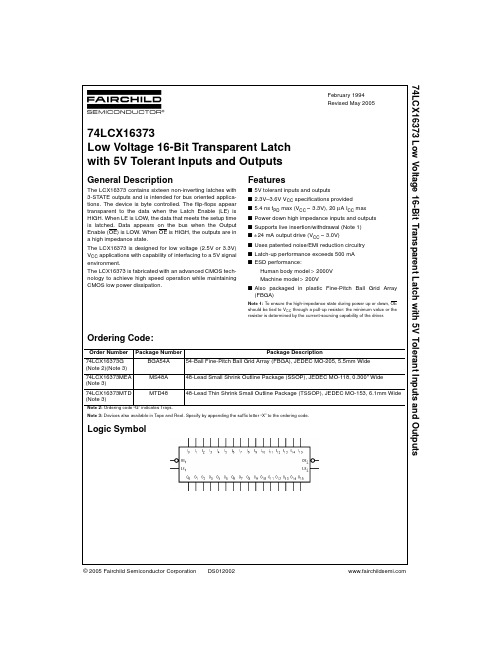

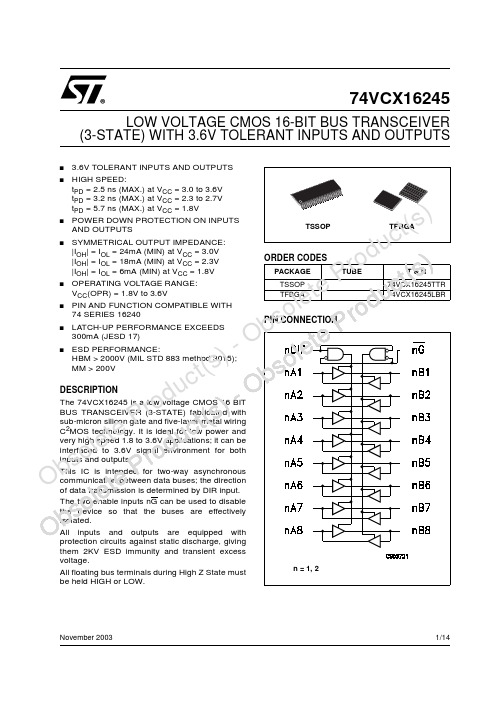

© 2005 Fairchild Semiconductor Corporation DS012021January 1999Revised June 200574LVT16373 • 74LVTH16373 Low Voltage 16-Bit Transparent Latch with 3-STATE Outputs74LVT16373 • 74LVTH16373Low Voltage 16-Bit Transparent Latch with 3-STATE OutputsGeneral DescriptionThe LVT16373 and LVTH16373 contain sixteen non-invert-ing latches with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled. The flip-flops appear transparent to the data when the Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in a high impedance state.The LVTH16373 data inputs include bushold, eliminating the need for external pull-up resistors to hold unused inputs.These latches are designed for low-voltage (3.3V) V CC applications, but with the capability to provide a TTL inter-face to a 5V environment. The LVT16373 and LVTH16373are fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.Featuress Input and output interface capability to systems at 5V V CC s Bushold data inputs eliminate the need for external pull-up resistors to hold unused inputs (74LVTH16373),also available without bushold feature (74LVT16373)s Live insertion/extraction permitteds Power Up/Power Down high impedance provides glitch-free bus loading s Outputs source/sink 32 mA/ 64 mAs Functionally compatible with the 74 series 16373s Latch-up performance exceeds 500 mA s ESD performance:Human-body model ! 2000V Machine model ! 200V Charged-device model ! 1000Vs Also packaged in plastic Fine-Pitch Ball Grid Array (FBGA) (Preliminary)Ordering Code:Note 1: BGA package available in Tape and Reel only.Note 2: Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic SymbolOrder Number Package Number Package Description74LVT16373GX (Note 1)BGA54A (Preliminary)54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL]74LVT16373MEA (Note 2)MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide 74LVT16373MTD (Note 2)MTD4848-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide 74LVTH16373GX (Note 1)BGA54A (Preliminary)54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL]74LVTH16373MEA (Note 2)MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide 74LVTH16373MTD (Note 2)MTD4848-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide 274L V T 16373 • 74L V T H 16373Connection DiagramsPin Assignment for SSOP and TSSOPPin Assignment for FBGA(Top Thru View)Pin DescriptionsFBGA Pin Assignments Truth TablesH HIGH Voltage LevelL LOW Voltage Level X ImmaterialZ HIGH ImpedanceO o Previous output prior to HIGH-to-LOW transition of LEPin Names DescriptionOE nOutput Enable Input (Active LOW)LE nLatch Enable Input I 0–I 15 Inputs O 0–O 15 3-STATE Outputs NC No Connect123456A O 0NC OE 1LE 1NC I 0BO 2O 1NCNC I 1I 2C O 4O 3V CC V CC I 3I 4D O 6O 5GND GND I 5I 6E O 8O 7GND GND I 7I 8F O 10O 9GND GND I 9I 10G O 12O 11V CC V CC I 11I 12H O 14O 13NC NC I 13I 14JO 15NCOE 2LE 2NCI 15InputsOutputs LE 1OE 1 I 0–I 7 O 0–O 7X H X ZH LL L H L H H LL XO o InputsOutputs LE 2OE 2 I 8–I 15 O 8–O 15X H XZ H L L L HL H H LLXO o74LVT16373 • 74LVTH16373Functional DescriptionThe LVT16373 and LVTH16373 contain sixteen D-typelatches with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but inde-pendent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LE n ) input is HIGH, data on the D n enters the latches. In this condition the latches are transparent, i.e, a latch output will change states each time its D input changes. When LE n is LOW,the latches store information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE n . The 3-STATE standard outputs are controlled by the Output Enable (OE n ) input. When OE n is LOW, the standard outputs are in the 2-state mode. When OE n is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.Logic DiagramsPlease note that these diagrams are provided only for the understanding of logic operations and should not be used to estimate propagation delays. 474L V T 16373 • 74L V T H 16373Absolute Maximum Ratings (Note 3)Recommended Operating ConditionsNote 3: Absolute Maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum rated conditions is not implied.Note 4: I O Absolute Maximum Rating must be observed.DC Electrical CharacteristicsSymbol ParameterValueConditionsUnits V CC Supply Voltage 0.5 to 4.6V V I DC Input Voltage 0.5 to 7.0VV O DC Output Voltage 0.5 to 7.0Output in 3-STATEV 0.5 to 7.0Output in HIGH or LOW State (Note 4)I IK DC Input Diode Current 50V I GND mA I OK DC Output Diode Current 50V O GND mA I O DC Output Current64V O ! V CC Output at HIGH State mA 128V O ! V CCOutput at LOW StateI CC DC Supply Current per Supply Pin r 64mA I GND DC Ground Current per Ground Pin r 128mAT STGStorage Temperature65 to 150q CSymbol ParameterMin Max Units V CC Supply Voltage 2.7 3.6V V I Input Voltage5.5V I OH HIGH Level Output Current 32mA I OL LOW Level Output Current 64mAT AFree-Air Operating Temperature4085q C 't/'VInput Edge Rate, V IN 0.8V –2.0V, V CC 3.0V10ns/VSymbol ParameterV CC T A 40q C to 85q C Units Conditions(V)MinMax V IK Input Clamp Diode Voltage 2.7 1.2V I I 18 mA V IH Input HIGH Voltage 2.7–3.6 2.0V V O d 0.1V or V IL Input LOW Voltage 2.7–3.60.8VV O t V CC 0.1V V OHOutput HIGH Voltage2.7–3.6V CC 0.2VI OH 100 P A 2.7 2.4I OH 8 mA 3.02.0I OH 32 mA V OLOutput LOW Voltage2.70.2V I OL 100 P A 2.70.5I OL 24 mA3.00.4I OL 16 mA 3.00.5I OL 32 mA 3.00.55I OL 64 mA I I(HOLD)Bushold Input Minimum Drive3.075P A V I 0.8V (Note 5) 75V I 2.0V I I(OD)Bushold Input Over-Drive 3.0500P A (Note 6)(Note 5)Current to Change State 500(Note 7)I IInput Current3.610P AV I 5.5V Control Pins 3.6r 1V I 0V or V CC Data Pins3.6 5V I 0V 1V I V CCI OFF Power Off Leakage Current 0r 100P A 0V d V I or V O d 5.5V I PU/PD Power Up/Down 3-STATE 0–1.5V r 100P A V O 0.5V to 3.0V Output CurrentV I GND or V CC I OZL 3-STATE Output Leakage Current 3.6 5P A V O 0.5V I OZH 3-STATE Output Leakage Current 3.65P A V O 3.0V I OZH3-STATE Output Leakage Current 3.610P A V CC V O d 5.5V74LVT16373 • 74LVTH16373DC Electrical Characteristics (Continued)Note 5: Applies to bushold versions only (74LVTH16373).Note 6: An external driver must source at least the specified current to switch from LOW-to-HIGH.Note 7: An external driver must sink at least the specified current to switch from HIGH-to-LOW.Note 8: This is the increase in supply current for each input that is at the specified voltage level rather than V CC or GND.Dynamic Switching Characteristics (Note 9)Note 9: Characterized in SSOP package. Guaranteed parameter, but not tested.Note 10: Max number of outputs defined as (n). n 1 data inputs are driven 0V to 3V. Output under test held LOW.AC Electrical CharacteristicsNote 11: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ).Capacitance (Note 12)Note 12: Capacitance is measured at frequency f 1 MHz, per MIL-STD-883, Method 3012.Symbol ParameterV CC T A 40q C to 85q C Units Conditions(V)MinMax I CCH Power Supply Current 3.60.19mA Outputs HIGH I CCL Power Supply Current 3.65mA Outputs LOW I CCZ Power Supply Current 3.60.19mA Outputs Disabled I CCZ Power Supply Current3.60.19mA V CC d V O d 5.5V,Outputs Disabled 'I CCIncrease in Power Supply Current 3.60.2mAOne Input at V CC 0.6V (Note 8)Other Inputs at V CC or GNDSymbol ParameterV CC T A 25q C Units Conditions (V)MinTyp MaxC L 50 pF, R L 500:V OLP Quiet Output Maximum Dynamic V OL 3.30.8V (Note 10)V OLVQuiet Output Minimum Dynamic V OL3.30.8V(Note 10)Symbol ParameterT A 40q C to 85q C, C L 50pF, R L 500:UnitsV CC 3.3V r 0.3V V CC 2.7VMin Max Min Max t PHL Propagation Delay 1.5 3.9 1.5 4.3ns t PLH D n to O n1.5 3.8 1.5 4.2t PHL Propagation Delay 1.9 4.2 1.9 4.4ns t PLH LE to O n1.6 4.3 1.6 4.8t PZL Output Enable Time1.3 4.3 1.3 4.9ns t PZH 1.0 4.3 1.0 5.1t PLZ Output Disable Time1.5 4.7 1.5 4.8ns t PHZ2.0 5.02.0 5.4t S Setup Time, D n to LE 1.00.8ns t H Hold Time, D n to LE 1.0 1.1ns t W LE Pulse Width3.03.0ns t OSHL Output to Output Skew (Note 11) 1.0 1.0ns t OSLH1.0 1.0Symbol ParameterConditionsTypical Units C IN Input Capacitance V CC Open, V I 0V or V CC 4pF C OUTOutput CapacitanceV CC 3.0V, V O 0V or V CC8pF 674L V T 16373 • 74L V T H 16373Physical Dimensionsinches (millimeters) unless otherwise noted54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm WidePackage Number BGA54APreliminary74LVT16373 • 74LVTH16373Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" WidePackage Number MS48A874L V T 16373 • 74L V T H 16373 L o w V o l t a g e 16-B i t T r a n s p a r e n t L a t c h w i t h 3-S T A T E O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm WidePackage Number MTD48Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74HCT377中文资料

Fig.4 Functional diagram.

December 1990

Fig.5 Logic diagram. 4

元器件交易网

Philips Semiconductors

Octal D-type flip-flop with data enable; positive-edge trigger

NAME AND FUNCTION data enable input (active LOW) flip-flop outputs data inputs ground (0 V) clock input (LOW-to-HIGH, edge-triggered) positive supply voltage

Product specification

74HC/HCT377

FUNCTION TABLE

OPERATING MODES

load “1” load “0” hold (do nothing)

INPUTS

CP E Dn

↑

l

h

↑

l

l

↑hX XHX

OUTPUTS

Qn H L no change no change

90

15

18

13

15

ns 2.0 Fig.7 4.5 6.0

3 −8

3

3

3 −3

3

3

3 −2

3

3

4 −3

4

4

4 −1

4

4

4 −14ຫໍສະໝຸດ 46 235

4

30 70

24

20

35 83

28

24

ns 2.0 Fig.7 4.5 6.0

(完整word版)74HC573功能说明(原创编辑)0001

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制 74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低 电压激活:1是低电压激活芯片2~9脚是数据的输入脚从 DO 到D710脚是接地11脚是高电压激活芯片12~19脚是数据的输出脚20是电源SNS4HCS7 3A . . FK PACKAGE(TOP VIEW)1•真值表3 2 1 20 19 厂ZUIH E苛[ 171stOE1D益3D 4D5Dec0D GKD]^ec ]1Q]%]4a ]5Q ]7Q 1 5Q ■ ■ILEOurPLFT ENABLE乂>EXPAMJtD I 1MAC ;K\M3C4D 5 口 6D7D/ t_n_IT _re_r~ir~LT~u~~m2Q 3Q4Q50fid亡I □ Ld □口 B N —l 在 g功能範高阻抗74HC573真值表,意思如下:第一行/第二行:当0E = 0、LE = 1时,输出端数据等于输入端数据;第三行:当0E = 0、LE = 0时,输出端保持不变;第四行:当0E = 1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573 都具备数据缓冲的能力。

0E : output_enable,输出使能;LE : latch_enable,数据锁存使能,atch是锁存的意思;Dn :第n路输入数据;On :第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:OE = 0;先将数据从单片机的口线上输出到 出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘 片机的资源有限啊。

74LVC16373ADGG,118,74LVC16373ADGG,518,74LVC16373ADGG,118,74LVC16373ADGG,118,规格书,Datasheet 资料

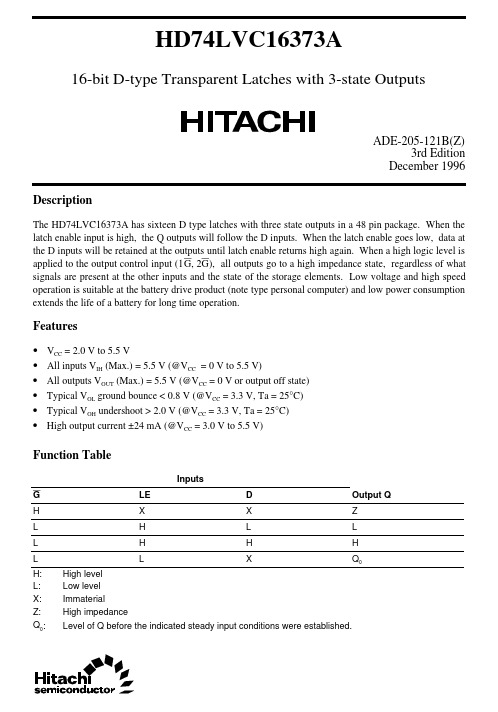

74LVC16373A; 74LVCH16373A

DESCRIPTION data input data input latch enable input (active HIGH)

4, 10, 15, 21, 28, ground (0 V) 34, 39, 45 5 6 7, 18, 31, 42 8 9 11 12 13 14 16 17 19 20 22 23 24 25 26 27 29 30 32 33 35 36 37 38 40 41 43 44 data output data output supply voltage data output data output data output data output data output data output data output data output data output data output data output data output output enable input (active LOW) latch enable input (active HIGH) data input data input data input data input data input data input data input data input data input data input data input data input data input data input Fig.1 Pin configuration SSOP48 and TSSOP48.

2003 Dec 08

2

芯天下--/

Philips Semiconductors

Product specification

16-bit D-type transparent latch with 5 V tolerant inputs/outputs; 3-state

74LCX16373A中文资料

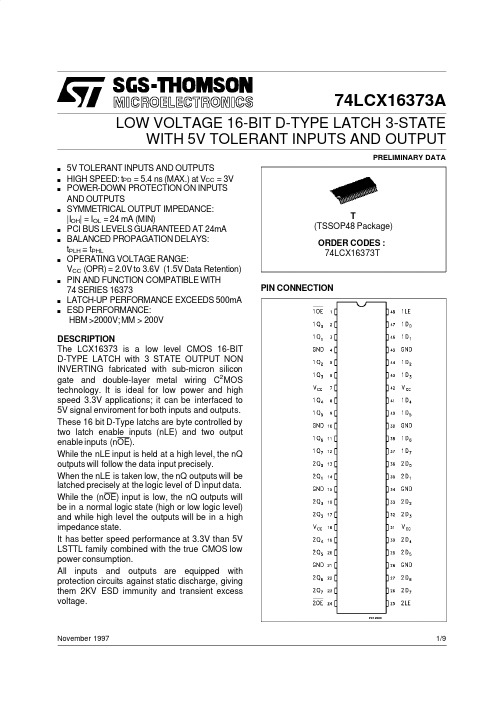

74LCX16373A LOW VOLTAGE16-BIT D-TYPE LATCH3-STATEWITH5V TOLERANT INPUTS AND OUTPUTPRELIMINARY DATANovember1997ORDER CODES: 74LCX16373Ts5V TOLERANT INPUTS AND OUTPUTSs HIGH SPEED:t PD=5.4ns(MAX.)at V CC=3V s POWER-DOWN PROTECTION ON INPUTS AND OUTPUTSs SYMMETRICAL OUTPUT IMPEDANCE: |I OH|=I OL=24mA(MIN)s PCI BUS LEVELS GUARANTEED AT24mAs BALANCED PROPAGATION DELAYS: t PLH≅t PHLs OPERATING VOLTAGE RANGE:V CC(OPR)=2.0V to3.6V(1.5V Data Retention)s PIN AND FUNCTION COMPATIBLE WITH 74SERIES16373s LATCH-UP PERFORMANCE EXCEEDS500mA s ESD PERFORMANCE:HBM>2000V;MM>200VDESCRIPTIONThe LCX16373is a low level CMOS16-BIT D-TYPE LATCH with3STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology.It is ideal for low power and high speed3.3V applications;it can be interfaced to 5V signal enviroment for both inputs and outputs. These16bit D-Type latchs are byte controlled by two latch enable inputs(nLE)and two output enable inputs(nOE).While the nLE input is held at a high level,the nQ outputs will follow the data input precisely.When the nLE is taken low,the nQ outputs will be latched precisely at the logic level of D input data. While the(nOE)input is low,the nQ outputs will be in a normal logic state(high or low logic level) and while high level the outputs will be in a high impedance state.It has better speed performance at3.3V than5V LSTTL family combined with the true CMOS low power consumption.All inputs and outputs are equipped with protection circuits against static discharge,giving them2KV ESD immunity and transient excess voltage.T(TSSOP48Package)PIN CONNECTION1/974LCX16373AINPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONIEC LOGIC SYMBOLS PIN No SYMBOL NAME AND FUNCTION11OE3State Output EnableInput(Active LOW)2,3,5,6,1Q0to1Q7Data Inputs8,9,11,122Q0to2Q7Data Inputs13,14,16,17,19,20,22,23242OE3State Output EnableInput(Active LOW)252LE Latch Enable Input2D0to2D73State Outputs36,35,33,32,30,29,27,261D0to1D73State Outputs47,46,44,43,41,40,38,37481LE Latch Enable InputGND Ground(0V)4,10,15,21,28,34,39,457,18,31,42V CC Positive Supply VoltageTRUTH TABLEINPUTS OUTPUTSOE LE D QH X X ZL L X NO CHANGE*L H L LL H H HX:Don’t careZ:High imp edance*Q output are latched at the timewhen the LE inputs taken low logic2/974LCX16373A LOGIC DIAGRAMABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7.0V V I DC Input Voltage-0.5to+7.0V V O DC Output Voltage(OFF state)-0.5to+7.0V V O DC Output Voltage(High or Low State)(note1)-0.5to V CC+0.5VI IK DC Input Diode Current-50mAI OK DC Output Diode Current(note2)±50mAI O DC Output Source/Sink Current±50mAI CC or I GND DC V CC or Ground Current Per Supply Pin±100mAT stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these condition is not implied.1)I O absolute maximum rating must be observed2)V O<GND,V O>V CCRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage(note1) 2.0to3.6V V I Input Voltage0to5.5V V O Output Voltage(OFF state)0to5.5V V O Output Voltage(High or Low State)0to V CC VI OH,I OL High or Low Level Output Current(V CC= 3.0to3.6V)±24mAI OH,I OL High or Low Level Output Current(V CC= 2.7to3.0V)±12mAT op Operating Temperature:-40to+85o C dt/dv Input Transition Rise or Fall Rate(V CC=3.0V)(note2)0to10ns/V1)Truth Table guaranteed:1.5V to3.6V2)V IN from0.8V to2.0V3/9DC SPECIFICATIONSSymbol Parameter Test Conditions Value UnitV CC (V)-40to85o C Min.Max.V IH High Level Input Voltage2.7to3.62.0VV IL Low Level Input Voltage0.8VV OH High Level Output Voltage 2.7to3.6V I=V IHor V IL I O=-100µA V CC-0.2V2.7I O=-12mA 2.23.0I O=-18mA 2.4 I O=-24mA 2.2V OL Low Level Output Voltage 2.7to3.6V I=V IHor V IL I O=100µA0.2V2.7I O=12mA0.43.0I O=16mA0.43.0I O=24mA0.55I I Input Leakage Current 2.7to3.6V I=0to5.5V±5µAI OZ3State Output Leakage Current 2.7to3.6V I=V IH or V ILV O=0to5.5V±5µAI off Power Off Leakage Current0V I or V O=5.5V(per pin)10µAI CC Quiescent Supply Current 2.7to3.6V I=V CC or GND20µAV I or V O=3.6to5.5V±20∆I CC ICC incr.per input 2.7to3.6V IH=V CC-0.6V500µA DYNAMIC SWITCHING CHARACTERISTICSSymbol Parameter Test Conditions Value UnitV CC (V)T A=25o C Min.Typ.Max.V OLP Dynamic Low Voltage Quiet Output (note1)3.3C L=50pFV IL=0VV IH=3.3V0.8VV OLV-0.81)Number of outputs defined as”n”.Me asured with”n-1”outputs switching from HIGH to LOW or LOW to HIGH.The remaining output is measured in the LOW state.74LCX16373A4/9CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValue UnitV CC (V)T A =25oCMin.Typ.Max.C IN Input Capacitance 3.3V IN =0to V CC 7pF C OU T Output Capacitance3.3V IN =0to V CC 8pF C PDPower Dissipation Capacitance (note 1)3.3f IN =10MHz V IN =0or V CC20pF1)C PD isdefined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.Average operting current can be obtained by the following equation.I CC (opr)=C PD •V CC •f IN +I CC /n (per circuit)AC ELECTRICAL CHARACTERISTICS (C L =50pF,R L =500Ω,Input t r =t f =2.5ns)SymbolParameterTest ConditionValue UnitV CC (V)Waveform-40to 85oC Min.Max.t PLH t PHL Propagation Delay Time Dn to Qn 2.71 1.58.0ns 3.0to 3.6 1.57.0t PLH t PHL Propagation Delay Time LE to Qn 2.71 1.58.0ns 3.0to 3.6 1.57.0t PZL t PZH Output Enable Time to HIGH and LOW level2.72 1.58.2ns3.0to 3.6 1.57.2t PLZ t PHZ Output Disable Time from HIGh and LOW level2.72 1.58.2ns3.0to 3.6 1.57.2t s Setup Time,HIGh or LOW level Dn to LE2.71 2.5ns3.0to 3.6 2.5t h Hold Time,HIGh or LOW level Dn to LE 2.71 1.5ns 3.0to 3.6 1.5t w LE Pulse Width,HIGH or LOW2.734.0ns 3.0to 3.6 3.0t OSLZ t OS HLOutput to Output Skew Time (note 1,2)3.0to 3.61.0ns1)Skew is defined as the absolute value of the difference between the ac tual propagation delay for any two outputs of the same device switching in the same direction,either HIGH or LOW (t OSLH =|t PLHm -t PLHn |,t OSHL =|t PHL m -t pHLn |)2)Parameter guaranteed by design74LCX16373A5/974LCX16373ATEST CIRCUITTEST SWITCH t PLH,t PHL Open t PZL,t PLZ6Vt PZH,t PHZ GND C L=50pF or equivalent(includes jig and probe capacitance)R L=R1=500Ωor equiva lentR T=Z OUT of pulse generator(typically50Ω)WAVEFORM1:LE TO Qn PROPAGATION DELAYS,LE MINIMUM PULSE WIDTH,Dn TO LE SETUP AND HOLD TIMES(f=1MHz;50%duty cycle)6/974LCX16373A WAVEFORM2:OUTPUT ENABLE AND DISABLE TIMES(f=1MHz;50%duty cycle)WAVEFORM3:PROPAGATION DELAY TIME(f=1MHz;50%duty cycle)7/9DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 1.10.433A10.050.100.150.0020.0040.006A20.850.90.950.3350.3540.374b 0.170.270.00670.011c 0.090.200.00350.0079D 12.412.512.60.4080.4920.496E 7.958.18.250.3130.3190.325E1 6.06.1 6.20.2360.2400.244e 0.5BSC 0.0197BSCK 0o 4o 8o 0o 4o 8o L0.500.600.700.0200.0240.028cEbA2AE1D1PIN 1IDENTIFICATIONA1LK eTSSOP48MECHANICAL DATA74LCX16373A8/974LCX16373A Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsabilit y for the consequences of use of such information nor for any infringemen t of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectr onics.Specifications mention ed in this publication are subject to change without notice.This publication supersede s and replaces all information previously supplied.SGS-THOMSON Microelectr onics products are not auth orized for use as critical compon ents in life support devices or systems without expre ss written approval of SGS-THOMSON Microelectonics.©1997SGS-THOMSON Microelectronics-Printed in Italy-All Rights Reserve dSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A...9/9。

0_74系列芯片功能略表

74系列芯片功能略表技术2008-12-17 10:47:39 阅读422 评论0 字号:大中小引自廖世迁的blog电子元件知识-74系列芯片功能略表74HC01 2输入四与非门(oc)74HC02 2输入四或非门74HC03 2输入四与非门(oc)74HC04 六倒相器74HC05 六倒相器(oc)74HC06 六高压输出反相缓冲器/驱动器(oc,30v)74HC07 六高压输出缓冲器/驱动器(oc,30v)74HC08 2输入四与门74HC09 2输入四与门(oc)74HC10 3输入三与非门74HC11 3输入三与门74HC12 3输入三与非门(oc)74HC13 4输入双与非门(斯密特触发)74HC14 六倒相器(斯密特触发)74HC15 3输入三与门(oc)74HC16 六高压输出反相缓冲器/驱动器(oc,15v)74HC17 六高压输出缓冲器/驱动器(oc,15v)74HC18 4输入双与非门(斯密特触发)74HC19 六倒相器(斯密特触发)74HC20 4输入双与非门74HC21 4输入双与门74HC22 4输入双与非门(oc)74HC23 双可扩展的输入或非门74HC24 2输入四与非门(斯密特触发)74HC25 4输入双或非门(有选通)74HC26 2输入四高电平接口与非缓冲器(oc,15v)74HC27 3输入三或非门74HC28 2输入四或非缓冲器74HC30 8输入与非门74HC31 延迟电路74HC32 2输入四或门74HC33 2输入四或非缓冲器(集电极开路输出)74HC34 六缓冲器74HC35 六缓冲器(oc)74HC36 2输入四或非门(有选通)74HC37 2输入四与非缓冲器74HC38 2输入四或非缓冲器(集电极开路输出)74HC39 2输入四或非缓冲器(集电极开路输出)74HC40 4输入双与非缓冲器74HC41 bcd-十进制计数器74HC42 4线-10线译码器(bcd输入)74HC43 4线-10线译码器(余3码输入)74HC44 4线-10线译码器(余3葛莱码输入)74HC45 bcd-十进制译码器/驱动器74HC46 bcd-七段译码器/驱动器74HC47 bcd-七段译码器/驱动器74HC48 bcd-七段译码器/驱动器74HC49 bcd-七段译码器/驱动器(oc)74HC50 双二路2-2输入与或非门(一门可扩展)74HC51 双二路2-2输入与或非门74HC51 二路3-3输入,二路2-2输入与或非门74HC52 四路2-3-2-2输入与或门(可扩展)74HC53 四路2-2-2-2输入与或非门(可扩展)74HC53 四路2-2-3-2输入与或非门(可扩展)74HC54 四路2-2-2-2输入与或非门74HC54 四路2-3-3-2输入与或非门74HC54 四路2-2-3-2输入与或非门74HC55 二路4-4输入与或非门(可扩展)74HC60 双四输入与扩展74HC61 三3输入与扩展74HC62 四路2-3-3-2输入与或扩展器74HC63 六电流读出接口门74HC64 四路4-2-3-2输入与或非门74HC65 四路4-2-3-2输入与或非门(oc)74HC70 与门输入上升沿jk触发器74HC71 与输入r-s主从触发器74HC72 与门输入主从jk触发器74HC73 双j-k触发器(带清除端)74HC74 正沿触发双d型触发器(带预置端和清除端)74HC75 4位双稳锁存器74HC76 双j-k触发器(带预置端和清除端)74HC77 4位双稳态锁存器74HC78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74HC80 门控全加器74HC81 16位随机存取存储器74HC82 2位二进制全加器(快速进位)74HC83 4位二进制全加器(快速进位)74HC84 16位随机存取存储器74HC85 4位数字比较器74HC86 2输入四异或门74HC87 四位二进制原码/反码/oi单元74HC89 64位读/写存储器74HC90 十进制计数器74HC91 八位移位寄存器74HC92 12分频计数器(2分频和6分频)74HC93 4位二进制计数器74HC94 4位移位寄存器(异步)74HC95 4位移位寄存器(并行io)74HC96 5位移位寄存器74HC97 六位同步二进制比率乘法器74HC100 八位双稳锁存器74HC103 负沿触发双j-k主从触发器(带清除端)74HC106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74HC107 双j-k主从触发器(带清除端)74HC108 双j-k主从触发器(带预置,清除,时钟)74HC109 双j-k触发器(带置位,清除,正触发)74HC110 与门输入j-k主从触发器(带锁定)74HC111 双j-k主从触发器(带数据锁定)74HC112 负沿触发双j-k触发器(带预置端和清除端)74HC113 负沿触发双j-k触发器(带预置端)74HC114 双j-k触发器(带预置端,共清除端和时钟端) 74HC116 双四位锁存器74HC120 双脉冲同步器/驱动器74HC121 单稳态触发器(施密特触发)74HC122 可再触发单稳态多谐振荡器(带清除端)74HC123 可再触发双单稳多谐振荡器74HC125 四总线缓冲门(三态输出)74HC126 四总线缓冲门(三态输出)74HC128 2输入四或非线驱动器74HC131 3-8译码器74HC132 2输入四与非门(斯密特触发)74HC133 13输入端与非门74HC134 12输入端与门(三态输出)74HC135 四异或/异或非门74HC136 2输入四异或门(oc)74HC137 八选1锁存译码器/多路转换器74HC138 3-8线译码器/多路转换器74HC139 双2-4线译码器/多路转换器74HC140 双4输入与非线驱动器74HC141 bcd-十进制译码器/驱动器74HC142 计数器/锁存器/译码器/驱动器74HC145 4-10译码器/驱动器74HC147 10线-4线优先编码器74HC148 8线-3线八进制优先编码器74HC150 16选1数据选择器(反补输出)74HC151 8选1数据选择器(互补输出)74HC152 8选1数据选择器多路开关74HC153 双4选1数据选择器/多路选择器74HC154 4线-16线译码器74HC155 双2-4译码器/分配器(图腾柱输出)74HC156 双2-4译码器/分配器(集电极开路输出)74HC157 四2选1数据选择器/多路选择器74HC158 四2选1数据选择器(反相输出)74HC160 可预置bcd计数器(异步清除)74HC161 可预置四位二进制计数器(并清除异步)74HC162 可预置bcd计数器(异步清除)74HC163 可预置四位二进制计数器(并清除异步)74HC164 8位并行输出串行移位寄存器74HC165 并行输入8位移位寄存器(补码输出)74HC166 8位移位寄存器74HC167 同步十进制比率乘法器74HC168 4位加/减同步计数器(十进制)74HC169 同步二进制可逆计数器74HC170 4*4寄存器堆74HC171 四d触发器(带清除端)74HC172 16位寄存器堆74HC173 4位d型寄存器(带清除端)74HC174 六d触发器74HC175 四d触发器74HC176 十进制可预置计数器74HC177 2-8-16进制可预置计数器74HC178 四位通用移位寄存器74HC179 四位通用移位寄存器74HC180 九位奇偶产生/校验器74HC181 算术逻辑单元/功能发生器74HC182 先行进位发生器74HC183 双保留进位全加器74HC184 bcd-二进制转换器74HC185 二进制-bcd转换器74HC190 同步可逆计数器(bcd,二进制)74HC191 同步可逆计数器(bcd,二进制)74HC192 同步可逆计数器(bcd,二进制)74HC193 同步可逆计数器(bcd,二进制)74HC199 八位移位寄存器74HC210 2-5-10进制计数器74HC213 2-n-10可变进制计数器74HC221 双单稳触发器74HC230 八3态总线驱动器74HC231 八3态总线反向驱动器74HC240 八缓冲器/线驱动器/线接收器(反码三态输出) 74HC241 八缓冲器/线驱动器/线接收器(原码三态输出) 74HC242 八缓冲器/线驱动器/线接收器74HC243 4同相三态总线收发器74HC244 八缓冲器/线驱动器/线接收器74HC245 八双向总线收发器74HC246 4线-七段译码/驱动器(30v)74HC247 4线-七段译码/驱动器(15v)74HC248 4线-七段译码/驱动器74HC249 4线-七段译码/驱动器74HC251 8选1数据选择器(三态输出)74HC253 双四选1数据选择器(三态输出)74HC256 双四位可寻址锁存器74HC257 四2选1数据选择器(三态输出)74HC258 四2选1数据选择器(反码三态输出)74HC259 8为可寻址锁存器74HC260 双5输入或非门74HC261 4*2并行二进制乘法器74HC265 四互补输出元件74HC266 2输入四异或非门(oc)74HC270 2048位rom (512位四字节,oc)74HC271 2048位rom (256位八字节,oc)74HC273 八d触发器74HC274 4*4并行二进制乘法器74HC275 七位片式华莱士树乘法器74HC276 四jk触发器74HC278 四位可级联优先寄存器74HC279 四s-r锁存器74HC280 9位奇数/偶数奇偶发生器/较验器74HC28174HC283 4位二进制全加器74HC290 十进制计数器74HC291 32位可编程模74HC293 4位二进制计数器74HC294 16位可编程模74HC295 四位双向通用移位寄存器74HC298 四-2输入多路转换器(带选通)74HC299 八位通用移位寄存器(三态输出)74HC348 8-3线优先编码器(三态输出)74HC352 双四选1数据选择器/多路转换器74HC353 双4-1线数据选择器(三态输出)74HC354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC365 6总线驱动器74HC366 六反向三态缓冲器/线驱动器74HC367 六同向三态缓冲器/线驱动器74HC368 六反向三态缓冲器/线驱动器74HC373 八d锁存器74HC374 八d触发器(三态同相)74HC375 4位双稳态锁存器74HC377 带使能的八d触发器74HC378 六d触发器74HC379 四d触发器74HC381 算术逻辑单元/函数发生器74HC382 算术逻辑单元/函数发生器74HC384 8位*1位补码乘法器74HC385 四串行加法器/乘法器74HC386 2输入四异或门74HC390 双十进制计数器74HC391 双四位二进制计数器74HC395 4位通用移位寄存器74HC396 八位存储寄存器74HC398 四2输入端多路开关(双路输出)74HC399 四-2输入多路转换器(带选通)74HC422 单稳态触发器74HC423 双单稳态触发器74HC440 四3方向总线收发器,集电极开路74HC441 四3方向总线收发器,集电极开路74HC442 四3方向总线收发器,三态输出74HC443 四3方向总线收发器,三态输出74HC444 四3方向总线收发器,三态输出74HC445 bcd-十进制译码器/驱动器,三态输出74HC446 有方向控制的双总线收发器74HC448 四3方向总线收发器,三态输出74HC449 有方向控制的双总线收发器74HC465 八三态线缓冲器74HC466 八三态线反向缓冲器74HC467 八三态线缓冲器74HC468 八三态线反向缓冲器74HC490 双十进制计数器74HC540 八位三态总线缓冲器(反向)74HC541 八位三态总线缓冲器74HC589 有输入锁存的并入串出移位寄存器74HC590 带输出寄存器的8位二进制计数器74HC591 带输出寄存器的8位二进制计数器74HC592 带输出寄存器的8位二进制计数器74HC593 带输出寄存器的8位二进制计数器74HC594 带输出锁存的8位串入并出移位寄存器74HC595 8位输出锁存移位寄存器74HC596 带输出锁存的8位串入并出移位寄存器74HC597 8位输出锁存移位寄存器74HC598 带输入锁存的并入串出移位寄存器74HC599 带输出锁存的8位串入并出移位寄存器74HC604 双8位锁存器74HC605 双8位锁存器74HC606 双8位锁存器74HC607 双8位锁存器74HC620 8位三态总线发送接收器(反相)74HC621 8位总线收发器74HC622 8位总线收发器74HC623 8位总线收发器74HC640 反相总线收发器(三态输出)74HC641 同相8总线收发器,集电极开路74HC642 同相8总线收发器,集电极开路74HC643 8位三态总线发送接收器74HC644 真值反相8总线收发器,集电极开路74HC645 三态同相8总线收发器74HC646 八位总线收发器,寄存器74HC647 八位总线收发器,寄存器74HC648 八位总线收发器,寄存器74HC649 八位总线收发器,寄存器74HC651 三态反相8总线收发器74HC652 三态反相8总线收发器74HC653 反相8总线收发器,集电极开路74HC654 同相8总线收发器,集电极开路74HC668 4位同步加/减十进制计数器74HC669 带先行进位的4位同步二进制可逆计数器74HC670 4*4寄存器堆(三态)74HC671 带输出寄存的四位并入并出移位寄存器74HC672 带输出寄存的四位并入并出移位寄存器74HC673 16位并行输出存储器,16位串入串出移位寄存器74HC674 16位并行输入串行输出移位寄存器74HC681 4位并行二进制累加器74HC682 8位数值比较器(图腾柱输出)74HC683 8位数值比较器(集电极开路)74HC684 8位数值比较器(图腾柱输出)74HC685 8位数值比较器(集电极开路)74HC686 8位数值比较器(图腾柱输出)74HC687 8位数值比较器(集电极开路)74HC688 8位数字比较器(oc输出)74HC689 8位数字比较器74HC690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)。

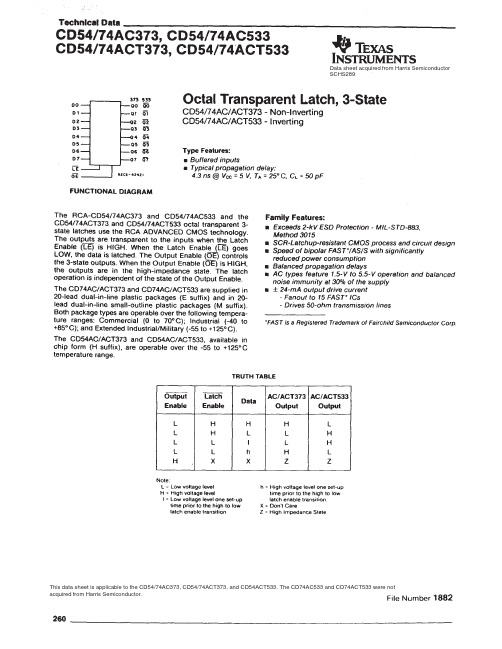

CD74ACT373中文资料

Data sheet acquired from Harris SemiconductorSCHS289This data sheet is applicable to the CD54/74AC373, CD54/74ACT373, and CD54ACT533. The CD74AC533 and CD74ACT533 were notacquired from Harris Semiconductor.IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

MC74LCX16373中文资料

nLE

Inputs LE1 X H H L OE1 H L L L D0:7 X L H X

Outputs O0:7 Z L H O0 LE2 X H H L

Inputs OE2 H L L L D8:15 X L H X

Outputs O8:15 Z L H O0

H = High Voltage Level; L = Low Voltage Level; Z = High Impedance State; X = High or Low Voltage Level and Transitions Are Acceptable, for ICC reasons, DO NOT FLOAT Inputsபைடு நூலகம்

MOTOROLA

2

LCX DATA BR1339 — REV 3

元器件交易网

MC74LCX16373

ABSOLUTE MAXIMUM RATINGS*

Symbol VCC VI VO Parameter DC Supply Voltage DC Input Voltage DC Output Voltage Value –0.5 to +7.0 –0.5 ≤ VI ≤ +7.0 –0.5 ≤ VO ≤ +7.0 –0.5 ≤ VO ≤ VCC + 0.5 IIK IOK DC Input Diode Current DC Output Diode Current –50 –50 +50 IO ICC IGND TSTG DC Output Source/Sink Current DC Supply Current Per Supply Pin DC Ground Current Per Ground Pin Storage Temperature Range ±50 ±100 ±100 –65 to +150 Output in 3–State Note 1. VI < GND VO < GND VO > VCC Condition Unit V V V V mA mA mA mA mA mA °C

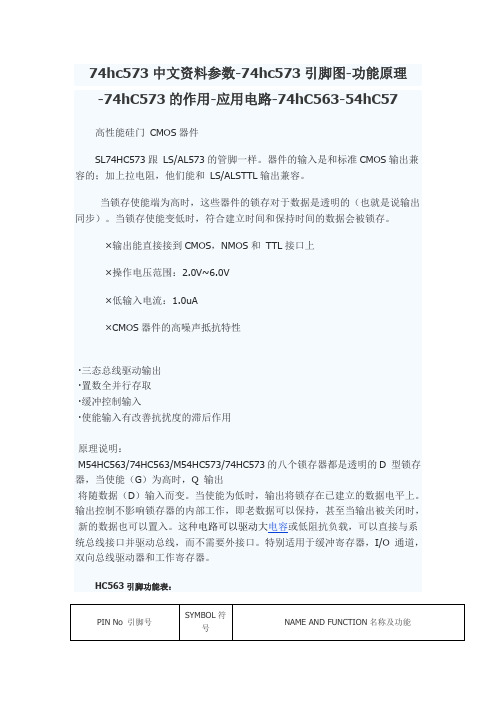

74hc573完整中文资料

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO=6.0mA-0.170.260.330.406.0IO=7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI =VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

SN74LVC3G07中文资料

_ _ _CV_

NanoFree™ – WCSP (DSBGA) 0.23-mm Large Bump – YZP (Pb-free)

SN74LVC3G07YZPR

SSOP – DCT

Reel of 3000 SN74LVC3G07DCTR

C07_ _ _

VSSOP – DCU

Reel of 3000 Reel of 250

DESCRIPTION/ORDERING INFORMATION (CONTINUED)

The output of the SN74LVC3G07 is open drain and can be connected to other open-drain outputs to implement active-low wired-OR or active-high wired-AND functions. The maximum sink current is 32 mA.

NanoFree™ – WCSP (DSBGA) 0.17-mm Small Bump – YZA (Pb-free)

NanoStar™ – WCSP (DSBGA) 0.23-mm Large Bump – YEP

Reel of 3000

SN74LVC3G07YZAR SN74LVC3G07YEPR

TA –40°C to 85°C

ORDERING INFORMATION

PACKAGE (1)

ORDERABLE PART NUMBER TOP-SIDE MARKING(2)

NanoStar™ – WCSP (DSBGA) 0.17-mm Small Bump – YEA

SN74LVC3G07YEAR

LT1637 1637FD 微型电源操场类型电阻电压输出电流输入电阻说明书

100µs/DIV1637 TA01b1231637fdInput Offset Voltage Drift (Note 9)N8, S8 Packages, –40°C ≤ T A ≤ 85°C ●13µV/°C MS8 Package, –40°C ≤ T A ≤ 85°C ●26µV/°C DDPackage, –40°C ≤ T A ≤ 85°C ●26µV/°C I OSInput Offset Current●0.4 6.0nA V CM = 44V (Note 5)● 2.5µA I BInput Bias Current●2050nA V CM = 44V (Note 5)●2360µA V S = 0V0.1nA Input Noise Voltage0.1Hz to 10Hz 0.6µV P-P e n Input Noise Voltage Density f = 1kHz 27nV/√Hz i n Input Noise Current Density f = 1kHz0.08pA/√Hz R IN Input Resistance Differential1 2.6M ΩCommon Mode, V CM = 0V to 44V0.7 1.4M ΩC IN Input Capacitance 4pF Input Voltage Range●044V CMRR Common Mode Rejection Ratio V CM = 0V to (V CC – 1V)●88110dB (Note 5)V CM = 0V to 44V (Note 8)●8098dB A VOLLarge-Signal Voltage GainV S = 3V, V O = 500mV to 2.5V, R L = 10k 150400V/mV V S = 3V, 0°C ≤ T A ≤ 70°C ●100V/mV V S = 3V, –40°C ≤ T A ≤ 85°C●75V/mV V S = 5V, V O = 500mV to 4.5V, R L = 10k 300800V/mV V S = 5V, 0°C ≤ T A ≤ 70°C ●200V/mV V S = 5V, –40°C ≤ T A ≤ 85°C●150V/mVV OLOutput Voltage Swing LOWNo Load ●38mV I SINK = 5mA●325700mV V S = 5V, I SINK = 10mA ●5801300mV V OHOutput Voltage Swing HIGHV S = 3V, No Load● 2.94 2.975V V S = 3V, I SOURCE = 5mA ● 2.25 2.67V V S = 5V, No Load● 4.94 4.975V V S = 5V, I SOURCE = 10mA●3.804.45V I SCShort-Circuit Current (Note 2)V S = 3V, Short Output to Ground 1014mA V S = 3V, Short Output to V CC 1545mA V S = 5V, Short Output to Ground 1522mA V S = 5V, Short Output to V CC1560mA PSRRPower Supply Rejection Ratio V S = 3V to 12.5V, V CM = V O = 1V●9098dBMinimum Supply Voltage ● 2.7V Reverse Supply VoltageI S = –100µA●2540V I SSupply Current 190250µA (Note 6)●295µA Supply Current, SHDNV PIN5 = 2V, No Load (Note 6)●312µA I SHDNShutdown Pin CurrentV PIN5 = 0.3V, No Load (Note 6)●0.215nA V PIN5 = 2V, No Load (Note 5)● 1.05µA V PIN5 = 3.3V 2.5µA V PIN5 = 5V4.3µA Output Leakage Current, SHDN V PIN5 = 2V, No Load (Note 6)●0.021µALT1637C/LT1637I SYMBOLPARAMETERCONDITIONSMIN TYP MAXUNITS The ● denotes the specifications which apply over the full operating temperature range of –40°C ≤ T A ≤ 85°C, otherwisespecifications are at T A = 25°C. V S = 3V, 0V; V S = 5V, 0V; V SHDN = V –,V CM = V OUT = half supply unless otherwise specified. (Note 4)3V 5V A D ELECTRICAL CHARACTERISTICS41637fdLT1637C/LT1637I SYMBOL PARAMETER CONDITIONS MIN TYP MAXUNITS V OSInput Offset VoltageN8, S8 Packages 100450µV 0°C ≤ T A ≤ 70°C ●650µV –40°C ≤ T A ≤ 85°C ●800µV MS8 Package 100450µV 0°C ≤ T A ≤ 70°C ●800µV –40°C ≤ T A ≤ 85°C ●1150µV DD Package 125650µV 0°C ≤ T A ≤ 70°C ●1000µV –40°C ≤ T A ≤ 85°C●1150µV Input Offset Voltage Drift (Note 9)N8, S8 Packages, –40°C ≤ T A ≤ 85°C ●13µV/°C MS8 Package, –40°C ≤ T A ≤ 85°C ●26µV/°C DD Package, –40°C ≤ T A ≤ 85°C●26µV/°C I OS Input Offset Current ●16nA I B Input Bias Current ●1750nA Input Noise Voltage 0.1Hz to 10Hz 0.6µV P-P e n Input Noise Voltage Density f = 1kHz 27nV/√Hz i n Input Noise Current Density f = 1kHz0.08pA/√Hz R IN Input Resistance Differential13M ΩCommon Mode, V CM = –15V to 14V2200M ΩC IN Input Capacitance 4pFInput Voltage Range●–1529V CMRR Common Mode Rejection Ratio V CM = –15V to 29V ●80110dB A VOLLarge-Signal Voltage GainV O = ±14V, R L = 10k 100400V/mV 0°C ≤ T A ≤ 70°C ●75V/mV –40°C ≤ T A ≤ 85°C ●50V/mVV OLOutput Voltage Swing LOWNo Load ●–14.997–14.95V I SINK = 5mA ●–14.680–14.25V I SINK = 10mA ●–14.420–13.65VThe ● denotes the specifications which apply over the full operating temperature range of –40°C ≤ T A ≤85°C, otherwise specifications are at T A = 25°C. V S = ±15V, V CM = 0V, V OUT = 0V, V SHDN = V – unless otherwise specified. (Note 4)±15V ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operating temperature range of –40°C ≤ T A ≤85°C, otherwisespecifications are at T A = 25°C. V S = 3V, 0V; V S = 5V, 0V; V SHDN = V –, V CM = V OUT = half supply unless otherwise specified. (Note 4)3V 5V A D ELECTRICAL CHARACTERISTICSLT1637C/LT1637I SYMBOL PARAMETERCONDITIONSMIN TYP MAXUNITS Maximum Shutdown Pin Current V PIN5 = 32V, No Load (Note 5)●20150µA t ON Turn-On Time V PIN5 = 5V to 0V, R L = 10k 45µs t OFF Turn-Off Time V PIN5 = 0V to 5V, R L = 10k 3µs t SETTLING Settling Time0.1% A V = 1, ∆V O = 2V 9µs GBWGain-Bandwidth Product f = 10kHz6501000kHz (Note 5)0°C ≤ T A ≤ 70°C ●550kHz –40°C ≤ T A ≤ 85°C ●500kHz SR Slew Rate A V = –1, R L = ∞0.2100.35V/µs (Note 7)0°C ≤ T A ≤ 70°C ●0.185V/µs –40°C ≤ T A ≤ 85°C●0.170V/µs51637fdV OHOutput Voltage Swing HIGHNo Load●14.914.967V I SOURCE = 5mA ●14.214.667V I SOURCE = 10mA ●13.714.440V I SCShort-Circuit Current (Note 2)Short Output to GND ±25±31.7mA 0°C ≤ T A ≤ 70°C ●±20mA –40°C ≤ T A ≤ 85°C ●±15mA PSRR Power Supply Rejection Ratio V S = ±1.5V to ±22V●90115dBMinimum Supply Voltage ●±1.35V I SSupply Current230300µA ●370µA Positive Supply Current, SHDNV PIN5 = –20V, V S = ±22V, No Load ●640µA I SHDNShutdown Pin Current V PIN5 = –21.7V, V S = ±22V, No Load ●0.315nA V PIN5 = –20V, V S = ±22V, No Load ●0.98µA Maximum Shutdown Pin Current V PIN5 = 32V, V S = ±22V●20150µA Output Leakage Current, SHDNV PIN5 = –20V, V S = ±22V, No Load ●0.022µA V L Shutdown Pin Input Low Voltage V S = ±22V ●–21.7–21.6V V H Shutdown Pin Input High Voltage V S = ±22V●–20.8–20.0V t ON Turn-On Time V PIN5 = –10V to –15V, R L = 10k 35µs t OFF Turn-Off Time V PIN5 = –15V to –10V, R L = 10k 3µs GBWGain-Bandwidth Productf = 10kHz7501100kHz 0°C ≤ T A ≤ 70°C ●650kHz –40°C ≤ T A ≤ 85°C●600kHz SR Slew Rate A V = –1, R L = ∞, V O = ±10V, Measure at V O = ±5V 0.2250.4V/µs 0°C ≤ T A ≤ 70°C ●0.200V/µs –40°C ≤ T A ≤ 85°C●0.180V/µsThe ● denotes the specifications which apply over the full operating temperature range of –40°C ≤ T A ≤85°C, otherwise specifications are at T A = 25°C. V S = ±15V, V CM = 0V, V OUT = 0V, V SHDN = V – unless otherwise specified. (Note 4)LT1637C/LT1637I SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITS±15V ELECTRICAL CHARACTERISTICS61637fdLT1637H/LT1637MP SYMBOL PARAMETER CONDITIONSMIN TYP MAXUNITS V OSInput Offset Voltage100450µV●3mV Input Offset Voltage Drift (Note 9)●310µV/°C I OS Input Offset Current●15nA V CM = 44V (Note 5)●10µA I BInput Bias Current●150nA V CM = 44V (Note 5)●100µA Input Voltage Range●0.344V CMRR Common Mode Rejection Ratio V CM = 0.3V to (V CC – 1V)●72dB (Note 5)V CM = 0.3V to 44V●74dBA VOLLarge-Signal Voltage GainV S = 3V, V O = 500mV to 2.5V, R L = 10k150400V/mV ●20V/mV V S = 5V, V O = 500mV to 4.5V, R L = 10k300800V/mV ●35V/mVV OLOutput Voltage Swing LOWNo Load ●15mV I SINK = 5mA●900mV V S = 5V, I SINK = 10mA ●1500mV V OHOutput Voltage Swing HIGHV S = 3V, No Load● 2.90V V S = 3V, I SOURCE = 5mA ● 2.05V V S = 5V, No Load● 4.90V V S = 5V, I SOURCE = 10mA● 3.50V PSRR Power Supply Rejection Ratio V S = 3V to 12.5V, V CM = V O = 1V ●80dB Minimum Supply Voltage ●2.7V Reverse Supply VoltageI S = –100µA ●23VI SSupply Current (Note 6)190250µA ●400µA Supply Current, SHDNV PIN5 = 2V, No Load (Note 6)●15µA I SHDNShutdown Pin Current V PIN5 = 0.3V, No Load (Note 6)●200nA V PIN5 = 2V, No Load (Note 5)●7µA Output Leakage Current, SHDN V PIN5 = 2V, No Load (Note 6)●5µA Maximum Shutdown Pin CurrentV PIN5 = 32V, No Load (Note 5)●200µA GBW Gain-Bandwidth Product f = 10kHz (Note 5)6501000kHz ●350kHz SRSlew RateA V = –1, R L = ∞ (Note 7)0.2100.35V/µs ●0.1V/µsThe ● denotes the specifications which apply over the full operating temperature range of –40°C ≤ T A ≤125°C for LT1637H and –55°C ≤ T A ≤ 125°C for LT1637MP. V S = 3V, 0V; V S = 5V, 0V; V CM = V OUT = half supply unless otherwise specified. (Note 4)3V 5V A UD ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operating temperature range of –40°C ≤ T A≤125°C for LT1637H and–55°C ≤ T A≤ 125°C for LT1637MP. V S = ±15V, V CM = 0V, V OUT = 0V, V SHDN = V–, unless otherwise specified. (Note 4)±15V ELECTRICAL CHARACTERISTICSLT1637H/LT1637MPSYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS V OS Input Offset Voltage100550µV● 3.4mVInput Offset Voltage Drift (Note 9)●311µV/°C I OS Input Offset Current●25nA I B Input Bias Current●250nA CMRR Common Mode Rejection Ratio V CM = –14.7V to 29V●72dBA VOL Large-Signal Voltage Gain V O = ±14V, R L = 10k100400V/mV●4V/mV V O Output Voltage Swing No Load●±14.8VI OUT = ±5mA●±14.0VI OUT= ±10mA●±13.4V PSRR Power Supply Rejection Ratio V S = ±1.5V to 22V●84dB Minimum Supply Voltage●±1.35VI S Supply Current230300µA●500µAPositive Supply Current, SHDN V PIN5 = –20V, V S = ±22V, No Load●60µA I SHDN Shutdown Pin Current V PIN5 = –21.7V, V S = ±22V, No Load●200nAV PIN5 = –20V, V S = ±22V, No Load●10µA Maximum Shutdown Pin Current V PIN5 = 32V, V S = ±22V●200µA Output Leakage Current, SHDN V PIN5 = –20V, V S = ±22V, No Load●100µA V L Shutdown Pin Input Low Voltage V S = ±22V●–21.7V V H Shutdown Pin Input High Voltage V S = ±22V●–20V GBW Gain-Bandwidth Product f = 10kHz7501100kHz●400kHz SR Slew Rate A V = –1, R L = ∞, V O = ±10V,0.2250.4V/µsMeasure at V O = ±5V●0.1V/µsNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: A heat sink may be required to keep the junction temperature below absolute maximum. The θJA specified for the DD package is with minimal PCB heat spreading metal. Using expanded metal area on all layers of a board reduces this value.Note 3: The LT1637C and LT1637I are guaranteed functional over the operating temperature range of –40°C to 85°C. The LT1637H is guaranteed functional over the operating temperature range of –40°C to 125°C. The LT1637MP is guaranteed functional over the operating temperature range –55°C to 125°C.Note 4: The LT1637C is guaranteed to meet specified performance from 0°C to 70°C. The LT1637C is designed, characterized and expected to meet specified performance from –40°C to 85°C but is not tested or QA sampled at these temperatures. The LT1637I is guaranteed to meet specified performance from –40°C to 85°C. The LT1637H is guaranteed to meet specified performance from –40°C to 125°C and the LT1637MP is guaranteed to meet specified performance from –55°C to 125°C.Note 5: V S = 5V limits are guaranteed by correlation to V S = 3V andV S = ±15V or V S = ±22V tests.Note 6: V S = 3V limits are guaranteed by correlation to V S = 5V andV S = ±15V or V S = ±22V tests.Note 7: Guaranteed by correlation to slew rate at V S = ±15V and GBW at V S = 3V and V S = ±15V tests.Note 8: This specification implies a typical input offset voltage of 650µV at V CM = 44V and a maximum input offset voltage of 5.4mV at V CM = 44V. Note 9: This parameter is not 100% tested.71637fd8TIME (s)081637 G0724619357109100V 10V OUTPUT VOLTAGE (5V/DIV)C1637 G241637 G25A: R L = 2k B: R L = 10k C: R L = 50k1637 G26AB–10V V S = ±15VV S = ±15V A V = –1V S = ±15V A V = 1A B C111637fdSupply VoltageThe positive supply pin of the LT1637 should be bypassed with a small capacitor (about 0.01µF) within an inch of the pin. When driving heavy loads an additional 4.7µF electro-lytic capacitor should be used. When using split supplies,the same is true for the negative supply pin.The LT1637 is protected against reverse battery voltages up to 25V. In the event a reverse battery condition occurs,the supply current is typically less than 1nA.When operating the LT1637 on total supplies of 30V or more, the supply must not be brought up faster than 1µs.This is especially true if low ESR bypass capacitors are used. A series RLC circuit is formed from the supply lead inductance and the bypass capacitor. 5Ω of resistance in the supply or the bypass capacitor will dampen the tuned circuit enough to limit the rise time.InputsThe LT1637 has two input stages, NPN and PNP (see the Simplified Schematic), resulting in three distinct operat-ing regions as shown in the Input Bias Current vs Common Mode typical performance curve.For input voltages about 0.9V or more below V +, the PNP input stage is active and the input bias current is typically –20nA. When the input voltage is about 0.5V or less from V +, the NPN input stage is operating and the input bias current is typically 80nA. Increases in temperature will cause the voltage at which operation switches from the PNP stage to the NPN stage to move towards V +. The input offset voltage of the NPN stage is untrimmed and is typically 600µV.A Schottky diode in the collector of each NPN transistor of the NPN input stage allows the LT1637 to operate with either or both of its inputs above V +. At about 0.3V above V + the NPN input transistor is fully saturated and the input bias current is typically 23µA at room temperature. The input offset voltage is typically 600µV when operating above V +. The LT1637 will operate with its input 44V above V – regardless of V +.APPLICATIO S I FOR ATIOW UUU The inputs are protected against excursions as much as 22V below V – by an internal 1.3k resistor in series with each input and a diode from the input to the negative supply. There is no output phase reversal for inputs up to 5V below V –. There are no clamping diodes between the inputs and the maximum differential input voltage is 44V.OutputThe output voltage swing of the LT1637 is affected by input overdrive as shown in the typical performance curves. When monitoring input voltages within 100mV of V +, gain should be taken to keep the output from clipping.The output of the LT1637 can be pulled up to 25V beyond V + with less than 1nA of leakage current, provided that V +is less than 0.5V.The normally reverse biased substrate diode from the output to V – will cause unlimited currents to flow when the output is forced below V –. If the current is transient and limited to 100mA, no damage will occur.The LT1637 is internally compensated to drive at least 200pF of capacitance under any output loading condi-tions. A 0.22µF capacitor in series with a 150Ω resistor between the output and ground will compensate these amplifiers for larger capacitive loads, up to 4700pF, at all output currents.DistortionThere are two main contributors of distortion in op amps:output crossover distortion as the output transitions from sourcing to sinking current and distortion caused by nonlinear common mode rejection. Of course, if the op amp is operating inverting there is no common mode induced distortion. When the LT1637 switches between input stages there is significant nonlinearity in the CMRR.Lower load resistance increases the output crossover distortion, but has no effect on the input stage transition distortion. For lowest distortion the LT1637 should be operated single supply, with the output always sourcing current and with the input voltage swing between ground and (V + – 0.9V). See the Typical Performance Character-istics curves.121314Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.1516Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2007LT 0107 REV D • PRINTED IN USA。

74LCX16373G中文资料