MC10E137中文资料

110COUNTER中文对照

MC01=NBR_DCCH_TERM_TRANS(被叫成功占用SDCCH次数)MC02=NBR_DCCH_ORIG_TRANS(主叫成功占用SDCCH次数)MC02a=NBR_DCCH_LOC_UPD(主叫成功占用SDCCH--位置更新次数)MC02b=NBR_DCCH_SMS_ORIG(主叫成功占用SDCCH--短消息服务)MC02c=NBR_DCCH_SUPPL_SERV_ORIG(主叫成功占用SDCCH--附加服务,呼叫前转等)MC02d=NBR_DCCH_FOLLOW_ON(LOC-UPD后做主叫次数)MC02e=NBR_DCCH_CM_REESTABL_REQ(呼叫重建次数-上层协议断,下层协议连接,重建上层协议)MC02f=NBR_DCCH_OTHER_ORIG(其它原因主叫次数-无法解开呼叫原因)MC02g=NBR_DCCH_IMSI_DETACH_IND(DETACH原因)MC02h=NBR_DCCH_CALL_ESTABL_ORIG(所有主叫电话-含NORMAL,EMERGENCY)MC04=NBR_NO_DCCH_A V AIL(SDCCH拥塞次数)MC07=NBR_SDCCH_HO_NO_MS_RET(SDC切换不成功后未回原信道)--SDC掉话的一种MC10=NBR_SDCCH_SEIZ_HO(SDC切换成功)MC12=NBR_NO_RTCH_A V AIL(TCH拥塞次数,包含主被叫、BSC间切换无TCH次数)MC12a=NBR_NO_RTCH_A V AIL_NO_QE(无队列造成TCH拥塞)MC12b=NBR_NO_RTCH_A V AIL_QE_FULL(队列满造成TCH拥塞)MC12c=NBR_NO_RTCH_A V AIL_QE_TIMEOUT(在队列中等待时间内无TCH信道空闲造成拥塞)MC12d=NBR_NO_RTCH_A V AIL_QE_REJ(由于更高级别手机接入造成被赶出队列)MC13=NBR_RTCH_REQ_QD(申请进入队列的总次数)MC14=NBR_RTCH_FAIL_BSS_PBL(由BSS造成TCH中断)1、ABIS收到ERROR REPORT 2、消息次序错误3、LAPD FAILURE 4、LOSE CHANNEL DUE TO OTHER BSC INTERNAL PROBLEM 5、BSS操作维护或软件问题MC14a=NBR_HO_RTCH_FAIL_BSS_PBL(由于BSS造成TCH切换失败)MC14b=NBR_ASS_RTCH_FAIL_BSS_PBL(由于BSS引起TCH分配失败)MC14c=NBR_RTCH_LOST_BSS_PBL(由于BSS引起TCH掉话)1、SWITCH板造成掉话2、传输问题MC146b=NB_ASS_RTCH_FAIL_MS_ACC_PBL(由于手机接入引起TCH分配失败)1、由于无线原因而引起,和BS硬件有关。

MC10E111FN中文资料

MC10E111 MC100E111

1:9 DIFFERENTIAL CLOCK DRIVER

• • • • • • •

Low Skew Guarateed Skew Spec Differential Design VBB Output Enable Extended 100E VEE Range of –4.2 to –5.46V 75kΩ Input Pulldown Resistors

MC10E111 MC100E111

DC CHARACTERISTICS (VEE = VEE (min) to VEE (max); VCC = VCCO = GND)

–40°C Symbol VBB Characteristic Output Reference Voltage 10E 100E Input HIGH Current Power Supply Current 10E 100E Input Sensitivity Commom Mode Range 50 –1.6 –0.4 48 48 Min –1.43 –1.38 Typ Max –1.30 –1.26 150 Min –1.38 –1.38 0°C Typ Max –1.27 –1.26 150 Min –1.35 –1.38 25°C Typ Max –1.25 –1.26 150 Min –1.31 –1.38 85°C Typ Max –1.19 –1.26 150 µA mA 60 60 50 –1.6 –0.4 48 48 60 60 50 –1.6 –0.4 48 48 60 60 50 –1.6 –0.4 48 55 60 69 mV V 1 2 Unit V Cond

元器件交易网

MOTOROLA

MC100E107FN资料

D4a D4b

Q4 Q4

12/93

© Motorola, Inc. 1996

2–1

REV 2

元器件交易网

MC10E107 MC100E107

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

W

28 1

D X VIEW D-D G1 0.010 (0.250)

S

V

T L –M

S

N

S

A Z R

0.007 (0.180) 0.007 (0.180)

M

T L –M T L –M

S

N N

S

H

S

0.007 (0.180)

M

T L –M

S

N

S

M

S

C

E G G1 0.010 (0.250)

S

K1 0.004 (0.100) J -TSEATING PLANE

DIM A B C E F G H J K R U V W X Y Z G1 K1

INCHES MIN MAX 0.485 0.495 0.485 0.495 0.165 0.180 0.090 0.110 0.013 0.019 0.050 BSC 0.026 0.032 0.020 — 0.025 — 0.450 0.456 0.450 0.456 0.042 0.048 0.042 0.048 0.042 0.056 — 0.020 2° 10° 0.410 0.430 0.040 —

0°C Symbol IIH IEE Characteristic Input HIGH Current Power Supply Current 10E 100E 42 42 min typ max 200 50 50 42 42 min 25°C typ max 200 50 50 42 48 min 85°C typ max 200 50 58 Unit µA mA Condition

飞机大小常识

738全称为Boeing737-800客机。

是中型飞机。

大型宽体飞机:座位数在200以上,飞机上有双通道通行747 波音747载客数在350-400人左右(747、74E均为波音747的不同型号)777 波音777载客在350人左右(或以77B作为代号)767 波音767载客在280人左右M11 麦道11载客340人左右340 空中客车340载客350人左右300 空中客车300 载客280人左右(或以AB6作为代号)310 空中客车310载客250人左右ILW 伊尔86苏联飞机载客300人左右中型飞机:指单通道飞机,载客在100人以上,200人以下M82/M90 麦道82 麦道90载客150人左右737/738/733 波音737系列载客在130-160左右320空中客车320载客180人左右TU54苏联飞机载客150人左右146英国宇航公司BAE-146飞机载客108人YK2 雅克42苏联飞机载客110人左右小型飞机:指100座以下飞机,多用于支线飞行YN7 运7国产飞机载客50人左右AN4 安24苏联飞机载客50人左右SF3 萨伯100载客30人左右ATR 雅泰72A载客70人左右世界上现有主要机型:美国波音商用飞机制造公司、欧洲空中客车工业公司、美国麦克唐纳.道格拉斯公司。

1996年底,波音公司已同麦道合并。

波音系列:波音707、波音727、波音737、波音747、波音757、波音767、波音777 。

空中客车系列:A-300、A-310、A-320、A-330、A-340。

麦道系列:MD-80、MD-81、MD-82、MD-83、MD-87、MD-88、MD-11。

此外,还有俄罗斯制造的图-154、图-154M型,前苏联生产的伊尔-18、伊尔-86、雅克-42、安-30,英国制造的英航-146(BAE-146)、肖特-360,荷兰的福克-100,以及中国制造的运-7、运-8、运-10、运-11、运-12等型飞机。

MC10E016中文资料

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

8 Bit Synchronous Binary Up Counter

The MC10E/100E016 is a high-speed synchronous, presettable, cascadable 8-bit binary counter. Architecture and operation are the same as the MC10H016 in the MECL 10H family, extended to 8-bits, as shown in the logic symbol. The counter features internal feedback of TC, gated by the TCLD (terminal count load) pin. When TCLD is LOW (or left open, in which case it is pulled LOW by the internal pull-downs), the TC feedback is disabled, and counting proceeds continuously, with TC going LOW to indicate an all-one state. When TCLD is HIGH, the TC feedback causes the counter to automatically reload upon TC = LOW, thus functioning as a programmable counter. The Qn outputs do not need to be terminated for the count function to operate properly. To minimize noise and power, unused Q outputs should be left unterminated.

MC10EP16T资料

MC10EP16T, MC100EP16T 3.3V / 5VĄECL Differential Receiver/Driver with Internal TerminationThe EP16T is a world–class differential receiver/driver. The device is functionally equivalent to the EP16 with internal termination resistors. A 50 W resistor is connected from the D input to the VT pin and from the D input to the VT pin. Tie the VT and VT pins to VTT supply (V CC – 2 V) for parallel termination or connect VT and VT pins for 100 W input series termination.Special considerations are required for differential inputs under No Signal conditions to prevent instability.The 100 Series contains temperature compensation.•220 ps Typical Propagation Delay •Maximum Frequency > 3 GHz Typical•PECL Mode Operating Range: V CC = 3.0 V to 5.5 V with V EE = 0 V•NECL Mode Operating Range: V CC = 0 V with V EE = –3.0 V to –5.5 V•Internal 50 W Termination ResistorsDevice Package Shipping ORDERING INFORMATIONMC10EP16TD SO–898 Units/Rail MC10EP16TDR2SO–82500 Tape & Reel MC100EP16TD SO–898 Units/Rail MC100EP16TDR2SO–82500 Tape & Reel MC10EP16TDT TSSOP–8100 Units/Rail MC10EP16TDTR2TSSOP–82500 Tape & Reel MC100EP16TDTTSSOP–8100 Units/Rail MC100EP16TDTR2TSSOP–82500 Tape & ReelQV EEV CCFigure 1. 8–Lead Pinout (Top View) and Logic DiagramD QD VT VT PIN DESCRIPTION1.For additional information, see Application Note AND8003/D.MAXIMUM RATINGS (Note 2)circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.3.Input and output parameters vary 1:1 with V CC. V EE can vary +0.3 V to –2.2 V.4.All loading with 50 W to V CC–2.0 volts.5.V IHCMR min varies 1:1 with V EE, V IHCMR max varies 1:1 with V CC. The V IHCMR range is referenced to the most positive side of the differentialinput signal.circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.6.Input and output parameters vary 1:1 with V CC. V EE can vary +2.0 V to –0.5 V.7.All loading with 50 W to V CC–2.0 volts.8.V IHCMR min varies 1:1 with V EE, V IHCMR max varies 1:1 with V CC. The V IHCMR range is referenced to the most positive side of the differentialinput signal.circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.9.Input and output parameters vary 1:1 with V CC.10.All loading with 50 W to V CC–2.0 volts.11.V IHCMR min varies 1:1 with V EE, V IHCMR max varies 1:1 with V CC. The V IHCMR range is referenced to the most positive side of the differentialinput signal.circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.12.Input and output parameters vary 1:1 with V CC. V EE can vary +0.3 V to –2.2 V.13.All loading with 50 W to V CC–2.0 volts.14.V IHCMR min varies 1:1 with V EE, V IHCMR max varies 1:1 with V CC. The V IHCMR range is referenced to the most positive side of the differentialinput signal.circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.15.Input and output parameters vary 1:1 with V CC. V EE can vary +2.0 V to –0.5 V.16.All loading with 50 W to V CC–2.0 volts.17.V IHCMR min varies 1:1 with V EE, V IHCMR max varies 1:1 with V CC. The V IHCMR range is referenced to the most positive side of the differentialinput signal.circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.18.Input and output parameters vary 1:1 with V CC.19.All loading with 50 W to V CC–2.0 volts.20.V IHCMR min varies 1:1 with V EE, V IHCMR max varies 1:1 with V CC. The V IHCMR range is referenced to the most positive side of the differentialinput signal.AC CHARACTERISTICS V= 0 V; V = –3.0 V to –5.5 V or V = 3.0 V to 5.5 V; V = 0 V (Note 21)CC 22.Skew is measured between outputs under identical transitions. Duty cycle skew is defined only for differential operation when the delays are measured from the cross point of the inputs to the cross point of the outputs.10020030040050060070080090005001000150020002500300035004000Figure 2. F max /JitterFREQUENCY (MHz)V O U T p p (m V )V TTV TT=V CC– 2.0 VFigure 3. Typical Termination for Output Driver and Device Evaluation(See Application Note AND8020 – Termination of ECL Logic Devices.)Resource Reference of Application NotesAN1404–ECLinPS Circuit Performance at Non–Standard V IH LevelsAN1405–ECL Clock Distribution TechniquesAN1406–Designing with PECL (ECL at +5.0 V)AN1504–Metastability and the ECLinPS FamilyAN1568–Interfacing Between LVDS and ECLAN1650–Using Wire–OR Ties in ECLinPS DesignsAN1672–The ECL Translator GuideAND8001–Odd Number Counters DesignAND8002–Marking and Date CodesAND8009–ECLinPS Plus Spice I/O Model KitAND8020–Termination of ECL Logic DevicesFor an updated list of Application Notes, please see our website at .PACKAGE DIMENSIONSSO–8D SUFFIX PLASTIC SOIC PACKAGECASE 751–07NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A AND B DO NOT INCLUDE MOLDPROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006) PERSIDE.5.DIMENSION D DOES NOT INCLUDE DAMBARPROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL INEXCESS OF THE D DIMENSION AT MAXIMUMMATERIAL CONDITION.6.751-01 THRU 751-06 ARE OBSOLETE. NEWSTANDAARD IS 751-07DIMAMIN MAX MIN MAXINCHES4.805.000.1890.197MILLIMETERSB 3.80 4.000.1500.157C 1.35 1.750.0530.069D0.330.510.0130.020G 1.27 BSC0.050 BSCH0.100.250.0040.010J0.190.250.0070.010K0.40 1.270.0160.050M0 8 0 8N0.250.500.0100.020S 5.80 6.200.2280.244 YM0.25 (0.010)Z S X S____DIM MIN MAX MIN MAXINCHESMILLIMETERSA 2.90 3.100.1140.122B 2.90 3.100.1140.122C0.80 1.100.0310.043D0.050.150.0020.006F0.400.700.0160.028G0.65 BSC0.026 BSCL 4.90 BSC0.193 BSCM0 6 0 6____K0.250.400.0100.016TSSOP–8DT SUFFIXPLASTIC TSSOP PACKAGECASE 948R–02ISSUE ANOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH.PROTRUSIONS OR GATE BURRS. MOLD FLASHOR GATE BURRS SHALL NOT EXCEED 0.15(0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEADFLASH OR PROTRUSION. INTERLEAD FLASH ORPROTRUSION SHALL NOT EXCEED 0.25 (0.010)PER SIDE.5.TERMINAL NUMBERS ARE SHOWN FORREFERENCE ONLY.6.DIMENSION A AND B ARE TO BE DETERMINEDAT DATUM PLANE -W-.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others.SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. PUBLICATION ORDERING INFORMATIONJAPAN: ON Semiconductor, Japan Customer Focus Center2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051Phone: 81–3–5773–3850Email: r14525@。

CIT-10中文手册new

端口进行连接,打开设备电源,此时系统会自动安装USB的驱动; z 安装后系统会产生一个名为CIT的目录(默认路径为C:\Program Files\CIT),目录中会

型号应用ae连接器eut连接器cdn801m1非屏蔽线主要4mmmc插孔4mmmc插孔cdn801m2非屏蔽线主要4mmmc插孔4mmmc插孔cdn801m3非屏蔽线主要4mmmc插孔4mmmc插孔cdn801m4非屏蔽线主要4mmmc插孔4mmmc插孔cdn801m5非屏蔽线主要4mmmc插孔4mmmc插孔cdn801m2m3非屏蔽线主要4mmmc插孔4mmmc插孔cdn801s1屏蔽线bncbnccdn801s2屏蔽线xlrfemalexlrmalecdn801s9屏蔽线subdcdn801s25屏蔽线subd25公subd25公cdn801af2非屏蔽非平衡线终端模块终端模块cdn801af4非屏蔽非平衡线终端模块终端模块cdn801af6非屏蔽非平衡线终端模块终端模块cit10cit1075用户手册19cdn801af8非屏蔽非平衡线终端模块终端模块cdn801t2非屏蔽平衡对线终端模块终端模块cdn801t4非屏蔽平衡对线终端模块终端模块cdn801t8非屏蔽平衡对线终端模块终端模块cdn801rj11非屏蔽数据线rj11接口rj11接口cdn801rj11s屏蔽数据线rj11接口rj11接口cdn801rj45非屏蔽数据线rj45接口rj45接口cdn801rj45s屏蔽数据线rj45接口rj45接口cdn801usbcusb设备usbausbbcdn801usbpusb设备usbbusba57技术参数rf功率表频率范围10khz400mhz测试电平30dbm40dbm精度典型值05db最大值10dbvswr输入接口bnc50欧姆rf信号发生器输出接口bnc50欧姆频率范围10khz400mhz频率分辨率hz输出电平63dbm输出电平分辨率01db输出电平精度典型值05db最大值10db精度频率ppmtcxo失真谐波30dbc

MC1378FN中文资料

Order this document by MC1378/D

MC1378 Color Television Composite Video Overlay Synchronizer

The MC1378 is a bipolar composite video overlay encoder and microcomputer synchronizer. The MC1378 contains the complete encoder function of the MC1377, i.e., quadrature color modulators, RGB matrix, and blanking level clamps, plus a complete complement of synchronizers to lock a microcomputer–based video source to any remote video source. The MC1378 can be used as a local system timing and encoding source, but it is most valuable when used to lock the microcomputer source to a remotely originated video signal. • Contains All Needed Reference Oscillators

Figure 1. Simplified Application

Chroma VCO

{

10 (11) (34) 31 11 (12) (33) 30 12 (13) (32) 29 13 (14) (31) 28 14 (15) (30) 27 15 (16) (29) 26 16 (18) (27) 25 17 (19) (26) 24 18 (20) (25) 23 19 (21) (24) 22 20 (22) (23) 21

BT137中文资料_数据手册_参数

Product specification

BT137 series

12 Ptot / W 10

8 6

BT137

1

Tmb(max) / C 101

= 180

120

105

90

109 60

30

113

4

117

2

121

0

125

0

2

4

6

8

10

IT(RMS) / A

Fig.1. Maximum on-state dissipation, Ptot, versus rms on-state current, IT(RMS), where α = conduction angle.

QUICK REFERENCE DATA

SYMBOL PARAMETER

MAX. MAX. MAX. UNIT

VDRM IT(RMS) ITSM

BT137- 500 600 800

BT137- 500F 600F 800F

BT137- 500G 600G 800G

Repetitive peak off-state

Tj = 25 ˚C unless otherwise stated SYMBOL PARAMETER

CONDITIONS

MIN. TYP.

MAX.

UNIT

BT137-

... ...F ...G

IGT

Gate trigger current

VD = 12 V; IT = 0.1 A

T2+ G+

-

5

35 25 50 mA

-

10 20

tgt

TM710e产品技术说明

TM710e水分仪技术规格TM710e探头检测范围:每个探头最多可测多达4种元素(水分/尼古丁/糖份/温度)测量范围和精度(%绝对值)水 分:范围0-60% 仪器精度±0.1%到±0.8%(烟丝:0.3%,梗丝:0.3%,叶片:0.5%,梗条:0.8%) 尼古丁:范围0-6% 仪器精度±0.1%糖 份:范围0-30% 仪器精度±1%温 度:范围1-120度 仪器精度±1度测量波段:达16个(VFS技术)探头到产品操作距离:250mm(标准)工作距离范围:150-350mm(±100mm)采样面积:60mm圆周块环境光敏感度:不敏感响应时间:0.1秒到1000秒指数或线性的标定调较:快速标定,预标定,勿须常规再标定可靠性:灯泡、马达保用5年,系统平均无故障时间(MTBF)10年●水分检测速度150次/秒;●测量高度(镜头至物料表面的距离)250mm±100mm;●可提供多达16波段近红外检测信号;●采样面积φ60mm;●铸铝外壳反射式传感器探头,带内置水冷却系统,使探头可在50ºC以上、80ºC以下正常工作;●符合CE认证;●内部工作状态诊断、监视、保护系统;●内置窗口污染监测器;●探头密闭标准为IP65(NEMA 4),对工作环境无特殊要求;●双探测器专利技术,提供高速信号处理功能,并有效地排除了环境因素(如温度、光线等)的干扰,从而提高了测量精度,使高速检测、单光路设计成为可能;●离轴聚光镜专利技术,充分利用近红外光能量;●24格变焦聚光镜,排除了物料抖动对测量精度的干扰;●统一电压输入24V直流电源。

外置交流220V转直流24V专用电源转换器,水分仪系统全部采用直流24V电源输入,提高了可靠性,安全性,降低功耗,保证了长期使用稳定性。

网卡等数据传输接口置于主操作界面,完全避免与探头内部器件及电源发热干扰。

MC100E137FNG,MC10E137FNG,MC100E137FN,MC100E137FNR2,MC10E137FN,MC10E137FNR2, 规格书,Datasheet 资料

MC10E137, MC100E1375 V ECL 8-Bit Ripple CounterDescriptionThe MC10E/100E137 is a very high speed binary ripple counter. The two least significant bits were designed with very fast edge rates while the more significant bits maintain standard ECLinPS ™ output edge rates. This allows the counter to operate at very high frequencies while maintaining a moderate power dissipation level.The device is ideally suited for multiple frequency clock generation as well as a counter in a high performance ATE time measurement board.Both asynchronous and synchronous enables are available to maximize the device’s flexibility for various applications. The asynchronous enable input, A_Start, when asserted enables the counter while overriding any synchronous enable signals. The E137 features XORed enable inputs, EN1 and EN2, which are synchronous to the CLK input. When only one synchronous enable is asserted the counter becomes disabled on the next CLK transition; all outputs remain in the previous state poised for the other synchronous enable or A_Start to be asserted to re-enable the counter. Asserting both synchronous enables causes the counter to become enabled on the next transition of the CLK.If EN1 (or EN2) and CLK edges are coincident, sufficient delay has been inserted in the CLK path (to compensate for the XOR gate delay and the internal D-flip flop setup time) to insure that the synchronous enable signal is clocked correctly, hence, the counter is disabled.All input pins left open will be pulled LOW via an input pulldown resistor. Therefore, do not leave the differential CLK inputs open.Doing so causes the current source transistor of the input clock gate to become saturated, thus upsetting the internal bias regulators and jeopardizing the stability of the device.The asynchronous Master Reset resets the counter to an all zero state upon assertion.The V BB pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to V BB as a switching reference voltage.V BB may also rebias AC coupled inputs. When used, decouple V BB and V CC via a 0.01 m F capacitor and limit current sourcing or sinking to 0.5 mA. When not used, V BB should be left open.The 100 Series contains temperature compensation.Features•Differential Clock Input and Data Output Pins •V BB Output for Single-Ended Use•Synchronous and Asynchronous Enable Pins •Asynchronous Master Reset•PECL Mode Operating Range: V CC = 4.2 V to 5.7 V with V EE = 0 V•NECL Mode Operating Range: V CC = 0 V with V EE = −4.2 V to −5.7 V•Internal Input 50 k W Pull −down Resistors •Transistor Count = 330 devices•ESD Protection: Human Body Model: > 2 kV ,Machine Model: > 200 V•Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test•Moisture Sensitivity Level: Pb = 1; Pb −Free = 3For Additional Information, see Application Note AND8003/D•Flammability Rating: UL 94 V −0 @ 0.125 in,Oxygen Index: 28 to 34•Pb −Free Packages are Available**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.MARKING DIAGRAM*xxx = 10 or 100A = Assembly Location WL = Wafer Lot YY = YearWW = Work WeekG = Pb −Free PackagePLCC −28FN SUFFIX CASE 776MCxxxE137FNG AWLYYWW1*For additional marking information, refer to Application Note AND8002/D.See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.ORDERING INFORMATIONV CCO 1Q0Q7Q6Q6Q5Q5Q4Q4V CC Q3Q3Q2Q2V CCOQ1Q1Q0V CCOMR V BBCLK CLK V EE EN2EN1A_Start 4322827262524232221201918171615141312111097865Pinout: 28-Lead PLCC(Top View)* All V CC and V CCO pins are tied together on the die.Figure 1. 28−Lead PinoutEN1EN2CLK CLK A_Start MRV BB Figure 2. Logic DiagramWarning: All V CC , V CCO , and V EE pins must be externally connected to Power Supply to guarantee proper operation.Q7Table 2. SEQUENTIAL TRUTH TABLEFunction EN1EN2A_Start MR CLK Q7Q6Q5Q4Q3Q2Q1Q0 Reset X X X H X L L L L L L L LCount LLL LLLLLLLLLZZZLLLLLLLLLLLLLLLLLLLHHHLHStop HH LLLLLLZZLLLLLLLLLLLLHHHHAsynch Start HHL LLLHHHLLLZZZLLLLLLLLLLLLLLLHHHLLHLHLCount LLL LLLLLLLLLZZZLLLLLLLLLLLLLHHHLLHLLHLHStop LL HHLLLLZZLLLLLLLLHHLLLLHHSynch Start HHH HHHLLLLLLZZZLLLLLLLLLLLLHHHLLHHHLLHLStop HH LLLLLLZZLLLLLLLLHHHHLLLLCount LLL LLLLLLLLLZZZLLLLLLLLLLLLHHHHHHLHHHLHReset X X X H X L L L L L L L L Z = Low to High TransitionTable 3. MAXIMUM RATINGSSymbol Parameter Condition 1Condition 2Rating Unit V CC PECL Mode Power Supply V EE = 0 V8V V EE NECL Mode Power Supply V CC = 0 V−8VV I PECL Mode Input VoltageNECL Mode Input Voltage V EE = 0 VV CC = 0 VV I v V CCV I w V EE6−6VVI out Output Current ContinuousSurge 50100mAmAT A Operating Temperature Range0 to +85°C T stg Storage Temperature Range−65 to +150°Cq JA Thermal Resistance (Junction−to−Ambient)0 lfpm500 lfpm PLCC−28PLCC−2863.543.5°C/W°C/Wq JC Thermal Resistance (Junction−to−Case)Standard Board PLCC−2822 to 26°C/WV EE PECL Operating RangeNECL Operating Range4.2 to5.7−5.7 to −4.2VVT sol Wave Solder PbPb−Free 265265°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.Symbol Characteristic Min Typ Max Min Typ Max Min Typ Max Unit I EE Power Supply Current121145121145121145mA V OH Output HIGH Voltage (Note 2)398040704160402041054190409041854280mV V OL Output LOW Voltage (Note 2)305032103370305032103370305032273405mV V IH Input HIGH Voltage (Single−Ended)383039954160387040304190394041104280mV V IL Input LOW Voltage (Single−Ended)305032853520305032853520305033023555mV V BB Output Voltage Reference 3.62 3.73 3.65 3.75 3.69 3.81VV IHCMR Input HIGH Voltage Common ModeRange (Differential Configuration)(Note 3)2.2 4.6 2.2 4.6 2.2 4.6VI IH Input HIGH Current150150150m AI IL Input LOW Current0.50.30.50.250.30.2m A NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declaredoperating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.1.Input and output parameters vary 1:1 with V CC. V EE can vary −0.46 V / +0.06 V.2.Outputs are terminated through a 50 W resistor to V CC− 2.0 V.3.V IHCMR min varies 1:1 with V EE, max varies 1:1 with V CC.Table 5. 10E SERIES NECL DC CHARACTERISTICS V CCx = 0.0 V; V EE = −5.0 V (Note 4)Symbol Characteristic0°C25°C85°CUnit Min Typ Max Min Typ Max Min Typ MaxI EE Power Supply Current121145121145121145mA V OH Output HIGH Voltage (Note 5)−1020−930−840−980−895−810−910−815−720mV V OL Output LOW Voltage (Note 5)−1950−1790−1630−1950−1790−1630−1950−1773−1595mV V IH Input HIGH Voltage (Single−Ended)−1170−1005−840−1130−970−810−1060−890−720mV V IL Input LOW Voltage (Single−Ended)−1950−1715−1480−1950−1715−1480−1950−1698−1445mV V BB Output Voltage Reference−1.38−1.27−1.35−1.25−1.31−1.19VV IHCMR Input HIGH Voltage Common ModeRange (Differential Configuration)(Note 6)−2.8−0.4−2.8−0.4−2.8−0.4VI IH Input HIGH Current150150150m AI IL Input LOW Current0.50.30.50.0650.30.2m A NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declaredoperating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.4.Input and output parameters vary 1:1 with V CC. V EE can vary −0.46 V / +0.06 V.5.Outputs are terminated through a 50 W resistor to V CC− 2.0 V.6.V IHCMR min varies 1:1 with V EE, max varies 1:1 with V CC.Symbol Characteristic UnitMin Typ Max Min Typ Max Min Typ MaxI EE Power Supply Current121145121145139167mA V OH Output HIGH Voltage (Note 8)397540504120397540504120397540504120mV V OL Output LOW Voltage (Note 8)319032953380319032553380319032603380mV V IH Input HIGH Voltage (Single−Ended)383539754120383539754120383539754120mV V IL Input LOW Voltage (Single−Ended)319033553525319033553525319033553525mV V BB Output Voltage Reference 3.62 3.73 3.62 3.74 3.62 3.74VV IHCMR Input HIGH Voltage Common ModeRange (Differential Configuration)(Note 9)2.2 4.6 2.2 4.6 2.2 4.6VI IH Input HIGH Current150150150m AI IL Input LOW Current0.50.30.50.250.50.2m A NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declaredoperating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.7.Input and output parameters vary 1:1 with V CC. V EE can vary −0.46 V / +0.8 V.8.Outputs are terminated through a 50 W resistor to V CC− 2.0 V.9.V IHCMR min varies 1:1 with V EE, max varies 1:1 with V CC.Table 7. 100E SERIES NECL DC CHARACTERISTICS V CCx = 0.0 V; V EE = −5.0 V (Note 10)Symbol Characteristic0°C25°C85°CUnit Min Typ Max Min Typ Max Min Typ MaxI EE Power Supply Current121145121145139167mA V OH Output HIGH Voltage (Note 11)−1025−950−880−1025−950−880−1025−950−880mV V OL Output LOW Voltage (Note 11)−1810−1705−1620−1810−1745−1620−1810−1740−1620mV V IH Input HIGH Voltage (Single−En-ded)−1165−1025−880−1165−1025−880−1165−1025−880mVV IL Input LOW Voltage (Single−En-ded)−1810−1645−1475−1810−1645−1475−1810−1645−1475mV V BB Output Voltage Reference−1.38−1.27−1.38−1.26−1.38−1.26VV IHCMR Input HIGH Voltage CommonMode Range (Differential Configu-ration) (Note 12)−3.8−0.4−3.8−0.4−3.8−0.4VI IH Input HIGH Current150150150m AI IL Input LOW Current0.50.30.50.250.50.2m ANOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declaredoperating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.10.Input and output parameters vary 1:1 with V CC. V EE can vary −0.46 V / +0.8 V.11.Outputs are terminated through a 50 W resistor to V CC− 2.0 V.12.V IHCMR min varies 1:1 with V EE, max varies 1:1 with V CC.Table 8. AC CHARACTERISTICS V CCx = 5.0 V; V EE = 0.0 V or V CCx = 0.0 V; V EE = −5.0 V (Note 13)Symbol Characteristic0°C25°C85°CUnit Min Typ Max Min Typ Max Min Typ Maxf COUNT Maximum Count Frequency180022001800220018002200MHzt PLH t PHL Propagation Delay to OutputCLK to Q0CLK to Q1CLK to Q2CLK to Q3CLK to Q4CLK to Q5CLK to Q6CLK to Q7A_Start to Q0MR to Q0130016001950227526252950325035759507001700202524252750312534503775407513251000215025002925335037504150445048001700130013001600195022752625295032503575950700170020502450277531503475380041251325100021502500292533503750415044504800170013001350165020252350270030503375370095070017502100250028503225355039254250132510002200255030003425382542504600495017001300pst s Setup Time (EN1, EN2)0−1500−1500−150ps t h Hold Time (EN1, EN2)300150300150300150ps t RR Reset Recovery TimeMR, A_Start400200400200400200pst PW Minimum Pulse WidthCLK, MR, A_Start400400400psV PP Input Voltage Swing CLK/CLK(Differential Configuration) (Note 14)0.25 1.00.25 1.00.25 1.0V t JITTER Random Clock Jitter (RMS)< 1< 1< 1pst r t f Rise/Fall Times (20%−80%)Q0,Q1Q2 to Q7150275400600150275400600150275400600psNOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declaredoperating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.13.10 Series: V EE can vary −0.46 V / +0.06 V.100 Series: V EE can vary −0.46 V / +0.8 V.14.Minimum input swing for which AC parameters are guaranteed. Full DC ECL output swings will be generated with only 50 mV input swings.Figure 3. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020/D − Termination of ECL Logic Devices.)V TTV TT = V CC − 2.0 VORDERING INFORMATIONDevicePackage Shipping †MC10E137FN PLCC −2837 Units / Rail MC10E137FNG PLCC −28(Pb −Free)37 Units / Rail MC10E137FNR2PLCC −28500 / Tape & Reel MC10E137FNR2G PLCC −28(Pb −Free)500 / Tape & Reel MC100E137FN PLCC −2837 Units / Rail MC100E137FNG PLCC −28(Pb −Free)37 Units / Rail MC100E137FNR2PLCC −28500 / Tape & Reel MC100E137FNR2GPLCC −28(Pb −Free)500 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.Resource Reference of Application NotesAN1405/D −ECL Clock Distribution Techniques AN1406/D −Designing with PECL (ECL at +5.0 V)AN1503/D −ECLinPS t I/O SPiCE Modeling Kit AN1504/D −Metastability and the ECLinPS Family AN1568/D −Interfacing Between LVDS and ECL AN1672/D −The ECL Translator Guide AND8001/D −Odd Number Counters Design AND8002/D −Marking and Date CodesAND8020/D −Termination of ECL Logic Devices AND8066/D −Interfacing with ECLinPSAND8090/D−AC Characteristics of ECL DevicesPACKAGE DIMENSIONSPLCC −28FN SUFFIXPLASTIC PLCC PACKAGECASE 776−02ISSUE ESL−M S 0.010 (0.250) NST VIEW SNOTES:1.DATUMS −L−, −M−, AND −N− DETERMINED WHERE TOP OF LEAD SHOULDER EXITS PLASTIC BODY AT MOLD PARTING LINE.2.DIMENSION G1, TRUE POSITION TO BEMEASURED AT DATUM −T−, SEATING PLANE.3.DIMENSIONS R AND U DO NOT INCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.250) PER SIDE.4.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.5.CONTROLLING DIMENSION: INCH.6.THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012(0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.7.DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037(0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).DIM MIN MAX MIN MAX MILLIMETERSINCHES A 0.4850.49512.3212.57B 0.4850.49512.3212.57C 0.1650.180 4.20 4.57E 0.0900.110 2.29 2.79F 0.0130.0190.330.48G 0.050 BSC 1.27 BSC H 0.0260.0320.660.81J 0.020−−−0.51−−−K 0.025−−−0.64−−−R 0.4500.45611.4311.58U 0.4500.45611.4311.58V 0.0420.048 1.07 1.21W 0.0420.048 1.07 1.21X 0.0420.056 1.07 1.42Y −−−0.020−−−0.50Z 2 10 2 10 G10.4100.43010.4210.92K10.040−−− 1.02−−−____ECLinPS is a trademark of Semiconductor Components Industries, LLC (SCILLC).ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

ASTM E213超探中文

内部资料名称:E 213 - 04金属管和管状材料超声检验方法1本标准是按照已经确定名称E-213发行的;名称后的数字表示最先采用的年份,如果修正,则是最后修正的年份。

括号中的数字表示最后重新批准的年份。

上标ε表示上次修正或者重新批准后的编排更改。

1. 范围1.1 本规程2规定了金属管及管状材料超声波检验缺陷的方法。

本规程适用的超声波检验方法包括:脉冲反射法,可以是接触及非接触式方法(例如:如指南E 1774中所述),和斜波入射检验法。

人工槽伤是标准化设置超声波系统的主要手段,人工槽伤具有纵向和横向槽伤(按使用方规定),位于表面。

1.2 本操作规程适用于外径大约1/2英寸[12.7毫米]及以上更大的管状产品,检验参数符合并且满足第12节的要求。

本操作规程已经成功地运用于较小尺寸的管子。

管子尺寸可以由使用方按合同协议规定。

本操作规程是用来确保使用适当的波束角和波束形状,以便覆盖管子和管状材料的整个体积范围,包括较小外径-壁厚比的管材,并且在检验小直径管和薄壁管时避免假反射信号。

1.3 在附录Al中的步骤适用于核工业及其它特殊和安全应用场合的管材。

附录A2中的步骤可以用于确定螺旋扫描节距。

1.4 本规定不是验收标准,验收标准必须由使用方确定。

1.5 本操作规程中使用英寸-磅英制单位。

相应的国际单位被括在括号中,可能是近似值。

1.6 本标准内容不包括说明所有与使用有关的安全事项。

任何使用本标准的人员有责任在使用前,咨询并且制定适当的安全和健康操作规程,并且确定规程的适用性。

1本操作规程属于美国材料试验学会E07无损检验委员会的管辖范围,并且是E07.06超声波探测分会的直接责任。

最新版本于2004年1月1日批准,于2004年2月出版。

最早批准是在1963年。

上一版E 213 - 02在2002年批准。

2要了解美国机械工程师学会锅炉及压力容器标准中规定的应用规程,参看标准中相关的操作规程SE - 213。

OMAPL137评估模块技术参考手册11

OMAP-L137 评估模块技术参考手册2008 DSP 开发系统 511345-0001 Rev. A 2009年2月15日第一章 OMAP-L137 EVM介绍第一章提供了omap-l137 EVM的描述,以及它的主要特点和电路框图1.1主要特点. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . .21.2 OMAP-L137功能性概述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31.3 基本操作. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . .. . . . . . . . . . . . . . . . 3 1.4 存储区映射. . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 1.5 启动开关设置. . . . . . . . .. . . .. . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . 4 1.6 电源供应. . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . 5 1.1主要特点:OMAP-L137 EVM自成体系(独立)的开发平台,此开发平台能让用户评估和开发TI OMAP-L137处理器系列应用。

MC10使用说明书

143

模拟量电流输出(AO) 测量范围 负载电阻 精度 4 ~ 20mA

42

<350Ω 1%

70

适用性条件 外形尺寸(mm)(适用标准DIN43700) 防护等级(适用标准GB/T4208) 重量(g) 工作温度范围 温度范围 工作电源 功耗 基本模块72(W) x 124(L) x 127(H) 显示模块72(W) x 72(W) x 57(D) IP54(显示单元前面板), IP40(外壳) 300 基本模块: -10 ~ 60℃ 显示模块: -10 ~ 60℃ 5 ~ 95%(无结露) 85Vac ~ 276Vac/100Vdc ~ 250Vdc 2W

订货须知

详细见样本

6

7

perfect in form and function

神形合一,完美呈现

安装说明和接线

显示模块及其安装图

68 1

实测 SOE 分合闸 RESET THD 报警 设置

C1 C2 C3 C4 C5 C6

C1 : ID C2 : IC C3 : IB C4 : IA C5 : AGND C6 : AGND

4 4 4 5~6 6 7~8 8 ~ 11 12 ~ 28 29 ~ 41

恒久不变的品牌理念

● ● ● ●

AEG是德国技术、 德国制造的代名词, 代表着性能卓越和精密设计 AEG是全球最早将艺术设计和美学引入工业设计的品牌 “Perfekt in Form und Funktion” “神形合一, 完美呈现” 是AEG恒久不变的设计理念 AEG品牌旗下产品广泛, 涉及你生活的多个方面, 汽车、 火车、 电动工具、 电子设备到 电子仪器、 核电、 电力设备、 电机、 微电子…无不延续着品牌一贯的理念

MC14106B中文资料

MC14106B 中文资料目录元件的最大额定值 (1)MC14106B功能介绍 (1)电气特性 (3)芯片转换特性 (4)芯片应用举例 (4)应用1 按键防抖 (4)应用2 积分电路 (5)MC14106B封装信息 (6)PDIP-14封装 (6)SOIC-14封装 (7)TSSOP-14封装 (8)元件的最大额定值条件之上进行功能操作。

长期暴露在高于推荐工作条件的环境下可能会影响器件的可靠性。

表中的电压值均为对地电压。

MC14106B功能介绍MC14106B共14个引脚,其中14号引脚为VDD(+),7号引脚为VSS (-),其余引脚为输入输出引脚,1,3,5,9,11,13号引脚为输入引脚,2,4,6,8,10,12号引脚为输出引脚。

内部逻辑如图1如所示,从图1中我们可以看出,MC14106B内部共有6组相同功能施密特触发器,每组施密特触发器的逻辑如图2所示。

图1图2下面通过图3所示施密特触发器讲解其工作过程。

其工作时序如图4所示。

当输入端输入低电平(VSS)时,输出端输出高电平(V OH)。

当输入端电平变为高电平(VDD)时,输出端电平经过一小段时间后也会发生变化,变为低电平(V OL)。

当输入端电平由VDD变为VSS后,一小段时间后,输出端电平变为高电平(V OH)。

施密特触发器最重要的是以下几个参数:从输入端电平由低到高变化到50%时,至输出端电平由高到低变化变化至50%时的时间记做t PHL;从输入端电平由高到低变化到50%时,至输出端电平由低到高变化变化至50%时的时间记做t PLH。

当输出端产生下调沿时,电平从90%变化至10%所用的时间t f;当输出端产生上跳沿时,电平从10%变化至90%所用的时间t r。

这些参数主要与VDD有关,可以通过下面提供的电气特性表格查出典型值。

图3图4通过图5进一步讲解施密特触发器的工作流程。

当输入端的电平达到V T+之后,输出端电平才会发生负跳变,当输入端平超过V T+之后,即使略低于该值,输出端不会发生负跳变,直到当输入端电平低于V T-,输出端才会发生正跳变。

MC9S08AC16数据手册(中文)

苏州大学飞思卡尔嵌入式系统研发中心翻译 2009 年 11 月

1

MC9S08AC16 系列特点

MC9S08AC16 系列特点

z 消费&工业 MC9S08AC16 MC9S08AC8

z 汽车 MC9S08AW16A MC9S08AW8A

3.6.1 Stop2 模式................................................................................................................................. 23 3.6.2 Stop3 模式................................................................................................................................. 23 3.6.3 停止模式下激活 BDM 使能 ................................................................................................... 24 3.6.4 停止模式下 LVD 使能 ............................................................................................................ 24 3.6.5 停止模式下的片上外设模块 .................................................................................................. 24

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

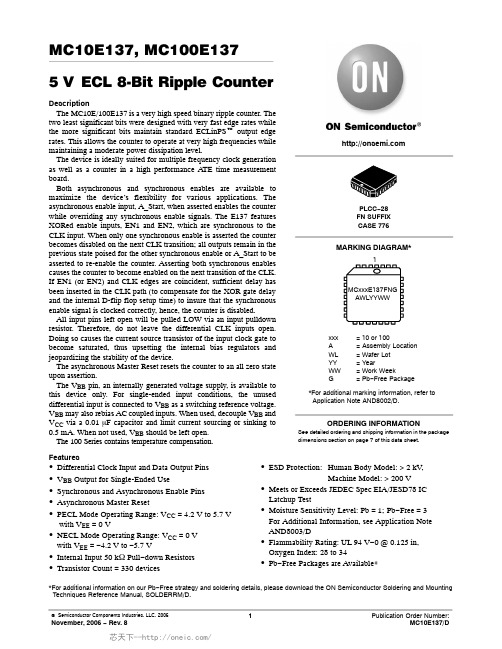

MC10E137 MC100E137

8-BIT RIPPLE COUNTER

• •• • • • •

1.8GHz Minimum Count Frequency Differential Clock Input and Data Output Pins VBB Output for Single-Ended Use Internal 75kΩ Input Pulldown Resistors Synchronous and Asynchronous Enable Pins Asynchronous Master Reset Extended 100E VEE Range of –4.2V to –5.46V

MC10E137 MC100E137

Pinout: 28-Lead PLCC (Top View)

Q7 25 A_Start EN1 EN2 VEE CLK CLK VBB 26 27 28 1 2 3 4 5 MR 6 VCCO 7 Q0 8 Q0 9 Q1 10 Q1 11 VCCO Q7 24 Q6 23 Q6 22 VCCO 21 Q5 20 Q5 19 18 17 16 15 14 13 12 Q4 Q4 VCC Q3 Q3 Q2 Q2

The device is ideally suited for multiple frequency clock generation as well as a counter in a high performance ATE time measurement board. Both asynchronous and synchronous enables are available to maximize the device’s flexibility for various applications. The asynchronous enable input, A_Start, when asserted enables the counter FN SUFFIX while overriding any synchronous enable signals. The E137 features PLASTIC PACKAGE XORed enable inputs, EN1 and EN2, which are synchronous to the CLK CASE 776-02 input. When only one synchronous enable is asserted the counter becomes disabled on the next CLK transition; all outputs remain in the previous state poised for the other synchronous enable or A_Start to be asserted to re-enable the counter. Asserting both synchronous enables causes the counter to become enabled on the next transition of the CLK. PIN NAMES If EN1 (or EN2) and CLK edges are coincident, sufficient delay has been PIN FUNCTION inserted in the CLK path (to compensate for the XOR gate delay and the internal D-flip flop setup time) to insure that the synchronous enable CLK, CLK Differential Clock Inputs signal is clocked correctly, hence, the counter is disabled. Q0-Q7, Q0-Q7 Differential Q Outputs The E137 can also be driven single-endedly utilizing the VBB output A_Start Asynchronous Enable Input supply as the voltage reference for the CLK input signal. If a single-ended EN1, EN2 Synchronous Enable Inputs signal is to be used the VBB pin should be connected to the CLK input and MR Asynchronous Master Reset bypassed to ground via a 0.01µF capacitor. VBB can only source/sink VBB Switching Refernce Output 0.5mA, therefore it should be used as a switching reference for the E137 only. All input pins left open will be pulled LOW via an input pulldown resistor. Therefore, do not leave the differential CLK inputs open. Doing so causes the current source transistor of the input clock gate to become saturated, thus upsetting the internal bias regulators and jeopardizing the stability of the device. The asynchronous Master Reset resets the counter to an all zero state upon assertion. LOGIC DIAGRAM

IIH IEE

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

0°C Symbol fCOUNT tPLH tPHL Characteristic Maximum Count Frequency Propagation Delay to Output CLK to Q0 CLK to Q1 CLK to Q2 CLK to Q3 CLK to Q4 CLK to Q5 CLK to Q6 CLK to Q7 A_Start to Q0 MR to Q0 Setup Time (EN1, EN2) Hold Time (EN1, EN2) Reset Recovery Time MR, A_Start Minimum Pulse Width CLK, MR, A_Start Minimum Input Swing (CLK) Com Mode Range (CLK) Rise/Fall Times Q0,Q1 Q2 to Q7 Min 1800 1300 1600 1950 2275 2625 2950 3250 3575 950 700 0 300 400 400 0.25 –0.4 150 275 1.0 –2.0 400 600 Typ 2200 1700 2025 2425 2750 3125 3450 3775 4075 1325 1000 –150 150 200 2150 2500 2925 3350 3750 4150 4450 4800 1700 1300 Max Min 1800 1300 1600 1950 2275 2625 2950 3250 3575 950 700 0 300 400 400 0.25 –0.4 150 275 1.0 –2.0 400 600 25°C Typ 2200 1700 2050 2450 2775 3150 3475 3800 4125 1325 1000 –150 150 200 2150 2500 2925 3350 3750 4150 4450 4800 1700 1300 Max Min 1800 1350 1650 2025 2350 2700 3050 3375 3700 950 700 0 300 400 400 0.25 –0.4 150 275 1.0 –2.0 400 600 V V ps 20%–80% Note 1 85°C Typ 2200 1750 2100 2500 2850 3225 3550 3925 4250 1325 1000 –150 150 200 ps 2200 2550 3000 3425 3825 4250 4600 4950 1700 1300 ps ps ps Max Unit MHz ps Condition

Stop Asynch Start

Count

Stop Synch Start

Stop Count

Reset

Z = Low to High Transition

MOTOROLA

2–2

ECLinPS and ECLinPS Lite DL140 — Rev 4

元器件交易网

MC10E137 MC100E137

* All VCC and VCCO pins are tied together on the die.

SEQUENTIAL TRUTH TABLE

Function Reset Count EN1 X L L L H H H H L L L L L L H H H H H L L L X EN2 X L L L L L L L L L L L H H H H H L L L L L X A_Start X L L L L L H H H L L L L L L L L L L L L L X MR H L L L L L L L L L L L L L L L L L L L L L H CLK X Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z X Q7 L L L L L L L L L L L L L L L L L L L L L L L Q6 L L L L L L L L L L L L L L L L L L L L L L L Q5 L L L L L L L L L L L L L L L L L L L L L L L Q4 L L L L L L L L L L L L L L L L L L L L L L L Q3 L L L L L L L L L L H H H H H H H H H H H H L Q2 L L L L L L H H H H L L L L L L H H H H H H L Q1 L L H H H H L L H H L L L L H H L L L L H H L Q0 L H L H H H L H L H L H H H L H L L L H L H L