M48T02中文资料

4CMC331M450AK8中文资料

2,000 h at 85 °C and full load∆ Capacitance ±20% ESR 200% of limit DCL 100% of limit3,000 h at 85 ºC with rated voltage∆ Capacitance ±10% ESR 200% of limit DCL 100% of limit500 h at 85 °C, capacitance, ESR and DCL, initial requirements10 to 55 Hz, 0.06” and 10 g max, 2 h each planeThe Type 4CMC is the PC-mount version of the high-capacitance Type DCMC screw-terminal capacitor and has about 50% more capacitance per can size through 250 V. It’s for bus filtering applications where more capacitance or smaller can size is important like welders and energy storage. It’s a much better value than a large snap-in capacitor. Its extended cathode foil assures cool operation with heatflow from the capacitor element to the can in all mounting orientations.Highlights• Much better value than large snap-in capacitor • Ripple Currents to > 50 amps at 55 °C • 3-leads for reverse proof, strong mounting • Printed-circuit mounting version of DCMC • Thermal-Pak™ extended cathode constructionSpecificationsOperating Temperature:Rated Voltage:Capacitance:Capacitance Tolerance:DC Leakage Current:Cold Impedance:Ripple Current Multipliers:EIA Ripple Life: Life Test:Shelf Life Test: Vibration: Best Value Printed Circuit Mount TypeFrequency–40 °C to +85 °C 16 to 500 Vdc210 µF to 420,000 µF ± 20%± 20%≤ 6 √CV µA, 6 max, 5 min.–20 °C multiple of 25 °C Z ≤ 8 for 16 to 50 V, 4 for 63 to 100 V, 3 for 160 V & up Ambient Temperature45 °C 55 °C 65 °C 75 °C 85 °C 2.002.001.731.411.0050 Hz 60 Hz 120 Hz 360 Hz 1 kHz 5 kHk-10 kHz & up6.3 to 50 V 0.800.85 1.00 1.05 1.08 1.08 1.0863 to 250 V 0.800.83 1.00 1.15 1.20 1.20 1.20300 to 5000.780.801.001.301.401.401.40Complies with the EU Directive 2002/95/EC requirement restricting the use of Lead (Pb), Mercury (Hg), Cadmium (Cd), Hexavalent chromium (Cr(VI)), PolyBrominated Biphenyls (PBB) and PolyBrominated Diphenyl Ethers (PBDE).Outline DrawingsCase DimensionsPart Numbering System4CMCType 8InsulationAKCase Code100Voltage M Tolerance382Capacitance(blank) = StraightLeads0 = Bare can 8 = PVC and Standoffs9 = Polyester and Standoffs6R3 = 6.3 V 063 = 63 V M = ±20%T = –10% +50% U = –10 +75% 382 = 3800 µF 212 = 2100 µF100 = 100 VCase InchesMillimeters Code D ± .031 L MAX C ± .015 S ± .031 E ± .031 F ± .015 D ± .78 L MAX C ± .78 S ± .78 E ± .78 F ± .38AK 1.375 1.750.500.1750.250.5534.9344.4512.70 4.45 6.3513.97 AA 1.375 2.250.500.1750.250.5534.9357.1512.70 4.45 6.3513.97 AH 1.375 2.750.500.1750.250.5534.9869.8512.70 4.45 6.3513.97 AB 1.375 3.250.500.1750.250.5534.9382.5512.70 4.45 6.3513.97 AJ 1.375 3.750.500.1750.250.5534.9395.2512.70 4.45 6.3513.97 AC 1.375 4.250.500.1750.250.5534.93107.9512.70 4.45 6.3513.97 AD 1.375 4.750.500.1750.250.5534.93120.6512.70 4.45 6.3513.97 AE 1.375 5.250.500.1750.250.5534.93133.3512.70 4.45 6.3513.97 AF 1.375 5.750.500.1750.250.5534.93146.0512.70 4.45 6.3513.97 EA 1.75 2.250.700.3750.350.9044.4557.1517.789.538.8922.86 EH 1.75 2.750.700.3750.350.9044.4569.8517.789.538.8922.86 EB 1.75 3.250.700.3750.350.9044.4582.5517.789.538.8922.86 EJ 1.75 3.750.700.3750.350.9044.4595.2517.789.538.8922.86 EC 1.75 4.250.700.3750.350.9044.45107.9517.789.538.8922.86 ED 1.75 4.750.700.3750.350.9044.45120.6517.789.538.8922.86 EE 1.75 5.250.700.3750.350.9044.45133.3517.789.538.8922.86 EF 1.75 5.750.700.3750.350.9044.45146.0517.789.538.8922.86 BA 2.00 2.250.800.4250.40 1.0050.8057.1520.3210.8010.1625.40 BH 2.00 2.750.800.4250.40 1.0050.8069.8520.3210.8010.1625.40 BB 2.00 3.250.800.4250.40 1.0050.8082.5520.3210.8010.1625.40 BJ 2.00 3.750.800.4250.40 1.0050.8095.2520.3210.8010.1625.40 BC 2.00 4.250.800.4250.40 1.0050.80107.9520.3210.8010.1625.40 BD 2.00 4.750.800.4250.40 1.0050.80120.6520.3210.8010.1625.40 BE 2.00 5.250.800.4250.40 1.0050.80133.2520.3210.8010.1625.40 BF2.005.750.800.4250.401.0050.80146.0520.3210.8010.1625.40RatingsESR Max. 25 ºC 120 Hz 20 kHz (mΩ) (mΩ)Ripple Amps,85 ºC 120 Hz 20 kHz (A) (A)Nominal Size D X L (in)ESR Max. 25 ºC 120 Hz 20 kHz (mΩ) (mΩ)Ripple Amps,85 ºC 120 Hz 20 kHz (A) (A)Nominal Size D X L (in)Cap.(µF)Catalog Part NumberCap.(µF)Catalog Part Number 16 Vdc (20 Vdc Surge)2000004CMC204M016AF8 10.38.216.919.0 1 3/8 X 5 3/4 330004CMC333M016AK8 34.227.2 5.7 6.4 1 3/8 X 1 3/4 2200004CMC224M016EC8 1310.315.217 1 3/4 X 4 1/4 550004CMC553M016AA821.216.98.49.4 1 3/8 X 2 1/4 2400004CMC244M016BJ8 11.79.315.617.5 2 X 3 3/4 770004CMC773M016AH8 18.314.69.310.4 1 3/8 X 2 3/4 2500004CMC254M016ED8 11.59.21719 1 3/4 X 4 3/4 790004CMC793M016EA8 23.018.39.210.4 1 3/4 X 2 1/4 2800004CMC284M016EE8 10.58.418.921.2 1 3/4 X 5 1/4 990004CMC993M016AB814.811.811.112.4 1 3/8 X 3 1/4 2800004CMC284M016BC8 11.49.115.917.8 2 X 4 1/4 1100004CMC114M016EH8 17.413.811.412.7 1 3/4 X 2 3/4 3100004CMC314M016EF8 9.77.721.023.5 1 3/4 X 5 3/4 1200004CMC124M016AJ8 12.810.212.514.0 1 3/8 X 3 3/4 3300004CMC334M016BD8 10.78.516.919 2 X 4 3/4 1200004CMC124M016BA817.714.110.011.2 2 X 2 1/4 3700004CMC374M016BE8 10.08.018.120.3 2 X 5 1/4 1400004CMC144M016AC8 12.59.913.315.0 1 3/8 X 4 1/4 4200004CMC424M016BF89.07.219.822.22 X 5 3/41400004CMC144M016EB815.812.612.914.4 1 3/4 X 3 1/4 25 Vdc (30 Vdc Surge) 1500004CMC154M016BH8 14.511.611.913.3 2 X 2 3/4 220004CMC223M025AK8 63.250.4 4.2 4.7 1 3/8 X 1 3/4 1600004CMC164M016AD8 11.59.114.516.2 1 3/8 X 4 3/4 370004CMC373M025AA8 23.919.17.98.8 1 3/8 X 2 1/4 1800004CMC184M016AE8 10.88.615.817.7 1 3/8 X 5 1/4 520004CMC523M025AH8 20.616.48.89.8 1 3/8 X 2 3/4 1800004CMC184M016EJ8 15.012.013.615.3 1 3/4 X 3 3/4 540004CMC543M025EA8 22.918.39.310.4 1 3/4 X 2 1/4 1900004CMC194M016BB812.39.813.615.22 X3 1/4670004CMC673M025AB816.613.210.511.71 3/8 X 3 1/4Typical Performance CurvesESR Max.25 ºC 120 Hz 20 kHz (mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)ESR Max.25 ºC120 Hz 20 kHz(mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)Cap. (µF)Catalog PartNumberCap.(µF)Catalog PartNumber780004CMC783M025EH8 19.0015.1010.9012.20 1 3/4 X 2 3/4 50 Vdc (65 Vdc Surge)820004CMC823M025AJ8 14.3011.4011.8013.20 1 3/8 X 3 3/4 100004CMC103M050AK8 44.3035.30 5.00 5.70 1 3/8 X 1 3/4 830004CMC833M025BA8 19.0015.2010.9012.20 2 X 2 1/4 170004CMC173M050AA8 27.3021.807.408.20 1 3/8 X 2 1/4 970004CMC973M025AC8 13.9011.1012.6014.20 1 3/8 X 4 1/4 240004CMC243M050AH8 23.4018.708.209.20 1 3/8 X 2 3/4 1000004CMC104M025BH8 15.5012.4013.0014.60 2 X 2 3/4 270004CMC273M050EA8 28.2022.508.409.40 1 3/4 X 2 1/4 1000004CMC1003M025EB8 17.3013.8012.3013.80 1 3/4 X 3 1/4 310004CMC313M050AB8 18.9015.109.8011.00 1 3/8 X 3 1/4 1100004CMC114M025AD8 12.8010.2013.8015.40 1 3/8 X 4 3/4 330004CMC333M050BA8 27.9022.309.0010.10 2 X 2 1/4 1200004CMC124M025AE8 11.909.5015.0016.80 1 3/8 X 5 1/4 360004CMC363M050EH8 21.2016.9010.3011.50 1 3/4 X 2 3/4 1200004CMC124M025EJ8 16.4013.0013.1014.60 1 3/4 X 3 3/4 380004CMC383M050AJ8 16.2013.0011.1012.40 1 3/8 X 3 3/4 1300004CMC134M025BB8 12.7010.1015.2017.00 2 X 3 1/4 390004CMC393M050EB8 20.3016.2011.3012.70 1 3/4 X 3 1/4 1400004CMC144M025AF8 11.409.1016.1018.00 1 3/8 X 5 3/4 450004CMC453M050AC8 15.7012.5011.9013.30 1 3/8 X 4 1/4 1500004CMC154M025EC8 14.1011.2014.6016.30 1 3/4 X 4 1/4 470004CMC473M050AD8 14.9011.9012.7014.30 1 3/8 X 4 3/4 1600004CMC164M025BJ8 12.5010.0017.1019.20 2 X 3 3/4 470004CMC473M050BH8 19.6015.6011.6013.00 2 X 2 3/4 1700004CMC174M025ED8 12.5010.0016.3018.30 1 3/4 X 4 3/4 480004CMC483M050EJ8 19.2015.3012.1013.50 1 3/4 X 3 3/4 1900004CMC194M025EE8 11.309.0018.2020.40 1 3/4 X 5 1/4 530004CMC533M050AE8 13.9011.0013.9015.60 1 3/8 X 5 1/4 1900004CMC194M025BC8 12.209.7017.4019.50 2 X 4 1/4 560004CMC563M050BB8 16.3013.0013.4015.00 2 X 3 1/4 2100004CMC214M025EF8 10.508.3020.2022.60 1 3/4 X 5 3/4580004CMC583M050EC8 16.5013.1013.5015.10 1 3/4 X 4 1/4 2200004CMC224M025BD8 11.409.1018.6020.80 2 X 4 3/4600004CMC603M050AF8 13.2010.5015.0016.80 1 3/8 X 5 3/4 2500004CMC254M025BE8 10.608.5019.9022.30 2 X 5 1/4670004CMC673M050ED8 14.5011.6015.1017.00 1 3/4 X 4 3/4 2800004CMC284M025BF8 9.607.6021.8024.40 2 X 5 3/4680004CMC683M050BJ8 15.0012.0015.6017.50 2 X 3 3/435 Vdc (40 Vdc Surge) 760004CMC763M050EE8 13.1010.5016.9018.90 1 3/4 X 5 1/4 150004CMC153M035AK8 63.2050.40 4.20 4.70 1 3/8 X 1 3/4820004CMC823M050BC8 14.3011.4016.1018.00 2 X 4 1/4 250004CMC253M035AA8 23.9019.107.908.80 1 3/8 X 2 1/4850004CMC853M050EF8 12.109.6018.8021.10 1 3/4 X 5 3/4 350004CMC353M035AH8 20.6016.408.809.80 1 3/8 X 2 3/4910004CMC913M050BD8 12.7010.1017.6019.80 2 X 4 3/4 380004CMC383M035EA8 22.7018.109.3010.40 1 3/4 X 2 1/41000004CMC104M050BE8 11.809.4019.0021.30 2 X 5 1/4 450004CMC453M035AB8 16.6013.2010.5011.70 1 3/8 X 3 1/41200004CMC124M050BF8 10.508.4020.7023.20 2 X 5 3/4 520004CMC523M035EH8 19.0015.1010.9012.20 1 3/4 X 2 3/463 Vdc (75 Vdc Surge)550004CMC553M035AJ8 14.3011.4011.8013.20 1 3/8 X 3 3/475004CMC752M063AK8 44.1035.10 5.10 5.70 1 3/8 X 1 3/4 560004CMC563M035BA8 19.0015.2010.9012.20 2 X 2 1/4120004CMC123M063AA8 26.8021.407.408.30 1 3/8 X 2 1/4 650004CMC653M035AC8 13.9011.1012.6014.20 1 3/8 X 4 1/4160004CMC163M063EA8 28.2022.508.309.30 1 3/4 X 2 1/4 670004CMC673M035EB8 17.3013.8012.3013.80 1 3/4 X 3 1/4160004CMC163M063AH8 23.5018.808.209.20 1 3/8 X 2 3/4 680004CMC683M035BH8 15.5012.4013.0014.60 2 X 2 3/4210004CMC213M063AB8 18.7014.909.9011.10 1 3/8 X 3 1/4 750004CMC753M035AD8 12.8010.2013.8015.40 1 3/8 X 4 3/4220004CMC223M063EH8 21.2016.9010.3011.50 1 3/4 X 2 3/4 830004CMC833M035EJ8 16.4013.0013.1014.60 1 3/4 X 3 3/4260004CMC263M063AJ8 16.9013.5010.9012.20 1 3/8 X 3 3/4 840004CMC843M035AE8 11.909.5015.2017.10 1 3/8 X 5 1/4260004CMC263M063BA8 27.7022.109.0010.10 2 X 2 1/4 870004CMC873M035BB8 12.7010.1015.2017.00 2 X 3 1/4290004CMC293M063EB8 20.9016.7011.2012.50 1 3/4 X 3 1/4 930004CMC933M035AF8 11.409.1016.1018.10 1 3/8 X 5 3/4300004CMC303M063AC8 17.3013.8011.3012.70 1 3/8 X 4 1/4 1000004CMC104M035EC8 14.1011.2014.6016.30 1 3/4 X 4 1/4330004CMC333M063BH8 19.5015.5011.6013.00 2 X 2 3/4 1100004CMC114M035BJ8 12.5010.0017.1019.20 2 X 3 3/4350004CMC353M063AD8 15.7012.5012.4013.90 1 3/8 X 4 3/4 1100004CMC114M035ED8 12.5010.0016.3018.30 1 3/4 X 4 3/4360004CMC363M063EJ8 20.0016.0011.8013.20 1 3/4 X 3 3/4 1300004CMC134M035EE8 11.309.0018.2020.40 1 3/4 X 5 1/4380004CMC383M063AE8 14.5011.5013.8015.50 1 3/8 X 5 1/4 1300004CMC134M035BC8 12.209.7017.4019.50 2 X 4 1/4430004CMC433M063EC8 17.2013.7013.2014.80 1 3/4 X 4 1/4 1400004CMC144M035EF8 10.508.3020.2022.60 1 3/4 X 5 3/4440004CMC443M063AF8 13.7010.9014.7016.50 1 3/8 X 5 3/4 1500004CMC154M035BD8 11.409.1018.6020.80 2 X 4 3/4470004CMC473M063BB8 16.2012.9013.4015.00 2 X 3 1/4 1700004CMC174M035BE8 10.608.5020.0022.40 2 X 5 1/4500004CMC503M063ED8 15.2012.2014.8016.60 1 3/4 X 4 3/4 1900004CMC194M035BF8 9.607.6021.7024.40 2 X 5 3/4530004CMC533M063BJ8 15.1012.0015.6017.40 2 X 3 3/4570004CMC573M063EE8 13.8011.0016.5018.50 1 3/4 X 5 1/4ESR Max.25 ºC 120 Hz 20 kHz (mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)ESR Max.25 ºC120 Hz 20 kHz(mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)Cap. (µF)Catalog PartNumberCap.(µF)Catalog PartNumber590004CMC593M063BC8 14.5011.5016.0017.90 2 X 4 1/4220004CMC223M100AF8 20.1016.0012.1013.60 1 3/8 X 5 3/4 640004CMC643M063EF8 12.7010.1018.4020.60 1 3/4 X 5 3/4220004CMC223M100EC8 21.9017.5011.7013.10 1 3/4 X 4 1/4 690004CMC693M063BD8 12.8010.2017.6019.70 2 X 4 3/4260004CMC263M100ED8 19.3015.4013.2014.70 1 3/4 X 4 3/4 790004CMC793M063BE8 11.609.2019.1021.40 2 X 5 1/4260004CMC263M100BJ8 23.6018.8012.5013.90 2 X 3 3/4 890004CMC893M063BF8 10.708.5020.6023.10 2 X 5 3/4300004CMC303M100EE8 17.3013.8014.7016.50 1 3/4 X 5 1/480 Vdc (100 Vdc Surge) 300004CMC303M100BC8 20.2016.1013.5015.20 2 X 4 1/4 56004CMC562M080AK8 59.6047.50 4.40 4.90 1 3/8 X 1 3/4330004CMC333M100EF8 15.8012.6016.4018.40 1 3/4 X 5 3/4 85004CMC852M080AA8 36.2028.80 6.407.20 1 3/8 X 2 1/4350004CMC353M100BD8 17.8014.2014.9016.70 2 X 4 3/4 120004CMC123M080EA8 38.4030.607.208.00 1 3/4 X 2 1/4400004CMC403M100BE8 16.1012.8016.3018.20 2 X 5 1/4 120004CMC123M080AH8 31.5025.107.107.90 1 3/8 X 2 3/4450004CMC453M100BF8 14.7011.7017.5019.60 2 X 5 3/4 150004CMC153M080AB8 31.6025.207.608.50 1 3/8 X 3 1/4160 Vdc (200 Vdc Surge)170004CMC173M080EH8 34.0027.108.109.10 1 3/4 X 2 3/415004CMC152M160AK8 81.7065.20 3.70 4.20 1 3/8 X 1 3/4 180004CMC183M080BA8 32.8026.108.309.30 2 X 2 1/425004CMC252M160AA8 51.8041.30 5.30 6.00 1 3/8 X 2 1/4 190004CMC193M080AJ8 25.2020.108.9010.00 1 3/8 X 3 3/435004CMC352M160AH8 37.5029.90 6.507.30 1 3/8 X 2 3/4 220004CMC223M080AC8 20.9016.7010.3011.50 1 3/8 X 4 1/437004CMC372M160EA8 47.1037.50 6.10 6.90 1 3/4 X 2 1/4 220004CMC223M080EB8 30.5024.309.3010.40 1 3/4 X 3 1/445004CMC452M160AB8 29.6023.607.808.80 1 3/8 X 3 1/4 230004CMC233M080BH8 23.1018.4010.7011.90 2 X 2 3/448004CMC482M160BA8 35.4028.207.208.10 2 X 2 1/4 260004CMC263M080AD8 19.1015.2011.2012.60 1 3/8 X 4 3/452004CMC522M160EH8 29.0023.108.309.30 1 3/4 X 2 3/4 270004CMC273M080EJ8 25.1020.0010.5011.80 1 3/4 X 3 3/455004CMC552M160AJ8 23.5018.7029.3032.80 1 3/8 X 3 3/4 290004CMC293M080AE8 17.7014.1012.5014.00 1 3/8 X 5 1/466004CMC662M160AC8 20.2016.1010.5011.70 1 3/8 X 4 1/4 300004CMC303M080BB8 19.2015.3012.3013.80 2 X 3 1/468004CMC682M160EB8 22.5017.9010.2011.50 1 3/4 X 3 1/4 320004CMC323M080AF8 16.7013.3013.3014.90 1 3/8 X 5 3/471004CMC712M160AD8 18.6014.8011.4012.80 1 3/8 X 4 3/4 320004CMC323M080EC8 21.5017.1011.8013.20 1 3/4 X 4 1/471004CMC712M160BH8 26.5021.209.0010.10 2 X 2 3/4 370004CMC373M080BJ8 18.0014.3014.3016.00 2 X 3 3/480004CMC802M160AE8 16.8013.4012.6014.20 1 3/8 X 5 1/4 370004CMC373M080ED8 18.9015.1013.3014.90 1 3/4 X 4 3/483004CMC832M160EJ8 18.5014.7011.7013.10 1 3/4 X 3 3/4 430004CMC433M080BC8 15.9012.6015.3017.10 2 X 4 1/490004CMC902M160AF8 19.2015.3012.4013.90 1 3/8 X 5 3/4 430004CMC433M080EE8 17.0013.6014.8016.60 1 3/4 X 5 1/493004CMC932M160BB8 20.6016.4010.8012.10 2 X 3 1/4 480004CMC483M080EF8 15.6012.4016.6018.60 1 3/4 X 5 3/4100004CMC1002M160EC8 15.8012.6013.1014.60 1 3/4 X 4 1/4 500004CMC503M080BD8 13.6010.8017.1019.10 2 X 4 3/4110004CMC113M160BJ8 16.9013.5013.3014.90 2 X 3 3/4 580004CMC583M080BE8 12.209.7018.6020.90 2 X 5 1/4120004CMC123M160ED8 13.9011.1014.7016.50 1 3/4 X 4 3/4 650004CMC653M080BF8 11.208.9020.1022.50 2 X 5 3/4130004CMC133M160EE8 12.509.9016.5018.40 1 3/4 X 5 1/4 100 Vdc (125 Vdc Surge) 130004CMC133M160BC8 14.5011.6014.5016.20 2 X 4 1/4 38004CMC382M100AK8 58.6046.70 4.40 4.90 1 3/8 X 1 3/4150004CMC153M160EF8 11.409.1018.4020.60 1 3/4 X 5 3/4 63004CMC632M100AA8 35.6028.30 6.507.20 1 3/8 X 2 1/4160004CMC163M160BD8 12.8010.2015.9017.80 2 X 4 3/4 81004CMC812M100AH8 32.8026.20 2.20 2.50 1 3/8 X 2 3/4180004CMC183M160BE8 11.509.2017.4019.50 2 X 5 1/4 82004CMC822M100EA8 39.2031.207.107.90 1 3/4 X 2 1/4200004CMC203M160BF8 10.508.4018.8021.00 2 X 5 3/4 100004CMC103M100AB8 32.9026.207.408.30 1 3/8 X 3 1/4200 Vdc (250 Vdc Surge)110004CMC113M100BA8 35.9028.707.908.90 2 X 2 1/412004CMC122M200AK8 105.2060.40 3.10 4.10 1 3/8 X 1 3/4 120004CMC123M100EH8 34.7027.708.009.00 1 3/4 X 2 3/419004CMC192M200AA8 66.6038.20 4.50 5.90 1 3/8 X 2 1/4 130004CMC133M100AJ8 31.7025.307.908.90 1 3/8 X 3 3/427004CMC272M200AH8 48.0027.60 5.407.20 1 3/8 X 2 3/4 150004CMC153M100EB8 31.1024.809.2010.30 1 3/4 X 3 1/427004CMC272M200EA8 60.0034.40 5.307.00 1 3/4 X 2 1/4 150004CMC153M100AC8 27.4021.800.90 1.10 1 3/8 X 4 1/435004CMC352M200AB8 37.8021.70 6.608.70 1 3/8 X 3 1/4 160004CMC163M100BH8 26.4021.0010.0011.20 2 X 2 3/435004CMC352M200BA8 44.2030.70 6.607.90 2 X 2 1/4 170004CMC173M100AD8 24.2019.3010.0011.20 1 3/8 X 4 3/437004CMC372M200EH8 38.1021.90 6.909.10 1 3/4 X 2 3/4 190004CMC193M100EJ8 25.6020.4010.4011.70 1 3/4 X 3 3/443004CMC432M200AJ8 29.9017.207.8010.20 1 3/8 X 3 3/4 200004CMC203M100AE8 21.9017.5011.2012.60 1 3/8 X 5 1/448004CMC482M200EB8 29.4016.908.5011.20 1 3/4 X 3 1/4 210004CMC213M100BB8 22.9018.3011.3012.60 2 X 3 1/450004CMC502M200BH8 33.1023.008.209.80 2 X 2 3/4ESR Max.25 ºC 120 Hz 20 kHz (mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)ESR Max.25 ºC120 Hz 20 kHz(mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)Cap. (µF)Catalog PartNumberCap.(µF)Catalog PartNumber51004CMC512M200AC8 25.7014.708.8011.70 1 3/8 X 4 1/416004CMC162M300AB8 82.7047.50 4.80 6.30 1 3/8 X 3 1/4 58004CMC582M200AD8 22.6013.009.8012.90 1 3/8 X 4 3/418004CMC182M300EH8 99.2056.90 4.80 6.30 1 3/4 X 2 3/4 59004CMC592M200EJ8 24.1013.809.7012.70 1 3/4 X 3 3/419004CMC192M300AJ8 68.0039.00 5.607.40 1 3/8 X 3 3/4 66004CMC662M200AE8 20.3011.6010.9014.40 1 3/8 X 5 1/422004CMC222M300BH8 67.1037.40 6.308.40 2 X 2 3/4 68004CMC682M200BB8 25.6017.809.8011.80 2 X 3 1/423004CMC232M300AC8 57.9033.20 6.408.40 1 3/8 X 4 1/4 71004CMC712M200EC8 20.5011.8010.8014.30 1 3/4 X 4 1/423004CMC232M300EB8 76.1043.70 5.807.70 1 3/4 X 3 1/4 74004CMC742M200AF8 23.1013.3010.7014.20 1 3/8 X 5 3/426004CMC262M300AD8 50.6029.007.109.40 1 3/8 X 4 3/4 81004CMC812M200BJ8 21.0014.6012.2014.60 2 X 3 3/429004CMC292M300AE8 45.0025.807.8010.30 1 3/8 X 5 1/4 82004CMC822M200ED8 17.9010.3012.2016.10 1 3/4 X 4 3/429004CMC292M300BB8 51.6028.707.6010.20 2 X 3 1/4 93004CMC932M200EE8 16.009.2013.7018.10 1 3/4 X 5 1/429004CMC292M300EJ8 61.9035.50 6.808.90 1 3/4 X 3 3/4 95004CMC952M200BC8 19.1013.3012.8015.40 2 X 4 1/433004CMC332M300AF8 50.7029.107.6010.10 1 3/8 X 5 3/4 100004CMC103M200EF8 14.508.3015.4020.30 1 3/4 X 5 3/435004CMC352M300EC8 52.2030.007.7010.20 1 3/4 X 4 1/4 110004CMC113M200BD8 15.7010.9014.6017.50 2 X 4 3/436004CMC362M300BJ8 51.2028.508.1010.80 2 X 3 3/4 120004CMC123M200BE8 14.109.8016.0019.20 2 X 5 1/440004CMC402M300ED8 45.3026.008.6011.40 1 3/4 X 4 3/4 140004CMC143M200BF8 12.808.9017.3020.80 2 X 5 3/443004CMC432M300BC8 43.3024.109.2012.30 2 X 4 1/4 250 Vdc (300 Vdc Surge)46004CMC462M300EE8 40.1023.009.5012.60 1 3/4 X 5 1/4 8904CMC891M250AK8 137.0078.60 2.60 3.40 1 3/8 X 1 3/449004CMC492M300BD8 38.0021.2010.2013.70 2 X 4 3/4 15004CMC152M250AA8 86.5049.70 3.70 4.90 1 3/8 X 2 1/451004CMC512M300EF8 36.0020.6010.4013.70 1 3/4 X 5 3/4 19004CMC192M250EA8 68.7039.40 4.80 6.30 1 3/4 X 2 1/457004CMC572M300BE8 33.3018.5011.3015.10 2 X 5 1/4 21004CMC212M250AH8 62.3035.70 4.50 6.00 1 3/8 X 2 3/464004CMC642M300BF8 29.9016.7012.3016.50 2 X 5 3/4 27004CMC272M250BA8 54.2037.60 5.807.00 2 X 2 1/4350 Vdc (400 Vdc Surge)27004CMC272M250AB8 48.8028.00 5.507.20 1 3/8 X 3 1/44304CMC431M350AK8 264.10151.60 2.10 2.80 1 3/8 X 1 3/4 28004CMC282M250EH8 47.8027.40 6.108.10 1 3/4 X 2 3/47104CMC711M350AA8 158.9091.20 3.10 4.00 1 3/8 X 2 1/4 32004CMC322M250AJ8 38.6022.10 6.508.50 1 3/8 X 3 3/410004CMC102M350EA8 119.2068.40 4.10 5.40 1 3/4 X 2 1/4 37004CMC372M250EB8 36.8021.107.6010.00 1 3/4 X 3 1/410004CMC102M350AH8 113.9065.40 3.70 4.90 1 3/8 X 2 3/4 38004CMC382M250BH8 40.5028.107.208.70 2 X 2 3/412004CMC122M350BA8 98.1054.60 4.80 6.40 2 X 2 1/4 39004CMC392M250AC8 33.0018.907.409.70 1 3/8 X 4 1/413004CMC132M350EH8 105.1060.30 4.60 6.10 1 3/4 X 2 3/4 44004CMC442M250AD8 29.0016.608.2010.80 1 3/8 X 4 3/413004CMC132M350AB8 89.0051.10 4.50 6.00 1 3/8 X 3 1/4 45004CMC452M250EJ8 30.1017.308.6011.40 1 3/4 X 3 3/416004CMC162M350BH8 71.8040.00 6.008.10 2 X 2 3/4 50004CMC502M250AE8 25.9014.909.1012.00 1 3/8 X 5 1/416004CMC162M350AJ8 73.2042.00 5.20 6.90 1 3/8 X 3 3/4 50004CMC502M250BB8 31.2021.708.7010.40 2 X 3 1/417004CMC172M350EB8 80.6046.30 5.707.50 1 3/4 X 3 1/4 54004CMC542M250EC8 25.5014.709.7012.80 1 3/4 X 4 1/418004CMC182M350AC8 62.3035.80 6.007.90 1 3/8 X 4 1/4 56004CMC562M250AF8 29.4016.909.0011.90 1 3/8 X 5 3/421004CMC212M350BB8 55.1030.707.309.70 2 X 3 1/4 62004CMC622M250BJ8 25.5017.7010.7012.90 2 X 3 3/421004CMC212M350AD8 54.4031.20 6.708.80 1 3/8 X 4 3/4 63004CMC632M250ED8 22.3012.8011.0014.50 1 3/4 X 4 3/421004CMC212M350EJ8 65.5037.60 6.508.60 1 3/4 X 3 3/4 72004CMC722M250EE8 19.8011.4012.3016.30 1 3/4 X 5 1/424004CMC242M350AE8 48.3027.707.409.80 1 3/8 X 5 1/4 73004CMC732M250BC8 21.7015.1011.7014.00 2 X 4 1/425004CMC252M350EC8 55.3031.707.409.70 1 3/4 X 4 1/4 81004CMC812M250EF8 18.0010.3013.8018.30 1 3/4 X 5 3/426004CMC262M350BJ8 47.9026.708.7011.70 2 X 3 3/4 85004CMC852M250BD8 19.0013.2012.9015.50 2 X 4 3/427004CMC272M350AF8 54.5031.307.409.70 1 3/8 X 5 3/4 97004CMC972M250BE8 17.0011.8014.2017.00 2 X 5 1/429004CMC292M350ED8 47.9027.508.3011.00 1 3/4 X 4 3/4 110004CMC113M250BF8 15.4010.7015.4018.40 2 X 5 3/431004CMC312M350BC8 45.7025.509.0012.10 2 X 4 1/4 300 Vdc (350 Vdc Surge) 33004CMC332M350EE8 42.4024.309.4012.40 1 3/4 X 5 1/4 5204CMC521M300AK8 245.00141.00 2.20 2.90 1 3/8 X 1 3/436004CMC362M350BD8 40.1022.409.9013.30 2 X 4 3/4 8704CMC871M300AA8 148.0084.70 3.10 4.10 1 3/8 X 2 1/437004CMC372M350EF8 38.0021.8010.6014.00 1 3/4 X 5 3/4 12004CMC122M300AH8 106.0060.70 4.00 5.30 1 3/8 X 2 3/442004CMC422M350BE8 35.1019.6011.0014.70 2 X 5 1/4 13004CMC132M300EA8 111.0063.80 4.20 5.50 1 3/4 X 2 1/447004CMC472M350BF8 31.6017.6012.0016.00 2 X 5 3/4 16004CMC162M300BA8 93.2051.90 5.00 6.70 2 X 2 1/4ESR Max.25 ºC 120 Hz 20 kHz (mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)ESR Max.25 ºC120 Hz 20 kHz(mΩ) (mΩ)Ripple Amps,85 ºC120 Hz 20 kHz(A) (A)NominalSizeD X L(in)Cap. (µF)Catalog PartNumberCap.(µF)Catalog PartNumber400 Vdc (450 Vdc Surge) 15004CMC152M450BB8 75.9042.20 5.807.80 2 X 3 1/43204CMC321M400AK2B 382.00195.00 1.70 2.40 1 3/8 X 1 3/415004CMC152M450AE8 61.8031.50 5.708.00 1 3/8 X 5 1/4 5904CMC591M400AA2B 212.00108.00 2.60 3.70 1 3/8 X 2 1/415004CMC152M450EJ8 75.1038.30 5.708.00 1 3/4 X 3 3/4 8004CMC801M400AH2B 156.0079.40 3.20 4.50 1 3/8 X 2 3/416004CMC162M450AF8 69.3035.40 5.708.00 1 3/8 X 5 3/4 8404CMC841M400EA8 154.0078.80 3.60 5.00 1 3/4 X 2 1/418004CMC182M450EC8 63.3032.30 6.509.10 1 3/4 X 4 1/4 10004CMC102M400BA8 130.0072.20 4.20 5.60 2 X 2 1/419004CMC192M450BJ8 61.7034.307.209.70 2 X 3 3/4 10004CMC102M400AB2B 119.0060.90 3.90 5.50 1 3/8 X 3 1/421004CMC212M450ED8 54.8028.007.3010.30 1 3/4 X 4 3/4 12004CMC122M400EH8 107.0054.60 4.60 6.40 1 3/4 X 2 3/422004CMC222M450BC8 52.1029.007.9010.60 2 X 4 1/4 13004CMC132M400AJ2B 96.9049.50 4.50 6.40 1 3/8 X 3 3/423004CMC232M450EE8 48.4024.708.3011.60 1 3/4 X 5 1/4 14004CMC142M400BH8 93.6052.10 5.307.10 2 X 2 3/426004CMC262M450EF8 43.5022.209.3013.00 1 3/4 X 5 3/4 15004CMC152M400EB8 87.4044.60 5.507.70 1 3/4 X 3 1/426004CMC262M450BD8 45.7025.408.7011.70 2 X 4 3/4 15004CMC152M400AC2B 81.8041.700.500.80 1 3/8 X 4 1/431004CMC312M450BE8 38.8021.609.8013.10 2 X 5 1/4 16004CMC162M400AD2B 78.6040.10 5.507.80 1 3/8 X 4 3/434004CMC342M450BF8 35.0019.5010.7014.30 2 X 5 3/4 18004CMC182M400EJ8 71.0036.20 6.308.80 1 3/4 X 3 3/4500 Vdc (550 Vdc Surge)18004CMC182M400AE2B 69.5035.40 6.208.70 1 3/8 X 5 1/42104CMC211M500AK8 487.00287.00 1.50 2.10 1 3/8 X 1 3/4 19004CMC192M400BB8 71.9040.00 6.408.50 2 X 3 1/43104CMC311M500AA8 325.00191.00 2.10 3.00 1 3/8 X 2 1/4 20004CMC202M400AF2B 77.9039.70 6.208.60 1 3/8 X 5 3/44404CMC441M500EA8 238.00140.00 2.90 4.00 1 3/4 X 2 1/4 21004CMC212M400EC8 59.9030.507.109.90 1 3/4 X 4 1/44504CMC451M500AH8 225.00133.00 2.60 3.70 1 3/8 X 2 3/4 23004CMC232M400BJ8 58.4032.507.9010.60 2 X 3 3/45604CMC561M500BA8 193.00114.00 3.40 4.60 2 X 2 1/4 25004CMC252M400ED8 51.9026.508.0011.20 1 3/4 X 4 3/45904CMC591M500AB8 173.00102.00 3.20 4.50 1 3/8 X 3 1/4 27004CMC272M400BC8 49.3027.508.7011.60 2 X 4 1/46304CMC631M500EH8 165.0097.20 3.70 5.20 1 3/4 X 2 3/4 29004CMC292M400EE8 45.8023.409.0012.70 1 3/4 X 5 1/47304CMC731M500AJ8 140.0082.60 3.80 5.30 1 3/8 X 3 3/4 32004CMC322M400EF8 41.1021.0010.2014.30 1 3/4 X 5 3/47804CMC781M500BH8 134.0078.70 4.40 5.90 2 X 2 3/4 32004CMC322M400BD8 42.8023.809.6012.90 2 X 4 3/48204CMC821M500EB8 126.0074.40 4.50 6.40 1 3/4 X 3 1/4 36004CMC362M400BE8 37.9021.1010.6014.20 2 X 5 1/48204CMC821M500AC8 125.0073.60 4.20 5.90 1 3/8 X 4 1/4 41004CMC412M400BF8 34.0018.9011.5015.40 2 X 5 3/49004CMC901M500AD8 113.0066.40 4.60 6.50 1 3/8 X 4 3/4 450 Vdc (500 Vdc Surge) 10004CMC102M500BB8 103.0060.30 5.307.10 2 X 3 1/4 3304CMC331M450AK8 281.00143.00 1.80 2.50 1 3/8 X 1 3/410004CMC102M500AE8 99.0058.50 5.207.30 1 3/8 X 5 1/4 4904CMC491M450AA8 188.0095.70 2.50 3.40 1 3/8 X 2 1/410004CMC102M500EJ8 103.0060.40 5.207.30 1 3/4 X 3 3/4 6004CMC601M450AH8 138.0070.40 3.00 4.10 1 3/8 X 2 3/411004CMC112M500AF8 114.0067.30 5.107.10 1 3/8 X 5 3/4 6904CMC691M450EA8 163.0083.30 3.30 4.60 1 3/4 X 2 1/412004CMC122M500EC8 86.4050.90 5.908.30 1 3/4 X 4 1/4 8604CMC861M450BA8 116.0064.80 4.10 5.60 2 X 2 1/413004CMC132M500BJ8 83.2049.00 6.608.90 2 X 3 3/4 8604CMC861M450AB8 106.0054.00 3.60 5.10 1 3/8 X 3 1/414004CMC142M500ED8 74.8044.00 6.709.40 1 3/4 X 4 3/4 9304CMC931M450EH8 121.0061.50 4.10 5.70 1 3/4 X 2 3/415004CMC152M500BC8 70.2041.307.309.70 2 X 4 1/4 10004CMC102M450AJ8 86.1043.90 4.20 5.90 1 3/8 X 3 3/416004CMC162M500EE8 66.0038.807.5010.60 1 3/4 X 5 1/4 11004CMC112M450BH8 98.9055.10 4.80 6.50 2 X 2 3/418004CMC182M500EF8 59.1034.808.5011.90 1 3/4 X 5 3/4 12004CMC122M450EB8 92.4047.10 5.007.00 1 3/4 X 3 1/418004CMC182M500BD8 60.7035.808.1010.80 2 X 4 3/4 12004CMC122M450AC8 72.7037.10 4.80 6.80 1 3/8 X 4 1/421004CMC212M500BE8 52.1030.709.0012.10 2 X 5 1/4 13004CMC132M450AD8 69.9035.70 5.107.20 1 3/8 X 4 3/423004CMC232M500BF8 46.9027.609.8013.20 2 X 5 3/4。

M48T59Y-70MH1E;M48T59Y-70MH6E;M48T59Y-70PC1;M48T59Y-70MH1F;中文规格书,Datasheet资料

Table 4. Write mode AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 5. Register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

lete 6

Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Obso 7

Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

List of tables

List of tables

Table 1. Signal names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 6. Alarm repeat mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

AT42QT1070中文手册

2.8 复位的类型

2.8.1

外部复位 如果需要一个外部复位逻辑线路可以使用,送入复位引脚.然而,在大多数情况下是可以接受的领带复位到Vdd.

通讯模式下 - 连接到I 独立模式 - 连接到输出

2 C时钟

通讯模式下 - 连接键6 独立模式 - 连接到输出

通讯模式下 - 连接键5 独立模式 - 连接到输出

没有连接

没有连接

没有连接

I

仅输入

OD 开漏输出

O

仅输出,推挽

P

地或电源

如果未使用的, 接 To...

Open Open Open Open Open

形状可能

层要求: One

电极材料: 蚀刻铜,银,碳,氧化铟锡(ITO)

面板材料: 塑料,玻璃,复合材料,油漆表面(低粒子密度金属

油漆可能

面板厚度: 多达10毫米的玻璃,最多5毫米的塑料(电极的大小而定)

按键灵敏度: 通讯模式下:通过以上我简单的命令可设置单独 接口 独立模式:设置固定的

接口: I2 C兼容的从模式(400千赫).离散检测输出

2 不需要C接口.要进入独立模式,

在独立模式下,启动值被硬编码在固件中,并且不能被改变.在默认的启动值使用.这意味着,关键检测是通过各自的IO报道. 保护通道功能会自动在关键0在独立模式下执行.这意味着该通道得到优先于所有其他键进入触摸.

2.3 Keys

依赖于模式,QT1070可以有一个最低的1键和最多七个键.这些可以是

M48Z58MH中文资料

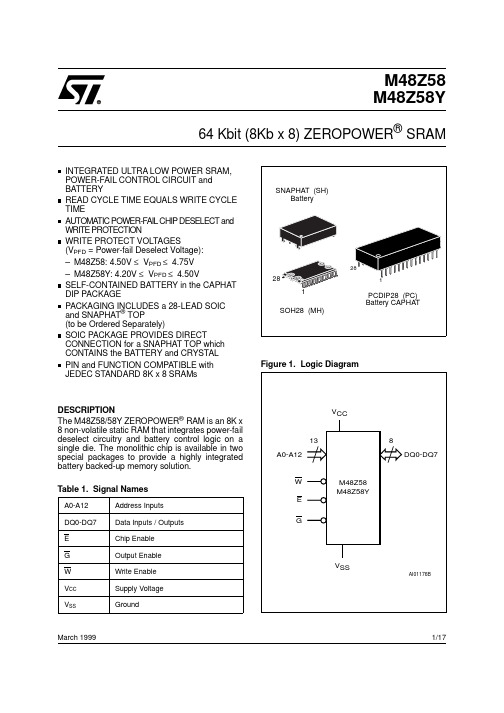

M48Z58M48Z58Y64 Kbit (8Kb x 8) ZEROPOWER ® SRAMMarch 19991/17INTEGRATED ULTRA LOW POWER SRAM,POWER-FAIL CONTROL CIRCUIT and BATTERYREAD CYCLE TIME EQUALS WRITE CYCLE TIMEAUTOMA TIC POWER-F AIL CHIP DESELECT and WRITE PROTECTIONWRITE PROTECT VOLTAGES(V PFD = Power-fail Deselect Voltage):–M48Z58: 4.50V ≤ V PFD ≤ 4.75V –M48Z58Y: 4.20V ≤ V PFD ≤ 4.50VSELF-CONTAINED BATTERY in the CAPHAT DIP PACKAGEPACKAGING INCLUDES a 28-LEAD SOIC and SNAPHAT ® TOP(to be Ordered Separately)SOIC PACKAGE PROVIDES DIRECTCONNECTION for a SNAPHAT TOP which CONTAINS the BATTERY and CRYSTAL PIN and FUNCTION COMPATIBLE with JEDEC STANDARD 8K x 8 SRAMsDESCRIPTIONThe M48Z58/58Y ZEROPOWER ® RAM is an 8K x 8 non-volatile static RAM that integrates power-fail deselect circuitry and battery control logic on a single die. The monolithic chip is available in two special packages to provide a highly integrated battery backed-up memory solution.AI01176B13A0-A12W DQ0-DQ7V CCM48Z58M48Z58YGV SS8E Figure 1. Logic DiagramA0-A12Address Inputs DQ0-DQ7Data Inputs / Outputs E Chip Enable G Output Enable W Write Enable V CC Supply Voltage V SSGroundTable 1. Signal Names281PCDIP28 (PC)Battery CAPHATSNAPHAT (SH)Battery281SOH28 (MH)Symbol ParameterValue Unit T A Ambient Operating Temperature Grade 1Grade 60 to 70–40 to 85 °C T STG Storage Temperature (V CC Off)–40 to 85°C T SLD (2)Lead Solder Temperature for 10 seconds 260°C V IO Input or Output Voltages –0.3 to 7 V V CC Supply Voltage –0.3 to 7V I O Output Current 20mA P DPower Dissipation1WNotes:1.Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is astress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to the absolute maximum rating conditions for extended periods of time may affect reliability.2.Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).CAUTION: Negative undershoots below –0.3 volts are not allowed on any pin while in the Battery Back-up mode.CAUTION: Do NOT wave solder SOIC to avoid damaging SNAPHAT sockets.Table 2. Absolute Maximum Ratings (1)Mode V CCE G W DQ0-DQ7Power Deselect 4.75V to 5.5Vor4.5V to5.5VV IH X X High Z Standby Write V IL X V IL D IN Active Read V IL V IL V IH D OUT Active Read V IL V IH V IH High Z Active Deselect V SO to V PFD (min) (2)X X X High Z CMOS Standby Deselect≤ V SO XXXHigh ZBattery Back-up ModeNotes : 1.X = V IH or V IL ; V SO = Battery Back-up Switchover Voltage.2.See Table 7 for details.Table 3. Operating Modes (1)A1A0DQ0A7A4A3A2A6A5NC A10A8A9DQ7W A11G E DQ5DQ1DQ2DQ3V SSDQ4DQ6A12NC V CCAI01177BM48Z58M48Z58Y 81234567910111213141615282726252423222120191817Figure 2A. DIP Pin ConnectionsAI01178B82345679101112131422212019181716152827262524231A1A0DQ0A7A4A3A2A6A5NC A10A8A9DQ7W A11G E DQ5DQ1DQ2DQ3V SSDQ4DQ6A12NC V CCM48Z58YFigure 2B. SOIC Pin ConnectionsWarning: NC = Not Connected.Warning: NC = Not Connected.2/17M48Z58, M48Z58YAI010305VOUTC L = 100pF or 5pFC L includes JIG capacitance1.9k ΩDEVICE UNDER TEST1k ΩFigure 4. AC Testing Load CircuitInput Rise and Fall Times ≤ 5ns Input Pulse Voltages0 to 3V Input and Output Timing Ref. Voltages1.5VNote that Output Hi-Z is defined as the point where data is no longer driven.Table 4. AC Measurement ConditionsAI01394LITHIUM CELLV PFDV CC V SSVOLTAGE SENSEAND SWITCHING CIRCUITRY8K x 8SRAM ARRAYA0-A12DQ0-DQ7E W GPOWERFigure 3. Block DiagramThe M48Z58/58Y is a non-volatile pin and function equivalent to any JEDEC standard 8K x 8 SRAM.It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special write timing or limitations on the number of writes that can be performed.The 28 pin 600mil DIP CAPHAT ™ houses the M48Z58/58Y silicon with a long life lithium button cell in a single package.The 28 pin 330mil SOIC provides sockets with gold plated contacts at both ends for direct connection to a separate SNAPHAT housing containing the battery. The unique design allows the SNAPHAT battery package to be mounted on top of the SOIC package after the completion of the surface mount process. Insertion of the SNAPHAT housing after reflow prevents potential battery damage due to the high temperatures required for device surface-mounting. The SNAPHAT housing is keyed to pre-vent reverse insertion.The SOIC and battery packages are shipped sepa-rately in plastic anti-static tubes or in Tape & Reel form.DESCRIPTION (cont’d)3/17M48Z58, M48Z58YSymbol ParameterTest Condition MinMax Unit I LI Input Leakage Current 0V ≤ V IN ≤ V CC ±1µA I LO Output Leakage Current 0V ≤ V OUT ≤ V CC ±5µA I CC Supply CurrentOutputs open 50mA I CC1 Supply Current (Standby) TTL E = V IH 3mA I CC2 Supply Current (Standby) CMOS E = V CC – 0.2V3mA V IL Input Low Voltage –0.30.8V V IH Input High Voltage 2.2V CC + 0.3V V OL Output Low Voltage I OL = 2.1mA 0.4V V OHOutput High VoltageI OH = –1mA2.4VTable 6. DC Characteristics(T A = 0 to 70°C or –40 to 85°C; V CC = 4.75V to 5.5V or 4.5V to 5.5V)Symbol ParameterTest ConditionMinMax Unit C IN Input Capacitance V IN = 0V 10pF C IO (3)Input / Output CapacitanceV OUT = 0V10pFNotes:1. Effective capacitance measured with power supply at 5V.2.Sampled only, not 100% tested.3.Outputs deselected.Table 5. Capacitance (1, 2) (T A = 25 °C)Symbol ParameterMin Typ Max Unit V PFD Power-fail Deselect Voltage (M48Z58/58Y) 4.5 4.6 4.75V V PFD Power-fail Deselect Voltage (M48Z58/58YY) 4.24.35 4.5V V SO Battery Back-up Switchover Voltage 3.0V t DR (2)Expected Data Retention Time10YEARSNotes:1.All voltages referenced to V SS .2.At 25 °CTable 7. Power Down/Up Trip Points DC Characteristics (1) (T A = 0 to 70°C or –40 to 85°C)For the 28 lead SOIC, the battery package (i.e.SNAPHAT) part number is "M4Z28-BR00SH1".The M48Z58/58Y also has its own Power-fail De-tect circuit. The control circuitry constantly monitors the single 5V supply for an out of tolerance condi-tion. When V CC is out of tolerance, the circuit write protects the SRAM, providing a high degree of data security in the midst of unpredictable system op-eration brought on by low V CC . As V CC falls below approximately 3V, the control circuitry connects the battery which maintains data until valid power re-turns.DESCRIPTION (cont’d)4/17M48Z58, M48Z58YSymbol ParameterMin MaxUnit t PD E or W at V IH before Power Down 0µs t F (1)V PFD (max) to V PFD (min) V CC Fall Time 300µs t FB (2)V PFD (min) to V SS V CC Fall Time 10µs t R V PFD (min) to V PFD (max) V CC Rise Time 10µs t RB V SS to V PFD (min) V CC Rise Time 1µs t REC (3)V PFD (max) to Inputs Recognized40200msNotes :1.V PFD (max) to V PFD (min) fall time of less than t F may result in deselection/write protection not occurring until 200 µs afterV CC passes V PFD (min).2.V PFD (min) to V SS fall time of less than t FB may cause corruption of RAM data.3.t REC (min) = 20ms for industrial temperature grade 6 device.Table 8. Power Down/Up Mode AC Characteristics (T A = 0 to 70°C or –40 to 85°C)AI01168CV CCINPUTS(PER CONTROL INPUT)OUTPUTS DON'T CAREHIGH-ZtFtFBtRtPDtRBtDRVALIDVALID(PER CONTROL INPUT)RECOGNIZEDRECOGNIZEDV PFD (max)V PFD (min)V SOtRECFigure 5. Power Down/Up Mode AC Waveforms5/17M48Z58, M48Z58YSymbolParameterM48Z58 / M48Z58YUnit-70MinMaxt AVAV Read Cycle Time70ns t AVQV (1)Address Valid to Output Valid 70ns t ELQV (1)Chip Enable Low to Output Valid 70ns t GLQV (1)Output Enable Low to Output Valid 35ns t ELQX (2)Chip Enable Low to Output Transition 5ns t GLQX (2)Output Enable Low to Output Transition 5ns t EHQZ (2)Chip Enable High to Output Hi-Z 25ns t GHQZ (2)Output Enable High to Output Hi-Z 25ns t AXQX (1)Address Transition to Output Transition10ns Notes:1.C L = 100pF (see Figure 4).2.C L = 5pF (see Figure 4).Table 9. Read Mode AC Characteristics(T A = 0 to 70°C or –40 to 85°C; V CC = 4.75V to 5.5V or 4.5V to 5.5V)AI01385tAVAVtAVQV tAXQX tELQVtELQXtEHQZtGLQVtGLQXtGHQZVALIDA0-A12EGDQ0-DQ7VALIDFigure 6. Read Mode AC WaveformsNote: Write Enable (W) = High.6/17M48Z58, M48Z58YSymbolParameterM48Z58 / M48Z58YUnit-70MinMaxt AVAV Write Cycle Time70ns t AVWL Address Valid to Write Enable Low 0ns t AVEL Address Valid to Chip Enable Low 0ns t WLWH Write Enable Pulse Width50ns t ELEH Chip Enable Low to Chip Enable High 55ns t WHAX Write Enable High to Address Transition 0ns t EHAX Chip Enable High to Address Transition 0ns t DVWH Input Valid to Write Enable High 30ns t DVEH Input Valid to Chip Enable High 30ns t WHDX Write Enable High to Input Transition 5ns t EHDX Chip Enable High to Input Transition 5ns t WLQZ (1, 2)Write Enable Low to Output Hi-Z 25ns t AVWH Address Valid to Write Enable High 60ns t AVEH Address Valid to Chip Enable High 60ns t WHQX (1, 2)Write Enable High to Output Transition5ns Notes:1.C L = 5pF (see Figure 4).2.If E goes low simultaneously with W going low, the outputs remain in the high impedance state.Table 10. Write Mode AC Characteristics(T A = 0 to 70°C or –40 to 85°C; V CC = 4.75V to 5.5V or 4.5V to 5.5V)READ MODEThe M48Z58/58Y is in the Read Mode whenever W (Write Enable) is high, E (Chip Enable) is low.Thus, the unique address specified by the 13 Ad-dress Inputs defines which one of the 8,192 bytes of data is to be accessed. Valid data will be avail-able at the Data I/O pins within Address Access time (t AVQV ) after the last address input signal is stable, providing that the E and G access times are also satisfied. If the E and G access times are not met, valid data will be available after the latter of the Chip Enable Access time (t ELQV ) or Output Enable Access time (t GLQV ).The state of the eight three-state Data I/O signals is controlled by E and G. If the outputs are activated before t AVQV , the data lines will be driven to an indeterminate state until t AVQV . If the Address In-puts are changed while E and G remain active,output data will remain valid for Output Data Holdtime (t AXQX ) but will go indeterminate until the next Address Access.WRITE MODEThe M48Z58/58Y is in the Write Mode whenever W and E are low. The start of a write is referenced from the latter occurring falling edge of W or E. A write is terminated by the earlier rising edge of W or E. The addresses must be held valid throughout the cycle. E or W must return high for a minimum of t EHAX from Chip Enable or t WHAX from Write Enable prior to the initiation of another read or write cycle. Data-in must be valid t DVWH prior to the end of write and remain valid for t WHDX afterward. G should be kept high during write cycles to avoid bus contention; although, if the output bus has been activated by a low on E and G, a low on W will disable the outputs t WLQZ after W falls.7/17M48Z58, M48Z58YAI01386tAVAVtWHAXtDVWHDATA INPUT A0-A12EWDQ0-DQ7VALID tAVWHtAVELtWLWHtAVWLtWLQZtWHDXtWHQXFigure 7. Write Enable Controlled, Write AC WaveformsAI01387BtAVAVtEHAXtDVEHA0-A12EWDQ0-DQ7VALID tAVEHtAVELtAVWLtELEHtEHDXDATA INPUT Figure 8. Chip Enable Controlled, Write AC Waveforms8/17M48Z58, M48Z58YDATA RETENTION MODEWith valid V CC applied, the M48Z58/58Y operates as a conventional BYTEWIDE™ static RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write protecting itself when V CC falls within the V PFD(max), V PFD(min) window. All outputs become high imped-ance, and all inputs are treated as "don’t care." Note: A power failure during a write cycle may corrupt data at the currently addressed location, but does not jeopardize the rest of the RAM’s content. At voltages below V PFD(min), the user can be assured the memory will be in a write protected state, provided the V CC fall time is not less than t F. The M48Z58/58Y may respond to transient noise spikes on V CC that reach into the deselect window during the time the device is sampling V CC. There-fore, decoupling of the power supply lines is rec-ommended.When V CC drops below V SO, the control circuit switches power to the internal battery which pre-serves data. The internal button cell will maintain data in the M48Z58/58Y for an accumulated period of at least 10 years when V CC is less than V SO. As system power returns and V CC rises above V SO, the battery is disconnected, and the power supply is switched to external V CC. Write protection con-tinues until V CC reaches V PFD(min) plus t REC(min). Normal RAM operation can resume t REC after V CC exceeds V PFD(max).For more information on Battery Storage Life refer to the Application Note AN1012.POWER SUPPLY DECOUPLING and UNDER-SHOOT PROTECTIONI CC transients, including those produced by output switching, can produce voltage fluctuations, result-ing in spikes on the V CC bus. These transients can be reduced if capacitors are used to store energy, which stabilizes the V CC bus. The energy stored in the bypass capacitors will be released as low going spikes are generated or energy will be absorbed when overshoots occur. A ceramic bypass capaci-tor value of 0.1µF (as shown in Figure 9) is recom-mended in order to provide the needed filtering. In addition to transients that are caused by normal SRAM operation, power cycling can generate negative voltage spikes on V CC that drive it to values below V SS by as much as one Volt. These negative spikes can cause data corruption in the SRAM while in battery backup mode. To protect from these voltage spikes, it is recommeded to connect a schottky diode from V CC to V SS (cathode connected to V CC, anode to V SS). Schottky diode 1N5817 is recommended for through hole and MBRS120T3 is recommended for surface mount.AI02169V CC0.1µF DEVICEV CCV SSFigure 9. Supply Voltage Protection9/17M48Z58, M48Z58YORDERING INFORMATION SCHEMESupply Voltage and Write Protect Voltage58 (1) V CC = 4.75V to 5.5VV PFD = 4.5V to 4.75V 58Y V CC = 4.5V to 5.5VV PFD = 4.2V to 4.5VSpeed-70 70nsPackagePC PCDIP28MH (2,3)SOH28Temp. Range1 0 to 70 °C6 (4)–40 to 85°CShipping Methodfor SOICblank TubesTR Tape & ReelExample: M48Z58Y -70 MH 1 TRNotes: 1. The M48Z58 part is offered with the PCDIP28 (i.e. CAPHAT) package only.2.The SOIC package (SOH28) requires the battery package (SNAPHAT) which is ordered separately under the part number"M4Z28-BR00SH1" in plastic tube or "M4Z28-BR00SH1TR" in Tape & Reel form.3.Delivery may include either the 2-pin version of the SOIC/SNAPHAT or the 4-pin version of the SOIC/SNAPHAT. Both arefunctionally equivalent (see package drawing section for details).4.Industrial temperature grade available in SOIC package (SOH28) only.Caution:Do not place the SNAPHAT battery package "M4Z28-BR00SH1" in conductive foam since this will drain the lithium button-cell battery.For a list of available options (Speed, Package, etc...) or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.10/17M48Z58, M48Z58YPCDIPA2A1ALB1B e1DEN1CeAe3Symbmm inches TypMin Max TypMin Max A 8.899.650.3500.380A10.380.760.0150.030A28.388.890.3300.350B 0.380.530.0150.021B1 1.14 1.780.0450.070C 0.200.310.0080.012D 39.3739.88 1.550 1.570E 17.8318.340.7020.722e1 2.29 2.790.0900.110e329.7236.32 1.170 1.430eA 15.2416.000.6000.630L 3.05 3.810.1200.150N2828Drawing is not to scale.PCDIP28 - 28 pin Plastic DIP , battery CAPHAT11/17SOH-A EN DCLA1α1HA CPB e A2eBSymbmm inchesTyp Min Max Typ Min MaxA 3.050.120A10.050.360.0020.014 A2 2.34 2.690.0920.106 B0.360.510.0140.020 C0.150.320.0060.012 D17.7118.490.6970.728 E8.238.890.3240.350e 1.27––0.050––eB 3.20 3.610.1260.142 H11.5112.700.4530.500 L0.41 1.270.0160.050α0°8°0°8°N2828CP0.100.004 Drawing is not to scale.SOH28 - 28 lead Plastic Small Outline, 4-socket battery SNAPHAT12/17SOH-B EN DCLA1α1HA CPB e A2eBSymbmm inchesTyp Min Max Typ Min MaxA 3.050.120A10.050.360.0020.014A2 2.34 2.690.0920.106B0.360.510.0140.020C0.150.320.0060.012D17.7118.490.6970.728E8.238.890.3240.350e 1.27––0.050––eB 3.20 3.610.1260.142H11.5112.700.4530.500L0.41 1.270.0160.050α0°8°0°8°N2828CP0.100.004 Drawing is not to scale.SOH28 - 28 lead Plastic Small Outline, 2-socket battery SNAPHAT13/17SHA1A DEeA eBA2BLA3Symbmm inches TypMinMax TypMinMax A 9.780.385A1 6.737.240.2650.285A2 6.48 6.990.2550.275A30.380.015B 0.460.560.0180.022D 21.2121.840.8350.860E 14.2214.990.5600.590eA 15.5515.950.6120.628eB 3.20 3.610.1260.142L2.03 2.290.0800.090SH - 4-pin SNAPHAT Housing for 49 mAh BatteryDrawing is not to scale.14/17SHZP-AA1A DEeBA2BLA3Symbmm inches TypMinMax TypMinMax A 9.780.385A1 6.737.240.2650.285A2 6.48 6.990.2550.275A30.380.015B 0.460.560.0180.022D 21.2121.840.8350.860E 14.2214.990.5600.590eB 3.20 3.610.1260.142L2.03 2.290.0800.090SH - 2-pin SNAPHAT Housing for 49 mAh BatteryDrawing is not to scale.15/17SHZP-BA1A DEeBA2BLA3Symbmm inches TypMinMax TypMinMax A 10.540.415A18.008.510.3150.335A27.248.000.2850.315A30.380.015B 0.460.560.0180.022D 21.2121.840.8350.860E 17.2718.030.6800.710eB 3.20 3.610.1260.142L2.03 2.290.0800.090Drawing is not to scale.SH - 2-pin SNAPHAT Housing for 130 mAh Battery16/17Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics© 1999 STMicroelectronics - All Rights Reserved® ZEROPOWER and SNAPHAT are registered trademarks of STMicroelectronics™ CAPHAT and BYTEWIDE are trademarks of STMicroelectronicsSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.17/17。

FF800R12KF4中文资料

European Power-Semiconductor and Electronics Company20.03.1998Marketing InformationFF 800 R 12 KF4FF 800 R 12 KF 4Höchstzulässige Werte / Maximum rated valuesElektrische Eigenschaften / Electrical propertiesKollektor-Emitter-Sperrspannung collector-emitter voltage V CES1200V Kollektor-Dauergleichstrom DC-collector current I C800A Periodischer Kollektor Spitzenstrom repetitive peak collctor current t p=1 ms I CRM1600A Gesamt-Verlustleistung total power dissipation t C=25°C, Transistor /transistor P tot5000W Gate-Emitter-Spitzenspannung gate-emitter peak voltage V GE± 20V Dauergleichstrom DC forward current I F800A Periodischer Spitzenstrom repetitive peak forw. current t p=1ms I FRM1600A Isolations-Prüfspannung insulation test voltage RMS, f=50 Hz, t= 1 min.V ISOL2,5kV Charakteristische Werte / Characteristic values: Transistor min.typ.max. Kollektor-Emitter Sättigungsspannung collector-emitter saturation voltage i C=800A, v GE=15V, T vj=25°C v CE sat-2,73,2Vi C=800A, v GE=15V, T vj=125°C -3,44V Gate-Schwellenspannung gate threshold voltage i C=32mA, v CE=v GE, T vj=25°C v GE(th)4,55,56,5VEingangskapazität input capacity fO =1MHz,T vj=25°C,v CE=25V, v GE=0V C ies-55-nFKollektor-Emitter Reststrom collector-emitter cut-off current v CE=1200V, v GE=0V, T vj=25°C i CES-16-mAv CE=1200V, v GE=0V, T vj=125°C-80-mA Gate-Emitter Reststrom gate leakage current v CE=0V, v GE=20V, T vj=25°C i GES--400nA Emitter-Gate Reststrom gate leakage current v CE=0V, v EG=20V, T vj=25°C i EGS--400nA Einschaltzeit (ohmsche Last)turn-on time (restistive load)i C=800A,v CE=600V,v LF=±15V,R G=1,2Ωt onv LF=15V, T vj= 25°C-0,7-µsv LF=15V, T vj= 125°C-0,8-µs Speicherzeit (induktive Last)storage time (inductive load)i C=800A,v CE=600V,v LF=±15V,R G=1,2Ωt sv LF=15V, T vj= 25°C-0,9-µsv LF=15V, T vj= 125°C-1-µs Fallzeit (induktive Last)fall time (inductive load)i C=800A,v CE=600V,v LF=±15V,R G=1,2Ωt fv LF=15V, T vj= 25°C-0,10-µsv LF=15V, T vj= 125°C-0,15-µs Einschaltverlustenergie pro Puls turn-on energy loss per pulse i C = 800 A, v CE = 600 V, L S = 70 nH E onV L = ±15 V, R G = 1,2 Ω, T vj = 125°C-130-mWs Abschaltverlustenergie pro Puls turn-off energy loss per pulse i C = 400 A, v CE = 600 V, L S = 70 nH E offV L = ±15 V, R G = 1,2 Ω, T vj = 125°C-120-mWs Charakteristische Werte / Characteristic valuesInversdiode / Inverse diodeDurchlaßspannung forward voltage i F=800A, v GE=0V, t vj=25°C v F-2,22,7Vi F=800A, v GE=0V, t vj=125°C-2,02,5VRückstromspitze peak reverse recovery current i F=800A, -di F/dt=4kA/µs I RMv RM=600V, v EG = 10V, T vj = 25°C-250-Av RM=600V, v EG = 10V, T vj = 125°C-400-A Sperrverzögerungsladung recovered charge i F=800A, -di F/dt=4kA/µs Q rv RM=600V, v EG = 10V, T vj = 25°C-26-µAsv RM=600V, v EG = 10V, T vj = 125°C-90-µAs Thermische Eigenschaften / Thermal propertiesInnerer Wärmewiderstand thermal resistance, junction to case Transistor / transistor, DC R thJC0,0125°C/WTransistor,DC,pro Zweig/per arm0,025°C/WDiode, DC, pro Modul/per module0,021°C/WDiode, DC, pro Zweig/per arm0,042°C/W Übergangs-Wärmewiderstand thermal resistance, case to heatsink pro Modul / per Module R thCK typ. 0,008°C/Wpro Zweit / per arm typ. 0,016°C/W Höchstzul. Sperrschichttemperatur max. junction temperature T vj max150°C Betriebstemperatur operating temperature T c op -40...+125°C Lagertemperatur storage temperature T stg -40...+125°C Mechanische Eigenschaften / Mechanical propertiesInnere Isolation internal insulation AI2O3 Anzugsdrehmoment f. mech. Befestigung mounting torque terminals M6 / tolerance ±15%M13Nm Anzugsdrehmoment f. elektr. Anschlüsse terminal connection torque terminals M4 / tolerance +5% / -10%M22Nmterminals M88...10Nm Gewicht weight G ca. 1500g Bedingung für den Kurzschlußschutz / Conditions for short-circuit protectiont fg = 10 µs V CC = 750 Vv L = ±15 V v CEM = 900 VR GF = R GR = 1,2 Ωi CMK1≈ 5000 At vj = 125°C i CMK2≈ 4000 AUnabhängig davon gilt bei abweichenden Bedingungen / with regard to other conditions v CEM = V CES - 20nH x |di c/dt|Mit dieser technischen Information werden Halbleiterbauelemente spezifiziert, jedoch keine Eigenschaften zugesichert. Sie gilt in Verbindung mit denzugehörigen Technischen Erläuterungen. This technical information specifies semiconductor devices but promises no characteristics. It is valid incombination with the belonging technical notes.元器件交易网FF 800 R 12 KF4FF 800 R 12 KF4 / 1FF 800 R 12 KF4 / 2FF 800 R 12 KF4 / 3FF 800 R 12 KF4 / 4FF 800 R 12 KF4 / 5FF 800 R 12 KF4 / 612345iC[A]C[A]i C[A]i C[A]vCE[V]vCEvCE1200100080060040020012001000800600400200vGE10005000200400600800100012001400 101010thJC[°C/W]0,511,522,53F[A]vF Bild / Fig. 1Kollektor-Emitter-Spannung im Sättigungsbereich (typisch) /Collector-emitter-voltage in saturation region (typical)V G E = 15 VT vj = 25°CT vj = 125°CBild / Fig. 2Kollektor-Emitter-Spannung im Sättigungsbereich (typisch) /Collector-emitter-voltage in saturation region (typical)T vj = 125°CBild / Fig. 3Übertragungscharakteristik (typisch) /Transfer characteristic (typical)V CE = 20 VBild / Fig. 4Rückwärts-Arbeitsbereich /Reverse biased safe operating areaT vj = 125°Cv LF = v LR = 15 VR G = 1,2 ΩBild / Fig. 5Transienter Wärmewiderstand (DC) /Transient thermal impedance (DC)Bild / Fig. 6Durchlaßkennlinien der Inversdiode (typisch)Forward characteristics of the inverse diode (typical)T vj = 25°CT vj = 125°CNutzungsbedingungenDie in diesem Produktdatenblatt enthaltenen Daten sind ausschließlich für technisch geschultes Fachpersonal bestimmt. Die Beurteilung der Geeignetheit dieses Produktes für die von Ihnen anvisierte Anwendung sowie die Beurteilung der Vollständigkeit der bereitgestellten Produktdaten für diese Anwendung obliegt Ihnen bzw. Ihren technischen Abteilungen.In diesem Produktdatenblatt werden diejenigen Merkmale beschrieben, für die wir eine liefervertragliche Gewährleistungübernehmen. Eine solche Gewährleistung richtet sich ausschließlich nach Maßgabe der im jeweiligen Liefervertrag enthaltenen Bestimmungen. Garantien jeglicher Art werden für das Produkt und dessen Eigenschaften keinesfalls übernommen.Sollten Sie von uns Produktinformationen benötigen, die über den Inhalt dieses Produktdatenblatts hinausgehen und insbesondere eine spezifische Verwendung und den Einsatz dieses Produktes betreffen, setzen Sie sich bitte mit dem für Siezuständigen Vertriebsbüro in Verbindung (siehe , Vertrieb&Kontakt). Für Interessenten halten wir ApplicationNotes bereit.Aufgrund der technischen Anforderungen könnte unser Produkt gesundheitsgefährdende Substanzen enthalten. Bei Rückfragenzu den in diesem Produkt jeweils enthaltenen Substanzen setzen Sie sich bitte ebenfalls mit dem für Sie zuständigen Vertriebsbüro in Verbindung.Sollten Sie beabsichtigen, das Produkt in gesundheits- oder lebensgefährdenden oder lebenserhaltenden Anwendungsbereichen einzusetzen, bitten wir um Mitteilung. Wir weisen darauf hin, dass wir für diese Fälle- die gemeinsame Durchführung eines Risiko- und Qualitätsassessments;- den Abschluss von speziellen Qualitätssicherungsvereinbarungen;- die gemeinsame Einführung von Maßnahmen zu einer laufenden Produktbeobachtung dringend empfehlen und gegebenenfalls die Belieferung von der Umsetzung solcher Maßnahmen abhängig machen.Soweit erforderlich, bitten wir Sie, entsprechende Hinweise an Ihre Kunden zu geben.Inhaltliche Änderungen dieses Produktdatenblatts bleiben vorbehalten.Terms & Conditions of usageThe data contained in this product data sheet is exclusively intended for technically trained staff. You and your technical departments will have to evaluate the suitability of the product for the intended application and the completeness of the productdata with respect to such application.This product data sheet is describing the characteristics of this product for which a warranty is granted. Any such warranty is granted exclusively pursuant the terms and conditions of the supply agreement. There will be no guarantee of any kind for the product and its characteristics.Should you require product information in excess of the data given in this product data sheet or which concerns the specific application of our product, please contact the sales office, which is responsible for you (see , sales&contact). For those that are specifically interested we may provide application notes.Due to technical requirements our product may contain dangerous substances. For information on the types in question please contact the sales office, which is responsible for you.Should you intend to use the Product in health or live endangering or life support applications, please notify. Please note, that for any such applications we urgently recommend- to perform joint Risk and Quality Assessments;- the conclusion of Quality Agreements;- to establish joint measures of an ongoing product survey,and that we may make delivery depended on the realizationof any such measures.If and to the extent necessary, please forward equivalent notices to your customers.Changes of this product data sheet are reserved.。

S-80842CNNB-B83T2G中文资料

元器件交易网

SUPER-SMALL PACKAGE HIGH-PRECISION VOLTAGE DETECTOR S-808xxC Series

Rev.4.3_00

Product Name Structure

The detection voltage, output form and packages for S-808xxC Series can be selected at the user's request. Refer to the "1. Product Name" for the construction of the product name and "2. Product Name List" for the full product names. 1. Product Name 1-1. SC-82AB, SOT-23-5, SOT-89-3, SNT-4A packages

Seiko Instruments Inc.

1

元器件交易网

SUPER-SMALL PACKAGE HIGH-PRECISION VOLTAGE DETECTOR S-808xxC Series Block Diagrams

1. Nch Open-drain Output Products

S - 808xx

C

x

xx

-

xxx

ห้องสมุดไป่ตู้

xx

G IC direction in tape specifications*1 T2: SC-82AB, SOT-23-5, SOT-89-3 TF: SNT-4A Product code*2 Package code NB: SC-82AB MC: SOT-23-5 UA: SOT-89-3 PF: SNT-4A Output form N: Nch open-drain output (Active Low) L: CMOS output (Active Low) Detection voltage value 08 to 60 (e.g. When the detection voltage is 0.8 V, it is expressed as 08.)

S108T02;S108T02F;S208T02;中文规格书,Datasheet资料

S108T02 Series S208T02 Series■ FeaturesI T (rms)≤8A, Zero Cross type Low profile SIP 4pin Triac output SSR1. Output current, I T (rms)≤8.0A2. Zero crossing functionary (V OX : MAX. 35V)3. Slim 4 pin low profile SIP package4. High repetitive peak off-state voltage (V DRM : 600V, S208T02 Series ) (V DRM : 400V, S108T02 Series )5. High isolation voltage between input and output (V iso (rms) : 3.0kV)6. Lead-free terminal components are also available (see Model Line-up section in this datasheet)7. Screw hole for heat sink■ DescriptionS108T02 Series and S208T02 Series Solid State Relays (SSR) are an integration of an infrared emitting diode (IRED), a Phototriac Detector and a main output Triac. These devices are ideally suited for controlling high voltage AC loads with solid state reliability while providing 3.0kV isolation (V iso (rms)) from input to out-put.Notice The content of data sheet is subject to change without prior notice.In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP ■ Agency approvals/Compliance1. Isolated interface between high voltage AC devices and lower voltage DC control circuitry.2. Switching motors, fans, heaters, solenoids, and valves.3. Power control in applications such as lighting and temperature control equipment.■ Applications1. Package resin : UL flammability grade (94V-0)∗Non-zero cross type is also available. (S108T01 Series/S208T01 Series)∗ : Do not allow external connection.( ) : Typical dimensions■ Internal Connection Diagram+)−)■ Outline Dimensions(Unit : mm)Date code (2 digit)Rank markThere is no rank mark indicator and currently there are no rank offered for this device.A.D.199019911992199319941995199619971998199920002001MarkABCDEFHJKLMN Mark P R S T U V W X A B C Mark 123456789O N DMonth January February March April May June July August September October November December A.D 20022003200420052006200720082009201020112012······2nd digitMonth of production 1st digitYear of productionCountry of originJapanrepeats in a 20 year cycle■ Electro-optical CharacteristicsParameter Symbol Unit InputOutput (T a =25˚C)Forward voltageReverse currentRepetitive peak OFF-state currentON-state voltageHolding currentCritical rate of rise of OFF-state voltageCritical rate of rise of OFF-state voltage at commutaion Minimum trigger currentZero cross voltageIsolation resistanceTurn-on time Turn-off timeThermal resistanceV F I R I DRM V T (rms)I H dV/dt (dV/dt)c I FT V OX R ISO t ont off R th (j-c)R th (j-a)I F =20mA V R =3V V D =V DRM I T (rms)=2A, Resistance load, I F =20mA −V D =2/3•V DRM T j =125˚C , V D =2/3•V DRM , dI T /dt =−4.0A/msV D =6V, R L =30ΩI F =8mA DC500V, 40 to 60%RH V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance load V D (rms)=200V, AC50Hz, I F =20mA I T (rms)=2A, Resistance load V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadV D (rms)=200V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadBetween junction and case Between junction and ambience Conditions MIN.TYP.MAX.Transfer charac-teristics S108T02S208T02S108T02S208T02−−−−−305−−1010−−−−−−1.2−−−−−−−−−−−−−4.5401.41001001.550−−835−10101010−−V µA µA V mA V/µs V/µs mA V Ωmsms˚C /W ■ Absolute Maximum RatingsParameter Symbol Rating UnitInputOutput(T a =25˚C)Forward current Reverse voltage RMS ON-state current Peak one cycle surge current Repetitive peak OFF-state voltage Non-Repetitive peak OFF-state voltage Critical rate of rise of ON-state current Operating frequency Isolation voltage Operating temperature Storage temperature Soldering temperature *2*1I FV R I T (rms)I surge V DRMV DSMdI T /dt fV iso (rms)T opr T stg T solmA V A A VVA/µs Hz kV ˚C ˚C ˚C*3*3*45068804006004006005045 to 653.0−25 to +100−30 to +125260*1 40 to 60%RH, AC for 1minute, f =60Hz *2 For 10s*3 Refer to Fig.1, Fig.2*4 f =60Hz sine wave, T j =25˚C startS108T02S208T02S108T02S208T02Soldering areaShipping PackageModel No.Sleeve 25pcs/sleeve S108T02F S208T02FI FT [mA](V D =6V, R L =30Ω)MAX.8400MAX.8600V DRM [V]Please contact a local SHARP sales representative to see the actual status of the production.■ Model Line-up (1) (Lead-free terminal components)■ Model Line-up (2) (Lead solder plating components)Shipping PackageModel No.Sleeve 25pcs/sleeve S108T02S208T02I FT [mA](V D =6V, R L =30Ω)MAX.8400MAX.8600V DRM [V]F o r w a r d c u r r e n t I F (m A )Ambient temperature T a (˚C)060−2502550751001255040302010Fig.1 Forward Current vs. AmbientTemperatureFig.2 RMS ON-state Current vs.Ambient TemperatureF o r w a r d c u r r e n t I F (m A )Forward voltage V F (mA)1010.1100Fig.4 Forward Current vs. Forward VoltageFig.3 RMS ON-state Current vs.Case TemperatureR M S O N -s t a t e c u r r e n t I T (r m s )(A )Case temperature T C (°C)010−25255075100125987654321R M S O N -s t a t e c u r r e n t I T (r m s )(A )Ambient temperature T a (˚C)0987654321−25100755025125(1)(2)(3)(4)(5)(1)With infinite heat sink(2)With heat sink (200×200×2mm Al plate)(3)With heat sink (100×100×2mm Al plate)(4)With heat sink (50×50×2mm Al plate)(5)Without heat sink(N ote)In natural cooling condition, please locate Al platevertically, spread the thermal conductive silicone grease on the touch surface of the device and tighten up the device in the center of Al plate at the torque of 0.4N•m.Fig.8-b Repetitive Peak OFF-state Current vs.Ambient Temperature (S208T02)Fig.8-a Repetitive Peak OFF-state Current vs.Ambient Temperature (S108T02)R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8Remarks : Please be aware that all data in the graph are just for reference.Fig.5 Surge Current vs. Power-on CycleFig.6 Minimum Trigger Current vs.Ambient TemperatureFig.7 Maximum ON-state Power Dissipationvs. RMS ON-state CurrentM i n i m u m t r i g g e r c u r r e n t I F T (m A )Ambient temperature T a (°C)0108642S u r g e c u r r e n t I s u r g e (A )Power-on cycle (Times)10080604020120M a x i m u m O N -s t a t e p o w e r d i s s i p a t i o n (W )RMS ON-state current I T (rms)(A)010864297531■ Design ConsiderationsIn order for the SSR to turn off, the triggering current (l F ) must be 0.1mA or less.When the input current (I F ) is below 0.1mA, the output Triac will be in the open circuit mode. However, if the voltage across the Triac, V D , increases faster than rated dV/dt, the Triac may turn on. To avoid this situation, please incorporate a snubber circuit. Due to the many different types of load that can be driven, we can merely recommend some circuit vales to start with : Cs=0.022µF and Rs=47Ω. The operation of the SSR and snubber circuit should be tested and if unintentional switching occurs, please adjust the snubber circuit component values accordingly.When making the transition from On to Off state, a snubber circuit should be used ensure that sudden drops in current are not accompanied by large instantaneous changes in voltage across the Triac.This fast change in voltage is brought about by the phase difference between current and voltage. Primarily, this is experienced in driving loads which are inductive such as motors and solenoids. Following the procedure outlined above should provide sufficient results. For over voltage protection, a Varistor may be used.Any snubber or Varistor used for the above mentioned scenarios should be located as close to the main out-put triac as possible.Particular attention needs to be paid when utilizing SSRs that incorporate zero crossing circuitry.If the phase difference between the voltage and the current at the output pins is large enough, zero crossing type SSRs cannot be used. The result, if zero crossing SSRs are used under this condition, is that the SSR may not turn on and off irregardless of the input current. In this case, only a non zero cross type SSR should be used in combination with the above mentioned snubber circuit selection process.The load current should be within the bounds of derating curve. (Refer to Fig.2) Also, please use the optional heat sink when necessary.In case the optional heat sink is used and the isolation voltage between the device and the optional heat sink is needed, please locate the insulation sheet between the device and the heat sink.When the optional heat sink is equipped, please set up the M3 screw-fastening torque at 0.3 to 0.5N•m.In order to dissipate the heat generated from the inside of device effectively, please follow the below sugges-tions.● Design guide● Recommended Operating ConditionsParameterS108T02S208T02Symbol Unit InputOutputInput signal current at ON state Input signal current at OFF state Load supply voltage Load supply currentFrequencyOperating temperatureI F (ON)I F (OFF)V OUT (rms)I OUT (rms)f T oprmA mA V mA Hz ˚C−−−Locate snubber circuit between output terminals(Cs =0.022µF, Rs =47Ω)−−Conditions(∗) See Fig.2 about derating curve (I T (rms) vs. ambient temperature).16080800.147−20240.1120240I T (rms)×80%(∗)6380MIN.MAX.✩ For additional design assistance, please review our corresponding Optoelectronic Application Notes.● Standard CircuitV +V S108T02● DegradationIn general, the emission of the IRED used in SSR will degrade over time.In the case where long term operation and / or constant extreme temperature fluctuations will be applied to the devices, please allow for a worst case scenario of 50% degradation over 5years.Therefore in order to maintain proper operation, a design implementing these SSRs should provide at least twice the minimum required triggering current from initial operation.(a) Make sure there are no warps or bumps on the heat sink, insulation sheet and device surface.(b) Make sure there are no metal dusts or burrs attached onto the heat sink, insulation sheet and device sur-face.(c) Make sure silicone grease is evenly spread out on the heat sink, insulation sheet and device surface.Silicone grease to be used is as follows;1) There is no aged deterioration within the operating temperature ranges.2) Base oil of grease is hardly separated and is hardly permeated in the device.3) Even if base oil is separated and permeated in the device, it should not degrade the function of a device. Recommended grease : G-746 (Shin-Etsu Chemical Co., Ltd.): G-747 (Shin-Etsu Chemical Co., Ltd.): SC102 (Dow Corning Toray Silicone Co., Ltd.) In case the optional heat sink is screwed up, please solder after screwed.In case of the lead frame bending, please keep the following minimum distance and avoid any mechanical stress between the base of terminals and the molding resin.Some of AC electromagnetic counters or solenoids have built-in rectifier such as the diode.In this case, please use the device carefully since the load current waveform becomes similar with rectangu-lar waveform and this results may not make a device turn off.■ Manufacturing Guidelines● Soldering MethodFlow Soldering (No solder bathing)Flow soldering should be completed below 260˚C and within 10s.Preheating is within the bounds of 100 to 150˚C and 30 to 80s.Please solder within one time.Other noticesPlease test the soldering method in actual condition and make sure the soldering works fine, since the impact on the junction between the device and PCB varies depending on the tooling and soldering conditions.分销商库存信息:SHARP-MICROELECTRONICSS108T02S108T02F S208T02。

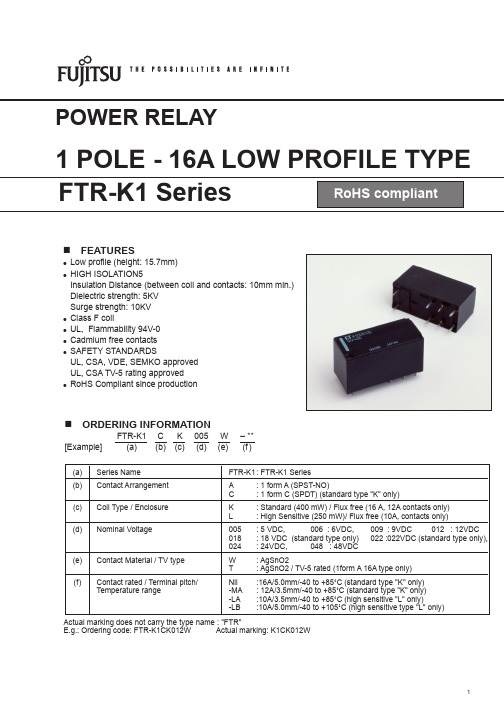

FTR-K1AK048T-LB中文资料

---

Lamp load (TV-5) ---

---

---

Misoperation

10 to 500 Hz, 5gn (double amplitude of 0.35mm) 10 to 55 Hz at double amplitude of 0.7mm

Endurance

10-55 Hz, (double amplitude of 1.5mm)

Shock Resistance

Weight

Misoperation Endurance

Min. 100m/s2 (11±1ms) Min. 1,000m/s2 (6±1ms) Approximately 13g

(d) Nominal Voltage

005 : 5 VDC,

006 : 6VDC, 009 : 9VDC

012 : 12VDC

018 : 18 VDC (standard type only) 022 :022VDC (standard type only),

024 : 24VDC,

n ORDERING INFORMATION

FTR-K1 C K 005 W – **

[Example]

(a) (b) (c) (d) (e) (f )

(a) Series Name

FTR-K1 : FTR-K1 Series

(b) Contact Arrangement

A

: 1 form A (SPST-NO)

Endurance

10 to 500 Hz, 5gn (double amplitude of 0.35mm) 10 to 55 Hz at double amplitude of 0.7mm

AN925中文资料

AN925APPLICATION NOTETime Update in ST’s TIMEKEEPER DevicesFigure 1 shows how the non-volatile, static memory array and the quartz controlled clock oscillator, of TIMEKEEPER devices from STMicroelectronics, are interconnected through the clock registers. The clock registers are mapped into the memory array (please see the data sheet for the precise mapping) as 8 or 16 BYTEWIDE BIPORT memory cells. The time data in these memory cells are updated from the clock side (the system side) and are made available to the user side within the user’s finest time resolution.However, the user’s finest time resolution is one second, so this leaves plenty of scope for variability (of the order of several milliseconds) between one update and the next. Since this variability might be notice-able to some applications (for example, those that poll the time registers regularly, or those that use an alarm function that is triggered once per second), this document sets out to explain the nature of the var-iability, to make it more predictable to the applications designer.Figure 1. Internal Architecture of an ST TIMEKEEPER DeviceDecember 19981/4AN925 - APPLICATION NOTEA 1 Hz clock signal, from the clock chain, is used to update the seconds register. Each rising edge of the1 Hz clock signal increments the system side of the seconds register. Having updated the seconds registera ripple carry to other registers might be initiated (for example, incrementing the minutes register from 00 to 01, after the seconds register has been incremented from 59 to 00). The longest possible ripple carry extends through all seven registers: seconds, minutes, hours, day of the week, date of the month, month of the year and year.Figure 2 shows two consecutive updates of the seconds register. The first update only updates the sec-onds register; the second update, though, ripples through all seven clock registers. When the system-side time registers have finished being updated, they are copied across to the user-side, thereby making the updated time available to the user. Thus, the spacing between successive System-to-User-Update-Pulse is one second plus a delta delay that can vary from 0.5ms to 3.5ms (1x0.5ms to 7x0.5ms). The M48T58 (revision B), M48T59 (revision B), M48T35 and M48T559 are examples of TIMEKEEPER devices that op-erate in this way.Figure 2. Time Update Waveform Diagram (variable delay)2/4AN925 - APPLICATION NOTEAn alternative approach, shown in Figure 3, is adopted by the M48T02, M48T12, M48T08, M48T18, M48T58 (revision C), , M48T59 (revision C), M48T37 and M48T201 devices. The spacing between suc-cessive System-to-User-Update-Pulse is always one second. Each pulse is delayed by the same delta time, of 3.5ms, regardless of the number of registers that need incrementing within that period.Figure 3. Time Update Waveform Diagram (fixed delay)(These examples are each shown with the calibration set to zero.)3/4AN925 - APPLICATION NOTE4/4If you have any questions or suggestions concerning the matters raised in this document, please send them to the following electronic mail addresses:apps.nvram@ (for application support)ask.memory@ (for general enquiries)Please remember to include your name, company, location, telephone number and fax number.Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequencesof use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© 1998 STMicroelectronics - All Rights Reserved The ST logo is a registered trademark of STMicroelectronics.All other names are the property of their respective owners.STMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore -Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.This datasheet has been download from: Datasheets for electronics components.。

落木源TX-KA102超大功率 IGBT 单管驱动器 HIC 芯片 用户手册说明书

北京落木源电子技术有限公司IGBT驱动器(TX-KA102) 产品手册IGBT驱动器HIC芯片(TX-KA102)产品手册特点• 超大功率IGBT 单管驱动器,最大输出电流20A ,最大输出电荷20uC 。

• 三段式完善的过电流保护功能,先降栅压,再延迟判断,确实短路时实行软关断,并封锁短路信号以执行一个完整的保护过程。

• 可按默认值直接使用,也可根据需要调节盲区时间、延迟判断时间、软关断的速度、故障后再次启动的时间。

• IGBT 短路时的集射极电压阈值的设定可用电阻精细调节,也可使用传统的稳压管调节。

• 使用单一电源,驱动器内部设有负压分配器,减少了外部元器件。

•IGBT 的栅极充电和放电速度可分别调节。

应用• 可驱动2000A 以下IGBT 一只驱动特性(除另有指定外,均为在以下条件时测得:Ta=25℃,Vp=24V ,Fop=50KHz,模拟负载电容CL=220nF)参数符号测试条件最小值 典型值 最大值 单位 输入脉冲电流幅值 Ipwm 9 10 12mA VOH 14.5 V 输出电压VOL-8.5 V IOHP 20A 输出电流 IOLP Fop=20KHz Ton=2μS -20A 栅极电阻 Rg0.5Ω输出总电荷 Qout 参见本表下的图线20 uC 工作频率 Fop 参见本表下的图线 0100 KHz 占空比 δ0 100% 最小工作脉宽 Tonmin CL=100nF 0.5 μS 上升延迟 Trd 0.4 0.6 μS 下降延迟 Tfd0.5 0.7μS 上升时间 Tr 0.6 μS 下降时间 TfRg=1Ω,CL=220nF0.6 μS 绝缘电压 VISO 50Hz/1 min 3500 Vrms 共模瞬态抑制CMR30KV/μS驱动电源参数符号测试条件最小值典型值最大值单位输入电压Vp 23 24 25 VCL=0 20输入电源电流IdmAFop=50KHz,CL=220nF,Vp=24V 330工作条件环境温度符号测试条件最小值典型值最大值单位工作温度Top -40 85 ℃存储温度Tst -40 120 ℃短路保护性能(除另有指定外,均为在以下条件时测得:Ta=25℃,Vp=24V,Fop=50KHz,模拟负载电容CL=220nF)最小值值典型值最大值单位参数符号测试条件最小保护动作阈值(1) Vn 用户设置,典型值为缺省值7.5 V 保护盲区(2) Tblind 用户设置,最小值为缺省值 2.2 μS 初始栅压降落Vdrop 5 V 延迟判断时间(3) Tdelay 用户设置,最小值为缺省值 2 μS 软关断时间(4) Tsoft 用户设置,最小值为缺省值 5.5 μS故障后再启动时间(5) Trst 用户设置,典型值为缺省值1.1 mS故障信号延迟Tflt 0.2 μS 故障信号输出电流Iflt 8 10 mA1. 触发过流保护动作时的7脚对16脚的电压。

AOT9608中文资料

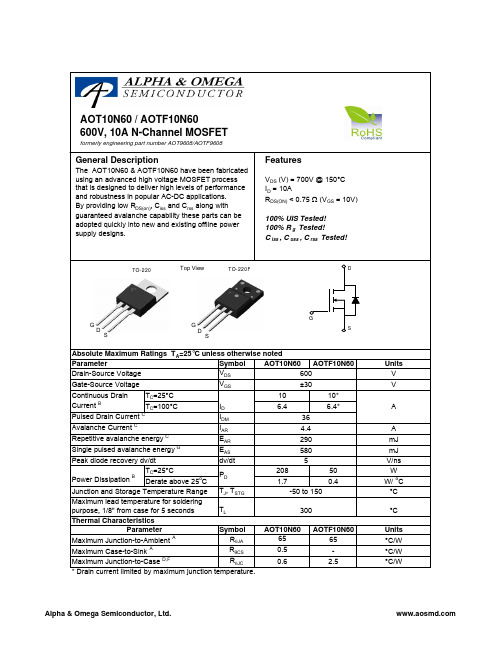

Continuous DrainParameter T =25°C Gate-Source Voltage Drain-Source Voltage Absolute Maximum Ratings T =25°C unless otherwise notedAOT10N60 / AOTF10N60DSDSSymbolMin Typ Max Units600V 700V BV DSS /∆T J 0.65V/ oC 110I GSS ±100nA V GS(th)345V R DS(ON)0.60.75Ωg FS 15S V SD 0.731V I S 10A I SM36A C iss 110013201600pF C oss 105130160pF C rss 7.59.311pF R g33.86ΩQ g 31.140nC Q gs 6.410nC Q gd 14.420nC t D(on)2835ns t r 6680ns t D(off)7695ns t f 6480ns t rr 290350ns Q rr3.94.7µC4.4THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.V DS =480V, T J =125°C Breakdown Voltage Temperature CoefficientI D =250µA, V GS =0V Gate Threshold VoltageV DS =V GS , I D =250µA V DS =600V, V GS =0V V DS =0V, V GS =±30V Zero Gate Voltage Drain Current Gate-Body leakage current Body Diode Reverse Recovery TimeI D =250µA, V GS =0V, T J =25°C V GS =10V, I D =5A Reverse Transfer Capacitance I F =10A,dI/dt=100A/µs,V DS =100VV GS =0V, V DS =25V, f=1MHz SWITCHING PARAMETERS I DSS µA Maximum Body-Diode Pulsed CurrentElectrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS Parameter Conditions Static Drain-Source On-Resistance Forward TransconductanceDiode Forward Voltage I S =1A, V GS =0V V DS =40V, I D =5ATurn-On Rise Time Turn-Off DelayTime V GS =10V, V DS =300V, I D =10A, R G =25ΩGate resistanceV GS =0V, V DS =0V, f=1MHzTurn-Off Fall TimeTotal Gate Charge V GS =10V, V DS =480V, I D =10AGate Source Charge Gate Drain Charge BV DSS Drain-Source Breakdown Voltage I D =250µA, V GS =0V, T J =150°C Body Diode Reverse Recovery Charge I F =10A,dI/dt=100A/µs,V DS =100VMaximum Body-Diode Continuous Current Input Capacitance Output Capacitance Turn-On DelayTime DYNAMIC PARAMETERS A: The value of R θJA is measured with the device in a still air environment with T A =25°C.B. The power dissipation P D is based on T J(MAX)=150°C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used.C: Repetitive rating, pulse width limited by junction temperature T J(MAX)=150°C.D. The R θJA is the sum of the thermal impedence from junction to case R θJC and case to ambient.E. The static characteristics in Figures 1 to 6 are obtained using <300 µs pulses, duty cycle 0.5% max.F. These curves are based on the junction-to-case thermal impedence which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of T J(MAX)=150°C.G. L=60mH, I AS =4.4A, V DD =50V, R G =25Ω, Starting T J =25°CRev 0. July 2008VdsC ha rgeG ate Charge Test Circuit & W av eformResistiv e Switching Test Circuit & W av eformsVddVdsI dVgsB V I Unclamped Inductive Switching (UIS) Test Circuit & W av eformsARDSS2E = 1/2 LI VddARAR。

MT48LC8M16A2TG-7E资料