六管单元高速低功耗4k静态CMOS_RAM的设计_摘要_

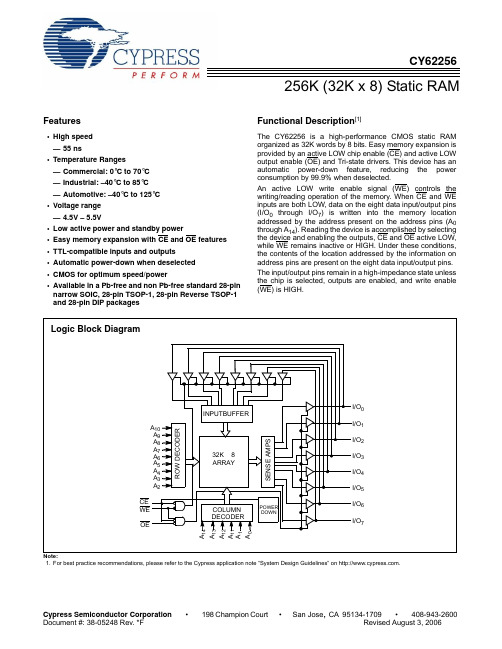

CY62256 32K x 8 位 CMOS 静态 RAM 数据手册说明书

256K (32K x 8) Static RAMCY62256Features•High speed —55ns •Temperature Ranges —Commercial: 0°C to 70°C —Industrial: –40°C to 85°C —Automotive: –40°C to 125°C •Voltage range —4.5V – 5.5V•Low active power and standby power•Easy memory expansion with CE and OE features •TTL-compatible inputs and outputs •Automatic power-down when deselected •CMOS for optimum speed/power•Available in a Pb-free and non Pb-free standard 28-pin narrow SOIC, 28-pin TSOP-1, 28-pin Reverse TSOP-1 and 28-pin DIP packagesFunctional Description [1]The CY62256 is a high-performance CMOS static RAM organized as 32K words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE) and active LOW output enable (OE) and Tri-state drivers. This device has an automatic power-down feature, reducing the power consumption by 99.9% when deselected.An active LOW write enable signal (WE) controls the writing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O 0 through I/O 7) is written into the memory location addressed by the address present on the address pins (A 0through A 14). Reading the device is accomplished by selecting the device and enabling the outputs, CE and OE active LOW,while WE remains inactive or HIGH. Under these conditions,the contents of the location addressed by the information on address pins are present on the eight data input/output pins.The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE) is HIGH.Note:1.For best practice recommendations, please refer to the Cypress application note “System Design Guidelines” on .A 9A 8A 7A 6A 5A 4A 3A 2COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUTBUFFERPOWER DOWNWE OEI/O 0CE I/O 1I/O 2I/O 3I/O 7I/O 6I/O 5I/O 4A 10A 13A 11A 12A A 14A 1Logic Block Diagram32K × 8ARRAYPin ConfigurationsProduct PortfolioProductV CC Range (V)Speed (ns)Power DissipationOperating, I CC(mA)Standby, I SB2(µA)Min.Typ.[2]Max.Typ.[2]Max.Typ.[2]Max.CY62256L Com’l/Ind’l 4.55.05.555/702550250CY62256LL Commercial 7025500.15CY62256LL Industrial 55/7025500.110CY62256LLAutomotive5525500.11512345678910111415162019181721242322Top ViewNarrow SOIC 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 322232425262728125101115141312161918173420217689OEA 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0CE I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12I/O 3TSOP I Top View (not to scale)Reverse Pinout 22232425262728125101115141312161918173420217689OE A 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0CE I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12I/O 3TSOP I Top View (not to scale)12345678910111415162019181721242322Top ViewDIP 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 3Pin DefinitionsPin Number Type Description1–10, 21, 23–26Input A 0–A 14. Address Inputs11–13, 15–19, Input/Output I/O 0–/O 7. Data lines. Used as input or output lines depending on operation27Input/Control WE . When selected LOW, a WRITE is conducted. When selected HIGH, a READ is conducted20Input/Control CE . When LOW, selects the chip. When HIGH, deselects the chip22Input/ControlOE . Output Enable. Controls the direction of the I/O pins. When LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O pins are Tri-stated, and act as input data pins14GroundGND . Ground for the device28Power Supply V CC . Power supply for the deviceNote:2.Typical specifications are the mean values measured over a large sample size across normal production process variations and are taken at nominal conditions (T A = 25°C, V CC ). Parameters are guaranteed by design and characterization, and not 100% tested.Maximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential(Pin 28 to Pin 14)..............................................–0.5V to +7V DC Voltage Applied to Outputsin High-Z State[3]....................................–0.5V to V CC + 0.5V DC Input Voltage[3]................................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V (per MIL-STD-883, Method 3015)Latch-up Current.................................................... > 200 mA Operating RangeRange Ambient Temperature (T A)[4]V CC Commercial0°C to +70°C 5V± 10% Industrial–40°C to +85°C 5V± 10% Automotive–40°C to +125°C 5V± 10%Electrical Characteristics Over the Operating RangeParameter Description Test ConditionsCY62256−55CY62256−70Unit Min.Typ.[2]Max.Min.Typ.[2]Max.V OH Output HIGH Voltage V CC = Min., I OH = −1.0 mA 2.4 2.4V V OL Output LOW Voltage V CC = Min., I OL = 2.1 mA0.40.4VV IH Input HIGH Voltage 2.2V CC+0.5V 2.2V CC+0.5VVV IL Input LOW Voltage–0.50.8–0.50.8V I IX Input Leakage Current GND < V I < V CC–0.5+0.5–0.5+0.5µA I OZ Output Leakage Current GND < V O < V CC, Output Disabled–0.5+0.5–0.5+0.5µAI CC V CC Operating SupplyCurrent V CC = 5.5V,I OUT = 0 mA,f = f Max = 1/t RCL25502550mALL25502550I SB1Automatic CEPower-down Current—TTL Inputs V CC = 5.5V, CE > V IH,V IN > V IH or V IN < V IL,f = f MaxL0.40.60.40.6mALL0.30.50.30.5I SB2Automatic CEPower-down Current—CMOS Inputs V CC = 5.5V,CE > V CC− 0.3VV IN > V CC− 0.3V, orV IN < 0.3V, f = 0L250250µALL - Com’l0.150.15LL - Ind’l0.1100.110LL - Auto0.115Capacitance[5]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = V CC(typ.)6pFC OUT Output Capacitance8pF Thermal Resistance[5]Parameter Description Test Conditions DIP SOIC TSOP RTSOP UnitΘJA Thermal Resistance(Junction to Ambient)Still Air, soldered on a 4.25 x 1.125 inch,2-layer printed circuit board75.6176.5693.8993.89°C/WΘJC Thermal Resistance(Junction to Case)43.1236.0724.6424.64°C/WNotes:3.V IL (min.)= −2.0V for pulse durations of less than 20 ns.4.T A is the “Instant-On” case temperature.5.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and WaveformsData Retention CharacteristicsParameter DescriptionConditions [6]Min.Typ.[2]Max.Unit V DR V CC for Data Retention 2.0V I CCDRData Retention CurrentL V CC = 2.0V , CE > V CC − 0.3V ,V IN > V CC − 0.3V , or V IN < 0.3V250µA LL - Com’l 0.15µA LL - Ind’l 0.110µA LL - Auto0.110µA t CDR [5]Chip Deselect to Data Retention Time 0ns t R [5]Operation Recovery Timet RCnsData Retention WaveformNote:6.No input may exceed V CC + 0.5V .3.0V 5V OUTPUTR1 1800ΩR2990Ω100pF INCLUDING JIG AND SCOPEGND90%10%90%10%<5ns<5ns5V OUTPUTR1 1800ΩR2990Ω5pFINCLUDING JIG AND SCOPE (a)(b)OUTPUT1.77VEquivalent to:THE VENIN EQUIVALENTALL INPUT PULSES 639ΩV CC(min)V CC(min)t CDRV DR >2V DATA RETENTION MODEt RCEV CCSwitching Characteristics Over the Operating Range[7]Parameter DescriptionCY62256−55CY62256−70Unit Min.Max.Min.Max.Read Cyclet RC Read Cycle Time5570nst AA Address to Data Valid5570nst OHA Data Hold from Address Change55nst ACE CE LOW to Data Valid5570nst DOE OE LOW to Data Valid2535nst LZOE OE LOW to Low-Z[8]55nst HZOE OE HIGH to High-Z[8, 9]2025nst LZCE CE LOW to Low-Z[8]55nst HZCE CE HIGH to High-Z[8, 9]2025nst PU CE LOW to Power-up00nst PD CE HIGH to Power-down5570ns Write Cycle[10, 11]t WC Write Cycle Time5570nst SCE CE LOW to Write End4560nst AW Address Set-up to Write End4560nst HA Address Hold from Write End00nst SA Address Set-up to Write Start00nst PWE WE Pulse Width4050nst SD Data Set-up to Write End2530nst HD Data Hold from Write End00nst HZWE WE LOW to High-Z[8, 9]2025nst LZWE WE HIGH to Low-Z[8]55ns Notes:7.Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OL/I OH and 100 pF load capacitance.8.At any given temperature and voltage condition, t HZCE is less than t LZCE, t HZOE is less than t LZOE, and t HZWE is less than t LZWE for any given device.9.t HZOE, t HZCE, and t HZWE are specified with C L = 5 pF as in (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.10.The internal Write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a Write and either signal canterminate a Write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the Write.11.The minimum Write cycle time for Write Cycle #3 (WE controlled, OE LOW) is the sum of t HZWE and t SD.Switching WaveformsRead Cycle No. 1 (Address Transition Controlled)[12, 13]Read Cycle No. 2 (OE Controlled)[13, 14]Write Cycle No. 1 (WE Controlled)[10, 15, 16]Notes:12.Device is continuously selected. OE, CE = V IL .13.WE is HIGH for Read cycle.14.Address valid prior to or coincident with CE transition LOW.15.Data I/O is high impedance if OE = V IH .16.If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state. 17.During this period, the I/Os are in output state and input signals should not be applied.ADDRESSDATA OUTPREVIOUS DATA VALIDDATA VALIDt RCt AAt OHA50%50%DATA VALIDt RCt ACEt DOEt LZOEt LZCE t PUHIGH IMPEDANCEt HZOE t HZCEt PDIMPEDANCEICCISBHIGH DATA OUTOECEV CC SUPPLY CURRENTt HDt SDt PWEt SAt HAt AWt WCt HZOEDATA IN VALIDNOTE 17DATA I/OADDRESSCEWEOEWrite Cycle No. 2 (CE Controlled)[10, 15, 16]Write Cycle No. 3 (WE Controlled, OE LOW)[11, 16]Switching Waveforms (continued)t WCt AWt SAt HAt HDt SDt SCEDATA IN VALIDWEDATA I/OADDRESSCEt HD t SDt LZWEt SAt HAt AWt WCt HZWEDATA IN VALIDNOTE 17DATA I/OADDRESSWECETypical DC and AC Characteristics1.21.41.00.60.40.24.04.55.05.56.01.61.41.21.00.8−5525125−55251251.21.00.8N O R M A L I Z E D t A A120100806040200.01.02.03.04.0O U T P U T S O U R C E C U R R E N T (m A )SUPPLY VOLTAGE (V)NORMALIZED SUPPLY CURRENT vs.SUPPLY VOLTAGENORMALIZED ACCESS TIME vs.AMBIENT TEMPERATURE AMBIENT TEMPERATURE (°C)NORMALIZED SUPPLY CURRENT vs.AMBIENT TEMPERATUREAMBIENT TEMPERATURE (°C)OUTPUT VOLTAGE (V)OUTPUT SOURCE CURRENT vs.OUTPUT VOLTAGE 0.00.81.41.11.00.94.04.55.05.56.0N O R M A L I Z E D t A ASUPPLY VOLTAGE (V)NORMALIZED ACCESS TIME vs.SUPPLY VOLTAGE 120140*********0.01.02.03.04.0O U T P U T S I N K C U R R E N T (m A )080OUTPUT VOLTAGE (V)OUTPUT SINK CURRENT vs.OUTPUT VOLTAGE0.60.40.20.0N O R M A L I Z E D I C CN O R M A L I Z E D I C C , I S BI CCI CCV CC = 5.0VV CC = 5.0V T A = 25°CV CC = 5.0V T A = 25°CI SBT A = 25°C0.60.801.31.2V IN = 5.0V T A = 25°C1.4V CC = 5.0V V IN = 5.0V−55251052.52.01.5CURRENT vs.AMBIENT TEMPERATUREAMBIENT TEMPERATURE (°C)1.00.50.0–0.5I SB3.0STANDBY V CC = 5.0V V IN = 5.0VI S B 2 µATruth TableCE WE OE Inputs/Outputs ModePowerH X X High-Z Deselect/Power-down Standby (I SB )L H L Data Out Read Active (I CC )L L X Data In WriteActive (I CC )LHHHigh-ZOutput DisabledActive (I CC )Typical DC and AC Characteristics (continued)3.02.52.01.51.00.50.01.02.03.04.0N O R M A L I Z E D I P OSUPPLY VOLTAGE (V)TYPICAL POWER-ON CURRENT vs.SUPPLY VOLTAGE 30.025.020.015.010.05.00200400600800D E L T A t (n s )AA CAPACITANCE (pF)TYPICAL ACCESS TIME CHANGE vs.OUTPUT LOADING1.251.000.7510203040N O R M A L I Z E D I C CCYCLE FREQUENCY (MHz)0.05.00.010000.50V CC = 4.5V T A = 25°CV CC =5.0V T A = 2 5°C V IN = 0.5VNORMALIZED I CC vs. CYCLE TIMEOrdering InformationSpeed(ns)Ordering Code PackageDiagram Package TypeOperatingRange55CY62256LL−55SNI51-8509228-pin (300-mil Narrow Body) SNC Industrial CY62256LL−55SNXI28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−55ZXI51-8507128-pin TSOP I (Pb-free)CY62256LL−55SNE51-8509228-pin (300-mil Narrow Body) SNC AutomotiveCY62256LL−55SNXE28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−55ZE51-8507128-pin TSOP ICY62256LL−55ZXE28-pin TSOP I (Pb-free)CY62256LL−55ZRXE51-8507428-pin Reverse TSOP I (Pb-free)70CY62256LL−70PC51-8501728-pin (600-Mil) Molded DIP Commercial CY62256LL−70PXC28-pin (600-Mil) Molded DIP (Pb-free)CY62256L−70SNC51-8509228-pin (300-mil Narrow Body) SNCCY62256L−70SNXC28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70SNC28-pin (300-mil Narrow Body) SNCCY62256LL−70SNXC28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70ZC51-8507128-pin TSOP ICY62256LL−70ZXC28-pin TSOP I (Pb-free)CY62256L–70SNI51-8509228-pin (300-mil Narrow Body) SNC IndustrialCY62256L–70SNXI28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70SNI28-pin (300-mil Narrow Body) SNCCY62256LL−70SNXI28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70ZXI51-8507128-pin TSOP I (Pb-free)CY62256LL−70ZRI51-8507428-pin Reverse TSOP ICY62256LL−70ZRXI28-pin Reverse TSOP I (Pb-free)Please contact your local Cypress sales representative for availability of these partsPackage DiagramsPackage Diagrams (continued)28-pin Thin Small Outline Package Type 1 (8 x 13.4 mm) (51-85071)51-85071-*GDocument #: 38-05248 Rev. *F Page 13 of 14All product and company names mentioned in this document are the trademarks of their respective holders.Package Diagrams (continued)51-85074-*F28-pin Reverse Thin Small Outline Package Type 1 (8x13.4 mm) (51-85074)Document History PageDocument Title: CY62256, 256K (32K x 8) Static RAM Document Number: 38-05248REV.ECN NO.IssueDateOrig. ofChange Description of Change**11345403/06/02MGN Change from Spec number: 38-00455 to 38-05248Remove obsolete parts from ordering info, standardize format*A11522705/23/02GBI Changed SN Package Diagram*B11650609/04/02GBI Added footnote 1Corrected package description in Ordering Information table*C238448See ECN AJU Added Automotive product information*D344595See ECN SYT Added Pb-free packages on page# 10*E395936See ECN SYT Changed address of Cypress Semiconductor Corporation on Page# 1 from“3901 North First Street” to “198 Champion Court”Added CY62256L–70SNXI package in the Ordering Information on Page # 10 *F493277See ECN VKN Updated Ordering Information table。

CMOS集成电路设计中的功耗优化与性能改进

CMOS集成电路设计中的功耗优化与性能改进CMOS(互补金属氧化物半导体)集成电路设计中的功耗优化和性能改进是一个重要的研究领域。

随着电子设备的不断发展和应用场景的不断扩大,对功耗和性能的要求也越来越高。

本文将从几个方面探讨CMOS集成电路设计中的功耗优化和性能改进的方法和技术。

首先,功耗优化是CMOS集成电路设计中的一个重要目标。

功耗优化的主要目的是降低电路的功耗,以延长电池寿命、减少散热和降低电源成本。

功耗优化的方法包括电源管理、低功耗电路设计和时钟管理等。

电源管理主要通过设计电源管理单元(PMU)来管理电源供应和功耗控制。

低功耗电路设计采用了一系列技术,如体积逻辑、低功耗时钟、低功耗存储器和低功耗处理器等。

时钟管理是通过优化时钟频率和时钟分配来降低功耗。

这些方法和技术可以有效地降低功耗,提高电路的能效。

其次,性能改进是CMOS集成电路设计中的另一个关键目标。

性能改进的主要目的是提高电路的工作速度和数据处理能力。

性能改进的方法包括时钟频率提升、电路结构优化和算法优化等。

时钟频率提升是通过提高时钟频率来提高电路的工作速度。

电路结构优化主要通过优化电路结构和布局来提高电路的性能。

算法优化主要通过优化算法和数据处理流程来提高电路的数据处理能力。

这些方法和技术可以有效地提高电路的性能,实现更高的数据处理速度和更强的计算能力。

此外,CMOS集成电路设计中还有一些其他的方法和技术可以用于功耗优化和性能改进。

例如,功耗优化可以通过采用动态电压频率调整(DVFS)技术来实现。

DVFS技术可以根据电路的工作负载和性能需求来动态调整电压和频率,以实现功耗和性能的最佳平衡。

性能改进可以通过采用多核处理器和并行计算技术来实现。

多核处理器可以将任务分配到多个处理核心上并行处理,以提高数据处理能力和计算速度。

此外,还有一些新的技术和方法正在被研究和应用于CMOS 集成电路设计中的功耗优化和性能改进。

例如,近年来兴起的深度学习和人工智能技术可以通过优化算法和数据处理流程来提高电路的性能。

六管静态mos管电路

六管静态mos管电路

六管静态MOS管电路是一种集成电路,由六个MOS管组成。

这种电路通常用于实现逻辑门电路,如与门、或门等。

在六管静态MOS管电路中,每个MOS管都有三个电极:源极、栅极和漏极。

通过在栅极上施加适当的电压,可以控制源极和漏极之间的导通或截止。

这种控制作用使得六管静态MOS管电路可以实现各种逻辑功能。

六管静态MOS管电路具有功耗低、速度快、集成度高、可靠性高等优点,因此在数字电路、微处理器、存储器等应用领域得到了广泛的应用。

在实际应用中,需要根据具体的需求和电路要求来选择适当的六管静态MOS管电路,并正确地连接和使用它。

同时,也需要对六管静态MOS管电路的基本原理和特点有一定的了解,以便更好地理解和应用这种电路。

6t_sram工作原理__理论说明以及概述

6t sram工作原理理论说明以及概述1. 引言1.1 概述在现代半导体芯片设计中,静态随机存储器(SRAM)是一种常见且重要的存储单元。

其中,6T SRAM作为一种经典的SRAM设计,被广泛应用于计算机内存、缓存以及其他集成电路中。

本篇长文将详细介绍6T SRAM工作原理的理论说明以及概述。

1.2 文章结构本文总共分为五个部分进行论述:引言、6T SRAM工作原理、6T SRAM的理论说明、6T SRAM的概述、结论。

在引言部分,我们将先对文章进行概述,并简要介绍本文的结构和目的。

1.3 目的该长文的目标是全面阐述6T SRAM的工作原理并提供相关基础知识与理论解释。

通过对SRAM定义和作用、6T SRAM基本结构以及读写操作过程的分析,希望能够使读者全面了解6T SRAM在半导体芯片中的核心功能与实现方式。

此外,在深入讨论存储单元设计原理、静态存储特性和动态存储特性时,本文也将帮助读者更加清晰地认识到6T SRAM在实际应用中的优势和限制。

最后,通过回顾6T SRAM的市场应用、发展历程以及当前研究和未来趋势展望,我们也希望引领读者对该技术进行全面评估,并探讨未来可能的研究方向。

以上就是本文“1. 引言”部分内容的详细清晰撰写。

2. 6T SRAM工作原理:2.1 SRAM的定义和作用:SRAM是静态随机访问存储器(Static Random Access Memory)的简称。

它是一种常用的半导体存储器,具有高速读写、无需刷新和可随机访问等特点。

SRAM主要用于构建计算机系统中的缓存和寄存器等临时存储器件。

2.2 6T SRAM的基本结构:6T SRAM是SRAM中最常见的类型之一,它由六个MOSFET(金属氧化物半导体场效应晶体管)组成。

这六个MOSFET分别被命名为Q1、Q2、Q3、Q4、Q5和Q6,它们通过互相连接以形成一个稳定可靠的存储单元。

在6T SRAM中,两个互补的反相信号线(Wordline和Bitline)被用来控制读写操作。

cmos静态功耗

cmos静态功耗CMOS技术是一种被广泛应用于数字集成电路中的技术,它能够有效地降低电路的功耗,提高电路的可靠性和性能,而静态功耗是CMOS 技术中必须要考虑的一个重要问题。

本文将结合CMOS技术的工作原理和静态功耗的概念,分步骤介绍CMOS静态功耗的相关知识。

第一步,介绍CMOS技术的工作原理。

CMOS全称是互补金属氧化物半导体技术,它是利用PMOS和NMOS两种互补型的晶体管构成的电路。

PMOS是由p型半导体和n型材料构成,NMOS则由n型半导体和p 型材料组成。

CMOS电路的工作原理是利用两个开关控制电路的通断,而这两个开关就是PMOS和NMOS两种晶体管,通过控制门电压的大小来控制晶体管的开启和闭合,从而实现电路的工作。

第二步,解释静态功耗的概念。

静态功耗是指在电路没有进行任何操作,并且电路的电源已经开通的情况下,电路仍然会存在能量的消耗。

这种消耗的原因是由于CMOS电路的构造原理,因为由于在现实电路中,开关处于某种状态下未禁止的电流通路会存在一些电阻,而这个电阻就会导致电流从源头经过到达极地的能量损耗。

第三步,分析CMOS电路的静态功耗问题。

因为CMOS电路是由PMOS和NMOS两种晶体管构成的,所以CMOS电路的静态功耗问题主要由这两种晶体管产生。

NMOS电路的静态功耗比较容易控制,而PMOS电路的静态功耗却比较难以控制。

因为PMOS电路的静态功耗与电路的设计有很大关系,如果电路的设计不合理,可能会导致PMOS电路的静态功耗增大,从而影响电路的性能。

第四步,说明降低CMOS静态功耗的方法。

降低CMOS电路的静态功耗可以从两个方面入手,一是优化电路的结构设计,二是利用新的技术和材料来改进电路的性能和可靠性。

对于电路的优化设计,可以通过优化功耗方面的电路结构、采用低功耗的设计方案等方法来有效地降低电路的静态功耗。

对于利用新的技术和材料来改进电路性能和可靠性,则可以应用硅基PMOS和InGaAsNMOS等新的材料,从而提高电路的性能和可靠性,同时也可以降低电路的静态功耗。

CMOS

第 2 卷第 2期 3

20 0 2年 2月

半

导

体

学

报

Vo. 1 23, o. N 2

CHI NES OURNAI EJ OF S EM I CONDUCTORS

Fe . 2 0 b , 02

CMoS S KbS / oI4 RAM 总剂 量 辐 照 实验

等研 制 出抗 总剂 量

加 固 的 2 6 Ol R 5 K S AM . 了 满 足 我 国 宇 航 和 国 S 为 防事 业的 飞速 发展 , 据 我们 的工 艺状况 和条 件 , 根 成

c Mos s K / ol4 b静 态存储 器 的状态 真值 表 见表 1 , 其中, E 为低 能 信号 维持 端 , E 0时 , 片处 于 当 芯 低 能 维 持 态 ; 为 读/ 控 制端 , W 一 1 , 片 W 写 当 时 芯 处 于读 状 态 , W 一0时 , 片处 于 写状 态. 电路 当 芯 其 结 构与 C MOS S 4 / O16 Kb静 态存 储 器 基本 相 同, 都

刘新宇 刘运龙 孙海锋 吴德馨 和致经。 刘忠立

( 1中 国科 学 院微 电 子 中 心 ,北 京 l02) 00 9 2中 国科 学院 半 导 体 研 究 所 .北 京 10 8 ) 0 0 3

摘要 :研究 了 C S S Kb静态随机存储器 的抗 总剂量辐 照性能 CMO /OI4 b静态 随机存储器 采用 I MO /OI 4 S S K K× 4的并行结 掏体系 , 其地址取数时间为 3 n , 0s 芯片尺 寸为 3 6 m×3 8rm; .r a .4 a 在工作 电压为 3 时 , MO /OI Kb V C SS 4 静态随机存 储器抗总剂 量高达 5 OR d S 能较好地满足军用和航天领域的要求. ×1= a (D,

CMOS超大规模集成电路设计课件

11

Corollaries

Many other factors grow exponentially – Ex: clock frequency, processor performance

1: Circuits & Layout

CMOS VLSI Design 4th Ed.

12

CMOS Gate Design

Integration Levels

SSI: 10 gates

MSI: 1000 gates

LSI:

[Moore65] Electronics Magazine

10,000 gates

VLSI: > 10k gates

9

1: Circuits & Layout

CMOS VLSI Design 4th Ed.

And Now…

1: Circuits & Layout

CMOS VLSI Design 4th Ed.

10

Feature Size

Minimum feature size shrinking 30% every 2-3 years

1: Circuits & Layout

CMOS VLSI Design 4th Ed.

Activity: – Sketch a 4-input CMOS NOR gate

A B C D Y

Hale Waihona Puke 1: Circuits & Layout

CMOS VLSI Design 4th Ed.

13

Complementary CMOS

Complementary CMOS logic gates – nMOS pull-down network – pMOS pull-up network inputs – a.k.a. static CMOS

浅谈CMOS集成电路低功耗设计

浅谈CMOS集成电路低功耗设计李名扬 20102466摘要:本文在对CMOS电路功耗来源分析的基础上,提出了降低电源电压、降低负载电容、降低开关活动性跳变率、调整晶体管的尺寸、降低MOS管的阈值电压等降低功耗的方法,然后介绍了CMOS集成电路低功耗设计中应注意的问题,最后对未来CMOS集成电路的发展进行了展望。

关键词:CMOS集成电路,低功耗,阈值电压,门控时钟1引言随着CMOS集成电路的规模越来越大,工作频率不断提高,芯片的功耗也越来越大,这就给电路的使用带来了两个负面的影响。

首先,为延长工作时间需要提高电源性能;其次,由于电路只能在一定的温度范围内工作,需要更精确的封装和良好的散热性能,这无疑会增加成本。

功耗特别是功耗密度问题变得越来越突出,将成为影响电路性能的关键问题。

功耗密度的增加将引起芯片温度升高,影响电路的可靠性,芯片温度每升高10℃,器件寿命将减少一半。

为了避免芯片发热,则要花费更多的成本解决芯片封装和冷却问题。

另外,VLSI的发展使整机体积缩小,促进了各种微小型的便携机和便携式设备的发展。

靠电池供电的便携式设备及航空航天设备都需要低功耗电路以维持更长的电池寿命。

因此,降低功耗是CMOS集成发展的需求,低功耗设计已成为一个关键的设计考虑。

以下从低功耗技术研究的意义开始,逐步介绍一下有关CMOS集成电路低功耗设计的方法及注意问题。

2低功耗技术的研究意义低功耗技术是上世纪九十年代开始由于实际应用需要受到广泛关注而迅速发展起来的,并且在集成电路设计中的重要性也随着工艺的发展越来越凸显。

促进低功耗技术研究的因素有很多,概括起来主要有以下几点:1.电路的可靠性电路的功耗将转化为热量而释放出来,过多的热量将导致期间工作温度升高,继而降低系统的可靠性,导致许多问题产生。

工作温度过高将使各种制造是的轻微物理缺陷所造成的故障显现出来,如桥接故障。

温度的提高意味着电迁移率的增加,当芯片温度上升到一定程度时,电路将无法正常工作。

嵌入式系统设计师考试试题及答案

嵌入式系统设计师考试试题及答案1、某嵌入式系统主存容量为64KB,其中ROM区为4KB,其余为RAM区,按字节编址。

现要用2K×8位的ROM芯片和4K×4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数和RAM芯片数分别是_。

A、1、15B、2、15C、1、30D、2、30答案:D2、软件项目实施过程中的里程碑点应在_文档中确定。

A、软件研制任务书B、软件开发计划C、软件测试计划D、软件研制总结报告答案:B3、以下关于死锁的叙述中,不正确的是_A、死锁涉及的资源必须遵循申请、分配、使用和释放的管理模式B、发生死锁时,系统中一定至少存在一个资源等待的回路C、死锁是用户之间循环等待资源而引起的僵局D、死锁只可能在单个进程中发生,不可能在多个进程中发生答案:D4、在嵌入式系统设计中,一般包含多种类型的存储资源,比如ROM、EEPROM、NAND Flash、Nor Flash、DDR、SD卡等。

下面关于这些资源的描述中,正确的是_A、EEPROM是电不可擦除的ROMB、Nand Flash上面的代码不能直接运行,需要通过加载的过程C、NORFlash上面的代码不能直接运行,需要通过加载的过程D、ROM是用来存储数据的,其上面的数据可以随意更新,任意读取答案:B5、常用的函数参数传递方式有传值与传引用两种。

_。

A、在传值方式下,形参与实参之间互相传值B、在传值方式下,实参不能是变量C、在传引用方式下,修改形参实质上改变了实参的值D、在传引用方式下,实参可以是任意的变量和表达式答案:C6、微内核操作系统在嵌入式系统中得到越来越广泛的应用,以下关于微内核操作系统叙述中,错误的是A、微内核操作系统,就是一种基于微内核架构的操作系统B、微内核操作系统由一群尽可能将数量最小化的软件程序组成C、微内核并非一个完整的操作系统,而只是操作系统中最基本的部分D、由于微内核不能有效的支持多处理机运行,所以不适用分布式系统环境答案:D7、在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是_来区分的。

低功耗CMOS静态随机存储器设计技术

L w O rCMOS SRAM sg c nq e O P we De in Te h iu

W ANG e P ng, HU Zi—y ng a

高功耗不仅仅会减少靠 电池供 电的设 备 的使用时 间, 而且带来的电路温升也会降低 电路 的可靠性并 影响芯 片 的使 用 寿命 。特别 是 最 近 掌 上 电脑 、 线 无

通讯 和个人数 字娱 乐 设 备 的迅 速 发 展 , 芯 片低 功 对

耗的要求更加迫切。作为 V s 系统 中不可或缺 的 LI 存储器部分 , 在不影响速度和面积的前提下 , 如何降 低功耗 就显得 尤 为重要 。

会被预充到供 电电压 , 读数据 时存储单元会根据存 储 的信 息在两个 位线 上 建 立 不 同的 电压 , 由灵 敏 放

大器放大并通过输出缓冲器输 出。而写操作时 , 输 入缓 冲器会在 位线 上 建 立 足 够 的 电压 差 , 数据 写 把

作者简介 : 王鹏 (9 4一) 男 , 17 , 辽宁沈 阳人 , 士研究生 , 硕 主研方向 : 集成电路设计 。 收稿 日期 :O7一 6—1 20 o 8

4 3 多级 译码 技术 .

3 通过多级译码等 方式来 降低 动态 电流以及 ) 降低存 储器供 电电压 。 4 通过 由高 阀值 晶体管或可 变阀值 晶体 管构 )

成 的存储 单元 来 降低存 储 单元 的漏 电流 。

4 1 层 次化字 线 结构 .

S A 中的译 码器 通 常包 括行 译码 器 和列 译码 R M 器 两部 分 , 主要 采用 高 速静 态 与/ 与非 门 , 或非 门 或/ 电路结 构 。地址 输 人缓 冲器 不仅 仅要 驱动长 地址线 上 的寄 生 电容 , 而且 还 包 括 很 多 数 量 的 与非 门 的栅 电容 , 时 和功耗 都 比较 大 。如果 采用 多级译 码 , 延 即 第 一级 预译码 , 二 级最 终译 码 的结构 , 第 连接 到地址

1Mb高速低功耗SRAM的设计

b、临时用水布置说明

临时用水管管材采用镀锌钢管。埋地敷设,埋设深度为80厘米,以免被现场过往车辆损坏,冬季还可起到保温作用。用水由闸阀控制。供现场消防。现场设临时用水值班人员两名,负责现场用水的巡视维修。

项目组织机构及项目主要管理人员名单见附表。

职务姓名性别职称项目经理高志春男工程师

材料员尚文琴男助工

施工员吴小茹男助工

安全员雷明录男助工质检员范雄飞男助工专职安全

郝卫星男技术员员

项目组织机构图

本工程质量标准要求高、计划施工总工期180日历天,期间经历雨期,工期较紧张。为了保证基础、面层、照明均尽可能有充裕的时间施工,优质高效地完成本工程,须充分考虑到各方面的影响因素,从任务划分、人力、资源、时间、空间的充分利用与合理配置上,科学部署,严密组织工程流水施工。

协作目标:积极配合甲方、监理、设计院和其他相关单位的工作和监督检查,圆满完成工程项目的施工,给公司创形象,为业主增光彩。

竣工回访和质量保修计划:根据我公司对业主的承诺,每年夏季对用户进行回访。根据第80号建设部令,《房屋建筑工程质量保修办法》的有关规定进行保修。房

屋地基基础和主体结构工程,保修年限为设计规定的该工程的合理使用年限,屋面防水、卫生间防水以及外墙面和房间的防渗漏、保候修期为5年,供热系统保修期为二个采暖期,电气系统、给排水设备安装保修期为二年;装修工程保修年限为二年。其它保修期限由建设单位与我方以合同形式约定。

Q2=q2N2K2/8/3600=200×20×1.5÷8÷3600=0.21L/s 消防用水Q3:本现场物料堆放齐全,因此现场消防器材布置相当重要。根据现场施工临水水量规定,当施工现场占地不大于1ha(公顷)时,q3取15L/s。

RAM的基本结构 RAM的存储单元

RAM容量的扩展

1. 位数的扩展:把各片对应的地址线连接在一 起,数据线并列使用即可。接线如下图:

CS

R/W

A... 0

A9

A9...A0 R/W CS A9...A0 R/W CS

2114 (1)

2114 (2)

D3 D2 D1 D0

D3 D2 D1 D0

D7 D6 D5 D4

D3 D2 D1 D0

2114 (4)

D3 D2 D1 D0

(8-12)

例:用8片1K×8位RAM构成的8K×8位RAM。

I /O7

... ...

I /O1

... I/O0 I/O1

I /O7

1024×8R A M

... I/O0 I/O1

I /O7

1024×8R A M

...

... I/O0 I/O1

I /O7

1024×8R A M

数据线 D D

31 0

31 1

.

.

.

.

.

.

Y0

Y1

列译 码 器

...

31 31

.

Y31

A5

A6

A7

A8

A9

地址输入

2 . 地 址 译 码 器 —— 将 寄 存器地址对应的二进制 数译成有效的行选信号

A0 地

A1

址 A2

行 译

和列选信号,从而选中

输 A3

码

该存储单元。

入

器

A4

采用双译码结构。

行地址译码器:5输入32输出,

A0

1

或.

门

. 阵

列

( 编 码器 )

1

sram六管单元结构

sram六管单元结构

SRAM(Static Random Access Memory)是一种静态随机存取存储器,它的六管单元结构是其关键组成部分之一。

六管单元结构是指每个存储单元都由6个晶体管组成,这种结构使得SRAM具有快速的读写速度、高密度和低功耗等优点。

首先,六管单元结构包括两个交叉的反相器和两个传输门。

这种结构使得SRAM的读写操作可以通过控制传输门来实现,而不需要像动态随机存取存储器(DRAM)那样需要周期性地刷新数据。

这就使得SRAM的读写速度比DRAM更快,因为它不需要等待刷新周期。

其次,六管单元结构还使得SRAM具有较高的集成度,因为每个存储单元只需要6个晶体管,相比之下,DRAM需要一个存储单元至少需要一个晶体管和一个电容器,因此SRAM相对更加紧凑,可以在同样的面积内存储更多的数据。

另外,六管单元结构也有助于降低功耗。

由于SRAM的存储单元是静态的,所以它不需要像DRAM那样需要不断地刷新数据,这就使得SRAM在静态状态下功耗较低。

而且,由于六管单元结构的特性,SRAM在读写操作时也能够更加高效地利用电路,从而降低功耗。

总之,SRAM的六管单元结构使得它成为了一种高速、高密度和低功耗的存储器,因此在许多应用中都得到了广泛的应用,比如高速缓存、寄存器文件等。

随着科技的不断进步,相信SRAM的六管单元结构也将继续发挥重要作用,为计算机系统的性能提供更好的支持。

六管静态mos管电路的读写原理

六管静态mos管电路的读写原理一、六管静态MOS管电路的结构六管静态MOS管电路由六个MOS管组成,其中包括两个传输门M1和M2,两个写入门M3和M4,以及两个输出门M5和M6。

这些MOS管通过互相连接的方式构成了一个复杂的电路结构,可以实现存储、读取和输出数据的功能。

1. 传输门M1和M2传输门M1和M2是六管静态MOS管电路中的两个主要控制元件,用于存储器的读取和写入操作。

它们分别由p型MOS管和n型MOS管组成,通过控制它们的栅极电压来实现不同的传输功能。

2. 写入门M3和M4写入门M3和M4是用于对存储器进行写入操作的控制元件,通过改变它们的栅极电压,可以实现对存储器中数据的写入和修改操作。

3. 输出门M5和M6输出门M5和M6是六管静态MOS管电路中用于存储器数据输出的控制元件,通过改变它们的栅极电压,可以实现对存储器中数据的输出操作。

二、六管静态MOS管电路的工作原理六管静态MOS管电路是一种基于MOS管工作原理的电路,它可以实现存储器的读取和写入操作。

其工作原理可以简单地分为写入和读取两个步骤。

1. 写入操作写入操作是指将数据写入存储器中,通过改变传输门M1和M2的栅极电压,可以实现对存储器的写入操作。

具体步骤如下:(1)确定要写入的数据,并将其输入到写入门M3和M4中;(2)控制写入门M3和M4的栅极电压,将数据写入传输门M1和M2中;(3)通过控制传输门M1和M2的通导状态,将数据写入存储器中。

2. 读取操作读取操作是指从存储器中读取数据,通过改变传输门M1和M2的通导状态,可以实现对存储器的读取操作。

具体步骤如下:(1)控制传输门M1和M2的通导状态,将存储器中的数据输出到输出门M5和M6中;(2)通过控制输出门M5和M6的栅极电压,将数据输出到外部电路中。

三、六管静态MOS管电路的读写操作过程六管静态MOS管电路的读写操作过程可以简单地分为写入和读取两个步骤。

下面我们将分别介绍这两个步骤的具体操作流程。

六管单元sram存储器工作原理

六管单元sram存储器工作原理

六管单元SRAM存储器是一种静态随机存取存储器,其工作

原理如下:

1. 储存单元槽位:六管单元SRAM存储器由若干个储存单元

组成,每个储存单元具有一个位宽(bit-width)的存储槽位。

2. 静态存储:每个储存单元用一个电容来储存一个位(bit)

的信息,电容充电等效于位值为1,不充电则等效于位值为0。

3. 读写管道:每个储存单元有两个互补的MOSFET管(传输

门和扩展门),用于控制读取和写入操作。

传输门位于存储单元的“上部”,扩展门位于存储单元的“下部”。

4. 读操作:当进行读操作时,访问线电压会传递到传输门上,导致传输门打开,相应的位值会通过输出线路传输给外部输出。

5. 写操作:当进行写操作时,访问线电压会传递到扩展门上,扩展门会传递电压变化到位线上,根据输入数据的位值来改变储存单元的电容充电状态。

具体来说,操作电压高时,扩展门打开传递电压至位线,电容充电导致位值为1;操作电压低时,扩展门关闭,位线无电压传递,电容不充电导致位值为0。

6. 刷新操作:为了保持存储的数据不丢失,六管单元SRAM

需要周期性刷新操作。

刷新操作会读取每个储存单元的数据,并写回以再次存储,以此更新电容状态。

需要注意的是,六管单元SRAM存储器的每个储存单元需要

占用相当大的面积,因此使用大量的储存单元构成SRAM存

储器会占用较大的芯片面积。

但是,它的读写速度较快,功耗较低,适合用于高速缓存和寄存器等需要快速读写的应用场景。

基于Cadence软件下的SRAM6T存储单元的介绍与设计

基于Cadence软件下的SRAM6T存储单元的介绍与设计作者:张斐洋来源:《中国新通信》 2017年第22期【摘要】文章主要以静态随机存储区(SRAM)6T 存储单元为基础,首先介绍了6T 存储单元的基本结构与工作原理, 并总结了其优缺点。

然后使用cadence 软件中的Virtuoso@Schematic Editing 对6 管单元电路进行设计以实现读写的基本功能。

最后在单管电路的基础上,通过外围电路的搭建与体系结构的设计,实现一款基于深亚微米CMOS 工艺下的128×8 位的SRAM 设计。

【关键词】静态随机存取存储器 CMOS 6 管单元深亚微米SRAM 设计电路仿真一、引言静态随机存取存储器(Static Random Access Memory, 简称SRAM),采用静态存储方式,靠双稳态电路存储信息,信息存储可靠,只要不断电存储信息就不会丢失[1]。

相比动态随机存取存储器(Dynamic Random Access Memory, 简称DRAM)靠电容存储信息,SRAM 单元电路复杂,占用面积大,因此集成度不如DRAM 高[1]。

但是SRAM 作为非挥发性存储器,其工作速度快、功耗低、与目前市场上标准工艺相兼容等优点,使其常用来作高速缓冲存储器(cache),并广泛用于PC、移动通信、智能卡等多种电子产品中[2]。

MOS 存储器的发展一直遵循着摩尔定律,集成度以每三年4 倍的速度增长,同时计算机的发展与普及对大容量、高性能存储器的需求越来越高,所以MOS 存储器的规模越来越大, 集成度越来越高,用来满足当前数字集成电路对存储器各性能的要求,特别是随着片上系统(System OnChip,SOC)的发展,片上集成的SRAM 已成为数字系统中非常重要的组成部分[3]。

SRAM 单元有多种基本结构,由于CMOS 存储单元可以解决电阻负载单元中功耗与可靠性的矛盾,目前SRAM 普遍采用CMOS 6T 结构。

SRAM的工作原理——6个MOS来讲述原理,醍醐灌顶 共13页

2019/7/22

10

• SRAM的操作

• Reading

• 假定存储的内容为1, 即在Q处的电平为高. 读周期之初,两根位线预充值为逻 辑1, 随后字线WL充高电平,使得两个访问控制晶体管M5与M6通路。第二步 是保存在Q的值传递给位线BL在它预充的电位,而泻掉(BL非)预充的值, 这是通过M1与M5的通路直接连到低电平使其值为逻辑0 (即Q的高电平使得晶 体管M1通路). 在位线BL一侧,晶体管M4与M6通路,把位线连接到VDD所代表 的逻辑1 (M4作为P沟道场效应管,由于栅极加了(Q非)的低电平而M4通路). 如果存储的内容为0, 相反的电路状态将会使(BL非)为1而BL为0. 只需要 (BL非)与BL有一个很小的电位差,读取的放大电路将会辨识出哪根位线 是1哪根是0. 敏感度越高,读取速度越快。

2019/7/22

• SRAM的操作

• SRAM的基本单元有3种状态:standby (电路处于空闲), reading (读)与writing (修 改内容).

• SRAM的读或写模式必须分别具有"readability"(可读)与"write stability"(写稳 定).

• Standby

请继续后面的学习 相信你会更了解

2019/7/22

5

• 反相器

• 反相器,是一种电路器件,其输出是输入的逻辑非。 如图所示的CMOS静态反相器,由两个互补的金属氧化 物半导体场效应管(MOSFET)组成,源极连接在高电平 的是P沟道场效应管,源极连接在低电平的是N沟道场 效应管。输入电路接在两个场效应管的栅极上,输出 电路从两个场效应管的连接处接出。当输入低电平, 则P沟道场效应管开通,N沟道场效应管关闭,输出高 电平。当输入高电平,则N沟道场效应管开通,P沟道 场效应管关闭,输出低电平。这就实现了“反相”输 出。

cmos电路动态功耗

cmos电路动态功耗CMOS电路是一种常用的数字电路设计技术,其动态功耗是指在切换过程中电路产生的功耗。

本文将从CMOS电路的基本原理、动态功耗的产生机制、减少动态功耗的方法等方面进行阐述。

一、CMOS电路的基本原理CMOS电路是由n型和p型MOSFET(金属氧化物半导体场效应晶体管)组成的。

n型MOSFET的导通由输入信号的高电平控制,p型MOSFET的导通由输入信号的低电平控制。

CMOS电路的优点是功耗低、噪声小、速度快、抗干扰能力强等。

二、动态功耗的产生机制动态功耗主要由两个部分组成:充电功耗和开关功耗。

1. 充电功耗:当CMOS电路切换时,由于电容的充放电过程会产生能量损耗,这部分损耗即为充电功耗。

充电功耗与电路的频率、电压幅值、电容大小等因素有关。

2. 开关功耗:当CMOS电路切换时,由于n型和p型MOSFET的导通和截止过程会产生短暂的瞬态电流,从而产生能量损耗,这部分损耗即为开关功耗。

开关功耗与电路的频率、输入信号的变化速度、晶体管的阈值电压等因素有关。

三、减少动态功耗的方法为了降低CMOS电路的动态功耗,可以采取以下方法:1. 降低电路频率:降低电路频率可以减少充电功耗和开关功耗。

但需要注意的是,降低频率可能会影响电路的工作速度。

2. 降低电压幅值:降低电压幅值可以降低充电功耗和开关功耗。

但需要注意的是,降低电压幅值可能会影响电路的噪声容限和抗干扰能力。

3. 优化电路结构:合理设计电路结构可以减少动态功耗。

例如,采用低阈值电压的晶体管、减少电容的大小等。

4. 优化输入信号:优化输入信号的变化速度可以减少开关功耗。

例如,采用渐变的输入信号,而非突变的输入信号。

5. 采用电源管理技术:通过采用电源管理技术,如动态电压调节(DVS)、动态频率调节(DFS)等,可以实现根据电路负载情况来调整电压和频率,从而降低功耗。

总结:CMOS电路的动态功耗是在切换过程中产生的功耗,主要由充电功耗和开关功耗组成。