DSP测试题及答案

DSP

一、填空1. DSP的基本结构是采用____________结构,即程序和数据是分开的。

2.直流电机的控制主要采用的控制方式是____________。

3. DSP芯片的前缀“LF”说明片内有___________存储器;而以“LC”为前缀的芯片,片内有____________工艺的程序存储器。

4.寄存器ST1的CNF位决定B0的作用,当CNF=________时,映射到程序存储空间,CNF=__________时映射到数据存储空间。

5.当工作于______________计数模式时,通用定时器会产生一个非对称波形。

6.若系统时钟频率为40MHz,SCI的BRR值设置为4,则SCI的异步波特率为_________。

7.WD复位关键字寄存器(WDKEY),向WDKEY写入55h后紧接着写入_________则清楚WDCNTR寄存器。

8.自动排序器的两种工作模式分别是____ ____和_____ ____。

9.同传统的单片机中断处理方式类似,DSP中断的处理也有两种方法,分别是__________和____________。

10. DSP对外部存储器和外部功能器件的片选方法有两种:___________和____________。

答案:1、哈佛 2、电枢控制法 3、Flash、CMOS4、1、05、连续递增6、1067、AAh8、不中断的排序模式、启动/停止模式 9. 查询法、回调法10、片选法、译码选通法1.DSP与单片机、嵌入式微处理器的最大区别是能够________、_________地进行数字信号处理运算。

2. DSP的基本结构是采用____________结构,即程序和数据是分开的。

3. DSP的应用非常广泛,试举一个应用的例子_____ ___。

4. 数模转换过程可分为两个时段_____ ___和_____ ____5.如果m是一个特定的读写操作的所要求的时钟周期(CLKOUT)的数目,w是附件的等待状态的数目,那么操作将会花费___________个周期。

电子科技大学智慧树知到“电子信息工程”《DSP技术》网课测试题答案4

电子科技大学智慧树知到“电子信息工程”《DSP技术》网课测试题答案(图片大小可自由调整)第1卷一.综合考核(共15题)1.在状态位寄存器ST1中,选用堆栈指针(SP)的直接寻址方式时()。

A.CPL=0B.CPL=1C.CMPT=0D.CMPT=12.把立即数80H装入累加器A指令是()。

A.LD #80h,AB.LD 80h,AC.LD #80h,16,AD.LD 80h,16A3.实时操作系统RTOS的任务有四种状态()。

A.运行、就绪、挂起、等待B.开始、就绪、挂起、等待C.执行、睡眠、挂起、等待D.运行、就绪、挂起、睡眠4.下列TMS320C54x的中断,不是可屏蔽中断的是()。

A.againB.readC.setD.reset5.TMS320C54X DSP微处理器采用的是()结构。

A.哈佛结构B.冯诺依曼结构C.矩阵结构D.以上都不是6.TMS320C54X DSP汇编指令的操作数域中,()前缀表示的操作数为间接数寻址的地址。

A.*B.#C.@D.&7.对于RTOS,内核调度的基本单位就是()。

A.程序B.进程C.任务D.线程8.TMS320C54X DSP微处理器采用的是()结构。

A.哈佛结构B.冯·诺依曼结构C.矩阵结构D.以上都不是9.在DSP中,CCS的初始化配置文件是()。

A.init.gelB.std.hC.loadctrl.exeD.init.ini10.DSP处理器是专门设计用来进行()数字信号处理的微处理器。

A.高速B.哈佛结构C.可控D.低速11.C54x采用()级流水线结构。

A.4B.3C.2D.612..sect ".vectors"rst: B _c_int00 ;复位中断向量的入口 NOP NOP .space 18*4*16tint: B timeout ;定时器0的中断向量的入口 NOP NOP".sect"伪指令的作用是()。

DSP芯片的原理与开发技术课后题部分答案

DSP课后习题答案总结第一章:概述1.2 简述DSP应用系统的典型结构和特点答:DSP系统的典型结构和工作过程:①对输入信号进行带限滤波和抽样;②进行A/D变换,将信号变换成数字比特流;③根据系统要求,DSP芯片对输入信号按照特定算法进行处理;④D/A转换,将处理后的数字样值转换为模拟信号;⑤平滑滤波,得到连续的模拟信号波形。

DSP系统的特点:接口方便、编程方便、稳定性好、精度高、可重复性好、集成方便等。

1.3 简述DSP应用系统的一般设计过程。

答:1.定义系统性能指标2.采用高级语言进行性能模拟3.设计实时DSP应用系统4.借助开发工具进行软硬件调试5.系统集成与独立系统运行1.8 设计DSP应用系统时,如何选择合适的DSP芯片。

答:根据实际应用系统的需要选择,以达到系统的最优化设计。

一般来说,需要考虑:DSP芯片的运算速度:DSP芯片的运算速度衡量指标:①指令周期;②MAC时间;③FFT执行时间;④MIPS;⑤MOPS;⑥MFLOPS;⑦BOPSDSP芯片的价格:DSP芯片的硬件资源DSP芯片的运算精度:一般字长为16bits,浮点芯片一般为32bitsDSP芯片的开发工具DSP芯片的功耗其他因素:例如,DSP芯片的封装形式、质量标准、供货情况、生命周期等。

1.11 中英文全称对照:DSP:Digital Signal ProcessingTI:Texa InstrumentsMAC:Multillier and AccumulatorMIPS:Million Istructions Per SecondMOPS: Million Operations Per SecondMFLOPS: Million Floating-point Operations Per SecondBOPS:Billion Operations Per secondDIP:Dual In-line PackagePGA:Pin Grid ArryPLCC:Plastic Leaded Chip CarrierPQFP:Plastic Quad Flat PackPWM:Pulse Width Modulation第二章:DSP芯片的基本结构和特性2.2 ALU和累加器的区别。

DSP考试题全解

第一章4、F2812和F2810的区别F2812有外部存储器接口TMS320F2810没有;TMS320F2812有128K的Flash TMS320F2810仅64K;F2812具有外部扩展接口XINTF,高达1MW的寻址空间,支持可编程的等待状态和读写选通时序,提供三个独立的片选信号,而F2810没有。

5、TMS320F281x系列DSP芯片有哪些外部接口?串行通信外设:一个高速同步串行外设接口(SPI),两个UART接口模块(SCI),增强的CAN2.0B接口模块,多通道缓冲串口(McBSP);其它外设:锁相环(PLL)控制的时钟倍频系数,看门狗定时模块,三个外部中断,3个32位CPU定时器,128位保护密码,高达56个通用I/O引脚。

思考题:1、TMS320F281x系列中的F2810、F2811、 F2812间有何区别?TMS320F2812有外部存储器接口,而TMS320F2811和TMS320F2810没有。

TMS320F2812和TMS320F2811有128K的Flash,而TMS320F2810仅64K。

2、与单片机相比,DSP有何特点?DSP器件具有较高的集成度。

DSP具有更快的CPU,更大容量的存储器,内置有波特率发生器和FIFO 缓冲器。

提供高速、同步串口和标准异步串口。

有的片内集成了A/D和采样/保持电路,可提供PWM输出。

DSP器件采用改进的哈佛结构,具有独立的程序和数据空间,允许同时存取程序和数据。

内置高速的硬件乘法器,增强的多级流水线,使DSP器件具有高速的数据运算能力。

DSP器件比16位单片机单指令执行时间快8~10倍完成一次乘加运算快16~30倍。

DSP器件还提供了高度专业化的指令集,提高了FFT快速傅里叶变换和滤波器的运算速度。

此外,DSP器件提供JTAG接口,具有更先进的开发手段,批量生产测试更方便,开发工具可实现全空间透明仿真,不占用用户任何资源。

软件配有汇编/链接C编译器、C源码调试器。

DSP课后习题答案--李建

第一章:1、数字信号处理的实现方法一般有哪几种?(1)在通用的计算机上用软件实现(2)在通用计算机系统中加上专用的加速处理机实现(3)用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理(4)用通用的可编程DSP 芯片实现,可用于复杂的数字信号处理算法(5)用专用的DSP 芯片实现(6)用基于通用dsp 核的asic 芯片实现2、简单的叙述一下dsp 芯片的发展概况?答:第一阶段,DSP 的雏形阶段(1980 年前后)代表产品:S2811。

主要用途:军事或航空航天部门第二阶段,DSP 的成熟阶段(1990 年前后)代表产品:TI 公司的TMS320C20 主要用途:通信、计算机领域第三阶段,DSP 的完善阶段(2000 年以后)代表产品:TI 公司的TMS320C54 主要用途:各行业领域3、可编程dsp 芯片有哪些特点?(1)采用哈佛结构:冯.诺依曼结构,哈佛结构,改进型哈佛结构(2)采用多总线结构(3)采用流水线技术(4)配有专用的硬件乘法-累加器(5) 具有特殊的dsp 指令(6)快速的指令周期(7) 硬件配置强(8)支持多处理器结构(9)省电管理和低功耗4、什么是哈佛结构和冯.诺依曼结构?它们有什么区别?哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成, 大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯.诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

区别: 哈佛:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

硬件工程师面试题集(含答案-很全)

硬件工程师面试题集(含答案-很全)硬件工程师面试题集(DSP,嵌入式系统,电子线路,通讯,微电子,半导体)1、下面是一些基本的数字电路知识问题,请简要回答之。

(1) 什么是Setup和Hold 时间?答:Setup/Hold Time 用于测试芯片对输入信号和时钟信号之间的时间要求。

建立时间(Setup Time)是指触发器的时钟信号上升沿到来以前,数据能够保持稳定不变的时间。

输入数据信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个T就是建立时间通常所说的SetupTime。

如不满足Setup Time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿到来时,数据才能被打入触发器。

保持时间(Hold Time)是指触发器的时钟信号上升沿到来以后,数据保持稳定不变的时间。

如果Hold Time 不够,数据同样不能被打入触发器。

(2) 什么是竞争与冒险现象?怎样判断?如何消除?答:在组合逻辑电路中,由于门电路的输入信号经过的通路不尽相同,所产生的延时也就会不同,从而导致到达该门的时间不一致,我们把这种现象叫做竞争。

由于竞争而在电路输出端可能产生尖峰脉冲或毛刺的现象叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

(3) 请画出用 D 触发器实现 2 倍分频的逻辑电路答:把 D 触发器的输出端加非门接到 D 端即可,如下图所示:(4) 什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?答:线与逻辑是两个或多个输出信号相连可以实现与的功能。

在硬件上,要用OC 门来实现(漏极或者集电极开路),为了防止因灌电流过大而烧坏OC 门,应在OC 门输出端接一上拉电阻(线或则是下拉电阻)。

(5) 什么是同步逻辑和异步逻辑?同步电路与异步电路有何区别?答:同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系.电路设计可分类为同步电路设计和异步电路设计。

《数字媒体技术》习题与答案

《数字媒体技术》习题与答案(解答仅供参考)一、名词解释1. 数字媒体技术:数字媒体技术是一门涉及计算机科学、信息工程、艺术设计等多个领域的交叉学科,主要研究如何通过数字化手段对文字、图像、音频、视频等多媒体信息进行采集、处理、存储、传播和展示的一系列技术方法与应用。

2. 数据压缩:数据压缩是将原始的数字媒体数据通过特定算法减少其在存储或传输时所需的比特数,以节省存储空间或提高传输效率的技术。

常见的数据压缩格式如JPEG用于图像,MP3用于音频,H.264用于视频。

3. 数字信号处理(DSP):数字信号处理是一种利用计算机或其他专用硬件设备对数字信号进行分析、变换、滤波、增强等操作的技术,广泛应用于语音识别、图像处理、通信系统等领域。

4. 交互式多媒体:交互式多媒体是指用户可以通过输入设备与数字媒体内容进行实时互动的一种媒体形式,如触摸屏应用、虚拟现实、增强现实等技术,能够根据用户的输入改变展示的内容和方式。

5. 流媒体技术:流媒体技术是一种使多媒体数据能边下载边播放的技术,无需等待整个文件下载完毕即可开始观看或收听,显著提高了用户体验,常见于在线视频、网络直播等领域。

二、填空题1. 在数字音频编码中,PCM(______)编码是最基本的编码方式,它将模拟声音信号转换为数字信号。

答案:脉冲编码调制2. ______技术是实现虚拟现实的关键技术之一,它通过追踪用户头部运动来实时更新显示画面视角。

答案:头部跟踪3. 在数字图像处理领域,________通常用于检测图像中的边缘和轮廓,它是图像分析和特征提取的基础。

答案:边缘检测4. MPEG-4标准不仅包括音视频编码标准,还支持对象的描述和合成,即基于内容的________。

答案:编码5. HTML5新增的<canvas>标签提供了在网页上绘制图形的能力,可以创建动态、交互式的________内容。

答案:二维图形三、单项选择题1. 下列哪种数字图像文件格式不支持透明通道?A. PNGB. JPEGC. GIFD. BMP答案:B2. 关于数字视频压缩编码,以下哪项表述是错误的?A. H.264/AVC编码因其高压缩率和高画质而被广泛应用B. MPEG-2主要用于DVD和早期的卫星电视广播C. VP9是Google推出的开源视频编解码器,性能优于H.264D. HEVC/H.265编码标准的压缩效率比H.264高出约一倍答案:C (VP9虽然性能优秀,但在某些场景下仍无法全面超越H.264)3. 在多媒体计算机系统中,负责对各种媒体信息进行实时处理和控制的核心部件是:A. 显卡B. 声卡C. CPUD. 多媒体处理器答案:D4. Flash动画制作软件的主要特点是:A. 支持矢量图形编辑,适合创作小体积但清晰度高的动画B. 只能制作静态图片,不能制作动画C. 不支持交互式功能,所有动画都是预设好的序列D. 仅适用于网页广告,不适合开发复杂的游戏或教育软件答案:A5. 针对移动互联网环境下的多媒体传输优化,采用________技术可以有效降低带宽需求和延迟。

DSP复习题

《DSP 复习题》一题名词解释20哈佛结构,流水线,MIPS,MAC,MOPS,MFLOPS,DARAM(双访问存储器)二题填空题25●DSP的选择应从数据格式,数据宽度,运算速度,存储器的安排,开发的难易程度,支持多处理器,功耗和电源管理以及器件的封装几个方面来考虑。

●CAN的通信距离最远可达10KM(传输速度为5Kbps);最高通信速度可达1Mbps(传输距离40m)。

●TMS320F2812中串行外设接口SPI是一个高速的同步串行输入输出接口,其可编程的传输数据长度为 1~16位,工作于全双工时需要4个引脚参与数据传送,它们分别是 SPISIMO,SPISOMI,SPISTE,SPICLK ,并且具有两种工作方式,分别为主模式和从模式●串行总线与并行总线相比,具有较少的控制和数据线的优点,因而得到广泛应用。

串行接口可分为三种,分别为单总线、双总线和多总线接口。

SPI属于多总线接口。

●哈佛结构可以获得更高的数据处理速度。

TMS320F2812 采用了增强哈佛结构总线数目一共有6条,它们分别是PAB,DRAB,DWAB,PRDB,DRDB,DWDB三题简答题251、TMS320F2812的片内外设中,比如SCI,SPI和McBSP,大量采用FIFO用于串行数据传输。

试述什么是FIFO,其又有什么特点?(见笔记)2、试画出基本DSP系统的构成图,并加以说明。

(P2页)3、试画出DSP应用系统的设计流程图,并加以说明(P3页)4、简述什么是DSP(数字信号处理器),其有什么特点?(P5)5、试说明TI公司DSP芯片分类及其各自的特点和应用范围。

(P6)6、简述TMS320F2812 的SCI通信接口的特点;7、简述TMS320F2812 的SPI通信接口的特点;接受和发送可同时操作(可通过软件屏蔽调发送功能)通过中断(Interrupt)或查询方式(Poll Algorithms)实现发送和接收操作12个SPI模块控制寄存器(其中3个是FIFO,每个寄存器16位,低字节有效,高字16X16发送/接受FIFO,同时可延时发送(0~256个SPICLK 时钟)9、结合图说明TMS320F2812 锁相环工作原理。

《学习强国》考试题库100题DSP【含答案】

《学习强国》测试题库100题[含参考答案]一、填空题1.漫云女子不英雄,万里乘风独向东。

诗思一帆海空阔,梦魂三岛月玲珑。

铜驼已陷悲回首,汗马终惭未有功。

如许伤心家国恨,那堪客里度春风。

这是女革命者秋瑾的《日人石井君索和即用原韵》,家国恨中应不包括(护国运动)2.每个人都是生态环境的保护者.建设者.受益者,没有哪个人是旁观者.局外人.批评家,谁也不能只说不做.置身事外。

要增强全民【节约意识】.【环保意识】.【生态意识】,培育生态道德和行为准则,开展全民绿色行动,动员全社会都以实际行动减少能源资源消耗和污染排放,为生态环境保护作出贡献。

3.强调,展形象,就是要推进国际传播能力建设,讲好中国故事.传播好中国声音,向世界展示【真实】.【立体】.【全面】的中国,提高国家文化软实力和中华文化影响力。

4.董必武同志的诗句“烟雨迷蒙访旧踪”访的是浙江嘉兴【D南湖】5.山洪灾害降雨强度预警信号的颜色等级,由低到高,黄色——橙色——红色6.变量和因变量各是:自变量是一天中的时间,因变量是温度7.发源于长白山的松花江滋养了松北大地..表述错误的是:松花江是中国最小的支流8.纳税人赡养一位以及被赡养的赡养支出,纳税为独生子女的按照每月2000标准扣除9.我国的中央银行是中国人民银行10.“宁德位于福建东北翼沿海,是中国大黄鱼之乡11.52.1963年出土于陕西省宝鸡市宝鸡县贾村镇的(何尊),造型…。

12.下面哪一诗句与“纸上得来终觉浅”同出自于一首诗?(A少壮工夫老始成)13.防范化解重大风险,是各级党委.政府和领导干部的政治职责,大家要坚持【守土有责】.【守土尽责】,把防范化解重大风险工作做实做细做好。

14.(煤炭.稀土和石油天然气)是内蒙古的优势矿产资源15.中华人民共和国的一切权利属于(人民)16.刘禹锡诗“千淘万漉虽辛苦”的下一句是(吹尽狂沙始到金)。

17.“语不惊人死不休”属于(律诗)。

18.下列不是伪科学的说法是(通过深度学习,人工智能可以模仿人的思维)。

dsp原理及应用试题及答案

dsp原理及应用试题及答案一、选择题(每题2分,共20分)1. DSP的全称是()。

A. Digital Signal ProcessorB. Digital Sound ProcessorC. Digital System ProcessorD. Digital Storage Processor答案:A2. 在DSP系统中,用于实现数字信号处理的处理器是()。

A. CPUB. GPUC. DSPD. MCU答案:C3. 下列哪个不是DSP的特点?()A. 高速度B. 低功耗C. 高成本D. 可编程答案:C4. DSP芯片中,用于存储程序和数据的存储器是()。

A. ROMB. RAMC. SRAMD. DRAM答案:C5. 在DSP应用中,通常使用哪种类型的算法来处理信号?()A. 线性算法B. 非线性算法C. 离散算法D. 连续算法答案:C6. DSP在音频处理中的主要应用不包括()。

A. 音频压缩B. 音频去噪C. 视频编码D. 音频增强答案:C7. 下列哪个是DSP编程语言?()A. CB. C++C. JavaD. Python答案:A8. DSP的指令周期通常比通用微处理器的指令周期()。

A. 长B. 短C. 相等D. 不可比较答案:B9. 在数字信号处理中,FFT算法主要用于()。

A. 信号滤波B. 信号压缩C. 信号变换D. 信号增强答案:C10. DSP系统设计中,通常不包括以下哪个步骤?()A. 系统建模B. 算法实现C. 硬件选择D. 软件测试答案:D二、填空题(每题2分,共20分)1. DSP的内部结构通常由_____、_____、_____和_____组成。

答案:CPU,存储器,输入/输出接口,总线2. 在DSP系统中,_____用于控制数据的流动。

答案:总线3. DSP的编程通常使用_____语言,因为它具有高效的执行速度。

答案:汇编4. DSP在图像处理中,常用于实现_____和_____等操作。

DSP原理及应用考试卷答案

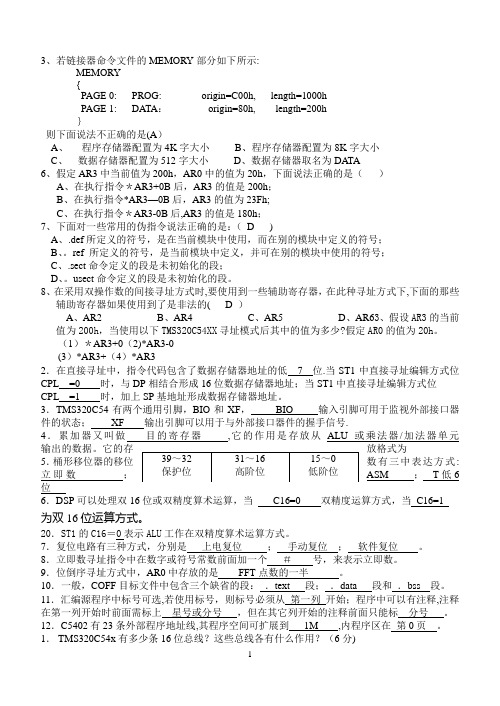

精品文档3、若链接器命令文件的MEMORY部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DATA: origin=80h, length=200h}则下面说法不正确的是(A)A、程序存储器配置为4K字大小B、程序存储器配置为8K字大小C、数据存储器配置为512字大小D、数据存储器取名为DATA6、假定AR3中当前值为200h,AR0中的值为20h,下面说法正确的是()A、在执行指令*AR3+0B后,AR3的值是200h;B、在执行指令*AR3-0B后,AR3的值为23Fh;C、在执行指令*AR3-0B后,AR3的值是180h;7、下面对一些常用的伪指令说法正确的是:(D )A、.def所定义的符号,是在当前模块中使用,而在别的模块中定义的符号;B、.ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

8、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的那些辅助寄存器如果使用到了是非法的( D )A、AR2B、AR4C、AR5D、AR63、假设AR3的当前值为200h,当使用以下TMS320C54XX寻址模式后其中的值为多少?假定AR0的值为20h。

(1)*AR3+0 (2)*AR3-0(3)*AR3+ (4)*AR32.在直接寻址中,指令代码包含了数据存储器地址的低7 位。

当ST1中直接寻址编辑方式位CPL =0 时,与DP相结合形成16位数据存储器地址;当ST1中直接寻址编辑方式位CPL =1 时,加上SP基地址形成数据存储器地址。

3.TMS320C54有两个通用引脚,BIO和XF,BIO 输入引脚可用于监视外部接口器件的状态;XF 输出引脚可以用于与外部接口器件的握手信号。

4.累加器又叫做目的寄存器,它的作用是存放从ALU或乘法器/加法器单元输出的数据。

DSP课后习题问题详解

第一章1.简述典型实时数字信号处理系统组成部分。

答:包括:抗混叠滤波器(Anti-aliasing filter)、模数转换器ADC(Analog-to-Digital Converter)、数字信号处理、数模转换器DAC(Digital-to-Analog Converter)和抗镜像滤波器(Anti-image filter) 。

2.简述X86处理器完成实时数字信号处理的优缺点。

答:利用X86处理器完成实时数字信号处理。

特点是处理器选择范围宽,主板及外设资源丰富,有多种操作系统可供选择,开发、调试较为方便;缺点是数字信号处理能力不强,硬件组成较为复杂,系统体积、重量较大,功耗较高,抗环境影响能力较弱。

3.简述数字信号处理器的主要特点。

答:(1)存储器采用哈佛或者改进的哈佛结构;(2)内部采用了多级流水;(3)具有硬件乘法累加单元;(4)可以实现零开销循环;(5)采用了特殊的寻址方式;(6)高效的特殊指令;(7)具有丰富的片内外设。

4.给出存储器的两种主要结构,并分析其区别。

答:存储器结构分为两大类:冯·诺依曼结构和哈佛结构。

冯·诺依曼结构的特点是只有一个存储器空间、一套地址总线和一套数据总线;指令、数据都存放在这个存储器空间中,统一分配地址,所以处理器必须分时访问程序和数据空间。

哈佛结构程序存储器空间和数据存储器空间分开,具有多套地址、数据总线,哈佛结构是并行体系结构,程序和数据存于不同的存储器空间,每个存储器空间独立编址、独立访问。

5.简述选择数字信号处理器所需要考虑的因素。

答:应考虑运算速度、算法格式和数据宽度、存储器类型、功耗和开发工具。

6.给出数字信号处理器的运算速度指标,并给出其具体含义。

答:常见的运算速度指标有如下几种:(1)指令周期:执行一条指令所需的最短时间,数值等于主频的倒数;指令周期通常以ns(纳秒)为单位。

例如,运行在200MHz的TMS320VC5510的指令周期为5ns。

DS原理与应用考试复习题答案

D S原理与应用考试复习题答案The pony was revised in January 2021填空:1.TI公司的定点DSP系列、TMS320C5000系列和系列。

2.TMS320X2812主频高达150mhz,采用哈佛总线结构模式。

3.TMS320X2812芯片的封装方式有176引脚的PGF低剖面四芯线扁平LQFP封装和179针的GHH球形网络阵列BGA封装。

4.TMS320X2812的事件管理器模块包括 2个通用定时器、 3个比较单元、 3个捕获单元、以及 1个正交编码电路。

5.CMD文件的有两大功能,一是通过MEMORY伪指令来指示存储空间,二是通过sections伪指令来分配到存储空间。

6.“# pragma DATA_SECTION”命令用来定义数据段,“# pragma DATA_SECTION”命令用来定义。

7.TMS320X2812三级中断分别是CPU级、 PIE中断和外设级。

8.F2812存储器被划分成程序空间和数据空间、保留区和 CPU中断向量。

9.SCI模块的信号有外部信号、控制信号和中断信号。

10.F2812 DSP中传送执行指令所需的地址需要用到 PAB 、DRAB和EAB 这3条地址总线。

语言程序经过编译后会生成两大类的段:代码段和数据段。

简答:1.DSP芯片有哪些主要特点?DSP的主要特点有:1.哈佛结构2.多总线结构3.流水线结构4.多处理单元5特殊的DSP指令 6.指令周期短7.运算精度高8.硬件配置强。

2.简述典型DSP应用系统的构成。

一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等组成。

输入信号首先进行带限滤波和抽样,然后进行数模变换将信号变换成数字比特流,根据奈奎斯特抽样定理,对低通模拟信号,为保持信号的不丢失,抽样频率至少必须是输入带限信号最高频率的2倍。

3.简述DSP应用系统的一般设计开发过程。

DSP测试题及答案

DSP测试题及答案1、什么是哈佛结构和冯·诺伊曼(VonNeuman)结构?它们有什么区别?答:(1)冯·诺伊曼(VonNeuman)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

(2)哈佛(Harvard)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

两者区别:哈佛(Harvard)结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯·诺伊曼(VonNeuman)结构:当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

2、TMS320VC5416-160的指令周期是多少毫秒?它的运算速度是多少MIPS?答:TMS320VC5416-160的指令周期16n,它的运算速度是160MIPS。

3、TMS320C54某芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?答:(1)六个操作阶段。

(2)各个阶段执行的任务:①预取指P:将PC中的内容加载到PAB②取指F:将读取到的指令字加载到PB③译码D:将PB的内容加载IR,对IR的内容译码④寻址A:CPU将数据1或数据2的读地址或同时将两个读地址分别加载到数据地址总线DAB和CAB中,并对辅助寄存器或堆栈指针进行修正。

⑤读数R:将读出的数据1和数据2分别加载到数据总线DB和CB中。

DSP原理及应用考试卷答案

3、若链接器命令文件的MEMORY 部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DATA : origin=80h, length=200h}则下面说法不正确的是(A )A 、 程序存储器配置为4K 字大小B 、程序存储器配置为8K 字大小C 、 数据存储器配置为512字大小D 、数据存储器取名为DATA6、假定AR3中当前值为200h ,AR0中的值为20h ,下面说法正确的是( )A 、在执行指令*AR3+0B 后,AR3的值是200h ;B 、在执行指令*AR3—0B 后,AR3的值为23Fh;C 、在执行指令*AR3-0B 后,AR3的值是180h ;7、下面对一些常用的伪指令说法正确的是:( D )A 、.def 所定义的符号,是在当前模块中使用,而在别的模块中定义的符号;B 、。

ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C 、.sect 命令定义的段是未初始化的段;D 、。

usect 命令定义的段是未初始化的段。

8、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的那些辅助寄存器如果使用到了是非法的( D )A 、AR2B 、AR4C 、AR5D 、AR63、假设AR3的当前值为200h ,当使用以下TMS320C54XX 寻址模式后其中的值为多少?假定AR0的值为20h 。

(1)*AR3+0(2)*AR3-0(3)*AR3+(4)*AR32.在直接寻址中,指令代码包含了数据存储器地址的低 7 位.当ST1中直接寻址编辑方式位CPL =0 时,与DP 相结合形成16位数据存储器地址;当ST1中直接寻址编辑方式位CPL =1 时,加上SP 基地址形成数据存储器地址。

3.TMS320C54有两个通用引脚,BIO 和XF , BIO 输入引脚可用于监视外部接口器件的状态; XF 输出引脚可以用于与外部接口器件的握手信号.4.累加器又叫做 目的寄存器 ,它的作用是存放从ALU 或乘法器/加法器单元 输出的数据。

DSP技术与应用习题库 2

一、填空题第一章1.数字信号处理特点大量的实时计算(FIR、IIR、FFT),数据具有高度重复(乘积和操作在滤波、卷积和FFT中等常见)。

2.信号处理的作用信号改善、信号检测、估计等。

3.信号处理的方法信号波形分析/变换、滤波、现代谱估计/分析、自适应滤波等。

4.信息系统包括采集、传输、处理等。

5.数字信号处理常用算法有FIR滤波、IIR滤波、离散傅里叶变换、卷积等。

6.处理器速度的提高得益于器件水平、处理器结构、并行技术等。

7.DSP结构特点包括哈弗结构、流水线技术、硬件乘法器、多处理单元、特殊的DSP指令。

8.DSP芯片按用途分为通用型DSP 、专用型DSP 。

9.DSP芯片按数据格式分为浮点型、定点型。

第二章1.C28x芯片具有C27x目标-兼容模式、C28x 模式、C2xLP源-兼容模式。

2.C28x芯片模式选择由ST1 中的OBJMODE 和AMODE 位组合来选定模式。

3.CPU内核由CPU 、仿真逻辑、接口组成。

4.CPU主要特性是、、、、。

5.CPU信号包括存储器接口信号、时钟和控制信号、复位和中断信号仿真信号。

6.TMS320F2812组成特点是32位、定点、改进哈佛结构、循环的寻址方式。

7.存储器接口有 3 组地址总线。

8.存储器接口有 3 组数据总线。

9.存储器接口地址总线有PAB 、DRAB 、DWAB 。

9.存储器接口数据总线有PRDB 、DRDB 、DWDB 。

10.CPU中断控制寄存器有IFR 、IER 、DBGIER 。

11.ACC累加器是32 位的,可表示为ACC 、AH 、AL 。

12.被乘数寄存器是32 位的,可表示为XT 、T 、TL 。

13.乘数结果寄存器是32 位的,可表示为P 、PH 、PL 。

14.数据页指针寄存器16 位的,有65536页,每页有64 存储单元。

数据存储空间容量是4M字。

15.堆栈指针复位后SP指向地址是0x000400h 。

第三章1.DSP芯片内部包含存储器类型有、、、、。

视听数字考试测试题及答案

视听数字考试测试题及答案一、选择题(每题2分,共20分)1. 数字信号处理中,将模拟信号转换为数字信号的过程称为:A. 采样B. 量化C. 编码D. 调制答案:A2. 在音频压缩技术中,通常使用哪种方法来减少数据量?A. 增加采样率B. 降低比特率C. 提高信噪比D. 增加动态范围答案:B3. 以下哪个不是数字视频的常见格式?A. MP4B. AVIC. DVDD. VHS答案:D4. 数字音频中,比特率是指:A. 每秒传输的比特数B. 音频信号的最高频率C. 音频信号的采样频率D. 音频信号的量化位数答案:A5. 在视频编码中,关键帧(Keyframe)和差异帧(Delta or P-frame)的主要区别是:A. 关键帧包含完整的图像信息,差异帧只包含变化部分B. 关键帧只包含变化部分,差异帧包含完整的图像信息C. 关键帧和差异帧都包含完整的图像信息D. 关键帧和差异帧都不包含完整的图像信息答案:A6. 以下哪种编码方式可以提供可变比特率(VBR)和恒定比特率(CBR)两种模式?A. MP3B. WAVC. AIFFD. FLAC答案:A7. 数字电视(DTV)与模拟电视(ATV)相比,主要优势不包括:A. 更高的图像质量B. 更丰富的节目内容C. 更高的信号传输效率D. 必须使用昂贵的接收设备答案:D8. 在音频编辑软件中,将一段音频的播放速度加快,但不改变其音调,应使用以下哪种效果处理?A. 时间拉伸B. 音高转换C. 增益调整D. 降噪处理答案:A9. 以下哪个不是数字水印技术的应用?A. 版权保护B. 内容认证C. 视频增强D. 隐藏信息传输答案:C10. 以下哪种音频格式支持无损压缩?A. MP3B. AACC. ALACD. WMA答案:C二、填空题(每题2分,共20分)11. 数字音频工作站(DAW)是一种专门用于________和________音频的软件应用程序。

答案:录制;编辑12. 在视频编辑中,将一个视频片段插入到另一个视频流中的技术称为________。

DSP程序题

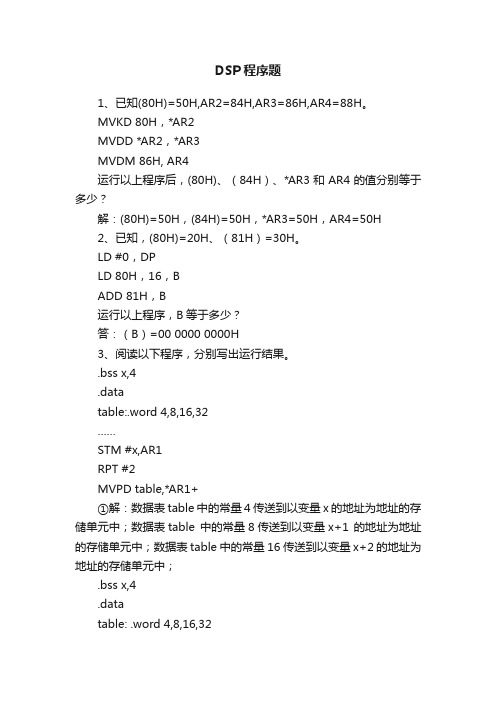

DSP程序题1、已知(80H)=50H,AR2=84H,AR3=86H,AR4=88H。

MVKD 80H,*AR2MVDD *AR2,*AR3MVDM 86H, AR4运行以上程序后,(80H)、(84H)、*AR3和AR4的值分别等于多少?解:(80H)=50H,(84H)=50H,*AR3=50H,AR4=50H2、已知,(80H)=20H、(81H)=30H。

LD #0,DPLD 80H,16,BADD 81H,B运行以上程序,B等于多少?答:(B)=00 0000 0000H3、阅读以下程序,分别写出运行结果。

.bss x,4.datatable:.word 4,8,16,32……STM #x,AR1RPT #2MVPD table,*AR1+①解:数据表table中的常量4传送到以变量x 的地址为地址的存储单元中;数据表table 中的常量8传送到以变量x+1 的地址为地址的存储单元中;数据表table中的常量16传送到以变量x+2 的地址为地址的存储单元中;.bss x,4.datatable: .word 4,8,16,32……STM #x,AR1RPT #2MVPD table,*+AR2②解:数据表table中的常量4传送到以变量x+1 的地址为地址的存储单元中;数据表table 中的常量8传送到以变量x+2 的地址为地址的存储单元中;数据表table中的常量16传送到以变量x+3 的地址为地址的存储单元中;4、指令●ADD #4568H,8,A,B //将4568H左移8位与A相加,赋给B。

●ADD A,-8,B//将A右移8位加上B,保存于B。

●ADD *AR3+,14,A//将AR3左移4加上A→A。

●DST B,*AR1-//B存到长字单元→AR1中,且AR减1。

●LDM AR1,A //存储器映像寄存器寻址方式,将映像寄存器加载累加器AR1→A的低位,其余位置0。

●LD #10H,4,A//将10H左移4位加载到累加器A中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、什么是哈佛结构和冯·诺伊曼(V on Neuman)结构?它们有什么区别?答:(1)冯·诺伊曼(V on Neuman)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

(2)哈佛(Harvard)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

两者区别:哈佛(Harvard)结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯·诺伊曼(V on Neuman)结构:当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

2、TMS320VC5416-160的指令周期是多少毫秒?它的运算速度是多少MIPS?答:TMS320VC5416-160的指令周期16ns,它的运算速度是160MIPS。

3、TMS320C54x芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?答:(1)六个操作阶段。

(2)各个阶段执行的任务:①预取指P:将PC中的内容加载到PAB②取指F:将读取到的指令字加载到PB③译码D:将PB的内容加载IR,对IR的内容译码④寻址A:CPU将数据1或数据2的读地址或同时将两个读地址分别加载到数据地址总线DAB和CAB中,并对辅助寄存器或堆栈指针进行修正。

⑤读数R:将读出的数据1和数据2分别加载到数据总线DB和CB中。

若是并行操作指令,可同时将数据3的写地址加载到数据地址总线EAB中。

⑥执行X:执行指令,写数据加载EB。

(3)完成一条指令需要的周期:需要:预取指周期、取指周期、译码周期、寻址周期和读数周期。

4、TMS320VC5402共有多少可屏蔽中断?它们分别是什么?NMI和RS属于哪一类中断源?答:(1)TMS320VC5402有13个可屏蔽中断。

(2)TMS320VC5402有的13个可屏蔽中断分别是:(课本56页最下面)属于外部硬件中断。

NMI和RS)3(.5、试分析下列程序的流水线冲突,画出流水线操作图。

如何解决流水冲突?STLM A,AR0STM#10,AR1LD*AR1,B答:流水线图如下图:解决流水线冲突:最后一条指令(LD*AR1,B)将会产生流水线冲突,在它前面加入一条NOP指令可以解决流水线冲突。

6、已知(1030H)=0050H,AR2=1040H,AR3=1060H,AR4=1080H。

MVKD1030H,*AR2MVDD*AR2,*AR3MVDM1060H,AR4运行以上程序后,(1030H)、(1040H)、*AR3和AR4的值分别等于多少?答:(1030H)=0050H,(1040H)=0050H,*AR3=0050H,AR4=0050H7、已知,(1080H)=0020H、(1081H)=0030H。

STM#1080H,AR0STM#1081H,AR1LD*AR0,16,BADD*AR1,B运行以上程序,B等于多少?0030H=0020)B(答:8、试阅读以下程序,分别写出运行结果。

(1).bss x,4.datatable:.word4,8,16,32……STM#x,AR1RPT#2MVPD table,*AR1+答:数据表table中的常量4传送到以变量x的地址为地址的存储单元中;数据表table中的常量8传送到以变量x+1的地址为地址的存储单元中;数据表table中的常量16传送到以变量x+2的地址为地址的存储单元中。

x,42).bss(.datatable:.word4,8,16,32……STM#x,AR1RPT#2MVPD table,*+AR2答:数据表table中的常量4传送到以变量x的地址为地址的存储单元中;数据表table中的常量8传送到以变量x+1的地址为地址的存储单元中;数据表table中的常量16传送到以变量x+2的地址为地址的存储单元中。

9、NOP指令不执行任何操作,它有什么作用?答:延时几个周期,避免流水线冲突;需要精确延时程序时,可能也会用到NOP指令。

10.说明.text段、.data段和.bss段分别包含什么内容?答:.text段(文本段),通常包含可执行代码;.data段(数据段),通常包含初始化数据;.bss段(保留空间段),通常为未初始化变量保留存储空间。

11.链接器能完成什么工作?链接器命令文件中,MEMORY命令和SECTIONS命令的任务是什么?答:链接器将各个目标文件合并起来,并完成如下工作:(1)将各个段配置到目标系统的存储器。

(2)对各个符号和段进行重新定位,并给它们指定一个最终的地址。

(3)解决输入文件之间的未定义的外部引用。

MEMORY命令的作用:MEMORY命令用来建立DSP应用系统中的存储器模型。

通过这条命令,可以定义系统中所包含的各种形式的存储器,以及它们占用的地址范围。

SECTION命令的作用:说明如何将输入段结合成输出段;在可执行程序中定义输出段;规定输出段在存储器中的存储位置;允许重新命名输出段。

.12.在堆栈操作中,PC当前地址为4020H,SP当前的地址为0013H,运行PSHM AR7的值分别为多少?和SP后,PCSP=0012H答:PC=4021H;试写出以下两条指令的运行结果:13.①EXPA A=FFFD876624T=0000的值各是多少?、T则以上指令执行后,B T=5答:A=0xFFFD876624;B②NORMT=FFF9B=420D0D0D0D,T的值各是多少?则以上指令执行后,B、B=0x841A1A1A,T=FFF9答:14.阅读以下程序,写出运行结果。

y,5.bss1,2,3,4,5table.wordAR2STM#y,#5RPTtable,*AR2+MVPD#0,B LDAR5LD#81h,#0,A STM#4,BRC STM#y,AR5STMsub-1RPTB*ARM5,B,A ADD A,*AR5+STL#0,B LD sub:)的值分别是多少?)和(,(84H85H)))运行以上程序后,(81H,(82H,(83H。

=#5)85H(,=#4)84H(,=#3)83H(,=#2)82H(,=#1)81H(答:滤波器的算法为,试用线性缓冲aaaaa x(n)+x(n-3)+15.FIR x(n-1)+y(n)=x(n-2)+x(n-4)42013区和直接寻址的方法实现。

“FIR1.ASM”.title答:.mmregs.def start“x”,ectPA0.set0PA1.set1.data1*32768/10;定义:a=COEF0.1.word4-3*32768/10;定义a=.word-0.335*32768/10;定义a=-0.5.word2-3*32768/10;定义a=.word-0.311*32768/10;定义a=-0.1.word0.text SSBXstart:FRCT#x+5,AR2STM STM#4,AR0#x+1,DPLD PORTR PA1,@x+1RPTZA,#4FIR1:*AR2-,COEF,AMACD A,*AR2STH*AR2+,PA0PORTWBDFIR1PORTR PA1,*AR2+0.end16.试用线性缓冲区和间接寻址的方法实现上题算法的FIR滤波器。

答:.title“FIR2.ASM”.mmregs.def start.bss y,1.usect“xn”,5xnb0 ect“0”,5PA0.set0PA11.set.data1*32768/10;定义table:a=0.1.word4-3*32768/10;定义a=.word-0.335*32768/10;定义 a.word=-0.52-3*32768/10;定义.word a=-0.311*32768/10;定义a=-0.1.word0.text SSBXFRCTstart:STM#a0,AR1#4RPT table,*AR1+MVPD#xn+4,AR2STM STM#b0+4,AR3STM#5,BK STM#-1,AR0LD#xn,DP PA1,@xn PORTR RPTZA,#4FIR2:MAC*AR2+0%,*AR3+0%,AA,@y STH PORTW@y,PA0BDFIR2PORTR PA1,*AR2+0%.end试分别说明下列有关定时器初始化和开放定时中断语句的功能:17.①STM#0080H,IFR答:清除定时器中断1标志位②STM#0080H,IMR答:允许定时器T1或DMAC1中断(使用哪一种中断由DMA通道优先级和使能控制寄存器DMPREC控制。

在复位以后,中断被配置为定时器T1中断)。

INTM③RSBX答:使能所有可屏蔽中断。

④STM#0279H,TCR答:设置定标计数器的值PSC为9;定时器分频系数为9;以PRD中的值加载TIM,以TDDR中的值加载PSC;定时器停止工作。

18.假设时钟频率为40MHZ,试编写在XF端输出一个周期为2ms的方波的程序。

答:(定时半周期=CLKOUT*(TDDR+1)*(PRD+1);1/2T=(1/40M)*(9+1)*(3999+1)=1ms);abc1.asm;定时器0寄存器地址TIM0.set0024HPRD0.set0025HTCR0.set0026H;K_TCR0:设置定时器控制寄存器的内容.set0b;K_TCR0_SOFTSoft=0.set0b;K_TCR0_FREEFree=0K_TCR0_PSC.set1001b;PSC=9HK_TCR0_TRB.set1b;TRB=1K_TCR0_TSS.set0b;TSS=0.set1001b K_TCR0_TDDR;TDDR=9K_TCR0.set K_TCR0_SOFT|K_TCR0_FREE|K_TCR0_PSC|K_TCR0_TRB|K_TCR0_TSS|K_TCR0_TDDR;初始化定时器0;Tt=25*(9+1)*(3999+1)=1000000(ns)=1(ms)STM#3999,TIM0STM#3999,PRD0STM#K_TCR0,TCR0;启动定时器0中断RET;定时器0的中断服务子程序:通过引脚XF给出.usect“vars”,1;若t0_flag=1则XF=1,若t0_flag=0t0_flag则XF=0time0_rev:PSHM TRNPSHM TST0PSHMST1PSHMt0_flag,BITF#1xf_out,NTC BCXF SSBX#0ST,t0_flagnext B.xf_out:RSBX XF#1,ST t0_flagST1POPMnext:POPM ST0POPM TPOPM TRNRETE19.试分别说明下列语句的功能:#SPCR10,SPSA0①STM#0001H,BSP0STM答:对串口控制寄存器SPCR10赋值。