APA2106SRCPRV中文资料

空调硬件设计说明书

北京环益创智科技有限公司Beijing Huanyi Creative Technology Co., Ltd.设备名称EQUIPMENT ITEM NAME 空调自控系统设备型号EQUIPMENT MODELHY6202文件标题 DOCUMENT TITLE硬件设计说明书Hardware Design Specification文件编号 DOCUMENT CODEHY-DA-2013-09-HDS客户名称 Customer Name河北大安制药有限公司0 供批准For approval版本Rev. 日期Date 目的 Purpose 编制 Write 审核Review 批准Approval文件名称硬件设计说明书设备名称空调自控系统生产单位北京环益创智科技有限公司使用单位河北大安制药有限公司空调自控系统硬件设计说明书姓名部门签名/日期编制技术研发中心审核技术研发中心批准技术研发中心目录1前言 (5)2总览 (5)3参考文件 (5)4术语 (6)5计算机和服务器系统 (7)5.1工作站计算机系统 (7)5.1.1最小硬件要求 (7)5.1.2详细说明 (8)5.2服务器系统 (8)5.2.1最小硬件要求 (8)5.2.2详细说明 (9)6光纤网络系统 (9)6.1网络设计原则 (9)6.1.1总体设计原则 (9)6.1.2设备选型依据 (10)6.2网络设计方案 (10)6.2.1方案概述 (10)6.2.2设备选型清单 (11)6.3网络设备简介 (11)6.3.1SR1024系列交换机 (11)7自控系统 (12)7.1自控概述 (12)7.2硬件要求 (12)7.2.1DDC要求 (12)7.2.2HMI要求 (12)7.2.3电气设备要求 (13)7.3控制柜设计 (13)7.4控制柜清单 (13)7.4.1动力柜清单: (13)7.4.2自控柜清单: (15)7.5控制柜安装应用 (16)8阀门仪表 (16)8.1电动冷冻水调节阀选型 (16)8.2电动蒸汽调节阀选型 (16)8.3风阀执行器选型 (17)8.4传感器选型 (17)8.4.1温湿度传感器 (17)8.4.2温度传感器 (18)8.4.3微差压传感器 (18)8.4.4压力传感器 (18)8.4.5设备联动传感器和开关型的传感器 (18)8.5空调控制设备 (18)8.5.1空调核心控制器 (19)8.5.2传感器 (22)8.5.3执行器 (24)8.5.4自动控制柜设备方案 (27)9环境 (28)9.1湿度 (28)9.2温度 (28)9.3外部干扰 (28)9.4安全 (28)10供电 (28)10.1接地保护 (28)10.2电源 (28)1 前言本文件由北京环益创智科技有限公司根据河北大安制药有限公司对于洁净空调自控系统的用户要求而起草。

ZR36060PQC中文资料(List Unclassifed)中文数据手册「EasyDatasheet - 矽搜」

应用

s 桌面视频编辑子系统 s PCMCIA视频采集卡 s 数码相机

Байду номын сангаас

ZR36060

综合JPEG编解码器

s 接口各种主机控制器,范围从 专用高性能ZR36057 PCI控制器

以通用低成本微控制器

s 灵活压缩数据接口: - 8位主模式下,支持高达30兆字节传输/ sec - 16位从模式,支持高达16.7转移 兆字节/秒 - 8位从模式,支持高达8.3兆字节传输/ sec

芯片中文手册,看全文,戳

集成JPEG编解码器

特征 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

应用. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

引脚说明. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

视频接口. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

视频可同步 - 主从模式. . . . . . . . . . . . . . . . . . . . . . 8 主模式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8 从模式. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.9

MPC2106CDG66中文资料

MOTOROLA FAST SRAM

MPC2105C•MPC2106C 3

元器件交易网

PIN ASSIGNMENT 178–LEAD DIMM TOP VIEW

VSS PD1/IDSDATA PD3 DH31 DH29 DH27 DH25 VDD CWE3 DH23 DH21 DH18 VSS DH16 CWE2 DH14 DH13 VCC DH10 DH8 CEW1 DH6 VDD DH4 VSS CLK0 VSS DH1 CWE0 DL31 DL30 VSS DL29 DL27 DL25 VCC CWE7 DL23 DL21 DL19 VSS DL17 CWE6 DL15 DL13 VSS DL10 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 016 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 VSS PD0/IDSCLK PD2 DH30 DH28 DH26 DH24 VDD DP3 DH22 DH20 DH19 VSS DH17 DP2 DH15 DH12 VCC DH11 DH9 DP1 DH7 VDD DH5 DH3 DH2 DH0 DP0 VSS CLK1 VSS DL28 DL26 DL24 DP7 VCC DL22 DL20 DL18 DL16 VSS DP6 DL14 DL12 DL11 VSS DL9 DL8 CWE5 DL6 VDD DL5 DL2 VSS CLK3 VSS CLK4 VSS CWE4 ALE VDD ADDR1 RESERVED CNTEN0 CNTEN1 A27 A24 A22 A20 VSS A18 A16 A15 A14 VDD A10 A8 A6 VSS A4 A2 A1 BURSTMODE VCC VALIDIN TWE STANDBY DIRTYOUT VSS 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 DP5 DL7 DL4 VDD DL3 DL1 DL0 VSS CLK2 VSS DP4 CG0 CG1 VDD ADDR0 RESERVED ADS0 ADS1 A28 A26 A25 A23 VSS A21 A19 A17 A13 VDD A12 A11 A9 VSS A7 A5 A3 A0 VCC TCLR MATCH TG DIRTYIN VSS

ZVP2106GTA中文资料

ZVP2106G

TYPICAL CHARACTERISTICS

ID(On) -On-State Drain Current (Amps) ID(On) -On-State Drain Current (Amps)

-3.5 -3.0 -2.5 -12V -2.0 -10V -1.5 -1.0 -0.5 0 0 -10 -20 -30 -40 -9V -8V -7V -6V -5V -4V -50 VGS= -20V -18V -14V -2.0 -1.8 -1.6 -1.4 -1.2 -1.0 -0.8 -0.6 -0.4 -0.2 0 0 -2 -4 -6 -8 VGS= -10V -9V -8V -7V -6V -5V -4V -3.5V -10

VGS-Gate Source Voltage (Volts)

Voltage Saturation Characteristics

RDS(ON) -Drain Source Resistance (Ω)

VGS=-5V -7V -8V -9V -10V 2.6

Transfer Characteristics

3 - 428

± 20

UNIT V mA A V W °C

2 -55 to +150

ELECTRICAL CHARACTERISTICS (at Tamb = 25°C unless otherwise stated).

MAX. UNIT CONDITIONS. V V nA

µA µA

ID=-1mA, VGS=0V ID=-1mA, VDS= VGS VGS=± 20V, VDS=0V VDS=-60 V, VGS=0 VDS=-48 V, VGS=0V, T=125°C(2) VDS=-18 V, VGS=-10V VGS=-10V,ID=-500mA VDS=-18V,ID=-500mA

艾维通信新一代宽带无线应急通信车应用技术基础知识介绍(V1.0)

艾维新一代宽带无线应急通信车应用技术基础知识介绍专网销售部夏海TEL(027)87568666-8896E-mail:xiahai@目录1 新一代宽带无线技术2 卫星通信技术3 集群通信技术车载无线通信网络覆盖指挥控制中心服务器监视矩阵管理终端麦克风无线终端HUB IP 电话存储器路由器卫星关口主站管理系统光纤卫星天线集群天线宽带天线宽带无线覆盖范围集群覆盖范围展开点1 新一代宽带无线技术公司是宽带无线通信运营商宽带无线的技术地位和采用标准2G3G802.16e802.16mLTE802.11n第二代第三代第四代802.16d宽带无线的频率1785MHZ~1805MHZ我国为公众移动网划分的频率有CDMA 825MHz~835MHz/870MHz~880MHzGSM 885MHz~915MHz/930MHz~960MHzGSM 1710MHz~1755MHz/1805MHz~1850MHz TD-SCDMA 2.3G~2.4G宽带无线基站的性能指标参数名称技术指标备注工作频段 1.785GHz ~1.805GHz信道间隔 1.25MHz的整数倍调制方式QPSK、16QAM、64QAM覆盖半径15km依据视通以及带宽要求基站最大扇区数3个下行最大系统吞吐量32Mbps/10MHz上行最大系统吞吐量10Mbps/10MHz信道复用方式OFDM/OFDMA双工模式TDD模式DL/UL Ratio = 3:1,2:1传输的数据类型IP数据包承载业务VoIP、VOD、视频会议、视频监控、移动办公和GPS等等网络协议IPv4/IPv6具备向IPv6网络协议平滑过渡的能力QoS UGS/rtPS/nrtPS/ertPS/BE支持5种服务级别协议技术性能比较技术IEEE 802.16e(WiMAX)3G WiFi(IEEE802.11a/g)吞吐量30M/s(10M/s)12M/s54M/s覆盖范围典型2-5km典型2-5km典型100m频率 1.8G 2.3G~2.4G 2.4G/5.8G载频带宽 1.25M~20M(灵活)10M20M物理层核心技术OFDMA,自适应调制解码CDMA,自适应调制解码CFDM双工方式TDD全双工TDD全双工TDD半双工移动性支持游牧式移动支持高速移动支持步行移动应用范围比较⏹3G 提供大范围、高速移动下的语音和中低速数据传输服务。

MRF6S21060NBR1中文资料

RF Power Field Effect TransistorsN-Channel Enhancement-Mode Lateral MOSFETsDesigned for W-CDMA base station applications with frequencies from 2110to 2170 MHz. Suitable for TDMA, CDMA and multicarrier amplifier applica-tions. To be used in Class AB for PCN-PCS/cellular radio and WLLapplications.•Typical 2-Carrier W-CDMA Performance: V DD = 28 Volts,I DQ = 610 mA, P out = 14 Watts Avg., Full Frequency Band, ChannelBandwidth = 3.84 MHz, PAR = 8.5 dB @ 0.01% Probability on CCDF.Power Gain — 15.5 dBDrain Efficiency — 26%IM3 @ 10 MHz Offset — -37 dBc in 3.84 MHz BandwidthACPR @ 5 MHz Offset — -40 dBc in 3.84 MHz Bandwidth•Capable of Handling 5:1 VSWR, @ 28 Vdc, 2140 MHz, 60 Watts CWOutput PowerFeatures•Characterized with Series Equivalent Large-Signal Impedance Parameters•Internally Matched for Ease of Use•Qualified Up to a Maximum of 32 V DD Operation•Integrated ESD Protection•Designed for Lower Memory Effects and Wide Instantaneous BandwidthApplications•200_C Capable Plastic Package•N Suffix Indicates Lead-Free Terminations. RoHS Compliant.•In Tape and Reel. R1 Suffix = 500 Units per 44 mm, 13 inch Reel.Table 1. Maximum RatingsRating Symbol Value Unit Drain-Source Voltage V DSS-0.5, +68Vdc Gate-Source Voltage V GS-0.5, +12Vdc Storage Temperature Range T stg-65 to +150°C Operating Junction Temperature T J200°C Table 2. Thermal CharacteristicsCharacteristic Symbol Value (1,2)Unit Thermal Resistance, Junction to CaseCase Temperature 79°C, 60 W CWCase Temperature 76°C, 14 W CWRθJC0.891.04°C/W1.MTTF calculator available at /rf. Select Tools/Software/Application Software/Calculators to accessthe MTTF calculators by product.2.Refer to AN1955, Thermal Measurement Methodology of RF Power Amplifiers. Go to /rf.Select Documentation/Application Notes - AN1955.Document Number: MRF6S21060NRev. 3, 5/2006 Freescale SemiconductorTechnical Data2RF Device DataFreescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1Table 3. ESD Protection CharacteristicsTest MethodologyClass Human Body Model (per JESD22-A114)1B (Minimum)Machine Model (per EIA/JESD22-A115) A (Minimum)Charge Device Model (per JESD22-C101)III (Minimum)Table 4. Moisture Sensitivity LevelTest MethodologyRating Package Peak TemperatureUnit Per JESD 22-A113, IPC/JEDEC J-STD-0203260°CTable 5. Electrical Characteristics (T C = 25°C unless otherwise noted)CharacteristicSymbolMinTypMaxUnitOff CharacteristicsZero Gate Voltage Drain Leakage Current (V DS = 68 Vdc, V GS = 0 Vdc)I DSS ——10μAdc Zero Gate Voltage Drain Leakage Current (V DS = 28 Vdc, V GS = 0 Vdc)I DSS ——1μAdc Gate-Source Leakage Current (V GS = 5 Vdc, V DS = 0 Vdc)I GSS——1μAdcOn Characteristics (DC)Gate Threshold Voltage(V DS = 10 Vdc, I D = 200 μAdc)V GS(th) 1.5 2.2 2.5Vdc Gate Quiescent Voltage(V DS = 28 Vdc, I D = 610 mAdc)V GS(Q)2 2.84Vdc Drain-Source On-Voltage(V GS = 10 Vdc, I D = 2.0 Adc)V DS(on)—0.3—VdcDynamic Characteristics (1)Reverse Transfer Capacitance(V DS = 28 Vdc ± 30 mV(rms)ac @ 1 MHz, V GS = 0 Vdc)C rss—1.5—pFFunctional Tests (In Freescale Test Fixture, 50 ohm system) V DD = 28 Vdc, I DQ = 610 mA, P out = 14 W Avg., f1 = 2112.5 MHz,f2 = 2122.5 MHz and f1 = 2157.5 MHz, f2 = 2167.5 MHz, 2-carrier W-CDMA, 3.84 MHz Channel Bandwidth Carriers. ACPR measured in 3.84 MHz Channel Bandwidth @ ±5 MHz Offset. IM3 measured in 3.84 MHz Bandwidth @ ±10 MHz Offset. PAR = 8.5 dB @ 0.01%Probability on CCDF.Power Gain G ps 13.515.516.5dB Drain EfficiencyηD 24.526—%Intermodulation Distortion IM3—-37-35dBc Adjacent Channel Power Ratio ACPR —-40-38dBc Input Return LossIRL—-14-10dB1.Part is internally matched both on input and output.MRF6S21060NR1 MRF6S21060NBR13RF Device DataFreescale SemiconductorFigure 1. MRF6S21060NR1(NBR1) Test Circuit SchematicZ100.270″ x 0.300″ Microstrip Z110.230″ x 0.080″ Microstrip Z120.310″ x 0.300″ Microstrip Z130.830″ x 0.080″ Microstrip Z140.200″ x 0.080″ Microstrip Z15 1.000″ x 0.080″ Microstrip Z16 1.100″ x 0.070″ Microstrip PCBArlon AD250, 0.030″, εr = 2.5Z10.250″ x 0.080″ Microstrip Z20.860″ x 0.080″ Microstrip Z30.300″ x 0.405″ Microstrip Z40.350″ x 0.080″ Microstrip Z50.350″ x 0.755″ Microstrip Z60.680″ x 0.080″ Microstrip Z70.115″ x 0.755″ Microstrip Z80.115″ x 1.000″ Microstrip Z90.240″ x 1.000″ MicrostripVTable 6. MRF6S21060NR1(NBR1) Test Circuit Component Designations and ValuesPartDescriptionPart NumberManufacturer C1100 nF Chip Capacitor CDR33BX104AKWS Kemet C2, C7 4.7 pF Chip Capacitors 100B4R7CW ATC C3, C8, C96.8 pF Chip Capacitors 100B6R8CWATC C4, C5, C6, C10, C1110 μF, 35 V Chip Capacitors GRM55DR61H106KA88LMurataR1 1 k W Chip Resistor R210 k W Chip Resistor R310 W Chip Resistor4RF Device DataFreescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1Figure 2. MRF6S21060NR1(NBR1) Test Circuit Component LayoutMRF6S21060NR1 MRF6S21060NBR15RF Device DataFreescale SemiconductorTYPICAL CHARACTERISTICSFigure 5. Two-Tone Power Gain versusOutput Power10111P out , OUTPUT POWER (WATTS) PEP200G p s , P O W E R G A I N (d B )100Figure 6. Third Order Intermodulation Distortionversus Output Power110200P out , OUTPUT POWER (WATTS) PEP1006RF Device DataFreescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1TYPICAL CHARACTERISTICS20010171P out , OUTPUT POWER (WATTS) CW10161412G p s , P O W E R G A I N (d B )151311Figure 10. Power Gain and Drain Efficiencyversus CW Output PowerFigure 11. Power Gain versus Output PowerP out , OUTPUT POWER (WATTS) CWI M D , I N T E R M O D U L A T I O N D I S T O R T I O N (d B c )12020406080100100MRF6S21060NR1 MRF6S21060NBR17RF Device DataFreescale SemiconductorTYPICAL CHARACTERISTICSW-CDMA TEST SIGNAL21010990T J , JUNCTION TEMPERATURE (°C)Figure 12. MTTF Factor versus Junction TemperatureThis above graph displays calculated MTTF in hours x ampere 2drain current. Life tests at elevated temperatures have correlated to better than ±10% of the theoretical prediction for metal failure. Divide MTTF factor by I D 2 for MTTF in a particular application.108107106120140160180190M T T F F A C T O R (H O U R S x A M P S 2)100110130150170200100.00011000PEAK−TO−AVERAGE (dB)Figure 13. CCDF W-CDMA 3GPP , Test Model 1, 64 DPCH, 67% Clipping, Single-Carrier Test Signal1010.10.010.0012468Figure 14. 2-Carrier W-CDMA Spectrumf, FREQUENCY (MHz)P R O B A B I L I T Y (%)(d B )2051510−5−10−15−20−25258RF Device DataFreescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1f MHz Z sourceΩZ load Ω2110214021703.31 - j5.353.06 - j4.923.17 - j5.167.59 - j8.396.71 - j8.835.84 - j8.62V DD = 28 Vdc, I DQ = 610 mA, P out = 14 W Avg.Z o = 10 ΩZ loadZ sourceZ source =Test circuit impedance as measured fromgate to ground.Z load=Test circuit impedance as measured from drain to ground.ZsourceZloadOutput Matching NetworkFigure 15. Series Equivalent Source and Load Impedancef = 2170 MHzf = 2110 MHzf = 2110 MHzf = 2170 MHzMRF6S21060NR1 MRF6S21060NBR19RF Device DataFreescale SemiconductorNOTES10RF Device Data Freescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1NOTESMRF6S21060NR1 MRF6S21060NBR111RF Device DataFreescale SemiconductorNOTES12RF Device Data Freescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1PACKAGE DIMENSIONSBOTTOM VIEW TO-270 WB-4PLASTICMRF6S21060NR1MRF6S21060NR1 MRF6S21060NBR113RF Device DataFreescale Semiconductor14RF Device Data Freescale SemiconductorMRF6S21060NR1 MRF6S21060NBR1MRF6S21060NR1 MRF6S21060NBR115RF Device DataFreescale SemiconductorInformation in this document is provided solely to enable system and softwareimplementers to use Freescale Semiconductor products. There are no express orimplied copyright licenses granted hereunder to design or fabricate any integratedcircuits or integrated circuits based on the information in this document.Freescale Semiconductor reserves the right to make changes without further notice toany products herein. Freescale Semiconductor makes no warranty, representation orguarantee regarding the suitability of its products for any particular purpose, nor doesFreescale Semiconductor assume any liability arising out of the application or use ofany product or circuit, and specifically disclaims any and all liability, including withoutlimitation consequential or incidental damages. “Typical” parameters that may beprovided in Freescale Semiconductor data sheets and/or specifications can and dovary in different applications and actual performance may vary over time. All operatingparameters, including “Typicals”, must be validated for each customer application bycustomer’s technical experts. Freescale Semiconductor does not convey any licenseunder its patent rights nor the rights of others. Freescale Semiconductor products arenot designed, intended, or authorized for use as components in systems intended forsurgical implant into the body, or other applications intended to support or sustain life,or for any other application in which the failure of the Freescale Semiconductor productcould create a situation where personal injury or death may occur. Should Buyerpurchase or use Freescale Semiconductor products for any such unintended orunauthorized application, Buyer shall indemnify and hold Freescale Semiconductorand its officers, employees, subsidiaries, affiliates, and distributors harmless against allclaims, costs, damages, and expenses, and reasonable attorney fees arising out of,directly or indirectly, any claim of personal injury or death associated with suchunintended or unauthorized use, even if such claim alleges that FreescaleSemiconductor was negligent regarding the design or manufacture of the part.Freescale t and the Freescale logo are trademarks of Freescale Semiconductor, Inc.All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2006. All rights reserved.How to Reach Us:Home Page:E-mail:support@USA/Europe or Locations Not Listed:Freescale SemiconductorTechnical Information Center, CH3701300 N. Alma School RoadChandler, Arizona 85224+1-800-521-6274 or +1-480-768-2130support@Europe, Middle East, and Africa:Freescale Halbleiter Deutschland GmbHTechnical Information CenterSchatzbogen 781829 Muenchen, Germany+44 1296 380 456 (English)+46 8 52200080 (English)+49 89 92103 559 (German)+33 1 69 35 48 48 (French)support@Japan:Freescale Semiconductor Japan Ltd.HeadquartersARCO Tower 15F1-8-1, Shimo-Meguro, Meguro-ku,Tokyo 153-0064Japan0120 191014 or +81 3 5437 9125support.japan@Asia/Pacific:Freescale Semiconductor Hong Kong Ltd.Technical Information Center2 Dai King StreetTai Po Industrial EstateTai Po, N.T., Hong Kong+800 2666 8080@For Literature Requests Only:Freescale Semiconductor Literature Distribution CenterP.O. Box 5405Denver, Colorado 802171-800-441-2447 or 303-675-2140Fax: 303-675-2150LDCForFreescaleSemiconductor@。

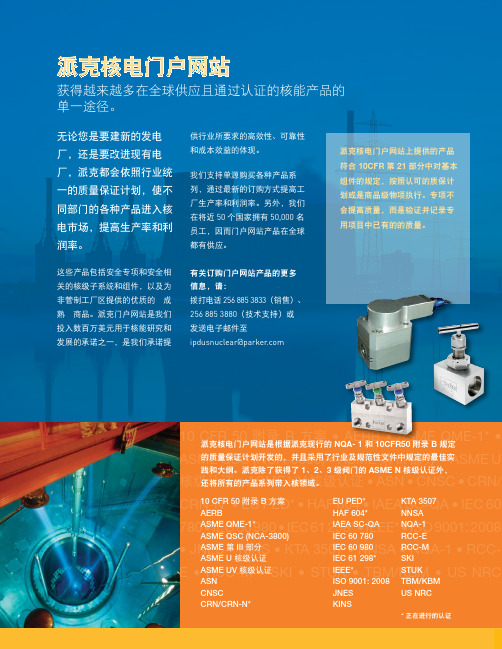

派克核电门户网站产品说明书

10 CFR 50 • AERB • ASME QME-1* • ASME QSC (NCA-3800) • ASME 第 III 部分 • ASME U核级认证核级认证 • ASN • CNSC CRN-N* HAF 604 • IAEA SC-QA 780 298* • IEEE* • ISO 9001: •E 派克核电门户网站无论您是要建新的发电厂,还是要改进现有电厂,派克都会依照行业统一的质量保证计划,使不同部门的各种产品进入核电市场,提高生产率和利润率。

这些产品包括安全专项和安全相关的核级子系统和组件,以及为非管制工厂区提供的优质的“成熟”商品。

派克门户网站是我们投入数百万美元用于核能研究和发展的承诺之一,是我们承诺提获得越来越多在全球供应且通过认证的核能产品的单一途径。

供行业所要求的高效性、可靠性和成本效益的体现。

我们支持单源购买各种产品系列,通过最新的订购方式提高工厂生产率和利润率。

另外,我们在将近 50 个国家拥有 50,000 名员工,因而门户网站产品在全球都有供应。

有关订购门户网站产品的更多信息,请:拨打电话 256 885 3833(销售)、256 885 3880(技术支持)或 发送电子邮件至 ipdusnuclear@parker .com派克核电门户网站是根据派克现行的 NQA- 1 和 10CFR50 附录 B 规定的质量保证计划开发的,并且采用了行业及规范性文件中规定的最佳实3 级阀门的 ASME N 核级认证外,派克核电门户网站上提供的产品符合 10CFR 第 21 部分中对基本组件的规定,按照认可的质保计划或是商品级物项执行。

专项不会提高质量,而是验证并记录专用项目中已有的的质量。

EU PED*HAF 604*IAEA SC-QA KTA 3507NNSANQA-1Parker Hannifin Ltd.Tachbrook Park DriveTachbrook Park,Warwick, CV34 6TU英国电话:+44 (0) 1926 317 878传真:+44 (0) 1926 317 855********************欧洲、中东和非洲AE – 阿联酋,迪拜电话:+971 4 8127100********************AT – 奥地利,维也纳新城电话:+43 (0)2622 23501-0*************************AT – 东欧,维也纳新城电话:+43 (0)2622 23501 900****************************AZ – 阿塞拜疆,巴库电话:+994 50 2233 458****************************BE/LU – 比利时,尼韦尔电话:+32 (0)67 280 900*************************BY – 白俄罗斯,明斯克电话:+375 17 209 9399*************************CH – 瑞士,埃托瓦电话:+41 (0)21 821 87 00*****************************CZ – 捷克共和国,Klecany电话:+420 284 083 111*******************************DE – 德国,卡尔斯特电话:+49 (0)2131 4016 0*************************DK – 丹麦,巴勒鲁普电话:+45 43 56 04 00*************************ES – 西班牙,马德里电话:+34 902 330 001***********************FI – 芬兰,万塔河电话:+358 (0)20 753 2500parker. ****************FR – 法国,Contamine s/Arve电话:+33 (0)4 50 25 80 25************************GR – 希腊,雅典电话:+30 210 933 6450************************HU – 匈牙利,布达佩斯电话:+36 23 885 470*************************IE – 爱尔兰,都柏林电话:+353 (0)1 466 6370*************************IT – 意大利,Corsico (MI)电话:+39 02 45 19 21***********************KZ – 哈萨克斯坦,阿拉木图电话:+7 7273 561 000****************************NL – 荷兰,奥尔登扎尔电话:+31 (0)541 585 000********************NO – 挪威,阿斯克尔电话:+47 66 75 34 00************************PL – 波兰,华沙电话:+48 (0)22 573 24 00************************PT – 葡萄牙,莱萨·达·帕尔梅拉电话:351 22 999 7360**************************RO – 罗马尼亚,布加勒斯特电话:+40 21 252 1382*************************RU – 俄罗斯,莫斯科电话:+7 495 645-2156************************SE – 瑞典,Spånga电话:+46 (0)8 59 79 50 00************************SK – 斯洛伐克,班斯卡·比斯特里察电话:+421 484 162 252**************************SL – 斯洛文尼亚,新梅斯托电话:+386 7 337 6650**************************TR – 土耳其,伊斯坦布尔电话:+90 216 4997081************************UA – 乌克兰,基辅电话:+380 44 494 2731*************************UK – 英国,沃里克电话:+44 (0)1926 317 878********************ZA – 南非,坎普顿公园电话:+27 (0)11 961 0700*****************************北美地区CA – 加拿大,安大略省米尔顿电话:+1 905 693 3000US – 美国,克利夫兰电话:+1 216 896 3000亚太地区AU – 澳大利亚,城堡山电话:+61 (0)2-9634 7777CN – 中国,上海电话:+86 21 2899 5000HK – 香港电话:+852 2428 8008IN – 印度,孟买电话:+91 22 6513 7081-85JP – 日本,东京电话:+81 (0)3 6408 3901KR – 韩国,首尔电话:+82 2 559 0400MY – 马来西亚,莎阿南电话:+60 3 7849 0800NZ – 新西兰,惠灵顿电话:+64 9 574 1744SG – 新加坡电话:+65 6887 6300TH – 泰国,曼谷电话:+662 186 7000-99TW – 台湾,台北电话:+886 2 2298 8987南美AR – 阿根廷,布宜诺斯艾利斯电话:+54 3327 44 4129BR – 巴西,圣若泽杜斯坎普电话:+55 800 727 5374CL – 智利,圣地亚哥电话:+56 2 623 1216MX – 墨西哥,阿波达卡电话:+52 81 8156 6000核电门户网站手册 M&K 12/10 1M派克授权的本地经销商© 2010 派克汉尼汾公司派克全球办事处联系信息欧洲产品信息中心免费电话:00 800 27 27 5374(AT, BE, CH, CZ, DE, DK, EE, ES, FI, FR, IE,IL, IS, IT, LU, MT, NL, NO, PL, PT, RU, SE,SK, UK, ZA)– 一点的方式。

ZVP2106A中文资料(diodeszetex)中文数据手册「EasyDatasheet - 矽搜」

2%

BV V I I

V V nA

µA µA

I =-1mA, V ID=-1mA, V V =± 20V, V V =-60 V, V V =-48 V, V V =-18 V, V V =-10V,I V =-18V,I

芯片中文手册,看全文,戳

p沟道增强 模式垂直 DMOS FET

ISSUE 2日 - 3月 94

特征

ZVP2106A

* 60电压V DS * R DS(on) =5Ω

D G

S

电子线

TO92兼容 绝对最大额定值 .

参数 漏源电压 连续漏极电流在T 漏电流脉冲 栅源电压 功耗在T 工作和存储温度范围 符号 值 单元

C-Capacitance (pF) -Gate Source Voltage (Volts) V V -Drain Source Voltage (Volts) Q-Charge (nC) 栅极电荷 V栅源电压

电容 V漏源电压

I V Gate Source Voltage (Volts) 传输特性

电压饱和特性 (Ω)

and V

-Drain Source Resistance

Normalised R

R I -Drain Current 导通电阻 V漏极电流 (Amps) 正常化 ř T -Junction Temperature (°C) 和V 与温度

V

-18V,

I =-500mA

(1)脉冲条件下进行测定.宽度=300μS.占空比 (2)抽样检测.

潘启panchip 2.4ghz无线收发soc芯片pan2416av产品说明书

PAN2416AV产品说明书2.4GHz无线收发SOC芯片V1.0PAN2416AV产品说明书2.4GHz单片高速无线收发SOC芯片概述PAN2416AV芯片是工作在2.400~2.483GHz世界通用ISM频段的单片无线收发芯片。

该芯片集成射频收发机、频率发生器、晶体振荡器、调制解调器和低功耗MCU等功能模块,并且支持一对多组网和带ACK的通信模式。

用户通过MCU的I/O口向芯片发出指令,芯片自动完成收发配置进行通信,并根据应答信息自动判断数据发送/接收是否成功,从而进行重发,丢包,继续发送和等待等操作,简化了用户程序。

发射输出功率、工作频道以及通信数据率均可配置。

PAN2416AV需要少量的外围器件,支持单层/双层印制电路板的方案。

主要特性1、功耗较低发射模式(2dBm)工作电流19mA;接收模式工作电流15mA;休眠电流2uA。

2、节省外围器件支持外围5个元器件,包括1颗晶振和少量电容;支持双层或单层印制板设计,可以使用印制板微带天线或者导线天线;芯片自带部分链路层的通信协议;配置少量的参数寄存器,使用方便。

3、性能优异250K/1M/2M bps模式的接收灵敏度为-91/-87/-83dBm;发射输出功率最大可达8dBm;抗干扰性好,接收滤波器的邻道抑制度高,接收机选择性较好。

4、集成MCU功能OTP:4K×16Bit;通用RAM:176×8Bit;MCU集成高精度12位ADC,内置WDT定时器、PWM输出、低压侦测电路等模块。

其它特性四线SPI 接口通信带自动扰码和CRC校验功能支持最大数据长度为32字节(两级FIFO)或者64字节(单级FIFO)SOP16封装1M / 2Mbps模式,需要晶振精度±40ppm 250kbps模式,需要晶振精度±20ppm 工作电压支持2.2~3.3V 工作温度支持-40~+85℃GFSK通信方式支持自动应答及自动重传支持RSSI检测功能10个GPIO中断源三路定时器应用方案无线鼠标电视和机顶盒遥控器无线游戏手柄遥控玩具常用遥控器智能家居版本修订时间更新内容相关文档V0.4 2016. 12 文字勘误V1.0 2017.09 文字修改目录1. 命名规则 (8)1.1 PAN2416AV命名规则 (8)1.2 PAN2416系列产品选择 (8)2. 主要电特性 (8)3. 极限最大额定值 (10)4. 系统结构方框图 (10)5. 引脚定义 (11)6. 芯片工作状态 (13)6.1 休眠模式 (14)6.2 待机模式-I(STB1) (14)6.3 待机模式-III(STB3) (14)6.4 待机模式-II(STB2) (14)6.5 接收模式 (14)6.6 发射模式 (14)7. 数据通信模式 (15)7.1 普通模式 (15)7.2 增强模式 (15)7.3增强发送模式 (16)7.4 增强接收模式 (16)7.5 增强模式下的数据包识别 (17)7.6 增强模式下的PTX和PRX的时序图 (17)7.7 增强模式下的接收端一对多通信 (17)7.8 DATA FIFO (19)7.9 中断引脚 (19)8. SPI控制接口 (19)8.1 SPI指令格式 (20)8.2 SPI 时序 (21)9. 控制寄存器 (22)10. 数据包格式描述 (32)10.1 普通模式的数据包形式 (32)10.2 增强模式的数据包形式 (33)10.3 增强模式的ACK包形式 (33)11. MCU寄存器 (34)11.1性能特性 (33)11.2系统结构框图 (34)11.3系统配置寄存器 (35)11.4在线串行编程 (36)12. 中央处理器(CPU) (37)12.1内存 (37)12.1.1程序内存 (37)12.1.2数据存储器 (41)12.2寻址方式 (43)12.2.1直接寻址 (43)12.2.2立即寻址 (43)12.2.3间接寻址 (43)12.3堆栈 (44)12.4工作寄存器(ACC) (45)12.4.1概述 (45)12.4.2 ACC应用 (45)12.5 程序状态寄存器(STATUS) (45)12.6 预分频器(OPTION_REG) (47)12.7程序计数器(PC) (48)12.8 看门狗计数器(WDT) (48)12.8.1 WDT周期 (48)12.8.2 看门狗定时器控制寄存器WDTCON (49)13. 系统时钟 (50)13.1 概述 (50)13.2 系统振荡器 (51)13.2.1 内部RC振荡 (51)13.3起振时间 (51)13.4振荡器控制寄存器 (51)14. 复位 (52)14.1上电复位 (52)14.2 掉电复位 (53)14.2.1掉电复位概述 (53)14.2.2掉电复位的改进办法 (54)14.3 看门狗复位 (54)15. 休眠模式 (55)15.1 进入休眠模式 (55)15.2 从休眠状态唤醒 (55)15.3 使用中断唤醒 (55)15.4 休眠模式应用举例 (56)15.5 休眠模式唤醒时间 (56)16. I/O端口 (57)16.1 PORTA (58)16.1.1 PORTA数据及方向控制 (58)16.1.2 PORTA模拟选择控制 (60)16.2 PORTB (60)16.2.1 PORTB数据及方向 (60)16.2.2 PORTB上拉电阻 (61)16.2.3 PORTB电平变化中断 (61)16.3 PORTC (62)16.3.1 PORTC数据及方向 (62)16.3.2 PORTC上拉电阻 (63)16.4 PORTE (63)16.4.1 PORTE数据及方向 (63)16.5 I/O使用 (64)16.5.1 写I/O口 (64)16.5.2 读I/O口 (64)16.6 I/O口使用注意事项 (65)17. 中断 (66)17.1 中断概述 (66)17.2 中断控制寄存器 (67)17.2.1 中断控制寄存器 (67)17.2.2 外设中断允许寄存器 (68)17.2.3 外设中断请求寄存器 (69)17.3 中断现场的保护方法 (70)17.4 中断的优先级,及多中断嵌套 (70)18. 定时计数器TIMER0 (71)18.1 定时计数器TIMER0概述 (71)18.2 TIMER0的工作原理 (72)18.2.1 8 位定时器模式 (72)18.2.2 8 位计数器模式 (72)18.2.3 软件可编程预分频器 (72)18.2.4 在TIMER0和WDT模块间切换预分频器 (72)18.2.5 TIMER0中断 (73)18.3 与TIMER0相关寄存器 (73)19. 定时计数器TIMER1 (74)19.1 TIMER1概述 (74)19.2 TIMER1 的工作原理 (74)19.3 TIMER1 预分频器 (74)19.4 TIMER1 中断 (74)19.5 TIMER1相关寄存器 (75)20. 定时计数器TIMER2 (75)20.1 TIMER2概述 (75)20.2 TIMER2的工作原理 (77)20.3 TIMER2相关的寄存器 (77)21. 模数转换(ADC) (79)21.1 ADC概述 (79)21.2 ADC配置 (79)21.2.1 端口配置 (79)21.2.2 通道选择 (80)21.2.3 ADC参考电压 (80)21.2.4 转换时钟 (80)21.2.5 ADC中断 (80)21.2.6 结果格式化 (80)21.3 ADC工作原理 (81)21.3.1 启动转换 (81)21.3.2 完成转换 (81)21.3.3 终止转换 (81)21.3.4 ADC在休眠模式下的工作原理 (81)21.3.5 A/D转换步骤 (81)21.4 ADC相关RAM (83)22. PWM模块 (85)22.1 PWM1 (85)22.2 PWM2 (86)22.3 PWM模式 (87)22.3.1 PWM周期 (88)22.3.2 PWM占空比 (88)22.3.3 PWM分辨率 (89)22.3.4 休眠模式下的操作 (89)22.3.5 系统时钟频率的改变 (89)22.3.6 复位的影响 (89)22.3.7 设置PWM操作 (89)23. MCU电气参数 (90)23.1 MCU DC特性 (90)23.2 MCU AC特性 (90)23.3指令一览表 (91)23.4 指令说明 (93)24. 典型应用电路(参考) (104)25. 封装尺寸 (105)26. 联系方式 (106)1. 命名规则1.1 PAN2416AV 命名规则图1.1 PAN2416系列产品命名规则1.2 PAN2416系列产品选择表1-1 PAN2416系列产品选择产品型号芯片版本 封装形式 PAN2416AV A V :SOP16 PAN2416AF A F :SOP142. 主要电特性表2-1 PAN2416AV 的RF 部分主要电特性参数值 特 性测试条件(VCC = 3V±5%,TA=25℃)最小 典型 最大 单位 休眠模式 2 uA 待机模式1 30 uA 待机模式3 650 uA 待机模式2 780 uA 发射模式 (-35dBm) 9 mA 发射模式 (-20dBm) 9.5 mA 发射模式 (0dBm) 16 mA 发射模式 (2dBm) 19 mA 发射模式 (8dBm) 30 mA 发射模式 (13dBm) 66 mA 接收模式 (250Kbps) 15 mA 接收模式 (1Mbps) 15.5 mA ICC接收模式 (2Mbps)16.5 mA 系统指标ƒOP 工作频率24002483MHzPLL res锁相环频率步径 1 MHz ƒXTAL晶振频率16 MHz DR码率0.25 2 Mbps ∆ƒ250K调制频偏@250Kbps 125 150 KHz ∆ƒ1M调制频偏@1Mbps 160 300 KHz ∆ƒ2M调制频偏@2Mbps 320 550 KHz FCH250K频道间隔@250Kbps 1 MHz FCH1M频道间隔@1Mbps 1 MHz FCH2M频道间隔@2Mbps 2 MHz发射模式指标PRF 典型输出功率 2 8 8 dBm PRFC 输出功率范围-35 8 dBmPBW1发射带数据调制的20dB带宽(250Kbps)500 KHzPBW2发射带数据调制的20dB带宽(1Mbps)1 MHzPBW3发射带数据调制的20dB带宽(2Mbps)2 MHz接收模式指标(注1)RX max误码率<0.1%时的最大接收幅度0 dBm RXSENS1 接收灵敏度(0.1%BER)@250Kbps-91 dBmRXSENS2 接收灵敏度(0.1%BER)@1Mbps-87 dBmRXSENS3 接收灵敏度(0.1%BER)@2Mbps-83 dBm接收模式邻道选择性C/I CO同频的通道选择性@250kbps 2 dBc C/I1ST第1相邻道选择性@250kbps -8 dBc C/I2ND第2相邻道选择性@250kbps -18 dBc C/I3RD第3相邻道选择性@250kbps -24 dBc C/I4TH第4相邻道选择性@250kbps -28 dBc C/I5TH第5相邻道选择性@250kbps -32 dBc C/I6TH第6相邻道选择性@250kbps -35 dBc C/I CO同频的通道选择性@1Mbps 10 dBc C/I1ST第1相邻道选择性@1Mbps 1 dBc C/I2ND第2相邻道选择性@1Mbps -18 dBc C/I3RD第3相邻道选择性@1Mbps -23 dBc C/I4TH第4相邻道选择性@1Mbps -28 dBc C/I5TH第5相邻道选择性@1Mbps -32 dBc C/I6TH第6相邻道选择性@1Mbps -35 dBc C/I CO同频的通道选择性@2Mbps 10 dBcC/I1ST第1相邻道选择性@2Mbps -6 dBcC/I2ND第2相邻道选择性@2Mbps -10 dBcC/I3RD第3相邻道选择性@2Mbps -22 dBcC/I4TH第4相邻道选择性@2Mbps -28 dBcC/I5TH第5相邻道选择性@2Mbps -34 dBc操作条件VDD 供电电压 2.2 3 3.3 VVSS 芯片地0 VV OH高电平输出电压VDD-0.3 VDD VV OL低电平输出电压VSS VSS+0.3 VV IH高电平输入电压VDD-0.3 VDD VV IL低电平输入电压VSS VSS+0.3 V*注1:在晶振16MHz的整数倍(如2416、2432MHz等)的频道及相邻正负1MHz的频道的接收灵敏度退化2dB;发射信号调制精度(EVM)退化10%。

ZVN2106中文资料

2.4

0.7

Normalised RDS(on) and VGS(th)

2.2 2.0 1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 -80 -60 -40 -20

ain Dr

ce an ist es R VGS=10V ce ID=1A ur So

VGS=VDS ID=1mA

gfs-Transconductance (S)

1.0

1.5

2.0

2.5

3.0

Q-Charge (nC)

Gate charge v gate-source voltage

3-363

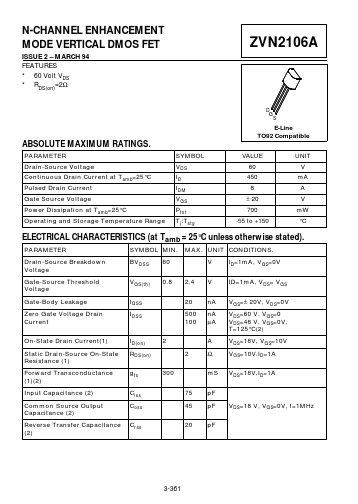

PARAMETER Drain-Source Voltage Continuous Drain Current at T amb=25°C Pulsed Drain Current Gate Source Voltage Power Dissipation at T amb=25°C Operating and Storage Temperature Range SYMBOL V DS ID I DM V GS P tot T j :T stg VALUE 60 450 8 ± 20 700 -55 to +150 UNIT V mA A V mW °C

0.5 0.4 0.3 0.2 0.1 0 0 2 4 6 8 10 VDS=10V

C-Capacitance (pF)

80 60 Ciss 40 20 Coss Crss 0 10 20 30 40 50

VGS-Gate Source Voltage (Volts)

VDS-Drain Source Voltage (Volts)

I D(on) R DS(on) g fs C iss C oss C rss

A2106V-111 PDF参数规格

Thermal Data

Parameter Thermal Resistance Junction to

Ambient

Symbol θja

SOP- 8 100

Units

oC /W

© Analog Vision Technology Inc. Proprietary & Confidential

6

A2106V V1.5 Jul 8, 2012

3

A2106V V1.5 Jul 8, 2012

Block Diagram

A2106V

CC/CV Mode Step Down Switching Regulator

Ordering and Marking Information

Signal Descriptions

Pin Configurations

Reversion # 1.0 1.1 1.2 1.3 1.3.1 1.4

Description New datasheet format released Modify MOS Ron Max value Modify Input Voltage Range Add Thermal Shut-down temperature range Add details for PCB layout guide Add UVLO Protection

Applications

■ Car charger ■ Portable charger applications

■ DC/DC converters with current limited

Typical Application Circuits

© Analog Vision Technology Inc. Proprietary & Confidential

APA2106SECK, 规格书,Datasheet 资料

SPEC NO: DSAD1018 APPROVED: WYNEC

REV NO: V.11 CHECKED: Allen Liu

DATE: APR/15/2011 DRAWN: J.Yu

PAGE: 1 OF 5 ERP: 1203000518

芯天下--/

Selection Guide

REV NO: V.11 CHECKED: Allen Liu

DATE: APR/15/2011 DRAWN: J.Yu

PAGE: 5 OF 5 ERP: 1203000518

芯天下--/

2.1x0.6mm RIGHT ANGLE SURFACE LED LAMP Super Bright Orange

Features

2.1mmX0.6mm right angle SMT LED, 1.0mm thickness. Low power consumption. Wide viewing angle. Ideal for backlight and indicator. Various colors and lens types available. Package: 2000pcs / reel. Moisture sensitivity level : level 3. RoHS compliant.

DATE: APR/15/2011 DRAWN: J.Yu

PAGE: 4 OF 5 ERP: 1203000518

芯天下--/

PACKING & LABEL SPECIFICATIONS

APA2106SECK

SPEC NO: DSAD1018 APPROVED: WYNEC

Recommended Soldering Pattern (Units : mm; Tolerance: ± 0.1)

安桥686功放说明书

bm

机播放操作。每次按下该按钮时,模式将按 复)、 (随机)顺序切换。

(单曲重复)、 (文件夹重

CLEAR 按钮:在电视屏幕上输入文本时删除已输入的所有字符。

11. 按钮:切换显示屏上的信息,并用于操作 RDS ( p62)。

12. 按钮:在设置期间使显示返回到以前状态。

13. MODE 按钮:用于切换 AM/FM 无线电台的自动调谐与手动调谐 ( p58),或

(ZONE 2) 中的前置主放大器。 15. SUBWOOFER PRE OUT 接口:使用重低音扬声器线缆连接有源重低音扬声

器。最多可以连接两个有源重低音扬声器。从每个 SUBWOOFER PRE OUT 接 口输出同一信号。

目录 ≫ 连接 ≫ 播放 ≫ 设置 ≫

10

前面板≫ 后面板≫ 遥控器≫

遥控器

49

34

基本操作

49

35

设备和支持的格式

51

36 播放 PC 和 NAS(Music Server)上的文件

52

37

Windows Media® Player 设置

52

37

播放

53

38

支持的音频格式

55

2

前面板≫ 后面板≫ 遥控器≫

Play Queue 初始设置 添加 Play Queue 信息 排序和删除 播放

AV RECEIVER

TX-NR686

使用手册

目录 ≫ 连接 ≫ 播放 ≫ 设置 ≫

目录

≫

连接

≫

- 连接扬声器

≫

播放

≫

设置

≫

故障排除

≫

附录

≫

补充信息

≫

ADSP-21060中文资料

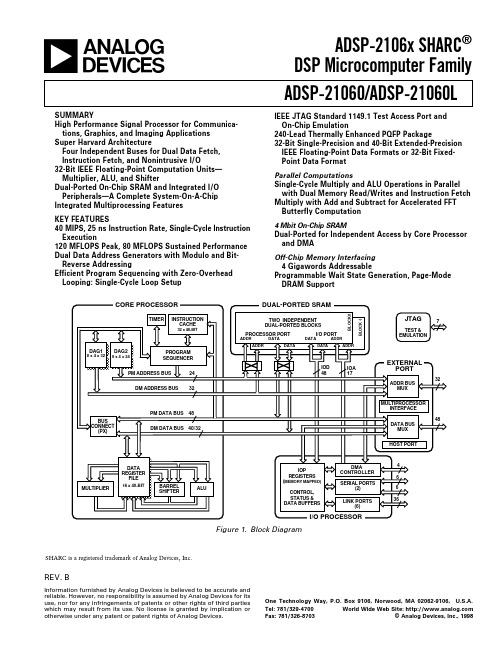

REV.BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aADSP-2106x SHARC ®DSP Microcomputer Family ADSP-21060/ADSP-21060LIEEE JTAG Standard 1149.1 Test Access Port and On-Chip Emulation240-Lead Thermally Enhanced PQFP Package32-Bit Single-Precision and 40-Bit Extended-Precision IEEE Floating-Point Data Formats or 32-Bit Fixed-Point Data FormatParallel ComputationsSingle-Cycle Multiply and ALU Operations in Parallel with Dual Memory Read/Writes and Instruction Fetch Multiply with Add and Subtract for Accelerated FFT Butterfly Computation 4 Mbit On-Chip SRAMDual-Ported for Independent Access by Core Processor and DMA Off-Chip Memory Interfacing 4 Gigawords AddressableProgrammable Wait State Generation, Page-Mode DRAM SupportSHARC is a registered trademark of Analog Devices, Inc.46636–2–ADSP-21060/ADSP-21060LREV. BDMA Controller10 DMA Channels for Transfers Between ADSP-2106xInternal Memory and External Memory, External Peripherals, Host Processor, Serial Ports, or Link PortsBackground DMA Transfers at 40 MHz, in Parallel with Full-Speed Processor Execution Host Processor Interface to 16- and 32-Bit Microprocessors Host Can Directly Read/Write ADSP-2106x InternalMemoryMultiprocessingGlueless Connection for Scalable DSP Multiprocessing ArchitectureDistributed On-Chip Bus Arbitration for Parallel Bus Connect of Up to Six ADSP-2106xs Plus HostSix Link Ports for Point-to-Point Connectivity and Array Multiprocessing240 Mbytes/s Transfer Rate Over Parallel Bus 240 Mbytes/s Transfer Rate Over Link Ports Serial PortsTwo 40 Mbit/s Synchronous Serial Ports with Companding HardwareIndependent Transmit and Receive FunctionsTABLE OF CONTENTSGENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 3ADSP-21000 FAMILY CORE ARCHITECTURE . . . . . . . 4ADSP-21060/ADSP-21060L FEA TURES . . . . . . . . . . . . . . 4DEVELOPMENT TOOLS . . . . . . . . . . . . . . . . . . . . . . . . . . 7PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . 8TARGET BOARD CONNECTOR FOR EZ-ICE ®PROBE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11RECOMMENDED OPERATING CONDITIONS (5 V) . 13ELECTRICAL CHARACTERISTICS (5 V) . . . . . . . . . . . 13POWER DISSIPATION ADSP-21060 (5 V) . . . . . . . . . . . .14RECOMMENDED OPERATING CONDITIONS (3.3 V) 15ELECTRICAL CHARACTERISTICS (3.3 V) . . . . . . . . . . 15POWER DISSIPATION ADSP-21060L (3.3 V) . . . . . . . . .16ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . .17TIMING SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . 17Memory Read—Bus Master . . . . . . . . . . . . . . . . . . . . . . . 20Memory Write—Bus Master . . . . . . . . . . . . . . . . . . . . . . 21Synchronous Read/Write—Bus Master . . . . . . . . . . . . . . 22Synchronous Read/Write—Bus Slave . . . . . . . . . . . . . . . . 24Multiprocessor Bus Request and Host Bus Request . . . . . 25Asynchronous Read/Write—Host to ADSP-2106x . . . . . . 27Three-State Timing—Bus Master, Bus Slave,HBR , SBTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29DMA Handshake . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Link Ports:1 × CLK Speed Operation . . . . . . . . . . . . . . 32Link Ports:2 × CLK Speed Operation . . . . . . . . . . . . . . 33Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35JTAG Test Access Port and Emulation . . . . . . . . . . . . . . . 38OUTPUT DRIVE CURRENTS . . . . . . . . . . . . . . . . . . . . . 39POWER DISSIPATION . . . . . . . . . . . . . . . . . . . . . . . . . . . 39TEST CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39ENVIRONMENTAL CONDITIONS . . . . . . . . . . . . . . . . 42240-LEAD METRIC PQFP PIN CONFIGURATIONS . . 43PACKAGE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 44ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44FIGURESFigure 1.ADSP-21060/ADSP-21060L Block Diagram . . . . 1Figure 2.ADSP-2106x System . . . . . . . . . . . . . . . . . . . . . . . 4Figure 3.Shared Memory Multiprocessing System . . . . . . . . 6Figure 4.ADSP-21060/ADSP-21060L Memory Map . . . . . 7Figure 5.Target Board Connector For ADSP-2106xEZ-ICE Emulator (Jumpers in Place) . . . . . . . . . . . . . . . 11Figure 6.JTAG Scan Path Connections for MultipleADSP-2106x Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . 11Figure 7.JTAG Clocktree for Multiple ADSP-2106xSystems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Figure 8.Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Figure 9.Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Figure 10.Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Figure 11.Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Figure 12.Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Figure 13.Memory Read—Bus Master . . . . . . . . . . . . . . . . 20Figure 14.Memory Write—Bus Master . . . . . . . . . . . . . . . 21Figure 15.Synchronous Read/Write—Bus Master . . . . . . . 23Figure 16.Synchronous Read/Write—Bus Slave . . . . . . . . . 24Figure 17.Multiprocessor Bus Request and Host BusRequest . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Figure 18a.Synchronous REDY Timing . . . . . . . . . . . . . . 27Figure 18b.Asynchronous Read/Write—Host toADSP-2106x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28Figure 19a.Three-State Timing (Bus Transition Cycle,SBTS Assertion) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29Figure 19b.Three-State Timing (Host Transition Cycle) . .29Figure 20.DMA Handshake Timing . . . . . . . . . . . . . . . . . 31Figure 21.Link Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34Figure 22.Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36Figure 23.External Late Frame Sync . . . . . . . . . . . . . . . . . 37Figure 24.IEEE 11499.1 JTAG Test Access Port . . . . . . . 38Figure 25.Output Enable/Disable . . . . . . . . . . . . . . . . . . . 40Figure 26.Equivalent Device Loading for AC Measurements (Includes All Fixtures) . . . . . . . . . . . . . . . . . . . . . . . . . . . 40Figure 27.Voltage Reference Levels for AC Measurements (Except Output Enable/Disable) . . . . . . . . . . . . . . . . . . . 40Figure 28.ADSP-2106x Typical Drive Currents(V DD = 5 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41Figure 29.Typical Output Rise Time (10%–90% V DD )vs. Load Capacitance (V DD = 5 V) . . . . . . . . . . . . . . . . . . .41Figure 30.Typical Output Rise Time (0.8 V–2.0 V)vs. Load Capacitance (V DD = 5 V) . . . . . . . . . . . . . . . . . . .41Figure 31.Typical Output Delay or Hold vs. Load Capacitance (at Maximum Case Temperature) (V DD = 5 V) . . . . . . . . .41Figure 32.ADSP-2106x Typical Drive Currents(V DD = 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41Figure 33.Typical Output Rise Time (10%–90% V DD )vs. Load Capacitance (V DD = 3.3 V) . . . . . . . . . . . . . . . . .41Figure 34.Typical Output Rise Time (0.8 V–2.0 V) vs. LoadCapacitance (V DD = 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . .42Figure 35.Typical Output Delay or Hold vs. Load Capacitance (at Maximum Case Temperature) (V DD = 3.3 V) . . . . . . . .42EZ-ICE is a registered trademark of Analog Devices, Inc.ADSP-21060/ADSP-21060L–3–REV. B GENERAL DESCRIPTIONThe ADSP-21060 SHARC—Super Harvard Architecture Com-puter—is a signal processing microcomputer that offers new capabilities and levels of performance. The ADSP-2106x SHARCs are 32-bit processors optimized for high performance DSP applications. The ADSP-2106x builds on the ADSP-21000 DSP core to form a complete system-on-a-chip, adding a dual-ported on-chip SRAM and integrated I/O peripherals sup-ported by a dedicated I/O bus.Fabricated in a high speed, low power CMOS process, the ADSP-2106x has a 25 ns instruction cycle time and operates at 40MIPS. With its on-chip instruction cache, the processor can execute every instruction in a single cycle. Table I shows performance benchmarks for the ADSP-2106x.The ADSP-2106x SHARC represents a new standard of inte-gration for signal computers, combining a high performance floating-point DSP core with integrated, on-chip system features including a 4 Mbit SRAM memory host processor interface,DMA controller, serial ports, and link port and parallel bus connectivity for glueless DSP multiprocessing.Figure 1 shows a block diagram of the ADSP-2106x, illustrating the following architectural features:Computation Units (ALU, Multiplier and Shifter) with a Shared Data Register FileData Address Generators (DAG1, DAG2)Program Sequencer with Instruction Cache Interval Timer On-Chip SRAMExternal Port for Interfacing to Off-Chip Memory and PeripheralsHost Port and Multiprocessor Interface DMA ControllerSerial Ports and Link Ports JTAG Test Access PortFigure 2 shows a typical single-processor system. A multi-processing system is shown in Figure 3.Table I.ADSP-21060/ADSP-21060L Benchmarks (@ 40 MHz)1024-Pt. Complex FFT0.46 ms 18,221 cycles (Radix 4, with Digit Reverse)FIR Filter (per Tap)25 ns 1 cycle IIR Filter (per Biquad)100 ns 4 cycles Divide (y/x)150 ns 6 cycles Inverse Square Root (1/√x )225 ns9 cyclesDMA Transfer Rate240 Mbytes/sS–4–ADSP-21060/ADSP-21060LREV. BADSP-21000 FAMILY CORE ARCHITECTUREThe ADSP-2106x includes the following architectural features of the ADSP-21000 family core. The ADSP-21060 is code- and function-compatible with the ADSP-21061 and ADSP-21062.Independent, Parallel Computation UnitsThe arithmetic/logic unit (ALU), multiplier and shifter all per-form single-cycle instructions. The three units are arranged in parallel, maximizing computational throughput. Single multi-function instructions execute parallel ALU and multiplier opera-tions. These computation units support IEEE 32-bit single-precision floating-point, extended precision 40-bit floating-point, and 32-bit fixed-point data formats.Figure 2.ADSP-2106x SystemData Register FileA general purpose data register file is used for transferring data between the computation units and the data buses, and for storing intermediate results. This 10-port, 32-register (16 pri-mary, 16 secondary) register file, combined with the ADSP-21000 Harvard architecture, allows unconstrained data flow between computation units and internal memory.Single-Cycle Fetch of Instruction and Two OperandsThe ADSP-2106x features an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the pro-gram memory (PM) bus transfers both instructions and data (see Figure 1). With its separate program and data memory buses and on-chip instruction cache, the processor can simulta-neously fetch two operands and an instruction (from the cache),all in a single cycle.Instruction CacheThe ADSP-2106x includes an on-chip instruction cache that enables three-bus operation for fetching an instruction and two data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This allows full-speed execution of core, looped operations such as digital filter multiply-accumulates and FFT butterfly processing.Data Address Generators with Hardware Circular BuffersThe ADSP-2106x’s two data address generators (DAGs) imple-ment circular data buffers in hardware. Circular buffers allow efficient programming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The two DAGs of the ADSP-2106x contain sufficient registers to allow the creation of up to 32 circular buffers (16 primary register sets, 16 second-ary). The DAGs automatically handle address pointer wrap-around, reducing overhead, increasing performance, andsimplifying implementation. Circular buffers can start and end at any memory location.Flexible Instruction SetThe 48-bit instruction word accommodates a variety of parallel operations, for concise programming. For example, the ADSP-2106x can conditionally execute a multiply, an add, a subtract and a branch, all in a single instruction.ADSP-21060/ADSP-21060L FEATURESAugmenting the ADSP-21000 family core, the ADSP-21060adds the following architectural features:Dual-Ported On-Chip MemoryThe ADSP-21060 contains four megabits of on-chip SRAM,organized as two blocks of 2 Mbits each, which can be config-ured for different combinations of code and data storage.Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor or DMA con-troller. The dual-ported memory and separate on-chip buses allow two data transfers from the core and one from I/O, all in a single cycle.On the ADSP-21060, the memory can be configured as a maxi-mum of 128K words of 32-bit data, 256K words of 16-bit data,80K words of 48-bit instructions (or 40-bit data), or combina-tions of different word sizes up to four megabits. All of the memory can be accessed as 16-bit, 32-bit, or 48-bit words.A 16-bit floating-point storage format is supported that effec-tively doubles the amount of data that may be stored on-chip.Conversion between the 32-bit floating-point and 16-bit floating-point formats is done in a single instruction.While each memory block can store combinations of code and data, accesses are most efficient when one block stores data,using the DM bus for transfers, and the other block storesinstructions and data, using the PM bus for transfers. Using the DM bus and PM bus in this way, with one dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache. Single-cycle execution is also maintained when one of the data operands is transferred to or from off-chip, via the ADSP-2106x’s external port.ADSP-21060/ADSP-21060L–5–REV. B Serial PortsThe ADSP-2106x features two synchronous serial ports that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. The serial ports can operate at the full clock rate of the processor, providing each with a maxi-mum data rate of 40 Mbit/s. Independent transmit and receive functions provide greater flexibility for serial communications.Serial port data can be automatically transferred to and from on-chip memory via DMA. Each of the serial ports offers TDM multichannel mode.The serial ports can operate with little-endian or big-endiantransmission formats, with word lengths selectable from 3 bits to 32 bits. They offer selectable synchronization and transmit modes as well as optional µ-law or A-law companding. Serial port clocks and frame syncs can be internally or externally generated.MultiprocessingThe ADSP-2106x offers powerful features tailored to multi-processing DSP systems. The unified address space (see Figure 4) allows direct interprocessor accesses of each ADSP-2106x’s internal memory. Distributed bus arbitration logic is included on-chip for simple, glueless connection of systems containing up to six ADSP-2106xs and a host processor. Master processor changeover incurs only one cycle of overhead. Bus arbitration is selectable as either fixed or rotating priority. Bus lock allows indivisible read-modify-write sequences for semaphores. A vector interrupt is provided for interprocessor commands. Maxi-mum throughput for interprocessor data transfer is 240 Mbytes/s over the link ports or external port. Broadcast writes allow simulta-neous transmission of data to all ADSP-2106xs and can be used to implement reflective semaphores.Link PortsThe ADSP-2106x features six 4-bit link ports that provide addi-tional I/O capabilities. The link ports can be clocked twice per cycle, allowing each to transfer eight bits per cycle. Link port I/O is especially useful for point-to-point interprocessor commu-nication in multiprocessing systems.The link ports can operate independently and simultaneously,with a maximum data throughput of 240 Mbytes/s. Link port data is packed into 32- or 48-bit words, and can be directly read by the core processor or DMA-transferred to on-chip memory.Each link port has its own double-buffered input and output registers. Clock/acknowledge handshaking controls link port transfers. Transfers are programmable as either transmit or receive.Program BootingThe internal memory of the ADSP-2106x can be booted at system power-up from either an 8-bit EPROM, a host proces-sor, or through one of the link ports. Selection of the boot source is controlled by the BMS (Boot Memory Select),EBOOT (EPROM Boot), and LBOOT (Link/Host Boot) pins.32-bit and 16-bit host processors can be used for booting.Off-Chip Memory and Peripherals InterfaceThe ADSP-2106x’s external port provides the processor’s inter-face to off-chip memory and peripherals. The 4-gigaword off-chip address space is included in the ADSP-2106x’s unified address space. The separate on-chip buses—for PM addresses,PM data, DM addresses, DM data, I/O addresses, and I/O data—are multiplexed at the external port to create an external system bus with a single 32-bit address bus and a single 48-bit (or 32-bit) data bus.Addressing of external memory devices is facilitated by on-chip decoding of high-order address lines to generate memory bank select signals. Separate control lines are also generated for sim-plified addressing of page-mode DRAM. The ADSP-2106x provides programmable memory wait states and external memory acknowledge controls to allow interfacing to DRAM and peripherals with variable access, hold, and disable time requirements.Host Processor InterfaceThe ADSP-2106x’s host interface allows easy connection to standard microprocessor buses, both 16-bit and 32-bit, with little additional hardware required. Asynchronous transfers at speeds up to the full clock rate of the processor are supported.The host interface is accessed through the ADSP-2106x’s exter-nal port and is memory-mapped into the unified address space.Four channels of DMA are available for the host interface; code and data transfers are accomplished with low software overhead.The host processor requests the ADSP-2106x’s external bus with the host bus request (HBR ), host bus grant (HBG ), and ready (REDY) signals. The host can directly read and write the internal memory of the ADSP-2106x, and can access the DMA channel setup and mailbox registers. Vector interrupt support is provided for efficient execution of host commands.DMA ControllerThe ADSP-2106x’s on-chip DMA controller allows zero-overhead data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simultaneously executing its program instructions.DMA transfers can occur between the ADSP-2106x’s internal memory and either external memory, external peripherals or a host processor. DMA transfers can also occur between the ADSP-2106x’s internal memory and its serial ports or link ports. DMA transfers between external memory and external peripheral devices are another option. External bus packing to 16-, 32-, or 48-bit words is performed during DMA transfers.Ten channels of DMA are available on the ADSP-2106x—two via the link ports, four via the serial ports, and four via the processor’s external port (for either host processor, otherADSP-2106xs, memory or I/O transfers). Four additional link port DMA channels are shared with serial port 1 and the exter-nal port. Programs can be downloaded to the ADSP-2106x using DMA transfers. Asynchronous off-chip peripherals can control two DMA channels using DMA Request/Grant lines (DMAR1-2, DMAG1-2). Other DMA features include inter-rupt generation upon completion of DMA transfers and DMA chaining for automatic linked DMA transfers.–6–ADSP-21060/ADSP-21060LREV. BFigure 3.Shared Memory Multiprocessing SystemADSP-21060/ADSP-21060L–7–REV. B0x0000 00000x0002 00000x0004 00000x0008 00000x0010 00000x0018 00000x0020 00000x0028 00000x0030 00000x0038 00000x003F FFFFMULTIPROCESSOR MEMORY SPACENORMAL WORD ADDRESSING: 32-BIT DATA WORDS48-BIT INSTRUCTION WORDS SHORT WORD ADDRESSING: 16-BIT DATA WORDSMS 0MS 1MS 2MS 3EXTERNAL MEMORY SPACEFigure 4.ADSP-21060/ADSP-21060L Memory MapCBUG and SHARCPAC are trademarks of Analog Devices, Inc.EZ-LAB is a registered trademark of Analog Devices, Inc.DEVELOPMENT TOOLSThe ADSP-21060 is supported with a complete set of software and hardware development tools, including an EZ-ICE In-Circuit Emulator, EZ-Kit, and development software. TheSHARC EZ-Kit is a complete low cost package for DSP evalua-tion and prototyping. The EZ-Kit contains a PC plug-in card (EZ-LAB ®) with an ADSP-21062 (5 V) processor. The EZ-Kit also includes an optimizing compiler, assembler, instruction level simulator, run-time libraries, diagnostic utilities and a complete set of example programs.The same EZ-ICE hardware can be used for the ADSP-21061/ADSP-21062, to fully emulate the ADSP-21060, with the excep-tion of displaying and modifying the two new SPORTS registers.The emulator will not display these two registers, but your code can use them.Analog Devices ADSP-21000 Family Development Software includes an easy to use Assembler based on an algebraic syntax,Assembly Library/Librarian, Linker, instruction-level Simulator,an ANSI C optimizing Compiler, the CBug™ C Source—Level Debugger and a C Runtime Library including DSP and math-ematical functions. The Optimizing Compiler includes Numeri-cal C extensions based on the work of the ANSI Numerical C Extensions Group. Numerical C provides extensions to the C language for array selections, vector math operations, complex data types, circular pointers and variably dimensioned arrays.The ADSP-21000 Family Development Software is available for both the PC and Sun platforms.The ADSP-21061 EZ-ICE Emulator uses the IEEE 1149.1JTAG test access port of the ADSP-21061 processor to monitor and control the target board processor during emulation. The EZ-ICE provides full-speed emulation, allowing inspection and modification of memory, registers, and processor stacks. Nonin-trusive in-circuit emulation is assured by the use of theprocessor’s JTAG interface—the emulator does not affect target system loading or timing.Further details and ordering information are available in the ADSP-21000 Family Hardware and Software Development Tools data sheet (ADDS-210xx-TOOLS). This data sheet can be requested from any Analog Devices sales office or distributor.In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the SHARC processor family. Hard-ware tools include SHARC PC plug-in cards multiprocessor SHARC VME boards, and daughter and modules with multiple SHARCs and additional memory. These modules are based on the SHARCPAC™ module specification. Third Party software tools include an Ada compiler, DSP libraries, operating systems and block diagram design tools.ADDITIONAL INFORMATIONThis data sheet provides a general overview of the ADSP-21060architecture and functionality. For detailed information on the ADSP-21000 Family core architecture and instruction set, refer to the ADSP-2106x SHARC User’s Manual, Second Edition .–8–ADSP-21060/ADSP-21060LREV. BPin Type FunctionADDR 31-0I/O/TExternal Bus Address . The ADSP-2106x outputs addresses for external memory and peripherals on these pins. In a multiprocessor system the bus master outputs addresses for read/writes of the internal memory or IOP registers of other ADSP-2106xs. The ADSP-2106x inputs addresses when a host processor or multiprocessing bus master is reading or writing its internal memory or IOP registers.DATA 47-0I/O/TExternal Bus Data . The ADSP-2106x inputs and outputs data and instructions on these pins. 32-bit single-precision floating-point data and 32-bit fixed-point data is transferred over bits 47–16 of the bus. 40-bit extended-precision floating-point data is transferred over bits 47–8 of the bus. 16-bit short word data is transferred over bits 31–16 of the bus. In PROM boot mode, 8-bit data is transferred over bits 23–16. Pull-up resistors on unused DATA pins are not necessary.MS 3-0O/TMemory Select Lines . These lines are asserted (low) as chip selects for the corresponding banks of external memory. Memory bank size must be defined in the ADSP-2106x’s system control register (SYSCON). The MS 3-0 lines are decoded memory address lines that change at the same time as the other address lines. When no external memory access is occurring the MS 3-0 lines are inactive; they are active however when a conditional memory access instruction is executed, whether or not the condition is true. MS 0 can be used with the PAGE signal to implement a bank of DRAM memory (Bank 0). In a multiprocessing system the MS 3-0 lines are output by the bus master.RD I/O/TMemory Read Strobe . This pin is asserted (low) when the ADSP-2106x reads from external memory devices or from the internal memory of other ADSP-2106xs. External devices (including other ADSP-2106xs) must assert RD to read from the ADSP-2106x’s internal memory. In a multiprocessing system RD is output by the bus master and is input by all other ADSP-2106xs.WR I/O/TMemory Write Strobe . This pin is asserted (low) when the ADSP-2106x writes to external memory devices or to the internal memory of other ADSP-2106xs. External devices must assert WR to write to the ADSP-2106x’s internal memory. In a multiprocessing system WR is output by the bus master and is input by all other ADSP-2106xs.PAGE O/TDRAM Page Boundary . The ADSP-2106x asserts this pin to signal that an external DRAM page boundary has been crossed. DRAM page size must be defined in the ADSP-2106x’s memory control register (WAIT). DRAM can only be implemented in external memory Bank 0; the PAGE signal can only be activated for Bank 0 accesses. In a multiprocessing system PAGE is output by the bus master.ADRCLK O/T Clock Output Reference . In a multiprocessing system ADRCLK is output by the bus master.SWI/O/TSynchronous Write Select . This signal is used to interface the ADSP-2106x to synchronous memory devices (including other ADSP-2106xs). The ADSP-2106x asserts SW (low) to provide an early indication of an impending write cycle, which can be aborted if WR is not later asserted (e.g., in a conditional write instruction). In a multiprocessing system, SW is output by the bus master and is input by all other ADSP-2106xs to determine if the multiprocessor memory access is a read or write.SW is asserted at the same time as the address output. A host processor using synchronous writes must assert this pin when writing to the ADSP-2106x(s).ACK I/O/SMemory Acknowledge . External devices can deassert ACK (low) to add wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other peripherals to hold off completion of an external memory access. The ADSP-2106x deasserts ACK as an output to add wait states to a synchronous access of its internal memory. In a multiprocessing system, a slave ADSP-2106x deasserts the bus master’s ACK input to add wait state(s) to an access of its internal memory.The bus master has a keeper latch on its ACK pin that maintains the input at the level it was last driven to.PIN FUNCTION DESCRIPTIONSADSP-21060 pin definitions are listed below. All pins are iden-tical on the ADSP-21060 and ADSP-21060L. Inputs identified as synchronous (S) must meet timing requirements with respect to CLKIN (or with respect to TCK for TMS, TDI). Inputs identified as asynchronous (A) can be asserted asynchronously to CLKIN (or to TCK for TRST ).Unused inputs should be tied or pulled to VDD or GND,except for ADDR 31-0, DATA 47-0, FLAG 3-0, SW , and inputs that have internal pull-up or pull-down resistors (CPA , ACK, DTx,DRx, TCLKx, RCLKx, LxDAT3-0, LxCLK, LxACK, TMS and TDI)—these pins can be left floating. These pins have a logic-level hold circuit that prevents the input from floating internally.A = Asynchronous G = Ground I = Input O = Output P = Power Supply S = Synchronous (A/D) = Active Drive (O/D) = Open DrainT = Three-State (when SBTS is asserted, or when the ADSP-2106x is a bus slave)。

DENON 收音环绕扩音机 AVR-2106 操作说明书

• 不能用報紙、桌布、窗簾等物品覆蓋通風口,以免妨 礙通風。 • 不能用报纸、桌布、窗帘等物品覆盖通风口,以免妨 碍通风。

• 應注意電池處置的環保問題。 • 应注意电池处置的环保问题。 • The use of apparatus in tropical and/or moderate climates. • 在熱帶和/或溫帶氣候下使用設備。 • 在热带和/或温带气候下使用设备。

Hold the plug when unplugging the cord.

避免在本機附近噴灑殺蟲劑,也勿用 苯、稀釋劑抹拭機箱。 避免在本机附近喷洒杀虫剂,也勿用 苯、稀释剂抹拭机箱。

警告:爲防止火災或電擊,請勿將本機暴露於雨中或潮濕的處所。

• 留意電源線。 從插座拔出插頭時應抓住插頭將 其拔出。 • 留意电源线。 从插座拔出插头时应抓住插头将 其拔出。

page 37 page 37, 38

page 38 page 38 page 39 page 39

中文简体字

序言 欢迎选购DENON AVR-2106 收音环绕扩音机。经过我们的精心设计,本品能通过您的家庭影院试 听系统,如DVD产生无与伦比的超值的环绕试听享受,同时还能高保真的重现您所喜爱的音乐。 由于本品提供了阵容强大的功能,我们建议您在安装和使用前,请仔细阅读本说明书的内容。 序言

· 如图所示将遥控器指向主机上的遥感传感器。 · 遥控器可以在离主机约7米的直线距离内使用。不过,如果遥控器与传感器之间有障碍物或 没有对准遥感传感器,这个距离会缩短。 · 遥控器可在与遥感传感器水平30度角内使用。

注意:为防电击,请勿打开机盖(或后盖)。本机内部无使用者可以维修的部件。请委托有资格的技术

人员进行维修。 等边三角形中有箭头闪电标号的图形表示警告使用者在产品内有非绝缘的“危险电压”,可能 会对人体造成很大的电击危险。 等边三角形中有感叹号的图形表示警告使用者该设备在操作与维护(维修)方面应严格按照所附 设备说明书。

ICE Analog Devices ADSP-21062-KS-160 说明书

S e r v i ng t h l S e m i c o n d u c t o r I n d u s t r yS i n c e 19INDEX TO TEXTTITLE PAGEINTRODUCTION1 MAJOR FINDINGS1TECHNOLOGY DESCRIPTIONAssembly2Die Process 2 - 3ANALYSIS RESULTS IAssembly 4ANALYSIS RESULTS IIDie Process and Design 5 - 7 ANALYSIS PROCEDURE8TABLESOverall Evaluation 9Package Markings10 Wirebond Strength10 Die Material Analysis10 Horizontal Dimensions11 Vertical Dimensions12INTRODUCTIONThis report describes a construction analysis of the Analog Devices ADSP-21062-KS-160 SHARC Digital Signal Processor. One device which was packaged in a 240-pin Plastic Quad Flat Package (PQFP) was received for the analysis. The device was date coded 9630.MAJOR FINDINGSQuestionable Items:1•Metal 2 aluminum thinned up to 90 percent2 at vias (Figure 16).Special Features:•Sub-micron gate lengths (0.55 micron).1These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.2Seriousness depends on design margins.TECHNOLOGY DESCRIPTIONAssembly:•The device was packaged in a 240-pin Plastic Quad Flat Package (PQFP). A copper heat slug (heatsink) was employed on the top of the package (cavity downorientation). It was internally connected to ground to bias the substrate.•Wirebonding method: A thermosonic ball bond technique employing 1.2 mil O.D.gold wire was used.•Dicing: Sawn (full depth) dicing.•Die attach: A silver epoxy compound.Die Process•Fabrication process: Selective oxidation CMOS process employing a twin-well process in a P substrate.•Die coat: No die coat was used on the device.•Final passivation: A layer of nitride over a layer of silicon-dioxide.•Metallization: Two levels of metal defined by standard dry-etch techniques. Metal 2 consisted of aluminum with a titanium-nitride cap and a titanium barrier. Metal 1consisted of aluminum, a titanium nitride cap and barrier, and a titanium adhesionlayer. Standard vias were used between metal 2 and metal 1. Tungsten plugs were used as the vertical interconnect under metal 1.•Interlevel dielectric: Interlevel dielectric consisted of two layers of silicon-dioxide with a planarizing spin-on-glass (SOG) between them.TECHNOLOGY DESCRIPTION(continued)•Pre-metal dielectric: This dielectric consisted of a layer of reflow glass over densified oxide.•Polysilicon: Two layers of polysilicon were used on the die. Poly 1 (polysilicon and tungsten silicide) was used to form redundancy fuses, all gates on the die, and word lines in the array. Poly 2 was used to form “pull-up” resistors in the cellarray, and formed resistors in fuse blocks which were connected to one end of the poly 1 fuses. Both poly layers were defined by a dry-etch of good quality.•Diffusions: Implanted N+ and P+ diffusions formed the sources/drains of transistors. No silicide was present on diffusions. An LDD process was used with the oxide sidewall spacers left in place. N+ diffusions were “pushed down” attungsten contacts.•Wells: Planar (no step in LOCOS) twin-well process in a P substrate. No epi layer.•Redundancy: Fuses consisting of poly 1 were present on the die. Passivation and interlevel dielectric cutouts were made over the fuses. One end of the fuse structure was connected to metal 1, while the other end was connected to a poly 2 resistor.Some laser blown fuses were noted.•Memory cells: The die employed a 2 Mbit SRAM array. The memory cells used a 4T CMOS SRAM cell design. Metal 2 distributed GND and Vcc (via Metal 1), and formed the bit lines using metal 1 links. Metal 1 was used as the “piggy-back”word lines. Poly 1 formed the word lines, select, and storage gates. Poly 2 formed “pull-up” resistors and distributed Vcc.•Design features: Slotted and beveled Metal 2 bus lines were employed for stress relief. Both metals 1 and 2 were used in the bond pads.Assembly:Figures 1 - 3 Questionable Items:1 None.Special Features: None.General Items:•Overall package: The device was packaged in a 240-pin PQFP. A large copper heat slug (heatsink) was employed on the top of the package (cavity down orientation). It was internally connected to GND and the substrate.•Wirebonding method: A thermosonic ball bond technique employing 1.2 mil gold wire was used. All bonds were well formed and placed. Bond strengths werenormal as determined by wire pull tests.•Dicing: Sawn (full depth). No large chips or cracks were noted.•Die attach: A silver epoxy compound of normal quality.1These items present possible quality or reliability concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.Die Process and Design:Figures 4 - 45 Questionable Items:1•Metal 2 aluminum thinned up to 90 percent2 at vias (Figure 16).Special Features:•Sub-micron gate lengths (0.55 micron).General Items:•Fabrication process: Selective oxidation CMOS process employing twin-wells in a P substrate.•Process implementation: Die layout was clean efficient. Alignment was good at all levels.•Die surface defects: None. No contamination, toolmarks or processing defects were noted.•Passivation: A layer of nitride over a layer of silicon-dioxide. Passivation coverage and edge seal were good.•Metallization: Two levels of metallization. Metal 2 consisted of aluminum with titanium-nitride cap and titanium barrier. Metal 1 consisted of aluminum, titanium-nitride cap and barrier, and a titanium adhesion layer. Standard vias were usedbetween metal 2 and 1. Tungsten plugs were employed under metal 1.1These items present possible quality concerns. They should be discussed with the manufacturer to determine their possible impact on the intended application.2Seriousness depends on design margins.•Metal patterning: All metal layers were defined by a dry etch of good quality.•Metal defects: None. No voiding, notching or cracking of the metal layers was found. No silicon nodules were found following removal of the aluminum.•Metal step coverage: Metal 2 aluminum thinned up to 90 percent at most vias. The barrier aided in retaining the connections. Virtually no metal thinning was noted in metal 1. The tungsten plugs were nearly level with the oxide surface, so no large steps were present for the metal to cover.•Vias and contacts: Vias were defined by a two step process while contacts were defined by a dry-etch. No significant over-etching was noted.•Interlevel dielectric: Interlevel dielectric consisted of two layers of silicon-dioxide with a spin-on-glass (SOG) to aid in planarization.•Pre-metal dielectric: This dielectric consisted of a layer of reflow glass over densified oxide. No problems were found..•Polysilicon: Two layers of polysilicon were employed. Poly 1 (polysilicon and tungsten silicide) formed the redundancy fuses, all gates on the die, and word lines in the array. Poly 2 was used to form resistors in the cell array and outside the fuse blocks. Definition was by a dry etch of good quality. No problems were found.•Isolation: LOCOS (local oxide isolation). No problems were noted and no step was present at the well boundaries.•Diffusions: Implanted N+ and P+ diffusions were used for sources and drains.Deep (pushed down) N+ diffusions were noted under contacts in N regions.Diffusions were not silicided. No problems were found.•Wells: Twin-wells were employed in a P substrate. No step was present at the well boundaries, but both wells were delineated by a silicon etch. No problems were noted.•Buried contacts: Direct poly-to-diffusion (buried) contacts were only used in the SRAM array. No problems were found in these areas.•Redundancy: Poly 1 fuses were present along the row and column decode logic outside the array. Passivation and interlevel dielectric cutouts were made over the fuses. Laser blown fuses were noted.•Memory cells: The die employed a 2 Mbit SRAM array. The memory cells used a 4T CMOS SRAM cell design. Metal 2 distributed GND and Vcc, and formed the bit lines using metal 1 links. Metal 1 was used as the “piggy-back” word lines.Poly 1 formed the word lines, select, and storage gates. Poly 2 formed “pull-up”resistors and distributed Vcc. Cell size was 3.3 x 5.7 microns (19 microns2).PROCEDUREThe devices were subjected to the following analysis procedures:External inspectionX-rayDelidSEM of passivationPassivation integrity test (chemical)Wirepull testPassivation removalSEM inspection of metal 2Aluminum 2 removalDelayer to metal 1 and inspectAluminum 1 removal and inspect barrierDelayer to polycide/substrate and inspectDie sectioning (90° for SEM)*Measure horizontal dimensionsMeasure vertical dimensionsDie material analysis*Delineation of cross-sections is by silicon etch unless otherwise indicated.OVERALL QUALITY EVALUATION: Overall Rating: NormalDETAIL OF EVALUATIONPackage integrity:GDie placement:GDie attach quality:GWire spacing:NWirebond placement:NWirebond quality:GDicing quality:GWirebond method Thermosonic ball bonds using 1.2 milgold wire.Die attach method Silver-epoxyDicing Sawn (full depth)Die surface integrity:Toolmarks (absence)GParticles (absence)GContamination (absence)GProcess defects (absence)GGeneral workmanship NPassivation integrity GMetal definition GMetal integrity NP*Metal registration GContact coverage GContact registration G*Metal 2 aluminum thinning up to 90 percent.G = Good, P = Poor, N = Normal, NP = Normal/PoorPACKAGE MARKINGSTOP(LOGO) ANALOG DEVICESADSP-210629630KS-160HD/BA5454.1-1.2 (SHARC LOGO)BOTTOMS6 2A2HONG KONGWIREPULL TESTSample1# of wires tested: 22Bond lifts: 0Force to break - high: 12g- low: 8g- avg.: 9.1g- std. dev.: 0.5DIE MATERIAL IDENTIFICATIONOverlay passivation:Nitride over silicon-dioxide. Metallization 2:Aluminum with a titanium-nitride cap and atitanium barrier.Interlevel dielectric:Multiple layers of silicon-dioxide. Metallization 1:Aluminum with a titanium-nitride cap and barrier, and a titanium adhesion layer.Plugs:Tungsten.Pre-metal glass:Silicon-dioxide.Silicide (Poly 1):Tungsten.Die size:11.9 x 14.9 mm (468 x 586 mils) Die area:177 mm2 (274,248 mils2)Min pad size:0.11 x 0.11 mm (4.4 x 4.4 mils) Min pad window:0.09 x 0.09 mm (3.7 x 3.7 mils) Min pad space:40 micronsMin metal 2 width:0.7 micronMin metal 2 space: 1.0 micronMin metal 2 pitch: 1.7 micronMin metal 1 width:0.6 micronMin metal 1 space:0.7 micronMin metal 1 pitch: 1.3 micronMin via:0.65 micron (round)Min contact:0.5 micron (round)Min polycide width:0.55 micronMin polycide space:0.8 micronMin gate length* - (N-channel):0.55 micron- (P-channel):0.55 micronMin LOCOS:0.8 micronSRAM cell size:19.0 microns2SRAM cell pitch: 3.3 x 5.7 microns*Physical gate length.Die thickness:0.5 mm (21 mils)LayersPassivation 2:0.6 micron Passivation 1:0.15 micronMetal 2 - cap:0.05 micron (approx.) - aluminum:0.75 micron- barrier:0.17 micron Interlevel dielectric - glass 2:0.5 micron (average) - glass 1: 0.15 micron (average) Metal 1 - cap:0.05 micron (approx.) - aluminum:0.5 micron- barrier:0.1 micron- plugs:0.6 - 1.0 micronPre-metal glass:0.6 micron (average) Polycide - silicide:0.1 micron- poly:0.13 micronLocal oxide:0.4 micronN+ S/D diffusion:0.2 micronDeep N+ S/D diffusion:0.4 micronP+ S/D diffusion:0.2 micronN-well: 2.0 microns (approx.) P-well: 2.5 microns (approx.)INDEX TO FIGURESASSEMBLY Figures 1 - 3 DIE LAYOUT AND IDENTIFICATION Figures 4 - 9 PHYSICAL DIE STRUCTURES Figures 10 - 46 COLOR DRAWING OF DIE STRUCTURE Figure 31 EEPROM MEMORY CELL STRUCTURES Figures 32 - 40 CIRCUIT LAYOUT AND I/O Figures 41 - 46sidetopMag. 6500xMag. 800xEDGE OF PASSIVATIONEDGE OF PASSIVATIONDIEN+METAL 1METAL 2PIN 1F i g u r e 9. O p t i c a l v i e w s o f d i e c o r n e r s . M a g . 80x .Integrated Circuit Engineering CorporationAnalog Devices ADSP-21062-KS-160SLOTPASSIVATION 1PASSIVATION 2PASSIVATION 2METAL 2METAL 2METAL 1METAL 1W PLUGW PLUGN+ S/DPOLY 1 GATEPOLY 1 GATELOCOSLOCOSMag. 4600xPASSIVATION 2PASSIVATION 1 METAL2INTERLEVEL DIELECTRICMag. 26,000xTIN CAPALUMINUM 2TiN BARRIERMag. 3200xMag. 6500xMag. 6500xMASK CHANGESMETAL 2VIASMag. 10,000xMag. 10,000xMag. 20,000xALUMINUM 2TiN CAPTi BARRIERMag. 13,000xMag. 26,000xMag. 52,000xPASSIVATION 2METAL 2METAL 2METAL 2INTERLEVEL DIELECTRICMETAL 1METAL 1METAL 190% THINNINGPOLY 1LOCOSSOGMag. 52,000xMag. 26,000xPASSIVATIONINTERLEVEL DIELECTRICMETAL 1SOGALUMINUM 1TiN CAPTiN BARRIERTi ADHESION LAYERVIAMag. 5000xMag. 10,000xMag. 20,000xALUMINUM 1TiN CAPTiN BARRIERMag. 32,000xMag. 16,000xTiN BARRIERW PLUGMETAL1W PLUGPOLY1LOCOSMETAL1W PLUGLOCOSN+DEEP N+METAL1W PLUGP+Mag. 3200xMag. 3200xMag. 5000xP+N+POLY 1Mag. 8000xMag. 12,000xMag. 32,000xDIFFUSIONLOCOSPOLY 1 GATEN-channelP-channelglass etchW SILICIDE POLY 1POLY 1GATEPOLY 1GATEGATE OXIDEGATE OXIDEP+ S/DN+ S/DDEEP N+ S/DREFLOW GLASSREFLOW GLASSSIDEWALL SPACERFigure 25. SEM section view of a typical birdsbeak. Mag. 52,000x.Mag. 1200xMag. 6500xDENSIFIED OXIDEPOLY 1P-SUBSTRATEP-WELLP-WELLN-WELLLOCOSLOCOSMETAL 2P+N+GATE OXIDEMag. 750xBLOWN FUSEMag. 1600xINTACT FUSELASER BLOWN FUSEPASSIVATIONCUTOUTBLOWN FUSE Mag. 2400xPASSIVATIONCUTOUTMag. 6500xMag. 13,000xMag. 13,000xCUTOUTCUTOUTPOLY 2METAL 2METAL 1PASSIVATION 2REFLOW GLASSLOCOSLOCOSPOLY 1FUSEPOLY 1FUSEPOLY 1 FUSEmetal 2metal 1unlayeredGNDGNDGNDBITBITBITBITWORD“PIGGY BACK”WORD LINEPOLY2POLY2 POLY1POLY1POLY1 WORD LINEmetal 2metal 1unlayeredWORD LINE“PIGGYBACK”WORD LINEGND V CCGND BITBITmetal 2GNDGNDBITBITBITBIT“PIGGYBACK”WORD LINEV CCunlayeredWORDBITBITR1143R22BITGNDGNDV CC。

LPC2106 RS232 QuickStart Board 用户指南说明书